# SYSTEM DESIGN OF A WIDE BANDWIDTH CONTINUOUS-TIME SIGMA-DELTA MODULATOR

A Thesis

by

VIJAYARAMALINGAM PERIASAMY

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

May 2010

Major Subject: Electrical Engineering

# SYSTEM DESIGN OF A WIDE BANDWIDTH CONTINUOUS-TIME SIGMA-DELTA MODULATOR

#### A Thesis

by

# VIJAYARAMALINGAM PERIASAMY

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

# Approved by:

Chair of Committee, Aydin I. Karsilayan Committee Members, Jose Silva-Martinez

Peng Li

Duncan M. Walker

Head of Department, Costas Georghiades

May 2010

Major Subject: Electrical Engineering

iii

#### **ABSTRACT**

System Design of a Wide Bandwidth Continuous-Time Sigma-Delta Modulator.

(May 2010)

Vijayaramalingam Periasamy, B.Tech, National Institute of Technology,

Tiruchirappalli, India

Chair of Advisory Committee: Dr. Aydin I. Karsilayan

Sigma-delta analog-to-digital converters are gaining in popularity in recent times because of their ability to trade-off resolutions in the time and voltage domains. In particular, continuous-time modulators are finding more acceptance at higher bandwidths due to the additional advantages they provide, such as better power efficiency and inherent anti-aliasing filtering, compared to their discrete-time counterparts.

This thesis work presents the system level design of a continuous-time low-pass sigmadelta modulator targeting 11 bits of resolution over 100MHz signal bandwidth. The design considerations and tradeoffs involved at the system level are presented. The individual building blocks in the modulators are modeled with non-idealities and specifications for the various blocks are obtained in detail. Simulation results obtained from behavioral models of the system in MATLAB and Cadence environment show that a signal-to-noise-and-distortion-ratio (SNDR) of 69.6dB is achieved.

A loop filter composed of passive LC sections is utilized in place of integrators or resonators used in traditional modulator implementations. Gain in the forward signal path is realized using active circuits based on simple transconductance stages. A novel method to compensate for excess delay in the loop without using an extra summing amplifier is proposed.

# **ACKNOWLEDGEMENTS**

Graduate school at the AMSC group has been a wonderful experience and I would like to thank the people who made it possible.

I would like to thank my advisor, Dr Aydin Karsilayan, for giving the opportunity to pursue my MS thesis under his guidance. I'm greatly indebted to him for his constant support throughout my graduate studies in both academic and personal matters. He set a perfect example for me to look up to with his methodical approach to solving problems and his attention to detail. I would like to thank both Dr. Karsilayan and Dr. Jose Silva-Martinez for having faith in me and giving me the chance to work on the sigma-delta modulator project. Discussions with both professors have been a great learning experience giving me the chance to appreciate the intricacies of circuit design. I would also like to thank Dr. Peng Li and Dr. Duncan Walker for being part of my thesis committee.

I would like to express my gratitude to all the professors who handled courses that I took during graduate studies for sharing their expertise with us. Thanks to Ella Gallagher, Tammy Carda and Jeanie Marshall for helping and advising with all manner of administrative work.

I would like to thank my team members, Aravind Kumar Padyana, Cheng-Ming Chien and Seokmin Hwang, for making work on the project a good experience. Thanks are due to graduate students at the group who had worked on sigma-delta projects earlier and were kind enough to share their knowledge with us — Manisha Gambhir, Fabian Silva-Rivas, Cho-Ying Lu, Vijayakumar Dhanasekaran. Being part of the sigma-delta project with Cho-Ying Lu, Marvin Onabajo, Venkata Gadde and Barry Chen was a good learning exercise and thanks for the same. Thanks to all my friends in the AMSC group for making the stay here an enjoyable one.

Financial support towards my graduate studies from the Analog & Mixed Signal Center by means of the Texas Instruments Fellowship is gratefully acknowledged.

I'm really thankful for the love and support that I have received from my family. My parents and brothers have stood by me in every endeavor of mine and I'm very grateful for the same.

# TABLE OF CONTENTS

|                                |                  | Page     |

|--------------------------------|------------------|----------|

| ABSTRACT                       |                  | iii      |

| ACKNOWLEDGEMENTS               |                  | iv       |

| TABLE OF CONTENTS              |                  | vi       |

| LIST OF FIGURES                |                  | viii     |

| LIST OF TABLES                 |                  | xi       |

| 1. INTRODUCTION                |                  | 1        |

| 1.1 Thesis organization        |                  | 3        |

| 2. OVERSAMPLING ANALOG-TO-DIC  | GITAL CONVERTERS | 4        |

|                                |                  | 4        |

| <u> </u>                       |                  | 6        |

|                                |                  | 7        |

| 7.2                            | ors              | 10<br>11 |

| 3. SYSTEM LEVEL DESIGN OF MODU | JLATOR           | 13       |

| 3.1 Design considerations      |                  | 13       |

| =                              | ion              | 17       |

| 3.3 Loop filter implementation |                  | 20       |

| •                              |                  | 25       |

|                                |                  | 29       |

| 3.6 Results                    |                  | 32       |

| 4. MODELING OF NON-IDEALITIES  |                  | 34       |

|                                | luctors          | 34       |

|                                | nsconductors     | 34       |

| <u> </u>                       | nsconductors     | 35       |

|                                |                  | 36       |

| 4.2 Non-idealities in the DAC  |                  | 37       |

|    |         |                                                             | Page |

|----|---------|-------------------------------------------------------------|------|

|    |         | 4.2.1 Element mismatch                                      | 37   |

|    |         | 4.2.2 Output resistance of the DAC                          | 39   |

|    | 4.3     | Quantizer non-idealities                                    | 39   |

|    |         | 4.3.1 Excess loop delay                                     | 39   |

|    |         | 4.3.2 Offset voltage                                        | 39   |

|    | 4.4     | Clock jitter                                                | 41   |

|    |         | 4.4.1 Modeling jitter                                       | 43   |

|    | 4.5     | Non-ideal inductor                                          | 45   |

|    | 4.6     | Thermal noise                                               | 46   |

|    | 4.7     | Variation of pole locations                                 | 48   |

|    | 4.8     | Results                                                     | 50   |

| 5. | EXCESS  | S LOOP DELAY                                                | 52   |

|    | 5.1     | Effect on stability                                         | 52   |

|    | 5.2     | Compensation techniques                                     | 53   |

|    |         | 5.2.1 Compensation using a direct path around the quantizer | 53   |

|    |         | 5.2.2 Compensation using digital differentiator             | 54   |

|    | 5.3     | Proposed compensation technique                             | 56   |

| 6. | SUMMA   | ARY                                                         | 61   |

|    | 6.1     | Specifications                                              | 61   |

|    | 6.2     | Results                                                     | 69   |

| 7. | CONCL   | USIONS                                                      | 71   |

|    | 7.1     | Future work                                                 | 71   |

| RI | EFERENC | CES                                                         | 72   |

| ΑI | PPENDIX | A VERILOG-A CODES                                           | 76   |

|    | A.1     | Verilog-A code for quantizer                                | 76   |

|    | A.2     | Verilog-A code for DAC driver                               | 81   |

| ΑI | PPENDIX | B MATLAB CODE                                               | 83   |

|    | B.1     | MATLAB code to synthesize loop filter                       | 83   |

| VI | TA      |                                                             | 85   |

# LIST OF FIGURES

| FIGURI | 3                                                             | Page |

|--------|---------------------------------------------------------------|------|

| 1      | Comparison of radio architectures                             | 1    |

| 2      | Signal processing chain                                       | 4    |

| 3      | Quantization noise probability density function               | 5    |

| 4      | Oversampled quantization noise power spectral density profile | 7    |

| 5      | First order sigma-delta modulator                             | 8    |

| 6      | First order modulator quantization noise profile              | 9    |

| 7      | Noise transfer function                                       | 15   |

| 8      | SNR vs input amplitude of discrete-time system                | 16   |

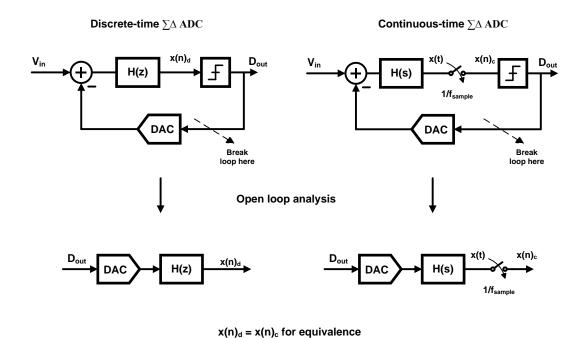

| 9      | Equivalence of discrete and continuous-time modulators        | 17   |

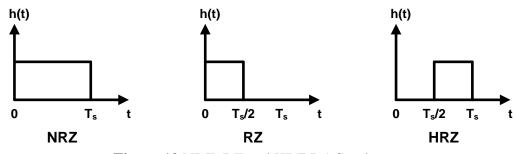

| 10     | NRZ, RZ and HRZ DAC pulses                                    | 18   |

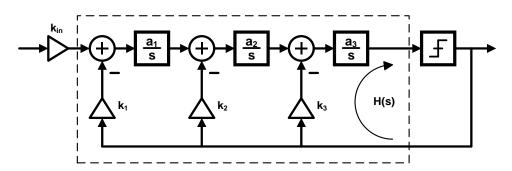

| 11     | Feedback configuration                                        | 20   |

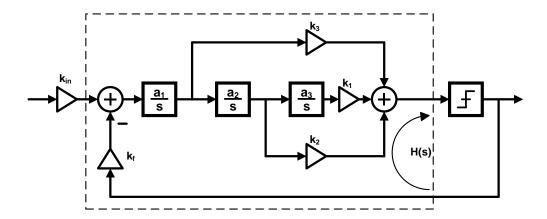

| 12     | Feed-forward configuration                                    | 21   |

| 13     | Proposed loop filter                                          | 22   |

| 14     | Modulator implementation                                      | 24   |

| 15     | MATLAB model of the system                                    | 27   |

| 16     | MATLAB coefficient extraction setup                           | 28   |

| 17     | Cadence schematic of the system                               | 31   |

| 18     | Output spectrum from ideal behavioral model                   | 32   |

| 19     | Loop filter                                                   | 33   |

| FIGURI | 3                                                                         | Page |

|--------|---------------------------------------------------------------------------|------|

| 20     | Closed loop transfer functions                                            | 33   |

| 21     | Transconductor model                                                      | 36   |

| 22     | Output spectrum with peaking                                              | 37   |

| 23     | Monte-Carlo simulations for offset voltage of comparators                 | 40   |

| 24     | Effect of clock jitter on different feedback DAC pulses                   | 42   |

| 25     | Modeling effect of clock jitter                                           | 44   |

| 26     | Clock jitter model in MATLAB                                              | 44   |

| 27     | SNR as a function of clock jitter                                         | 45   |

| 28     | Non-ideal inductor                                                        | 46   |

| 29     | Noise sources in the loop filter                                          | 47   |

| 30     | SNR variations with change in values of L and C                           | 48   |

| 31     | Variation of SNR with change in the R & C values of 3 <sup>rd</sup> stage | 49   |

| 32     | Output spectrum of modulator with non-idealities                          | 50   |

| 33     | Two-tone simulation of modulator with non-idealities                      | 51   |

| 34     | Continuous-time sigma-delta modulator with excess loop delay              | 52   |

| 35     | Feedback pulse in a modulator with excess loop delay                      | 52   |

| 36     | Loop delay compensation with direct path around quantizer                 | 53   |

| 37     | Principle of direct path compensation scheme                              | 54   |

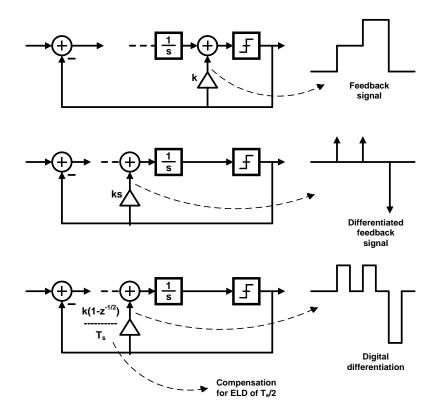

| 38     | Principle of digital differentiator compensation scheme                   | 55   |

| 39     | Modulator with digital differentiator based compensation scheme           | 56   |

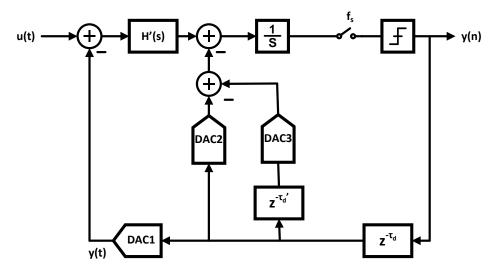

| 40     | Proposed loop delay compensation scheme                                   | 57   |

| FIGUR | E                                                                              | Page |

|-------|--------------------------------------------------------------------------------|------|

| 41    | Output spectrum with proposed loop delay compensation                          | 60   |

| 42    | Modulator implementation with proposed loop compensation                       | 61   |

| 43    | MATLAB model of complete system with clock jitter                              | 64   |

| 44    | Cadence schematic of the complete system with proposed loop delay compensation | 65   |

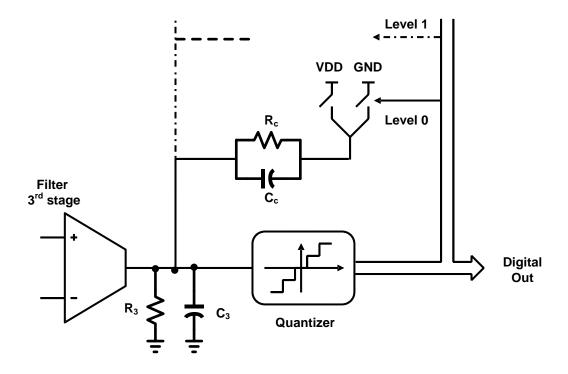

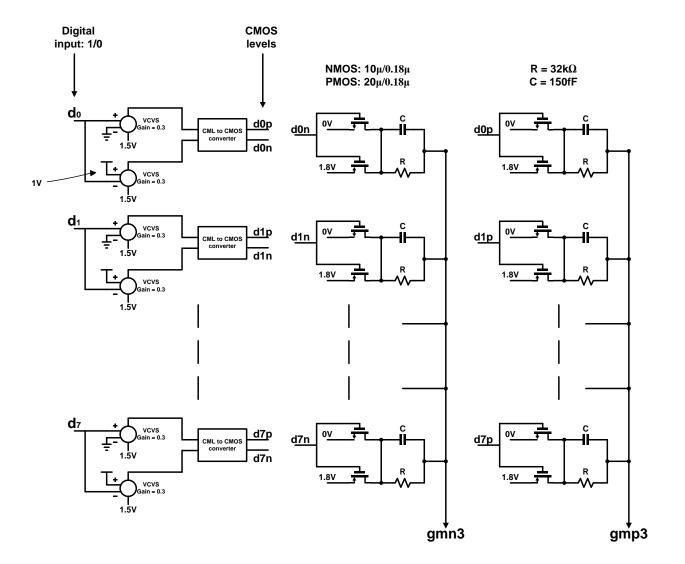

| 45    | DAC implementation.                                                            | 66   |

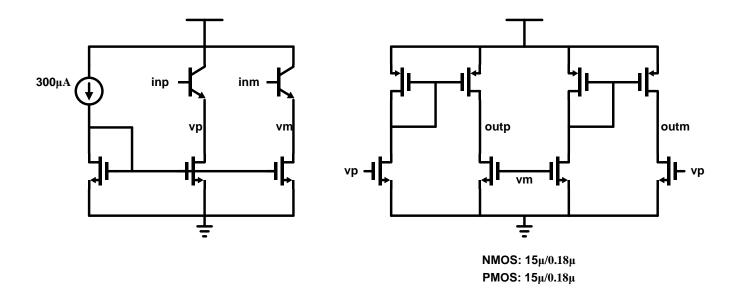

| 46    | Loop delay compensation circuit                                                | 67   |

| 47    | CML-to-CMOS converter                                                          | 68   |

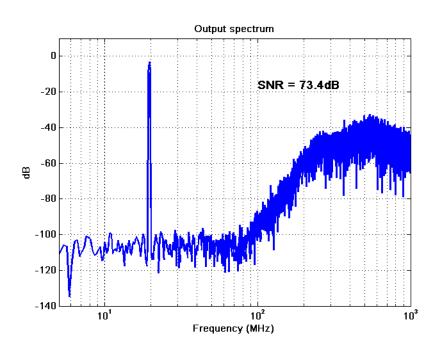

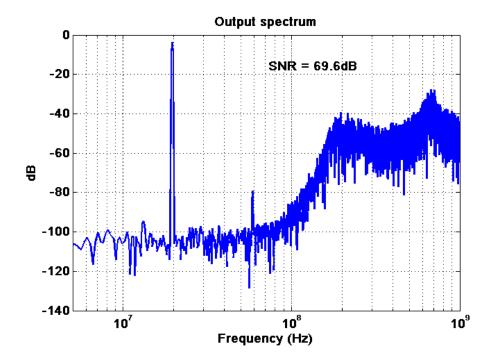

| 48    | Output spectrum from complete system simulation                                | 69   |

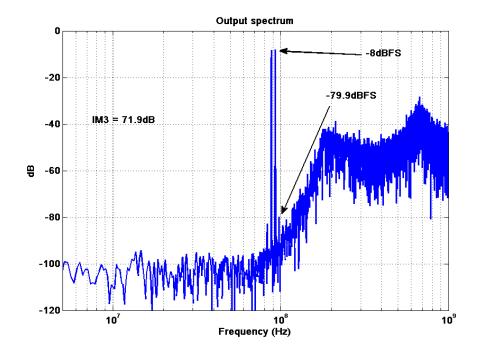

| 49    | Two-tone simulation at complete system level                                   | 70   |

# LIST OF TABLES

| TABLE |                                                        | Page |

|-------|--------------------------------------------------------|------|

| 1     | Brief summary of wide bandwidth sigma-delta modulators | 11   |

| 2     | Specifications                                         | 13   |

| 3     | Noise transfer function parameters                     | 15   |

| 4     | Modulator component values                             | 24   |

| 5     | Transconductor non-linearity specifications            | 35   |

| 6     | Transconductor excess phase specifications             | 36   |

| 7     | DAC output resistance specification                    | 39   |

| 8     | Input referred RMS noise values                        | 48   |

| 9     | Loop delay compensation circuit parameters             | 60   |

| 10    | Component values                                       | 62   |

| 11    | Transconductor specifications                          | 62   |

| 12    | DAC specifications.                                    | 62   |

| 13    | Quantizer specifications.                              | 63   |

| 14    | Clock specifications                                   | 63   |

| 15    | System performance                                     | 70   |

#### 1. INTRODUCTION

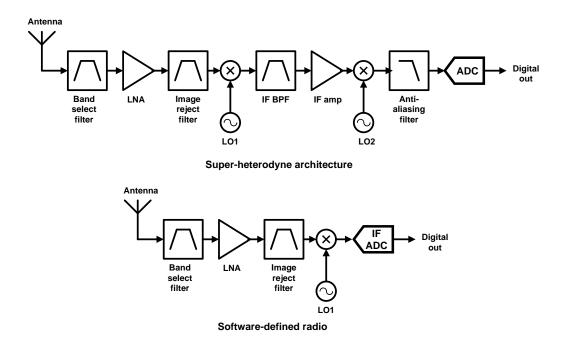

Technological evolution in the semiconductor industry in the past couple of decades has been following Moore's law, which aims to pack higher digital functionality into a smaller area coupled with smaller power consumption continuously over time. This has made available vast amount of computing power in the digital realm that has resulted in many applications going 'digital', such as storage and communications. This shift is especially apparent in the field of communication where there is a push to perform as much of the processing in the digital domain as possible, with little RF and analog preprocessing. This fact is highlighted in Fig. 1 that compares the traditional superheterodyne receiver architecture with that of software defined radio.

Figure 1 Comparison of radio architectures

As can be seen in the Fig. 1, in the traditional architecture, digitization is preceded by significant analog processing (down-conversion, filtering, and amplification). In the more digital intensive software-defined radio architecture, the signal is digitized much

This thesis follows the style of IEEE Journal of Solid State Circuits.

earlier enabling the performing of filtering and amplification operations in digital with more flexibility. This however places much higher requirements of bandwidth and dynamic range on the analog-to-digital converter. Also, the quest for higher data rates is leading to the proliferation of standards with larger signal bandwidths. This again reinforces the need for wide bandwidth analog-to-digital converters.

Traditionally, ADCs with sampling rates in the range of 100MSPS and above have been Nyquist-sampling based ones. However, the use of oversampling ADCs in their place can provide power and cost improvements at the system level because of their inherent advantages like simpler anti-aliasing filtering. As mentioned above, there has been tremendous advancement in silicon technologies in the past decade. This results in the availability of very fast devices that gives additional motivation to use oversampling converters that make use of resolution in the time domain while trading off with resolution in the voltage domain.

Oversampling ADCs can be divided into two categories based on the point in the signal chain where sampling takes place: discrete-time (DT), which are built using switched-capacitor filters and continuous-time (CT), which, as their name suggests, are implemented using continuous-time filters. CT sigma-delta ADCs are becoming more popular recently than DT ADCs primarily because of their reduced settling time requirements that results in better power efficiency. Also, they present a constant load to the previous driver stage in place of the switching capacitive load in case of discrete-time sigma-delta modulators. This results in additional power savings in the driver stage. In addition, they have some other advantages like inherent anti-aliasing and reduced sample-and-hold requirements. However, they do have some drawbacks like increased sensitivity to clock jitter, susceptibility to time constant variations and excess loop delay. In spite of these shortcomings, there has been a tremendous interest in continuous-time sigma-delta ADCs as seen by papers published in the recent literature [1-10].

In this work, the design of a wide-bandwidth (100MHz) continuous-time sigma-delta modulator providing 11 bits of resolution is presented. The loop filter is designed using

passive LC sections instead of the conventional implementation using active integrators or resonators. The system level design is done in MATLAB using the  $\sum \Delta$  toolbox. Excess loop delay is a critical issue in continuous-time modulators, especially when the loop is being operated at a high sampling frequency. In this work, a novel scheme to compensate for excess loop delay is presented.

#### 1.1 Thesis organization

The organization of the thesis is highlighted next.

Section 2 presents an overview of analog-to-digital conversion. The concepts of oversampling and noise shaping are introduced. A literature survey of recent wide bandwidth sigma-delta modulators is presented as well.

Section 3 presents the system design of a continuous-time sigma-delta modulator. The use of tools such as MATLAB and Verilog-A in the design process is highlighted.

Section 4 presents the incorporation of non-idealities into the ideal model built in the previous section. Specifications for the individual building blocks are derived in this section.

Section 5 focuses on the problem of excess loop delay in continuous-time sigma-delta modulators. Various compensation methods found in literature and the method proposed in this work are detailed.

Section 6 summarizes the work by presenting the entire system along with the specifications for the individual blocks.

Section 7 presents the conclusions and also some directions for future work.

#### 2. OVERSAMPLING ANALOG-TO-DIGITAL CONVERTERS

#### 2.1 Introduction

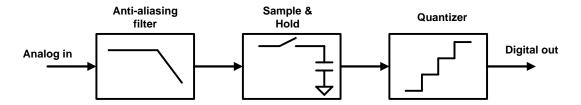

Signals in the real world like sound, temperature and pressure are analog in nature. However, with the progress in semiconductor technology and the availability of vast processing power in the digital domain, more and more signal processing operations are performed on the digital side. Digital signals, by their very nature, are defined only at discrete instances of time and can only take discrete values of amplitude as opposed to the continuous-time, continuous-amplitude nature of analog signals. Analog-to-digital converters serve as the interface between these two domains. A typical signal processing chain is shown in Fig. 2.

Figure 2 Signal processing chain

Assume that the input analog signal has useful content up to a frequency of f<sub>b</sub>. The sample and hold block in Fig. 2 performs the operation of converting the continuous-time signal into discrete-time. To perform this operation without a loss of information, the sampling frequency has to satisfy the following relationship as specified by the Nyquist criterion.

$$f_{sample} \ge 2.f_b$$

(2.1)

Note that the above criterion makes sure that the required signal content less than the frequency  $f_b$  is not lost due to sampling. However, if the input signal has other frequency content higher than  $f_b$ , the sampled signal can be corrupted due to a process known as aliasing. The anti-aliasing filter (AAF) in the signal chain prior to the sample and hold

block prevents this from happening by removing any frequencies higher than  $f_b$  before it is sampled.

The output of the sample and hold block, while being discrete in time, still spans a continuous range of values in amplitude. The conversion from continuous to discrete amplitudes is done by the quantizer. While the discretization process in time is lossless, the operation of the quantizer is inherently lossy. The error introduced by this quantization process is dependent on the number of levels in the quantizer.

Assume that the quantizer has a full-scale value of  $\pm Vref$  and outputs N digital bits. The step size,  $\Delta$ , of such a quantizer is given by,

$$\Delta = \frac{2V_{ref}}{2^N} \tag{2.2}$$

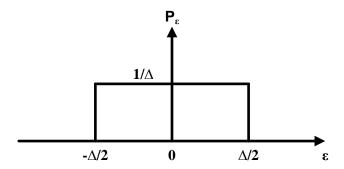

In such a quantizer, the error,  $\varepsilon$ , introduced in the quantization operation at every sampling instant will lie in the range  $(-\Delta/2, \Delta/2)$ . Even though we know the value of the quantization error at sampling instant, if the input signal is sufficiently 'busy', then the behavior of the quantization error can be considered a white noise process with the probability density function as shown in Fig. 3 [11].

Figure 3 Quantization noise probability density function

The quantization noise introduced can hence be computed as,

$$\sigma_{\varepsilon}^{2} = \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} \epsilon^{2} \cdot \frac{1}{\Delta} \cdot d\varepsilon = \frac{\Delta^{2}}{12}$$

(2.3)

Assuming that the input to the quantizer is a full-scale sine wave, the power of such a signal is given by  $(V_{ref}^2/2)$ . Knowing the power of the signal and the quantization noise introduced, the signal to quantization noise can be obtained as,

$$SQNR = \frac{\frac{(2^{N-1}\Delta)^2}{2}}{\frac{\Delta^2}{12}} = \frac{3}{2} \cdot 2^{2N}$$

(2.4)

Expressed in dB, the above equation turns into the more familiar expression relating SNR with an equivalent number of bits.

$$SQNR(dB) = 6.02N + 1.76$$

(2.5)

The above principle is used in a number of ADC architectures to perform analog-to-digital conversion. Such ADCs with sampling rate equal to twice the signal bandwidth are called Nyquist-rate ADCs.

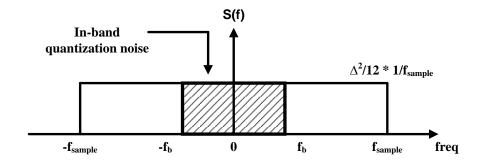

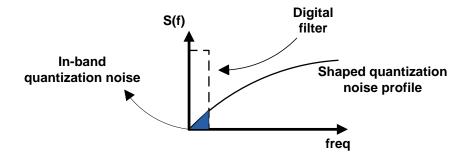

# 2.2 Oversampling

In the previous section, the expression for quantization noise power was obtained. Since this noise is considered as a white noise process, the power is distributed equally across all frequencies from DC to half the sampling rate, i.e. the entire signal bandwidth. If the signal were to be sampled at a rate higher than the Nyquist rate (2 \* signal bandwidth), the same quantization noise power is spread over a higher frequency range. Hence the noise within the frequency of interest gets reduced and the signal-to-quantization noise ratio (SQNR) can be improved a shown in Fig. 4 [11].

Figure 4 Oversampled quantization noise power spectral density profile

The improvement in SQNR due to oversampling is quantified by,

$$SQNR(dB) = 6.02N + 1.76 + 10 \log_{10} OSR$$

(2.6)

where,

$$OSR = \frac{f_{sample}}{2f_b}$$

(2.7)

For example, oversampling improves SQNR at the rate of 3dB/octave or 0.5bit/octave.

# 2.3 Noise shaping

The section above shows the advantages that can be obtained through oversampling. As an example, say we want to increase the resolution of a 6 bit converter by 6 bits over a bandwidth of 2MHz. From the relations shown above, we need 12 octaves of OSR, i.e. a sampling frequency of 16.3Gsamples/s. This kind of implementation will be very expensive in terms of power.

A more effective way of improving resolution is by using some method that would shape the quantization noise out of the signal band. This is the principle of sigma-delta data converters. A simple block diagram of a first order sigma-delta converter is shown in Fig. 5.

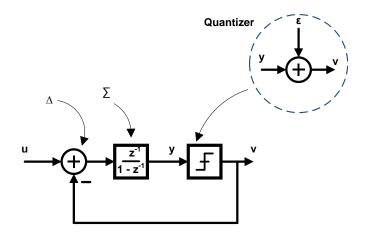

Figure 5 First order sigma-delta modulator

In Fig. 5, the quantization noise is considered as an additive noise. The model in Fig. 5 is that of a linear system with 2 inputs and 1 output. The output can hence be expressed as,

$$v = STF. u + NTF. \varepsilon (2.8)$$

where, STF and NTF refer to the signal transfer function and noise transfer function respectively and are given by,

$$STF = \frac{V(z)}{U(z)} = \frac{H(z)}{1 + H(z)} = z^{-1}$$

(2.9)

$$NTF = \frac{V(z)}{E(z)} = \frac{1}{1 + H(z)} = 1 - z^{-1}$$

(2.10)

As seen in equations (2.9) and (2.10), the signal and quantization noise have different transfer functions to the output. While the signal appears unchanged at the output with just a delay, the noise is shaped as shown in Fig. 6.

Figure 6 First order modulator quantization noise profile

Upon integrating the noise over the frequency of interest, the total noise is obtained as,

$$\sigma_{\epsilon}^2 = \frac{\Delta^2}{12} \cdot \frac{1}{OSR^3} \cdot \frac{\pi^2}{3} \tag{2.11}$$

Expressing as SQNR, we can see that we get an improvement in SQNR of 9dB/octave (1.5bit/octave) of oversampling.

In the above example, the quantization noise is shaped out of band by a first order transfer function. We can obtain further improvements in resolution by using higher orders of noise shaping. For example, by using an L<sup>th</sup> order loop filter, we can obtain an NTF given by,

$$NTF = (1 - z^{-1})^L (2.12)$$

The SQNR in such a case is given by [12],

$$SQNR_{max} = 6.02N + 1.76 + (20L + 10)log_{10}OSR$$

$$-10log_{10}\frac{\pi^{2L}}{2L+1}$$

(2.13)

Hence, the SQNR will improve at the rate of (L+0.5) bits/octave of oversampling in the case of an  $L^{th}$  order sigma-delta modulator.

# 2.4 Types of sigma-delta modulators

In the previous section, the modulators considered were implemented using loop filters that were composed of discrete-time integrators. Hence it is a sampled data system and the sampling for such a system happens at the input of the modulator. These modulators are known as discrete-time (DT) sigma-delta modulators. They are implemented using switched-capacitor techniques. They are very popular for use at low frequencies for applications such as audio signal processing. At such low signal frequencies (20kHz), they make use of a high oversampling ratio (of the order of 128 or higher) and an inherently linear 1-bit quantizer/DAC to obtain resolutions of the order of 20 bits or higher.

Because of their implementation using switched capacitor circuits, the amplifiers used in the integrator structures need to have a unity gain frequency (UGF) of the order of 10 times the sampling frequency to obtain sufficient settling to the desired accuracy. As a result, when the same architecture is extended to higher frequencies, the UGF requirements become very high resulting in very high power consumption. Hence an approach that avoids the switching action and the settling requirements is necessary.

Continuous-time sigma-delta modulators process data using continuous-time filters and the sampling operation is performed after the filter within the loop. Since the input now processes continuous data instead of one that is switching, the UGF requirements are relaxed. This makes them very suitable for use in high bandwidth applications. Also, since the sampling action occurs within the loop, any errors due to sampling are introduced at the same point as quantization noise. Hence these errors undergo the same transfer function and are hence noise shaped outside the frequency band of interest. Sigma-delta converters, by their very oversampling nature, relax the anti-aliasing requirements significantly in comparison to Nyquist-rate converters. Continuous-time sigma-delta converters have the additional advantage that they provide inherent anti-aliasing as well.

For all the advantages compared to their discrete-time counterparts, continuous-time modulators have their own distinct drawbacks as well. The time-constants defining the pole locations are defined by capacitor ratios in DT modulators. These can be accurate to the order of 1% in modern technologies. However, the same pole locations are defined by RC products in CT modulators and these can have variations of the order of  $\pm 20\%$ . Hence tuning for setting the proper pole locations is often necessary. CT modulators are also susceptible to error introduced due to clock jitter while DT modulators are not.

# 2.5 Literature survey

Table 1 Brief summary of wide bandwidth sigma-delta modulators

| Year     | Technology     | Sampling  | Bandwidth | SNR  | SNDR | Power |

|----------|----------------|-----------|-----------|------|------|-------|

|          |                | Freq (Hz) | (Hz)      | (dB) | (dB) | (mW)  |

| 1998[1]  | InGaAs<br>HEMT | 5G        | 100M      | 43   | 39   | 400   |

| 2001[2]  | InGaAs HBT     | 18G       | 500M      | -    | 42 * | 1500  |

| 2003[3]  | InP HBT        | 8G        | 250M      | -    | 40   | 1800  |

| 2006[4]  | SiGe HBT       | 20G       | 312.5M    | 30.5 | -    | 490   |

| 2009[5]  | SiGe HBT       | 35G       | 100M      | 58.9 | 53.1 | 350   |

| 2006[6]  | 130nm CMOS     | 640M      | 20M       | 76   | 74   | 20    |

| 2007[7]  | 180nm CMOS     | 400M      | 25M       | 53   | 52   | 18    |

| 2008[8]  | 90nm CMOS      | 420M      | 20M       | 72   | 70   | 27.9  |

| 2009[9]  | 65nm CMOS      | 250M      | 20M       | 62   | 60   | 10.5  |

| 2009[10] | 130nm CMOS     | 900M      | 20M       | 81.2 | 78.1 | 87    |

<sup>\*</sup> Two-tone SNR

As shown in Table 1, there has been tremendous amount of work going on in the field of continuous-time sigma-delta modulators trying to achieve high bandwidths at reasonable power consumption.

Because of the widespread use of CMOS technology for digital applications, it has emerged as the technology of choice for cost-conscious designs as it enables easy integration with further downstream digital processing. This is shown by publications such as [6-10] showing modulator implementations in the most advanced process technology nodes. Note that, recently there have been novel ideas [9-10] that make use of the high speed capability of the latest CMOS technologies to harness resolution in the time domain instead of being limited to just that in amplitude. Although these CMOS implementations achieve high resolutions with low power consumption, the bandwidths achieved are limited to the 20-25MHz range.

Works reported in [1-3] have achieved medium resolutions over very wide bandwidths (>100MHz). They make use of exotic III-V process technologies for their ability to provide very high speed operation. However, as of now, these technologies are limited in their use to niche applications and hence tend to be very expensive. Also, the power consumptions shown are quite high (>1W) [2-3].

#### 3. SYSTEM LEVEL DESIGN OF MODULATOR

In the last decade, sigma-delta modulators were primarily discrete-time in nature and hence were implemented using switched-capacitor techniques. Only in the recent past, with the push towards higher bandwidths together with higher power efficiency, have continuous-time modulators become more prominent. Because of the wide usage of switched-capacitor modulators, design methodologies for DT modulators have been very well studied and many tools geared for the same have also been developed, e.g. the  $\Delta\Sigma$  MATLAB toolbox by Richard Schreier [13], DAISY [14] etc. Hence, during the design of loop filters for continuous-time modulators as well, it is more common to first obtain a DT loop filter and then use the impulse-invariant transformation to convert the same into a CT loop filter. This approach is followed in this work as well. However, it should be noted that this is not the only way to design continuous-time modulators and the design of the same can be done entirely in the CT domain as shown by [15], [16].

# 3.1 Design considerations

The target in this work is to realize a continuous-time sigma-delta modulator with the specifications shown in Table 2 in 180nm BiCMOS technology.

**Table 2 Specifications**

| Performance parameter | Targeted specification |  |  |

|-----------------------|------------------------|--|--|

| Bandwidth             | 100 MHz                |  |  |

| Resolution            | 11 bits                |  |  |

| Power consumption     | < 500mW                |  |  |

For this purpose, the first step in the design process is to obtain an optimum noise transfer function (NTF) with the major system level parameters as the variables. At the system level, the variables to be considered are over-sampling ratio (OSR), number of bits in the internal quantizer (N), order of the loop (L) and the aggressiveness of the

noise shaping (determined by the out-of-band gain of the NTF) [12]. This optimization is performed by using the MATLAB toolbox by Richard Schreier to obtain the best NTF.

The roles played by the variables mentioned above will be highlighted in the next few paragraphs. The signal-to-quantization ratio (SQNR) of an L<sup>th</sup> order modulator incorporating an N-bit internal quantizer operating with an oversampling ratio of OSR is shown as:

$$SQNR_{max} = 6.02N + 1.76 + (20L + 10)log_{10}OSR$$

$$-10log_{10}\frac{\pi^{2L}}{2L + 1}$$

(3.1)

From equation (3.1), we can see that increase in the order of the modulator leads to a higher SQNR. However, higher order modulators are more difficult to stabilize and usually the order of the system is limited to 5.

Similarly, increasing the OSR of the design provides a better SQNR. However, the maximum speed of operation is usually limited by technology to some finite value. Also, operation at higher speeds leads to higher power dissipation.

Along the same lines, we would like to have more number of bits in the internal quantizer to obtain small quantizaton noise. However the power and area of the implementation of quantizers rise exponentially with increase in the number of bits. Also, higher number of bits in the quantizer places more stringent requirements on the DAC elements used in the feedback path.

The aggressiveness of the noise shaping is determined by the maximum gain of the NTF outside the signal band (NTF<sub>max</sub>). A higher value of NTF<sub>max</sub> tends to push more of the quantization noise from the signal band to higher frequencies. The downside is that higher values of NTF<sub>max</sub> tend to degrade the performance of the modulator when jitter in the system clock is taken into account. This will be discussed in more detail in section 4.

Based on extensive simulations in MATLAB using the  $\Sigma\Delta$  toolbox, the values in Table 3 were arrived at to obtain the best SQNR performance.

**Table 3 Noise transfer function parameters**

| OSR                       | 10   |  |  |

|---------------------------|------|--|--|

| Order (L)                 | 5    |  |  |

| No of levels in quantizer | 9    |  |  |

| NTF <sub>max</sub>        | 3.36 |  |  |

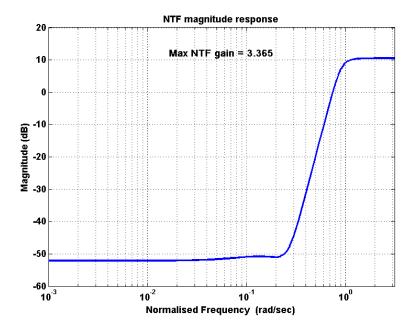

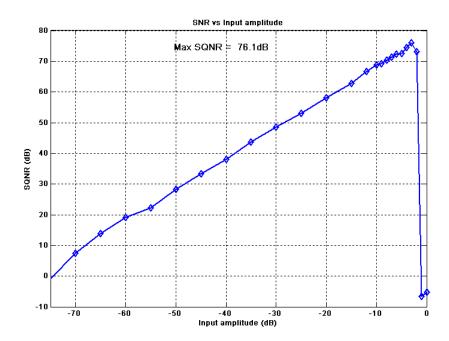

The NTF used in the design is shown in Fig. 7.

Figure 7 Noise transfer function

A plot of the SQNR of the discrete-time system as a function of the input amplitude is shown in Fig. 8. From the figure, we can see that the modulator can provide a maximum SQNR of 76.1dB at input amplitude of -3dBFS.

Figure 8 SNR vs input amplitude of discrete-time system

Once the NTF is known, the loop transfer function (LTF) of the modulator can be easily obtained using the following relation [17]:

$$LTF = \frac{1}{NTF} - 1 \tag{3.2}$$

The corresponding loop transfer function is obtained as:

$$LTF = \frac{2.253z^4 - 5.539z^3 + 5.727z^2 - 2.8z + 0.5389}{z^5 - 4.387z^4 + 7.797z^3 - 7.016z^2 + 3.196z - 0.5899}$$

(3.3)

Excess loop delay (discussed in section 5) is a real concern in CT sigma-delta modulators and it is good practice to incorporate compensation for the loop delay during the system design phase itself. Hence, in this work, an excess delay of 1 cycle is taken into account and the discrete time loop transfer function is modified by factoring out the delay ( $z^{-1}$ ) term from the loop transfer function in equation (3.3) [6]. The modified loop transfer function to be implemented in the modulator is obtained as,

$$LTF = \frac{2.253z^5 - 5.539z^4 + 5.727z^3 - 2.8z^2 + 0.5389z}{z^5 - 4.387z^4 + 7.797z^3 - 7.016z^2 + 3.196z - 0.5899}$$

(3.4)

# 3.2 Impulse-Invariant transformation

The input to a discrete-time modulator is sampled in nature and data transfer through the modulator happens at fixed instants in time controlled by a clock. In contrast, a continuous-time modulator, as its name suggests, processes data that is continuous in nature. However, the internal quantizer in the loop is clocked and there is a sampling action happening within the continuous-time modulator loop. This provides a means to obtain equivalence between a DT and CT modulators as described below [18].

**Figure 9** Equivalence of discrete and continuous-time modulators

Fig. 9 shows discrete-time and continuous-time modulator loops and the corresponding open loop structures obtained by breaking the loops at the DAC inputs. For the two loops to be identical, for the same input, the outputs of the two loops at the sampling instants should be the same.

$$x(n)_d = x(t)|_{t=nT_s}$$

(3.5)

The condition in equation (3.5) is satisfied if the impulse responses of the two loops in question are the same. Expressed in the frequency domain, this takes the form given by,

$$Z^{-1}[H(z)] = L^{-1}[H_d(s) * H(s)]$$

(3.6)

where,  $Z^{\text{-1}}$  and  $L^{\text{-1}}$  stand for inverse Z and Laplace transforms respectively and  $H_d(s)$  represents the frequency response of the DAC in the feedback loop.

In the time domain, equation (3.6) can be expressed as,

$$h(n) = \{h_d(t) * h(t)\}|_{t=nT_s}$$

(3.7)

where, h(n),  $h_d(t)$  and h(t) represent the impulse responses of the discrete-time loop filter, the DAC and the continuous-time loop filter respectively.

Since the above principle is based on the impulse response being the same in the discrete-time and continuous-time structures, it is known as the impulse-invariant transformation.

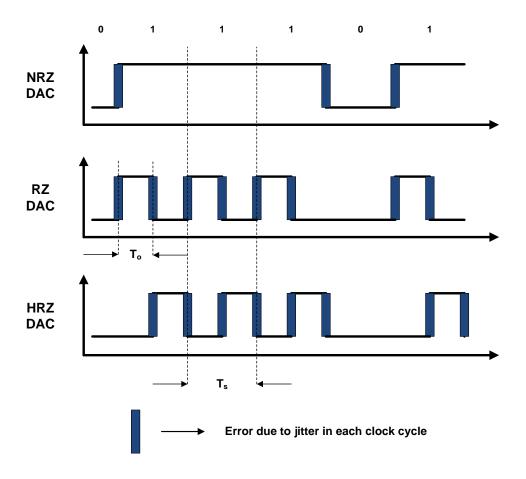

As can be seen from equations (3.6) and (3.7), the continuous-time loop filter to be used in the modulator is dependent on the impulse response of the DAC pulse used in the feedback loop. The most commonly used DAC pulses in continuous-time modulators are Non-Return to Zero (NRZ), Return to Zero (RZ) and Half-Return to Zero (HRZ). The impulse responses of the mentioned DAC pulses are shown in Fig. 10 [12].

Figure 10 NRZ, RZ and HRZ DAC pulses

Because of their inherent nature, the RZ and HRZ DAC pulses have more number of transitions on average in each clock cycle. As a result they are more susceptible to clock jitter than the NRZ DAC pulse shape. Hence, in this work, the NRZ DAC pulse is used for its better jitter robustness.

It should be noted that these are not the only DAC pulse shapes possible. Pulse shapes such as exponential [19] and sinusoidal [20] have been reported in the literature.

For the case of the NRZ DAC pulse, the impulse invariant transformation is available in MATLAB using the built-in function 'd2c' [6]. Upon usage of this function, the corresponding continuous-time loop filter for the discrete-time transfer function in equation (3.4) is obtained as,

$$H(s) = \frac{2.253s^5 + 8.716e9s^4 + 1.719e19s^3 + 2.212e28s^2 + 1.811e37s + 7.57e45}{s^5 + 1.056e9s^4 + 9.471e17s^3 + 4.115e26s^2 + 1.418e35s + 1.88e43}$$

(3.8)

The procedure to obtain the loop transfer function, starting from the design of the NTF, is summarized below.

1. Choose a high-pass filter transfer function for the NTF. The common filter types chosen are Butterworth, Chebyshev and Inverse-Chebyshev. When done in MATLAB, for a filter of order n, the resulting transfer function takes the form,

$$H(z) = \frac{b_1 + b_2 z^{-1} + \dots + b_{n+1} z^{-n}}{1 + a_2 z^{-1} + \dots + a_{n+1} z^{-n}}$$

(3.9)

For a noise transfer function to be realizable,  $H(\infty) = 1$ . To satisfy this condition, divide the transfer function H(z) in equation (3.9) by  $b_1$ . A good starting point for the stop-band of the NTF is the desired signal bandwidth. The zeros of the transfer function can be spread across the signal bandwidth to obtain optimum SQNR [21].

2. Choose values for the oversampling ratio (OSR) and quantizer resolution.

- 3. Simulate the modulator obtained using 'simulateDSM' function of the  $\Sigma\Delta$  toolbox. Use 'ds\_hann' and 'calculateSNR' functions to obtain the SQNR.

- 4. In case the SQNR obtained is not sufficient, go back to steps 1 & 2 and pick a higher stop-band frequency, OSR or resolution in the quantizer, and vice-versa if the SQNR is too high.

- 5. Once the desired SQNR is obtained, use equation (3.2) to obtain the discrete-time loop transfer function from the NTF.

- 6. Modify the loop transfer function to account for excess loop delay by factoring out  $z^{-k}$  term, where k is the amount of delay in the loop.

- Use the impulse-invariant transformation to convert the discrete-time loop transfer function to continuous-time, taking into account the shape of the DAC feedback pulse.

### 3.3 Loop filter implementation

Once the loop transfer function is obtained as shown in the previous section, the next step is the implementation of the transfer function using individual building blocks. In continuous-time sigma-delta modulators, the loop filters are generally implemented as a cascade of integrators or resonators comprised of biquads. The individual integrator or biquad sections can be connected together in two different configurations called feedback and feed-forward implementations. These two configurations are shown in Fig. 11 and 12 for the case of a 3<sup>rd</sup> order modulator with all the poles at DC (implemented with integrators).

Figure 11 Feedback configuration

Figure 12 Feed-forward configuration

As shown in Fig. 11, in a feedback implementation of the modulator, the zeros are implemented by the feedback to each node of the filter. The loop filter, with transfer function H(s), is shown in the figure within the dotted box. The advantage of the feedback topology is that it provides anti-aliasing of an order equal to the order of the loop filter. However, it needs multiple DACs in the feedback path and also tends to be power hungry.

The feed-forward configuration, as shown in Fig. 12, uses feed-forward paths from the individual integrators to the quantizer to implement the zeros. The advantage with this configuration is that only one DAC is needed in the feedback path. Also, this architecture is more power-efficient when compared to the feedback based implementation. However, the feed-forward implementation only provides first order anti-aliasing filtering. Also, the signal transfer function shows peaking outside the signal band, which can lead to saturation in the modulator in the presence of blockers. The summing amplifier in front of the quantizer is present in the high frequency path and is very critical for stability.

In both the feedback and feed-forward representations shown in Fig. 11 and 12 the poles are realized by integrators. Non-DC poles can be realized using resonators formed by biquad sections. In all these cases, as the bandwidth of interest in a modulator implementation increases, the power consumption in the amplifier within the integrators

or biquads rises to accommodate the higher frequency signals. Hence, in this work, the use of passive filters comprised of LC sections is explored.

Also, the feedback architecture is used as compared to a feed-forward one for the following two reasons:

- 1. The proposed LC filter has convenient feeding points to obtain low-pass and band-pass transfer functions.

- 2. It avoids the summing amplifier that would be required in a feed-forward architecture case. With a sampling frequency of 2GHz, the summing amplifier can be a potential speed bottle-neck.

A single-ended representation of the proposed loop filter with the feedback paths included is shown in Fig. 13.

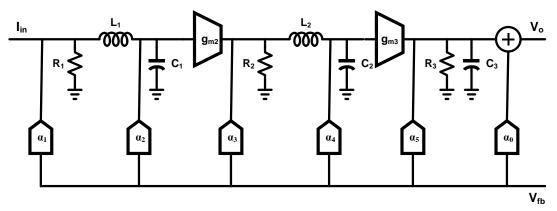

Figure 13 Proposed loop filter

The loop transfer function of the filter in Fig. 13 is given by,

$$\frac{V_{o}(s)}{V_{fb}(s)} = \alpha_{0} + \frac{\alpha_{5}/C_{3}}{s + \omega_{3}} + \frac{g_{m3}/C_{3}}{s + \omega_{3}} \cdot \frac{1}{s^{2} + s\left(\frac{\omega_{2}}{Q_{2}}\right) + \omega_{2}^{2}} \cdot \left[s\left(\frac{\alpha_{4}}{C_{2}}\right) + R_{2}\omega_{2}^{2}(\alpha_{3} + \alpha_{4})\right] + \frac{g_{m3}/C_{3}}{s + \omega_{3}} \cdot \frac{g_{m2}R_{2}\omega_{2}^{2}}{s^{2} + s\left(\frac{\omega_{2}}{Q_{2}}\right) + \omega_{2}^{2}} \cdot \frac{1}{s^{2} + s\left(\frac{\omega_{1}}{Q_{1}}\right) + \omega_{1}^{2}} \cdot \left[s\left(\frac{\alpha_{2}}{C_{1}}\right) + R_{1}\omega_{1}^{2}(\alpha_{1} + \alpha_{2})\right]$$

(3.10)

where,

$$\omega_1 = \frac{1}{\sqrt{L_1 C_1}} \tag{3.11}$$

$$\omega_2 = \frac{1}{\sqrt{L_2 C_2}} \tag{3.12}$$

$$\omega_3 = \frac{1}{R_3 C_3} \tag{3.13}$$

$$Q_1 = \frac{\omega_1 L_1}{R_1} \tag{3.14}$$

$$Q_2 = \frac{\omega_2 L_2}{R_2} \tag{3.15}$$

By comparing the transfer function of the loop filter shown above and the desired filter response obtained earlier in equation (3.8) the coefficients can be obtained.

The parameters of the modulator obtained after performing the comparison mentioned above are shown in Table 4.

| $\alpha_0$     | 0.45  | $L_1$                      | 100nH  | $L_2$          | 100nH  |

|----------------|-------|----------------------------|--------|----------------|--------|

| $\alpha_1$     | 20μ   | $C_1$                      | 35.6pF | $C_2$          | 31.4pF |

| $\alpha_2$     | 2.58m | $R_1$                      | 33Ω    | $R_2$          | 51Ω    |

| α <sub>3</sub> | 6.20m | $\mathbf{g}_{\mathrm{m2}}$ | 100mS  | $g_{m3}$       | 40mS   |

| $\alpha_4$     | 3.84m | R <sub>3</sub>             | 2kΩ    | C <sub>3</sub> | 2.4pF  |

| $\alpha_5$     | 3.16m |                            |        |                |        |

**Table 4 Modulator component values**

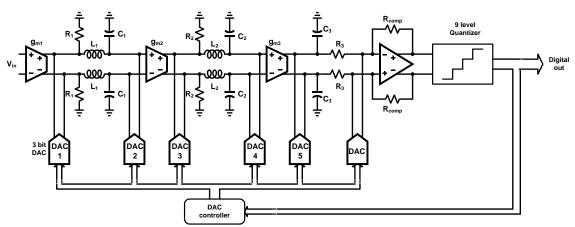

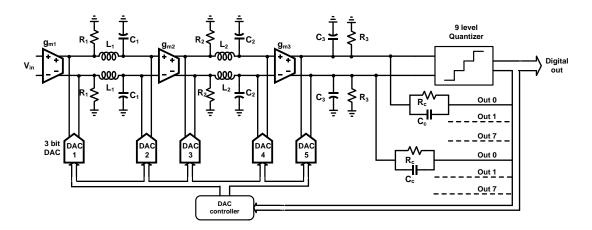

A representation of the complete modulator with the loop filter, quantizer and the feedback DACs is as shown in Fig. 14.

Figure 14 Modulator implementation

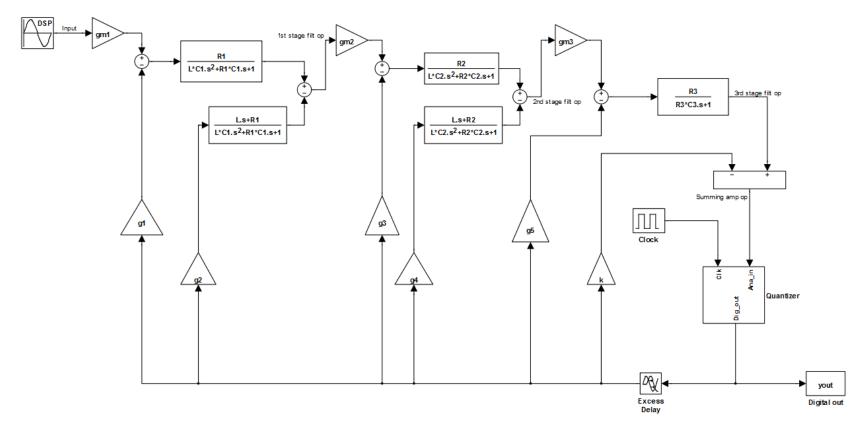

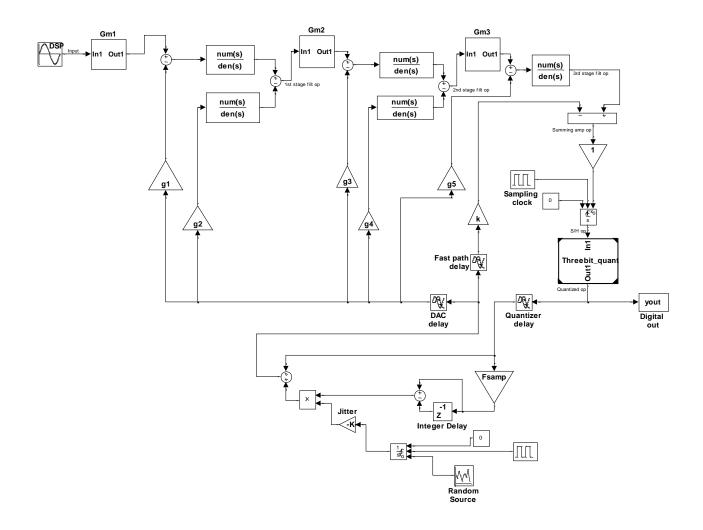

The model of the system built in the simulink environment of MATLAB is shown in Fig 15.

# 3.4 Simulation-based synthesis

In the previous section, it was shown how to obtain the parameters of the sigma-delta modulator by using the desired and theoretical loop transfer functions and comparing the corresponding coefficients. This process was made simple by the existence of a built-in function in MATLAB for the special case of the NRZ pulse shape chosen. For other pulse shapes, the process is not as straight-forward. In such cases, the simulation-based synthesis method proposed in [12] can be used. A brief explanation of the method is given below.

The method is based on the fact that the loop in a sigma-delta modulator is a linear time-invariant system. Hence the output response of the loop is composed of a natural response and a forced response [12].

The natural response is determined primarily by the denominator (poles) of the transfer function. These poles and their quality factors can be obtained from the corresponding DT poles using the impulse-invariant transformation using [12],

$$z_p = e^{s_p} (3.16)$$

where,  $z_p$  and  $s_p$  denote the DT and CT poles, respectively.

Once the pole locations are obtained, these can be mapped into component values for the  $2^{nd}$  order sections using,

$$\omega = \frac{1}{\sqrt{LC}} \tag{3.17}$$

$$Q = \frac{\omega L}{R} \tag{3.18}$$

Similarly, for the first order section, we get,

$$\omega = \frac{1}{RC} \tag{3.19}$$

Once the individual 2<sup>nd</sup> order and 1<sup>st</sup> order sections of the loop are determined, what remains to be found are the coefficients that form the different feedback paths to give the entire loop transfer function. This is what determines the forced response of the system.

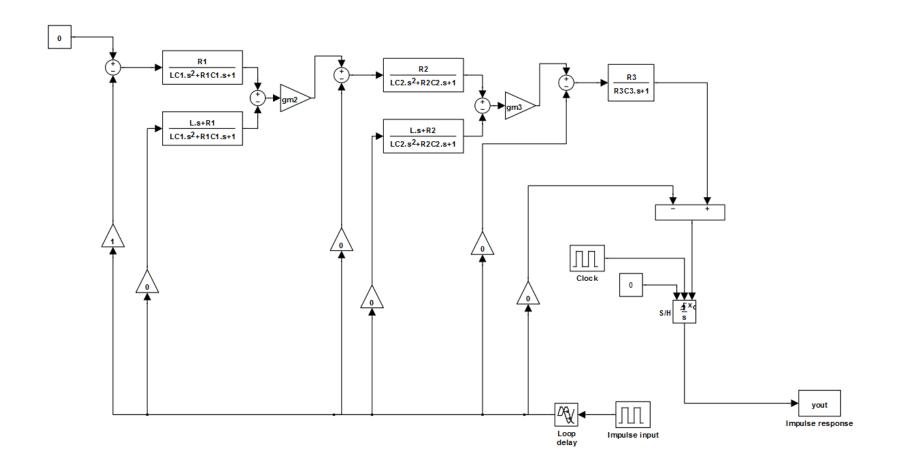

The loop filter is composed of six independent paths from the DAC input to the input of the quantizer (5 feedback paths and the fast path for stability). Since this is a linear system, the impulse response of the entire system will be the linear sum of the impulse responses of the individual paths mentioned above. The impulse response of each path can be found by exciting the loop with an impulse by enabling only the required path with a coefficient of 1 and setting the other coefficients to 0. A simulation setup in MATLAB to obtain the coefficients is shown in Fig. 16 for the 1<sup>st</sup> feedback path.

Figure 15 MATLAB model of system

Figure 16 MATLAB coefficient extraction setup

Let the response obtained by this step for the 1<sup>st</sup> path is denoted by  $h_1(m)$ , m denoting the sampling instants. Similar responses can be obtained for each of the individual paths and let they be denoted by  $h_n(m)$ . Let the required coefficients in the feedback path be denoted by  $[\alpha_0, \alpha_1, \alpha_2, \alpha_3, \alpha_4, \alpha_5]$ . As mentioned above, the net impulse response of the system, h(m), is the linear sum of the above obtained responses and is given by,

$$h(m) = \sum_{n=0}^{5} \alpha_n h_n(m)$$

(3.20)

By the impulse invariant transformation, this response should be equal to the response of the desired equivalent discrete-time system. The discrete-time impulse response can be easily obtained from the z-domain loop transfer function H(z) in equation (3.4). Let this impulse response be denoted by  $h_d(m)$ . By equating the two sets of values, we obtain a system of linear equations given by,

$$\alpha_0 h_0(m) + \alpha_1 h_1(m) + \alpha_2 h_2(m) + \alpha_3 h_3(m) + \alpha_4 h_4(m) + \alpha_5 h_5(m) = h_d(m), \quad m \to 1 - 6$$

(3.21)

By rearranging the equations (3.21) and using matrix algebra, we can solve for the coefficients  $[\alpha_0, \alpha_1, \alpha_2, \alpha_3, \alpha_4, \alpha_5]$ .

$$\begin{bmatrix} \alpha_0 \\ \alpha_1 \\ \alpha_2 \\ \alpha_3 \\ \alpha_4 \\ \alpha_5 \end{bmatrix} = \begin{bmatrix} h_0(1) & h_1(1) & h_2(1) & h_3(1) & h_4(1) & h_5(1) \\ h_0(2) & h_1(2) & h_2(2) & h_3(2) & h_4(2) & h_5(2) \\ h_0(3) & h_1(3) & h_2(3) & h_3(3) & h_4(3) & h_5(3) \\ h_0(4) & h_1(4) & h_2(4) & h_3(4) & h_4(4) & h_5(4) \\ h_0(5) & h_1(5) & h_2(5) & h_3(5) & h_4(5) & h_5(5) \\ h_0(6) & h_1(6) & h_2(6) & h_3(6) & h_4(6) & h_5(6) \end{bmatrix}^{-1} \begin{bmatrix} h_d(1) \\ h_d(2) \\ h_d(3) \\ h_d(4) \\ h_d(5) \\ h_d(6) \end{bmatrix}$$

(3.22)

#### 3.5 Modeling in Verilog-A

In the previous section, design of the sigma-delta modulator at the system level in MATLAB was shown. The next step in the implementation process is the design of the individual blocks at the circuit level and verification of the modulator at circuit level. This is usually done using spice simulations in Cadence. However, the simulations at

this stage tend to be much time-consuming and debugging of issues, if any, becomes difficult. An intermediate step here can be the building of a behavioral model for the system using ideal elements in the Cadence environment. Now system simulations can be performed more easily with circuits of the individual blocks replacing the ideal ones in the behavioral model.

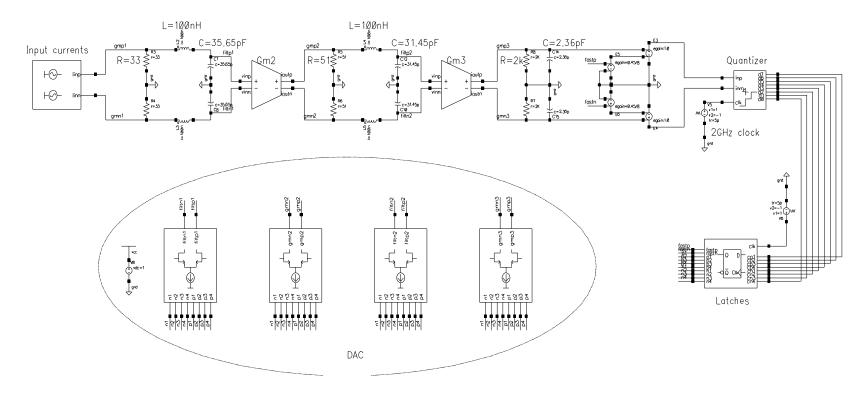

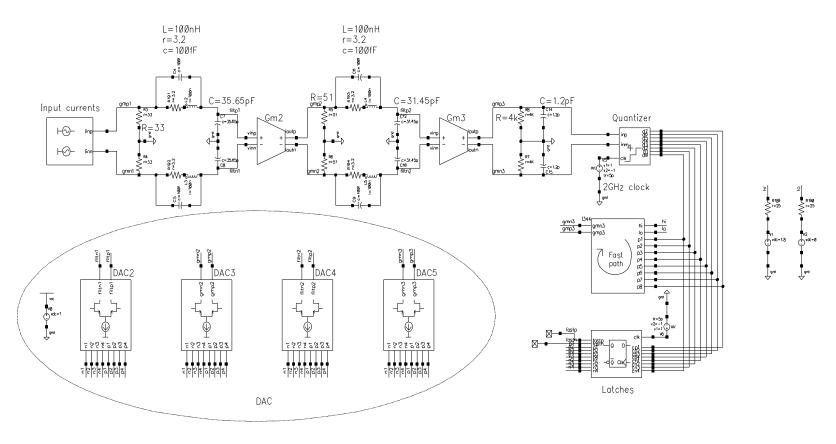

In building the ideal model in Cadence, while elements of the passive filter and transconductance elements can be easily obtained from the basic devices available in the component library, more complex blocks like quantizers are not readily available. These components were modeled in this work using hardware description language Verilog-A [22]. The schematic of the system built in Cadence with Verilog-A models included is shown in Fig. 17.

Figure 17 Cadence schematic of the system

#### 3.6 Results

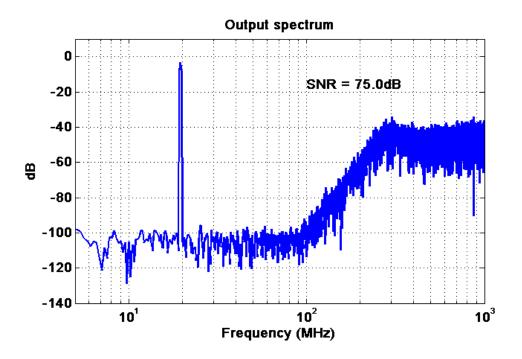

A behavioral model of the system was built in MATLAB using simulink. The output obtained from a simulation of the system is shown in Fig. 18. The input is a -3dBFS sine wave (the input amplitude for maximum SQNR as shown in Fig. 8) at 19.53MHz and the SNR is computed over a bandwidth of 100MHz.

Figure 18 Output spectrum from ideal behavioral model

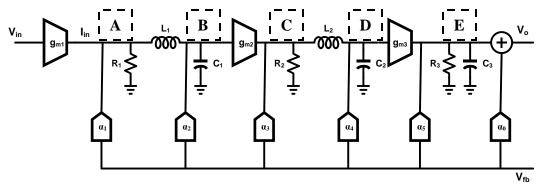

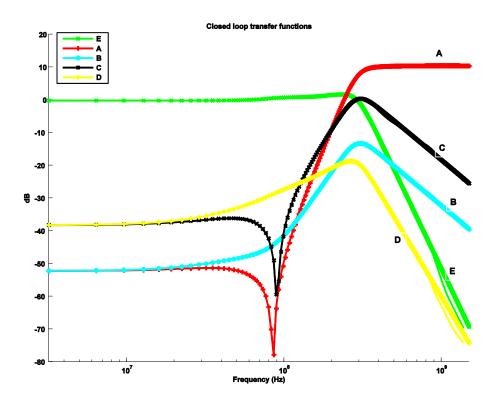

The closed loop transfer functions from the input to different points in the loop filter were obtained using simulink. An illustration of the loop filter with the different points annotated and the closed loop transfer function results are shown in Fig 19 and 20 below respectively.

Figure 19 Loop filter

It can be seen from Fig 20 that out-of-band signals can have a gain of up to 10dB at node A in the loop filter. Care needs to be taken that this does not result in saturation in the filter stage.

Figure 20 Closed loop transfer functions

#### 4. MODELING OF NON-IDEALITIES

In section 3, the design for the sigma-delta modulator was performed at the system level using SIMULINK and Verilog-A in Cadence. The design process then assumed that all the components used in the loop are ideal and will behave exactly as assumed in the model. However, in the real world, this is not the case and various non-idealities are associated with the different elements in the loop. We will have a look at some of the major deviations from the ideal model in this section.

#### 4.1 Non-idealities in the transconductors

#### **4.1.1** Non-linearity in the transconductors

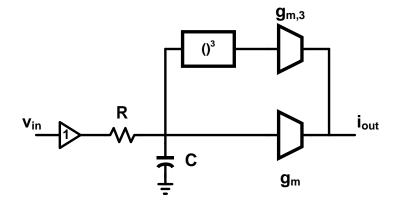

The proposed architecture in this work utilizes passive elements in the signal path to obtain the filtering action. However, a sufficient amount of gain is still needed in the forward path and active circuits are used for this purpose. In contrast to passive elements that are inherently linear, active circuits exhibit non-linearity and in the case of a transconductor, this non-linear relationship between input voltage and output current can be expressed as,

$$i = g_m.v + g_{m,3}.v^3 (4.1)$$

where, i is the output current of the transconductor, v is the input voltage of the transconductor,  $g_m$  is the linear transconductance and  $g_{m,3}$  is the third order non-linear transconductance.

Only odd-order non-linearities are considered here, since the circuit will be implemented in a differential manner eliminating even-order disturbances.

Since the transconductor element  $g_{m2}$  in Fig. 19 does not have any gain in the signal path before it, any non-linearity introduced by the transconductor, when reflected back to the input, will appear without any attenuation. This non-linearity will then directly appear at the output due to the feedback action. Hence, the transconductor  $g_{m2}$  needs to have

stringent linearity requirements. In contrast, the signal received by the transconductor  $g_{m3}$  has already been amplified in the loop filter (with gain  $g_{m2}R_2$ ) and hence its non-linearity is not as critical. In this work, an inter-modulation distortion (IM3), in a two-tone test, of 70dB is targeted.

Using equation (4.1) to model the non-linearity in the two transconductors, system simulations were performed in MATLAB. IM3 specifications for each of the blocks were derived to obtain an overall system IM3 of 70dB. The specifications derived are as shown in Table 5:

**Table 5 Transconductor non-linearity specifications**

| Transconductor  | IM3 specification |

|-----------------|-------------------|

|                 | (dB)              |

| g <sub>m2</sub> | 68.5              |

| g <sub>m3</sub> | 54.5              |

### **4.1.2** Excess phase in the transconductors

In the model of the transconductors considered so far, it is assumed that they have the same value of transconductance over all frequencies. In reality, there are finite impedances and capacitances within the transconductance circuit implementations and these tend to introduce one or more poles. In this work, the transconductors are modeled as single-pole systems and the output current is hence given by,

$$i = \frac{g_m}{1 + \frac{s}{\omega_p}} \cdot v \tag{4.2}$$

where,  $\omega_p$  represents the dominant pole of the transconductance block.

The primary effect of poles within the transconductance block is due to their phase characteristic that tends to introduce additional delay in the signal path. Since the sigmadelta modulator is a closed loop system, excess delay due to these blocks can cause the

loop to become unstable. Hence, we need to make sure that the poles are at high enough frequencies so that this is not an issue.

The effect of excess phase was modeled by using an RC network ahead of the ideal transconductance block. The transconductance model incorporating both non-linearity and excess phase is as shown in Fig. 21.

Figure 21 Transconductor model

After several time-domain simulations of checking the system for stability, the dominant poles of the transconductors were obtained as shown in Table 6.

Table 6 Transconductor excess phase specifications

| Transconductor  | Dominant pole |

|-----------------|---------------|

|                 | (MHz)         |

| g <sub>m2</sub> | 300           |

| g <sub>m3</sub> | 500           |

# **4.1.3** Output capacitance

The transconductors when implemented at the transistor level finally will have finite values of parasitic capacitance at the output nodes. The capacitance of transconductor  $g_{m3}$  will cause a shift in the pole frequency of the  $3^{rd}$  stage of the filter. The external

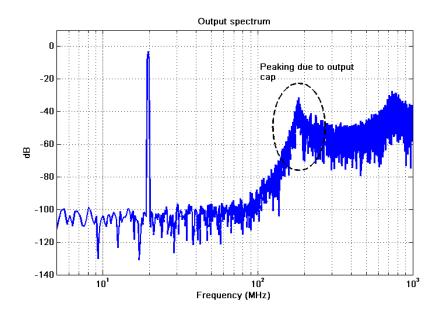

capacitor needs to be tuned to compensate for this output capacitance. In the case of transconductor  $g_{m2}$ , the output capacitance appears in parallel with resistance  $R_2$ . It was observed that high value of this capacitance produces peaking in the output spectrum of the modulator. This is illustrated in Fig. 22 where a capacitance of 3.5pF was used on the output nodes.

Figure 22 Output spectrum with peaking

In the presence of a blocker signal in the input around the peaking frequency, the modulator can become unstable. Even in the absence of a blocker, higher values of capacitance can cause the quantization noise to rise significantly due to the peaking to cause instability. To avoid this phenomenon, a value of 2pF for the output capacitance was arrived at to have some margin in the design.

### 4.2 Non-idealities in the DAC

#### 4.2.1 Element mismatch

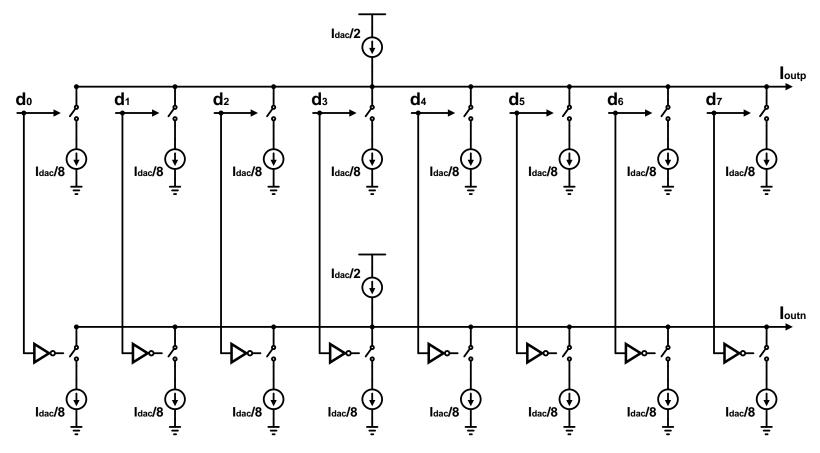

As discussed in section 3, high performance sigma-delta modulators use multi-bit internal quantizers to reduce the quantization noise power. However, the use of a multi-

bit quantizer necessitates the use of a multi-bit DAC in the feedback path. These multi-bit DACs are generally implemented as a summation of many unit elements and mismatch between these unit elements results in non-linearity being introduced at the output of the DAC. The output of the DAC enters the modulator loop at the same point as the input. Hence any non-linear components introduced at the output of the DAC appear directly along with the signal at the output and degrade the performance of the modulator.

There have been various methods reported in the literature, collectively called Dynamic Element Matching (DEM) techniques, to compensate for the non-linearity of the DACs. The essential idea in all these methods is to pre-process the digital data from the quantizer before applying it to the input of the DAC. This digital data processing has two effects [12]:

- 1. It makes sure that any error introduced by the DAC is no longer correlated to the input signal. Hence, the error that would have manifested itself as non-linear tones at the output gets converted to white noise.

- 2. Some of the techniques also tend to shape the mismatch-error introduced by the DAC out of the signal band thus reducing their damaging effect.

Some of the popular digital pre-processing techniques are DWA (Data Weighted Averaging) [23], ILA (Individual Level Averaging) [24].

Another way to compensate for the non-linearity of the DACs is to use analog calibration on the individual unit elements [25]. In this method, each of the unit elements is compared to an ideal reference and any existing error in the unit element is corrected. When calibration is used, the number of unit elements in the DAC is more than that actually required. This ensures that unused unit elements of the DAC can be calibrated while ensuring continuous operation with the other elements of the DAC.

In this work, calibration is used to combat non-linearity in the feedback DACs.

### **4.2.2** Output resistance of the DAC

The feedback DACs are implemented in current-mode and they connect to different points in the LC filter-section as shown in Fig 14. Since the output resistance of the DAC elements appears in parallel with the resistance element in the filter section, a low value of output resistance would degrade the gain in the forward path (at low frequencies) and raise the noise floor of the quantization noise in the output spectrum. Hence, a minimum value needs to be maintained for the output resistance in the DACs. Using time-domain simulations in MATLAB, the value shown in Table 7 was obtained for the output resistance.

Table 7 DAC output resistance specification

| Output resistance | $25\mathrm{k}\Omega$ |

|-------------------|----------------------|

#### 4.3 Quantizer non-idealities

# 4.3.1 Excess loop delay

Excess loop delay is a unique problem in continuous-time modulators because of the fact that the feedback waveform is continuous in nature and any delay in the feedback path changes the feedback into the loop filter. In this modulator, NRZ pulse shape is used for the feedback DAC and hence delay in the quantizer will appear as excess loop delay. Hence, a half clock period (250ps) delay each is assigned to the quantizer and feedback DAC and the 1 clock cycle delay is later compensated. In this work, a novel method is used to overcome the effect of excess loop delay. This and a couple of other methods reported in the literature will be discussed in detail in section 5.

#### **4.3.2** Offset voltage

In sigma-delta modulators, errors associated with the quantizer are noise-shaped the same way as quantization noise and in general, are not critical. However, in high-order,

high-resolution implementation, care needs to be taken to make sure that the quantizer non-idealities do not limit performance.

In a quantizer, presence of an offset can be considered as a change in the threshold level and hence additional quantization error is introduced. Also, in a multi-bit quantizer, the individual comparators will each have a random offset voltage. Hence, the transfer function of the quantizer is no longer a straight line and the quantizer adds distortion to the output. These effects tend to reduce the signal-to-noise-and-distortion-ratio (SNDR) of the modulator.

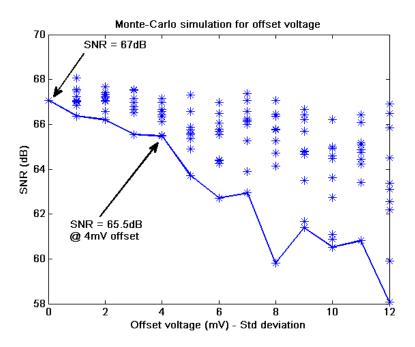

A Monte-Carlo simulation of the modulator was performed with the offset voltage of the comparators being considered as random variables. The input signal in this simulation is a -9dBFS signal (half of the maximum stable amplitude). The variation of the SNR with offset voltage is shown in Fig. 23. At each value of offset voltage, 10 different simulations were performed. In Fig. 23, all the obtained SNR values are plotted and the minimum SNR values are shown connected by a solid line.

Figure 23 Monte-Carlo simulations for offset voltage of comparators

From Fig. 23, it can be concluded that, to keep SNR degradation due to offset voltage less than 2dB, the standard deviation of the offset voltage needs to be 4mV or smaller.

### 4.4 Clock jitter

Nyquist-rate and discrete-time sigma-delta ADCs are sampled-data systems. Hence any error in the sampling process appears together with the input to the ADC and degrades the SNR directly. However, in continuous-time sigma-delta modulators, the sampling occurs in the quantizer which is present after the loop filter. Hence, any errors introduced at this point due to sampling have the same transfer function to the output as the quantization noise and are hence noise-shaped outside the signal band.

Since oversampled converters are closed-loop systems, there is feedback to the input of the system and this feedback action is also controlled by the same clock used in the quantizer. Hence the effect of clock jitter needs to be considered at the input of the loop as well. Discrete-time modulators are insensitive to jitter at the input to the system because of their sampled nature. As long as the signal settles to the required accuracy within the clock period, any jitter in the feedback clock does not introduce any errors. However, in the case of continuous-time modulators, any timing error in the feedback signal is equivalent to an error in the feedback signal [12]. Since the transfer function from the feedback signal to the output is the same as the input, this error appears at the output without any attenuation.

The jitter noise power at the output of a continuous-time modulator is dependent on the shape of the DAC feedback pulse. This can be seen in Fig. 24 where the feedback waveform shapes in the case of NRZ, RZ and HRZ type feedback pulses [18] for the same modulator digital output are shown.

In Fig. 24, the digital pattern being considered is shown at the top of the figure. The effect of clock jitter is to change the point in time at which the feedback signal is applied at the input. The feedback applied between the ideal and jittered time instant manifests

itself as error applied at the input. This is shown by the shaded regions in each of the feedback pulses in Fig. 24.

Figure 24 Effect of clock jitter on different feedback DAC pulses

Since the error due to clock jitter is injected into the modulator only during the feedback signal edges and the NRZ pulse shape has lower number of transitions compared to the RZ and HRZ shapes, the NRZ feedback shape is more tolerant to clock jitter. This is further quantified by the relations for the in-band error powers given by [12],

$$\sigma_{NRZ}^2 = \frac{1}{OSR} \left( \frac{\sigma_{jitter}}{T_s} \right)^2 \sigma_{dy}^2 \tag{4.3}$$

$$\sigma_{RZ}^2 = \frac{2}{OSR} \left(\frac{\sigma_{jitter}}{T_o}\right)^2 \sigma_y^2 \tag{4.4}$$

where, OSR is the oversampling ratio,  $\sigma_{jitter}^2$  is the variance of clock jitter,  $T_s$  is the clock period,  $T_o$  is amount of time for which feedback is activated in RZ case,  $\sigma_y^2$  is the variance of the digital output signal, y(n), of the modulator and  $\sigma_{dy}^2$  is the variance of the signal (y(n) - y(n-1)).

The improvement in signal-to-jitter noise ratio when NRZ feedback is used in place of RZ can be obtained by taking the ratio of equations (4.3) and (4.4) [12] and is given by,

$$SJNR_{improvement} (dB) = 10log\left(\frac{\sigma_{RZ}^2}{\sigma_{NRZ}^2}\right) = 10log\left(2.\left(\frac{T_s}{T_o}\right)^2.\frac{\sigma_y^2}{\sigma_{dy}^2}\right)$$

(4.5)

Hence, in this work NRZ feedback is used to avoid degradation of SNR due to clock jitter.

### 4.4.1 Modeling jitter

To study the effect of clock jitter at the system level, the simplest method is to replace the ideal clock by a jittered clock with the required rms jitter power. However, this can increase the simulation time significantly because the simulation now has to account for clock edges that vary randomly around the ideal value. Hence, a different approach is necessary in this case [26].

When jitter is present in the feedback signal, the error introduced is in reality an error in the amount of charge fed into the loop filter. This error charge is given by the area in the jitter period in the current-time waveform. The same effect can be obtained by changing the signal amplitude by constant amount over the entire clock period to produce the same error charge. The required change in the signal amplitude is given by,

$$e_{j,NRZ}(n) = (y(n) - y(n-1)) \cdot \frac{\Delta t(n)}{T_s}$$

$$(4.6)$$

Jittered waveform

Jitter modeled waveform

ldeal waveform

Jitter modeled waveform

ldeal levels

This is shown pictorially in Fig. 25 [12].

Figure 25 Modeling effect of clock jitter

time

$(n\text{--}2)T_s \ (n\text{--}1)T_s \quad nT_s \quad (n\text{+-}1)T_s \ (n\text{+-}2)T_s \ (n\text{+-}3)T_s \ (n\text{+-}4)T_s$

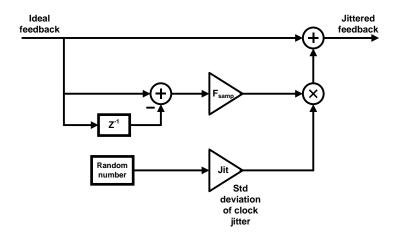

The approach shown in equation (4.6) can be used to model the effect of jitter in a continuous-time sigma-delta modulator. The fact that the simulation now uses ideal clock edges once again helps to reduce the simulation time. The MATLAB model used to study the jitter phenomenon is shown in Fig. 26.

Figure 26 Clock jitter model in MATLAB

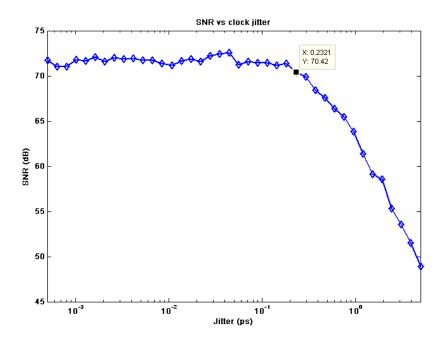

The model shown in Fig. 26 was used to study the effect of jitter on the proposed modulator by adding different amounts of jitter to the clock and noting the change in the SNR at the output. The result obtained is shown in Fig. 27. From the figure, we can see that to maintain the SNR in the presence of jitter above 70dB, we need a clock source with an RMS jitter less than 0.25ps.

Figure 27 SNR as a function of clock jitter

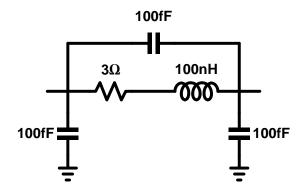

#### 4.5 Non-ideal inductor

The inductors used in this work would be fabricated outside the chip but within the package itself. This inductor would have non-idealities of its own and these were taken into account by using a quality factor of 20 and a self-resonant frequency of 1.6GHz. The model of the real inductor is shown in Fig. 28.

Figure 28 Non-ideal inductor

### 4.6 Thermal noise

Apart from the non-idealities described earlier, thermal noise in the circuits also needs to be taken into consideration. In this section, thermal noise specifications for the blocks will be obtained.

The resolution of the modulator in this work is targeted at 11 bits. This implies a signal-to-noise ratio (SNR) of 68dB. Assigning equal weights to thermal noise and the sum of other noise sources, we obtain a signal-to-thermal noise ratio of 71dB. To give some margin in the design, a target of 72dB is used. Since the differential input signal is  $250 \text{mV}_{\text{peak}}$ , the above SNR value leads to an rms noise value of  $44 \mu \text{V}$ .

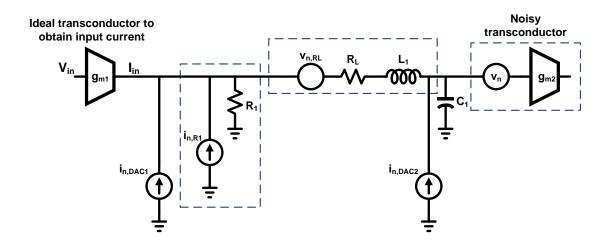

The loop filter with the different noise sources from the first stage is shown in Fig. 29. Noise sources of the stages ahead are not considered because they are attenuated by the gain factor  $g_{m2}R_2$ .

Figure 29 Noise sources in the loop filter

The input referred noise power spectral density is given by,

$$v_{noise}^{2} = \frac{1}{g_{m1}^{2}} \left[ i_{n,R1}^{2} + i_{n,DAC1}^{2} + \frac{v_{n,RL}^{2}}{R_{1}^{2}} + i_{n,DAC2}^{2} \left| 1 + \frac{sL_{1}}{R_{1}} \right|^{2} + \frac{v_{n}^{2}}{R_{1}^{2}} |s^{2}L_{1}C_{1} + sR_{1}C_{1} + 1|^{2} \right]$$

$$(4.7)$$

where,

$$i_{n,R1}^2 = \frac{4kT}{R_1} \tag{4.8}$$

$$i_{n,DAC1}^2 = 4kT\left(\frac{2}{3}g_m\right) \tag{4.9}$$

$$i_{n,DAC2}^2 = 4kT \left(\frac{2}{3}g_m\right) (4.10)$$

$$v_{n,RL}^2 = 4kTR_L \tag{4.11}$$

The values of the various circuit elements in equation (4.7) and Fig. 29 are given in Table 3. Using the given values and picking a value of 200 mV for the  $v_{d,sat}$  of the current sources implementing the DACs, the input-referred noise contributions from the various blocks for a differential implementation are obtained as shown in Table 8.

Table 8 Input referred RMS noise values

| Block                            | RMS noise |

|----------------------------------|-----------|

| Resistor R <sub>1</sub>          | 10.5μV    |

| Inductor resistor R <sub>L</sub> | 3.3µV     |

| DACs                             | 22.8μV    |

| Transconductor g <sub>m2</sub>   | 36μV      |

### 4.7 Variation of pole locations

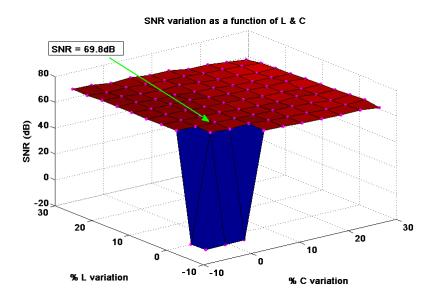

The loop filter pole locations in discrete-time modulators are set by ratios of capacitors and hence can be defined with good accuracy. However in continuous-time modulators they are either set by RC products or  $g_m/C$  ratios and can vary by as much as  $\pm 30\%$ . In this work, the pole locations are set by LC products and are subject to the same variations. To assess the behavior of the modulator in presence of component variations, simulations of the modulator were performed where the values of L and C were varied from about -10% to 30%. The SNR of the modulator obtained under these conditions is shown in Fig. 30.

Figure 30 SNR variations with change in values of L and C

From Fig. 30, we can see that the SNR at the default values of L and C (as shown by the arrow) is 69.8dB. As the values of L and C increase, the poles move to lower frequencies and the noise shaping of the loop becomes less optimum and hence the SNR reduces as seen in Fig. 30. On the other hand, reductions in the L and C values move the poles to high frequencies and provide better noise shaping for a while. But soon the modulator becomes unstable and SNR drops drastically. For the current work, we can see that this happens when the L and C values reduce by about 5%.

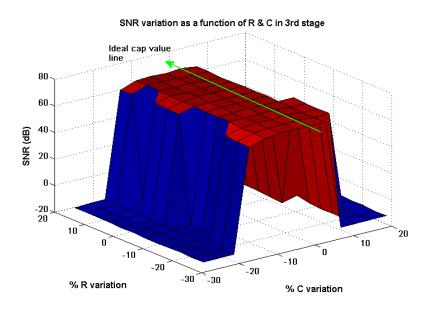

Similarly, the pole in the 3<sup>rd</sup> stage of the filter is defined by the RC product in that stage. Variation of SNR of the modulator with variation in the R and C is shown in Fig. 31.

Figure 31 Variation of SNR with change in the R & C values of 3<sup>rd</sup> stage

We can see from Fig. 31 that when the value of the capacitor increases by more than 4%, the modulator can become unstable.

To counter the effects of change in pole locations due to variations in component values, we need to be able to tune the values of the components to obtain the desired poles. In this work, this is accomplished by implementing the capacitor as a capacitor bank controllable by a digital code.

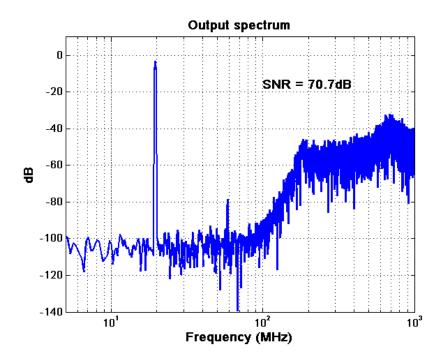

# 4.8 Results

The non-idealities discussed in this section were incorporated into the ideal behavioral model of the system in MATLAB. The output obtained for the same input conditions used earlier in section 3 (-3dBFS sine wave at 19.53MHz) is shown in Fig. 32.

Figure 32 Output spectrum of modulator with non-idealities

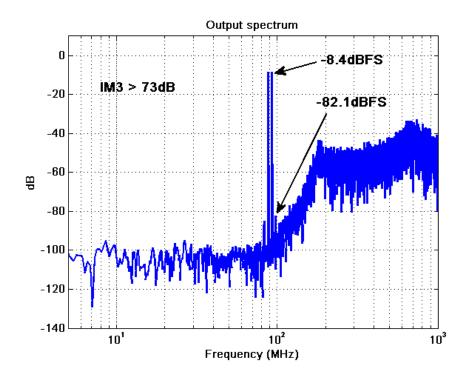

The output of a two-tone simulation to observe non-linearity is shown in Fig. 33. The inputs in this case are 2 -9dBFS sine waves at 87.9MHz and 92.8MHz, close to the signal bandwidth of 100MHz.

Figure 33 Two-tone simulation of modulator with non-idealities

#### 5. EXCESS LOOP DELAY

Excess loop delay (ELD) is a non-ideality that is unique to continuous-time (CT) sigmadelta modulators. ELD is caused due to the fact that the feedback pulse cannot be fed back instantaneously after the sampling instant due to delays in the quantizer and feedback DACs. This is not an issue in discrete-time sigma-delta modulators since they are sampled-data systems and only the final value of the settled waveforms are of interest. In multi-bit continuous-time modulators, if any linearization techniques like Dynamic Element Matching (DEM) are used to compensate for mismatches in the DACs, the additional delay aggravates the problem of ELD.

### 5.1 Effect on stability

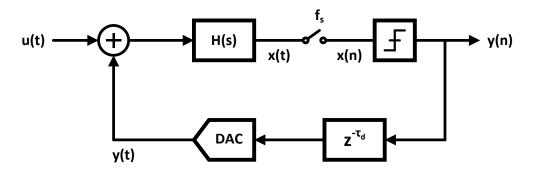

Fig. 34 shows a typical continuous-time sigma-delta modulator loop, where  $\tau_d$  represents the excess delay in the loop.

Figure 34 Continuous-time sigma-delta modulator with excess loop delay

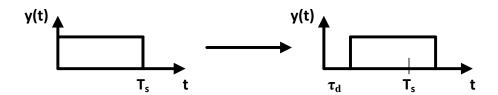

Fig. 35 shows the effect of such a delay on the feedback pulse in the system.

Figure 35 Feedback pulse in a modulator with excess loop delay

It was shown in section 3 that every continuous-time sigma-delta modulator can be transformed into an equivalent discrete-time one which has the same impulse response at the sampling instants by means of the impulse invariant transformation. From Fig. 35, it can be seen that the effect of the delay is that the feedback pulse is extended beyond the current sampling period. It has been shown that this alters the equivalence between the designed continuous-time modulator and corresponding discrete-time system [27]. In particular, this increases the order of the loop and can lead to instability.

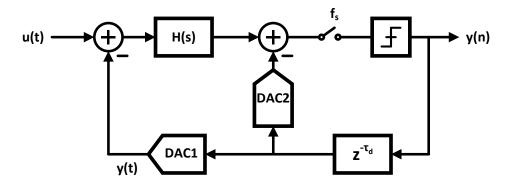

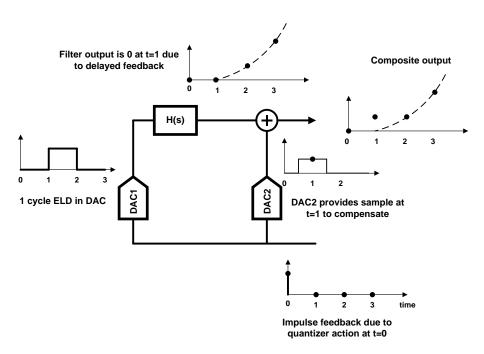

#### **5.2 Compensation Techniques**