# HARDWARE ACCELERATION OF ELECTRONIC DESIGN AUTOMATION ALGORITHMS

A Dissertation

by

#### KANUPRIYA GULATI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2009

Major Subject: Computer Engineering

# HARDWARE ACCELERATION OF ELECTRONIC DESIGN AUTOMATION **ALGORITHMS**

#### A Dissertation

by

#### KANUPRIYA GULATI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

### Approved by:

Chair of Committee, Sunil P. Khatri Committee Members,

Peng Li Jim Ji

Duncan M. Walker

Desmond A. Kirkpatrick

Costas N. Georghiades Head of Department,

December 2009

Major Subject: Computer Engineering

#### **ABSTRACT**

Hardware Acceleration of Electronic Design Automation Algorithms. (December 2009) Kanupriya Gulati, B.E., Delhi College of Engineering, New Delhi, India;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. Sunil P. Khatri

With the advances in very large scale integration (VLSI) technology, hardware is going parallel. Software, which was traditionally designed to execute on single core microprocessors, now faces the tough challenge of taking advantage of this parallelism, made available by the scaling of hardware. The work presented in this dissertation studies the acceleration of electronic design automation (EDA) software on several hardware platforms such as custom integrated circuits (ICs), field programmable gate arrays (FPGAs) and graphics processors. This dissertation concentrates on a subset of EDA algorithms which are heavily used in the VLSI design flow, and also have varying degrees of inherent parallelism in them. In particular, Boolean satisfiability, Monte Carlo based statistical static timing analysis, circuit simulation, fault simulation and fault table generation are explored. The architectural and performance tradeoffs of implementing the above applications on these alternative platforms (in comparison to their implementation on a single core microprocessor) are studied. In addition, this dissertation also presents an automated approach to accelerate uniprocessor code using a graphics processing unit (GPU). The key idea is to partition the software application into kernels in an automated fashion, such that multiple instances of these kernels, when executed in parallel on the GPU, can maximally benefit from the GPU's hardware resources.

The work presented in this dissertation demonstrates that several EDA algorithms can be successfully rearchitected to maximally harness their performance on alternative platforms such as custom designed ICs, FPGAs and graphic processors, and obtain speedups upto  $800\times$ . The approaches in this dissertation collectively aim to contribute towards enabling the computer aided design (CAD) community to accelerate EDA algorithms on arbitrary hardware platforms.

## To My Grandmas,

## Late Gurcharan Kaur Gulati and

Prakash Kaur Arora,

for their unassailable faith and patience.

#### **ACKNOWLEDGMENTS**

I can no other answer make, but thanks, and thanks, and ever thanks.

- William Shakespeare

This acknowledgment is an insufficient platform to express my deep sense of gratitude, but here's my heartfelt attempt.

In order to present this dissertation in its entirety, I *cannot not* acknowledge my Ph.D. adviser and mentor Dr. Sunil Khatri for his remarkable guidance, undying enthusiasm, high expertise and especially his *let's get it done* attitude. But for his constant support and timely critisism, this work may have never seen the light of day.

My thanks are due to my mentor at my Intel internships, and my Ph.D. committee member, Dr. Desmond Kirkpatrick, for inspiring me with his ingenious knowledge base, and for providing me the opportunity to intern at Strategic CAD Labs (SCL), and for extending his confidence towards my research.

I am grateful to my Ph.D. committee members, Drs. Hank Walker, Peng Li and Jim Ji, for their valuable feedback and encouragement for my research, and even more for being outstanding teachers.

During the (rather long) course of my graduate studies, I have had the opportunity to work with some extremely smart students in my research group. I would especially like to thank Nikhil and Rajesh, for being excellent lab mates, and inspiring me with their intense sincerity and hard work; Suganth, for letting me win at squash (at least until he learned it); Kalyan, for sharing a (teeny) part of his Linux expertise; Karan and Charu, for their tenacity at work and cheerful demeanor; and all past and present group members, for their infectious dedication.

I was fortunate to befriend some excellent folks at Texas A&M University. I thank

Prasenjit, for helping me believe over 'sushi and fish fry' that 'it all works out'; Richa, for interesting conversations over 'chai and paranthas'; Rouella and Harneet, for insanely delicious home-cooked dinners; and Gaurav for always ensuring that I 'Don't Panic', for driving thousands of miles and for being patient with me (more often than not).

I am grateful to my friends and family who helped me in ways one too many to list.

Above all, I owe it to my family - Mom, Dad, Samaira, Geety and Ashu, for being there, always.

## TABLE OF CONTENTS

| CHAPTER |         |                                                        | Page |

|---------|---------|--------------------------------------------------------|------|

| I       | INTRODU | JCTION                                                 | 1    |

|         | I-A.    | Hardware Platforms Considered in This Dissertation     | . 4  |

|         | I-B.    | EDA Algorithms Studied in This Dissertation            |      |

|         |         | 3.1. Control Dominated Applications                    |      |

|         | I-E     | 3.2. Control Plus Data Parallel Applications           |      |

|         | I-C.    | Automated Approach for GPU Based Software Acceleration |      |

|         | I-D.    | Chapter Summary                                        |      |

| II      | HARDWA  | ARE PLATFORMS                                          | 14   |

|         | II-A.   | Chapter Overview                                       | . 14 |

|         | II-B.   | Introduction                                           | . 15 |

|         | II-C.   | Hardware Platforms Studied in This Dissertation        | . 15 |

|         | II-     | C.1. Custom ICs                                        | . 15 |

|         | II-     | C.2. FPGAs                                             | . 16 |

|         | II-     | C.3. Graphics Processors                               | . 16 |

|         | II-D.   | General Overview and Architecture                      | . 17 |

|         | II-E.   | Programming Model and Environment                      | . 21 |

|         | II-F.   | Scalability                                            |      |

|         | II-G.   | Design Turn-around Time                                | . 24 |

|         | II-H.   | Performance                                            | . 24 |

|         | II-I.   | Cost of Hardware                                       | . 27 |

|         | II-J.   | Floating Point Operations                              | . 27 |

|         | II-K.   | Security and Real Time Applications                    | . 28 |

|         | II-L.   | Applications                                           | . 29 |

|         | II-M.   | Chapter Summary                                        | . 30 |

| III     | GPU ARC | CHITECTURE AND THE CUDA PROGRAMMING                    |      |

|         | MODEL   |                                                        | 31   |

|         | III-A.  | Chapter Overview                                       | . 31 |

|         | III-B.  | Introduction                                           | . 31 |

|         | III-C.  | Hardware Model                                         |      |

|         | III-D.  | Memory Model                                           | . 34 |

|         | III-E.  | Programming Model                                      | . 37 |

|         | III-F.  | Chapter Summary                                        | . 40 |

| CHAPTER | P                                                     | Page |

|---------|-------------------------------------------------------|------|

| IV      | ACCELERATING BOOLEAN SATISFIABILITY ON A CUS-         |      |

|         | TOM IC                                                | 41   |

|         | IV-A. Chapter Overview                                | 41   |

|         | IV-B. Introduction                                    | 42   |

|         | IV-C. Previous Work                                   | 45   |

|         | IV-D. Hardware Architecture                           | 47   |

|         | IV-D.1. Abstract Overview                             | 47   |

|         | IV-D.2. Hardware Overview                             | 48   |

|         | IV-D.3. Hardware Details                              | 49   |

|         | IV-D.3.a. Decision Engine                             | 49   |

|         | IV-D.3.b. Clause Cell                                 | 50   |

|         | IV-D.3.c. Base Cell                                   | 55   |

|         | IV-D.3.d. Partitioning the Hardware                   | 59   |

|         | IV-D.3.e. Inter-bank Communication                    | 61   |

|         | IV-E. An Example of Conflict Clause Generation        | 64   |

|         | IV-F. Partitioning the CNF Instance                   | 66   |

|         | IV-G. Extraction of the Unsatisfiable Core            | 68   |

|         | IV-H. Experimental Results                            | 70   |

|         | IV-I. Chapter Summary                                 | 76   |

| V       | ACCELERATING BOOLEAN SATISFIABILITY ON AN FPGA        | 77   |

|         | V-A. Chapter Overview                                 | 77   |

|         | V-B. Introduction                                     | 78   |

|         | V-C. Previous Work                                    | 79   |

|         | V-D. Hardware Architecture                            | 82   |

|         | V-D.1. Architecture Overview                          | 82   |

|         | V-E. Solving a CNF Instance Which Is Partitioned into |      |

|         | Several Bins                                          | 83   |

|         | V-F. Partitioning the CNF Instance                    | 85   |

|         | V-G. Hardware Details                                 | 87   |

|         | V-H. Experimental Results                             | 90   |

|         | V-H.1. Current Implementation                         | 90   |

|         | V-H.2. Performance Model                              | 92   |

|         | V-H.2.a. FPGA Resources                               | 92   |

|         | V-H.2.b. Clauses/Variable Ratio                       | 93   |

|         | V-H.2.c. Cycles Vs. Bin Size                          | 94   |

|         | V-H.2.d. Bins Touched Vs. Bin Size                    | 95   |

|         | V-H.2.e. Bin Size                                     | 96   |

| CHAPTER | Page                                                                                                                                                                                                                                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | V-H.3. Projections                                                                                                                                                                                                                                                                                                                           |

| VI      | ACCELERATING BOOLEAN SATISFIABILITY ON A GRAPHICS PROCESSING UNIT                                                                                                                                                                                                                                                                            |

|         | VI-A. Chapter Overview102VI-B. Introduction103VI-C. Related Previous Work105VI-D. Our Approach108VI-D.1. SurveySAT and the GPU108VI-D.1.a. SurveySAT109VI-D.1.b. SurveySAT on the GPU113VI-D.1.c. SurveySAT Results on the GPU115VI-D.2. MiniSAT Enhanced with Survey Propagation(MESP)VI-E. Experimental Results120VI-F. Chapter Summary121 |

| VII     | ACCELERATING STATISTICAL STATIC TIMING ANALYSIS USING GRAPHICS PROCESSORS                                                                                                                                                                                                                                                                    |

|         | VII-A. Chapter Overview123VII-B. Introduction124VII-C. Previous Work127VII-D. Our Approach129VII-D.1. Static Timing Analysis (STA) at a Gate130VII-D.2. Statistical Static Timing Analysis (SSTA) at a Gate133VII-E. Experimental Results136VII-F. Chapter Summary139                                                                        |

| VIII    | ACCELERATING FAULT SIMULATION USING GRAPHICS PROCESSORS                                                                                                                                                                                                                                                                                      |

| CHAPTER | P                                                                                                                                                                                                                                                                                                                                                                                                                                            | age                                                  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|         | VIII-D.4. Fault Simulation of a Circuit                                                                                                                                                                                                                                                                                                                                                                                                      | 155                                                  |

| IX      | FAULT TABLE GENERATION USING GRAPHICS PROCESSORS                                                                                                                                                                                                                                                                                                                                                                                             | 159                                                  |

|         | IX-A. Chapter Overview IX-B. Introduction IX-C. Previous Work IX-D. Our Approach IX-D.1. Definitions IX-D.2. Algorithms: FSIM* and GFTABLE IX-D.2.a. Generating Vectors (Line 9) IX-D.2.b. Fault Free Simulation (Line 10) IX-D.2.c. Computing Detectabilities and Cumulative Detectabilities (Lines 13, 14) IX-D.2.d. Fault Simulation of SR(s) (Lines 15, 16) IX-D.2.e. Generating the Fault Table (Line 22-31) IX-E. Experimental Results | 160<br>163<br>164<br>165<br>169<br>170<br>171<br>177 |

| X       | IX-F. Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |

|         | X-A. Chapter Overview                                                                                                                                                                                                                                                                                                                                                                                                                        | 186<br>186<br>190<br>192                             |

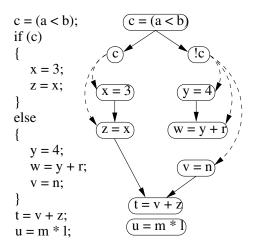

|         | X-D.1.a. Inlining If-Then-Else Code                                                                                                                                                                                                                                                                                                                                                                                                          | 194<br>196<br>197<br>200<br>200                      |

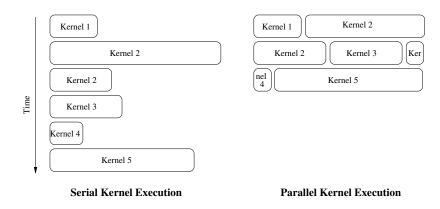

| XI      | AUTOMATED APPROACH FOR GRAPHICS PROCESSOR BASED SOFTWARE ACCELERATION                                                                                                                                                                                                                                                                                                                                                                        | 205                                                  |

|         | XI-A. Chapter Overview                                                                                                                                                                                                                                                                                                                                                                                                                       | 205                                                  |

| CHAPTER   |                                                       | Page   |

|-----------|-------------------------------------------------------|--------|

|           | XI-B. Introduction                                    | 206    |

|           | XI-C. Our Approach                                    | 208    |

|           | XI-C.1. Problem Definition                            | 209    |

|           | XI-C.2. GPU Constraints on the Kernel Generation Engi | ne 209 |

|           | XI-C.3. Automatic Kernel Generation Engine            | 211    |

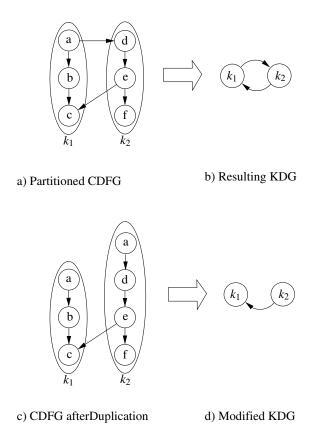

|           | XI-C.3.a. Node Duplication                            | 214    |

|           | XI-C.3.b. Cost of a Partitioning Solution             | 215    |

|           | XI-D. Experimental Results                            | 216    |

|           | XI-D.1. Evaluation Methodology                        | 216    |

|           | XI-E. Chapter Summary                                 |        |

| XII       | CONCLUSIONS                                           | 221    |

| REFERENCE | ES                                                    | 230    |

| VITA      |                                                       | 253    |

## LIST OF TABLES

| TABLE  |                                                             | Page  |

|--------|-------------------------------------------------------------|-------|

| IV.1   | Encoding of {reg,reg_bar} Bits                              | . 52  |

| IV.2   | Encoding of {lit,lit_bar} and var_implied Signals           | . 54  |

| IV.3   | Partitioning and Binning Results                            | . 72  |

| IV.4   | Comparing against MiniSAT (a BCP-based Software SAT Solver) | . 75  |

| V.1    | Number of Bins Touched with Respect to Bin Size             | . 96  |

| V.2    | LUT Distribution for FPGA Devices                           | . 97  |

| V.3    | Runtime Comparison XC4VFX140 Versus MiniSAT                 | . 99  |

| VI.1   | Comparing MiniSAT with SurveySAT (CPU) and SurveySAT (GPU)  | . 116 |

| VI.2   | Comparing MESP with MiniSAT                                 | . 120 |

| VII.1  | Monte Carlo Based SSTA Results                              | . 137 |

| VIII.1 | Encoding of the Mask Bits                                   | . 151 |

| VIII.2 | Parallel Fault Simulation Results                           | . 156 |

| IX.1   | Fault Table Generation Results with $L = 32K$               | . 179 |

| IX.2   | Fault Table Generation Results with $L = 8K$                | . 181 |

| IX.3   | Fault Table Generation Results with $L = 16K$               | . 182 |

| X.1    | Speedup for BSIM3 Evaluation                                | . 201 |

| X.2    | Speedup for Circuit Simulation                              | . 202 |

| XI.1   | Validation of the Automatic Kernel Generation Approach      | . 219 |

## LIST OF FIGURES

| FIGURE |                                              | Page |

|--------|----------------------------------------------|------|

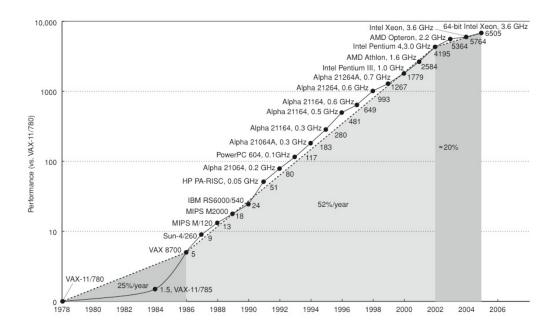

| I.1    | CPU Performance Growth                       | 2    |

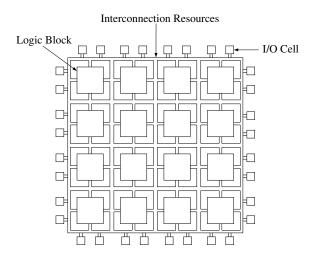

| II.1   | FPGA Layout                                  | 17   |

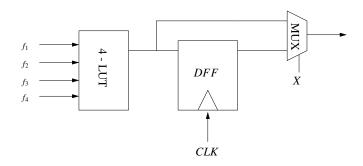

| II.2   | Logic Block in the FPGA                      | 18   |

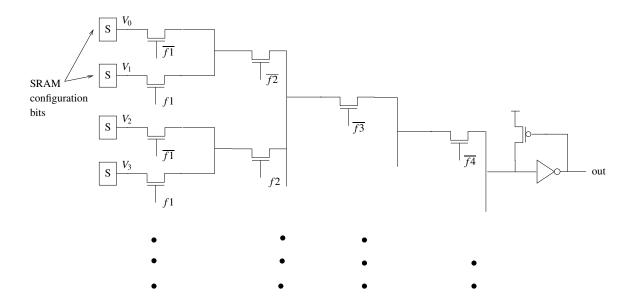

| II.3   | LUT Implementation Using a 16:1 MUX          | 19   |

| II.4   | SRAM Configuration Bit Design                | 20   |

| II.5   | Comparing Gflops of GPUs and CPUs            | 21   |

| II.6   | FPGA Growth Trend                            | 25   |

| III.1  | CUDA for Interfacing with GPU Device         | 32   |

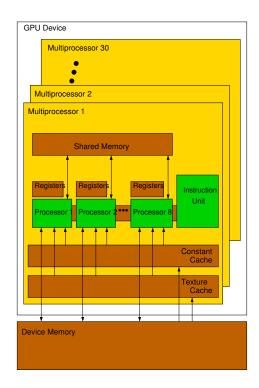

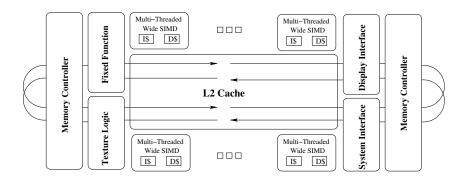

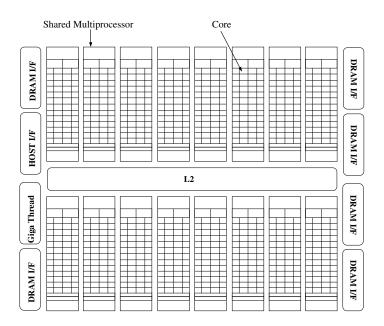

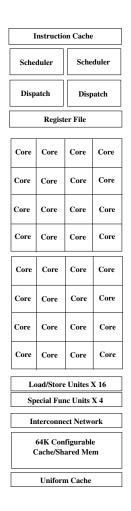

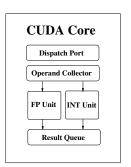

| III.2  | Hardware Model of the NVIDIA GeForce GTX 280 | 33   |

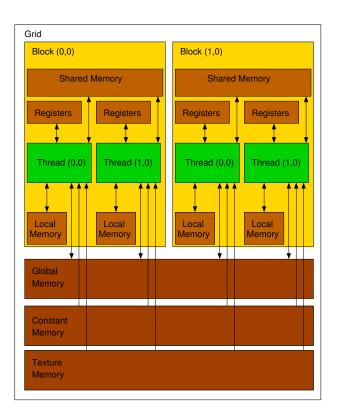

| III.3  | Memory Model of the NVIDIA GeForce GTX 280   | 34   |

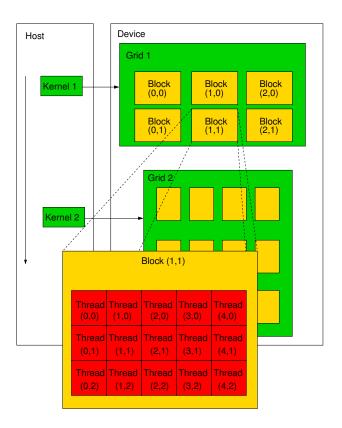

| III.4  | Programming Model of CUDA                    | 37   |

| IV.1   | Abstracted View of the Proposed Idea         | 48   |

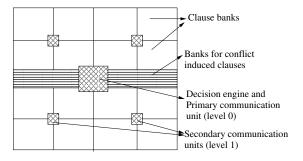

| IV.2   | Generic Floorplan                            | 49   |

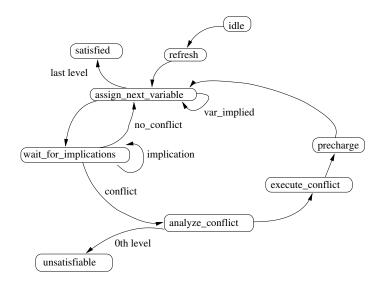

| IV.3   | State Diagram of the Decision Engine         | 51   |

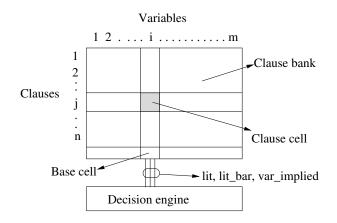

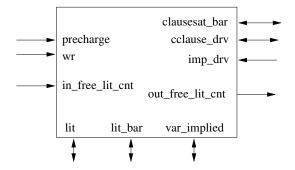

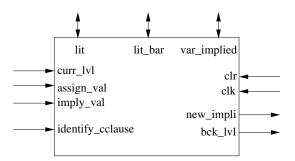

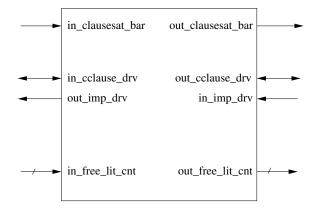

| IV.4   | Signal Interface of the Clause Cell          | 52   |

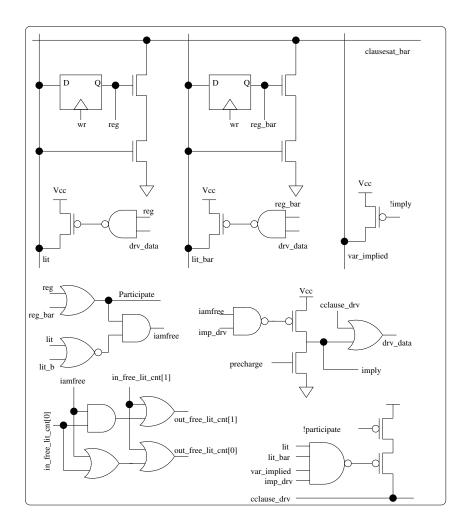

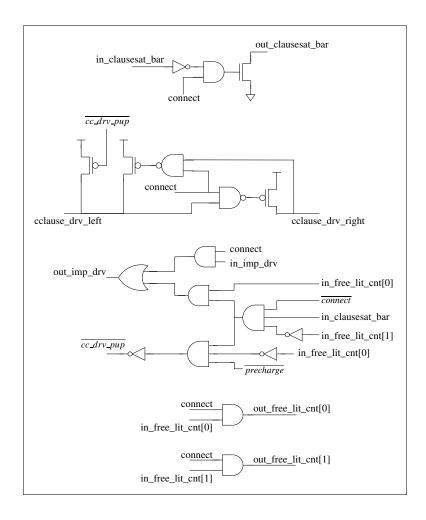

| IV.5   | Schematic of the Clause Cell                 | 53   |

| IV.6   | Layout of the Clause Cell                    | 55   |

| IV.7   | Signal Interface of the Base Cell            | 55   |

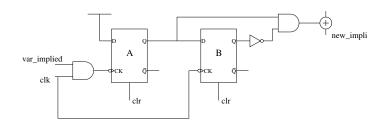

| IV.8   | Indicating a New Implication                 | 57   |

| IV.9   | Computing Backtrack Level                    | 59   |

| FIGURE | 3                                                                                                   | Page  |

|--------|-----------------------------------------------------------------------------------------------------|-------|

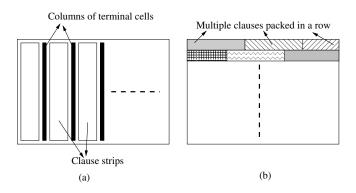

| IV.10  | (a) Internal Structure of a Bank (b) Multiple Clauses Packed in One Bank-row                        | . 60  |

| IV.11  | Signal Interface of the Terminal Cell                                                               | . 60  |

| IV.12  | Schematic of a Terminal Cell                                                                        | . 62  |

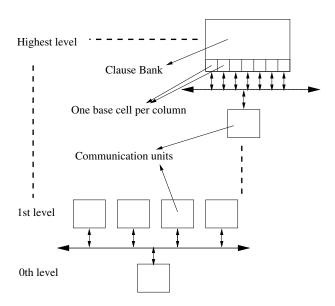

| IV.13  | Hierarchical Structure for Inter-bank Communication                                                 | . 63  |

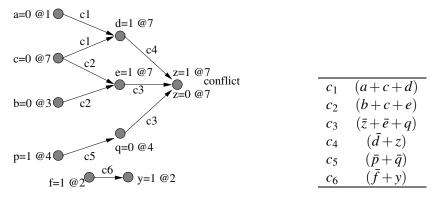

| IV.14  | Example of Implicit Traversal of Implication Graph                                                  | . 65  |

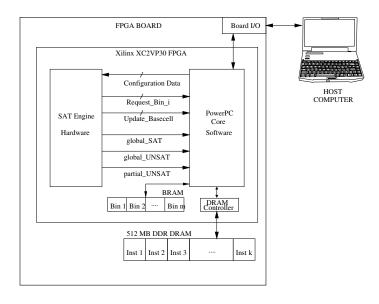

| V.1    | Hardware Architecture                                                                               | . 83  |

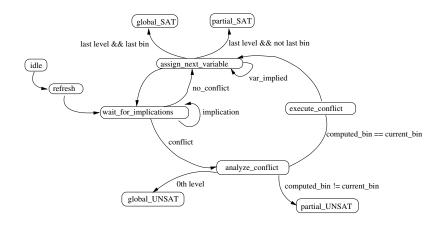

| V.2    | State Diagram of the Decision Engine                                                                | . 90  |

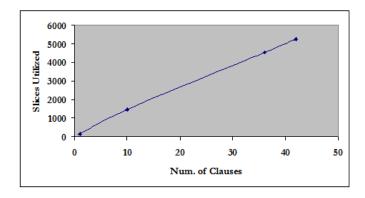

| V.3    | Resource Utilization for Clauses                                                                    | . 92  |

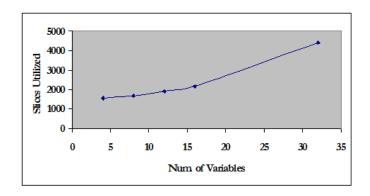

| V.4    | Resource Utilization for Variables                                                                  | . 93  |

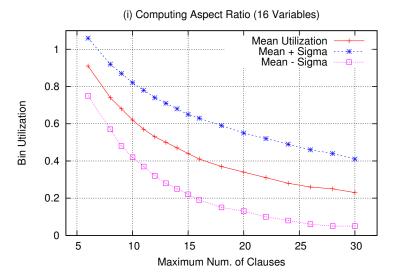

| V.5    | Computing Aspect Ratio (16 Variables)                                                               | . 94  |

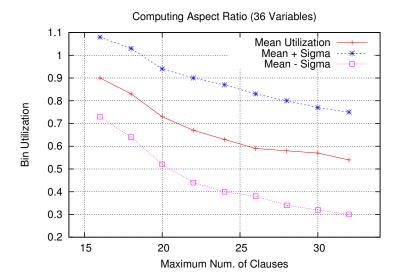

| V.6    | Computing Aspect Ratio (36 Variables)                                                               | . 95  |

| VI.1   | Data Structure of the SAT Instance on the GPU                                                       | . 115 |

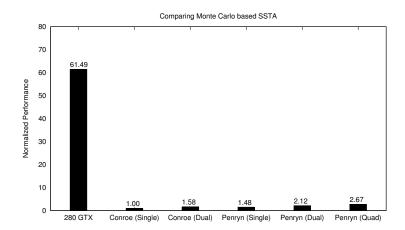

| VII.1  | Comparing Monte Carlo Based SSTA on GTX 280 GPU and Intel Core 2 Processors (with SEE Instructions) | . 139 |

| VIII.1 | Truth Tables Stored in a Look-up Table                                                              | . 147 |

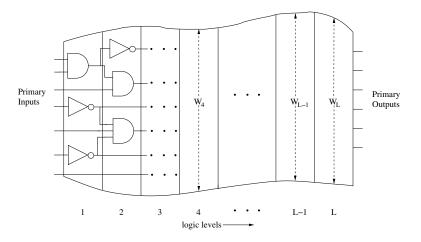

| VIII.2 | Levelized Logic Netlist                                                                             | . 154 |

| IX.1   | Example Circuit                                                                                     | . 166 |

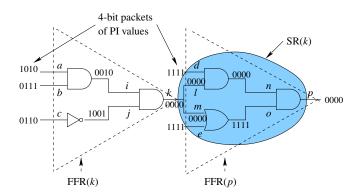

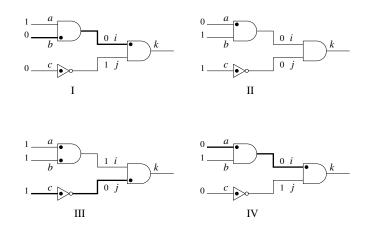

| IX.2   | CPT on FFR( <i>k</i> )                                                                              | . 171 |

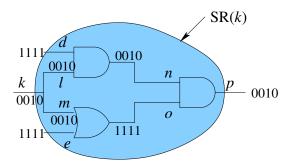

| IX.3   | Fault Simulation on $SR(k)$                                                                         | . 176 |

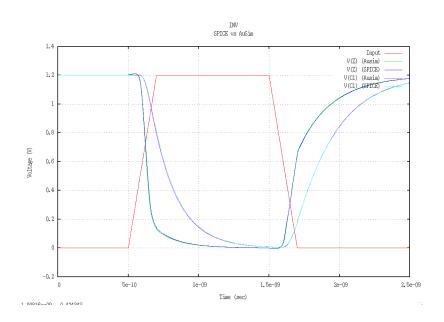

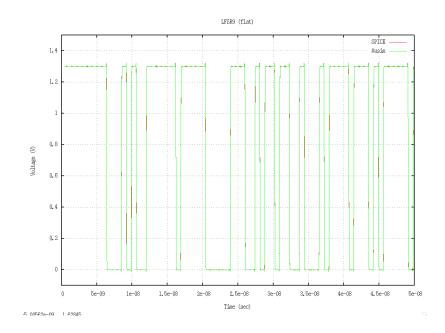

| X.1    | Industrial_2 Waveforms                                                                              | . 203 |

| X.2    | Industrial_3 Waveforms                                                                              | . 204 |

| XI.1   | CDFG Example                                                                                        | . 213 |

| FIGURE |                                                               | Page  |

|--------|---------------------------------------------------------------|-------|

| XI.2   | KDG Example                                                   | 214   |

| XII.1  | New Parallel Kernel GPUs                                      | 226   |

| XII.2  | Larrabee Architecture from Intel                              | 226   |

| XII.3  | Fermi Architecture from NVIDIA                                | . 227 |

| XII.4  | Block Diagram of a Single Shared Multiprocessor (SM) in Fermi | 228   |

| XII.5  | Block Diagram of a Single Processor (Core) in SM              | 229   |

#### CHAPTER I

#### INTRODUCTION

With the advances in VLSI technology over the past few decades, several software applications got a 'free' performance boost, without needing any code redesign. The steadily increasing clock rates and higher memory bandwidths resulted in improved performance with zero software cost. However, more recently, the gain in the single core performance of general-purpose processors has diminished due to the decreased rate of increase of operating frequencies. This is because VLSI system performance hit two big *walls*:

- the *memory wall* and

- the *power wall*.

The memory wall refers to the increasing gap between processor and memory speeds. This results in an increase in cache sizes required to hide memory access latencies. Eventually the memory bandwidth becomes the bottleneck in performance. The power wall refers to power supply limitations or thermal dissipation limitations (or both) - which impose a hard constraint on the total amount of power that processors can consume in a system. Together, these two walls reduce the performance gains expected for general purpose processors, as shown in Figure I.1 [1]. Due to these two factors, the rate of increase of processor frequency has greatly decreased. Further, the VLSI system performance has not shown much gain from continued processor frequency increases as was once the case.

Further, newer manufacturing and device constraints are faced with decreasing feature sizes, making future performance increases harder to obtain. A leading processor design company summarized the causes of reduced speed improvements in their white paper [2]

The journal model is *IEEE Transactions on Automatic Control*.

Fig. I.1. CPU Performance Growth

stating, First of all, as chip geometries shrink and clock frequencies rise, the transistor leakage current increases, leading to excess power consumption and heat ... Secondly, the advantages of higher clock speeds are in part negated by memory latency, since memory access times have not been able to keep pace with increasing clock frequencies. Third, for certain applications, traditional serial architectures are becoming less efficient as processors get faster (due to the so-called Von Neumann bottleneck), further undercutting any gains that frequency increases might otherwise buy. In addition, partly due to limitations in the means of producing inductance within solid state devices, resistance-capacitance (RC) delays in signal transmission are growing as feature sizes shrink, imposing an additional bottleneck that frequency increases don't address.

In order to maintain increasing peak performance trends without being hit by these 'walls', the microprocessor industry rapidly shifted to multi-core processors. As a conse-

quence of this shift in microprocessor design, traditional single threaded applications no longer see significant gains in performance with each processor generation, unless these applications are rearchitectured to take advantage of the multi-core processors. This is due to the *instruction level parallelism (ILP) wall*, which refers to the rising difficulty in finding enough parallelism in the existing instructions stream of a single process, making it hard to keep multiple cores busy. The ILP wall further compounds the difficulty of performance scaling at the application level. These *walls* are a key problem for several software applications, including software for electronic design.

The electronic design automation (EDA) field collectively uses a diverse set of software algorithms and tools, which are required to design complex next generation electronics products. The increase in VLSI design complexity poses a challenge to the EDA community, since single-thread performance is not scaling effectively due to reasons mentioned above. Parallel hardware presents an opportunity to solve this dilemma, and opens up new design automation opportunities which yield orders of magnitude faster algorithms. In addition to multi-core processors, other hardware platforms may be viable alternatives to achieve this acceleration as well. These include custom designed ICs, reconfigurable hardware such as FPGAs, and streaming processors such as graphics processing units. All these alternatives need to be investigated as potential solutions for accelerating EDA applications. This dissertation studies the feasibility of using these alternative platforms for a subset of EDA applications which

- address some extremely important steps in the VLSI design flow and

- have varying degrees of inherent parallelism in them.

The rest of this chapter is organized as follows. In the next section, we briefly introduce the hardware platforms that are studied in this dissertation. In Section I-B we discuss the EDA applications considered in this dissertation. In Section I-C we discuss our approach to automatically generate Graphics Processing Unit (GPU) based code to accelerate uniprocessor software. Section I-D summarizes this chapter.

#### I-A. Hardware Platforms Considered in This Dissertation

In this dissertation, we explore three following hardware platforms for accelerating EDA applications. *Custom designed ICs* are arguably the fastest accelerators we have today, easily offering several orders of magnitude speedup compared to the single threaded software performance on the CPU [3]. These chips are application specific, and thus deliver high performance for the target application, albeit at a high cost.

Field Programmable Gate Arrays (FPGAs) are arrays of reconfigurable logic and are popular devices for hardware prototyping. Recently, high performance systems have begun to increasingly utilize FPGAs because of improvements in FPGA speeds and densities. The increasing cost of custom IC implementations along with improvements in FPGA tool flows has helped make FPGAs viable platforms for an increasing number of applications.

Graphic Processing Units (GPUs) are designed to operate in a Single Instruction Multiple Data (SIMD) fashion. GPUs are being actively explore for general purpose computations in recent times [4, 5, 6]. The rapid increase in the number and diversity of scientific communities exploring the computational power of GPUs for their data intensive algorithms has arguably had a contribution in encouraging GPU manufacturers to design easily programmable general purpose GPUs (GPGPUs). GPU architectures have been continuously evolving towards higher performance, larger memory sizes, larger memory bandwidths and relatively lower costs.

In Chapter II, we compare and contrast the hardware platforms that are considered in this dissertation. In particular, we discuss custom designed ICs, reconfigurable architectures such as FPGAs, and streaming processors such as graphics processing units (GPUs). This comparison is performed over various criteria such as architecture, expected performance, programming model and environment, scalability, time to market, security, cost of hardware, etc. In Chapter III, we describe the programming environment used for interfacing with the GPUs.

Note that the hardware platforms discussed in this dissertation require an (expensive) communication link with the host processor. All the EDA applications considered have to work around this communication cost, in order to obtain a healthy speedup on their target platform. Future generation hardware architectures may not face a high communication cost. This would be the case if the host and the accelerator are implemented on the same die, or share the same physical RAM. However, for existing architectures, it is important to consider the cost of this communication while discussing the feasibility of the platform for a particular application.

#### I-B. EDA Algorithms Studied in This Dissertation

In this dissertation, we study two different categories of EDA algorithms, namely *control* dominated and control plus data parallel algorithms. Our work demonstrates the rearchitecting of EDA algorithms from both these categories, to maximally harness their performance on the alternative platforms under consideration. We chose applications for which there is a strong motivation to accelerate, since they are used in key time-consuming steps in the VLSI design flow. Further, these applications have different degrees of inherent parallelism in them, which make them an interesting implementation challenge for these alternative platforms. In particular, Boolean satisfiability, Monte Carlo based statistical static timing analysis, circuit simulation, fault simulation and fault table generation are explored.

#### I-B.1. Control Dominated Applications

In the control dominated algorithms category, this dissertation studies the implementation of Boolean satisfiability (SAT) on the custom IC, FPGA and GPU platforms. SAT is a classic NP-complete problem, and has been widely studied in the past. Given a set V of variables, and a collection C of Conjunctive Normal Form (CNF) clauses over V, the SAT problem consists of determining if there is a satisfying truth assignment for C. Given the broad applicability of SAT to several diverse application domains such as logic synthesis, circuit testing, verification, pattern recognition and others [7], there has been much effort devoted to devising efficient heuristics to solve SAT. In this dissertation we present hardware solutions to the SAT problem, with the main goals of scalability and speedup.

In Chapter IV, we discuss a custom IC based hardware approach to accelerate SAT. In this approach, the traversal of the implication graph as well as conflict clause generation are performed in hardware, in parallel. We also propose a hardware approach to extract the minimum unsatisfiable core (i.e. the sub-formula consisting of the smallest set of clauses of the initial formula which is unsatisfiable) for any unsatisfiable formula. We store the clause literals in specially designed clause cells and implement the clauses in banks, such that clauses of variable widths can be accommodated in these banks. We also perform an upfront partitioning of the SAT problem in order to better utilize these banks. Our custom IC based solution demonstrates significantly larger capacity than existing hardware SAT solvers, and is scalable in the sense that several ICs can be effectively used to simultaneously operate on the same large SAT instance. We conducted layout and SPICE studies to estimate the area, power and speed of this solution. Our approach has been functionally validated in Verilog. Our experiments show that instances with approximately 63K clauses can be accommodated on a single IC of size 1.5cm×1.5cm. Our custom IC based SAT solver results in over 3 orders of magnitude speed improvement over BCP based soft-

ware SAT approaches. Further, the capacity of our approach is significantly higher than all existing hardware based approaches.

In Chapter V, we discuss an FPGA based hardware approach to accelerate SAT. In this approach, we store the clause literals in the FPGA slices. In order to solve large SAT instances, we partition the clauses into 'bins', each of which can fit in the FPGA. This is done in a pre-processing step. In general, these bins may share variables and hence do not solve independent sub-problems. The FPGA operates on one bin at a time. All the bins of the partitioned SAT problem are stored in the on-chip Block RAM (BRAM). The embedded PowerPC processor on the FPGA performs the task of loading the appropriate bin from the BRAM. Conflict clause generation and Boolean constant propagation (BCP) are performed in parallel in the FPGA hardware. The entire flow, which includes the preprocessing step, loading of the BRAM, programming the PowerPC and the subsequent communication between partitions (which is required for BCP, conflict clause generation and both inter- and intra-bin non-chronological backtracking) has been automated and verified for correctness on a Virtex-II Pro (XC2VP30) FPGA board. Experimental results and their analysis, along with the performance models, are discussed in detail. Our results demonstrate that an order of magnitude improvement in runtime can be obtained over the best-in-class software based approach, by using a Virtex-4 (XC4VFX140) FPGA device. The resulting system can handle instances with as many as 10K variables and 280K clauses.

In Chapter VI, we present a SAT approach which employs a new GPU-enhanced variable ordering heuristic. In this approach, we augment a CPU-based complete procedure, with a GPU based approximate procedure (which benefits from the high parallelism of the GPU). The CPU implements MiniSAT, while the GPU implements SurveySAT. The SAT instance is read and the search is initiated on the CPU. After a user-specified fraction of decisions have been made, the CPU invokes the GPU based SurveySAT procedure multiple times and updates its variable ordering based on any decisions made by SurveySAT. This

approach retains completeness (since it is implements a complete procedure) but has the potential of high speedup (since the approximate procedure is executed on a highly parallel graphics processor based platform). Experimental results demonstrate an average 64% speedup up over MiniSAT, for several satisfiable and unsatisfiable benchmarks.

#### I-B.2. Control Plus Data Parallel Applications

Among EDA problems with varying amounts of control and data parallelism, we accelerated the following applications using GPUs.

• Statistical Static Timing Analysis (SSTA) Using Graphics Processors With the diminishing minimum feature sizes of VLSI fabrication processes, the impact of process variations is becoming increasingly significant. The resulting increase in delay variations significantly affects the timing yield and the maximum operating frequency of designs. Static timing analysis (STA) is heavily used in a conventional VLSI design flow to estimate circuit delay and the maximum operating frequency of the design. Statistical STA (SSTA) was developed to include the effect of process variations, in order to analyze circuit delay more accurately. Monte Carlo based SSTA is a simple and accurate method of performing SSTA. However, its main drawback is its high runtime. We exploit the inherent parallelism in Monte Carlo based SSTA, and present its implementation on a GPU in Chapter VII. In this approach we map Monte Carlo based SSTA to the large number of threads that can be computed in parallel on a GPU. Our approach performs multiple delay simulations of a single gate in parallel. Our approach further benefits from a parallel implementation of the Mersenne Twister pseudo-random number generator on the GPU, followed by Box-Muller transformations (also implemented on the GPU). These are used for generating gate delay numbers from a normal distribution. We only need to store the  $\mu$  and  $\sigma$

of the pin-to-output delay distributions for all inputs and for every gate. This data is stored in fast cached memory on the GPU, and we thereby leverage the large memory bandwidth of the GPU. All threads compute identical instructions, but on different data, with no control or data dependency, as required by the SIMD programming semantics of the GPU. Our approach is implemented on a NVIDIA GeForce GTX 280 GPU card. Experimental results indicate that this approach can obtain an average speedup of about 818× as compared to a serial CPU implementation. With the recently announced cards with quad GTX 280 GPUs, we estimate that our approach would attain a speedup of over 2400×.

#### • Accelerating Fault Simulation on a Graphics Processor

In today's complex digital designs, with possibly several million gates, the number of faulty variations of the design can be dramatically higher. Fault simulation is an important but expensive step of the VLSI design flow, and it helps to identify faulty designs. Given a digital design and a set of input vectors V defined over its primary inputs, fault simulation evaluates the number of stuck-at faults  $F_{sim}$  that are tested by applying the vectors V. The ratio of  $F_{sim}$  to the total number of faults in the design  $F_{total}$  is a measure of the fault coverage. The task of finding this ratio is often referred to as  $fault\ grading$  in the industry. Given the high computational cost for fault simulation, it is extremely important to explore ways to accelerate this application. The ideal fault simulation approach should be fast, scalable, and cost effective. In Chapter VIII, we study the acceleration of fault simulation on a GPU. Fault simulation is inherently parallelizable, and the large number of threads that can be executed in parallel on a GPU can be employed to perform a large number of gate evaluations in parallel. We implement a pattern and fault parallel fault simulator, which fault-simulates a circuit in a levelized fashion. We ensure that all threads of the GPU

compute identical instructions, but on different data. Fault injection is also performed along with gate evaluation, with each thread using a different fault injection mask. Since GPUs have an extremely large memory bandwidth, we implement each of our fault simulation threads (which execute in parallel with no data dependencies) using memory lookup. Our experiments indicate that our approach, implemented on a single NVIDIA GeForce GTX 280 GPU card, can simulate on average 47× faster when compared to an industrial fault simulator. On a Tesla (8-GPU) system, our approach is potentially 300× faster.

#### • Fault Table Generation using a Graphics Processor

A fault table is essential for fault diagnosis during VLSI testing and debug. Generating a fault table requires extensive fault simulation, with no fault dropping, This is extremely expensive from a computational standpoint. We explore the generation of a fault table using a GPU in Chapter IX. We employ a pattern parallel approach, which utilizes both bit-parallelism and thread-level parallelism. Our implementation is a significantly modified version of FSIM, which is pattern parallel fault simulation approach for single core processors. Like FSIM, our approach utilizes critical path tracing and the dominator concept to reduce runtime by pruning unnecessary simulations. Further modifications to FSIM allow us to maximally harness the GPU's immense memory bandwidth and high computational power. In this approach we do not store the circuit (or any part of the circuit) on the GPU. We implement efficient parallel reduction operations to speed up fault table generation. In comparison to FSIM\*, which is FSIM modified to generate a fault table on a single core processor, our approach on a single NVIDIA Quadro FX 5800 GPU card can generate a fault table  $15 \times$  faster on average. On a Tesla (8-GPU) system, our approach can potentially generate the same fault table  $90 \times$  faster.

#### • Fast Circuit Simulation Using Graphics Processor

SPICE based circuit simulation is a traditional workhorse in the VLSI design process. Given the pivotal role of SPICE in the IC design flow, there has been significant interest in accelerating SPICE. Since a large fraction (on average 75%) of the SPICE runtime is spent in evaluating transistor model equations, a significant speedup can be availed if these evaluations are accelerated. We study the speedup obtained by implementing the transistor model evaluation on a GPU, and porting it to a commercial fast SPICE tool in Chapter X. Our experiments demonstrate that significant speedups  $(2.36 \times \text{ on average})$  can be obtained for the commercial fast SPICE tool. The asymptotic speedup that can be obtained is about  $4 \times .$  We demonstrate that with circuits consisting of as few as about 1000 transistors, speedups in the neighborhood of this asymptotic value can be obtained.

#### I-C. Automated Approach for GPU Based Software Acceleration

Due to the high degree of available hardware parallelism on the GPU, these platforms have received significant interest for accelerating scientific software. The task of implementing a software application on a GPU currently requires significant manual effort (porting, iteration and experimentation). In Chapter XI, we explore an automated approach to partition a uniprocessor software application into kernels (which are executed in parallel on the GPU). The key idea here is to partition a software subroutine into kernels in an automated fashion, such that multiple instances of these kernels, when executed in parallel on the GPU, can maximally benefit from the GPU's hardware resources. The input to our algorithm is a uniprocessor subroutine which is executed multiple times, on different data, and needs to be accelerated on the GPU. Our approach aims at automatically partitioning this routine into GPU kernels. This is done by first extracting a graph which models the

data and control dependencies of the subroutine in question. This graph is then partitioned. Various partitions are explored, and each is assigned a cost which accounts for GPU hardware and software constraints, as well as the number of instances of the subroutine that are issued in parallel. From the least cost partition, our approach automatically generates the resulting GPU code. Experimental results demonstrate that our approach correctly and efficiently produces fast GPU code, with high quality. We show that with our partitioning approach, we can speed up certain routines by 15% on average when compared to a monolithic (unpartitioned) implementation. Our entire technique (from reading a C subroutine to generating the partitioned GPU code) is completely automated, and has been verified for correctness.

#### I-D. Chapter Summary

In recent times, improvements in VLSI system performance have slowed due to several walls that are being faced. Key among these are the power and memory walls. Since the growth of single-processor performance is hampered due to these walls, EDA software needs to explore alternate platforms, in order to deliver the increased performance required to design the complex electronics of the future.

In this dissertation, we explore the acceleration of several different EDA algorithms (with varying degrees of inherent parallelism) on alternative hardware platforms. We explore custom ICs, FPGAs and graphics processors as the candidate platforms. We study the architectural and performance tradeoffs involved in implementing several EDA algorithms on these platforms. We study two classes of EDA algorithms in this dissertation, i) control dominated algorithms such as Boolean Satisfiability (SAT) and ii) control plus data parallel algorithms such as Monte Carlo based statistical static timing analysis, circuit simulation, fault simulation and fault table generation. Another contribution of this dissertation is to

automatically generate GPU code to accelerate software routines that are run repeatedly on independent data.

This dissertation is organized as follows. In Chapters II and III, different hardware platforms are compared, and the programming model used for interfacing with the GPU platform is presented. We present the following techniques to accelerate a control dominated algorithm (Boolean Satisfiability). We present an IC-based approach (Chapter IV), an FPGA-based approach (Chapter V) and a GPU-based scheme (Chapter VI) to accelerate SAT. We present our approaches to accelerate control and data parallel applications in the next four chapters. In particular we focus on accelerating Monte Carlo based SSTA (Chapter VII), fault simulation (Chapter VIII), fault table generation (Chapter IX) and model card evaluation of SPICE (Chapter X), on a graphics processor. Finally, in Chapter XI, we present an automated approach for GPU based software acceleration. The dissertation is concluded in Chapter XII, along with a brief description of next generation hardware platforms. The larger goal of this work is to provide techniques to enable the acceleration of EDA algorithms on different hardware platforms.

#### CHAPTER II

#### HARDWARE PLATFORMS

#### II-A. Chapter Overview

As discussed in Chapter I, single threaded software applications no longer obtain significant gains in performance with the current processor scaling trends. With the growing complexity of VLSI designs, this is a significant problem for the electronic design automation (EDA) community. In addition to multi-core processors, hardware based accelerators such as custom designed ICs, reconfigurable hardware such as FPGAs, and streaming processors such as Graphics Processing units (GPUs) - are being investigated as a potential solution to this problem. These platforms allow the CPU to offload compute intensive portions of an application to the hardware for a faster computation, and the results are transferred back to the CPU upon completion. Different platforms are best suited for different application scenarios and algorithms. The pros and cons of the platforms under consideration are discussed in this chapter.

The rest of this chapter is organized as follows. Section II-B discusses the hardware platforms studied in this dissertation, with a brief introduction of custom ICs, FPGAs and GPUs in Section II-C. Sections II-D and II-E compare the hardware architecture and programming environment of these platforms. Scalability of these platforms is discussed in Section II-F, while design turn around time on these platforms is compared in Section II-G. These platforms are contrasted for performance and cost of hardware in Sections II-H and II-I, respectively. The implementation of floating point operations on these platforms is compared in Section II-J, while security concerns are discussed in Section II-K. Suitable applications for these platforms are discussed in Section II-L. The chapter is summarized in Section II-M.

#### II-B. Introduction

Most hardware accelerators are not stand alone platforms, but are co-processors to a CPU. In other words, a CPU is needed for initial processing, before the compute intensive task is offloaded to the hardware accelerators. In some cases the hardware accelerator might communicate with the CPU even during the computation. The different platforms for hardware acceleration in this dissertation are compared in the following sections.

#### II-C. Hardware Platforms Studied in This Dissertation

#### II-C.1. Custom ICs

Traditionally, custom ICs are included in a product to improve its performance. With a high production volume, the high manufacturing cost of the IC is easily amortized. Among existing hardware platforms, custom ICs are easily the fastest accelerators. By being application specific, they can deliver very high performance for the target application. There exist a vast literature of advanced circuit design techniques which help in reducing the power consumption of such ICs while maintaining high performance [8]. Some of the more well known techniques to reduce power consumption (both dynamic and leakage) are design and protocol changes [9, 10], reducing supply voltage [11], variable Vt devices, dynamic bulk modulation [12, 13], power gating [14] and input vector control [15, 16, 17]. Also, newer gate materials which help achieve further performance gains at a low power cost are being investigated [18]. Due to their high performance and small footprint, custom ICs are the most suitable accelerators for space, military and medical applications that are compute intensive.

#### II-C.2. FPGAs

A field-programmable gate array (FPGA) is an integrated circuit which is designed to be configured by the designer in the field. The FPGA is generally programmed using a hardware description language (HDL). The ability of the user to program the functionality of the FPGA in the field, along with the low non-recurring engineering costs (relative to a custom IC design) make the FPGA an attractive platform for many applications. FPGAs have significant performance advantages over microprocessors due to their highly parallel architectures and significant flexibility. Hardware-level parallelism allows FPGA-based applications to operate 1 to 2 orders of magnitude faster than equivalent applications running on an embedded processor, or even a high-end workstation. Compared to custom ICs, FP-GAs have a somewhat lower performance, but their reconfigurability makes them an easy choice for several (particularly low-volume) applications.

#### II-C.3. Graphics Processors

General purpose graphics processors turn the massive computational power of a modern graphics accelerator into general-purpose computing power. In certain applications which include vector processing, this can yield several orders of magnitude higher performance than a conventional CPU. In recent times, general purpose computation on graphics processors has been actively explored for several scientific computations [4, 5, 6, 19]. The rapid increase in the number and diversity of scientific communities exploring the computational power of GPUs for their data intensive algorithms has arguably had a contribution in encouraging GPU manufacturers to design GPUs that are easy to program for general purpose applications as well. GPU architectures have been continuously evolving towards higher performance, larger memory sizes, larger memory bandwidths and relatively lower costs. Additionally, the development of open-source programming tools and languages for

interfacing with the GPU platforms, along with the continuous evolution of the computational power of GPUs, has further fueled the growth of general purpose GPU (GPGPU) applications.

A comparison of hardware platforms considered in this dissertation is presented next, in Sections II-D through II-L.

#### II-D. General Overview and Architecture

Fig. II.1. FPGA Layout

Custom designed ICs have no fixed architecture. Depending on the algorithm, technology, target application and skill of the designers, custom ICs can have extremely diverse architectures. This flexibility allows the designer to trade off design parameters such as throughput, latency, power and clock speed. The smaller features also open the door to higher levels of system integration, making the architecture even more diverse.

FPGAs are high density arrays of reconfigurable logic, as shown in Figure II.1 [20]. They allow a designer the ability to trade off hardware resources versus performance, by giving the hardware designers the choice to select the appropriate level of parallelism to

Fig. II.2. Logic Block in the FPGA

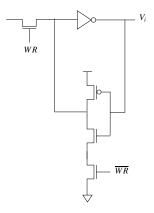

implement an algorithm. The ability to tradeoff parallelism and pipelining yields significant architectural variety. The circuit diagram for a typical FPGA logic block is shown in Figure II.2, and it can implement both combinational as well sequential logic, based on the value of the MUX select signal X. The Look-up Table (LUT) in this FPGA logic block is shown in Figure II.3. It consists of a 16:1 MUX circuit, implemented using NMOS passgates. This is the typical circuit used for implementing LUTs [21, 22]. The circuit for the 16 SRAM configuration bits (labeled as "S" in Figure II.3) is shown in Figure II.4. The DFF of Figure II.2 is implemented using identical master and slave latches, each of which has a NMOS passgate connected to the clock, and a pair of inverters in a feedback configuration to implement the storage element.

In the FPGA paradigm, the hardware consists of a regular array of logic blocks. Wiring between these blocks is achieved by reconfigurable interconnect, which can be programmed via passgates and SRAM configuration bits to drive these passgates (and thereby customize the wiring).

Recent FPGAs provide on-board hardware IP blocks for DSP, hard processor macros, and large amounts of on-chip Block RAM (BRAM). These hardware IP blocks allow a de-

Fig. II.3. LUT Implementation Using a 16:1 MUX

signer to perform many common computations without using FPGA logic blocks or LUTs, resulting in a more efficient design.

One downside of FPGA devices is that they have to be reconfigured every time the system is powered-up. This either requires the use of a special external memory device (which has an associated cost and consumes real estate on the board) or the use of an on-board microprocessor (or some variation on these techniques).

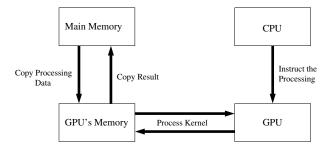

GPUs are commodity parallel devices which provide extremely high memory bandwidths and a large number of programmable cores. They can support thousand of simultaneously issued software threads operating in a SIMD fashion. GPUs have several multiprocessors which execute these software threads. Each multiprocessor has a special function unit, which handles infrequent, expensive operations, like divide, square root etc. There is a high bandwidth, low latency local memory attached to each multiprocessor. The threads executing on that multiprocessor can communicate among themselves using this

Fig. II.4. SRAM Configuration Bit Design

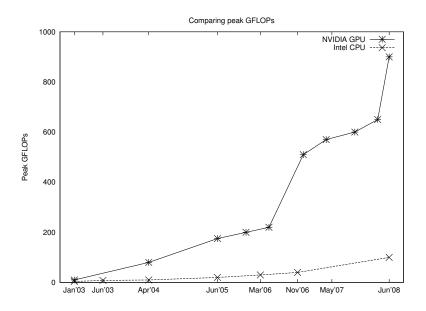

local memory. In the current generation of NVIDIA GPUs, the local memory is quite small (16KB). There is also a large global device memory (over 4GB in some models) of GPU cards. Virtual memory is not implemented, and so paging is not supported. Due to this limitation, all the data has to fit in the global memory. The global device memory has very high bandwidth (but also has high latency) to the multiprocessors. The global device memory is not directly accessible by the host CPU, nor is the host memory directly accessible to the GPU. Data from the host that needs to be processed by the GPU must be transferred via DMA (across an IO bus) from the host to the device memory. Similarly, data is transferred via DMA from the GPU to the CPU memory as well. GPU memory bandwidths have grown from 42 GB/s for the ATI Radeon X1800XT to 141.7 GB/s for the NVIDIA GeForce GTX 280 GPU [6]. A recent comparison of the performance in Gflops of GPUs to CPUs is shown in Figure II.5 [23]. A key drawback of the current GPU architectures (as compared to FPGAs) is that the onchip memory cannot be used to store the intermediate data [24] of a computation. Only off-chip global memory (DRAM) can be used for storing intermediate data. On the FPGA, processed data can be stored in on-chip Block RAM

Fig. II.5. Comparing Gflops of GPUs and CPUs

(BRAM).

# II-E. Programming Model and Environment

Custom designed ICs require several EDA tools in their design process. From functional correctness at the RTL/HDL level to the hardware testing and debugging of the final silicon, EDA tools and simulators are required at every step. For certain steps, a designer has to manually fix the design or interface signals to meet timing or power requirements. Needless to say, for ICs with several million transistors, design and testing can take months before the hardware masks are finalized for fabrication. Unless the design and manufacturing cost can be justified by large volumes or extremely high performance requirements, the custom design approach is typically not practical.

FPGAs are generally customized based on the use of SRAM configuration cells. The

main advantage of this technique is that new design ideas can be implemented and tested much faster compared to a custom IC. Further, evolving standards and protocols can be accommodated relatively easily, since design changes are much simpler to incorporate. On the FPGA, when the system is first powered-up, it can initially be programmed to perform one function such as a self-test and/or board/system test, and it can then be reprogrammed to perform its main task. FPGA vendors provide software and hardware IP cores [25] that implement several common processing functions. More recently, high-end FPGAs have become available that contain one or more embedded microprocessors. Tasks that used to be performed by an external microprocessor, can now be moved into the FPGA core. This provides several advantages such as cost reduction, significantly reduced data transfer times from FPGA to the microprocessor, simplified circuit board design, and a smaller, more power efficient system. Debugging the FPGA is usually performed using embedded logic analyzers at the bitstream level [26]. FPGA debugging, depending on the design density and complexity, can easily take weeks. However, this is still a small fraction of the time taken for similar activities in the custom IC approach. Given these advantages, FPGAs are often used in low and medium volume applications.

In the recent high level languages released for interfacing with GPUs, the hardware details of the graphics processor are abstracted away. High level APIs have made GPU programming very flexible. Existing libraries such as ACML-GPU [27] for AMD GPUs, and CUFFT and CUBLAS [28] for NVIDIA GPUs have inbuilt efficient parallel implementations of commonly used mathematical functions. CUDA [29] from NVIDIA provides guidelines for memory access and the usage of hardware resources for maximal speedup. Brook+ [27] from AMD-ATI provides a lower level API for the programmer to extract higher performance from the hardware. Further, GPU debugging and profiling tools are available for verification and optimization. In comparison to FPGAs or custom ICs, using GPUs as accelerators incurs a significantly lower design turn around time.

General purpose CPU programming has all the advantages of GPGPU programming, and is a mature field. Several programming environments, debugging and profiling tools, and operating systems have been around for decades now. The vast amount of existing code libraries for CPU based applications is an added advantage of system implementation on a general purpose CPU.

# II-F. Scalability

In high performance computing, scalability is an important issue. Combining multiple ICs together for more computing power or using an array of FPGAs for emulation purposes are known techniques to enhance scalability. However, the extra hardware usually requires careful reimplementation of some critical portions of the design. Further, parallel connectivity standards (PCI, PCI-X, EMIF) often fall short when scalability and extensibility are taken into consideration.

Scalability is hard to achieve in general, and should be considered during the architectural and design phases of FPGA based or custom IC based algorithm acceleration efforts. Scalability concerns are very specific to the algorithm being targeted, as well as the acceleration approach employed.

For graphics processors, existing techniques for scaling are intracluster and intercluster scaling. GPU providers such as NVIDIA and AMD provide multi-GPU solutions such as [30] and [31], respectively. These multi-GPU architectures claim high scalability, inspite of limited parallel connectivity, provided the application lends itself well to the architecture. Scalability requires efficient use of hardware as well as communication resources in multi-core architectures, custom ICs, FPGAs and GPUs. Architecting applications for scalability remains a challenging open problem for all platforms.

## II-G. Design Turn-around Time

Custom ICs have a high design turn-around time. Even for modest sized designs, it takes many months from the start of the design to when the silicon is delivered. If design revisions are required, the cost and design turn-around time of custom ICs can become even higher.

FPGAs offer better flexibility and rapid prototyping capabilities as compared to custom designs. An idea or concept can be tested and verified in an FPGA without going through the long and expensive fabrication process of custom design. Further, incremental changes or design revisions (on an FPGA) can be implemented within hours or days instead of months. Commercial off-the-shelf prototyping hardware is readily available, making it easier to rapidly prototype a design. The growing availability of high-level software tools for FPGA design, along with valuable IP cores (prebuilt functions) for several commonly used control and signal processing tasks, makes it possible to achieve rapid design turnarounds.

GPUs and CPUs allow for a far more flexible development environment and faster turn around times. Newer compilers and debuggers help trace software bugs rapidly. Incremental changes or design revisions can be compiled much faster than in custom IC or FPGA designs. Code profiling techniques for optimization purposes is a mature area [32, 29]. Thus, a software implementation can easily be used to rapidly prototype a new design or to modify an existing design.

### II-H. Performance

Depending on the application, custom designed ICs offer speedups of several orders of magnitude as compared the single threaded software performance on the CPU. However, as mentioned earlier, the time taken to design a IC can be prohibitive. FPGAs provide a

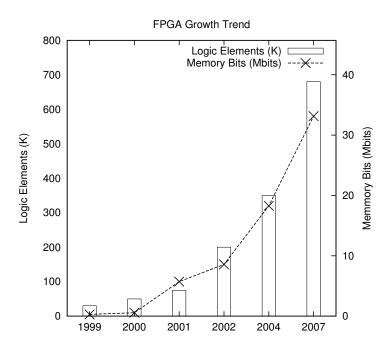

performance that is intermediate between that of custom ICs and single threaded CPUs. Hardware-level parallelism allows some FPGA-based applications to operate 1 to 2 orders of magnitude faster than an equivalent application running on a higher-end workstation. More recently, high performance system designers have begun to explore the capabilities of FPGAs [33]. Advances in FPGA tool flows, and the increasing FPGA speed and density characteristics (shown in Figure II.6) [34] have made FPGAs increasingly popular. Compared to custom designed ICs, FPGA based designs yield lower performance, but the reconfigurable property gives it an edge over custom designs, especially since custom ICs incur significant NRE costs.

Fig. II.6. FPGA Growth Trend

When measured in terms of power efficiency, the advantages of an FPGA-based computing strategy become even more apparent. Calculated as a function of millions of operations (MOPs) per watt, FPGAs have demonstrated greater than  $1,000 \times$  power/performance

advantages over today's most powerful processors [35]. For this reason, FPGA accelerators are now being deployed for a wide variety of power-hungry computing applications.

The power of the GPGPU paradigm stems from the fact that GPUs, with their large memories, large memory bandwidths, and high degrees of parallelism are readily available as off-the-shelf devices, at very inexpensive prices. The theoretical performance of the GPU [6] has grown from 50 Gflops for the NV40 GPU in 2004 to more than 900 Gflops for GTX 280 GPU in 2008. This high computing power mainly arises due to a heavily pipelined and highly parallel architecture, with extremely high memory bandwidths. GPU memory bandwidths have grown from 42 GB/s for the ATI Radeon X1800XT to 141.7 GB/s for the NVIDIA GeForce GTX 280 GPU. In contrast, the theoretical performance of a 3 GHz Pentium4 CPU is 12 Gflops, with a memory bandwidth of 8-10 GB/s to main memory. The GPU IC is arguably one of the few VLSI platforms which has faithfully kept up with Moore's law in recent times. Recent CPU cores have 2-4 GHz core clocks, with single and multi-threaded performance capabilities. The Intel QuickPath Interconnect (4.8 GT/s version) copy bandwidth (using triple-channel 1066 MHz DDR3) is 12.0 GB/s [36]. A 3.0 GHz Core 2 Quad system using dual-channel 1066 MHz DDR3 achieves 6.9 GB/s. The level 2 and 3 caches have 10-40 cycle latencies. CPU cores today also support a limited amount of SIMD parallelism, with SEE [37] instructions.

Another key difference between GPUs and more general purpose multi-core processors is hardware support for parallelism. GPUs have a hardware thread control unit that manages the distribution and assignment of thread blocks to multiprocessors. There is additional hardware support for synchronization within a thread block. Multi-core processors, on the other hand, depend on software and the OS to perform these tasks. However the amount of power consumed by GPUs for executing only the accelerated portion of the computation is typically more than twice than needed by the CPU with all its peripherals. It can be argued that, since the execution is sped up, the power delay product (PDP) of a

GPU based implementation would potentially be lower. However, such a comparison is application dependent, and thus cannot be generalized.

## II-I. Cost of Hardware

The nonrecurring engineering (NRE) expense associated with custom IC design far exceeds that of FPGA-based hardware solutions. The large investment in custom IC development is easy to justify if the anticipated shipping volumes are large. However many designers need custom hardware functionality for systems with low-to-medium shipping volumes. The very nature of programmable silicon eliminates the cost for fabrication and long lead times for chip assembly. Further, if system requirements change over time, the cost of making incremental changes to FPGA designs are negligible when compared to the large expense of redesigning custom ICs. The reconfigurability feature of FPGAs can add to the cost saving, based on the application. GPU's are the least expensive hardware platform for the performance they can deliver. Also, the cost of the software tool-chain required for programming GPUs is negligible compared to the EDA tool costs incurred by custom design and FPGAs.

#### II-J. Floating Point Operations

In comparison to software based implementations, a higher numerical precision is a bigger problem for FPGAs and custom ICs. In FPGAs, for instance, onchip programmable logic resources are utilized to implement floating point functionality for higher precisions [38]. These implementations consume significant die-area and tend to require deep pipelining before acceptable performance can be obtained. For example, hardware implementations of double precision multipliers typically require around 20 pipeline stages, and the square root operation requires 30-40 stages [39].

GPUs targeting scientific computations can handle IEEE double precision floating point [40, 41] while providing peak performance as high as 900 GFlops. GPUs, unlike FPGAs and custom ICs, provide native support for floating point operations.

## II-K. Security and Real Time Applications

In industry practice, design details (including HDL code) are typically documented to make reuse more convenient. At the same time, this makes IP piracy and infringement easier. It is estimated that the annual revenue loss due to IP infringement in the IC industry is in excess of \$5 billion [42]. The goals of IP protection include: enabling IP providers to protect their IPs against unauthorized use, protecting all types of design data used to produce and deliver IPs, and detecting and tracing the use of IPs [42].

FPGAs, because of their re-programmability, are becoming very popular for creating and exchanging VLSI IPs in the reuse-based design paradigm [43]. Existing watermarking and fingerprinting techniques embed identification information into FPGA designs to deter IP infringement. However, such methods incur timing and/or resource overheads, and cause performance degradation. Custom ICs offer much better protection for intellectual property [44].

CPU/GPU software IPs have higher IP protection risks. The emerging trend is that most IP exchange and reuse will be in the form of soft IPs because of the design flexibility they provide. The IP provider may also prefer to release soft IPs, and leave the customer-dependent optimization process to the users [43]. From a security point of view, protecting soft IPs is a much more challenging task than protecting hard IPs. Soft IPs are hard to trace and therefore not preferred in highly secure application scenarios.

Compared to a CPU/GPU based implementation, FPGA and custom IC designs are truly *hard* implementations. Software-based systems like CPUs and GPUs, on the other

hand, often involve several layers of abstraction to schedule tasks and share resources among multiple processors or software threads. The driver layer controls hardware resources and the operating system manages memory and processor utilization. For a given processor core, only one instruction can execute at a time, and hence processor-based systems continually run the risk of time-critical tasks pre-empting one another. FPGAs and custom ICs, which do not use operating systems, minimize these concerns with true parallel execution and dedicated hardware. As a consequence, FPGA and custom IC implementations are more suitable for applications that demand hard real-time computation guarantees.

# II-L. Applications

Custom ICs are a good match for space, military and medical compute intensive applications, where the footprint and weight constraints are tight. Due to their high performance, several DSP based applications make use of custom designed ICs. A custom IC designer can create highly efficient special functions such as arithmetic units, multi-port memories, and a variety of non-volatile storage units. Due to their cost and high performance, custom IC implementations are best suited for high-volume and high-performance applications.

Applications for FPGA are primarily hybrid software/hardware embedded applications including DSP, video processing, robotics, radar processing, secure communications, and many others. These applications are often instances of implementing new and evolving standards, where the cost of designing custom ICs cannot be justified. Further, the performance obtained from high-end FPGAs are reasonable. In general, FPGA solutions are used for low-to-medium volume applications that do not demand extreme high performance.

GPUs are an upcoming field, but have already been used for accelerating scientific computations in fluid mechanics, image processing and financial applications among other areas. The number of commercial products using GPUs are currently limited, but this might

change due to newer architectures and high level languages that make it easy to program the powerful hardware.

# II-M. Chapter Summary

In recent times, due to the power, memory and ILP walls, single threaded applications do not see any significant gains in performance. Existing hardware based accelerators such as custom designed ICs, reconfigurable hardware such as FPGAs, and streaming processors such as GPUs, are being heavily investigated as potential solutions. In this chapter we discussed these hardware platforms and pointed out several key differences among them.

In the next chapter we discuss the CUDA programming environment, used for interfacing with the GPUs. We describe the hardware, memory and programming models for the GPU devices used in this dissertation. This discussion is intended to serve as background material for the reader, to ease the explanation of the details of the GPU based implementations of several EDA algorithms described in this dissertation.

#### CHAPTER III

# GPU ARCHITECTURE AND THE CUDA PROGRAMMING MODEL

## III-A. Chapter Overview

In this chapter we discuss the programming environment and model for programming the NVIDIA GeForce 280 GTX GPU, NVIDIA Quadro 5800 FX and NVIDIA GeForce 8800 GTS devices, which are the GPUs used in our implementations. We discuss the hardware model, memory model and the programming model for these devices, in order to provide background for the reader to understand the GPU platform better.