# A CONCURRENCY AND TIME CENTERED FRAMEWORK FOR CERTIFICATION OF AUTONOMOUS SPACE SYSTEMS

A Dissertation

by

## DAMIAN DECHEV

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2009

Major Subject: Computer Science

# A CONCURRENCY AND TIME CENTERED FRAMEWORK FOR CERTIFICATION OF AUTONOMOUS SPACE SYSTEMS

#### A Dissertation

by

# DAMIAN DECHEV

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Committee Members, Bjarne Stroustrup Jaakko Järvi

Rabi N. Mahapatra Raytcho Lazarov

Head of Department,

Valerie E. Taylor

December 2009

Major Subject: Computer Science

# ABSTRACT

A Concurrency and Time Centered Framework for

Certification of Autonomous Space Systems. (December 2009)

Damian Dechev, B.S., University of Indianapolis;

M.S., University of Delaware

Chair of Advisory Committee: Dr. Bjarne Stroustrup

Future space missions, such as Mars Science Laboratory, suggest the engineering of some of the most complex man-rated autonomous software systems. The present process-oriented certification methodologies are becoming prohibitively expensive and do not reach the level of detail of providing guidelines for the development and validation of concurrent software. Time and concurrency are the most critical notions in an autonomous space system. In this work we present the design and implementation of the first *concurrency* and *time* centered framework for product-oriented software certification of autonomous space systems. To achieve fast and reliable concurrent interactions, we define and apply the notion of Semantically Enhanced Containers (SEC). SECs are data structures that are designed to provide the flexibility and usability of the popular ISO C++ STL containers, while at the same time they are hand-crafted to guarantee domain-specific policies, such as conformance to a given concurrency model. The application of nonblocking programming techniques is critical to the implementation of our SEC containers. Lock-free algorithms help avoid the hazards of deadlock, livelock, and priority inversion, and at the same time deliver fast and scalable performance. Practical lock-free algorithms are notoriously difficult to design and implement and pose a number of hard problems such as ABA avoidance, high complexity, portability, and meeting the linearizability correctness requirements. This dissertation presents the design of the first lock-free dynamically resizable array. Our approach offers a set of practical, portable, lock-free, and linearizable STL vector operations and a fast and space efficient implementation when compared to the alternative lock- and STM-based techniques. Currently, the literature does not offer an explicit analysis of the ABA problem, its relation to the most commonly applied nonblocking programming techniques, and the possibilities for its detection and avoidance. Eliminating the hazards of ABA is left to the ingenuity of the software designer. We present a generic and practical solution to the fundamental ABA problem for lock-free descriptor-based designs. To enable our SEC container with the property of validating domain-specific invariants, we present Basic Query, our expression template-based library for statically extracting semantic information from C++ source code. The use of static analysis allows for a far more efficient implementation of our nonblocking containers than would have been otherwise possible when relying on the traditional run-time based techniques. Shared data in a real-time cyber-physical system can often be polymorphic (as is the case with a number of components part of the Mission Data System's Data Management Services). The use of dynamic cast is important in the design of autonomous real-time systems since the operation allows for a direct representation of the management and behavior of polymorphic data. To allow for the application of dynamic cast in mission critical code, we validate and improve a methodology for constant-time dynamic cast that shifts the complexity of the operation to the compiler's static checker. In a case study that demonstrates the applicability of the programming and validation techniques of our certification framework, we show the process of verification and semantic parallelization of the Mission Data System's (MDS) Goal Networks. MDS provides an experimental platform for testing and development of autonomous real-time flight applications.

To my parents, Tsvetanka and Decho, for their endless encouragement and love.

#### ACKNOWLEDGMENTS

I thank my dissertation advisor and mentor, Dr. Bjarne Stroustrup, for always encouraging free and independent creative thinking and promoting the search for practical and efficient engineering solutions. His patience, guidance, fostering of original ideas, resourceful and broad outlook, and respectful and friendly attitude created a unique and inspiring research environment in our research lab. I am grateful to my committee members, Dr. Jaakko Järvi, Dr. Rabi N. Mahapatra, and Dr. Raytcho Lazarov, for their guidance, helpful advice, patience, and service. I would like to thank my good colleague and friend, Peter Pirkelbauer, for being a great friend and good collaborator on a number of interesting research projects. I am thankful to my colleagues and mentors at the Jet Propulsion Laboratory, Dr. William K. Reinholtz, Dr. Nicolas Rouquette, Dr. David Wagner, and Dr. Garard Holzmann, for giving me the exciting chance to collaborate with them on a number of interesting projects, for their welcoming and friendly attitude, and for providing me with the unique perspective on the application of C++ for space missions.

# TABLE OF CONTENTS

| CHAPTER |                                                                                                                  | Page |

|---------|------------------------------------------------------------------------------------------------------------------|------|

| I       | INTRODUCTION                                                                                                     | 1    |

|         | A. Goals                                                                                                         | 2    |

|         | <ol> <li>Semantically Enhanced Containers</li> <li>Verification and Semantic Parallelization of Real-</li> </ol> |      |

|         | Time $C++$ in the Mission Data System Platform                                                                   | 4    |

|         | B. Challenges for Mission Critical Autonomous Software                                                           | 4    |

|         | C. Parallelism and Complexity                                                                                    | 6    |

|         | 1. The Mars Pathfinder Mission                                                                                   | 7    |

|         | D. Overview and Contribution                                                                                     | 8    |

|         | 1. Overview of the Algorithms                                                                                    | 13   |

|         | 2. Overview of the Experiments                                                                                   | 14   |

| II      | BACKGROUND AND PREVIOUS WORK                                                                                     | 16   |

|         | A. Temporal Constraint Networks                                                                                  | 17   |

|         | B. Lock-Free Dynamically Resizable Arrays                                                                        | 19   |

|         | 1. Foundations of Lock-Free Programming                                                                          | 20   |

|         | 2. Practical Lock-Free Programming Techniques                                                                    | 21   |

|         | a. Lock-Free Data Containers                                                                                     | 23   |

|         | 3. Semantics                                                                                                     | 24   |

|         | 4. Design Goals                                                                                                  | 24   |

|         | 5. Implementation Concerns                                                                                       | 25   |

|         | a. Portability                                                                                                   | 25   |

|         | b. Linearizability Requirements                                                                                  | 26   |

|         | c. Interfaces of the Concurrent Operations                                                                       | 28   |

|         | d. The ABA Problem                                                                                               | 29   |

|         | e. Memory Allocation and Management                                                                              | 30   |

| III     | LOCK-FREE VECTOR: DESIGN AND IMPLEMENTATION .                                                                    | 31   |

|         | A. Operations                                                                                                    | 33   |

|         | B. Semantics                                                                                                     | 35   |

|         | C. Memory Management                                                                                             | 39   |

|         | D. The ABA Problem and the Shared Vector                                                                         | 40   |

|         | E. Alternatives                                                                                                  | 40   |

| CHAPTER |                                                                                     | Page                    |

|---------|-------------------------------------------------------------------------------------|-------------------------|

|         | F. Performance Evaluation                                                           | . 41                    |

| IV      | SOFTWARE TRANSACTIONAL MEMORY                                                       | . 50                    |

|         | A. RSTM-based Vector B. Analysis and Results C. Predictive Log Synchronization      | . 52                    |

| V       | SEMANTIC ENHANCEMENT OF THE SYSTEM IMPLE-<br>MENTATION                              | . 60                    |

|         | A. Principles of Model-Based Product-Oriented Certification .  1. Development       | 62                      |

| VI      | SEMANTICALLY ENHANCED CONTAINERS                                                    | . 69                    |

|         | A. Using Static Analysis to Express and Validate Domain-Specific Guarantees         |                         |

| VII     | NONBLOCKING ABA-FREE SYNCHRONIZATION                                                | . 84                    |

|         | <ul> <li>A. Known ABA Detection and Avoidance Techniques, Part</li> <li>I</li></ul> |                         |

|         | II                                                                                  | 92                      |

|         | F. Implementing a $\lambda\delta$ -modifying Operation                              | 98<br>100<br>101<br>101 |

| VIII    | VERIFICATION AND SEMANTIC PARALLELIZATION OF GOAL-DRIVEN AUTONOMOUS SOFTWARE        | . 109                   |

|         | A. The MDS Architecture                                                             | . 114                   |

| CHAPTER  |                                                  | Page |

|----------|--------------------------------------------------|------|

|          | D. Framework Application for Accelerated Testing | 121  |

| IX       | C++ DYNAMIC CAST IN AUTONOMOUS SPACE SYSTEMS     | 129  |

|          | A. Fast Dynamic Casting Algorithm                | 133  |

|          | B. A Co-simulation Framework                     | 135  |

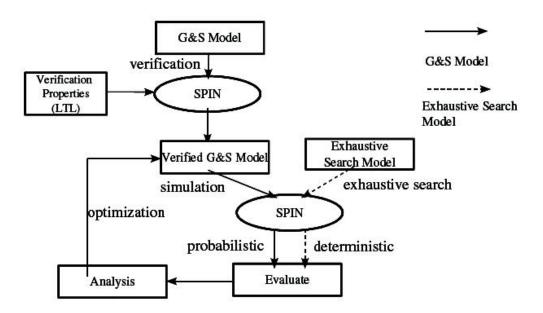

|          | 1. Formal Verification                           | 136  |

|          | 2. Evaluation                                    | 137  |

|          | 3. Analysis                                      | 139  |

|          | C. Application in Mission-Critical Software      | 141  |

|          | D. Results                                       | 142  |

| X        | CONCLUSION                                       | 150  |

| REFERENC | CES                                              | 152  |

| VITA     |                                                  | 164  |

# LIST OF TABLES

| TABLE |                                                                               | Page |

|-------|-------------------------------------------------------------------------------|------|

| 1     | List of Algorithms                                                            | 14   |

| 2     | List of Experiments                                                           | 15   |

| 3     | STL Vector — Number of Memory Locations to be Updated per Operation           | 27   |

| 4     | Interfaces of STL Vector                                                      | 28   |

| 5     | Shared Vector - Operations Description and Complexity                         | 33   |

| 6     | Linearization Points of $o_1, o_2$                                            | 38   |

| 7     | Basic Query Operations                                                        | 76   |

| 8     | Application of the Basic Query Operations                                     | 77   |

| 9     | Result Description of the Basic Query Operations                              | 77   |

| 10    | ABA-free and ABA-prone Interleaving of Two Concurrent Operations              | 79   |

| 11    | ABA at $L_i$                                                                  | 85   |

| 12    | ABA Occurrence in the Execution of a Descriptor Object                        | 96   |

| 13    | A Shared Vector's Operations Cost (Best Case Scenario)                        | 103  |

| 14    | Linking Certification Artifacts, Development Tools, and Levels of Abstraction | 125  |

| 15    | Fast Dynamic Cast, Enumeration of All Solutions                               | 138  |

| 16    | Fast Dynamic Cast, Co-simulation of the Seven Cases                           | 144  |

# LIST OF FIGURES

| FIGURE |                                                                         | Page |

|--------|-------------------------------------------------------------------------|------|

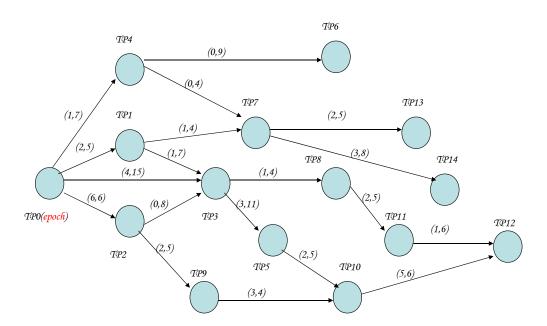

| 1      | An Example of a Temporal Constraint Network: A TCN Topology with 14 TPs | 18   |

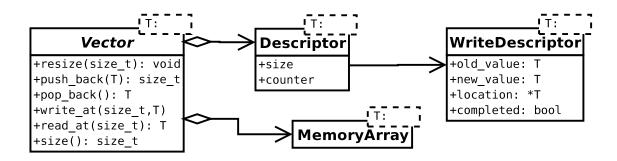

| 2      | Lock-free Shared Vector: UML Class Diagram                              | 32   |

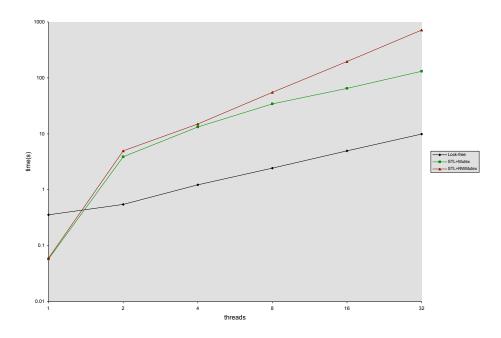

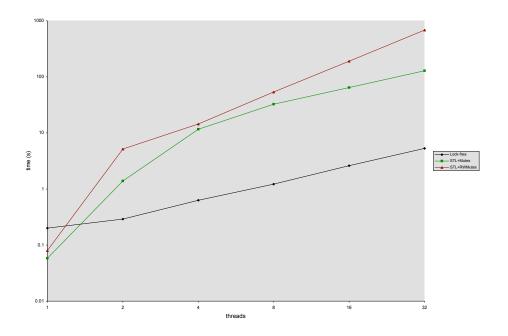

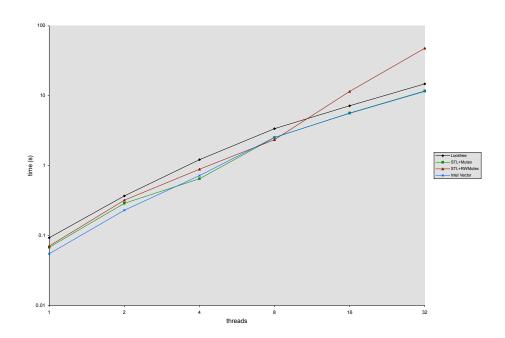

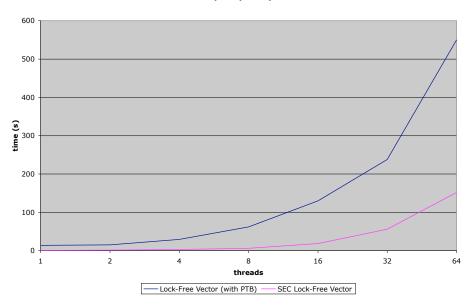

| 3      | Shared Vector Performance Results A - Intel Core Duo                    | 43   |

| 4      | Shared Vector Performance Results B - Intel Core Duo                    | 44   |

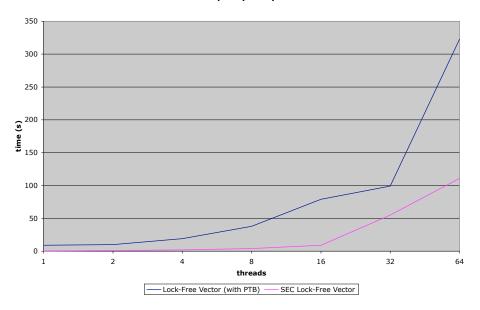

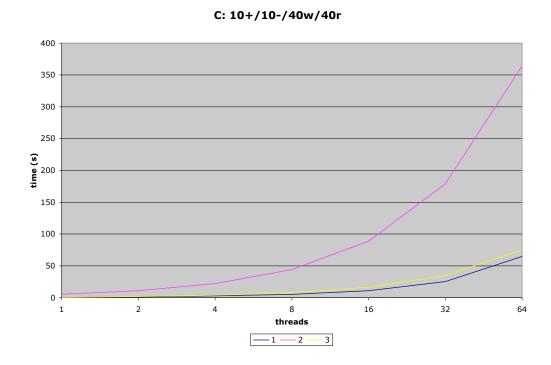

| 5      | Shared Vector Performance Results C - Intel Core Duo                    | 45   |

| 6      | Shared Vector Performance Results D - Intel Core Duo                    | 46   |

| 7      | Shared Vector Performance Results - Alternative Memory Managemen        | t 47 |

| 8      | Shared Vector Performance Results A - AMD 8-way Opteron                 | 48   |

| 9      | Shared Vector Performance Results B - AMD 8-way Opteron                 | 49   |

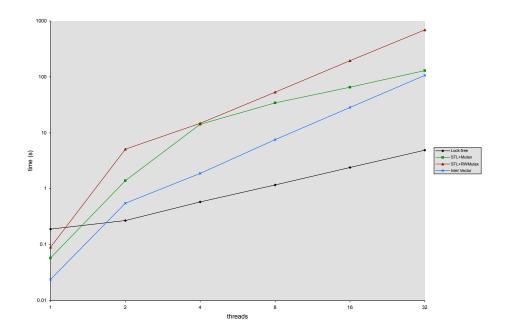

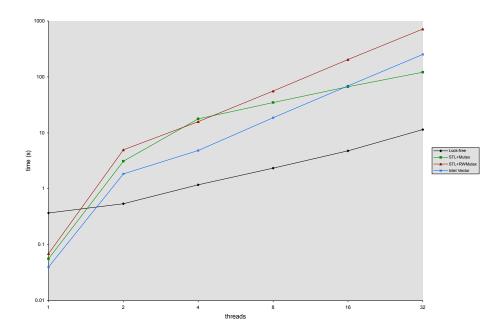

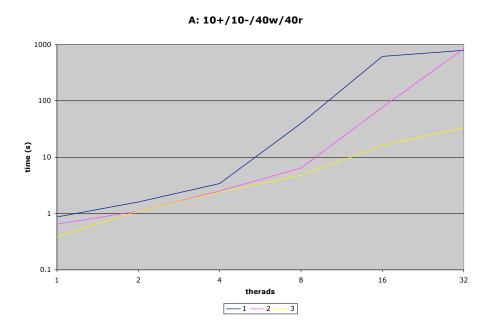

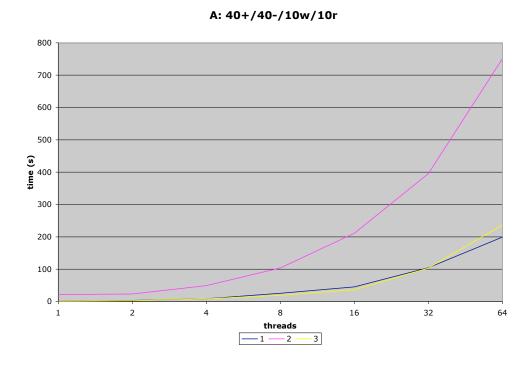

| 10     | STM Performance Results A                                               | 56   |

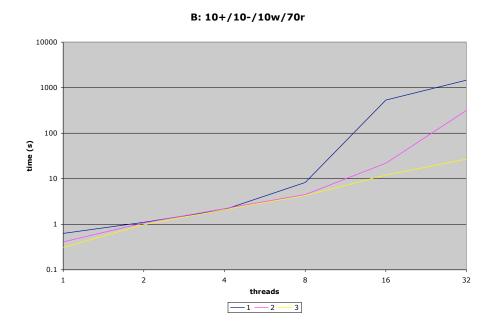

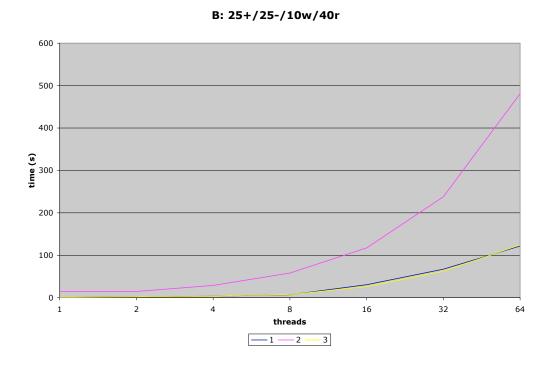

| 11     | STM Performance Results B                                               | 57   |

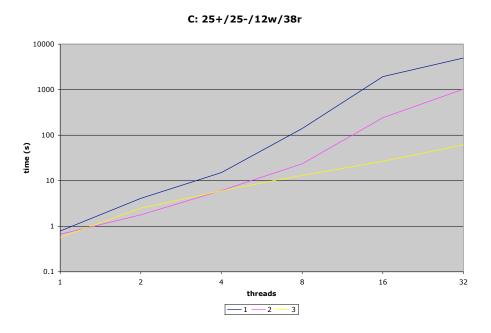

| 12     | STM Performance Results C $\dots$                                       | 58   |

| 13     | An XPR and IPR Representation of a C++ Template Class Definition        | n 72 |

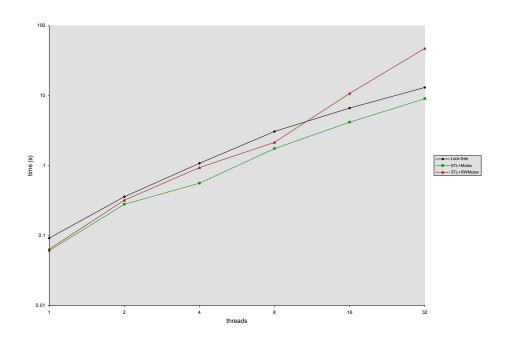

| 14     | SEC Performance Analysis                                                | 83   |

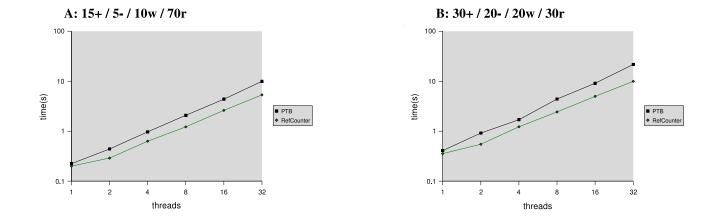

| 15     | ABA-free Synchronization Performance Results A                          | 104  |

| 16     | ABA-free Synchronization Performance Results B                          | 105  |

| 17     | ABA-free Synchronization Performance Results C                          | 106  |

| 18     | ABA-free Synchronization Performance Results D                          | 107  |

| FIGURI | ${f \Sigma}$                                                    | Page |

|--------|-----------------------------------------------------------------|------|

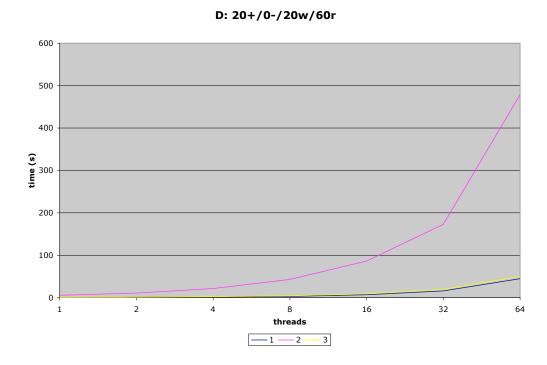

| 19     | A Framework for Verification and Semantic Parallelization       | 110  |

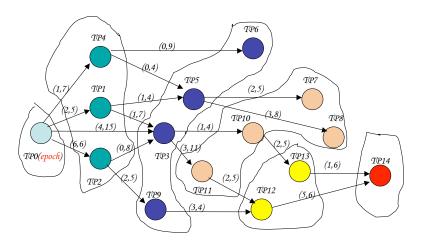

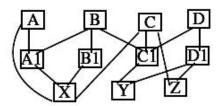

| 20     | A Parallel TCN Topology with 15 Time Points and 6 Time Phases . | 120  |

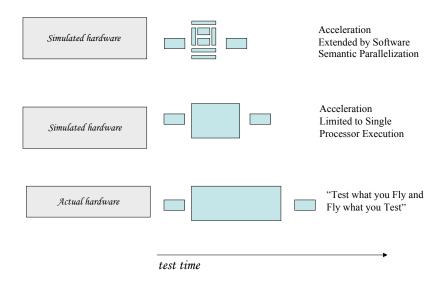

| 21     | Testing Scenarios of Mission Software                           | 123  |

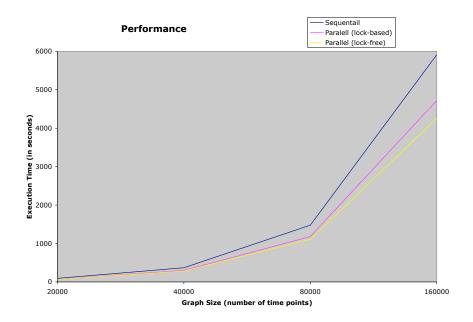

| 22     | TCN Constraint Propagation Performance Analysis                 | 124  |

| 23     | Fast Dynamic Cast, a Class Hierarchy with 11 Classes            | 134  |

| 24     | A Co-Simulation Framework for G&S Improvement and Verification  | 135  |

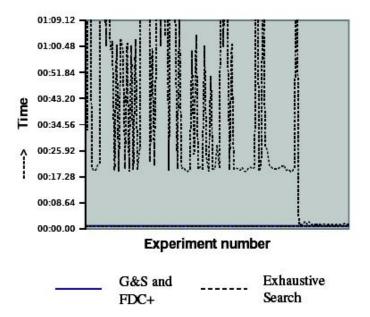

| 25     | Fast Dynamic Cast, Exhaustive Search Computation                | 138  |

| 26     | Fast Dyanmic Cast, Search Time for Type ID Assignment           | 145  |

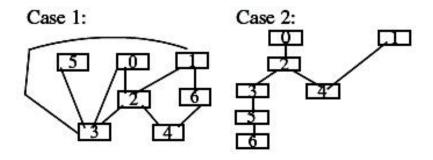

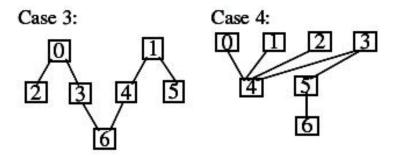

| 27     | Fast Dynamic Cast, Test Cases 1 and 2                           | 146  |

| 28     | Fast Dynamic Cast, Test Cases 3 and 4                           | 146  |

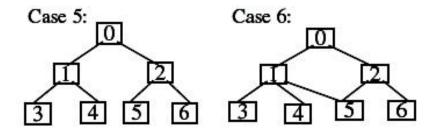

| 29     | Fast Dynamic Cast, Test Cases 5 and 6                           | 147  |

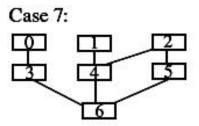

| 30     | Fast Dynamic Cast, Test Case 7                                  | 147  |

#### CHAPTER I

#### INTRODUCTION

In this work we present the design and application of the first concurrency and time centered framework for product-oriented software certification of autonomous space systems. The process of software certification establishes the level of confidence in a software system in the context of its functional and safety requirements. A software certificate contains the evidence required for the system's independent assessment by an authority having minimal knowledge and trust in the technology and tools employed [1]. Providing such certification evidence may require the application of a number of software development, analysis, verification, and validation techniques [2]. The goal of our work is not to provide a grade or a rating of the software development process and the existing software for cyber-physical systems. Instead, we engineer a number of programming and validation techniques that play a critical role for the design and implementation of reliable real-time autonomous software. This dissertation offers the following contributions: the design of the first lock-free dynamically resizable array, detailed analysis and generic solution to the fundamental ABA problem, a comparison study of the available state-of-the-art nonblocking techniques, the application of static analysis to deliver most efficient and reliable nonblocking designs than otherwise would have been possible, improved and verified constant-time dynamic cast operation for polymorphic data, suggests the scope and dimensions of product-oriented certification, a study on the applicability of lock-free designs in mission critical code, the design and implementation of a framework for formal verification and automatic parallelization of control modules for cyber-physical

This dissertation follows the style of IEEE Transactions on Software Engineering.

systems.

#### A. Goals

The goal of this work is to provide the definition, design, and implementation of the first concurrency and time centered framework for product-oriented software certification of autonomous space systems. To achieve fast and reliable concurrent interactions, we define and apply the notion of Semantically Enhanced Containers (SEC). SECs are data structures designed to provide the flexibility and usability of the popular ISO C++ STL containers, while at the same time they are hand-crafted to guarantee domain-specific policies, such as the validity of given semantic invariants or the conformance to a specific concurrency model. In particular, to meet the challenges of engineering mission critical code, we require a SEC to provide the following: a) built-in safe concurrent synchronization, b) use of static analysis for enhanced safety and faster run-time execution, and c) syntactic interface and semantics similar to the widely applied and supported containers of the programming language used for the system implementation. As our experience with MDS demonstrates, shared data can often be polymorphic. To allow for the direct representation of the polymorphic behavior of such data in MDS, we describe and validate an improved constant-time dynamic cast operation. Such an approach achieves safe real-time application and low cost of the operation at the expense of some extra work performed by the compiler's static checker.

#### 1. Semantically Enhanced Containers

To achieve higher safety and faster performance, we define the notion and propose the application of Semantically Enhanced Containers (SEC) for lock-free synchroniza-

tion. As defined by Herlihy [3], a concurrent object is nonblocking if it guarantees that some process in the system will make progress in a finite amount of steps. Nonblocking algorithms do not apply mutually exclusive locks and instead rely on a set of atomic primitives supported by the hardware architecture. The most ubiquitous and versatile data structure in the ISO C++ Standard Template Library [4] is vector, offering a combination of dynamic memory management and constant-time random access. A number of pivotal concurrent applications in the Mission Data System framework employ a shared STL vector protected by mutually exclusive locks, such as the Data Management Service containers [5], the Goal Checker — an application for monitoring the status of goals, and Elf — a framework for message passing and transportation. In this work we present and utilize the design of the first lock-free implementation of a SEC dynamically-resizable array in ISO C++. It provides fast linearizable operations, disjoint-access parallelism for random access reads and writes, lock-free memory allocation and management, and fast execution. To allow the validation of domain-specific concerns in SEC and achieve faster run-time execution, we utilize the Pivot framework for C++ program representation and static analysis [6] and introduce Basic Query (BQ), an expression-template based library for the definition of static queries. While eliminating the hazards associated with the application of locks, nonblocking programming techniques introduce a safety hazard on their own: the ABA problem [7], [8]. Our SEC approach directly addresses the ABA problem and offers a number of practical techniques for its avoidance. In addition, we define a generic condition for ABA safety, called the  $\lambda\delta$  approach, that allows the elimination of the ABA hazard in a time and space efficient manner and with no reliance on complex atomic primitives. In an object-oriented design, the application of dynamic cast provides flexibility in the use of data management facilities. The traditional compiler implementations of dynamic cast do not provide the timing guarantees needed

for hard real-time embedded systems. Because of the dynamic cast's important role in the MDS Data Management Services, we explore the model-based semantic enhancement of the dynamic cast operation that allows for its application in embedded autonomous space systems.

# 2. Verification and Semantic Parallelization of Real-Time C++ in the Mission Data System Platform

We rely on the notion of Semantically Enhanced Containers to design and implement a methodology for verification and semantic parallelization of real-time C++. Our notion of semantic parallelization implies the thread-safe concurrent execution of system algorithms that utilize shared data, based on the application's semantics and invariants. As a practical industrial-scale application, we demonstrate the parallelization and verification of the MDS Temporal Constraint Networks. A Temporal Constraint Network (TCN) defines the goal-oriented operation of a control system. The Temporal Constraint Networks Library is at the core of the Jet Propulsion Laboratory's Mission Data System (MDS) [9] state- and goal-oriented unified architecture for testing and development of mission software. The MDS framework and its associated system engineering processes and development tools have been successfully applied on a number of test platforms including the physical rovers Rocky 7 and Rocky 8 and a simulated Entry, Descent, and Landing (EDL) module for the Mars Science Laboratory mission.

#### B. Challenges for Mission Critical Autonomous Software

The dominant paradigms for software development, assurance, and management of autonomous flight applications rely on the principle "test-what-you-fly and fly-whatyou-test." This methodology has been applied in a large number of robotic space missions at the Jet Propulsion Laboratory. For such missions, it has proven suitable in achieving adherence to some of the most stringent standards of man-rated certification, such as DO-178B [10], the Federal Aviation Administration's (FAA) software standard. Its Level A certification requirements demand 100% coverage of all highand low-level assurance policies. Some future space exploration projects such as Mars Science Laboratory (MSL) [11], Project Constellation [12], and the development of the Crew Launch Vehicle (CLV) and the Crew Exploration Vehicle (CEV) [13] suggest the engineering of some of the most complex man-rated software systems. As stated in the Columbia Accident Investigation Board's Report [14], the inability to thoroughly apply the required certification protocols had been determined to be a contributing factor to the loss of STS-107, Space Shuttle Columbia. Schumann and Visser's discussion in [15] suggests that the current certification methodologies are prohibitively expensive for systems of such complexity. A detailed analysis by Lowry [2] indicates that at the present moment the certification cost of mission-critical space software exceeds its development cost. The challenges of certifying and re-certifying avionics software has led NASA to initiate a number of advanced experimental software development and testing platforms, such as Mission Data System (MDS) [9], as well as a number of program synthesis, modeling, analysis, and verification techniques and tools, such as JavaPathFinder [16], CLARAty project [17], Project Golden Gate [18], and New Millenium Architecture Prototype (NewMAAP) [19]. The high cost and demands of man-rated certification have motivated the experimental development of several accelerated testing platforms [20].

Perrow [21] studies the risk factors in the modern high technology systems. His work identifies two significant sources of complexity in modern systems: *interactions* and *coupling*. The systems most prone to accidents are those with *complex* inter-

actions and tight coupling. With the increase of the size of a system, the number of functions it has to serve, as well as its interdependence with other systems, its interactions become more incomprehensible to human and machine analysis and this can cause unexpected and anomalous behavior. Tight coupling is defined by the presence of time-dependent processes, strict resource constraints, and little or no possible variance in the execution sequence. Perrow classifies space missions in the riskiest category since both hazard factors are present. The notions of concurrency and time are the most critical elements in the design and implementation of an embedded autonomous space system. According to a study on concurrent models of computation for embedded software by Lee and Neuendorffer [22], the major contributing factors to the development and design's complexity of cyber-physical systems are the underlying sequential memory models and the lack of first class representation of the notions of time and concurrency in the applied programming languages.

#### C. Parallelism and Complexity

ISO C++ [23] is widely used for parallel and multi-threaded software, despite the fact that the C++ Standard currently does not mention concurrency or thread-safety. In a parallel application, there are a number of challenges that are not known in sequential programming: most importantly to correctly manipulate data where multiple threads access it. The most commonly applied technique for controlling the interactions of concurrent processes is the application of mutual exclusion locks. A mutual exclusion lock guarantees thread-safety of a concurrent object by blocking all contending threads except the one holding the lock. This can seriously affect the performance of the system and diminish its parallelism. For the majority of applications, the problem with locks is one of difficulty of providing correctness more than one of performance.

The application of mutual exclusion locks poses significant safety hazards (such as livelock, deadlock, priority inversion, and convoying [24]) and incurs high complexity in the testing and validation of mission-critical software. Mutual exclusion locks can be optimized in some scenarios by utilizing fine-grained locks [25] or context-switching. Often due to the resource limitations of flight-qualified hardware, optimized lock mechanisms are not a desirable alternative [2]. Even for efficient locks, the interdependence of processes implied by the use of locks, introduces the dangers of deadlock, livelock, and priority inversion. The incorrect application of locks is hard to detect with the traditional testing procedures and a program can be deployed and used for a long period of time before the flaws trigger anomalous behavior [2].

#### 1. The Mars Pathfinder Mission

As discussed by Lowry [2], in July 1997 The Mars Pathfinder mission experienced a number of anomalous system resets that caused operational delay and loss of scientific data. The follow-up study identified the presence of a priority inversion problem caused by the low-priority meteorological process blocking the high-priority bus management process. The investigation furthermore revealed that it would have been impossible to detect the problem with the black box testing applied at the time to derive the certification artifacts. A safer priority inversion inheritance algorithm had been ignored due to its frequency of execution, the real-time requirements imposed, and its high cost incurred on the slower flight-qualified computer hardware.

The subtle interactions in the concurrent applications of the modern aerospace autonomous systems are of critical importance to the system's safety and correct operation. Despite the challenges in debugging and verification of the system's concurrent components, the existing certification process [10] does not provide guidelines at the level of detail reaching the development, application, and testing of concurrent

programs. This is largely due to the process-oriented nature of the current certification protocols and the complexity and high level of specialization of the aerospace autonomous embedded applications.

In the near future, NASA plans to deploy a number of diverse vehicles, habitats, and supporting facilities for its imminent missions to the Moon, Mars and beyond. The large array of complex tasks that these systems would have to perform implies their high level of autonomy. Rasmussen et al. [9] present the challenges for these systems' control as one of the most demanding tasks facing NASA's Exploration Systems Mission Directorate. Some of the most significant challenges that the authors identify are managing a large number of tightly-coupled components, performing operations in uncertain remote environments, ability to respond and recover from anomalies, guaranteeing the system's correctness and reliability, and the effective communication across the system's components.

#### D. Overview and Contribution

Here, we summarize the contributions of this dissertation and provide an overview of the remaining chapters:

- Chapter II presents in detail the theoretical background and the technical terms that lay at the foundation of this work. The chapter discusses a. the concept and requirements of Temporal Constraint Networks (TCN) and their application in the Mission Data System Platform, b. the foundations of nonblocking synchronization, and c. the challenges in the design and implementation of lock-free containers and in particular a dynamically resizable array.

- In Chapter III we describe our design and implementation of the first lock-free dynamically resizable array. Our approach offers a set of practical, portable,

lock-free, and linearizable STL vector operations and a fast and space efficient implementation that incorporates nonblocking memory management and allocation libraries. The chapter presents nonblocking algorithms defining the following vector's operations: push\_back, pop\_back, reserve, read, write, and size. The chapter further analyzes the concurrent semantics of the operations and the implementation's correctness. Our performance analysis contrasts our lock-free vector implementation with a. the concurrent vector provided by Intel [25] and b. an STL vector protected by a lock. The chapter discusses the following set of experiments:

- 1. performance evaluation on a shared memory system: our experimental data shows that under contention the lock-free vector outperforms the alternative lock-based approaches by a factor of 10 or more,

- 2. evaluation of the vector's performance using two different garbage collection approaches,

- 3. performance evaluation on a system without shared L2 cache: the results demonstrate that in such systems the lock-free approach offers performance comparable to that of the best available lock-based alternatives.

Our performance analysis concludes that the presented implementation is portable, practical, fast, and space-efficient. Using the current implementation, a user has to avoid one particular ABA problem.

• In Chapter IV we study the application of the state-of-the-art nonblocking Software Transactional Memory libraries for the design of nonblocking containers. We demonstrate the use of the Rochester Software Transactional Memory (RSTM) [26] library for the construction of a nonblocking shared vector. Our RSTM-based vector provides algorithms that implement the following basic vector operations: push\_back, pop\_back, read, and write. In our performance analysis we compare: a. the RSTM-based nonblocking vector, b. a variation of the RSTM-based vector using lock-based transactions, and c. our hand-crafted CAS-based design as presented in Chapter III. Our performance evaluation suggests that while hard to design and implement, CAS-based algorithms provide fast and scalable performance and outperform the nonblocking STM-based alternatives by a significant factor.

- In Chapter V we introduce the principles of our product-oriented certification framework founded on the concept of source code enhancement and analysis. The chapter offers a description of our classification of the certification artifact types, the development and validation tools and techniques used to implement a cyber-physical system, the application's domain-specific factors, and the levels of abstraction in the system's design and implementation.

- In Chapter VI we introduce the concept of Semantically Enhanced Containers (SEC). We restrict the notion of a SEC to a container that meets three core criteria: a) built-in safe concurrent synchronization suitable for real-time embedded applications, b) use of static analysis for enhanced safety such as the elimination of the ABA problem, and c) syntactic interface and semantics similar to the widely applied and supported ISO C++ STL containers. In Chapter VI we present a SEC vector engineered to ensure safe and efficient concurrent synchronization as well as offer the mechanisms to establish the validity of certain user-defined semantic guarantees. The chapter discusses our application of static analysis and the Pivot framework [6] that help us achieve more efficient run-time execution of the container's operations (when

compared to the use of dynamic checks and garbage collection). The chapter further explains the design and application of Basic Query (BQ), our expression-template based library for extracting semantic information from C++ source code. BQ defines the programming techniques for specifying and statically checking domain-specific properties in code. We apply BQ to avoid the ABA problem in our lock-free vector implementation from Chapter III. According to our performance analysis the SEC approach offers a cost-efficitive and flexible approach for the prevention of ABA hazards with only mild limitations on the uses of the lock-free vector.

- In Chapter VII we present a generic and practical solution to the ABA problem, called the  $\lambda\delta$  approach, that can easily be adopted in any Descriptor-based lock-free design. Currently the literature does not offer an explicit analysis of the ABA problem, its relation to the most commonly applied nonblocking programming techniques, and the possibilities for its detection and avoidance. At the present moment of time, eliminating the hazards of ABA in a nonblocking algorithm is left to the ingenuity of the software designer. In Chapter VII we study in detail and define the conditions that lead to ABA. We investigate the relationship between the ABA hazards and the most commonly applied nonblocking programming techniques and correctness guarantees. Our performance evaluation establishes that the single word CAS-based  $\lambda\delta$  approach delivers performance comparable to the use of the architecture-specific CAS2 [27] and offers considerable performance gains when compared to the use of garbage collection.

- In Chapter VIII we present the design, implementation, and practical application of our framework for verification and semantic parallelization of real-time C++ within JPL's MDS framework. The nonblocking synchronizations

techniques discussed in Chapters III, VI, and VII play a central role for the realization of our framework. The end goal of the framework is, given the implementation of the optimized iterative propagation scheme and the topology of a particular goal network, to establish the correctness of the core TCN semantic invariants and automatically derive a C++ implementation that can be executed concurrently on one of JPL's experimental testbeds for accelerated testing. We describe the architectural principles of the Mission Data System Platform in the context of our product-oriented certification [28] framework. Furthermore, the chapter presents an optimized algorithm for constraint propagation and proceeds by discussing our approach for modeling, formal verification, and automatic parallelization of the TCN propagation scheme. We show the Alloy formal models and the certification invariants applied. In addition, we use the certification framework introduced in Chapter V to analyze the process of model-based development of the parallel autonomic goals network. We identify seven critical certification artifacts in the process of model-driven development and validation of the MDS goal network. In the analysis of this process, we establish the relationship among the seven certification artifacts, the applied development and validation techniques and tools, and the levels of abstraction of system design and development. The analysis and performance evaluation of our approach show that the use of nonblocking synchronization is of significant importance in achieving reliability, efficiency, and better scalability in our parallel propagation algorithm.

• In Chapter IX we apply the principles of model-based analysis and certification and source code enhancement to the use of the C++ dynamic cast operation in MDS. The application of dynamic cast is considered hazardous for embed-

ded real-time software due to the lack of constant time reply in its standard implementation. However, the dynamic cast allows flexibility in the design and use of data management facilities in object-oriented programs and has an important role in the implementation of the MDS Data Management Services Library. In Chapter IX we define and apply a co-simulation framework based on the SPIN model checker to formally verify and evaluate the G&S fast dynamic casting approach [29], an implementation strategy that guarantees fast constant-time execution of the dynamic cast operation. In the G&S scheme, a heuristic algorithm assigns an integer type ID at link time to each class. Our co-simulation framework consists of a. an abstract formal model of the G&S type ID assignment heuristics and b. a procedure for exhaustive search of the state space discovering the best type ID assignment. The chapter shows the pseudocode of our co-simulation approach and an algorithm for the discovery of a global minimum in the state space of the formal verification process. The analysis of the heuristics simulation performed in SPIN provides us with ideas of possible improvements to the G&S type ID assignment. The application of the co-simulation framework helped us implement optimizations to the G&S heuristics leading to the discovery of optimal type ID assignment in 85% of the class hierarchies, in contrast to 48% for the original G&S algorithm.

• Chapter X concludes this dissertation and provides directions for future research.

# 1. Overview of the Algorithms

Table 1 shows a list of the algorithms presented in this dissertation.

Table 1. List of Algorithms

| Component                           | Operation                                           | Chapter      |

|-------------------------------------|-----------------------------------------------------|--------------|

| Descriptor-based Lock-free Vector   | push_back                                           | Chapter III  |

| Descriptor-based Lock-free Vector   | pop_back                                            | Chapter III  |

| Descriptor-based Lock-free Vector   | Allocate Memory Bucket                              | Chapter III  |

| Descriptor-based Lock-free Vector   | size                                                | Chapter III  |

| Descriptor-based Lock-free Vector   | read                                                | Chapter III  |

| Descriptor-based Lock-free Vector   | write                                               | Chapter III  |

| Descriptor-based Lock-free Vector   | reserve                                             | Chapter III  |

| Descriptor-based Lock-free Vector   | Complete Write                                      | Chapter III  |

| RSTM-based Vector                   | read                                                | Chapter IV   |

| RSTM-based Vector                   | write                                               | Chapter IV   |

| RSTM-based Vector                   | pop_back                                            | Chapter IV   |

| RSTM-based Vector                   | push_back                                           | Chapter IV   |

| Semantically Enhanced Containers    | exclude push_back                                   | Chapter VI   |

| ABA-free Sync.                      | CAS-based speculation at $L_i$                      | Chapter VII  |

| ABA-free Sync.                      | Two-step execution of a $\delta$ object             | Chapter VII  |

| ABA-free Sync.                      | Descriptor Object with obstruction-free semantics   | Chapter VII  |

| ABA-free Sync.                      | Implementing a $\lambda\delta$ -modifying operation | Chapter VII  |

| Automatic Parallelization Framework | TCN Propagation, Forward Pass                       | Chapter VIII |

| Automatic Parallelization Framework | TCN Propagation, Backward Pass                      | Chapter VIII |

| Automatic Parallelization Framework | Definition of Temporal Constraint and Time Point    | Chapter VIII |

| Automatic Parallelization Framework | Definition of Time Phase and TP-based TCN           | Chapter VIII |

| Automatic Parallelization Framework | Main TCN invariants                                 | Chapter VIII |

| Automatic Parallelization Framework | Main TP-based TCN invariants                        | Chapter VIII |

| Fast Dynamic Cast                   | Co-simulation execution                             | Chapter IX   |

| Fast Dynamic Cast                   | Finding the global minimum                          | Chapter IX   |

# 2. Overview of the Experiments

Table 2 presents a list of the core experiments executed and described in this dissertation.

${\bf Table\ 2.\ List\ of\ Experiments}$

| Component                       | Experiment                                      | Chapter                        |

|---------------------------------|-------------------------------------------------|--------------------------------|

| Descriptor-based Vector         | Comp. w/ Lock-based Vector, Intel Core Duo      | Ch. III, Figures 3, 4, 5, 6    |

| Descriptor-based Vector         | Comp. w/ Lock-based Vectorss, AMD 8-way Opteron | Ch. III, Figures 8, 9          |

| Descriptor-based Vector         | Comp. of Alternative Memory Management          | Ch. III, Figure 7              |

| RSTM-based Vector               | Comp. w/ CAS-based vector                       | Ch. IV, Figures 10, 11, 12     |

| SEC (Sem. Enh. Cont.)           | SEC Performance Analysis                        | Ch. VI, Figure 14              |

| ABA-free Sync.                  | Comp. w/ CAS2 and All-GC                        | Ch. VI, Figures 15, 16, 17, 18 |

| Automatic Parallelization Frmk. | TCN Constraint Propagation                      | Ch. VIII, Figure 22            |

| Fast Dynamic Cast               | Co-simulation of the Seven Cases                | Ch. IX, Table 16               |

| Fast Dynamic Cast               | Search Time for Type ID Assignment              | Ch. IX, Figure 26              |

#### CHAPTER II

#### BACKGROUND AND PREVIOUS WORK

As opposed to process-oriented certification, the product-oriented methodology [1] relies on the application of safety concerns directly on implementation source code. The product-oriented approach is inherently more flexible by offering the developers the freedom to follow a variety of software development life-cycle paradigms. In addition, the certification authority itself has the ability to collect all required artifacts for the system's safety and quality assurance. Product-oriented certification has been approached by the application of a variety of formal verification [30], modeling ([31] and [32]), code synthesis [33], and static analysis techniques [34]. An example of a program synthesis technique is AutoFilter [35] that has been developed for the automatic generation of the safety-critical parts of flight software that estimates the position and altitude of the spacecraft. Since the correctness of the generated code is directly dependent on the correctness of the program synthesis tool, FAA regulates that such synthesis tools must meet the same certification criteria as the mission-critial software being generated. The significant implementation effort and the sophisticated design of such tools incur a prohibitive cost to the certification process in this approach. As demonstrated by Denney and Fisher's work [36], rewrite-based simplifications and other program transformations are often necessary in order to reduce the verification state space. In such methodologies, it is the developers' responsibility to certify and establish the fidelity of the formal models with respect to the source as well as the semantic derivation in the applied program transformations.

The rest of this chapter presents the background knowledge accumulated and needed to derive and apply the principles of our time and concurrency framework for product-oriented software certification.

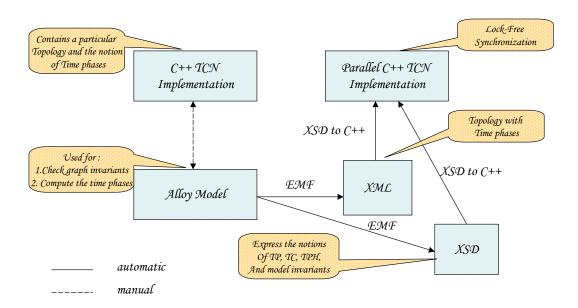

## A. Temporal Constraint Networks

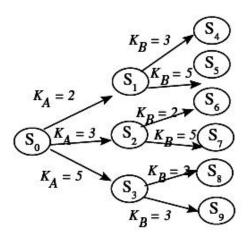

A Temporal Constraint Network (TCN) defines the goal-oriented operation of a control system. The TCN library is at the core of the Jet Propulsion Laboratory's Mission Data System (MDS) [9] state-based and goal-oriented unified architecture for testing and development of mission software. A TCN consists of a set of temporal constraints (TCs) and a set of time points (TPs). In this model of goal-driven operation, a time point is defined as an interval of time when the configuration of the system is expected to satisfy a property predicate. The width of the interval corresponds to the temporal uncertainty inherent in the satisfaction of the predicate. Similarly, temporal constraints have an associated interval of time corresponding to the acceptable bounds on the interactions between the control system and the system under control during the performance of a specific activity. A TCN graph topology represents a snapshot at a given time of the known set of activities the control system has performed so far, is currently engaged in, and will be performing in the near future up to the horizon of the elaborate plan initially created as a solution for a set of goals. Figure 1 illustrates an example of a TCN topology with 14 time points. The topology of a temporal constraint network must satisfy a number of invariants.

- (a) A TCN is a directed acyclic graph where the vertices represent the set of all time points  $(S_{tps})$  and the edges the set of all temporal constraints  $(S_{tcs})$ .

- (b) For each time point  $TP_i \in S_{tps}$ , there is a set of temporal constraints that are immediate successors  $(S_{succ_i})$  of  $TP_i$  and a set,  $S_{pred_i}$ , consisting of all of  $TP_i$ 's immediate predecessors.

- (c) Each temporal constraint  $TC_j \in S_{tcs}$  has exactly one successor  $TP_{succ_j}$  and one predecessor  $TP_{pred_i}$ .

- (d) For each pair  $\{TP_i, TC_j\}$ , where  $TP_i \equiv TC_{succ_j}$ ,  $TC_j \in S_{pred_i}$  must hold. The reciprocal invariant must also be valid, namely for each pair of  $\{TP_i, TC_j\}$  such that  $TP_i \equiv TC_{pred_j}$ ,  $TC_j \in S_{succ_i}$ .

- (e) The firing window of a time point  $TP_i \in S_{tps}$  is represented by the pair of time instances  $\{TP_{min_i}, TP_{max_i}\}$ . Assuming that the current moment of time is represented by  $T_{now}$ , then  $TP_{min_i} \leq T_{now} \leq TP_{max_i}$ , for every  $TP_i \in S_{tps}$ .

Fig. 1. An Example of a Temporal Constraint Network: A TCN Topology with 14 TPs

General-purpose programming languages lack the capabilities to formally specify and check domain-specific design constraints. Direct representation and verification of the TCN invariants in the implementation source code would likely result in a cumbersome and inefficient solution. However, any implementation (in C++, Java, or another programming language) must operate under the assumption that the basic TCN invariants are satisfied. Thus, prior to implementing a solution to the TCN constraint propagation problem, it is necessary to guarantee the correctness and consistency of the topology of the goal network. We further discuss these issues as well as demonstrate an approach for automatic semantic parallelization for accelerated testing of the TCN propagation approach in Chapter VIII.

# B. Lock-Free Dynamically Resizable Arrays

In this section we examine the following topics:

- (1) Briefly introduce the foundations of lock-free programming.

- (2) Examine in details the challenges for the design and implementation of a concurrent dynamic array.

- (a) Discuss the possible consistency models and the assumed concurrent semantics.

- (b) Identify the most desirable characteristics of a nonblocking array, given the assumed semantics.

- (c) Analyze implementation issues related to:

- (-) ensuring portability,

- (-) meeting the requirements for linearizability,

- (-) coping with the ABA problem,

- (-) effectively incorporating nonblocking memory management techniques.

- (3) Present a study of three state-of-the-art approaches for a nonblocking design of a concurrent dynamic array.

- (a) The hand-crafted approach: lock-free dynamically resizable arrays (as further discussed in Chapter III).

- (b) The Software Transactional Memory (STM) approach: the design based on the utilization of an STM library (Chapter IV).

- (c) Predictive Log Synchronization: a recent concept suggested by Shalev and Shavit [37].

# 1. Foundations of Lock-Free Programming

A concurrent object is nonblocking [8] if it guarantees that some process in the system will make progress in a finite number of steps. An object that guarantees that each process will make progress in a finite number of steps is defined as wait-free. Obstruction-freedom [38] is an alternative nonblocking condition that guarantees progress if a thread eventually executes in isolation. It is the weakest nonblocking property and obstruction-free objects require the support of a contention manager to prevent livelocking.

The lock-free, wait-free, and obstruction-free algorithms do not apply mutual exclusion locks. Instead, they rely on a set of atomic primitives such as the word-size CAS instruction [27]. Common CAS implementations [27], [8] require three arguments: a memory location, Mem, an old value,  $V_{old}$ , and a new value,  $V_{new}$ . The instruction atomically exchanges the value stored in Mem with  $V_{new}$ , provided that its current value equals  $V_{old}$ . The architecture ensures the atomicity of the operation by applying a fine-grained hardware lock such as a cache or a bus lock (e.g.: IA-32 [27]). The use of a hardware lock does not violate the nonblocking property as defined

by Herlihy [8]. Common locking synchronization methods such as semaphores, mutexes, monitors, and critical sections utilize the same atomic primitives to manipulate a control token. Such applications of the atomic instructions introduce interdependencies of the contending processes. In the most common scenario, lock-free systems utilize CAS in order to implement a speculative manipulation of a shared object. Each contending process speculates by applying a set of writes on a local copy of the shared data and attempts to CAS the shared object with the updated copy (see Chapter III for further details on the application of CAS in nonblocking designs). This speculative execution guarantees that from within a set of contending processes, there is at least one that succeeds within a finite number of steps (thus the system is nonblocking). Linearizability [8] is an important correctness condition for concurrent objects: a concurrent operation is linearizable if it appears to execute instantaneously in a given point of time between the time  $\tau_{\text{inv}}$  of its invocation and the time  $\tau_{\text{end}}$  of its completion. The consistency model implied by the linearizability requirements is stronger than the widely applied Lamport's sequential consistency model [39]. According to Lamport's definition, sequential consistency requires that the results of a concurrent execution are equivalent to the results yielded by some sequential execution (given the fact that the operations performed by each individual processor appear in the sequential history in the order as defined by the program).

## 2. Practical Lock-Free Programming Techniques

The practical implementation of a hand-crafted lock-free container is notoriously difficult: in addition to addressing the hazards of race conditions, the developer must also find a way to incorporate nonblocking memory management and memory allocation schemes. As suggested by the authors in [40], [41], and [24], the use of only a single-word CAS operation makes the task of designing a practical non-trivial con-

current container very difficult and complex. A simpler and more efficient design of a nonblocking data container requires the atomic update of several memory locations. The use of a Double-Compare-And-Swap primitive (DCAS) has been suggest by Detlefs et al. [41], however such complex atomic operations are rarely supported by the hardware architecture.

Harris et al. describe [42] a software implementation of a multiple-compare-and-swap (MCAS) algorithm based on CAS. This software-based MCAS algorithm has been applied by Fraser in the implementation of a number of lock-free containers such as binary search trees and skip lists [43]. The cost of the MCAS operation is expensive requiring 2M+1 CAS instructions. Consequently, the direct application of the MCAS scheme is not an optimal approach for the design of lock-free algorithms. However, the MCAS implementation employs a number of techniques, such as pointer bit marking and the use of Barne's style announcements [44], that are useful for the design of practical lock-free systems. A Barne's style announcement is an object that allows an interrupting thread help an interrupted thread complete. The pointer bit marking technique exploits the last two bits of a pointer value, which are unused in a pointer representation, to store up to three additional binary states. Thus, a single CAS operation can atomically exchange the pointer and its state.

A number of advanced and recent Software Transactional Memory (STM) Libraries provide nonblocking transactions (typically obstruction-free) with linearizable operations [45]. Such transactions can be utilized for some designs of nonblocking containers. The high cost of the conflict detection and validation schemes in such systems would often not allow performance that is superior to that of a hand-crafted lock-free container which relies solely on the application of the portable atomic primitives. In addition, to prevent livelocking in an obstruction-free design, the implementor needs to apply a contention manager [38].

Predictive Log Synchronization (PLS) is an alternative paradigm suggested by Shalev and Shavit [37] that allows for simpler designs and less costly conflict detection and validation schemes. The core idea is to delegate all writes to a single thread that performs the data structure's modifications based on a log file protected by a single mutual exclusion lock. The design is nonblocking because once a thread finds the lock unavailable, it runs a speculative execution based on the description of the concurrent operations available in the log file. The presented approach is very recent and its implementation is still unavailable. PLS has been published simply as a proof-of-concept and thus has not been applied and extensively tested in the design of complex concurrent algorithms. The main drawbacks for its practical application are the weaker consistency model that it provides (Lamport's sequential consistency), its inefficiency in the scenario of an application performing a larger volume of concurrent writes, and the unbounded growth in the cost of its speculative routine in certain scenarios.

#### a. Lock-Free Data Containers

Recent research in the design of lock-free data structures includes linked-lists ([46] and [47]), double-ended queues ([48] and [49]), stacks [50], hash tables ([47] and [51]), and binary search trees [43]. The problems encountered include excessive copying, low parallelism, inefficiency, and high overhead. Despite the widespread use of the STL vector in real-world applications, we are aware of only one published work [7] that discusses the problem of the design and implementation of a lock-free dynamic array. The vector's random access, data locality, and dynamic memory management poses serious challenges for its nonblocking implementation.

#### 3. Semantics

The semantics of a concurrent data container can be based on a number of assumptions. For the designs we study in this report, we assume that each processor can execute a number of the vector's operations. This establishes a history of invocations and responses and defines a real-time order between them. An operation  $O_1$  is said to precede an operation  $O_2$  if  $O_2$ 's invocation occurs after  $O_1$ 's response. Operations that do not have real-time ordering are defined as concurrent. A sequential history is one where all invocations have immediate responses. A linearizable history is one where:

- (1) all invocations and responses can be reordered so that they are equivalent to a sequential history,

- (2) the yielded sequential history must correspond to the semantic requirements of the sequential definition of the object,

- (3) in case a given response precedes an invocation in the concurrent execution, then it must precede it in the derived sequential history.

It is the last requirement that differentiates the consistency model implied by the definition of linearizability with Lamport's sequential consistency model and makes linearizability stricter.

### 4. Design Goals

In this section we synthesize the most desirable characteristics of a shared nonblocking container:

(1) thread-safety: the data should be accessible to multiple processors at all times,

- (2) lock-freedom: apply nonblocking techniques for the implementation,

- (3) portability: do not rely on uncommon architecture-specific instructions,

- (4) easy-to-use interfaces: offer the interfaces, functionality, and guarantees available in the sequential STL vector,

- (5) high level of parallelism: concurrent completion of non-conflicting operations should be possible,

- (6) minimal overhead: achieve lock-freedom without excessive copying, levels of indirection, and costly conflict detection and validation schemes, minimize the time spent on redundant and speculative computations and the number of calls to costly atomic primitives.

# 5. Implementation Concerns

We provide a brief summary of the most important implementation concerns for the practical and portable design of a nonblocking dynamic array. The following sections discuss the implementation issues related to guaranteeing portability, meeting the requirements for linearizability, preventing race conditions, coping with the ABA problem, and incorporating nonblocking memory management and allocation schemes.

# a. Portability

Virtually at the core of every known synchronization technique is the application of a number of hardware atomic primitives. The semantics of such primitives varies depending on the specific hardware platform. There are a number of architectures that offer the support of some hardware atomic instructions that provide greater flexibility

(compared to a single-word CAS) such as the Load-Link/Store Conditional (LL/SC) supported by the PowerPC, Alpha, MIPS, and the ARM architectures or instructions that perform atomic writes to more than a single word in memory, such as the Double-Compare-And-Swap (DCAS) instruction [41]. The hardware support for such atomic instructions can vastly simplify the design of a nonblocking algorithm as well as offer immediate solutions to a number of challenging problems such as the ABA problem [52]. However, to maintain portability across a large number of hardware platforms, the design and implementation of a nonblocking algorithm cannot rely on the support of such atomic primitives. The most common atomic primitive that is supported by a large majority of hardware platforms is the single-word Compare-And-Swap (CAS) instruction.

### b. Linearizability Requirements

In a CAS-based design, a major difficulty is meeting the linearizability requirements for operations that require the update of more than a single-word in the system's shared memory. To cope with this problem, it is possible to apply a combination of a number of known techniques:

- (1) Extra Level of Indirection: Reference semantics can be used in case that the data being manipulated is larger than a memory word size.

- (2) Descriptor Object: A Descriptor Object (see Chapter III) stores a record of a pending operation on a given memory location. It allows the interrupting threads help the interrupted thread complete an operation rather than wait for its completion.

- (3) Descriptive Log: The Descriptive Log methodology lies at the core of virtually all Software Transactional Memory implementations. A Descriptive Log stores a

record of all pending reads and writes to the shared data. It is used for conflict detection, validation, and optimistic speculation.

- (4) Transactional Memory: A duplicate memory copy used to perform speculative updates that are invisible to all other threads until the linearization point of the entire transaction.

- (5) Optimistic Speculation: A complex nonblocking operation employs optimistic speculative execution in order to carry out the memory updates on a local or duplicate memory copy and commit once there are no conflicts with interfering operations.

To illustrate the complexity of a CAS-based design of a dynamically resizable array, Table 3 provides an overview of the number of shared memory locations that need to be updated upon the execution of some of its basic operations.

Table 3. STL Vector — Number of Memory Locations to be Updated per Operation

|           | Operations                                             | Memory Locations    |

|-----------|--------------------------------------------------------|---------------------|

| push_back | $Vector \times Elem \rightarrow void$                  | 2: element and size |

| pop_back  | $Vector \rightarrow Elem$                              | 1: size             |

| reserve   | $Vector \times size\_t \rightarrow Vector$             | n: all elements     |

| read      | $Vector \times size\_t \rightarrow Elem$               | none                |

| write     | $Vector \times size\_t \times Elem \rightarrow Vector$ | 1: element          |

| size      | $Vector \rightarrow size\_t$                           | none                |

# c. Interfaces of the Concurrent Operations

According to the ISO C++ Standard [23], the STL containers' interfaces are inherently sequential. The next ISO C++ Standard [53] is going to include a concurrent memory model [54] and possibly a blocking threading library. In Table 4 we show a brief overview of some of the basic operations of an STL vector according to the current standard of the C++ programming language. Consider the sequence of opera-

Table 4. Interfaces of STL Vector

| Operation                                | Description                            |  |

|------------------------------------------|----------------------------------------|--|

| size_type size() const                   | Number of elements in the vector       |  |

| size_type capacity() const               | Number of available memory slots       |  |

| void reserve( $size\_type\ n$ )          | Allocation of memory with capacity $n$ |  |

| bool empty() const                       | true when size $= 0$                   |  |

| $T^*$ operator[] $(size\_type\ n)$ const | returns the element at position $n$    |  |

| T* front()                               | returns the first element              |  |

| T* back()                                | returns the last element               |  |

| void push_back(const T&)                 | inserts a new element at the tail      |  |

| void pop_back()                          | removes the element at the tail        |  |

| void resize(n, $t = T()$ )               | modifies the tail, making size $= n$   |  |

tions applied to an instance, vec, of the STL vector: vec[vec.size()-1]; vec.pop\_back();. In an environment with concurrent operations, we cannot have the guarantee that the element being deleted by thepop\_back is going to be the element that had been read earlier by the invocation of operator[]. Such a sequential history is just one of the several legal sequential histories that can be derived from the concurrent execution of the above operations. While the STL interfaces have proven to be efficient and flexible for a large number of applications [4], to preserve the semantic behavior implied by the sequential definitions of STL, one can either rely on a library with atomic transactions [45], [26] or alternatively define concurrent STL interfaces adequate with respect to the applied consistency model. In the example we have shown, it might be appropriate to modify the interface of the pop\_back operation and return the element being deleted instead of the void return type specified in STL. Such an implementa-

tion efficiently combines two operations: reading the element to be removed from the container and removing the element. The ISO C++ implementation of  $pop\_back()$  returns void so that the operation is optimal (and does not perform extra work) in the most general case: the deletion of the tail element. Should we prefer to keep the STL standard interface of void  $pop\_back()$  in a concurrent implementation, the task of obtaining the value of the removed element in a concurrent nonblocking execution might be quite costly and difficult to implement. Based on the shared containers' usage, observing the possibilities for such combinations can deliver better usability and performance advantages in a nonblocking implementation. Other possibly beneficial combinations of operations are 1) CAS-based read-modify-write at location  $L_i$  that unifies a random access read and write at location  $L_i$  and 2) the  $push\_back$  of a block of tail elements.

### d. The ABA Problem

The ABA problem [52] is fundamental to all CAS-based systems. A universal solution to the ABA problem is to associate a version counter to each element on platforms supporting Double-Compare-And-Swap or alternatively provide Load-Link/Store-Conditional (LL/SC) semantics. We cannot assume availability of these atomic primitives since they are specific to a limited number of hardware platforms.

There are two particular instances when the ABA problem can affect the correctness of the vector's operations:

- (1) The user intends to store a memory address value A multiple times.

- (2) The memory allocator reuses the address of an already freed object.

To eliminate the ABA problem of (2) (in the absence of CAS2 [27] or LL/SC), it is possible to incorporate a memory management scheme such as Herlihy et al.'s Pass The Buck algorithm [55] that utilizes a separate thread to periodically reclaim

unguarded objects. The vector's vulnerability to (1) (in the absence of CAS2 or LL/SC), can be eliminated by requiring the data structure to copy all elements and store pointers to them. Such behavior complies with the STL value-semantics [4], however it can incur significant overhead in some cases due to the additional heap allocation and object construction. In a lock-free system, both the object construction and heap allocation can execute concurrently with other operations.

### e. Memory Allocation and Management

A nonblocking algorithm needs to be able to acquire and safely release memory in an efficient, nonblocking manner. A garbage collected environment could significantly reduce the complexity of the implementation (by moving key implementation problems inside the GC implementation). However, we do not know of any available general lock-free garbage collector for C++ or Java.

Object Reclamation: it is possible to incorporate a reference counting technique as described by Michael and Scott [56]. The major drawback of such a scheme is that a timing window allows objects to be reclaimed while a different thread is about to increase the counter. Consequently, objects cannot be freed but only recycled. Alternatives such as Michael's Hazard Pointers [52] and Herlihy et al.'s Pass The Buck [55] overcome this problem.

Allocator: recent research by Michael [57] and Gidenstam [58] presents implementations of practical lock-free memory allocators.

# CHAPTER III

### LOCK-FREE VECTOR: DESIGN AND IMPLEMENTATION

In this chapter we provide an overview of our design and implementation of the first lock-free dynamically resizable array. The presented approach is based on a single-word atomic Compare-And-Swap (CAS) instruction. It provides a linearizable and highly parallelizable STL-like interface, lock-free memory allocation and management, and fast execution. Experiments on a dual-core Intel processor with shared L2 cache indicate that our lock-free vector outperforms its lock-based STL counterpart and the latest concurrent vector implementation provided by Intel by a large factor. The performance evaluation on a quad dual-core AMD system with non-shared L2 cache demonstrated timing results comparable to the best available lock-based techniques. The presented design implements the most common STL vector's interfaces, namely random access read and write, tail insertion and deletion, pre-allocation of memory, and query of the container's size. Using the current implementation, a user has to avoid one particular ABA problem. The lock-free vector's design and implementation provided follow the syntax and semantics of the ISO STL vector as defined in ISO C++ [23].

In the following sections we define a semantic model of the vector's operations, provide a description of the design and the applied implementation techniques, outline a correctness proof of the vector's lock-free semantics based on the adopted semantic model, address concerns related to memory management, and discuss some alternative solutions. The presented algorithms have been implemented in ISO C++ and designed for execution on an ordinary multi-threaded shared-memory system supporting only single-word read, write, and CAS instructions.

The major challenges of providing a lock-free vector implementation stem from

the fact that key operations need to atomically modify two or more non-colocated words. For example, the critical vector operation <code>push\_back</code> increases the size of the vector and stores the new element. Moreover, capacity-modifying operations such as <code>reserve</code> and <code>push\_back</code> potentially allocate new storage and relocate all elements in case of a dynamic table [59] implementation. Element relocation must not block concurrent operations (such as <code>write</code> and <code>push\_back</code>) and must guarantee that interfering updates will not compromise data consistency. Therefore, an update operation needs to modify up to four shared memory locations: size, capacity, storage, and a vector's element.

Fig. 2. Lock-free Shared Vector: UML Class Diagram

The UML diagram in Figure 2 presents the collaborating classes and their programming interfaces and data members. Each vector object contains the memory locations of the data storage of its elements as well as an object named Descriptor that encapsulates the container's size, a reference counter required by the applied memory management scheme (Section C) and an optional reference to a Write Descriptor. Our approach requires that data types bigger than word size are indirectly stored through pointers. Like Intel's concurrent vector [25], our implementation avoids storage relocation and its synchronization hazards by utilizing a two-level array. Whenever push\_back exceeds the current capacity, a new memory block twice the size of the

previous one is added.

The semantics of the pop\_back and push\_back operations are guaranteed by the Descriptor object. The use of a Descriptor and Write Descriptor allows a thread-safe update of two memory locations thus eliminating the need for a DCAS instruction. An interrupting thread intending to change the descriptor needs to complete any pending operation. Not counting memory management overhead, push\_back executes two successful CAS instructions to update two memory locations.

### A. Operations

write

size

Table 5 illustrates the implemented operations as well as their signatures, descriptor modifications, and runtime guarantees.

Operations Descriptor (Desc) Complexity  $Vector \times Elem \rightarrow \mathsf{void}$ push\_back  $\mathrm{Desc}_t \to \mathrm{Desc}_{t+1}$  $O(1) \times congestion$ pop\_back  $Vector \rightarrow Elem$  $\mathrm{Desc}_t \to \mathrm{Desc}_{t+1}$  $O(1) \times congestion$  $Vector \times size\_t \rightarrow Vector$ reserve  $\mathrm{Desc}_t \to \mathrm{Desc}_t$ O(1) $Vector \times size\_t \rightarrow Elem$  $\mathrm{Desc}_t \to \mathrm{Desc}_t$ O(1)read

$\mathrm{Desc}_t \to \mathrm{Desc}_t$

$\mathrm{Desc}_t \to \mathrm{Desc}_t$

O(1)

O(1)

Table 5. Shared Vector - Operations Description and Complexity

The remaining part of this section presents the generalized pseudo-code of the implementation. It omits code necessary for a particular memory management scheme. We use the symbols ^, &, and . to indicate pointer dereferencing, obtaining an object's address, and integrated pointer dereferencing and field access respectively. The

$Vector \times size\_t \times Elem \rightarrow Vector$

$Vector \rightarrow size\_t$

function HighestBit returns the bit-number of the highest bit that is set in an integer value. On modern x86 architectures HighestBit corresponds to the BSR assembly instruction [27]. FBS is a constant representing the size of the first bucket and equals eight in our implementation.