# DESIGNING COST-EFFECTIVE COARSE-GRAINED RECONFIGURABLE ARCHITECTURE

A Dissertation

by

YOONJIN KIM

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2009

Major Subject: Computer Engineering

# DESIGNING COST-EFFECTIVE COARSE-GRAINED RECONFIGURABLE ARCHITECTURE

A Dissertation

by

### YOONJIN KIM

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Rabi N. Mahapatra Committee Members, Eun Jung Kim

Duncan Henry M. Walker

Gwan Choi

Head of Department, Valerie E. Taylor

May 2009

Major Subject: Computer Engineering

#### **ABSTRACT**

Designing Cost-Effective Coarse-Grained Reconfigurable Architecture. (May 2009)

Yoonjin Kim, B.S., SungKyunKwan University;

M.S., Seoul National University

Chair of Advisory Committee: Dr. Rabi N. Mahapatra

Application-specific optimization of embedded systems becomes inevitable to satisfy the

market demand for designers to meet tighter constraints on cost, performance and power.

On the other hand, the flexibility of a system is also important to accommodate the short

time-to-market requirements for embedded systems. To compromise these incompatible

demands, coarse-grained reconfigurable architecture (CGRA) has emerged as a suitable

solution. A typical CGRA requires many processing elements (PEs) and a configuration

cache for reconfiguration of its PE array. However, such a structure consumes signifi-

cant area and power. Therefore, designing cost-effective CGRA has been a serious con-

cern for reliability of CGRA-based embedded systems.

As an effort to provide such cost-effective design, the first half of this work

focuses on reducing power in the configuration cache. For power saving in the configu-

ration cache, a low power reconfiguration technique is presented based on reusable con-

text pipelining achieved by merging the concept of context reuse into context pipelining.

In addition, we propose dynamic context compression capable of supporting only re-

quired bits of the context words set to enable and the redundant bits set to disable. Fi-

nally, we provide *dynamic context management* capable of reducing reduce power consumption in configuration cache by controlling a read/write operation of the redundant context words

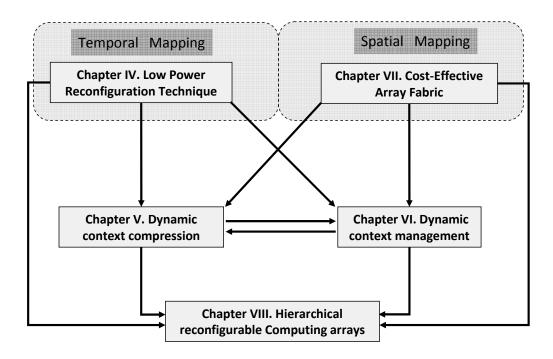

In the second part of this dissertation, we focus on designing a cost-effective PE array to reduce area and power. For area and power saving in a PE array, we devise *a cost-effective array fabric* addresses novel rearrangement of processing elements and their interconnection designs to reduce area and power consumption. In addition, *hierarchical reconfigurable computing arrays* are proposed consisting of two reconfigurable computing blocks with two types of communication structure together. The two computing blocks have shared critical resources and such a sharing structure provides efficient communication interface between them with reducing overall area.

Based on the proposed design approaches, a CGRA combining the multiple design schemes is shown to verify the synergy effect of the integrated approach. Experimental results show that the integrated approach reduces area by 23.07% and power by up to 72% when compared with the conventional CGRA.

## **DEDICATION**

To my family and friends

#### **ACKNOWLEDGEMENTS**

It has been my life-long dream to become a professional in the engineering/science field and to infuse my passion into my research work. For this reason, this acknowledgement is very meaningful for me. The completion a Ph.D. in computer engineering at Texas A&M University has been the best way to accomplish my goals and achieve my dream.

First of all, I am sincerely grateful to my advisor Dr. Rabi N. Mahapatra for allowing me to conduct research with him and for his guidance during my Ph.D. program. His exceptional commitment to research and strong demand for excellence have guided me this far. I am truly grateful to his insightful advice, encouragement, and constant motivation throughout this work. Many thanks also go to my previous advisor, Professor Kiyoung Choi of Seoul National University, for his encouragement and helpful discussions. For two years of my master's course, he taught me to appreciate that a successful graduate student must have an arduous and passionate attitude. I would also like to thank the other members of my dissertation committees: Professors Eun Jung Kim, Duncan Henry M. Walker, and Gwan Choi. Their insightful comments and constructive criticisms helped me improve my research. Without their feedback, this dissertation would not have been made in it present form. In addition, I am deeply grateful to Professor Jundong Cho of SungKyunKwan University for his teaching and advice in my undergraduate days.

Furthermore, I would like to thank my friends and fellow students at Texas A&M University for numerous discussions about various issues related to research and life. I

sincerely thank current and former members of Embedded Systems and Co-design Group for being supportive of me during this work. I thank them all, including Woo-Seok Hong, In-choon Yeo, Baik-Song Ahn, Ja-Ryeong Koo, Sun-Young Choi, Ju-Young Jung, Young-Ah Kim, Moon-Jeong Kang and Young-Ho Koh, for being great friends and always being available whenever I need their assistance and help. Members of the Design Automation Lab in Seoul National University have helped me in various ways during the years of my Ph.D. program. I thank them all, especially Yong-Jin Ahn, Dong-Kwan Suh, Young-Chul Cho, Imyong Lee, Il-Hyun Park, Dong-Wook Lee, and Man-Hwee Jo.

Last, but not least, I am especially grateful to my parents and my elder brother for their incredible support and trust for me. Without their dedication and belief in me, I couldn't have completed this work in due time.

## **TABLE OF CONTENTS**

|                                                                                                         | Page                 |

|---------------------------------------------------------------------------------------------------------|----------------------|

| ABSTRACT                                                                                                | iii                  |

| DEDICATION                                                                                              | v                    |

| ACKNOWLEDGEMENTS                                                                                        | vi                   |

| TABLE OF CONTENTS                                                                                       | viii                 |

| LIST OF FIGURES                                                                                         | xiii                 |

| LIST OF TABLES                                                                                          | xvii                 |

| CHAPTER                                                                                                 |                      |

| I INTRODUCTION                                                                                          | 1                    |

| A. Objective and Approach B. Contributions C. Dissertation Organization                                 | 2<br>3<br>5          |

| II BACKGROUND AND RELATED WORKS                                                                         | 6                    |

| A. Coarse-Grained Reconfigurable Architecture  B. Related Works                                         | 6<br>8               |

| III BASE CGRA IMPLEMENTATION                                                                            | 13                   |

| A. Reconfigurable Array Architecture Coupling with Processor  B. Base Reconfigurable Array Architecture | 13<br>15<br>16<br>16 |

| 3. Frame Buffer  4. Configuration Cache  5. Execution Controller                                        | 18<br>18<br>19       |

| C. Breakdown of Area, Delay, and Power Cost                                                             | 19<br>20<br>23       |

| CHAPTER |                                                                  | Page       |

|---------|------------------------------------------------------------------|------------|

| IV      | LOW POWER RECONFIGURATION TECHNIQUE                              | 25         |

|         | A. Motivation                                                    | 25         |

|         | 1. Loop Pipelining                                               | 25         |

|         | 2. Spatial Mapping and Temporal Mapping                          | 31         |

|         | B. Individual Approaches to Reduce Power in Configuration Cache  | 32         |

|         | 1. Spatial Mapping with Context Reuse                            | 33         |

|         | 2. Temporal Mapping with Context Pipelining                      | 34         |

|         | 3. Limitation of Individual Approaches                           | 35         |

|         | C. Integrated Approach to Reduce Power in Configuration Cache    | 36         |

|         | 1. Reusable Context Pipelining                                   | 47         |

|         | 2. Limitation of Reusable Context Pipelining                     | 41         |

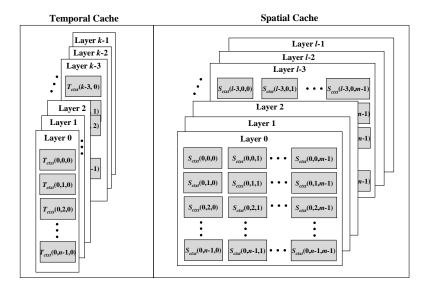

|         | 3. Hybrid Configuration Cache Structure                          | 43         |

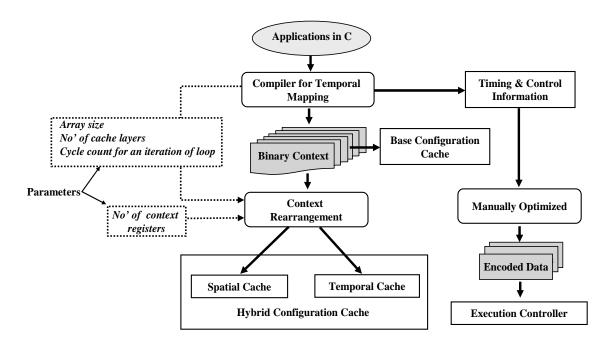

|         | D. Application Mapping Flow                                      | 44         |

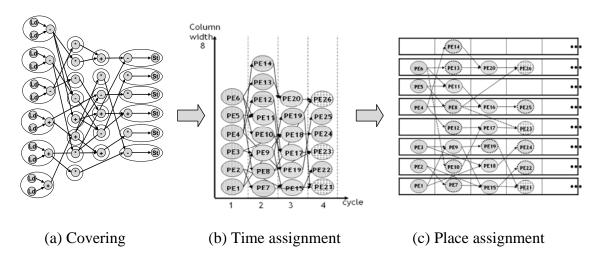

|         | 1. Temporal Mapping Algorithm                                    | 45         |

|         | a. Covering                                                      | 45         |

|         | b. Time Assignment                                               | 46         |

|         | c. Place Assignment                                              | 47         |

|         | 2. Context Rearrangement                                         | 47         |

|         | E. Experiments                                                   | 49         |

|         | 1. Experimental Setup                                            | 49         |

|         | 2. Results                                                       | 50         |

|         | a. Necessary Context Registers for Evaluated Kernels             | 50         |

|         | b. Configuration Cache Size                                      | 52         |

|         | c. Performance Evaluation                                        | 52         |

|         | d. Power Evaluation                                              | 53         |

| V       | DYNAMIC CONTEXT COMPRESSION FOR LOW POWER                        | <i>E E</i> |

|         | CGRA                                                             | 55         |

|         | A. Preliminary                                                   | 55         |

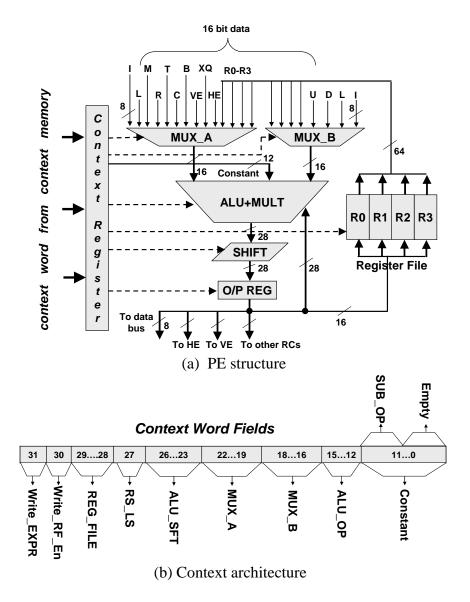

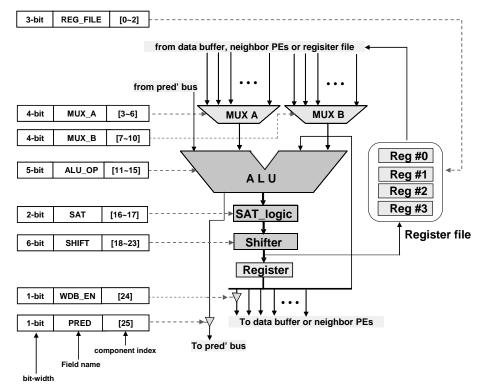

|         | 1. Context Architecture                                          | 55         |

|         | B. Motivation                                                    | 57         |

|         | 1. Power Consumption by Configuration Cache                      | 57         |

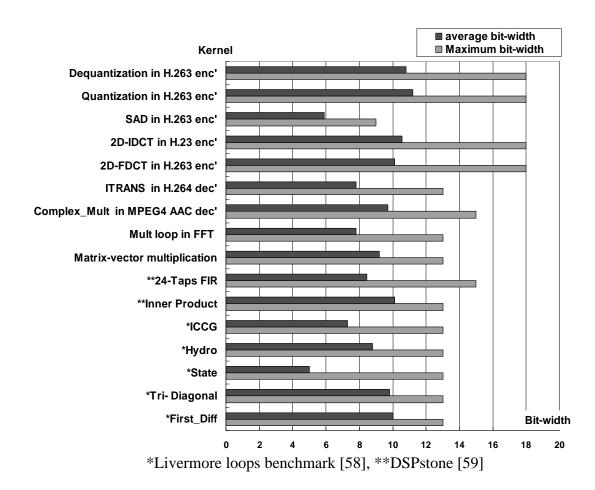

|         | 2. Valid Bit-Width of Context Words                              | 57         |

|         | 3. Dynamic Context Compression for Low Power CGRA                | 59         |

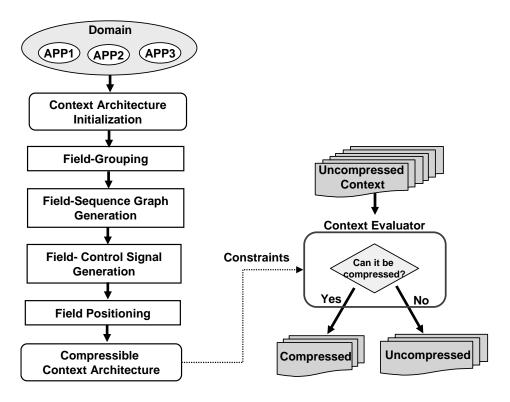

|         | C. Design Flow of Dynamically Compressible Context Architecture. | 59         |

|         | 1. Context Architecture Initialization                           | 62         |

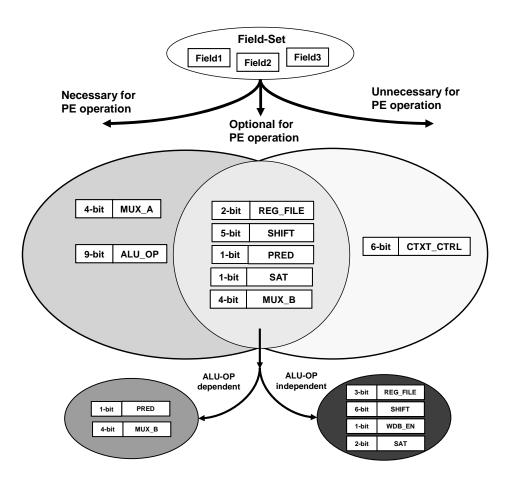

|         | 2. Field Grouping                                                | 62         |

|         | 3. Field Sequence Graph Generation                               | 64         |

|         | 4. Generation of Field Control Signal                            | 65         |

|         | a. Control Signals for ALU-Dependent Fields                      | 66         |

| CHAPTER |                                                              | Page |

|---------|--------------------------------------------------------------|------|

|         | b. Control Signals for ALU-Independent Fields                | 66   |

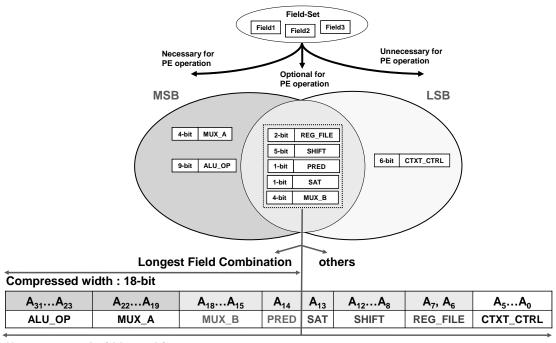

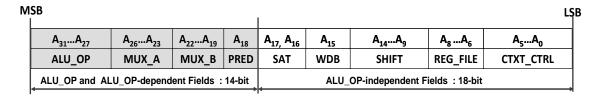

|         | 5. Field Positioning                                         | 67   |

|         | a. Field Positioning on Uncompressed Context Word            | 67   |

|         | b. Field Positioning on Compressed Context Word              | 69   |

|         | 6. Compressible Context Architecture                         | 78   |

|         | 7. Context Evaluation                                        | 78   |

|         | D. Experiments                                               | 78   |

|         | 1. Experimental Setup                                        | 78   |

|         | 2. Results                                                   | 79   |

|         | a. Area Cost Evaluation                                      | 79   |

|         | b. Performance Evaluation                                    | 80   |

|         | c. Context Compression Ratio and Power Evaluation            | 81   |

| VI      | DYNAMIC CONTEXT MANAGEMENT FOR LOW POWER                     | 0.0  |

|         | CGRA                                                         | 82   |

|         | A. Motivation                                                | 82   |

|         | 1. Power Consumption by Configuration Cache                  | 82   |

|         | 2. Redundancy of Context Words                               | 83   |

|         | a. NOP Context Words                                         | 83   |

|         | b. Consecutively Same Part in Context Words                  | 85   |

|         | c. Redundancy Ratio                                          | 86   |

|         | B. Dynamic Context Management                                | 86   |

|         | 1. Context Partitioning                                      | 87   |

|         | 2. Context Management at Transfer Time                       | 90   |

|         | 3. Context Management at Run Time                            | 92   |

|         | C. Experiments                                               | 94   |

|         | 1. Experimental Setup                                        | 94   |

|         | 2. Results                                                   | 94   |

|         | a. Area Cost Evaluation                                      | 94   |

|         | b. Power Evaluation                                          | 95   |

|         | c. Performance Evaluation                                    | 96   |

| VII     | COST-EFFECTIVE ARRAY FABRIC                                  | 97   |

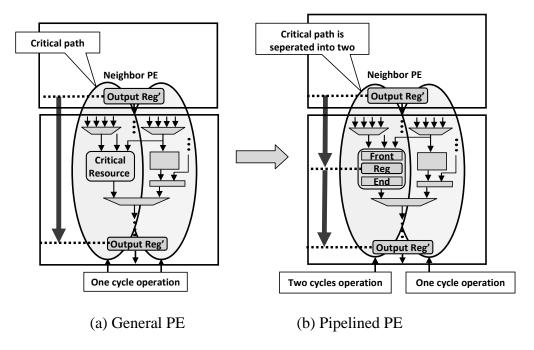

|         | A. Preliminary                                               | 97   |

|         | 1. Resource Sharing                                          | 98   |

|         | 2. Resource Pipelining.                                      | 101  |

|         | B. Cost-Effective Reconfigurable Array Fabric                | 103  |

|         | 1. Motivation                                                | 103  |

|         | a. Characteristics of Computation-Intensive and Data-Paralle |      |

|         | <u>*</u>                                                     | 103  |

|         | Application                                                  | 103  |

| CHAPTER |                                                                                                                                         | Page |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

|         | b. Redundancy in Conventional Array Fabric                                                                                              | 104  |

|         | 2. New Cost Effective Data Flow-Oriented Array Structure                                                                                | 105  |

|         | <ul><li>a. Derivation of Data Flow-Oriented Array Structure</li><li>b. Mitigation of Spatial Limitation in the Proposed Array</li></ul> | 105  |

|         | Structure                                                                                                                               | 109  |

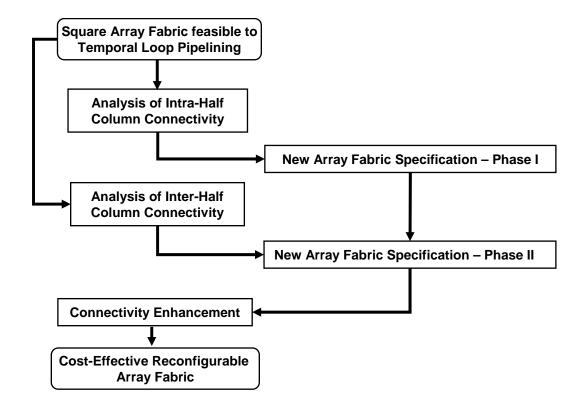

|         | 3. Data Flow-Oriented Array Design Flow                                                                                                 | 110  |

|         | a. Input Reconfigurable Array Fabric                                                                                                    | 112  |

|         | b. New Array Fabric Specification-Phase I                                                                                               | 112  |

|         | c. New Array Fabric Specification-Phase II                                                                                              |      |

|         | d. Connectivity Enhancement                                                                                                             | 122  |

|         | 4. Cost-Effective Array Fabric with Resource Sharing                                                                                    |      |

|         | and Pipelining                                                                                                                          | 123  |

|         | C. Experiments                                                                                                                          | 125  |

|         | 1. Experimental Setup                                                                                                                   | 125  |

|         | a. Evaluated Applications                                                                                                               |      |

|         | b. Hardware Design and Power Estimation                                                                                                 | 126  |

|         | 2. Results                                                                                                                              | 127  |

|         | a. Area Evaluation                                                                                                                      | 127  |

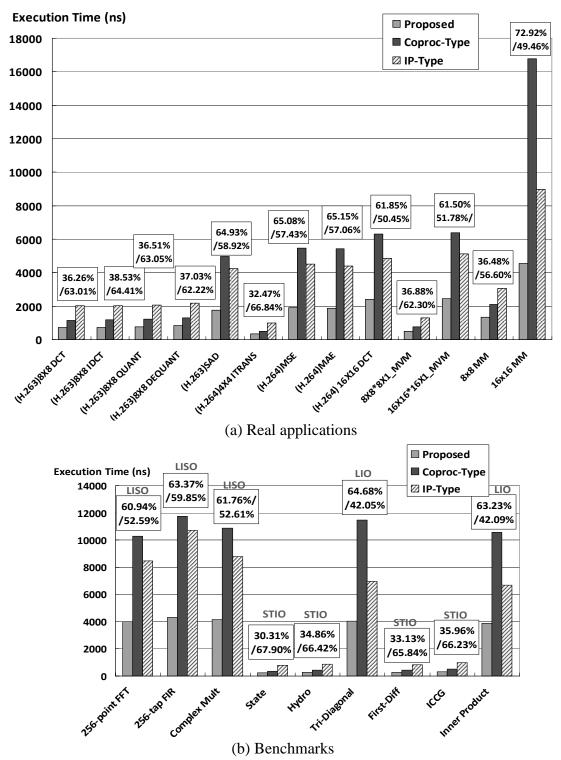

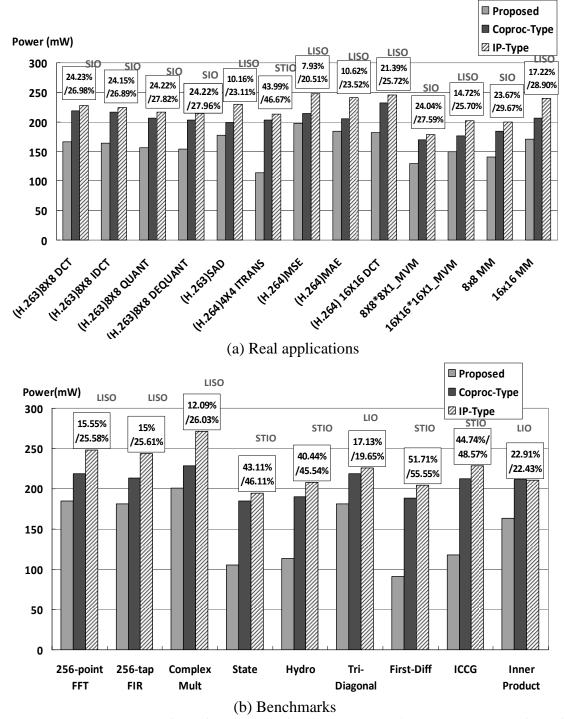

|         | b. Performance Evaluation                                                                                                               | 127  |

|         | c. Power Evaluation                                                                                                                     | 130  |

|         |                                                                                                                                         |      |

| VIII    | HIERARCHICAL RECONFIGURABLE COMPUTING ARRAYS.                                                                                           | 131  |

|         | A. Motivation                                                                                                                           | 131  |

|         | 1. Limitation of Existing Processor-RAA                                                                                                 |      |

|         | Communication Structures                                                                                                                | 131  |

|         | 2. RAA-based Computing Hierarchy                                                                                                        |      |

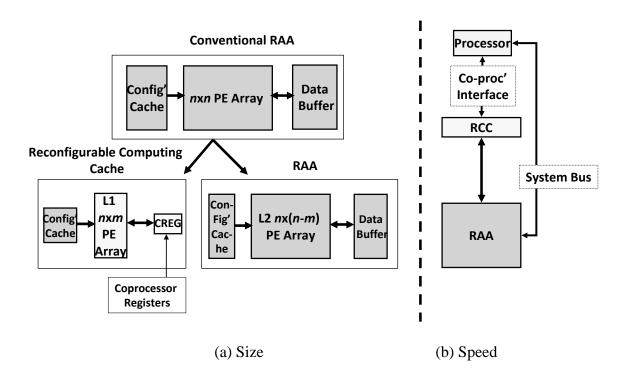

|         | B. Computing Hierarchy in CGRA                                                                                                          | 134  |

|         | 1. Computing Hierarchy –Size and Speed                                                                                                  | 135  |

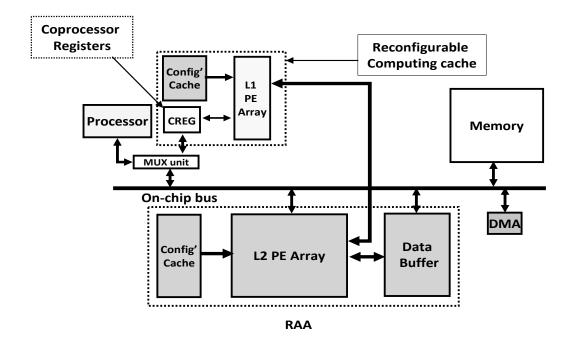

|         | 2. Resource Sharing in RCC and RAA                                                                                                      | 136  |

|         | 3. Computing Flow Optimization                                                                                                          | 140  |

|         | C. Experiments                                                                                                                          | 142  |

|         | 1. Experimental Setup                                                                                                                   | 142  |

|         | a. Architecture Implementation                                                                                                          | 142  |

|         | b. Evaluated Applications                                                                                                               | 144  |

|         | 2. Results                                                                                                                              | 144  |

|         | a. Area Cost Evaluation                                                                                                                 | 144  |

|         | b. Performance Evaluation                                                                                                               | 144  |

|         | c. Power Evaluation                                                                                                                     | 146  |

| IX      | INTEGRATED APPROACH TO OPTIMIZE CGRA                                                                                                    | 149  |

| CHAPTER  |                                                                                                   | Page       |

|----------|---------------------------------------------------------------------------------------------------|------------|

|          | A. Combination among the Cost-Effective CGRA Design Schemes B. Case Study for Integrated Approach |            |

|          | <ol> <li>An CGRA Design Example Merging Three Design Schemes.</li> <li>Results</li> </ol>         | 150<br>151 |

|          | a. Area and Performance Evaluationb. Power Evaluation                                             |            |

|          | C. Potential Combinations and Expected Outcomes                                                   |            |

| X        | CONCLUSIONS                                                                                       | 155        |

| REFERENC | CES                                                                                               | 158        |

| VITA     |                                                                                                   | 168        |

## LIST OF FIGURES

| FIGURE |    |                                                                                         | Page |

|--------|----|-----------------------------------------------------------------------------------------|------|

|        | 1  | Block diagram of general CGRA                                                           | 7    |

|        | 2  | Basic types of reconfigurable array coupling                                            | 14   |

|        | 3  | Block diagram of base CGRA                                                              | 14   |

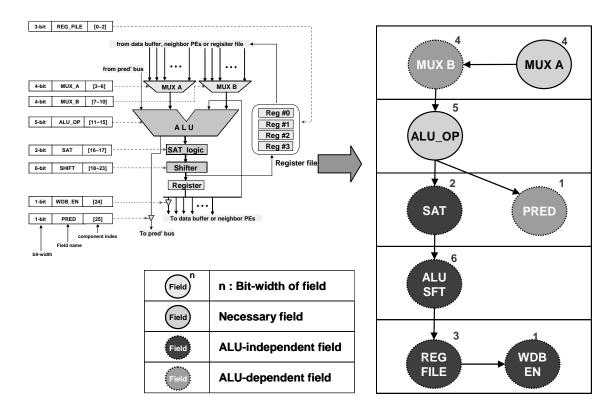

|        | 4  | Processing element structure of base RAA                                                | 16   |

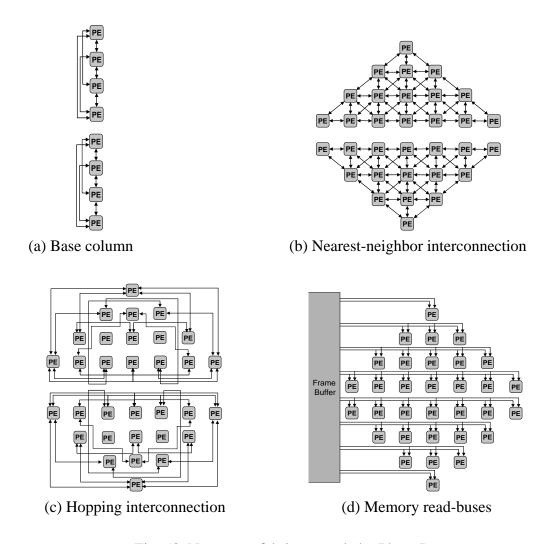

|        | 5  | Interconnection structure of PE array                                                   | 17   |

|        | 6  | Distributed configuration cache structure                                               | 18   |

|        | 7  | Area cost breakdown for CGRA                                                            | 20   |

|        | 8  | Cost analysis for a PE                                                                  | 21   |

|        | 9  | Power cost breakdown for CGRA running 2D-FDCT                                           | 22   |

|        | 10 | 4x4 reconfigurable array                                                                | 26   |

|        | 11 | C-code of Eq. (2)                                                                       | 28   |

|        | 12 | Execution model for CGRA                                                                | 29   |

|        | 13 | Comparison between temporal mapping and spatial mapping                                 | 32   |

|        | 14 | Configuration cache structure for context reuse                                         | 33   |

|        | 15 | Cache structure for context pipelining                                                  | 35   |

|        | 16 | Proposed configuration cache structure                                                  | 37   |

|        | 17 | Reusable context pipelining for Eq. (2)                                                 | 40   |

|        | 18 | Reusable context pipelining with temporal cache                                         | 41   |

|        | 19 | Reusable context pipelining according to the execution time for one iteration $(i > 1)$ | 42   |

| FIGURE |    | Page                                                                     |    |

|--------|----|--------------------------------------------------------------------------|----|

|        | 20 | Hybrid configuration cache structure                                     | 44 |

|        | 21 | Application mapping flow for base architecture and proposed architecture | 45 |

|        | 22 | Temporal mapping steps                                                   | 46 |

|        | 23 | Context rearrangement                                                    | 48 |

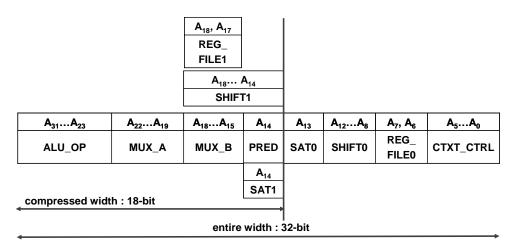

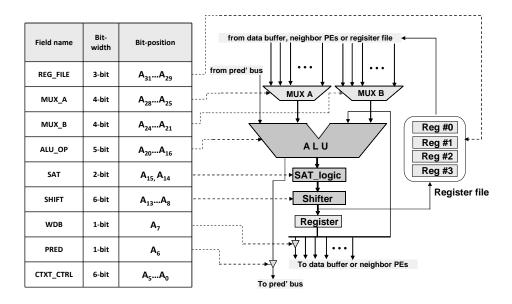

|        | 24 | PE structure and context architecture of MorphoSys                       | 56 |

|        | 25 | Valid bit-width of context words                                         | 58 |

|        | 26 | Entire design flow                                                       | 60 |

|        | 27 | Context architecture initialization                                      | 61 |

|        | 28 | Field grouping                                                           | 63 |

|        | 29 | Field sequence graph                                                     | 64 |

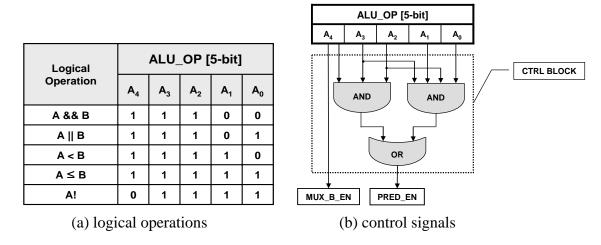

|        | 30 | Control signals for 'MUX_B' and 'PRED'                                   | 65 |

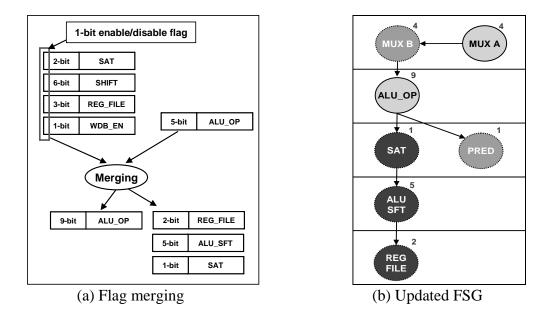

|        | 31 | Updated FSG from flag merging                                            | 67 |

|        | 32 | Default field positioning.                                               | 68 |

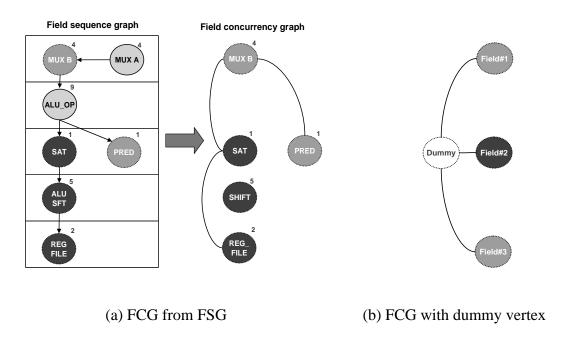

|        | 33 | Field concurrency graph                                                  | 69 |

|        | 34 | Examples of 'Find_Interval'                                              | 75 |

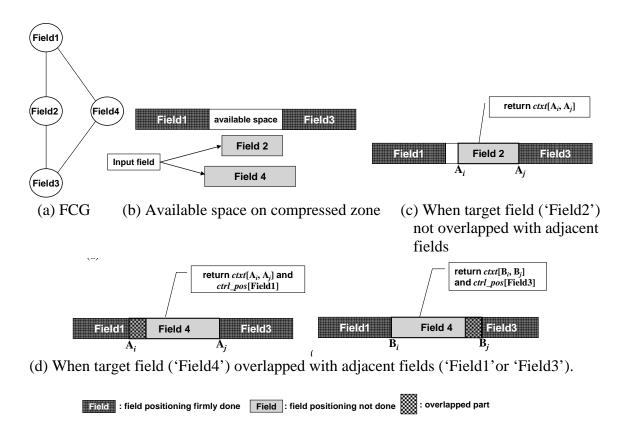

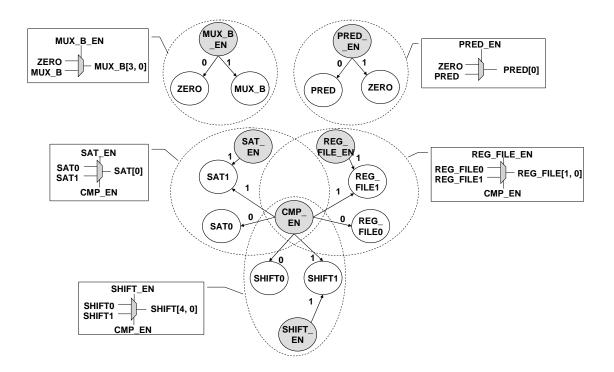

|        | 35 | Multiplexer port-mapping graph                                           | 76 |

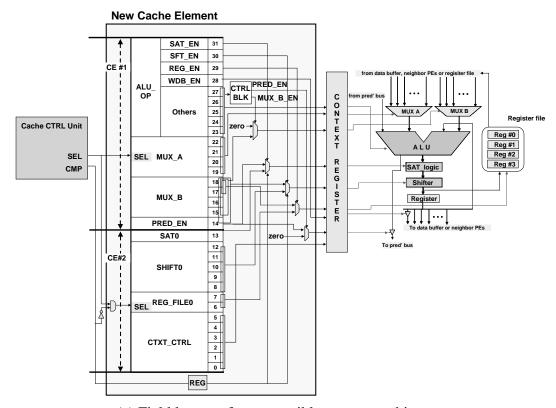

|        | 36 | Compressible context architecture                                        | 77 |

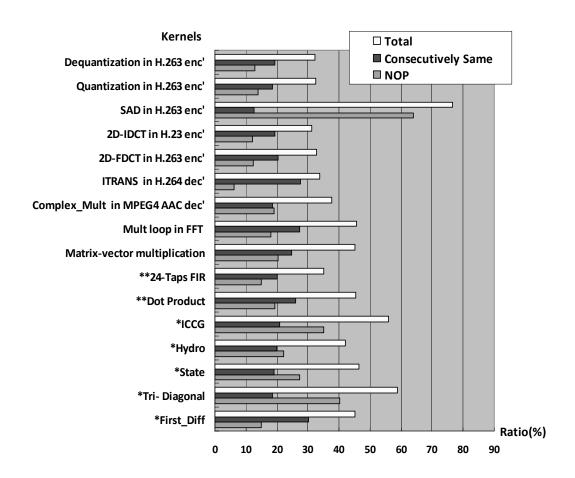

|        | 37 | Consecutively same part in context words                                 | 84 |

|        | 38 | Redundancy ratio of context words                                        | 85 |

|        | 39 | An example of PE and context architecture                                | 87 |

|        | 40 | Context partitioning                                                     | 88 |

| FIGURE |                                                                           |     |

|--------|---------------------------------------------------------------------------|-----|

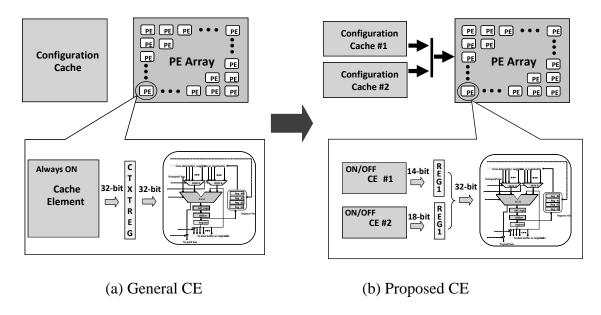

| 41     | Comparison between general CE and proposed CE                             | 89  |

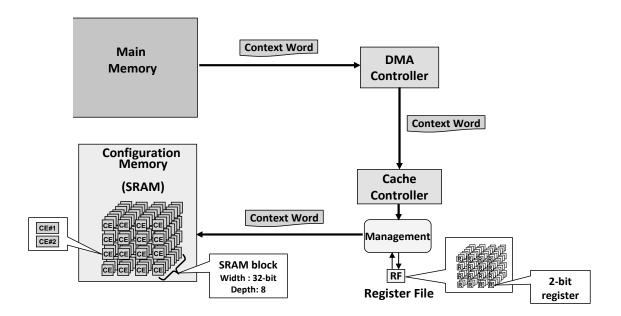

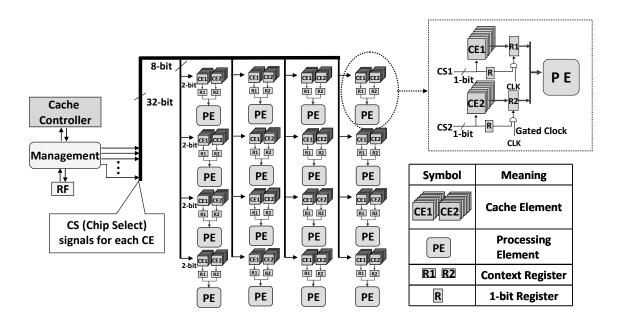

| 42     | Context management when context words are transferred                     | 89  |

| 43     | Context management at run time                                            | 92  |

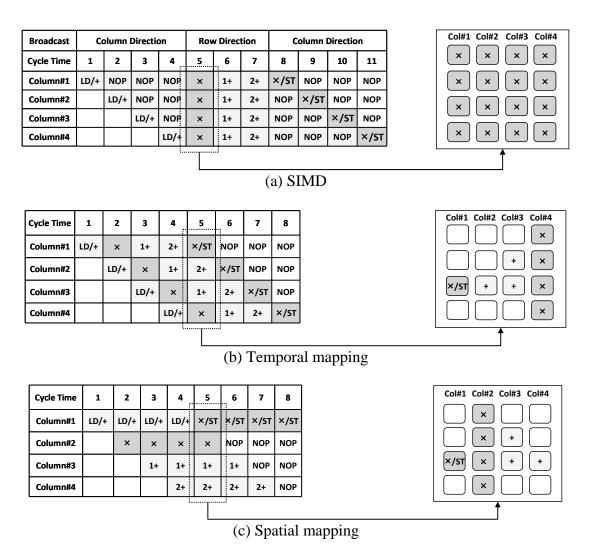

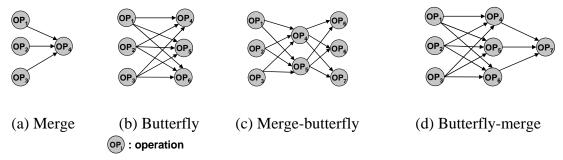

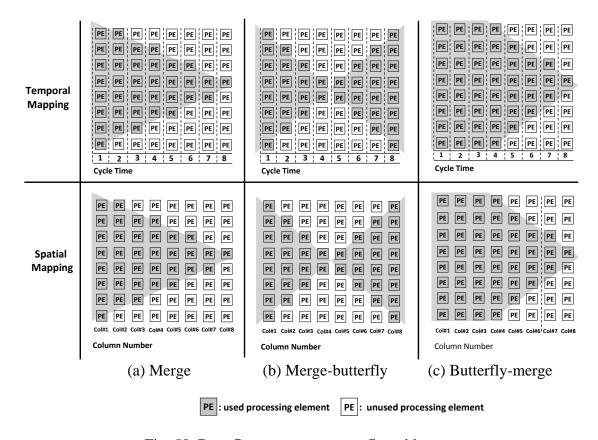

| 44     | Snapshots of three mappings                                               | 98  |

| 45     | Eight multipliers shared by sixteen PEs                                   | 99  |

| 46     | The connection between a PE and shared multipliers                        | 100 |

| 47     | Critical paths                                                            | 101 |

| 48     | Loop pipelining with pipelined multipliers                                | 102 |

| 49     | Subtask classification                                                    | 104 |

| 50     | Data flow on square reconfigurable array                                  | 105 |

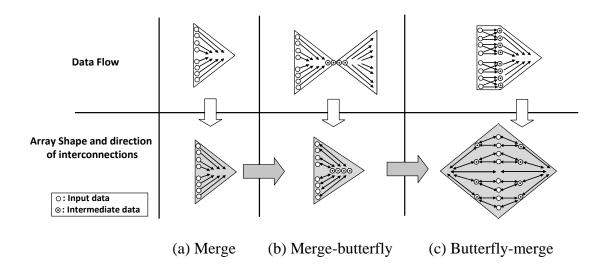

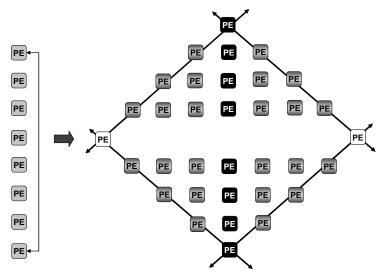

| 51     | Data flow-oriented array structure derived from three types of data flow. | 106 |

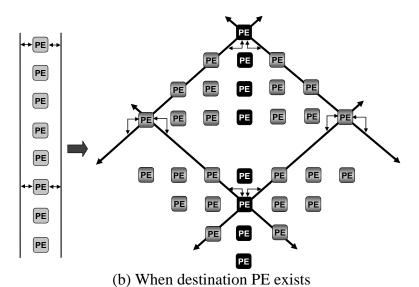

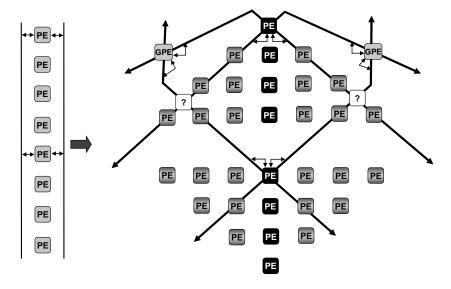

| 52     | An example of data flow-oriented array                                    | 107 |

| 53     | Snapshots showing the maximum utilization of PEs                          | 109 |

| 54     | Overall design flow                                                       | 111 |

| 55     | Basic concept of local triangulation method                               | 114 |

| 56     | Local triangulation method                                                | 115 |

| 57     | Interconnection derivation in Phase I                                     | 116 |

| 58     | New array fabric example by Phase I                                       | 117 |

| 59     | Global triangulation method when $n = 2$ (L2)                             | 120 |

| 60     | New array fabric example by Phase II                                      | 122 |

| 61     | New array fabric example by connectivity enhancement                      | 123 |

| FI | FIGURE |                                                                                |     |

|----|--------|--------------------------------------------------------------------------------|-----|

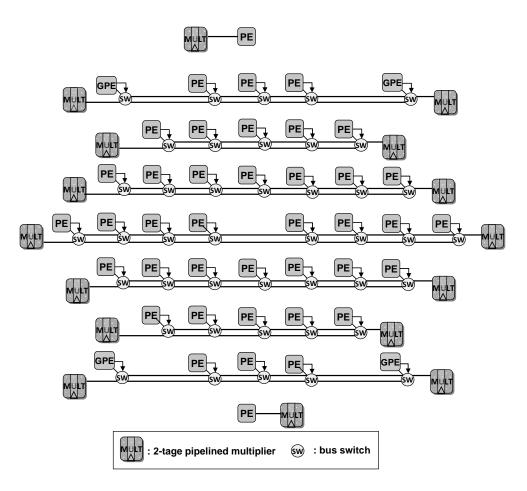

|    | 62     | New array fabric with resource sharing and pipelining                          | 124 |

|    | 63     | Mapping example on new array fabric                                            | 125 |

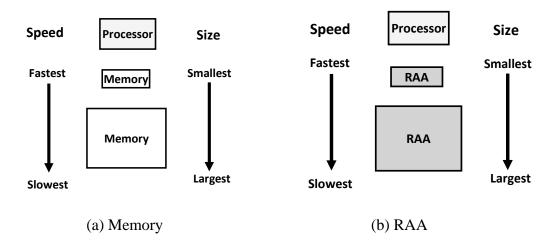

|    | 64     | Analogy between Memory and RAA-computing hierarchy                             | 134 |

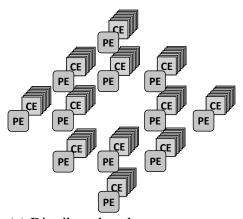

|    | 65     | Computing hierarchy of CGRA                                                    | 134 |

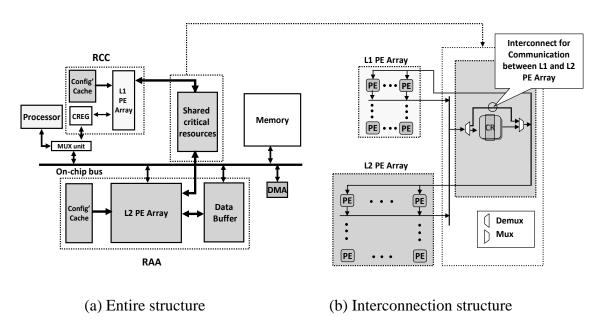

|    | 66     | CGRA configuration with RCC and RAA                                            | 136 |

|    | 67     | Two cases of functional resource assignment                                    | 138 |

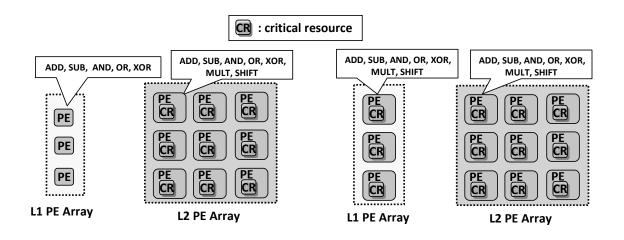

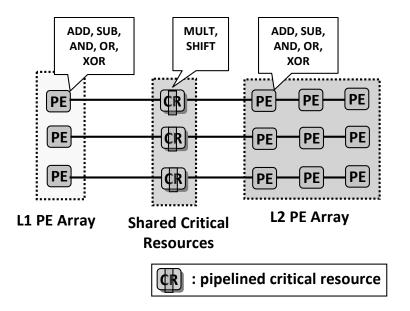

|    | 68     | Critical resource sharing and pipelining in L1 and L2 PE array                 | 139 |

|    | 69     | Interconnection structure among RCC, shared critical resources and L2 PE array | 139 |

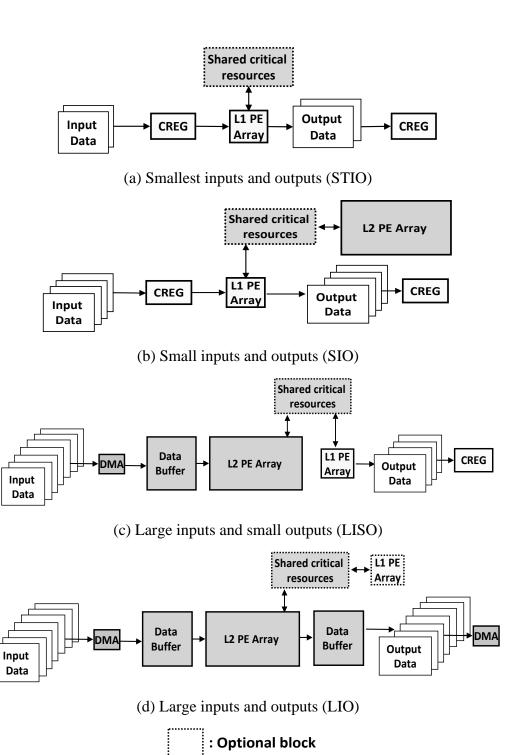

|    | 70     | Four cases of computing flow according to the input/output size of application | 141 |

|    | 71     | Performance comparison                                                         | 145 |

|    | 72     | Power comparison                                                               | 147 |

|    | 73     | Combination flow of the proposed design schemes                                | 150 |

|    | 74     | A combination example combining three design schemes                           | 151 |

|    | 75     | Potential combination of multiple design schemes                               | 154 |

## LIST OF TABLES

| TABLE |                                                              | Page |

|-------|--------------------------------------------------------------|------|

| I     | Architecture Specification of Base and Proposed Architecture | 51   |

| II    | Necessary Context Registers for Evaluated Kernels            | 51   |

| III   | Size of Configuration Cache and Context Registers            | 52   |

| IV    | Power Reduction Ratio by Reusable Context Pipelining         | 53   |

| V     | Notations for Port-Mapping Algorithm                         | 71   |

| VI    | Area Overhead by Dynamic Context Compression                 | 80   |

| VII   | Power Reduction Ratio by Dynamic Context Compression         | 80   |

| VIII  | Area Overhead by Dynamic Context Management                  | 94   |

| IX    | Power Reduction Ratio by Dynamic Context Management          | 95   |

| X     | Area Reduction Ratio by RSPA and NAF                         | 127  |

| XI    | Applications Characteristics and Performance Evaluation      | 128  |

| XII   | Power Reduction Ratio by RSP+NAF                             | 129  |

| XIII  | Comparison of the Basic Coupling Types                       | 133  |

| XIV   | Comparison of the Architecture Implementations               | 142  |

| XV    | Applications Characteristics                                 | 143  |

| XVI   | Area Cost Comparison                                         | 144  |

| XVII  | Area Reduction Ratio by Integrated RAA                       | 152  |

| XVII  | I Entire Power Comparison                                    | 153  |

#### **CHAPTER I**

#### INTRODUCTION

With the growing demand for high quality multimedia, especially over portable media, there has been continuous development on more sophisticated algorithms for audio, video, and graphics processing. These algorithms have the characteristics of data-intensive computation of high complexity. For such applications, we can consider two extreme approaches to implementation: software running on a general purpose processor and hardware in the form of ASIC. In the case of general purpose processor, it is flexible enough to support various applications but may not provide sufficient performance to cope with the complexity of the applications. In the case of ASIC, we can optimize best in terms of power and performance but only for a specific application. With a coarse-grained reconfigurable architecture (CGRA), we can take advantage of the above two approaches. This architecture has higher performance level than general purpose processor and wider applicability than ASIC.

As the market pressure of embedded systems compels the designer to meet tighter constraints on cost, performance, and power, the application specific optimization of a system becomes inevitable. On the other hand, the flexibility of a system is also important to accommodate rapidly changing consumer needs. To compromise these incompatible demands, domain-specific design is focused on as a suitable solution for recent

The journal model is IEEE Transactions on Very Large Scale Integration Systems.

embedded systems. Coarse-grained reconfigurable architecture is the very domainspecific design in that it can boost the performance by adopting specific hardware engines while it can be reconfigured to adapt to ever-changing characteristics of the applications.

In spite of the above advantages, the deployment of CGRA is prohibitive due to its significant area and power consumption. This is due to the fact that CGRA is composed of several memory components and the array of many processing elements including ALU, multiplier and divider, etc. Especially, processing element (PE) array occupies most of the area and consumes most of the power in the system to support flexibility and high performance. Therefore, reducing area and power consumption in the PE array has been a serious concern for the adoption of CGRA.

#### A. Objective and Approach

This dissertation explores the problem of reducing area and power in CGRA based on architecture optimization. To provide cost-effective CGRA design, the following questions are considered.

- How to reduce area and power consumption in CGRA? For power saving in CGRA, We should obtain area and power breakdown data of CGRA to identify area and power-dominant components. Then the components may be optimized for area and power by removing redundancies of CGRA wasting area and power. Such redundancies may depend on the characteristics of computation model or applications.

- How to design cost-effective CGRA with non-sacrificing or enhancing perform-

ance? Ultimately, the goals of designing cost-effective CGRA is that proposed approaches do not cause performance degradation with saving area and power. It means that the proposed cost-effective CGRA keeps original functionality of CGRA intact and does not increase critical path delay. In addition, the performance may be enhanced by optimizing the performance bottleneck with keeping the area and power-efficient approaches.

In this dissertation, these central questions are addressed for area/power-critical components of CGRA and we suggest new frameworks to achieve these goals. The validation of the proposed approaches is demonstrated through the use of real application benchmarks and gate level simulations.

#### **B.** Contributions

This work makes the following contributions:

- Low power reconfiguration technique for CGRA. It presents a novel power-conscious architectural technique called reusable context pipelining (RCP) for CGRA to close the power-performance gap between low power-oriented spatial mapping and high performance-oriented temporal mapping prevailing in existing CGRA architectures. A new configuration cache structure has been proposed to support reusable context pipelining with negligible overheads. The temporal mapping with RCP has been shown to be a universal approach in reducing power and enhancing performance for CGRA.

- Dynamic context compression for low power CGRA. A new design flow for

CGRA design has been proposed to generate architecture specifications that are required for modifying configuration cache dynamically. Design methodology for dynamically compressible context architecture and a new cache structure to support the configurability are being presented to reduce the power consumption in configuration cache without performance degradation.

- Dynamic context management for low power CGRA. It presents a novel control mechanism of configuration cache called dynamic context management to reduce the power consumption in configuration cache without performance degradation. A new configuration cache structure is proposed to support dynamic context management.

- A new array fabric for CGRA. A novel array fabric design exploration method has been proposed to generate cost-effective reconfigurable array structure. Novel rearrangement of processing elements and their interconnection designs are introduced for CGRA to reduce area and power consumption without any performance degradation.

- Hierarchical reconfigurable computing arrays for efficient CGRA-based embedded systems. A new reconfigurable computing hierarchy has been proposed to design cost-effective CGRA-based embedded systems. Efficient communication structure between processor and reconfigurable computing blocks is introduced to reduce performance bottleneck in the CGRA-based architecture.

#### C. Dissertation Organization

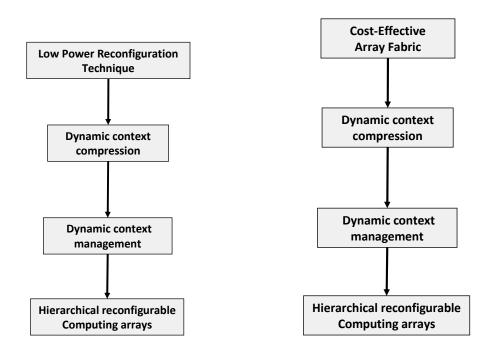

The rest of the dissertation is organized as follows. In Chapter II, we describe background and related work of this dissertation. Chapter III presents base architecture implementation and its cost breakdown. In Chapter IV, we propose *low power reconfiguration technique* to reduce power in configuration cache. Chapters V and VI present *dynamic context compression* and *dynamic context management* capable of reducing power consumption in configuration cache. In Chapter VII, we device a cost-effective array fabric for CGRA to reduce area and power in PE array. Chapter VIII presents hierarchical reconfigurable computing array to reduce area and power with enhancing performance. Finally, we present integrated approach to merge the multiple design schemes and conclude this work in Chapters IX and X.

#### **CHAPTER II**

#### BACKGROUND AND RELATED WORKS

#### A. Coarse-Grained Reconfigurable Architecture

A recent trend in the architectural platforms for embedded systems is the adoption of reconfigurable computing elements for cost, performance, and flexibility issues [1]. Coarse-Grained Reconfigurable Architectures (CGRAs) [1] exploit both the flexibility and efficiency, and are shown to be a generally better solution for compute-intensive applications than fine-grained reconfigurable architectures. There are different styles of CGRAs, but many architectures are based on 2D array of ALU-like datapath blocks. These are particularly interesting due to the wide acceptance in recent reconfigurable processors as well as their expected high performance for many heavy-load applications in the domains of signal processing, multimedia, communication, security, and so on.

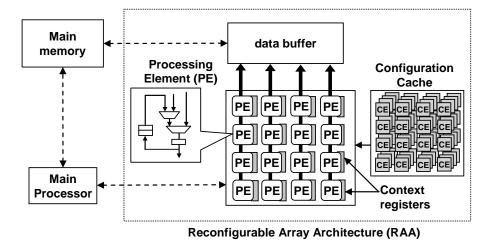

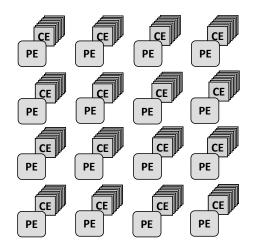

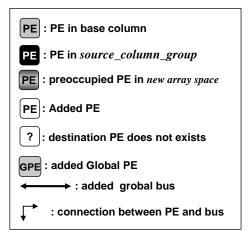

Typically, a CGRA consists of a main processor, a Reconfigurable Array Architecture (RAA), and their interface as Fig. 1. The RAA has identical processing elements (PEs) containing functional units and a few storage units such as ALU, multiplier, shifter and register file. The data buffer provides operand data to PE array through a high-bandwidth data bus. The configuration cache (or context memory) stores the context words used for configuring the PE array elements. The context register between a PE and a cache element (CE) in configuration cache is used to keep the cache access path from being the critical path of the CGRA.

Fig. 1. Block diagram of general CGRA.

Unlike FPGA (most typical of a fine-grained reconfigurable architecture), which are built with bit-level configurable logic blocks (CLBs), CGRA is built with PEs, which are word-level configurable functional blocks. By raising the granularity of operations from a bit to a word, CGRA can improve on the speed and the performance as well as the resource utilization for compute-intensive applications. Another consequence of this raised granularity is that whereas FPGA can be used for implementing any digital circuits, CGRA is targeted only for a limited set of applications, although different CGRAs may target different application domains. Still, CGRA retains the idea of "reprogrammable hardware" in the reprogrammable interconnects as well as in the configurable functional blocks (i.e., PEs). Moreover, since the amount of the configuration bit-stream is greatly reduced through the raised granularity, the configuration can be actually changed even at the runtime very fast. Most of the CGRAs feature single-cycle configuration change, fetching the configuration data from a distributed local cache. This unique com-

bination of efficiency and flexibility, which in the main advantage of CGRA, explains an evaluation result [2] that under certain conditions CGRAs are actually more cost-effective for wireless communication applications than alternatives such as FPGA implementations as well as DSP architectures. It is worth mentioning that the improved efficiency of CGRAs in terms of the speed, performance, and area is a result of the architecture specialization for compute-intensive applications.

#### **B.** Related Works

Many kinds of coarse-grained reconfigurable architecture have been proposed with the increasing interests in reconfigurable computing until 2001 [1]. These CGRAs can be classified into two cases: mesh-based reconfigurable array and linear reconfigurable array. Mesh-based reconfigurable arrays arrange their processing elements (PEs) mainly as a rectangular 2-D array with horizontal and vertical connections, which support rich communication resources for efficient parallelism. In the case of linear reconfigurable arrays, they support pipelined execution for stream-based applications with static or dynamic reconfiguration. MorphoSys [3] and REMARC [4] are representations of meshbased architectures. MorphoSys consists of Tiny\_RISC processor, RC (Reconfigurable Cell) array, frame buffer, context memory and DMA controller. RC array is an 8×8 array of ALUs that performs 16-bit operations based on SIMD programming model. RE-MARC consists of a global control unit and an 8x8 array of nano processors. A nano processor consists of an ALU, a 16-entry data RAM, an 8-entry register file, data input registers and data output registers. The configuration for each nano processor is stored in the 32-entry instruction RAM to support MIMD execution model as well as SIMD model. RaPiD [5] and PipeRench [6][7] have linear array structure. RaPiD provides different computing resources like ALUs, RAMs, multipliers and registers. These resources are irregularly distributed on one dimension and are mostly static reconfigured. However, PipeRench [6][7] relies on dynamic reconfiguration, allowing the reconfiguration of a processing element (PE) in each execution cycle. It consists of strips composed of interconnect and PEs with registers and ALUs. The reconfigurable fabric allows the configuration of a pipeline stage in every cycle, while concurrently executing all other stages.

Since then, many more new CGRAs [2][8][9][10][11][12][13][14] [15][16][17][18] [19] have been continuously proposed and evolved. Most of them comprise of a fixed set of specialized processing elements (PEs) and interconnection fabrics between them. The run-time control of the operation of each PE and the interconnection provides the reconfigurability.

However, such fixed architecture has limitations in optimizing the area cost and performance for various applications. For example, MorphoSys [3] consists of 8x8 array of Reconfigurable Cell coupled with Tiny\_RISC processor through system bus. It shows good performance for regular code segments in computation intensive domains but requires large amount of area and power consumption. XPP configurable system-on-chip architecture [10] is another example. XPP has 4 x 4 or 8 x 8 reconfigurable array and LEON processor with AMBA bus architecture. A processing element of XPP is composed of an ALU and some registers. Since the processing elements do not include heavy resources, the total area cost is not high but the range of applicable domains is restricted. In addition, XPP shows significant communication overhead between the proc-

essor and RAA through the system bus. REMARC [4] is reconfigurable Multimedia Array Coprocessor that consists of a global control unit and an 8x8 array of nano processors. The nano processors do not also include heavy resources like XPP but it also restricts the range of applicable domains. However, the communication with main processor is faster than [3] or [20] because the processor can access the register-set by coprocessor data transfer instructions. However, limited size of the register-set causes heavy registers-array traffic restricting performance enhancement. ADRES [21] tightly couples a VLIW processor and a reconfigurable matrix through shared register file. The reconfigurable matrix is used to accelerate the dataflow-like kernels in a highly parallel way, whereas the VLIW processor executes the non-kernel code by exploiting instructionlevel parallelism. Even though it also provides the fast communication speed between VLIW and the matrix but the entire structure is very dependent on VLIW processor architecture and it require huge register file for the communication. Therefore, the performance is limited by size of the register file. Most design space exploration techniques previously suggested are limited to the configuration of the internal structure of a PE and the interconnection scheme. Such configuration techniques are in general good at obtaining high performance but require high hardware cost. This is mainly because even a primitive PE design should be equipped with basic functional resources to gain reasonable performance. Moreover, adding a small functional block to a primitive PE design increases the total cost of the aggregate architecture a lot. In ADRES template [21], an XML-based architecture description language is used to define the overall topology, supported operation set, resource allocation, timing, and even internal organization of each processing element. KressArray [20] also defines the exploration properties such as array size, interconnections, and functionality of certain processing elements. However, both templates do not support common resources shared among processing elements, thus some critical functional resources may have low utilization while occupying large area.

The research on low power CGRA has three different aspects: architecture exploration, code compilation & mapping and physical implementation. Although the architecture exploration flows that have been suggested in [8][20][21] [22][23][24][25][26][27] [28] generate a good instance of CGRA considering area and performance, they do not deal with power consumption. Interconnect architecture explorations have been suggested for low energy [21][29]. Because CGRA has complex interconnection for performance and flexibility, power consumption due to interconnection is crucial. In [8][29] the authors have proposed energy-aware interconnection exploration to minimize energy by changing the topology between global register file and function units. However, this exploration only provides the trade-off between performance and energy. In [30] the authors have suggested hierarchical generalized mesh structure exploration that continues to exploit locality while reducing the cost of long connections but it has been only evaluated for specific reconfigurable DSPs. In the case of code compilation and mapping, loops are exploited mainly for performance [9][31][32][33][34][35][36][37][38][39][40] [43][44]. Many reconfigurable architectures have been implemented with various technologies [6][10][12][43][44][45][46]. Most of these researches have focused on efficient design with respect to small area and high performance. In [6][8], even though authors have presented power estimation data of the implemented architectures, these are only accessorial results and they do not offer power/energy-aware implementation. In [2][14], authors have emphasized that the implemented architectures are power-efficient as compared to fine-grained architectures such as FPGA running specific applications. These architectures are not general CGRA but specific for running some applications with low power consumption. In [6], the authors have fabricated PipeRench [7] in a 0.18 micron process. Their experimental results show that the power consumption is significantly high. Authors describe that the increase in power consumption is due to the dynamic reconfiguration requiring frequent configuration and state memory accesses. Hence, that power consumption by dynamic reconfiguration is a serious overhead as compared to other types of IP cores such as ASIC or ASIP.

#### **CHAPTER III**

#### BASE CGRA IMPLEMENTATION

We have first designed a conventional CGRA as the base architecture and implemented it at the RT-level. This conventional architecture will be used throughout this dissertation as a reference for quantitative comparison with our cost-effective approaches.

#### A. Reconfigurable Array Architecture Coupling with Processor

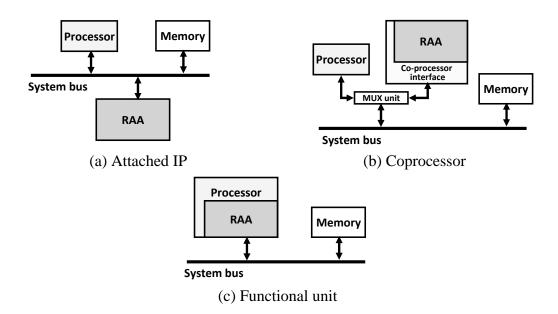

A typical coarse-grained reconfigurable architecture consists of a microprocessor, a Reconfigurable Array Architecture (RAA), and their interface. We can consider three ways of connecting the RAA to the processor [47]. First, the array can be connected to a bus as an 'Attached IP' shown in Fig. 2(a). Secondly, the array can be placed next to the processor as a 'Coprocessor' as shown in Fig. 2(b). In this case, the communication is done using a protocol similar to those used for floating point coprocessors. Finally, the array can be placed inside the processor like a 'FU (Functional Unit)' as shown in Fig. 2(c). In this case, the instruction decoder issues special instructions to perform specific functions on the reconfigurable array as if it were one of the standard functional units of the processor.

Fig. 2. Basic types of reconfigurable array coupling.

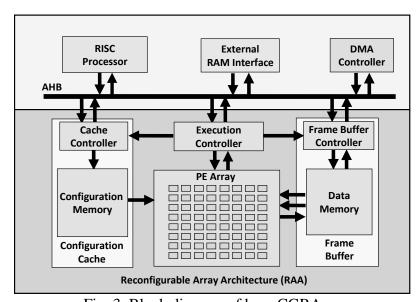

Fig. 3. Block diagram of base CGRA.

We have implemented the first type of reconfigurable architecture connecting the RAA as an Attached IP. In this case, the speed improvement using the RAA may have to

compensate for significant communication overhead. However, the main benefit of this type is the ease of constructing such a system using a standard processor and standard reconfigurable array without any modification. It consists of a RISC processor, a main memory block, a DMA controller, and an RAA. The RISC processor is a 32-bit processor which is small and simple with three pipeline stages and the communication bus is AMBA AHB [48], which couples the RISC processor and the DMA controller as master devices and the RAA as a slave device. The RISC processor executes control intensive, irregular code segments and the RAA executes data-intensive kernel code segments. The block diagram of the entire reconfigurable architecture is shown in Fig. 3.

#### B. Base Reconfigurable Array Architecture

Base RAA is similar to MorphoSys [3], which is a very representative CGRA showing high performance and flexibility as well as physical implementation. The difference from MorphoSys is that the proposed architecture supports both SIMD and MIMD execution model whereas the memory structure (frame buffer and configuration cache) of MorphoSys supports only the SIMD model. The SIMD model is efficient for data parallelism since it saves configurations and cache storage by sharing an instruction for multiple data. But its execution models are limited in that each individual PE cannot execute different instructions independently at the same time. Therefore, we take MIMD-style CGRA in which each PE can be configured separately to facilitate processing its own instructions. Since it allows more versatile configurations than their SIMD-style siblings, we adopt more general forms of loop pipelining [32] through simultaneous execution of multiple iterations of a loop in a pipeline.

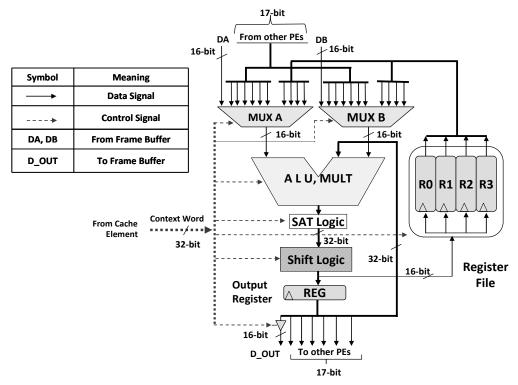

Fig. 4. Processing element structure of base RAA.

Base architecture specification is determined by our target application domain including audio/video codec as well as various benchmark kernels. Detailed features of each component of the architecture are as follows.

#### 1. Processing Element

Each PE is a dynamically reconfigurable unit executing arithmetic and logical operations. The inner structure of a PE is shown in Fig. 4. A PE contains a 16-bit ALU, 16 x 16-bit array multiplier, shift logic, Arithmetic saturation (SAT\_Logic), multiplexors and registers.

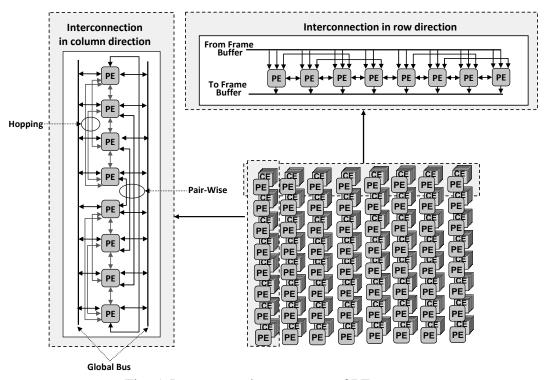

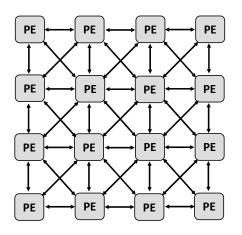

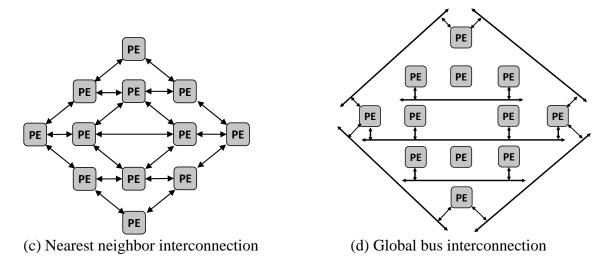

#### 2. PE Array

The PE array is an 8x8 reconfigurable array of PEs, which we think is big enough for

most of the applications considered in our experiments. We assume that computation model of the array is loop pipelining based on temporal mapping [32] for high performance - each iteration of application kernel (critical loop) is mapped onto each column of

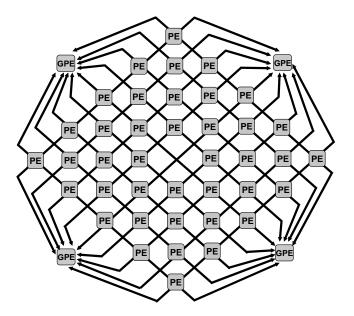

Fig. 5. Interconnection structure of PE array.

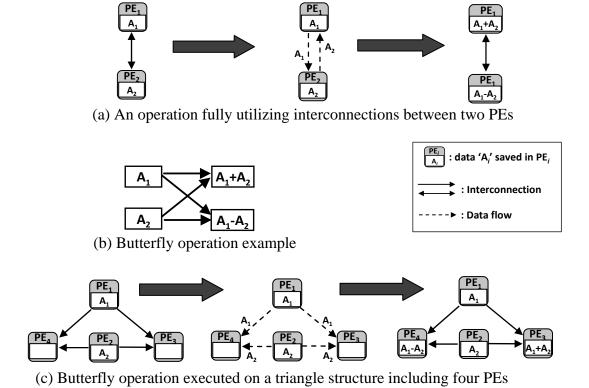

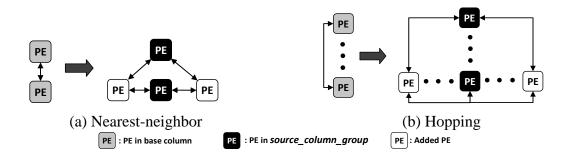

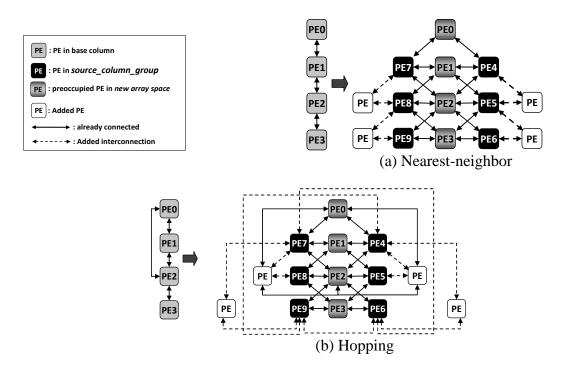

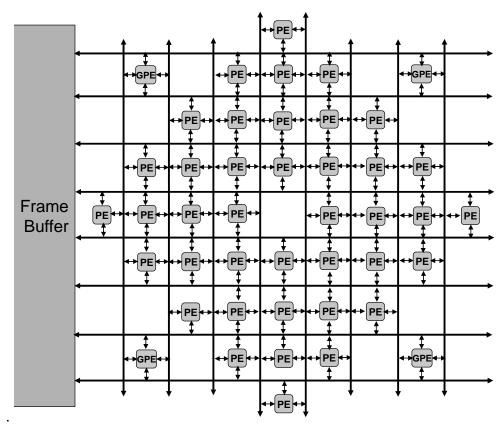

square array. Therefore, in this PE array, columns have more interconnection than rows. Fig. 5 shows interconnection structure of the PE array. The interconnection in rows is used mainly for the communication taking care of loop-carried dependencies. Columns and rows have nearest-neighbor and hopping interconnections for connectivity between two PEs in a half column and a half row. In addition, each column has pair-wise interconnections and two global buses for connectivity between two half columns. Each row shares two read-buses and one write-bus.

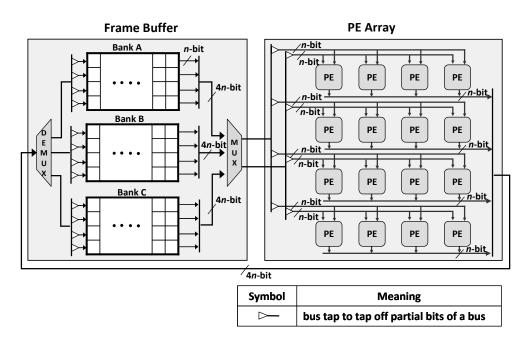

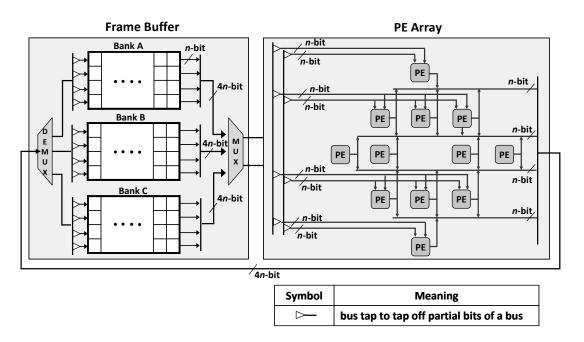

#### 3. Frame Buffer

Frame buffer (FB) of MorphoSys does not support concurrency between the load of two operands and the store of result in a same column, since it is not needed in SIMD-style mapping. However, in the case of MIMD-style execution, concurrent load and store operations can happen between different loop iterations. So our FB has two sets of buffers, each having three banks: one bank connected to the write bus and the other two banks

Fig. 6. Distributed configuration cache structure.

connected to the read buses. However, any combination of one-to-one mapping between the three banks and the three buses is possible.

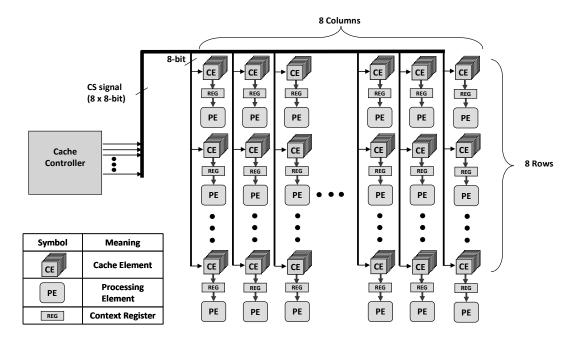

#### 4. Configuration Cache

The context memory of MorphoSys is designed for broadcasting configuration. So PEs

in the same row or column share the same context word for SIMD-style operation [3]. However, in the case of MIMD-style operation, each PE can be configured by different context word. Our configuration cache is composed of 64 Cache Elements (CEs) and a cache controller for controlling the CEs (Fig. 6). Each CE has 32 layers, each of which stores a context that configures the corresponding PE. The context register between a PE and a CE is used to keep the cache access path from being the critical path of the CGRA.

#### **5 Execution Controller**

Controlling the PE array execution directly from the main processor through AMBA AHB will cause high overhead in the main processor. In addition, the latency of the control will degrade the performance of the whole system, especially when dynamic reconfiguration is used. So a separate control unit is necessary to control the execution of the PE array every cycle. The execution controller receives the encoded control data from the main processor. The control data contains read/write mode and addresses of frame buffer and cache for guaranteeing correct operations of the PE array.

#### C. Breakdown of Area, Delay, and Power Cost

We have implemented the base architecture shown in Fig. 2 at the RT-level with VHDL. We have synthesized a gate-level circuit from the VHDL description and analyzed area, delay, and power cost. The synthesis has been done using Design Compiler [49] with 0.18  $\mu$ m technology. We have used DesignWare [49] library for the multipliers (carry-save array synthesis model) and dividers (restoring carry-look-ahead, 2-way overlapped synthesis model). SRAM Macro Cell library is used for the frame buffer and configuration cache. ModelSim [50] and PrimePower [49] have been used for gate-level simula-

tion and power estimation.

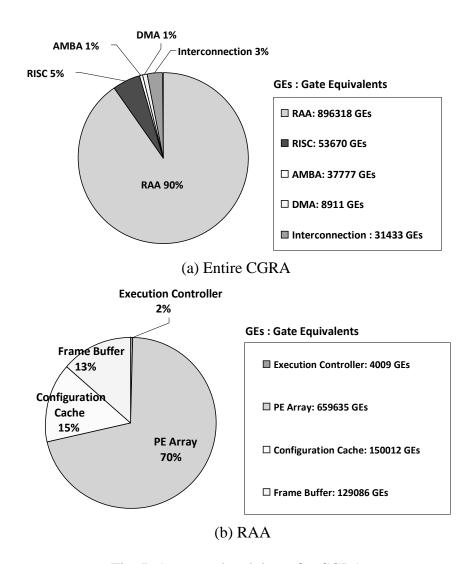

Fig. 7. Area cost breakdown for CGRA.

# 1. Area and Delay

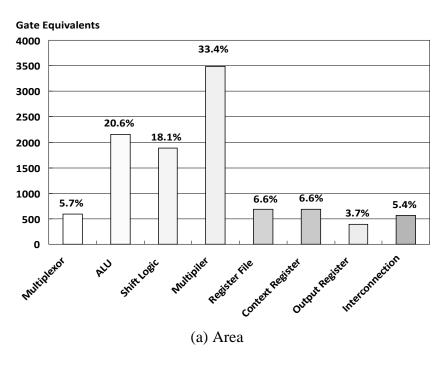

As shown in Fig. 7 (a), the RAA occupies as much as 90 % of the total area of the CGRA. Fig. 7 (b) shows more detailed area breakdown in the RAA. The PE array occupies as much as 70.5 % of the total area of the RAA, which is mainly due to heavy com-

putational resources such as ALU, multiplier, etc. in each PE. The critical path of the entire RAA is also in the PEs and its delay is given by

$$T_{Critical\ path} = T_{Multiplexor} + T_{Multiplier} + T_{Shift\_logic} + T_{others}$$

$$(8.96ns = 0.32ns + 5.21ns + 1.42ns + 1.78ns)$$

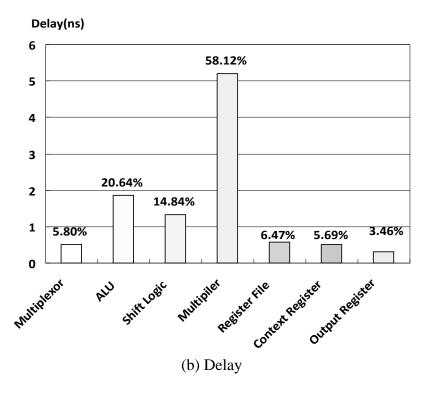

From the area and delay cost breakdown of the RAA as shown in Figs. 7 and 8, we see that PE array design is crucial for cost-effective design. In the case of area, Fig. 8 (a) shows that multiplier occupies about 33.4% of the total area in a PE. In the case of delay, the multiplier again takes as much as 58.12 % (Fig. 8 (b)). Therefore, in our PE design, the multiplier is considered to be area-critical and delay-critical resource.

Fig. 8. Cost analysis for a PE.

Fig. 8. Continued.

Fig. 9. Power cost breakdown for CGRA running 2D-FDCT.

Fig. 9. Continued.

#### 2. Power

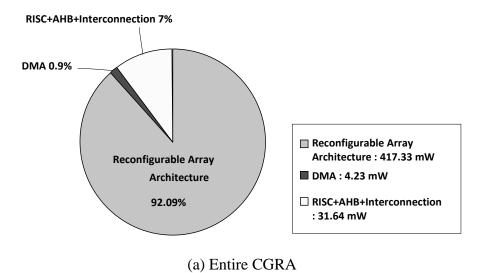

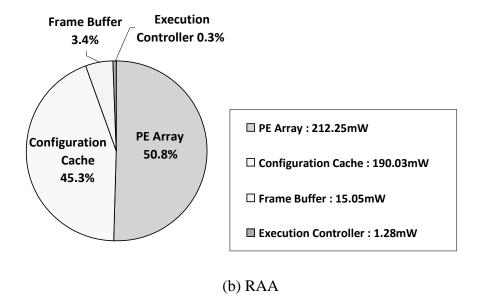

To obtain power breakdown data, we have used 2D-FDCT as the kernel for simulation-based power measurement. The simulation has been done under the typical operating condition of 100 MHz frequency, 1.8 V Vdd, and 27 °C temperature. As can be observed from Fig. 9 (a), the RAA spends about 92.09% of the total power consumed in CGRA. Fig. 9 (b) shows more detailed power breakdown in the RAA. The RAA spends about 50.8% of its total power in the PE array, which consists of many components such as ALUs, multipliers, shifters and register files. The PE array consumes most of the power, which is natural because coarse-grained architecture aims to achieve high performance and flexibility with plenty of resources. The configuration cache spends about 45.3% of the overall power, which is the second largest. Even though the frame buffer uses the same kind of SRAM as the configuration cache, it consumes much less power (3.4%).

This is because the configuration cache performs read operations frequently to load the context words, one for each PE, whereas the frame buffer performs load/store operations less frequently to access data on row basis rather than for every PE.

# **CHAPTER IV**

# LOW POWER RECONFIGURATION TECHNIQUE

In this chapter, we suggest a novel power-conscious architectural technique called *reusable context pipelining* (RCP) to reduce power consumption in configuration cache [51]. RCP is a universal approach in reducing power and enhancing performance for CGRA because it can be achieved by closing the power-performance gap between low power-oriented spatial mapping and high performance-oriented temporal mapping. Furthermore, we propose new configuration cache structure (called hybrid configuration cache) to support reusable context pipelining with reduced memory size. Experimental results show that the proposed approach saves much power even with reduced configuration cache size. Power reduction ratio in the configuration cache and the entire architecture are up to 86.33 % and 47.60 % respectively compared to the base architecture.

#### A. Motivation

In this section, we present the motivation of our power-conscious approaches. The main motivation is due to the characteristics of loop pipelining (spatial mapping and temporal mapping) [32] based on MIMD-style execution model.

## 1. Loop Pipelining

To represent the characteristics of loop pipelining [32], we examine the difference between SIMD and MIMD in the RAA with a simple example. We assume a mesh-based 4x4 coarse-grained reconfigurable array of PEs, where a PE is a basic reconfigurable

(a) Distributed cache structure

(b) Frame buffer and data bus

Fig. 10. 4x4 reconfigurable array.

- (c) Nearest neighbor interconnection

- (d) Global bus interconnection

Fig. 10. Continued.

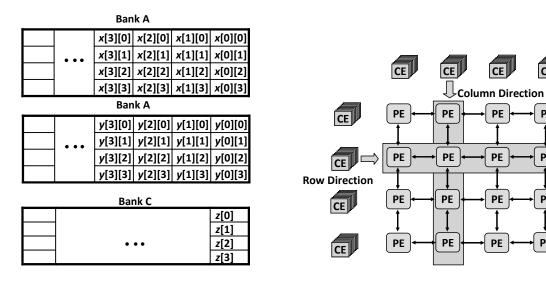

element composed of an ALU, an array multiplier, etc. and the configuration is controlled by the words stored in the CE as shown in Fig. 10 (a). In addition, we assume that Frame Buffer has simply one set having three banks and two read-ports and one write-port, supporting any combination of one-to-one mapping between the three banks and the three buses. Fig. 10 (b) shows such a Frame Buffer and data bus structure, where the PEs in each row of the array share two read buses and one write bus. The 4x4 array has nearest neighbor interconnections as shown in Fig. 10 (c) and each row or each column has a global bus as shown in Fig. 10 (d).

(a) Before parallelization

(b) After parallelization

Fig. 11. C-code of Eq. (2).

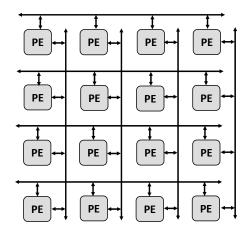

Consider a square matrix X and Y, both of order N, and the computation of Z, an N element vector, given by

$$Z(i) = K \times \sum_{j=0}^{N-1} \{ (X(i,j) + Y(i,j) \times C(j)) \}$$

(2)

where i, j = 0,1,...,N-1, C(j) is a constant vector, and K is a constant.

Consider N = 4 for the mapping of the computation defined in Eq. (2) on our 4x4 PE array and let the computation be given as a C-program (Fig. 11 (a)). It is assumed that the input matrix X, Y, constant vector C and output vector Z are stored in the arrays x[i][j], y[i][j], c[j] and z[i], and z[i] is initialized to zero. Fig. 11 (b) shows parallelized code for execution on the array as shown in Fig. 12, where we assume that matrix X and Y have been loaded into the Frame Buffer (FB) and all of the constants (C and K) have been already saved in a register file of each PE. Vector Z is stored in the FB after it has been

PE

PΕ

processed by the PE array as shown in Fig. 12 (a).

(a) Operand and result data in FB

| Symbol | Meaning                  |

|--------|--------------------------|

| LD/+   | Data Load and Addition   |

| NOP    | No Operation             |

| ×      | Multiplication           |

| 1+, 2+ | Addition                 |

| ×/ST   | Multiplication and Store |

| Broadcast  | Column Direction |      |      | Row Direction |   |    | Column Direction |      |      |      |      |

|------------|------------------|------|------|---------------|---|----|------------------|------|------|------|------|

| Cycle Time | 1                | 2    | 3    | 4             | 5 | 6  | 7                | 8    | 9    | 10   | 11   |

| Column#1   | LD/+             | NOP  | NOP  | NOP           | × | 1+ | 2+               | ×/ST | NOP  | NOP  | NOP  |

| Column#2   |                  | LD/+ | NOP  | NOP           | × | 1+ | 2+               | NOP  | ×/ST | NOP  | NOP  |

| Column#3   |                  |      | LD/+ | NOP           | × | 1+ | 2+               | NOP  | NOP  | ×/ST | NOP  |

| Column#4   |                  |      |      | LD/+          | × | 1+ | 2+               | NOP  | NOP  | NOP  | ×/ST |

(c) SIMD model

| Cycle Time | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    |

|------------|------|------|------|------|------|------|------|------|

| Column#1   | LD/+ | ×    | 1+   | 2+   | ×/ST | NOP  | NOP  | NOP  |

| Column#2   |      | LD/+ | ×    | 1+   | 2+   | ×/ST | NOP  | NOP  |

| Column#3   |      |      | LD/+ | ×    | 1+   | 2+   | ×/ST | NOP  |

| Column#4   |      |      |      | LD/+ | ×    | 1+   | 2+   | ×/ST |

(d) Loop pipelining schedule

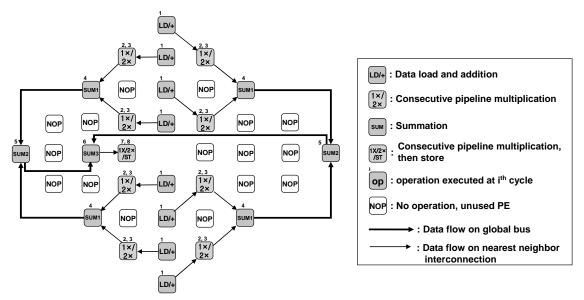

Fig. 12. Execution model for CGRA.

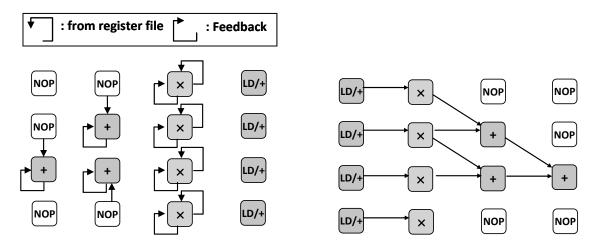

The SIMD-based scheduling enables parallel execution of multiple loop iterations as shown in Fig. 12 (c), whereas the MIMD-based scheduling enables loop pipelining as shown in Fig. 12 (d). The first row of Fig. 12 (c) represents the direction of configuration broadcast. The second row of Fig. 12 (c) and the first row of Fig. 12 (d) indicate the schedule time in cycles from the start of the loop. In the case of SIMD model, load and addition operations in PEs are executed on all columns till 4th cycle with broadcast in column direction. Then the PEs in a row perform the same operation with broadcast in row direction. In the case of loop pipelining, PEs in the first column perform load and addition operations in the first cycle and then perform multiplications in the second cycle. In the next two cycles, the PEs in the first column perform summations, while the PEs in the next column perform multiplication and summation operations. When the first column performs the multiplication/store operation in the 5th cycle, the fourth column performs multiplication. Comparing the latency, SIMD takes three more cycles.

As shown in this example, SIMD model does not utilize PEs efficiently since all data should be loaded before the computations of the same type are performed synchronously. On the other hand, since MIMD allows any type of computations at any moment, it does not need to wait for a specific data to be loaded but can process other data that is readily available. Loop pipelining is an effective way of exploiting this fact, thereby utilizing PEs better. The loop pipelining in the example of Fig. 11 improves the performance by three cycles compared to the SIMD, but for loops with more frequent memory operations, it will have higher performance improvement.

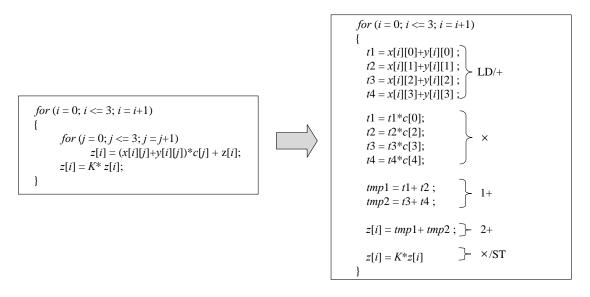

## 2. Spatial Mapping and Temporal Mapping

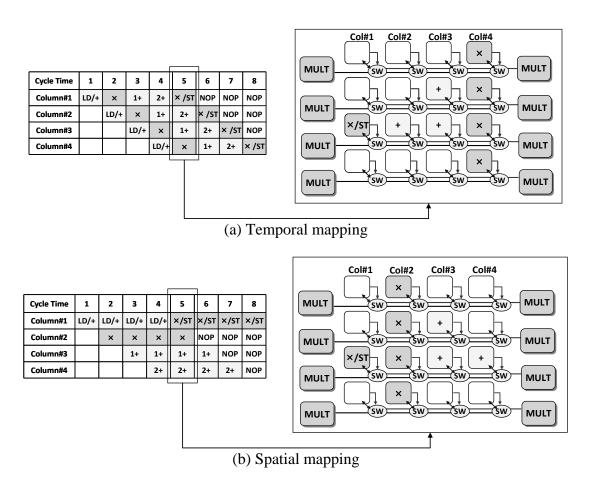

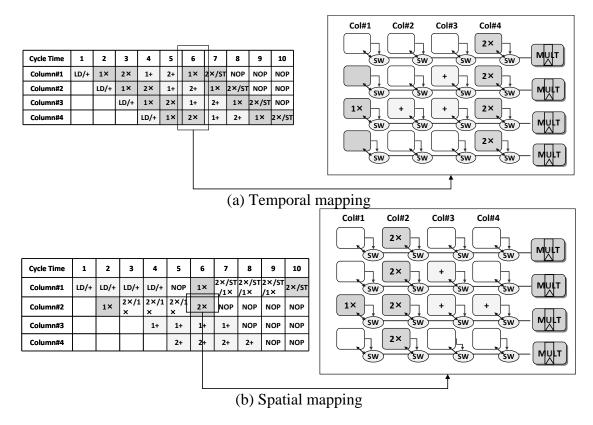

When mapping kernels onto the reconfigurable architecture with loop pipelining, we can consider two mapping techniques [32]: spatial mapping and temporal mapping. Fig. 13 shows the difference between the two techniques with the previous example. In the case of temporal mapping (Fig. 13 (a)), like the previous illustration of loop pipelining in Fig. 12 (d), a PE executes multiple operations within a loop by changing the configuration dynamically. Therefore, complex loops having many operations with heavy data dependencies can be mapped better in temporal fashion, provided that the configuration cache has sufficient layers to execute the whole loop body.

In the case of spatial mapping, a loop body is spatially mapped onto the reconfigurable array implying that each PE executes a fixed operation with static configuration as shown in Fig. 13 (b). The advantage of spatial mapping is that it may not need reconfiguration during execution of a loop. As can be seen from Fig. 13, spatial mapping needs only one or two cache layers whereas temporal mapping needs 4 cache layers. One disadvantage of spatial mapping is that spreading all the operations of the loop body over the limited reconfigurable array may require too many resources. Moreover, data dependencies between the operations should be taken care of by allocating interconnect resources to provide a path and inserting registers (or using PEs) in the path to synchronize the arrival of operands. Therefore, if the loop is simple enough to map the loop body to the limited reconfigurable array and there is not much data dependency between the operations, then spatial mapping is the right choice. The effectiveness of the mapping strategies depends on the characteristics of the target architecture as well as the target

**Cycle Time** 5 6 Cycle Time 3 6 LD/+ ×/ST NOP NOP NOP Column#1 × 1+ 2+ LD/+ LD/+ LD/+ LD/ŧ ×/ST k/ST ×/ST ×/st Column#1 Column#2 LD/+ × 2+ Column#2 × NOP NOP NOP Column#3 LD/+ 1+ 2+ ×/ST NOP Column#3 1+ 1+ 1+ 1+ NOP NOP Column#4 LD/+ × 2+ ×/ST 1+ Column#4 2+ **Distributed Cache with 5 Layers** Distributed Cache with 1 or 2 layers ×/ST ×/ST 2+ LD/+ 1+ 1+ NOP × NOP NOP × × LD/+ LD/+ LD/+ NOP NOP NOP NOP-× + + NOP NOP Operation: Operation executed at the 5<sup>th</sup> cycle (a) Temporal mapping (b) Spatial mapping

application.

Fig. 13. Comparison between temporal mapping and spatial mapping.

## B. Individual Approaches to Reduce Power in Configuration Cache

In this section, we suggest individual power-conscious approaches for two different execution models (spatial mapping and temporal mapping) and describe their limitations. These approaches achieve the goal by making use of the characteristics of spatial mapping and temporal mapping [52][53][54].

# 1. Spatial Mapping with Context Reuse

Because most power consumption in the configuration cache is due to memory readoperations, one of the most effective ways to achieve power reduction in the configurati-

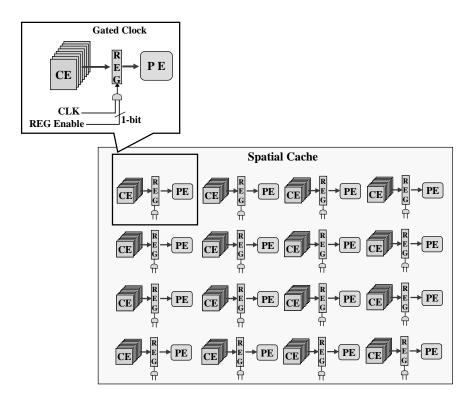

Fig. 14. Configuration cache structure for context reuse.

on cache is to reduce the frequency of read operations.

Even though temporal mapping is more efficient in mapping complex loops onto the reconfigurable array, it requires many configuration data layers for each PE and performs power consuming read-operations in every cycle. On the other hand, spatial mapping does not need to read a new context word from the cache every cycle because each PE executes a fixed operation within a loop. As shown in Fig. 14, if a context register between a CE and a PE is implemented by a gated clock, one spatial cache<sup>1</sup> read-operation is enough in spatial mapping to configure PEs for static operations with fixed output of the context register caused by non-oscillated clock. In summary, spatial mapping with context reuse is more efficient than temporal mapping from the viewpoint of power consumption in configuration cache. However, all kinds of loops cannot be spatially mapped because of the limitation of the spatial mapping. Moreover, if we consider performance alone, temporal mapping is a better choice for loops having long and complex loop body. In the next subsection, we propose a new cache structure and mapping technique that reduce power consumption while retaining the merits of temporal mapping.

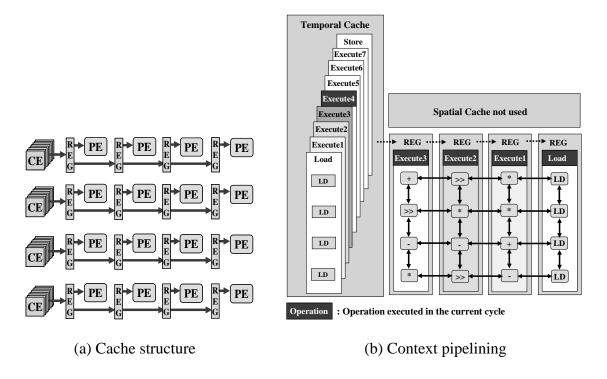

# 2. Temporal Mapping with Context Pipelining

As shown in Fig. 13 (a), in temporal mapping with loop pipelining, operations flow column by column from left to right. In Fig. 13 (a) for example, the first column executes 'LD/+' in the first cycle and then in the second cycle, the second column executes 'LD/+' while the first column executes '×'. In temporal mapping, there is no need for a PE to have a CE. Instead, only PEs in the first column have CEs and the context word can be fetched from the left neighboring column. By organizing a pipelined cache structure as shown in Fig 15, we can propagate the context words column by column through the pipeline. In this way, we can remove most of the CEs from the array keeping temporal

<sup>&</sup>lt;sup>1</sup> We use the term 'spatial cache'. Spatial cache is connected to context registers implemented by gated clock. 'spatial' means that such configuration cache is used for spatial mapping with context reuse. This naming is to differentiate spatial cache from general configuration cache.

cache<sup>2</sup>, thereby saving power consumption without any performance degradation. In summary, temporal mapping with context pipelining can efficiently support long and complex loops reducing power consumption in configuration cache. However, temporal mapping with context pipelining still needs cache-read operations for providing context words to the first column of PE array whereas spatial mapping with context reuse can remove cache-read operation after initial cache-read operation.

Fig. 15. Cache structure for context pipelining.

#### 3. Limitation of Individual Approaches

As mentioned in previous section, even though individual low power techniques provide

<sup>&</sup>lt;sup>2</sup> We use the term 'temporal cache'. Temporal cache is composed of the cache elements connected to the PEs in the first column. 'temporal' means that such CEs are used for temporal mapping with context pipelining. This naming is to differentiate temporal cache from general configuration cache and spatial cache.

solution to reduce power consumption for spatial mapping and temporal mapping, each case has both advantage and disadvantage. Spatial mapping with context reuse only need one cache-read operation for initialization but it can not support the complex loops that cannot be spatially mapped. However, temporal mapping with context pipelining support such complex loops but cache-read operations still remain in context pipelining for the running time. Therefore we should consider the trade-off between performance and power while deploying these techniques.

We can consider two ways to close the gap between spatial mapping and temporal mapping. One is to implement more complex architecture to support high performance spatial mapping by adding additional interconnections or global register files for data dependency. However, in this case the area cost and mapping complexities will increase. Another way is to implement low power temporal mapping taking advantage of spatial mapping with negligible over-head. However, the problem is how to implement this method. In the next section, we propose new technique to guarantee the advantage of spatial mapping and temporal mapping. This is achieved by merging the concept of context reuse into context pipelining.

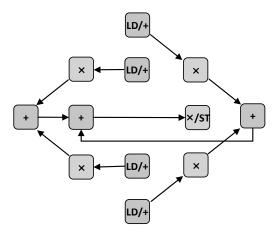

## C. Integrated Approach to Reduce Power in Configuration Cache

Filling the gap between two mappings means that context pipelining is executed by reusable context words. However, it means conjunction of two mappings that are contrary to each other. This is because spatial mapping with context reuse requires spatially static position of each context whereas temporal mapping with context pipelining is performed with temporally changed context words. To solve this contradiction, we propose to add

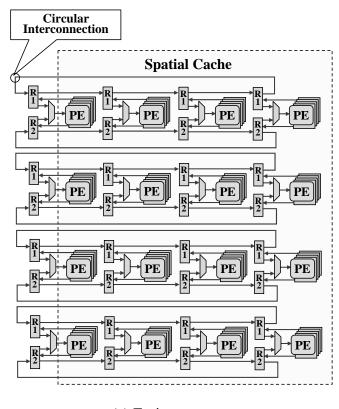

circular interconnection between the first PE and the last PE in the same row and suggest a reusable context pipelining using this interconnection.

# 1. Reusable Context Pipelining

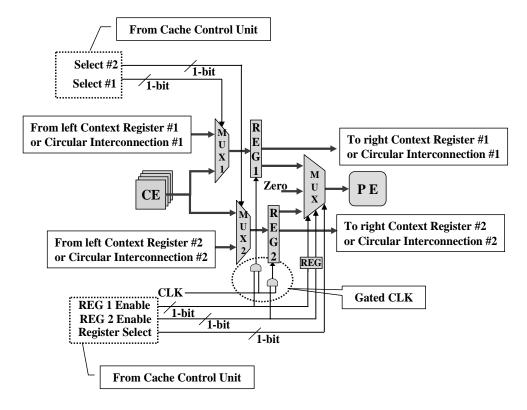

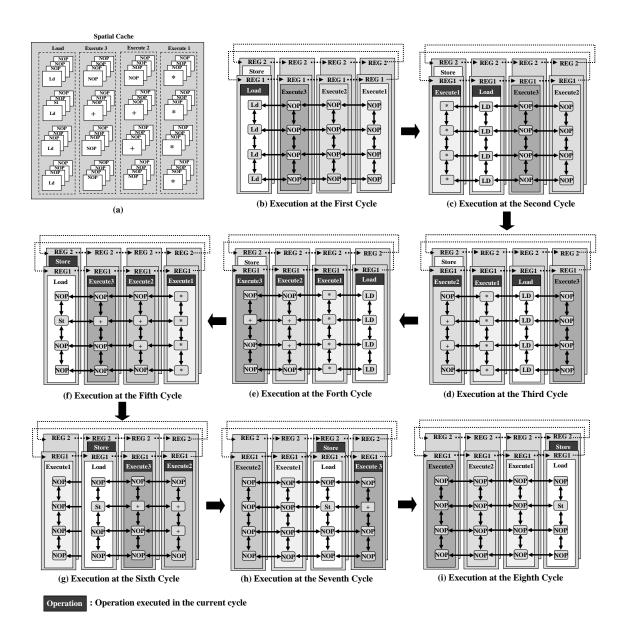

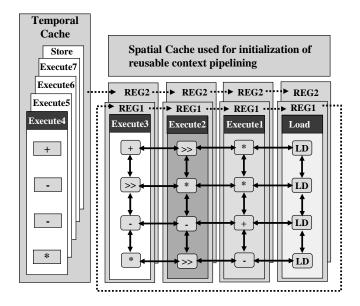

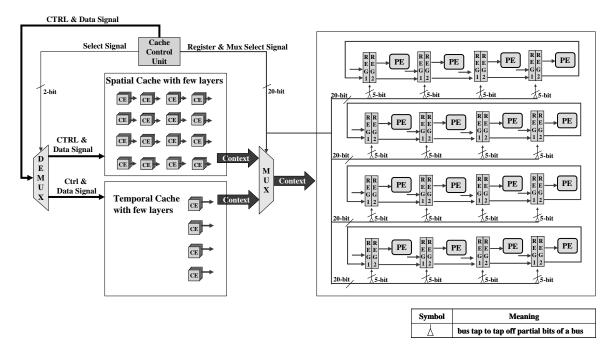

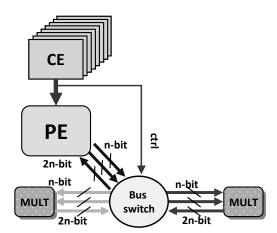

Reusable context pipelining (RCP) means that reusable context words in spatial cache are pipelined through context registers as context pipelining. Fig. 16 (a) depicts the proposed configuration cache structure for RCP. Even though it is similar to the structure of Fig. 14 (spatial mapping with context reuse), the new one has two context registers ('R1' and 'R2') connected to each PE, circular interconnections and less cache layers whereas the original model had one context register and more cache layers.

(a) Entire structure

Fig. 16. Proposed configuration cache structure.

(b) Connection between a CE and a PE

Fig. 16. Continued.

The circular interconnections and the context registers are necessary for pipelining of reusable context words from spatial cache. Fig. 16 (b) shows the detailed structure between a CE and a PE for RCP. A multiplexer ('MUX') is added between context registers ('REG1' and 'REG2') and PE for selecting one of the context registers or 'Zero'. Each context register is connected to each multiplexer ('MUX 1' or 'MUX 2') having two inputs: context word from left context register and context word from spatial cache. The input from spatial cache is for loading a reusable context word to the context register and the input from left context register is for pipelining execution of the loaded con-

text word in left context register. Each select signal ('Select #1' or 'Select #2') connects one from two inputs to the single output connected with right context registers. Each context register is implemented by gated clock for holding the output as well as reducing the wasteful power consumption. All of the select-signals of the multiplexers are generated by cache control unit.