## POWER SUPPLY NOISE IN DELAY TESTING

A Dissertation

by

JING WANG

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

August 2007

Major Subject: Computer Engineering

### POWER SUPPLY NOISE IN DELAY TESTING

A Dissertation

by

JING WANG

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Duncan M. Walker Committee Members, Rabinarayan Mahapatra

> Vivek Sarin Weiping Shi

Head of Department, Valerie E. Taylor

August 2007

Major Subject: Computer Engineering

#### **ABSTRACT**

Power Supply Noise in Delay Testing.

(August 2007)

Jing Wang, B.S., Zhejiang University, China

Chair of Advisory Committee: Dr. Duncan M. Walker

As technology scales into the Deep Sub-Micron (DSM) regime, circuit designs have

become more and more sensitive to power supply noise. Excessive noise can significantly

affect the timing performance of DSM designs and cause non-trivial additional delay. In

delay test generation, test compaction and test fill techniques can produce excessive power

supply noise. This will eventually result in delay test overkill.

To reduce this overkill, we propose a low-cost pattern-dependent approach to analyze

noise-induced delay variation for each delay test pattern applied to the design. Two noise

models have been proposed to address array bond and wire bond power supply networks,

and they are experimentally validated and compared. Delay model is then applied to

calculate path delay under noise. This analysis approach can be integrated into static test

compaction or test fill tools to control supply noise level of delay tests. We also propose

an algorithm to predict transition count of a circuit, which can be applied to control

switching activity during dynamic compaction.

Experiments have been performed on ISCAS89 benchmark circuits. Results show that

compacted delay test patterns generated by our compaction tool can meet a moderate

noise or delay constraint with only a small increase in compacted test set size. Take the

benchmark circuit s38417 for example: a 10% delay increase constraint only results in 1.6% increase in compacted test set size in our experiments. In addition, different test fill techniques have a significant impact on path delay. In our work, a test fill tool with supply noise analysis has been developed to compare several test fill techniques, and results show that the test fill strategy significant affect switching activity, power supply noise and delay. For instance, patterns with minimum transition fill produce less noise-induced delay than random fill. Silicon results also show that test patterns filled in different ways can cause as much as 14% delay variation on target paths. In conclusion, we must take noise into consideration when delay test patterns are generated.

## **DEDICATION**

# To my parents:

without their support, this would not have been possible.

#### **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to my advisor, Dr. Duncan M. (Hank) Walker, for his guidance, patience and continuous support throughout my doctoral study. I highly appreciate his contributions to my intellectual and personal development in the past five years. I would also like to thank him for guiding me in my dissertation research with such dedication and consideration, and never failing to pay attention to any details of my work. His technical insight, his novel ideas and his encouragement are all essential to this work. This dissertation would never have been accomplished without his technical and editorial advice.

I would like to extend my gratefulness to my committee: Dr. Weiping Shi, Dr. Vivek Sarin and Dr. Rabinarayan Mahapatra. They provided a lot of valuable suggestions and personal encouragement, and I learned a lot from talking to them.

A special thanks to Dr. Shi and his student Xiang Lu for their contributions to my modeling theories and to the experiment set-ups. I highly appreciate the time and effort Xiang spent in generating circuit layouts and in executing circuit simulations. He helped me pave a path through bushes during my early stage of research.

My gratitude also goes to my industry mentors and colleagues in the former Philips Research Lab, which now becomes part of NXP Semiconductors. Dr. Ananta Majhi supervised me during my internship in Philips, and he worked together with me on every problem in my research and paid attention to every detail in the work. Dr. Bram Kruseman helped me collect silicon data on a Philips design and edited our publications. Guido Gronthoud taught me to use tools for carrying out experiments. Paul van de Wiel spent

quite some time in discussion with me and provided solutions to a critical problem in my research. Dr. Stefan Eichenberger and Luis Elvira Villagra gave me a lot of insight comments on the research. I had a wonderful internship experience working with all my colleagues there, and I also very much enjoyed my stay in this beautiful country.

Thanks to my teammates Wangqi Qiu, Bin Xue, Sagar Sabade, Abhijit Prasad, Lei Wu and Ziding Yue. I learned a lot from them in the past several years. Especially I want to thank Wangqi Qiu for his help and advice on my research. He gave me many valuable suggestions when I made a decision on the research topic. Another special thanks goes to Ziding Yue for her important contribution to the experiment part of my research.

My research was funded by Semiconductor Research Corporation (SRC) and National Science Foundation (NSF). I thank these sponsors for providing financial support.

Finally, I want to acknowledge the love and support of my parents. They were always there for me whenever I had problems, and they always shared my happiness for every progress I made. I'm deeply indebted to them, more than my words can ever express.

## TABLE OF CONTENTS

|     |      |                                           | Page |

|-----|------|-------------------------------------------|------|

| 1.  | INT  | RODUCTION                                 | 1    |

| 2.  | BAC  | CKGROUND AND PRIOR WORK                   | 7    |

|     | 2.1  | Noise                                     | 7    |

|     | 2.2  | Power Supply Noise                        | 10   |

|     | 2.3  | Delay Testing                             | 16   |

|     | 2.4  | Power Supply Noise in Delay Testing       | 17   |

| 3.  | POV  | VER SUPPLY NOISE ANALYSIS                 | 20   |

|     | 3.1  | Noise Model I                             | 21   |

|     | 3.2  | Noise Model II                            | 26   |

|     | 3.3  | Model Comparison in Model Application     |      |

|     | 3.4  | Discussion on Off-chip Current Modeling   |      |

|     | 3.5  | Switching Models                          | 40   |

|     | 3.6  | Delay Models                              | 43   |

| 4.  | COM  | MPACTION AND FILLING STRATEGIES           | 47   |

|     | 4.1  | Basics of Compaction                      | 47   |

|     | 4.2  | Noise Consideration in Static Compaction  | 48   |

|     | 4.3  | Noise Consideration in Dynamic Compaction | 54   |

|     | 4.4  | Test Fill                                 | 67   |

| 5.  | EXP  | PERIMENTS                                 | 69   |

|     | 5.1  | Experiments on ISCAS Benchmark Circuits   | 69   |

|     | 5.2  | Experiments on an Industrial Design       | 103  |

|     | 5.3  | Comparison of the Noise Models            | 115  |

| 6.  | SUM  | MMARY AND FUTURE WORK                     | 116  |

| REF | EREN | ICES                                      | 118  |

| VIT | Λ    |                                           | 132  |

## LIST OF FIGURES

|            |                                                                          | Page |

|------------|--------------------------------------------------------------------------|------|

| Figure 1.  | On-chip frequency in the near-term years                                 | 2    |

| Figure 2.  | Transistor density in the near-term years.                               | 2    |

| Figure 3.  | Power density in the near-term years.                                    | 3    |

| Figure 4.  | Power supply voltage in the near-term years.                             | 4    |

| Figure 5.  | A region in an array bond chip                                           | 22   |

| Figure 6.  | Supply noise model within a region (Noise Model I)                       | 25   |

| Figure 7.  | Power noise analysis procedure.                                          | 26   |

| Figure 8.  | An anualar-shaped metal board                                            | 28   |

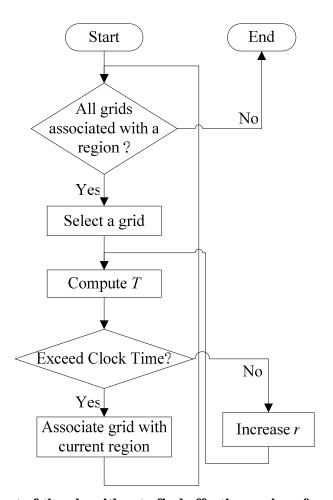

| Figure 9.  | Flowchart of the algorithm to find effective regions for all devices     | 30   |

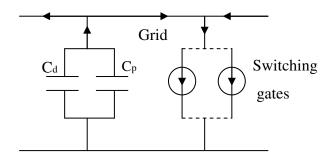

| Figure 10. | Supply noise model within a grid (Noise Model II).                       | 33   |

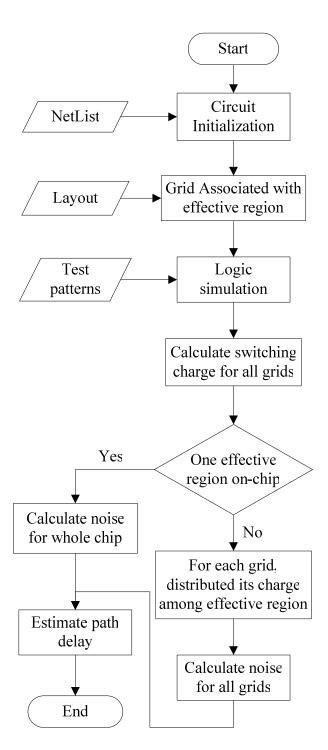

| Figure 11. | Flow chart for power supply noise analysis.                              | 35   |

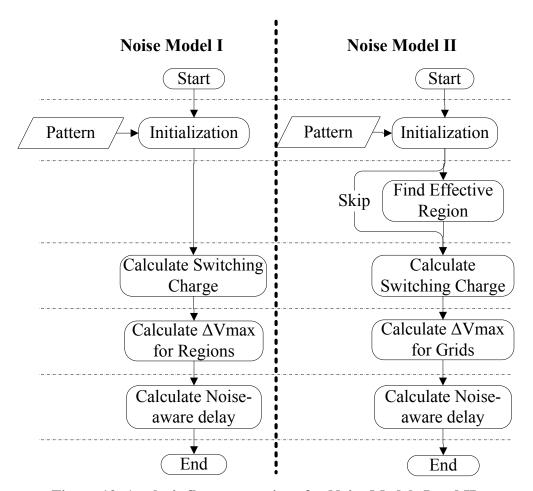

| Figure 12. | Analysis flow comparison for Noise Models I and II.                      | 36   |

| Figure 13. | Charging/discharging current waveform for an inverter                    | 41   |

| Figure 14. | Switching current model of dynamic charging current for CMOS devices     | 42   |

| Figure 15. | Flow chart of compaction using greedy algorithm (w/o noise constraints)  | 50   |

| Figure 16. | Flow chart of compaction with noise constraints                          | 54   |

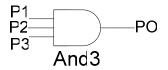

| Figure 17. | A 2-input AND gate.                                                      | 57   |

| Figure 18. | A 3-input AND gate.                                                      | 58   |

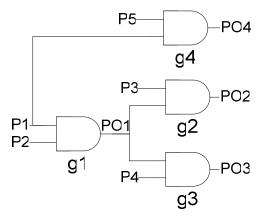

| Figure 19. | A circuit for analysis.                                                  | 60   |

| Figure 20. | Pre-compaction analysis of the circuit to compute the average transition |      |

|            | count given a transition on each circuit input                           | 62   |

|                                                                                    | Page |

|------------------------------------------------------------------------------------|------|

| Figure 21. A circuit with fan-in.                                                  | 62   |

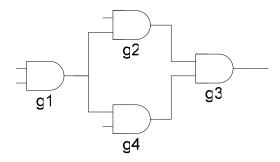

| Figure 22. Circuit transition count prediction algorithm                           | 66   |

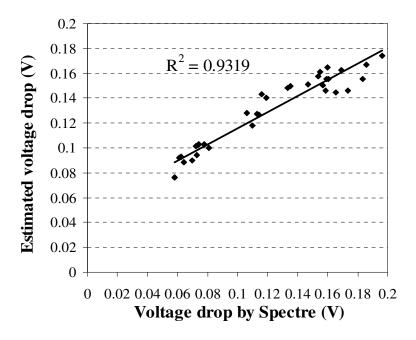

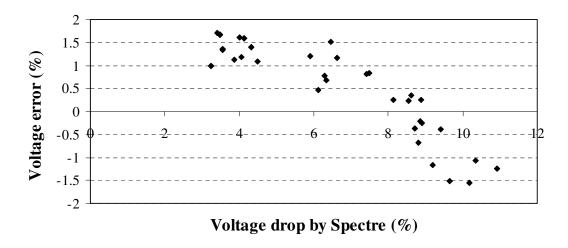

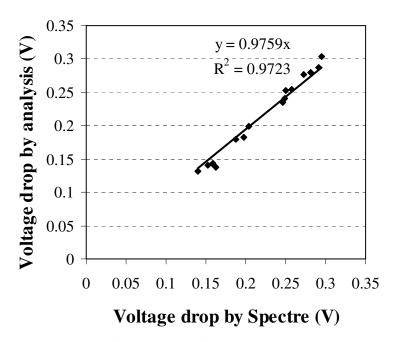

| Figure 23. Correlation of voltage drop on s1488.                                   | 73   |

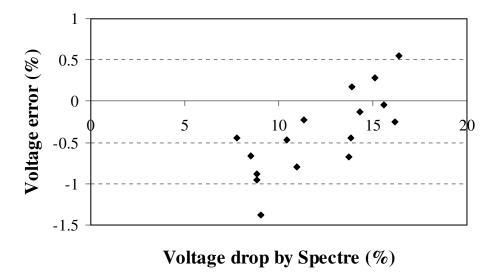

| Figure 24. Voltage error of s1488.                                                 | 73   |

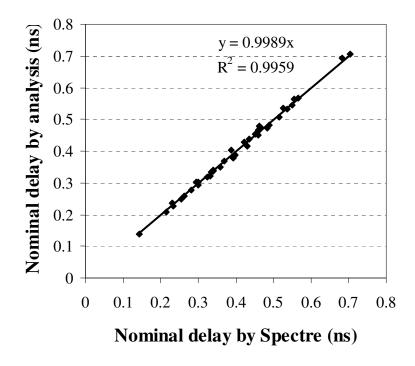

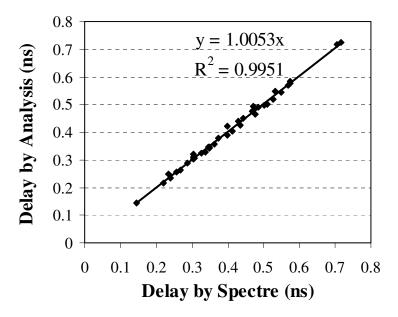

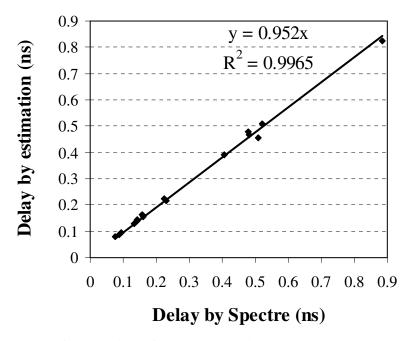

| Figure 25. Correlation of nominal path delay for circuit s1488                     | 74   |

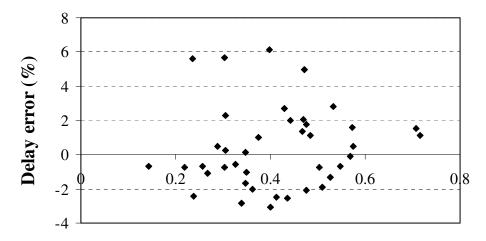

| Figure 26. Nominal delay error of s1488.                                           | 75   |

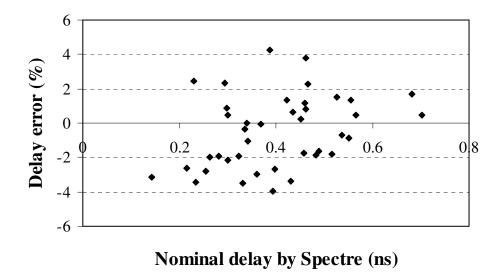

| Figure 27. Correlation of path delay with supply noise on s1488                    | 76   |

| Figure 28. Delay error of noise-induced delay of s1488.                            | 77   |

| Figure 29. Correlation of voltage drop on s38417.                                  | 78   |

| Figure 30. Voltage error for circuit s38417                                        | 79   |

| Figure 31. Correlation of path delay with supply noise on s38417                   | 80   |

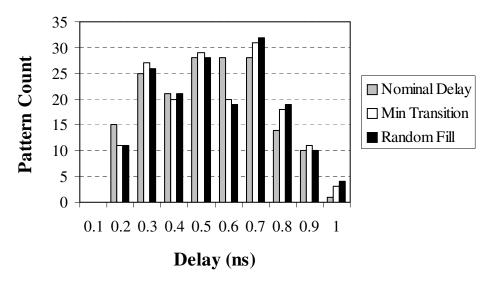

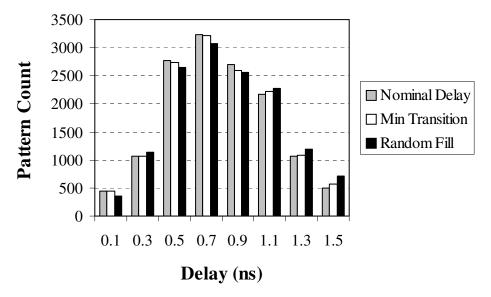

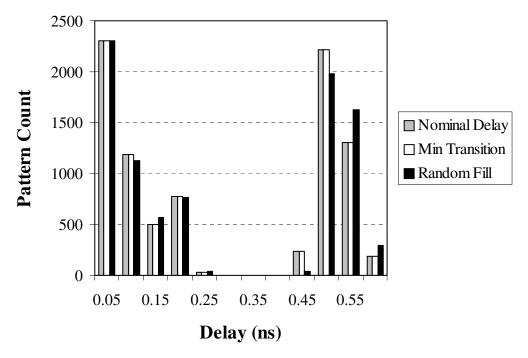

| Figure 32. Delay histogram with minimum transition fill and random fill on s1488   | 89   |

| Figure 33. Delay histogram with minimum transition fill and random fill on s38417. | 89   |

| Figure 34. Delay histogram with minimum transition fill and random fill on s35932. | 90   |

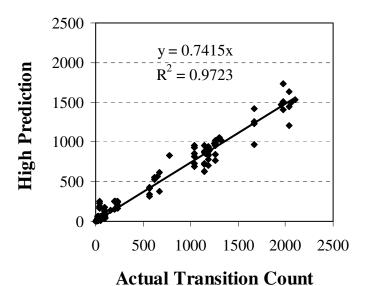

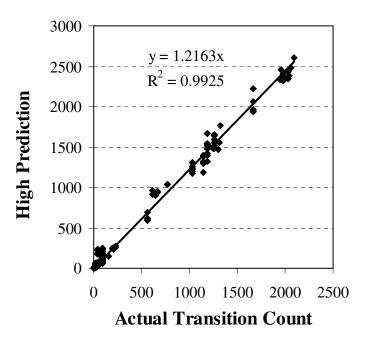

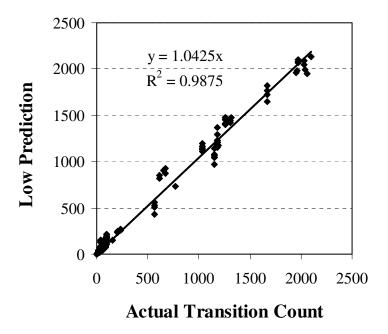

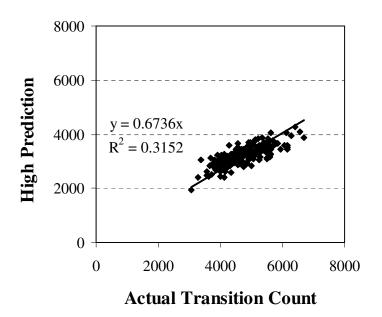

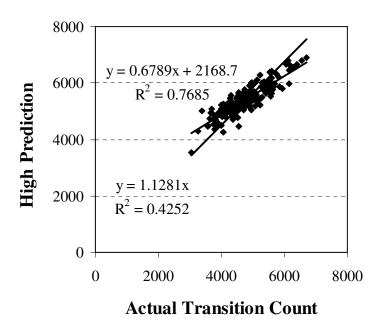

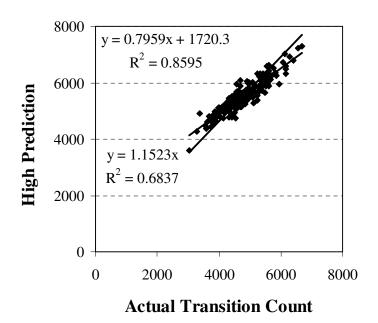

| Figure 35. High prediction vs. actual transition count on circuit s38417 with 1%   |      |

| signal values, using static uncompacted test set.                                  | 94   |

| Figure 36. High prediction vs. actual transition count on circuit s38417 with 5%   |      |

| signal values, using static uncompacted test set.                                  | 95   |

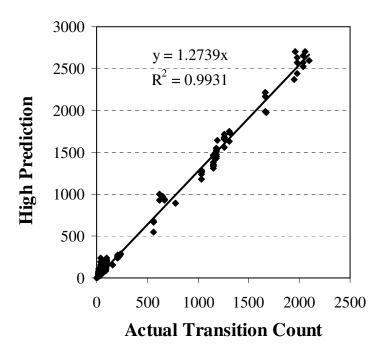

| Figure 37. High prediction vs. actual transition count on circuit s38417 with 10%  |      |

| signal values, using static uncompacted test set.                                  | 95   |

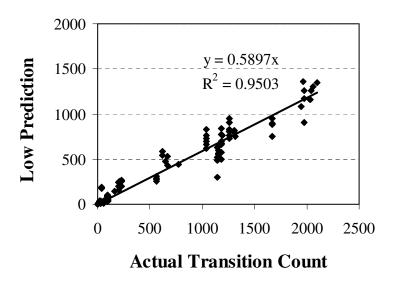

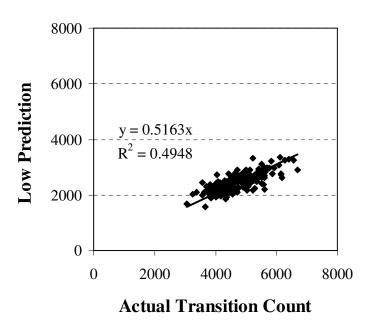

| Figure 38. Low prediction vs. actual transition count on circuit s38417 with 1%    |      |

| signal values, using static uncompacted test set                                   | 97   |

|                                                                                    | Page |

|------------------------------------------------------------------------------------|------|

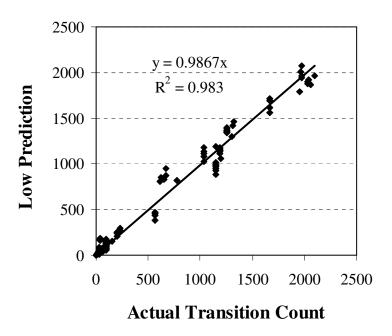

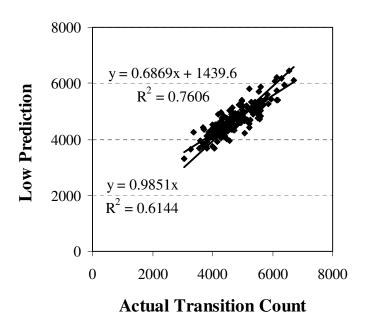

| Figure 39. Low prediction vs. actual transition count on circuit s38417 with 5%    |      |

| signal values, using static uncompacted test set.                                  | 97   |

| Figure 40. Low prediction vs. actual transition count on circuit s38417 with 10%   |      |

| signal values, using static uncompacted test set.                                  | 98   |

| Figure 41. High prediction vs. actual transition count on circuit s38417 with 1%   |      |

| signal values, using static compacted test set.                                    | 100  |

| Figure 42. High prediction vs. actual transition count on circuit s38417 with 5%   |      |

| signal values, using static compacted test set.                                    | 100  |

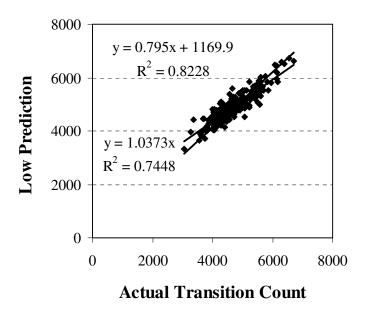

| Figure 43. High prediction vs. actual transition count on circuit s38417 with 10%. |      |

| signal values, using static compacted test set.                                    | 101  |

| Figure 44. Low prediction vs. actual transition count on circuit s38417 with 1%    |      |

| signal values, using static compacted test set.                                    | 101  |

| Figure 45. Low prediction vs. actual transition count on circuit s38417 with 5%    |      |

| signal values, using static compacted test set.                                    | 102  |

| Figure 46. Low prediction vs. actual transition count on circuit s38417 with 10%   |      |

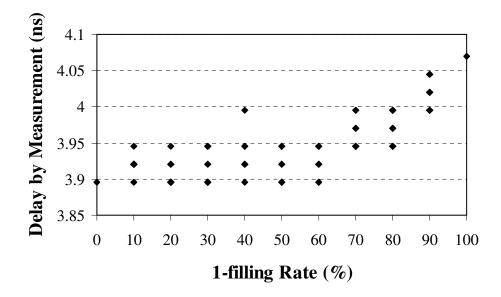

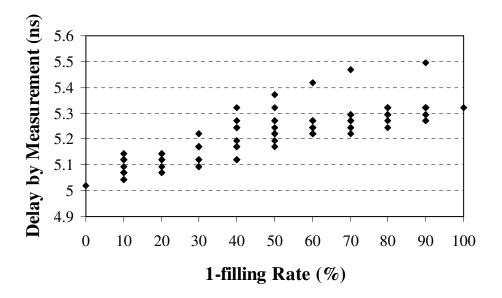

| signal values, using static compacted test set.                                    | 102  |

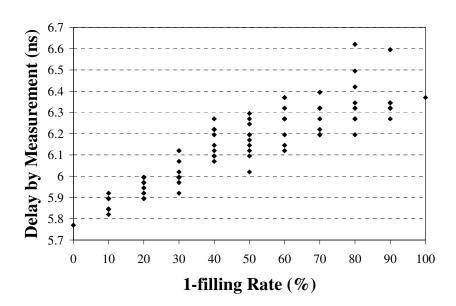

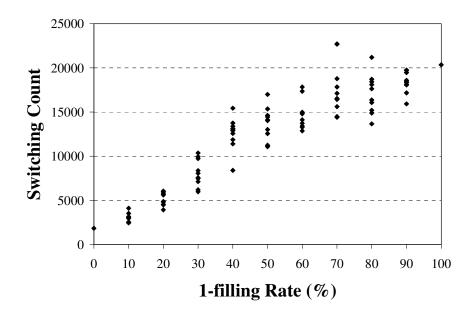

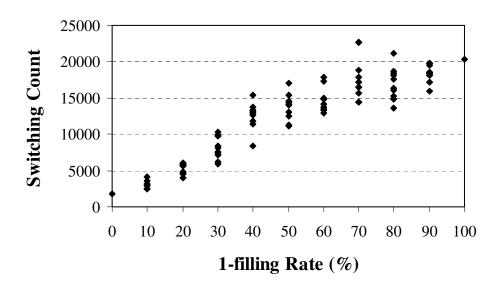

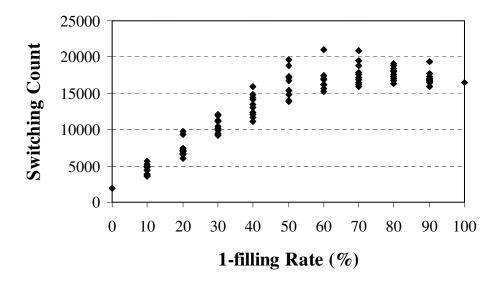

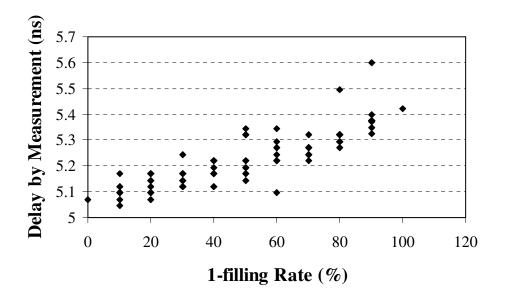

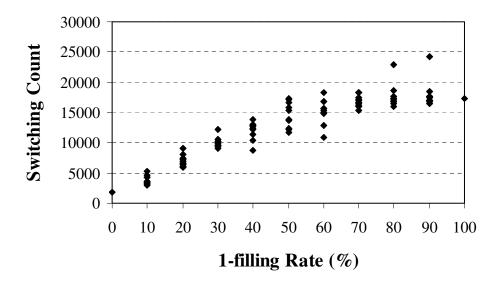

| Figure 47. Measured path delay vs. 1-filling rate for set 2                        | 105  |

| Figure 48. Switching count vs. 1-filling rate for set 2.                           | 107  |

| Figure 49. Measured path delay vs. 1-filling rate for set 1                        | 108  |

| Figure 50. Switching count vs. 1-filling rate for set 1.                           | 108  |

| Figure 51. Measured path delay vs. 1-filling rate for set 3                        | 109  |

| Figure 52. Switching count vs. 1-filling rate for set 3.                           | 109  |

|                                                                               | Page |

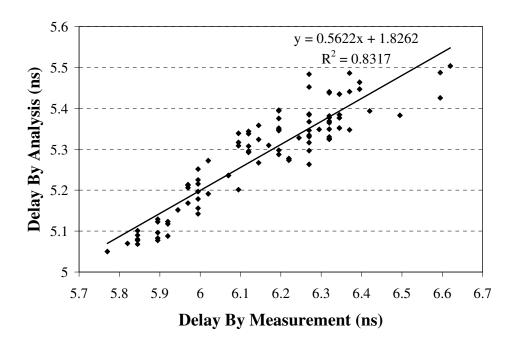

|-------------------------------------------------------------------------------|------|

| Figure 53. Measured path delay vs. 1-filling rate for set 4                   | 110  |

| Figure 54. Switching count vs. 1-filling rate for set 4.                      | 110  |

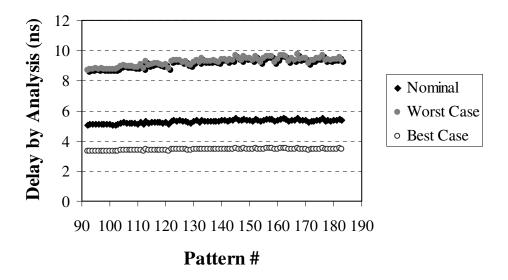

| Figure 55. Tester delay vs. timing analysis delay for set 2.                  | 111  |

| Figure 56. Nominal and noise induced delay by analysis, and measured delay be |      |

| tester for the same test set.                                                 | 112  |

| Figure 57. Tester delay vs. timing analysis delay for set 3.                  | 113  |

| Figure 58. Tester delay vs. timing analysis delay for set 4.                  | 113  |

| Figure 59. Tester delay vs. timing analysis delay for set 1.                  | 114  |

| Figure 60. Delay variation under different operating conditions for set 2     | 115  |

## LIST OF TABLES

| Page                                                                                        |

|---------------------------------------------------------------------------------------------|

| Table 1. Compaction operation of two bit vectors                                            |

| Table 2. Compaction results for greedy algorithms and simulated annealing51                 |

| Table 3. Transition probability and expectation for logic gates                             |

| Table 4. Compaction results for s38417 with worst-case voltage drop constraint (The         |

| fill-rate of the un-compacted test set is $2.5\%$ , with ucs = $13941$ and s = $940$ ) $83$ |

| Table 5. Compaction running time for s38417 with worst-case voltage drop constraint84       |

| Table 6. Compaction results for s38417 with max path delay increase constraint (The         |

| fill-rate of the un-compacted test set is $2.5\%$ , with ucs = $13941$ and s = $940$ ) 85   |

| Table 7. Compaction running time for s38417 with max path delay increase constraint86       |

| Table 8. Compaction results for s38417 when decoupling capacitance varies with              |

| worst-case voltage drop constrained at 10% (The fill-rate of the                            |

| un-compacted test set is $2.5\%$ , with ucs = $13941$ and s = $940$ )                       |

| Table 9. Compaction running time for s38417 when decoupling capacitance varies              |

| with worst-case voltage drop constrained at 10%                                             |

#### 1. INTRODUCTION

As technology advances into the deep submicron (DSM) regime, designs are becoming increasingly sensitive to power supply noise. Excessive noise can cause performance degradation and signal integrity problems. Moreover, it can significantly affect the timing performance of DSM designs.

Power supply noise refers to the noise on the supply and ground network, which reduces device voltage levels and increases signal delay. As operating frequency and gate density increase, power density increases as well. Meanwhile, DSM CMOS technologies require the use of reduced supply voltages. These technology trends have led to higher current density, and consequently increased power supply noise.

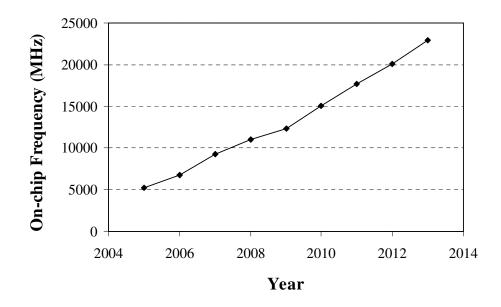

Data from the International Technology Roadmap for Semiconductors (ITRS) report [1], is projected in the following four figures. Figure 1 shows the on-chip operating frequency data based on the fundamental transistor delay and an assumed maximum number of 12 inverter delays beginning 2007; after 2007, the fundamental reduction rate is modeled as ~ -14.7% for the transistor delay and results in a ~17.2% growth trend of the on-chip frequency through 2020.

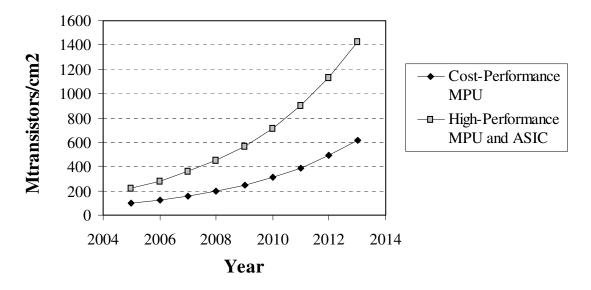

Figure 2 plots transistor density data for cost-performance MPU and highperformance MPU and ASIC product generations in the unit of million transistors per square centimeter. The transistor density for Cost-Performance MPU includes logic

This dissertation follows the style and format of *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*.

only, while the transistor density for high-performance MPU includes on-chip SRAM as well. Both increase exponentially with time.

Figure 1. On-chip frequency in the near-term years.

Figure 2. Transistor density in the near-term years.

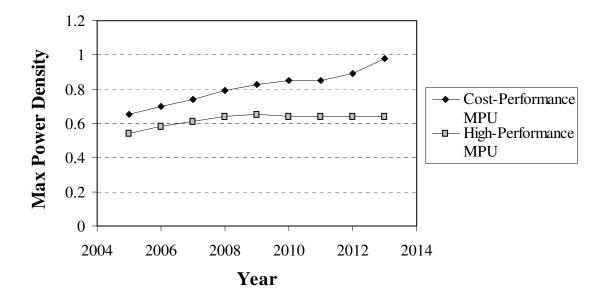

Figure 3 shows the increase in maximum power density for both cost-performance and high-performance MPU products for maximum power calculation. We can see that the maximum power density for high-performance MPU products will become stable after year 2008. However, the power density for cost-performance MPU products keeps increasing, and will continue to increase after year 2013, which is not shown here.

Figure 3. Power density in the near-term years.

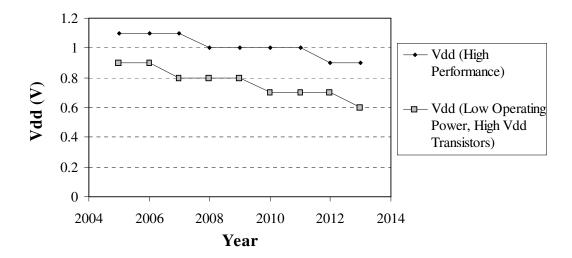

Figure 4 shows the decreasing supply voltage level for both high-performance and low-power designs.

All the technology trends illustrated in Figure 1 to Figure 4 imply a higher supply noise as technology advances. Furthermore, industry data shows gate delay becoming increasingly sensitive to supply voltage variations due to reduced gate overdrive. In 130 nm CMOS technology, a 10% variation in supply voltage causes a 30% delay variation for typical gates [2]. In 90 nm 0.9 V technology, a 1% voltage change causes

approximately a 4% change in gate delay [3]. This increased sensitivity contributes to a larger power noise impact on delay.

Figure 4. Power supply voltage in the near-term years.

At-speed delay test has been investigated for many years to detect small manufacturing defects that do not cause functional failures, but reduce the speed of circuits. As the noise impact on delay becomes more and more significant, it also inevitably becomes a concern for delay test generation.

In industry, random fill of don't care bits is usually applied to delay test patterns to increase fortuitous detection of non-target defects. Unfortunately, random fill can produce excessive supply noise and result in delay test overkill. Worse, test compaction itself can generate excessive supply noise. Both test fill and test compaction are necessary steps in delay test generation. Therefore, the goal of this work is to provide an approach that can be integrated into test fill and test compaction tools to prevent

excessive power supply noise in delay tests and reduce noise-induced overkill.

In this dissertation, we propose a low-cost, vector-dependent modeling approach to analyze power supply noise and noise-induced delay. Two noise models are proposed to address circuits with array bond and wire bond package. This approach is then integrated into test fill and static compaction to control the supply noise level. In addition, we also propose a heuristic to estimate circuit transition count, which can be used to constrain noise during dynamic compaction.

Section 2 provides background and related work on various sources of noise. It particularly addresses power supply noise and lists all prior work in supply noise suppression, noise measurement and analysis. It also includes previous studies in delay variation with supply noise. Then, delay testing is briefly introduced including basic fault models and at-speed testing approaches. The last section lists a number of previous publications in delay testing addressing power supply noise, though they target different problems.

Section 3 introduces two power supply noise models for layout-aware noise analysis. Our noise models avoid complicated power network analysis, which significantly speeds up the supply noise analysis procedure. The two noise models are proposed to address array bond chips and wire bond chips, respectively. These two models are then compared in model application. Discussions on modeling off-chip current are also included.

Section 4 introduces algorithms for noise constrained static compaction based on the power supply noise analysis introduced in Section 3. It also includes a heuristic to

predict transition count based on partial assignment of input patterns, which can help control switching activity during dynamic compaction. Different test fill approaches are introduced, which are implemented in the experiments to show how delay varies with different test fill approaches.

Section 5 describes the experimental results. The experiments have been performed on both ISCAS benchmark circuits as well as an industrial design. First, all experimental data collected on ISCAS benchmark circuits is presented. It includes validation data of one noise model, noise constrained static compaction results that show how compacted test set size change with noise constraint, test fill data that show delay variation with test fill approaches, and transition count prediction results to address its efficiency in estimating switching activity. Then data on an industrial design is presented to show delay variation with different test fill and validation for the second noise model. The validation results of the two models are compared.

The last section gives conclusions and directions for future work.

#### 2. BACKGROUND AND PRIOR WORK

#### 2.1 Noise

Noise is inevitable in all electronic circuits. For decades, noise has always been of special interest to solid-state circuit designers and material scientists in the area of analog circuit design, where the noise generally comes from random motion of electrons in a resistive material, or the random recombination of holes and electrons in a semiconductor, or when holes and electrons diffuse through a potential barrier [4]. Typical types of noise considered in analog circuits are thermal noise, shot noise, flicker noise and burst noise [5].

In contrast to analog circuits, digital circuits are inherently immune to these noise problems through the use of high-gain logic gates, which restore logic values via nonlinear voltage transfer characteristics and significantly reduce the analog noise impact [6] [7]. However, the high gain of digital circuits has its own weakness and can result in much greater noise sources.

Noise in digital circuits first appeared as a problem in mixed digital-analog Integrated Circuits (IC) domain where noisy digital circuits strongly affect analog circuits [7] [8]. In the past decade, as technology scaled into the deep submicron (DSM) regime, digital circuits have also become more and more sensitive to noise, though the noise sources perceived in digital systems are quite different from the analog domain. As a consequence, noise analysis has become a critical concern for submicron digital circuit design.

For the purpose of noise analysis, noise can be roughly classified into two categories: functional and delay noise [9]. Functional noise causes performance degradation and signal integrity problems [10] [11]. If noise is of sufficient magnitude and can be propagated to a storage cell, such as a latch or a flip-flop, it can change the state of the circuit and cause functional failure. The goal of analysis of circuit behavior in the presence of functional noise is to verify that every signal line retains correct "1" or "0" values. Delay noise impacts the switching devices during signal transitions, thus changes the delay of the signal and affects the timing performance of the design [7] [12].

Noise can also be classified based on the noise source. There are various noise sources in digital systems [7]. The most relevant sources are:

- Leakage Noise

- Subthreshold Leakage

- Gate Leakage

- o Band-to-band Tunneling Leakage

- Charge-Sharing Noise

- Crosstalk Noise

- Power Supply Noise

There are several leakage mechanisms in the nanometer regime [13]. Three dominant components are: subthreshold leakage, gate tunneling leakage and reverse biased drain-substrate and source-substrate junction Band-To-Band-Tunneling (BTBT) leakage. Subthreshold leakage is the leakage current from drain to source. It increases exponentially with the scaling of threshold voltage. Gate tunneling leakage is the leakage current due

to the tunneling of electrons or holes between the bulk silicon and the gate through the gate oxide potential barrier. As the oxide thickness scales to maintain reasonable Short Channel Effect (SCE) immunity, it also considerably increases direct tunneling current through the gate insulator of the transistor. In scaled devices, BTBT current through the reverse biased drain-substrate and source-substrate junctions also significantly contributes to leakage with higher substrate doping density and the use of "halo" doping profiles. However, the BTBT current can be reduced by SOI technology or other doping profiles. Leakage current has become a critical concern in power dissipation especially for low-power designs, and many leakage reduction techniques have been proposed [14] [15] [16].

The increased use of dynamic circuitry to achieve high speed and small area makes designs more vulnerable to noise problems [17]. Charge sharing is one of the problems that may cause failure in dynamic logic circuits due to their low noise immunity. Charge-sharing noise is produced by charge redistribution between internal nodes of the circuit. Techniques such as dual-rail logic and p-feedback/n-feedback transistors are often used to overcome charge sharing problems [18].

Capacitive coupling is the one of the primary noise sources in digital CMOS VLSI circuits. With technology scaling, signal lines that were once considered isolated can now interact with each other and significantly impact functionality and performance. One such interaction is known as capacitive crosstalk. It comes from parasitic coupling between adjacent signal nets and most likely affects the "victim" nets, the nets that have weaker drivers [19][20]. Capacitive crosstalk can either lead to logic failures, or

significantly increase propagation delay. Many approaches have been proposed to address capacitive coupling noise issues in design and test [21][22].

In additional to all of these noise sources introduced above, there is also power supply noise, which explicitly refers to the noise on the supply and ground network [7]. It is the focus of our work and will be explained in the following section.

### 2.2 Power Supply Noise

Power supply noise is the noise on the supply and ground network, which reduces the actual device voltage levels and increases signal arrival time at the primary outputs and next state lines [7][12].

Power supply noise consists of both DC and sinusoidal content. The DC noise, also termed IR drop, comes from resistive voltage drop due to wire resistance and the average static current demand of the chip [7]. In the case of DC noise, a DC network is built and solved to obtain the average IR drop at each location [23]. The sinusoidal noise, also termed as inductive  $\Delta I$  noise, di/dt noise or simultaneous switching noise, comes from the RLC response of both chip and package due to switching current demands that peak at the beginning of the clock cycle [7]. The IR drop usually occurs on chip, while the inductive  $\Delta I$  noise usually occurs on package. Therefore, these two different power supply noise sources are often treated separately, with different budgets.

In traditional analysis for power supply noise, the on-chip IR drop was the main focus, so most analysis tools modeled the on-chip power grid as a RC network. However, as we move into deep submicron design (DSM), the *di/dt* noise is becoming a

critical concern.

As operating frequency and gate density increase, simultaneous switching activity per unit area increases, which increases power density [3]. Meanwhile, DSM CMOS technologies require the use of reduced supply voltages [24]. Industry data shows that until recently, the power density of high-end microprocessors was increasing by approximately 80% per technology generation, with the voltage scaling by 0.8 [3]. This has led to higher current density, and consequently increased power supply noise. In the long run, *di/dt* noise will become dominant compared with IR drop, as it worsens with both increasing current demand and clock frequency [2]. Moreover, the requirement of cheap packaging, which means lower pin count and larger pin inductance, also causes larger *di/dt* noise [25]. Therefore, the *di/dt* noise is our main concern.

The *di/dt* noise may cause several types of errors in digital systems [25]. First and most important, *di/dt* noise will increase delay [26], especially on critical paths in pipelined circuits, and result in logic timing failures. Other problems includes phase-locked loop (PLL) jitter, which causes either timing errors due to clock skew or synchronization failures between different clock domains; I/O reference level problems; which may cause misinterpretation of input logic level or degrade circuit speed; and dynamic logic problems, since dynamic logic is quite sensitive to power supply noise.

### 2.2.1 Power Supply Noise Suppression

Many semiconductor companies, including AMD [27], IBM [28] and Intel [29], have included noise suppression techniques in their designs. Various techniques have been proposed to reduce power supply noise, *di/dt* noise in particular. Some of the techniques

makes changes to the circuits to generate less noise and improve noise immunity, while others suppress noise without modifying the circuits [25], requiring less time and fewer constraints in the design cycle. A most promising and widely used technique is adding on-chip decoupling capacitance between the power supply and ground.

The decoupling capacitance is usually made much larger than the capacitance of the switching devices, so it dominates power supply noise. A lot of research has been done on decoupling capacitor sizing and placement, either in the post-floorplanning stage or incorporated into floorplanning as a constrained maximum flow problem [30][31][32]. Recent work also proposed improved noise suppression techniques, such as active distributed decoupling capacitors [33] or active resistors in parallel with decoupling capacitors [34].

## 2.2.2 Power Supply Noise Measurement

Power supply noise measurement provides data on the noise occurring in chips. A possible measurement solution is to integrate power supply noise measurement systems on chip to characterize internal signals and noise behavior, which helps designers to improve and verify their designs [35]. These measurement circuits usually target special properties of supply noise, since it is very difficult to get a full time-domain voltage waveform during circuit operation. Muhtaroglu et al. proposed a circuit that targets overshoot and undershoot events [36]. Alton et al. presented a measurement technique to characterize the statistical properties and spectrum of power supply noise [35]. Another class of solutions integrates an online concurrent monitoring scheme to give warnings at the presence of excessive power supply noise, either for circuit diagnosis purposes or for

self-adaptation and correction [37][38]. Such schemes should be distributed across the whole circuit to observe power supply noise at any location and any given time.

### 2.2.3 Power Supply Noise Analysis

As the power supply noise problem becomes critical, the supply noise model is becoming one of the most interesting topics for researchers. An efficient supply noise model will help designers to gain a good knowledge of noise impact on circuit functionality and timing performance, and to improve the consideration of noise in design and test.

Power supply noise modeling and analysis generally is a challenging problem. Early research adopted a cell-based circuit model [39] and estimated power supply noise to calculate average power consumption, or investigated noise problem in a small circuit and scaled to larger designs [40]. However, a comprehensive package/on-chip power supply model usually consists of a number of circuit elements [41]:

- RLC model of package leads, ball grid arrays, power planes

- RC model of on-chip power interconnect

- RC model of intrinsic decoupling capacitance of non-switching devices and N-well regions

- RC model of explicitly designed decoupling capacitance

- Model of AC currents of switching devices

Much work has been proposed to cover the elements listed above. Chen et al. proposed a methodology to analyzed both resistive IR drop and inductive *di/dt* noise based on an integrated package/chip power bus model along with simulated switching

circuit model [11][42]. Power grid network analysis for noise estimation can be found in various other papers [43][44]. Nassif et al. introduced a novel Partial Differential Equation (PDE) related multigrid method for fast power grid simulation [45]. Zhu et al. also proposed a power network analysis method using a multigrid approach [46]. In 2003, Qian et al. proposed a fast and efficient power grid analyzer based on a random walk technique, which can be applied to both DC and transient analysis [47].

Despite these improvements, power network analysis remains an expensive approach, and it worsens with technology scaling. To save computation cost, some previous work adopted simple heuristics to estimate worst-case supply noise, such as switching transition count or sum of switching current [48][49]. These approaches can be used to simulate worst-case power supply noise when an accurate noise value is not required.

## 2.2.4 Delay Variation with Power Supply Noise

The voltage variations in the power supply network can have adverse impact on the timing performance of the circuit, and noise-aware timing analysis is a critical need. In order to develop a noise-aware timing analysis approach, we need to have a noise-sensitive cell delay model, and then integrate it in a comprehensive path delay model.

In general, the delay of a switching logic gate/cell is usually dependent on many factors, including supply voltage level, input voltage level, input slew rate, output capacitive load and other intrinsic design specifications. The sensitivity to supply noise increases as the supply voltage level declines. The rising delay is more sensitive to the voltage drop on the supply network while the falling delay to the ground bounce [48]. Early models usually adopted analytical approaches such that they represented gate

delay as an inverse or linear/quadratic function of the supply voltage [50]. Jiang et al. proposed a statistical approach to characterize delay [12]. Standard cell delay is treated as a perturbed random variable, and the probability distribution functions (PDF) are derived by simulating a set of characterization patterns. Look-up tables based on simulation are another widely used approach to model gate/cell delay [51]. Hashimoto et al. further studied the spatial power/ground level variation and proposed a power/ground (P/G) equalization method when the driver voltage level is different from the receiver, so that the gate delay model does not need to use input voltage levels as variables [52].

Path delay variation is roughly calculated as the summation of gate delay variations of all switching gates on the propagation path. Interconnect delay variation is not included since it is not sensitive to power supply noise. If input slew rate is also a variable in the gate delay model, the delay of each gate on the path is dependent on the output slew rate of its preceding gate.

A number of techniques have been proposed to compute the impact of power supply noise on timing performance. The static timing analysis (STA) technique in the presence of power supply and ground voltage variations was proposed to give the worst-case circuit delay [24]. Dynamic timing analysis, which predicts timing performance by simulating a set of selected patterns, is even more sensitive to power supply noise [53]. This is because power supply noise is highly dependent on the input vectors. In selecting the critical paths and generating patterns for dynamic analysis, one needs to consider the noise impact to ensure that the pattern set can produce realistic worst-case path delay.

### 2.3 Delay Testing

Timing performance is critical for high-end semiconductor products such as microprocessors. Testing is applied to integrated circuits after manufacturing to screen out defective parts from good ones. Most common defects are gross defects that produce incorrect values at primary output pins at any frequency, which is also called functional failure. However, some small manufacturing defects do not cause functional failures, but fail to produce correct values at the desired frequency. Delay testing is designed to detect such defects and ensure the parts that are shipped to customers meet the desired timing specifications [54].

Typical structural delay testing is performed as follows. Each delay test pattern contains two test vectors. The first vector initializes the circuit under test (CUT) and the second vector stimulates transitions on target signal lines, and makes sure a slow transition on these signal lines can be detected. A faulty circuit with a delay defect may pass a slow speed test but fail at higher frequency.

A fault model is an abstraction of a type of defect behavior. Classic delay fault models that are commonly used in delay testing are the transition fault model [55] and the path delay fault model [56]. The transition fault model assumes that the delay fault affects only one gate or line in the circuit under test, and can be detected on any sensitized path through the fault site. As the transition fault model targets relatively large delay faults, its test quality for small delay faults is a concern [57][58]. With the path delay fault model, a circuit is considered faulty if the delay of any of its paths exceeds the specified time. The path delay fault model is more realistic in modeling physical

delay defects, but the number of paths in the circuit can be exponential in the number of gates. Many techniques have been proposed to reduce the number of paths.

Test speed is another challenge in delay testing. Applying a test at the CUT functional speed is called at-speed test. Two scan-based at-speed test approaches have been widely used in industry. One is launch-on-shift (or skewed load [59][60]), which requires the second vector of the test pattern to be 1-bit shift of the first vector. The other is launch-on-capture (or functional justification, broadside [61]), which requires the second vector to be the system output of the first vector. The launch-on-shift approach has less test generation cost and higher coverage, but it requires a full-speed scan enable signal. On the other hand, the launch-on-capture approach does not require the scan enable signal to operate at full speed, and the sensitizable paths under the launch-on-capture constraints are also sensitizable in functional mode.

#### 2.4 Power Supply Noise in Delay Testing

While noise-aware timing analysis has been thoroughly investigated in the past several years, the noise impact in delay testing has received only limited work. As more and more semiconductor manufacturers include at-speed delay testing into their product test flows, the noise impact on circuit timing, if not handled appropriately, may lead either to test escapes or test overkill. However, not much work has been published to address this issue.

Krstic et al. [62] [63] proposed a Genetic Algorithm based approach in pattern generation, which not only sensitizes and propagates the given fault, but also maximizes

power supply noise on path nodes and produces worst-case path delay. The results showed that their test patterns produced 19-59% extra path delay on average. However, the resulting maximum noise may be considerably greater than the functional mode worst-case noise. Moreover, this method set all don't care bits in the original patterns to a value, either "1" or "0", and this assignment of the don't care bits will very likely compete with other goals, such as crosstalk generation, that sometimes have greater impact on path delay or test power control.

Kokrady et al. [64] focused on timing validation for delay test vectors to avoid misclassification of good parts. Validation of test vectors is usually done by vector-based timing simulation, which invalidates and eliminates test vectors that cannot reliably distinguish between good parts and faulty ones. In their approach, the noise issue was taken into account during test validation, to improve the reliability of validated vectors. A layout-aware static method was proposed to validate at-speed transition fault delay test vectors in the presence of IR drop induced delay. However, inductive *di/dt* noise was not discussed in this work, although it usually dominates IR drop in current DSM designs.

Tirumurti et al. [3] proposed a fault modeling method that added power noise to a generalized fault model [65]. A vector-less approach was adopted to save expensive simulation time, so that actual simulation is performed on small cells to characterize peak switching current and current distribution on the power supply network, and the superposition rule is used for adding cell currents to estimate the impact of simultaneous switching activity. This work provides a comprehensive solution for switching cell

characterization, power grid analysis and fault identification, but the worst-case voltage drop is too pessimistic, and would never appear in functional mode.

#### 3. POWER SUPPLY NOISE ANALYSIS

Section 2.2 introduced power supply noise, which is the noise on the supply and ground network that reduces the actual device voltage levels and increases signal arrival time at the primary outputs and next state lines. As we discussed in section 1, we need to design a vector-based modeling approach for power supply noise analysis that can be applied to restrain noise induced overkill in delay test.

The first and most important requirement for this modeling approach is short execution time. Power supply noise variation is largely dependent on the input pattern and the state of the circuit. To accurately characterize supply noise variation and noise-induced delay during delay testing, a vector-based approach is a must. However, during a vector-based approach, any slight computation cost increase per vector will be multiplied by the number of total vectors, and may eventually turn out to be a severe concern.

A lot of prior work has been published on power supply noise analysis to improve design and test while considering noise. Section 2.2.3 listed some of the approaches proposed in the past several years to characterize noise [11][39-47]. However, these approaches adopt vector-less strategies. Despite their comprehensiveness and accuracy, they are too expensive to be applied to vector-based analysis. Therefore, we propose a pattern-dependent solution for noise analysis that avoids heavy computation. The basic idea of our approach is explained as follows. We assume two-pattern delay tests. During the beginning of the launch clock cycle, when most switching activity occurs, the power pads are unable to provide current immediately to satisfy the switching current demand.

This is because off-chip inductance prevents the supply current from rising appreciably before most transitions have propagated. Therefore, during this period, most charge demanded by the switching devices comes from nearby, on-chip sources, such as parasitic capacitors and decoupling capacitors embedded in the circuit. The switching charge is finally provided by off-chip sources, but its impact on propagation delay is relatively small because most transitions complete before the off-chip current rises appreciably. This analysis ignores the background leakage current, since it is relatively constant.

With this basic idea, we conducted a series of experiments on ISCAS benchmark circuits and proposed our first noise model, which we identify as Noise Model I in the rest of the dissertation. It models on-chip activity as well as off-chip current based on an array bond power grid topology, so it works for array bond chips only. This model was found to be inadequate for peripheral bond chips in later research. We proposed a second noise model, which models on-chip activity more accurately, but neglects the off-chip current noise impact for simplicity. This second model was designed for peripheral bond chips, but can be extended to array bond chips. This model is referred to as Noise Model II in the rest of the dissertation. These two models are introduced and compared to each other in the following sections.

#### 3.1 Noise Model I

Array bond chips, or area-array bond chips, adopts array bond approaches in the packaging process that distribute the chip I/O over the entire face of the die [66]. A

widely used array bond approach is Flip Chip. Flip Chip assembly is the direct electrical connection of face-down electronic components onto substrates, circuit boards, or carriers via solder bumps to the chip bond pads. It is first developed by IBM to assemble their mainframe computer modules in the 1960s, and the use of Flip Chip technology has grown rapidly in recent years. Array bonding is are highly effective in high performance systems. Its main disadvantage is high cost in manufacturing.

In contrast to array bond, peripheral bond chips require all the die I/Os to be in a single row or at most double around the periphery of the die. We will discuss peripheral bonding along with our Noise Model II.

## 3.1.1 Region

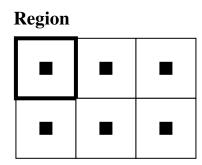

Power grid analysis [3] of array bond chips shows that the supply voltage impact of a switching transient is contained within a local area, since most current flows through nearby pads. Based on the topology of array bond chips, a region is defined as the area centered by a power pad, as shown in Figure 5. It is expected for an array bond design that each power pad should provide the current for the devices in its region. Hence, we start our first modeling approach based on this region concept.

Figure 5. A region in an array bond chip.

#### 3.1.2 Approximations

We make several approximations in our modeling approach [67][68. First, we assume that the supply voltage within a region is uniform, and the voltage of the regions is independent of each other. Further, we assume that the voltage drop for any cell in the region is identical. In addition, all switching activity across the region is equivalent, and any switching events outside the region can be neglected. The error of this approximation, along with several other approximations introduced later, will be estimated in experiments.

Our second approximation is that the on-chip switching current in a region, denoted as  $I_{on-chip}$ , comes from the on-chip decoupling and parasitic supply capacitance within the region. The decoupling capacitors are modeled as a single lumped capacitor between power and ground. The on-chip inductance is neglected for simplicity. On-chip wire resistance is also ignored in this model, so that the analysis becomes much easier than a traditional RLC network. Our model approximates the supply grid voltage as stepwise constant across the chip.

Third, we assume that the off-chip current in a region, denoted as  $I_{off-chip}$ , comes from a constant current source. This current source averages the previous K clock cycles of current consumption (based on the off-chip time constant). Thus,  $I_{off-chip}$  must be taken into consideration if much switching activity occur in the previous cycles. However, during scan test, the scan-to-launch period is usually much longer than the functional mode cycle, so a chip is always in an idle state prior to the launch of a delay test vector. If the off-chip time constant is comparable to the scan clock cycle,  $I_{off-chip}$  becomes

insignificant and can be safely ignored. More discussion on modeling off-chip current is included in section 3.4.

Fourth, voltage drop occurs on both supply and ground nets. A complete voltage drop analysis should take both networks into account. However, most prior work focuses only on the power supply network, with the assumption that power and ground can be separated [45]. We assume that the ground network is ideal, which means that ground bounce is not taken into account in this work. The techniques used here for the power network could also be used to the ground network to improve accuracy.

The leakage current is not considered here. This is because leakage current only affects static IR drop, which is almost the same from pattern to pattern. Therefore, it has no impact on our vector-based analysis and is not taken into account.

### 3.1.3 Noise Model I

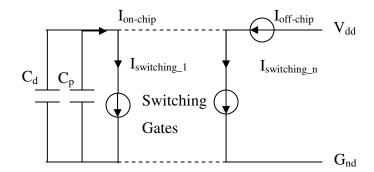

Our simplified Power Supply Noise model within a region is illustrated in Figure 6.  $C_d$  is the distributed decoupling capacitance in a region, and  $C_p$  is the total parasitic capacitance of devices and interconnect within the region connected to the power supply network in the current clock cycle. All switching cells that draw current from the supply within this region during the clock cycle are modeled as time-varying current sources  $I_{switching\_i}$ . The switching current model is discussed below.  $I_{on-chip}$  is the switching current provided by the on-chip capacitance, and  $I_{off-chip}$  is the switching current provided by the power pads.

Figure 6. Supply noise model within a region (Noise Model I).

The maximum voltage drop in this region during a clock cycle,  $\Delta V_{max}$ , is:

$$\Delta V_{\text{max}} = \left( \int I_{\text{on-chip}} \right) / \left( C_{\text{d}} + C_{\text{p}} \right) \tag{1}$$

$$\Delta V_{\text{max}} = \left( \left( \sum I_{\text{switching}_{-i}} \right) - \int I_{\text{off-chip}} \right) / \left( C_{\text{d}} + C_{\text{p}} \right)$$

(2)

After most switching transitions occur, voltage recovers through  $I_{off\text{-}chip}$  until the start of the next cycle.

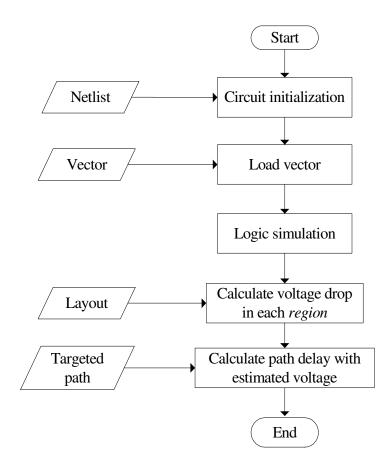

The flow chart of the noise analysis procedure is illustrated in Figure 7. To estimate the power supply noise effect of a delay test vector (a vector pair for delay faults), we first use logic simulation to find transitions on all nets in the circuit. Layout information is then needed to estimate voltage drop for each region. In practice, only those regions traversed by the targeted path need to be considered. We then calculate path delay with our delay model.

The time complexity for this procedure is  $O(cell\_count)$ , where  $cell\_count$  is the total number of cells of the circuit. This means that our analysis approach has the same time complexity as logic simulation.

Figure 7. Power noise analysis procedure.

### 3.2 Noise Model II

Although area-array bonding technology prevails in high-performance chips, its high manufacturing cost prevents it from replacing peripheral bonding approaches in cost-driven applications. Peripheral bonding approaches, most often wire bonding, require all the die I/Os to be in a single row or at most double rows around the periphery of the die

[66]. It is an older technology that uses face-up chips with a wire connection to each pad. Today, wire bonding is still considered the most cost-effective technology in assembly and packaging, and is used for the vast majority of semiconductor products.

Noise Model I cannot be applied to peripheral bond chips. The definition of a region, on which Noise Model I was based, was the area centered on each power pad. Obviously, for peripheral designs, this definition does not work. Therefore, a model that more accurately characterizes localized voltage variation is necessary.

## 3.2.1 Effective Region

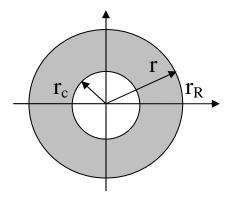

Here we propose a new concept for Noise Model II [69. The circuit is first extracted as a large RC network. On-chip inductance is neglected since it is relatively small compared to the package inductance. Assume a current impulse occurs somewhere in the network. Capacitors around this impulse will begin to discharge in order from nearby to far away, and result in localized voltage drop. However, if a capacitor is far enough away, it is possible that it will not discharge within the clock cycle. Such capacitors should be considered irrelevant to the noise analysis. Consequently, an effective region for a switching device is defined as the area whose RC time constant is less than or equal to the clock cycle time. Put another way, a capacitor only provides current to devices whose effective regions cover that capacitor.

The RC time constant T of a region follows from the integration over the region area of the supply network resistance times the circuit capacitance, which is recently presented by Paul van de Wiel et al.[70]. To introduce the calculation for RC time constant, we first start with an annular metal board in Figure 8, and come up with the

following equations:

Figure 8. An anualar-shaped metal board.

$$dR = \rho \cdot dr / (2\pi r) \tag{3}$$

$$dC = c \cdot (2\pi r) \cdot dr \tag{4}$$

where  $\rho$  is the sheet resistance, c is the average capacitance per unit area, r is the distance from the center, and R and C are resistance and capacitance as a function of r, respectively [70]. Based on equations above, the following function can be derived to compute RC time constant T as a function of r:

$$T = \int d(RC) = \int (R \cdot dC + C \cdot dR) = 0.5 \cdot \rho \cdot c \cdot \ln(r_R / r_c) \cdot (r_R^2 - r_c^2)$$

(5)

where  $r_c$  is the inner radius and  $r_R$  is the outer radius of the annular sheet. These equations can also be extended to the circuit, which is not annular-shaped or evenly distributed. Approximations are necessary in this extension. The power grid can be approximated as a metal sheet by using the metal fill rate when computing sheet

resistance. The inner radius  $r_c$  is set to half of the diameter of a first-level contact, which is usually much smaller than the radius  $r_R$  of the area, so the function can be approximated as:

$$T \approx 0.5 \cdot \rho' \cdot C_A \cdot \ln(r_R / r_c) \tag{6}$$

where  $\rho$ ' can be computed by dividing the metal sheet resistance by metal fill rate and number of layers, and  $C_A$  is the total capacitance of the whole area. However, the parasitic capacitance included in  $C_A$  is pattern-dependent and makes the RC time constant and so the effective region pattern-dependent as well. In order to compute a pattern-independent effective region,  $C_A$  is approximated as the total decoupling capacitance of the area times a ratio. The ratio is defined as the whole chip signal net capacitance plus decoupling capacitance, divided by the decoupling capacitance. The assumption is that the ratio of signal net and decoupling capacitance is similar in each region.

Most of time, the majority of switching activity is completed within the first half clock cycle. Therefore, it is also valid to use half of the clock cycle time in deciding the size of the effective region.

An algorithm has been developed to define effective regions for all devices on the chip. This algorithm only needs to be applied once for each circuit. Its flowchart is shown in Figure 9.

If two switching devices, or two decoupling capacitors, are very close to each other, it is obvious that they will have very similar effective regions and voltage variation. These devices can be put together for analysis to reduce computation complexity. Therefore,

we first divide the whole chip area into  $m \times n$  small squares or grids, each containing a limited number of capacitors and switching devices. These grids will then be assigned to effective regions, which will determine the effective region for all devices and capacitances within the grid. The grid size is chosen such that the effective region can be accurately determined. In practice, the grid size can be quite large as long as its RC time constant is small compared to the clock cycle time.

Figure 9. Flowchart of the algorithm to find effective regions for all devices.

To determine the region associated with each grid, we start with the grid itself, and then increase the radius by one grid width each time to expand the region until the RC time constant equals or exceeds the clock cycle time. Some grids are only partially covered, but they are still considered part of the region as long as over 50% of the grid area is covered. We repeat this analysis for all grids until each has an effective region.

The complexity of the effective region algorithm is  $O(grid\_count^2)$ , where  $grid\_count$  is the total number of grids As discussed above, grids must have RC time constants small compared to the clock cycle time to achieve good accuracy. In our experiments, we have found that we can achieve this accuracy by setting  $grid\_count$  to the square root of cell count, so that the complexity of the algorithm is  $O(cell\_count)$ .

## 3.2.2 Approximations

As with Noise Model I, we make several approximations before introducing our noise model.

First, the voltage level (and power supply noise) is uniform within each grid. Therefore, the voltage level for all cells in the grid is identical. This approximation is reasonable, since the spatial voltage variation within a small area is small, due to embedded capacitance and low resistance. This is different from our approximation for Noise Model I, which assumes uniform voltage in the whole region.

Second, in response to a switching impulse, all capacitors in the effective region are assumed to be equally effective, despite their varying distance to the switching device. Therefore, the total switching charge in the grid is evenly provided by all capacitors in the effective region. For each grid in the region, the percentage of total charge it needs to

provide for the center grid depends on the ratio of its capacitance to that of the whole region. Further, parasitic capacitance is approximated as constant, since experiments show that the pattern-to-pattern variation of parasitic capacitance is small. This approximation makes the effective regions independent of test patterns.

A third approximation is that there is no current coming from off-chip sources. As we discussed before, the power supply cannot response immediately to the impulsive switching current demand, due to high package inductance and the long idling time during the scan cycle prior to the launch cycle. Approximately, most switching activity occurs in the first half of the clock cycle. For example for the chip in [71], the average path length is 3 ns, while the longest path is 7 ns. Therefore, the off-chip current is considered insignificant compared to on-chip current demand when most transitions are propagated. However, this approximation can be replaced by more accurate off-chip current modeling approaches, which are discussed in section 3.4.

### 3.2.3 Noise Model II

Our simplified noise model within a grid is illustrated in Figure 10. As we have discussed, each grid contains two kinds of components: capacitors and switching devices. A grid provides current by discharging its capacitance for any switching devices whose effective region covers this grid. In the meantime, it absorbs current from all capacitors in its effective region. Similar to Noise Model I,  $C_d$  is the distributed decoupling capacitance in a grid, and  $C_p$  is the total parasitic capacitance of devices and interconnect connected to the power supply network in the current clock cycle. All switching cells that draw current from the supply within this region during the clock

cycle are modeled as time-varying current sources, which will be discussed in Section 3.5.

The maximum voltage drop for a particular grid during a clock cycle is:

$$\Delta V \max = \left(\sum (\alpha_i \cdot Q_i)\right) / \left(C_d + C_p\right) \tag{7}$$

where  $Q_i$  is the total switching charge of grid i, whose effective region covers the current grid, and  $\alpha_i$  is the ratio of the decoupling capacitance of the current grid to the whole effective region of grid i.

Figure 10. Supply noise model within a grid (Noise Model II).

Figure 11 is the flow chart of the entire noise analysis procedure for one test pattern. We first load the circuit netlist and layout to locate devices and extract parasitic capacitance. Each grid is then associated with an effective region. This initialization only needs to be performed once per circuit. Then for each test pattern, logic simulation is applied to find transitions on all signal nets of the circuit. We use zero-delay simulation in either noise model, but we can also apply a timed logic simulation to accurately estimate glitches using a back-annotated Standard Delay Format (SDF) file. Note that a

glitch is also considered as a full rising and a full falling transition in our work. We then calculate the switching charge needed for each grid, and distribute the charge among all the grids in its effective region. Equation 3 introduced above can then be applied to each grid to calculate power supply noise. Delay models are applied in the last step of the analysis to calculate path delay with noise impact.

The time complexity for this procedure is  $O(cell\_count + grid\_count^2)$ . As discussed in section 3.2.1,  $grid\_count$  can be of the order of the square root of  $cell\_count$ . In addition, finding effective regions for grids only needs to be performed once per circuit. Hence the complexity becomes  $O(cell\_count)$ . This means that our noise estimation approach has the same time complexity as logic simulation.

## 3.3 Model Comparison in Model Application

For each test pattern, a complete power-noise-aware timing analysis can be classified into two consecutive steps: 1) compute the on-chip voltage level, and 2) compute the propagation delay on the critical paths. The analysis flows for the two noise models both follow this scheme, yet there is still some difference in model application. The analysis flows of the two models are compared in Figure 12.

The time complexity of power supply noise analysis per test pattern is  $O(cell\_count)$  for Noise Model I, where  $cell\_count$  is the total number of cells of the circuit. For Noise Model II, the time complexity is  $O(cell\_count + grid\_count^2)$ . In practice,  $grid\_count$  can be of the order of the square root of  $cell\_count$  with slight impact on accuracy. Hence the complexity also becomes  $O(cell\_count)$ , the same as Noise Model I.

Figure 11. Flow chart for power supply noise analysis.

# 3.4 Discussion on Off-chip Current Modeling

Because Noise Model II better characterizes local voltage variation, it has the potential to be more accurate. However, a major drawback in Noise Model II is that it does not consider off-chip current. Off-chip current has always been a difficult problem in either of our noise models. In general, three approaches can be applied to address off-chip current.

Figure 12. Analysis flow comparison for Noise Models I and II.

First, off-chip current can be neglected. We adopt this approach in Noise Model II for simplicity. As mentioned before, the power supply cannot response immediately to the impulsive switching current demand, due to high package inductance and the long idling time during the scan cycle prior to the launch cycle. Also for peripheral chips, most switching devices are not close to the power pads, which limits the impact of off-chip current. This strategy relieves us from analyzing the off-chip current effect in reducing voltage drop. However, if non-scan testing is used, or if the idle time before the launch cycle is short enough, this approach will no longer be accurate.

Second, off-chip current can be modeled as a constant current source, since the off-chip time constant of the power supply is much larger than the system clock cycle due to high package inductance. This current source averages the previous K clock cycles of current consumption (K is based on the off-chip time constant). Noise Model I adopts this approach. For scan test, this approach will give us a close-to-zero constant off-chip current due to the long scan cycle before the system clock cycle, which is similar to the first approach. This approach takes previous circuit state into account, hence it is a more accurate model of off-chip circuits. The disadvantage is that it does not consider the impact on off-chip current from switching activity in the current clock cycle.

Third, we can model the off-chip current with a theoretical approach. Three assumptions are made to validate this approach:

- All switching activity is finished by the first half of the clock cycle. No switching activity occur in the second half of the clock cycle.

- Switching charge demand increases linearly during the first half of the clock

cycle.

• On-chip voltage level is uniform across the chip.

Therefore, we have the following equations based on charge conservation, assuming the initial off-chip current is 0 (which is valid for scan-based test with long scan cycle prior to the launch cycle):

$$\begin{cases}

CL \frac{di_1}{dt} \Big|_{t_x} + \int_0^{t_x} i_1 dt = \alpha \cdot t_x \\

i_1(t=0) = 0 \\

t_x < t_c / 2 \\

\alpha = \frac{2Q_s}{t_c}

\end{cases}$$

(8)

in which  $i_l$  is the off-chip current from the power supply, C is the on-chip capacitance,  $t_x$  stands for a time point in the first half of the clock cycle,  $t_c$  is the system clock cycle time,  $Q_s$  is the total switching charge demand from the circuit, and  $\alpha$  is the linear factor of switching charge demand increase.

And we get:

$$i_1 = \alpha (1 - \cos(t / \sqrt{CL})) \tag{9}$$

$$\Delta v(t) = \alpha \sqrt{\frac{L}{C}} \sin(t/\sqrt{CL})$$

(10)

In case the initial off-chip current is non-zero, we have:

$$\begin{cases}

CL \frac{di_1}{dt} \Big|_{t_x} + \int_0^{t_x} i_1 dt = \alpha \cdot t_x \\

i_1(t=0) = i_{init} \\

t_x < t_c / 2

\end{cases}$$

$$\alpha = \frac{2Q_s}{t_c}$$

(11)

The results become:

$$i_1 = (\alpha - i_{init})(1 - \cos(t/\sqrt{CL})) + i_{init}$$

(12)

$$\Delta v(t) = (\alpha - i_{init}) \sqrt{\frac{L}{C}} \sin(t/\sqrt{CL})$$

(13)

In which  $i_{init}$  is the initial value of off-chip current when the launch clock cycle is applied. It can be the current that averages the previous K cycles of current consumption, as we did in the second approach. In this way, we combine previous circuit state impact with current circuit state impact in analyzing off-chip current, and this approach should be more accurate than the previous two.

These three approaches are all applicable for Noise Model I. However, the second and the third approaches, which are regarded as more accurate, can not be directly integrated into Noise Model II. What is missing from these two approaches is how the off-chip current is distributed on-chip, and how many switching devices and how much area it affects in reducing voltage drop.

A practical method is to view the power pad as a current source similar to any on-chip switching devices, but negative in value, and find an effective region for it. In this way,

we can perform the same analysis for off-chip current as for on-chip switching devices. The second approach, which averages previous cycles of current consumption, can be integrated to Noise Model II in this way. The third approach, which should be the most accurate, needs further modification if it will be adopted in Noise Model II in future work.

## 3.5 Switching Models

We must calculate  $\int I_{switching\_i}$  for each library cell, or  $Q_i$  for each grid in Noise Model II, in order to compute worst-case voltage drop. Switching current drawn from the supply network in CMOS circuits consists mainly of two parts, the short circuit current and the charging/discharging current on the output capacitive load. The latter term is usually the dominant term, due to slew rate design constraints.

## 3.5.1 Dynamic Charging/discharging Current

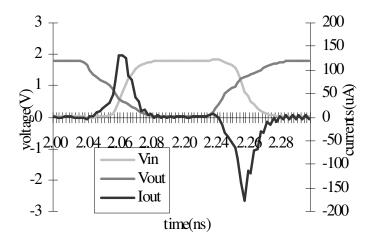

Charging/discharging current in CMOS circuits is well understood and easy to estimate. Tirumurti et al. [3] created a table of peak power and ground currents for different values of cell output load and input slope by simulation. This approach incorporates both short-circuit and charging current. We adopt a similar approach to calculation charge due to dynamic charging current. Figure 13 shows a typical waveform for an inverter. This waveform is usually approximated as triangular in order to compute the total charge of each transition, as shown in Figure 14. If the load is quite large, sometimes this waveform is also approximated as a trapezoid.

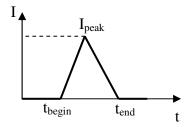

Based on the triangular approximation in Figure 14, a table is built by simulation for each cell, such that one can determine its peak current and output transition time for different values of output load and input slew rate. Once we get the peak current and transition time from the table, the total charge demanded by a transition can be calculated as:

$$Q = 0.5 \cdot I_{\text{peak}} \cdot (t_{\text{end}} - t_{\text{begin}}) \tag{14}$$

where  $I_{peak}$ ,  $t_{end}$  and  $t_{begin}$  are computed from simulation. The input slope during circuit operation is unknown, since we do not know the actual input slope for each gate before estimating voltage drop and apply our delay models. Instead, we can use the input slew rate from static timing analysis, assuming nominal delay.

Figure 13. Charging/discharging current waveform for an inverter.

Figure 14. Switching current model of dynamic charging current for CMOS devices.

#### 3.5.2 Short Circuit Current

During switching in a static CMOS logic gate, a direct path from the power supply to ground is established [72] that results in short circuit current. Short circuit current is dependent on the input rise/fall time, the load capacitance and gate design. When the load capacitance is small enough, the short circuit current dominates the current drawn from the supply network. Similar to charging/discharging current, we can also create a table of peak current for different values of gate output load and input slope by circuit simulation. Similarly, the input slope for each gate is computed by static timing analysis assuming nominal delay. The current waveform is approximated as triangular, which is accurate in most circuit designs, particularly low power designs.

Another practical approach is using analytical functions to calculate short circuit charge for all cells, since most of the time short circuit current is relatively small. The short circuit current model used here is based on previous work by Sylvester et al [73][74]. By making various assumptions and approximations, the peak current is

substituted with a certain fraction of the saturation current, and the time of short circuit current is approximated as:

$$T_{\text{short}} = 1.1 \cdot (R_d \cdot (C_i + C_{in}) + R_d \cdot C_w + R_w \cdot C_{in} + 0.4 \cdot R_w \cdot C_w)$$

(15)

where  $T_{short}$  is the flow time,  $R_d$  and  $R_w$  are the device and wiring resistance, and  $C_j$ ,  $C_{in}$  and  $C_w$  are the junction, input and wiring capacitance, respectively. Assuming a triangular waveform for the short circuit current, we can calculate the short circuit charge using both  $T_{short}$  and peak current.

# 3.6 Delay Models

Power-noise-aware timing analysis consists of two consecutive steps: computing the on-chip voltage levels and computing the propagation delay on target paths considering noise impact. The first step was included in the two noise models. Here we focus on propagation delay computation with noise.

Several delay definitions must first be given. Cell delay is measured as the time interval between the input crossing approximately  $V_{ddl}/2$  and the output crossing approximately  $V_{dd2}/2$ , where  $V_{DD1}$  and  $V_{DD2}$  are the input and output voltage ranges of the cell. For both input and output, the accurate measurement point is the 40% point for rising transitions and the 60% point for falling transitions. The transition time is specified in the 10% to 90% interval of full swing. Some prior work also suggests the 30% to 70% interval is more accurate [75].

Several models have been proposed for delay functions. Bai et al. proposed the following delay equation [76]:

$$t_{d} = A + BV_{DD} + CV_{DD}^{2}$$

$$\tag{16}$$

where the coefficients can be obtained from simulation. The coefficients here strongly depend on the input transition time and output capacitance. Bai et al. also suggested linear functions of supply voltage with appropriate coefficients if the voltage drop is not too large [76].

Another widely used delay modeling approach is to model both delay and transition time as a function of input slope, output capacitive load and device voltage level. This approach was applied in our experiments for Noise Model I. The models are generalized as follows.

$$t_{d} = f(t_{in}, C_{out}, V_{dd})$$

$$\tag{17}$$

$$t_{\text{out}} = g(t_{\text{in}}, C_{\text{out}}, V_{\text{dd}}) \tag{18}$$

where  $t_d$  is the gate delay,  $C_{out}$  is the output load,  $t_{in}$  is the input transition time and  $t_{out}$  is the output transition time. A table method based on these equations has been used to calculate  $t_d$  and  $t_{out}$ .

A third delay model, which we used in the experiments for Noise Model II, models both delay and transition time as a function of input slope and output capacitive load first. A look-up table is built in this step. Then simulations are performed for each library cell to find a linear relationship between delay or slope and voltage level. Rising and falling transitions on the output are considered separately. We then use the linear model to calculate real delay and slew rate:

$$t_{d} = \beta \cdot f(t_{in}, C_{out}) + \gamma \tag{19}$$

$$t_{out} = \lambda \cdot g(t_{in}, C_{out}) + \zeta \tag{20}$$

where  $t_d$  is the cell delay,  $t_{in}$  is the input transition time and  $t_{out}$  is the output transition time.  $\beta$ ,  $\gamma$ ,  $\lambda$ , and  $\zeta$  are coefficients from simulation. They will have different values for rising and falling transitions.

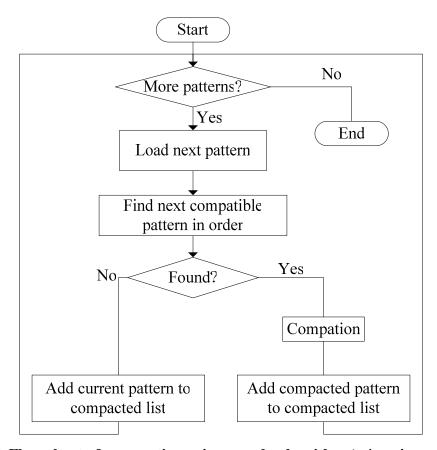

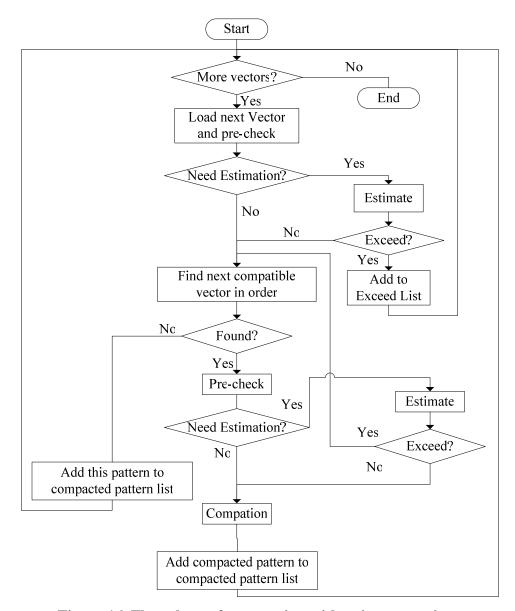

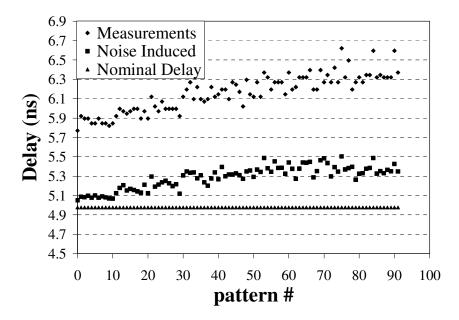

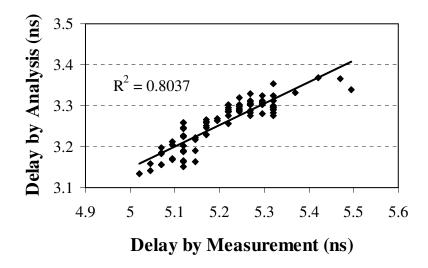

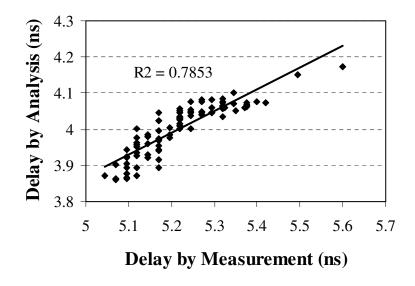

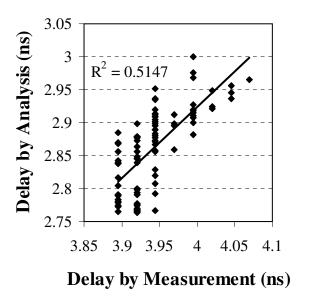

Different operating conditions may have a significant impact on delay. The main factors in operation conditions are nominal voltage, temperature and process parameters. Different delay models may be necessary when operating conditions change.