# DESIGN METHODOLOGIES FOR VARIATION-AWARE INTEGRATED CIRCUITS

### A Dissertation

by

## RUPAK SAMANTA

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

December 2008

Major Subject: Computer Engineering

# DESIGN METHODOLOGIES FOR VARIATION-AWARE INTEGRATED CIRCUITS

### A Dissertation

by

## RUPAK SAMANTA

## Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Jiang Hu              |

|---------------------|-----------------------|

| Committee Members,  | Weiping Shi           |

|                     | Jose Silva-Martinez   |

|                     | Vivek Sarin           |

| Head of Department, | Costas N. Georghiades |

December 2008

Major Subject: Computer Engineering

#### ABSTRACT

Design Methodologies for Variation-Aware Integrated Circuits. (December 2008)

Rupak Samanta, B.E., Sambalpur University, Burla;

M.Tech., Indian Institute of Technology, Mumbai

Chair of Advisory Committee: Dr. Jiang Hu

The scaling of VLSI technology has spurred a rapid growth in the semiconductor industry. With the CMOS device dimension scaling to and beyond 90nm technology, it is possible to achieve higher performance and to pack more complex functionalities on a single chip. However, the scaling trend has introduced drastic variation of process and design parameters, leading to severe variability of chip performance in nanometer regime. Also, the manufacturing community projects CMOS will scale for three to four more generations. Since the uncertainties due to variations are expected to increase in each generation, it will significantly impact the performance of design and consequently the yield.

Another challenging issue in the nanometer IC design is the high power consumption due to the greater packing density, higher frequency of operation and excessive leakage power. Moreover, the circuits are usually over-designed to compensate for uncertainties due to variations. The over-designed circuits not only make timing closure difficult but also cause excessive power consumption. For portable electronics, excessive power consumption may reduce battery life; for non-portable systems it may impose great difficulties in cooling and packaging.

The objective of my research has been to develop design methodologies to address variations and power dissipation for reliable circuit operation. The proposed work has been divided into three parts: the first part addresses the issues related with power/ground noise induced by clock distribution network and proposes techniques to reduce power/ground noise considering the effects of process variations. The second part proposes an elastic pipeline scheme for random circuits with feedback loops. The proposed scheme provides a low-power solution that has the same variation tolerance as the conventional approaches. The third section deals with discrete buffer and wire sizing for link-based non-tree clock network, which is an energy efficient structure for skew tolerance to variations.

For the power/ground noise problem, our approach could reduce the peak current and the delay variations by 50% and 51% respectively. Compared to conventional approach, the elastic timing scheme reduces power dissipation by 20% - 27%. The sizing method achieves clock skew reduction of 45% with a small increase in power dissipation. To my Parents and Wife Archana

#### ACKNOWLEDGMENTS

There is a lifetime's worth of people who have undoubtedly influenced and encouraged me in many aspects of my life. I would like to thank all of them. I must limit myself to recognizing those in the present and most recent past.

First and foremost, I would like to express my deepest gratitude to my advisor Dr. Jiang Hu, for his invaluable academic guidance, patience and respect to my ideas and thoughts and timely advice on various aspects of my graduate student life. This research work would not have been possible without his support and guidance.

I would like to thank my committee members Dr. Weiping Shi, Dr. Jose Silva-Martinez and Dr. Vivek Sarin, for their valuable input and advice throughout the duration of my research. I would like to thank all the faculty members of computer engineering for their help during course projects or for my research. Special thanks to Dr. Weiping Shi for his course Algorithms for VLSI CAD which greatly helped me in honing my physical design skills and igniting my interest into the world of physical design. The students of the computer engineering group were equally helpful to my research effort. In particular, I'd like to thank Karandeep Singh, Rajesh Garg, Charu Nagpal, Nimay Shah, Shiyan Hu, Ganesh Venkataraman and Rohit Singhal. I really enjoyed working with them. I'd like to thank Saurabh Pradhan, Feroze Merchant, Nicholas Tsang and Manjunath Shamanna for being my mentors at Intel Austin during my internship. Many thanks to the FEC team members for the wonderful time I had during the internship.

I would like to thank all my friends who made my stay at Texas A&M very enjoyable. In particular, I would like to thank Bhoj, Karan, Ranjani, Charu, Nimay, Rajesh, Bhagi, Binoy, Rajmohan, Biswajit, Somnath, Gagan, Ashwin, Aditi and Vivek. Many thanks to Venkat, Swapna, Anuj and Sonal for the wonderful time in Austin. I would like to extend my appreciation to a few friends who have been with me during all the difficult times of my life. Those who need special mention are Rakesh, Lala, Deba, Raju, Aditya, Manas and Suchismita. Lastly, I would like to thank the late Soyuz Priyadarshan for his invaluable advice during the initial years of my Ph.D.

I would like to thank my parents and my dear wife Archana, who have given me all their love and support and let me freely do whatever I want. Without them, there is no way I could possibly have accomplished this. Their understanding on the value of education is truly beyond my comprehension. I am just a lucky beneficiary. Along the way, my sister Rasmita has always shared her caring thoughts and encouraged me during the difficult times of my research. I would like to thank my Uncles (Kabuli Dada and Tuku Dada) and Aunts (Bina Khudi and Shanti khudi) for taking special care of my parents during my stay outside my hometown. Thanks to my cousins Runu Apa, Bhupen Nana, Aji Nana, Sanji Nana, Babuna Nana, Deepak, Dipu, Nandini Apa, Dudu, Puchi, Ruchi, Rima and the cute Jini. Finally, I would like to extend my appreciation to my grandmother and my late grandfather for their love and affection throughout my life.

And last, but not least, I would like to thank Dr. Madhav Desai and Dr. Ashok Pradhan for motivating me to consider higher study without which I would never have thought of pursuing the doctoral degree.

Thank you all!

## TABLE OF CONTENTS

## CHAPTER

## Page

| Ι   | INTRODUCTION                                           | 1  |

|-----|--------------------------------------------------------|----|

|     | A. Background and Motivation                           | 1  |

|     | 1. Manufacturing/Fabrication Sources of Variations     | 1  |

|     | 2. Environmental Sources of Variations                 | 2  |

|     | 3. Power Components in CMOS Logic                      | 3  |

|     | B. Contribution                                        | 4  |

|     | 1. Clock Buffer Polarity Assignment for Power Noise    |    |

|     | Reduction                                              | 4  |

|     | 2. Elastic Timing Scheme for Energy-Efficient and      |    |

|     | Robust Performance                                     | 5  |

|     | 3. Discrete Buffer and Wire Sizing for Link-based Non- |    |

|     | tree Clock Networks                                    | 6  |

|     | C. Organization                                        | 7  |

| II  | CLOCK BUFFER POLARITY ASSIGNMENT FOR POWER             |    |

| 11  | NOISE REDUCTION                                        | 8  |

|     |                                                        |    |

|     | A. Introduction                                        | 8  |

|     | B. Impact to Delay Variation                           | 13 |

|     | C. Problem Formulation                                 | 16 |

|     | D. Polarity Assignment Algorithms                      | 17 |

|     | 1. Partitioning                                        | 17 |

|     | 2. 2-coloring on Minimum Spanning Tree                 | 17 |

|     | 3. Recursive Min-matching                              | 18 |

|     | E. Buffer Type Selection and Post Processing           | 21 |

|     | 1. Buffer Type Matching                                | 23 |

|     | 2. Clock Skew Tuning                                   | 25 |

|     | F. Experimental Results                                | 26 |

| III | ELASTIC TIMING SCHEME FOR ENERGY-EFFICIENT             |    |

|     | AND ROBUST PERFORMANCE                                 | 34 |

|     | A. Introduction                                        | 34 |

|     | B. Background on Razor                                 | 36 |

|     | C. New Timing Error Correction Scheme                  | 37 |

| Page |

|------|

|------|

|         | D. Dynamic Speed Boosting                      | 38 |

|---------|------------------------------------------------|----|

|         | 1. Dynamic Dual- $V_{DD}$                      | 38 |

|         | 2. Dynamic Fast Lane                           | 39 |

|         | 3. Power Reduction and Overhead                | 41 |

|         | E. Shared Boosting via Dynamic Skew Shifting   | 41 |

|         | F. Timing Control                              | 42 |

|         | G. Optimization for Minimizing the Overhead    | 46 |

|         | H. Experimental Results                        | 48 |

| IV      | DISCRETE BUFFER AND WIRE SIZING FOR LINK-BASED |    |

|         | NON-TREE CLOCK NETWORKS                        | 54 |

|         | A. Introduction                                | 54 |

|         | B. Skew Modeling via Statistical Learning      | 57 |

|         | C. Sizing Algorithms                           | 59 |

|         | 1. Overview                                    | 59 |

|         | 2. Optimization Stage 1                        | 62 |

|         | a. Overall Optimization Flow                   | 62 |

|         | b. ILP Formulation                             | 65 |

|         | 3. Optimization Stage 2                        | 68 |

|         | D. Experimental Results                        | 70 |

| V       | CONCLUSION                                     | 81 |

| REFEREN | NCES                                           | 83 |

| VITA    |                                                | 91 |

## LIST OF TABLES

| TABLE |                                                                                                      | Page |

|-------|------------------------------------------------------------------------------------------------------|------|

| Ι     | An example of power/ground noise for the three cases in Figure 4. $% f(x)=1,$ .                      | 14   |

| II    | Characteristics of testcases                                                                         | 27   |

| III   | Results for peak current (mA)                                                                        | 28   |

| IV    | Results for power noise (mV) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 28   |

| V     | Results for ground noise $(mV)$                                                                      | 29   |

| VI    | Results for delay variation (ps)                                                                     | 29   |

| VII   | Results for nominal skew (ps)                                                                        | 30   |

| VIII  | Results for skew due to variation for ISCAS89 (ps) $\ldots \ldots \ldots$                            | 30   |

| IX    | Results for total resource consumption (power in mW and cap in $pf$ )                                | 31   |

| Х     | Results for CPU time (sec)                                                                           | 32   |

| XI    | Sleep transistor timing in dynamic dual- $V_{DD}$ boosting $\ldots \ldots \ldots$                    | 43   |

| XII   | Results from conventional safety margin based timing scheme $\ . \ . \ .$                            | 49   |

| XIII  | Results of MILP for elastic timing scheme (CPU time in $sec$ )                                       | 50   |

| XIV   | Results of the elastic timing scheme (power in $mW$ )                                                | 50   |

| XV    | Testcases                                                                                            | 70   |

| XVI   | Results of global skew for non-tree clock network (global skew in ps)                                | 72   |

| XVII  | Results of resource consumption for non-tree clock network (power in mW and total cap in $pF$ )      | 73   |

| XVIII | Results of CPU time for non-tree clock network (min)                                                 | 73   |

| TAI | BLE |

|-----|-----|

|-----|-----|

| XIX   | Results of skew due to variation for non-tree clock network (aver-<br>age and maximum skew in ps)                                                                              | 74 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| XX    | Results of per stage skew improvement for Tree+Link+SVM siz-<br>ing (skew in ps)                                                                                               | 75 |

| XXI   | Results of CPU time for SVM modeling for Tree+Link+SVM siz-<br>ing (CPU time in min)                                                                                           | 76 |

| XXII  | Results of global skew for clock tree network (global skew in ps)                                                                                                              | 79 |

| XXIII | Results of resource consumption for clock tree network (power in mW and total cap in pF) $\ldots \ldots \ldots$ | 79 |

| XXIV  | Results of CPU time for clock tree network (min)                                                                                                                               | 80 |

Page

## LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                                    | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

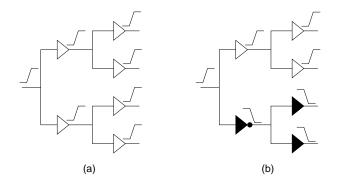

| 1      | All buffers in (a) have positive signal polarity and switch in the same direction. The dark buffers in (b) are assigned with negative polarity and switch in the direction opposite to the buffers with positive polarity.                                                                                         | 10   |

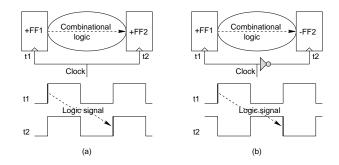

| 2      | (a) Positive-edge triggered FFs with original polarity (b) FF2 is changed to negative-triggered for the reversed polarity. The circuit timing is not affected if the skew t1 - t2 is maintained                                                                                                                    | 11   |

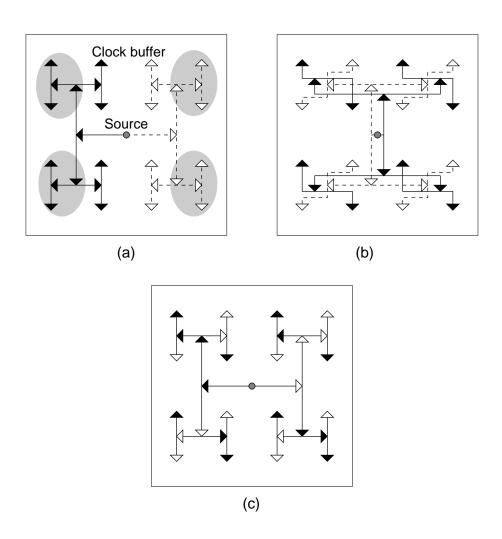

| 3      | Constructing two subtrees separately for opposite polarities either<br>cannot reduce local power noise if the two subtrees are spatially<br>apart like in (a), or results in huge wirelength overhead as in (b).<br>We propose to perform fine-grained polarity assignment on an<br>existing clock tree as in (c). | 12   |

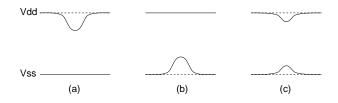

| 4      | Power noise in a local region when (a) all buffers have rising switches, (b) all buffers have falling switchings, and (c) half of the buffers rising while the others falling.                                                                                                                                     | 14   |

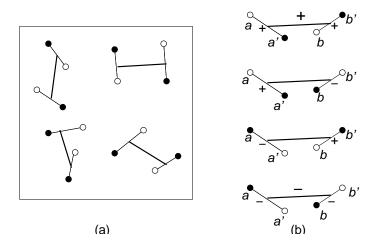

| 5      | Recursive min-matching                                                                                                                                                                                                                                                                                             | 19   |

| 6      | Algorithm of recursive min-matching based polarity assignment                                                                                                                                                                                                                                                      | 22   |

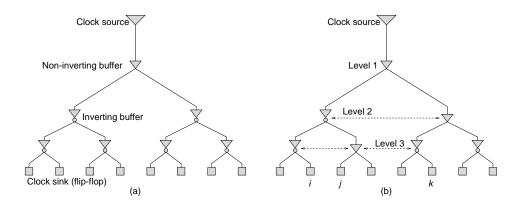

| 7      | <ul><li>(a) Original clock tree. (b) Buffer type mismatch occurs at level</li><li>2 and level 3 after polarity assignment.</li></ul>                                                                                                                                                                               | 23   |

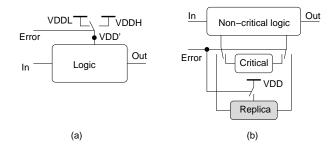

| 8      | (a) Razor flip-flop. (b) Modified Razor flip-flop                                                                                                                                                                                                                                                                  | 37   |

| 9      | Speed boosting by (a) dynamic dual- $V_{DD}$ and (b) dynamic fast lane.                                                                                                                                                                                                                                            | 39   |

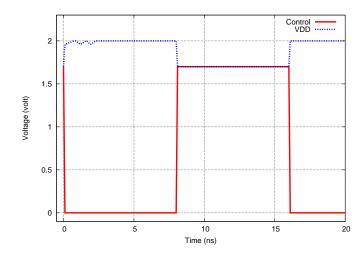

| 10     | The upper waveform is the dynamic supply voltage. The lower waveform is the control (error) signal that switches the $V_{DD}$ level                                                                                                                                                                                | 40   |

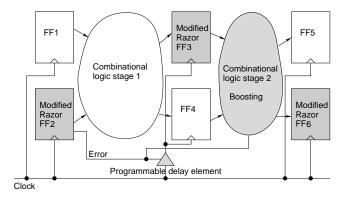

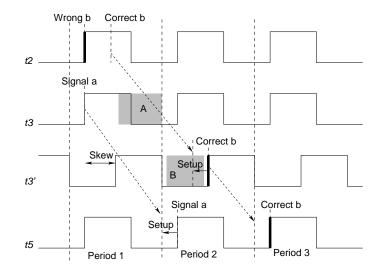

| 11     | Elastic timing via simultaneous skew shifting and speed boosting                                                                                                                                                                                                                                                   | 42   |

| FIGURE |  |

|--------|--|

|--------|--|

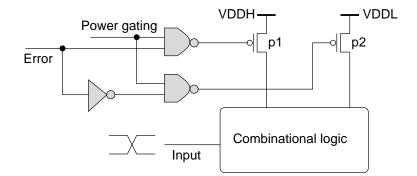

| 12 | Dynamic dual- $V_{DD}$ with power gating                                                                                                                                                                                                                                | 43 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 13 | Timing diagram for the pipeline in Figure 11. $t_3$ is the clock arrival time at FF3 in normal mode. $t'_3$ is the clock arrival time at FF3 after skew shifting. The error signal should arrive FF3 in shaded interval A and arrive logic stage 2 in shaded interval B | 45 |

| 14 | Overall optimization flow.                                                                                                                                                                                                                                              | 60 |

| 15 | Optimization core.                                                                                                                                                                                                                                                      | 61 |

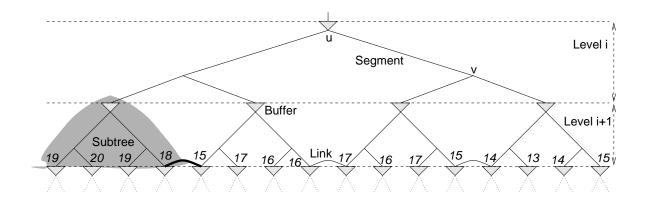

| 16 | Illustration of definitions. The number besides each buffer is the clock signal arrival time to the buffer input.                                                                                                                                                       | 62 |

| 17 | Optimization engine $\mathcal{E}_1$ for stage 1                                                                                                                                                                                                                         | 64 |

| 18 | Optimization engine $\mathcal{E}_2$ for stage 2                                                                                                                                                                                                                         | 69 |

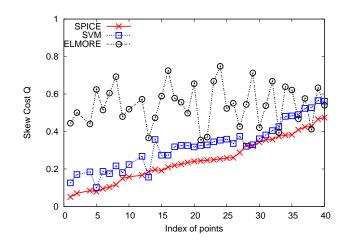

| 19 | Comparison of SPICE, SVM model and Elmore delay.                                                                                                                                                                                                                        | 71 |

Page

#### CHAPTER I

#### INTRODUCTION

#### A. Background and Motivation

The rapid growth of VLSI technology has been made possible by continuous scaling of CMOS devices to the ever smaller dimensions. The result of this rapid growth is high performance and low cost Integrated Circuits (ICs). In 1965, Gordon Moore predicted that the number of transistors on a chip would double every eighteen months. During the last three decades, semiconductor industries have closely followed the technology scaling trend of Moore's law. Intel is one of the leading players in the microprocessor/IC design and manufacture, which has kept pace with Moore's prediction. However, with the advent of nanometer regime, it has been difficult to meet Moore's prediction. One of the major challenges in designing fast and complex ICs is the shrinking device dimensions, that give rise to drastic variations in the device and design parameters leading to severe variability of the chip performance in the nanometer regime. The sources of variabilities can be categorized as follows [1]:

- 1. Manufacturing/Fabrication sources of variations

- 2. Environmental sources of variations

- 1. Manufacturing/Fabrication Sources of Variations

Manufacturing sources of variabilities are caused by processing and mask imperfections and reliability related degradations [1]. Until now it was sufficient to model the sources of variations as die-to-die variations. These variation models assume no

This dissertation follows the style of IEEE Transactions on VLSI Systems.

variability of parameters within a die. Such cases can be analyzed using classic Monte Carlo or the worst-case analysis. However, in deep sub-micron technology, there are significant within-die variations of device and interconnect parameters [1]. Within-die variations are dependent upon both the fabrication process and on the implementation of the ICs. These parameters can be spatially correlated or independent of each other.

#### 2. Environmental Sources of Variations

The environmental sources include variations due to power supply voltage, noise coupling among nets and temperature fluctuation. These variations can be characterized as probability distribution and analyzed using Monte Carlo or the worst-case analysis. The variations are of low time constant and can vary within fraction of seconds.

- Supply voltage can vary from a nominal value during the operation of the chip. Moreover, the voltage variation is non-uniform across the entire chip. Since, supply voltage affects the drain current, the gate delay would vary across the chip with the variation in supply voltage.

- Signal nets can be affected by rising and falling signals of the neighboring nets due to its capacitive coupling with the neighbors. The signal net that gets affected by switching of the neighboring nets is called the victim net and the neighboring nets are called the aggressor nets. Coupling noise significantly impact the propagation delay of a signal net depending upon the direction of switching of its aggressor nets. The coupling noise is calculated using Miller coupling factor (MCF). With shrinking feature size and higher clock frequency, the coupling noise poses a serious threat to the delay variability.

- Temperature can vary throughout the chip depending upon the workload. Tem-

perature affects the mobility of the electrons and holes; higher the temperature lower is the mobility. This in turn affects the propagation delay of the gates. Thus, the propagation delay of a chip would vary depending upon its temperature variations.

Another challenging issue in nanometer IC design is the increase of power consumption. Over the past few years, low power IC design has been an important focus of research and development. The increase in power consumption is mainly due to the rapid technology scaling, enormous integration capacity and the mounting active and leakage power consumption. Moreover, the parasitic capacitances increase with the increase in number of devices on every technology scaling. The charging and discharging of these additional parasitic capacitances leads to soaring amount of power dissipation. With the clock frequency in modern ICs at 4 Ghz, the power dissipation is expected to be even worse. Thus, careful power planning and low power design techniques need to be adopted to reduce the ever increasing power demand of the chip.

#### 3. Power Components in CMOS Logic

The power consumption in CMOS logic is usually estimated by

$$P_{total} = \alpha C V^2 f + V I_{leakage} + P_{short\_circuit}$$

(1.1)

Equation 1.1 consists of three components, namely dynamic power due to switching of the CMOS devices, static power due to leakage current and short-circuit power from power supply. Dynamic power depends upon activity factor ( $\alpha$ ), load capacitance (C), supply voltage (V) and the frequency of operation (f). It is also called the active power of the chip. The leakage power consists of (1) subthreshold leakage (2) gate leakage (3) substrate and junction leakage. The short-circuit power of CMOS logic is due to switching of input and output of the logic gate from one state to the other. During the input/output transition both the PMOS and NMOS of the CMOS logic are on for a certain period of time, thereby connecting the supply and ground through a resistive path. The short-circuit power is higher when the difference in slope between the input and output transition of the CMOS logic is greater. Traditionally, dynamic power is the dominant component of the total power consumption. However, due to aggressive scaling, the leakage components are growing at a faster rate and can not be neglected in nanometer VLSI design. The short circuit components are higher for bad designs where there is larger disparity between input and output slope of the logic gates.

#### B. Contribution

The dissertation deals with two key aspects of the modern IC design - variation and power dissipation. We develop design methodologies to address the two key issues for reliable circuit operation. The proposed work has been divided into three parts: (1) Clock buffer polarity assignment for power noise reduction (2) Elastic timing scheme for energy-efficient and robust performance (3) Discrete buffer and wire sizing for link-based non-tree clock network.

#### 1. Clock Buffer Polarity Assignment for Power Noise Reduction

As supply voltage reduces with VLSI technology scaling, the circuit performance becomes increasingly vulnerable to power and ground noise. This work aims to reduce the clock induced power/ground noise by a fine grained polarity assignment on an existing buffered clock tree. We use three existing algorithms for polarity assignment: (1) partitioning (2) 2-coloring on minimum spanning tree (3) recursive min-matching. The fine granularity of assignment implies that even a very small region usually contains opposite polarity as long as there are more than one clock buffers. By doing so, the clock-induced power noise can be reduced remarkably.

#### 2. Elastic Timing Scheme for Energy-Efficient and Robust Performance

The critical concern in nanometer IC design is the need to deliver high performance given ever-diminishing power budget and significant variation effects. The conventional approach of using safety margin to guard against low probability timing errors consumes power continuously. One of the alternatives to conventional safety margin based approach is the Razor technology [2], that eliminates such power inefficiency by using error detection and correction scheme. However, the error correction requires stalling/flushing of the pipeline, thus, is not preferred in real-time systems or finite state machines (FSM) with feedback loops. In this work, we propose an elastic timing scheme that can correct timing errors without stalling or flushing the pipeline. The main idea of this scheme is dynamic speed boosting. During normal operation, the circuit works with relatively low power consumption. When a timing error is detected, a few parts of the circuits are temporarily switched to a faster speed so that the timing deficit due to error is compensated. In order to minimize the overhead of the speed boosting, we incorporate dynamic clock skew shifting into the elastic timing scheme. Speed boosting and skew shifting should be applied in such a way that the overall power/cost overhead is minimized. We formulate and solve this problem by mixed integer programming. The management complexity of the elastic timing scheme is moderate and therefore not difficult to handle in practice. This timing scheme can also tolerate multiple simultaneous timing errors.

#### 3. Discrete Buffer and Wire Sizing for Link-based Non-tree Clock Networks

The growing complexity of IC design can be attributed to two key issues: variability and power. Clock network is a subcircuit that deeply involves both the challenges. Link-based clock network has drawn people's attention for its appealing tradeoff between variation tolerance and power overhead. In this work, we investigate optimizing link-based non-tree clock network via buffer and wire sizing. Most of the previous work on buffer and wire sizing are either based on the Elmore delay, which is inaccurate for evaluation of skew in modern technology or handle continuous sizing. We will focus on discrete buffer and wire sizing with accurate delay models. Unlike continuous sizing, the discrete sizing rarely depends upon sensitivity analysis, which is valid over very small changes. Moreover, it is difficult to get fine-grained control for highly discrete problems. Using accurate model is also too expensive in a large solution space and may take large amount of time to converge to a solution. Thus, discrete sizing using accurate delay model is a very difficult problem. This difficulty is due to both the discreteness and model complexity. We made the following contributions to solve this difficult yet important problem:

- Support vector machine (SVM) is explored to handle the complex delay model issue and provide guidance for discrete optimization in large design space.

- We propose a two-stage hybrid optimization approach, which can significantly reduce clock skew.

- In the core part of the optimization, we introduce a technique to convert an integer nonlinear programming problem to an integer linear programming formulation.

- To the best of our knowledge, this is the first work on discrete clock network sizing using accurate delay model.

- To the best of our knowledge, this is also the first work on sizing link-based non-tree clock network.

- C. Organization

The remainder of this dissertation is organized as follows. Chapter II discusses power/ground noise reduction for buffered clock tree by performing polarity assignment of the clock buffers. We detail three different algorithms used for polarity assignment. Chapter III includes an elastic timing scheme for energy-efficient and robust IC design. We describe the new timing error correction scheme and the boosting techniques used for on-line error correction. Chapter IV explains the discrete buffer and wire sizing scheme for link-based non-tree clock network. We present a two stage hybrid optimization scheme for buffer and wire sizing. It also includes the description of support vector machine (SVM) used for guidance to our sizing algorithm. Chapter V summarizes our conclusions.

#### CHAPTER II

# CLOCK BUFFER POLARITY ASSIGNMENT FOR POWER NOISE REDUCTION

Power/ground noise is a major source of VLSI circuit timing variations. This work aims to reduce clock network induced power noise by assigning different signal polarities (opposite switchings) to clock buffers in an existing buffered clock tree. Three assignment algorithms are proposed: (1) partitioning, (2) 2-coloring on minimum spanning tree and (3) recursive min-matching. A post-processing of clock buffer sizing is performed to achieve desired clock skew. SPICE based experimental results indicate that our techniques could reduce the average peak current and average delay variations by 50% and 51% respectively.

#### A. Introduction

When the supply voltage decreases with VLSI technology scaling, circuit performance becomes increasingly vulnerable to power/ground noise [3, 4, 5]. This problem is exacerbated by the increase in frequency and large gate count in the scaled technologies. Based on an estimation in [6], a 0.1V power noise may cause 80% inverter delay variation at 45nm technology. A main culprit of power noise is clock network which keeps drawing huge current frequently from the power supply network [7, 8, 9, 10, 11]. Power/ground noise is acute at the beginning of clock cycle when flip-flops and the gates are switching simultaneously. In order to reduce the clock-induced power noise, a few works [7, 8, 9, 11] attempt to avoid simultaneous flip-flop switchings through clock skew scheduling. The common approach is to spread the computation across the entire clock period so that the peak of the power/ground noise occurring at the beginning of the clock cycle is distributed across the entire clock period. In [7, 8], the flip-flops are grouped into buckets that are switched at different times. However, such an approach suffers from the limitation that the flip-flops within the same bucket still switch at the same instant of time. Moreover, the approaches [7, 8], do not consider the effect of clock skew scheduling on current profiles of combinational logic. The work [9], uses a graph based clock scheduling approach to minimize the peak current, hence the power supply noise. In [11], a circuit optimization technique called skew spreading is used to schedule the clock arrival time at each flip-flops such that peak current is reduced. In addition to performing the clock skew scheduling, the approaches [9, 11] also consider the effect of clock scheduling on the current profiles of combinational logic. The skew scheduling approaches [7, 8, 9, 11] are restricted by timing constraints of the combinational logic. Since the effectiveness of these approaches is dependent upon the available slack in the application, the power/ground noise result is expected to vary across different applications.

The use of on-chip decoupling capacitor to suppress the power/ground noise has been discussed in [12, 13]. The main idea is to use the charge stored in the decoupling capacitor to supply the switching transients. In another similar approach [14], the authors use a stub to suppress the power/ground noise. They attach a quarter length stub to the power supply line of the LSI chip. It acts as a band eliminate filter and suppresses power supply noise for a designed frequency.

Besides the flip-flops, the switchings of clock buffers also contribute greatly to the clock-induced noise. In a clock network of an industrial ASIC design, there could be dozens of thousands of clock buffers [15]. A recent work [10] proposes to use different signal polarities on clock buffers so that the roughly simultaneous same-direction switchings are replaced by a mixture of opposite-direction switchings. Signal polarity refers to whether or not a signal switches in the same direction as the clock source. The main idea of [10] is illustrated in Figure 1. In Figure 1(a), all buffers have the same signal polarity and therefore they have either simultaneous rising switches, which draw large current from power  $(V_{dd})$  network, or simultaneous falling switches which draw large current from ground  $(V_{ss})$  network. In contrast, the application of opposite polarities as in Figure 1(b) decreases current withdraw since only a half of the buffers draw current from  $V_{dd}$  while the others draw from  $V_{ss}$  at the same time. Please note that polarity assignment to a buffer is different from selecting between inverting or non-inverting type for the buffer, although these two are related. By using different types of flip-flops, positive-edge or negative-edge triggered, both signal polarities can be accommodated at flip-flops with hardly any impact to the original circuit design. For the example in Figure 2, when the polarity of clock signal  $t_2$  is reversed from Figure 2(a) to Figure 2(b), the circuit timing is not affected if flip-flop FF2 is changed from positive-edge triggered to negative-edge triggered.

Fig. 1. All buffers in (a) have positive signal polarity and switch in the same direction. The dark buffers in (b) are assigned with negative polarity and switch in the direction opposite to the buffers with positive polarity.

When assigning polarities, the work of [10] partitions the clock sinks (flip-flops) into two subsets, one for positive polarity and the other for negative polarity. Then, two subtrees are constructed separately for the two subsets, i.e., one subtree has only positive polarity and the other subtree has only negative polarity. However, this

Fig. 2. (a) Positive-edge triggered FFs with original polarity (b) FF2 is changed to negative-triggered for the reversed polarity. The circuit timing is not affected if the skew t1 - t2 is maintained.

approach faces a dilemma considering the following two typical scenarios:

- If the two subsets are spatially separated from each other like in Figure 3(a), the two subtrees (one in solid lines and the other in dashed lines in Figure 3) are in two separated regions. Except the boundary region between the two subtrees, the power noise in a local area such as the shaded regions in Figure 3(a), is not reduced by the application of opposite polarities. This is because power noise is mostly a local effect.

- If the sink locations of the two subsets are intermingled, the approach of [10] results in two intermingled subtrees like Figure 3(b). In this scenario, the power noise in each local region can be reduced, but the wirelength of the clock network is increased greatly.

Therefore, constructing two subtrees independently [10] either is ineffective for reducing local power noise or suffers from huge wirelength overhead. Moreover, the work of [10] evaluates only the peak current while neither power supply voltage noise nor the impact on delay variation is discussed.

Fig. 3. Constructing two subtrees separately for opposite polarities either cannot reduce local power noise if the two subtrees are spatially apart like in (a), or results in huge wirelength overhead as in (b). We propose to perform finegrained polarity assignment on an existing clock tree as in (c).

In this work, we propose to perform fine-grained clock buffer polarity assignment on an existing clock tree. We carry out a buffer type matching on the resulting clock tree to minimize the path unbalance that may arise due to buffer polarity assignment. Then, a clock buffer tuning is carried out to restore the clock skew altered by the polarity assignment. Three existing algorithms are used for polarity assignment: (1) partitioning, (2) 2-coloring on minimum spanning tree and (3) recursive min-matching. The fine granularity of the assignment implies that even a very small region usually contains opposite polarities as long as there are more than one clock buffers. By doing so, the clock-induced power noise can be reduced almost everywhere. Please note, our approach does not provide an alternative to the power noise reduction using clock skew scheduling [7, 8, 9, 11]. Our technique can be combined with these approaches to further improve the power noise results. Also, our technique complements the power noise reduction using the decoupling capacitors [12, 13, 14] and can reduce the stress on the decoupling capacitor network.

SPICE based experimental results indicate that our techniques could reduce the average peak current and average delay variations by 50% and 51% respectively.

#### B. Impact to Delay Variation

Power/ground noise directly affects gate/buffer delay variation [5]. We present a first order analysis on the impact of clock buffer polarity assignment to gate/buffer delay variations. Without polarity assignment, i.e., with identical polarity for all clock buffers, all clock buffers have either simultaneous rising switchings, which cause decreased  $V_{dd}$  and almost no disturbance to  $V_{ss}$  (Figure 4(a)), or simultaneous falling switchings, which raise  $V_{ss}$  but have negligible influence on  $V_{dd}$  (Figure 4(b)). With polarity assignment, both  $V_{dd}$  and  $V_{ss}$  degrade but with less degree (Figure 4(c)).

Fig. 4. Power noise in a local region when (a) all buffers have rising switches, (b) all buffers have falling switchings, and (c) half of the buffers rising while the others falling.

We define power noise  $\Delta V_{dd}$  and ground noise  $\Delta V_{ss}$  as

$$\Delta V_{dd} = V_{dd} - V_{dd} \qquad \Delta V_{ss} = V_{ss} - V_{ss}$$

where  $V_{dd}$  and  $V_{ss}$  are ideal voltage values, and  $\tilde{V}_{dd}$  and  $\tilde{V}_{ss}$  are the actual voltages considering noise. As in [5], the power/ground noise can be equivalently evaluated by *differential mode noise*

$$\Delta V_{dif} = \Delta V_{dd} - \Delta V_{ss}$$

and *common mode noise*

$$\Delta V_{com} = \Delta V_{dd} + \Delta V_{ss}$$

Table I. An example of power/ground noise for the three cases in Figure 4.

| Case in Figure 4              | $\Delta V_{dd}$ | $\Delta V_{ss}$ | $\Delta V_{dif}$ | $\Delta V_{com}$ |

|-------------------------------|-----------------|-----------------|------------------|------------------|

| All rising (a)                | -0.2            | 0               | -0.2             | -0.2             |

| All falling (b)               | 0               | 0.2             | -0.2             | 0.2              |

| Half rising, half falling (c) | -0.1            | 0.1             | -0.2             | 0                |

In Table I, we list a rough numerical example of power/ground noise for the three cases in Figure 4. One can see that the polarity assignment does not change the differential mode noise but can reduce the common mode noise to nearly zero. According to [5], the variation of rising delay and falling delay can be expressed as

$$\Delta t_{rise} = -A \cdot \Delta V_{com} - B \cdot \Delta V_{dif} \tag{2.1}$$

and

$$\Delta t_{fall} = C \cdot \Delta V_{com} - D \cdot \Delta V_{dif} \tag{2.2}$$

respectively, where A, B, C and D are all positive constants dependent upon device and technology parameters, the input transition time and the gate output load. The differential mode noise  $(\Delta V_{dif})$  affects the delay to charge/discharge the capacitive load at the output of the gate. The larger the value of the differential mode noise faster is the charging and discharging of the capacitive load i.e. smaller is the gate delay. The common mode noise  $(\Delta V_{com})$  contributes to modifying the effective switching threshold of the gate. For a positive common mode noise, the switching threshold of the n/p transistors are higher than the threshold without noise i.e., the fall delay of the gate is larger with positive common mode noise. Similarly, for negative common mode noise the threshold of n/p transistors are lower, thus, the rise delay of the gate is larger than without common mode noise. According to [5], delay variation of a gate is linearly dependent on differential mode and common mode noise. Thus, rise and fall delay variations are expressed as a linear combination of differential mode noise  $(\Delta V_{dif})$  and common mode noise  $(\Delta V_{com})$ .

The three cases in Figure 4 result in approximately the same negative value of  $\Delta V_{dif}$  which contributes to roughly the same amount of delay increase. The case of Figure 4(a) has more rising delay increase and less falling delay increase due to its negative common mode noise. Symmetrically, the case of Figure 4(b) has less rising delay increase and more falling delay increase. In contrast, the common mode noise from the case of Figure 4(c) is almost zero and therefore does not contribute

to the delay variation. We consider the example of Table I to find the worst case delay variation of a gate. For simplicity, A, B, C and D are assumed to be equal to 1. Substituting the values of  $\Delta V_{dif}$  and  $\Delta V_{com}$  for Figure 4(a) and Figure 4(b) in equation (2.1) or equation (2.2), the delay variation without polarity assignment:

$$\Delta t_{w/o,pol} = 0.2 + 0.2 = 0.4$$

The worst case delay variation of the gate due to polarity assignment can be found similarly by substituting values of  $\Delta V_{dif}$  and  $\Delta V_{com}$  for Figure 4(c) in equation (2.1) or equation (2.2):

$$\Delta t_{w/o,pol} = 0.0 + 0.2 = 0.2$$

Hence, clock buffer polarity assignment, which corresponds to Figure 4(c), can reduce the worst case delay variation compared to using identical polarity (Figure 4(b) and Figure 4(b)).

#### C. Problem Formulation

Given a buffered clock tree with n buffers, assign either positive or negative signal polarity to every buffer such that peak current reduction is maximized in any region of arbitrary size.

For a region including all of the clock buffers, this objective requires that roughly a half of the buffers have positive polarity and the others have negative polarity. For a small region containing only two clock buffers, this formulation requests one of them is positive and the other is negative.

#### D. Polarity Assignment Algorithms

We have extended the application of three existing algorithms to solve the problem formulated in the previous section.

#### 1. Partitioning

First, a graph G = (V, E) is constructed with each node uniquely corresponding to a clock buffer and the node set V covers all of the clock buffers. There is an edge between every pair of nodes, i.e., this is a complete graph. Then, a bi-partitioning [16] is performed on G to partition V into two disjoint subsets  $V_+$  and  $V_-$  such that  $V = V_+ \cup V_-$  and  $||V_+| - |V_-|| \leq 1$ . The subsets  $V_+$  and  $V_-$  correspond to positive and negative polarities, respectively.

If two clock buffers are very close to each other, we prefer to separate them into different subsets (polarities). In a typical graph bi-partitioning [16], two nodes with a small edge weight in-between are more likely to be separated into two subsets. Thus, we let the weight of edge (i, j) to be  $d_{ij}$  which is the distance between node i and j. Since a typical bi-partitioning algorithm minimizes the total weight of edges in the cut, an edge with small weight (or distance) has a large chance to be in the cut and its two end nodes are separated in different subsets. The complexity of bi-partitioning algorithm is O(|V||E|) [16]. Since G is a complete graph, the number of edges is proportional to  $|V|^2$ . Thus, complexity of bi-partitioning is  $O(|V|^3)$ .

#### 2. 2-coloring on Minimum Spanning Tree

This is a very simple yet effective technique. First, a minimum spanning tree is generated for the nodes representing clock buffers. Again, each edge weight is defined as the distance between its two incident nodes. Then, a 2-coloring procedure is applied on the minimum spanning tree. In 2-coloring, two end nodes of an edge are always assigned with different colors (or polarities). For a tree, there is always a feasible solution for 2-coloring and it can be found easily. Each color corresponds to a polarity. Since the minimum spanning tree algorithm chooses short edges, two nodes close to each other have opposite polarities. The minimum spanning tree is generated using greedy method. We iterate for |V|-1 times to construct the minimum spanning tree, where |V| is the number of nodes in the graph G. During each iteration, we chose the shortest edge from the edges connected to the nodes of the spanning tree obtained in the previous iteration. Since graph G is a complete graph, the total number of edges is proportional to  $|V^2|$ . Thus, the time complexity of choosing the shortest edge during each iteration is  $O(|V|^2)$ . Since we have |V| - 1 iterations, the complexity of constructing the minimum spanning tree for the graph G is  $O(|V|^3)$ . The 2-coloring on minimum spanning tree is O(|E| + |V|) [17]. Thus, the complexity of polarity assignment due to 2-coloring on minimum spanning tree is  $O(|V|^3)$ .

#### 3. Recursive Min-matching

A graph G = (V, E) same as that in Section 1 is constructed. Performing minmatching (minimum weighted matching [18]) on this graph results in about |V|/2matched node pairs. In a min-matching, the total weight of the edges between matched nodes is minimized among all possible matchings. Then, we force the two nodes (clock buffers) in the same pair to have opposite polarities. Since the minmatching algorithm normally selects pairs corresponding to small edge weight, the min-matching based polarity assignment tends to let two nearby buffers have opposite polarities.

However, requiring opposite polarities is not a complete assignment for a pair of buffers. For example, for a pair of clock buffers (a, a'), we can either let a be positive and a' be negative (denoted as  $(a_+, a'_-)$ ), or let a be negative and a' be positive  $(a_-, a'_+)$ . Both of the polarity permutations satisfy the constraint of being opposite. We denote the former as positive permutation  $(a_+, a'_-)_+$  and the latter as negative permutation  $(a_-, a'_+)_-$ .

Fig. 5. Recursive min-matching.

The selection of polarity permutation is decided by performing another iteration of min-matching on the node pairs obtained in the first min-matching. In this iteration, the nodes of the graph is composed by the centroids of the node pairs matched in the previous iteration. Each edge weight is defined as the distance between corresponding centroids. If two node pairs ((a, a'), (b, b')) is selected to be matched in this iteration of min-matching, we have four different polarity permutations: (1)  $((a_+, a'_-)_+, (b_+, b'_-)_+)$ , (2)  $((a_+, a'_-)_+, (b_-, b'_+)_-)$ , (3)  $((a_-, a'_+)_-, (b_+, b'_-)_+)$ and (4)  $((a_-, a'_+)_-, (b_-, b'_+)_-)$ . The notations for these permutations can be abbreviated as ++, +-, -+ and --. These four cases are illustrated in Figure 5(b). It can be seen that ++ and -- have no difference to the four clock buffers themselves. Similarly, +- and -+ are equivalent to each other for the four buffers. But, ++ and -- are different from +- and -+. For the example of Figure 5(b), it is obvious that permutation ++ (at top) and -- (at bottom) are better than permutation +and -+ (in middle). Therefore, we choose ++ and -- which are fully denoted by  $((a_+, a'_-)_+, (b_+, b'_-)_+)_+$  and  $((a_-, a'_+)_-, (b_-, b'_+)_-)_-$ , respectively. The former is called positive permutation and the later is negative permutation. Now we have multiple node groups, each of which contains four nodes. The min-matching and polarity permutation selection can be repeated recursively on them till there is a single group containing all nodes.

We discuss how to decide polarity permutations for two matched node groups in general cases. Suppose two node groups A and B are matched. Each group has positive permutation  $A_+$  and  $B_+$  and negative permutation  $A_-$  and  $B_-$ . We need to choose + + / - - or + - / - + for these two groups. Each polarity permutation can be evaluated by a score which is defined as follows. For a polarity permutation such as ++, for each node v in a group, we consider all nodes of the other group which are nearby, i.e., nodes within certain distance D from v. If a nearby node of the other group has the same polarity as v, then the score of this polarity permutation is added by 1. Such score is counted for all nodes in one group. Finally, the polarity permutation with the smallest score is selected. For the example in Figure 5(b), the top (++) and bottom (--) permutations have score of 0 while the middle permutations (+- and -+) have score of 1. The algorithm of the min-matching based polarity assignment is summarized in Figure 6.

The complexity of the minimum weighted matching algorithm is  $O(|V|^3)$  [18], where |V| is the number of nodes in the graph G. The recursive min-matching algorithm is called |V|/2 times to perform polarity assignment to each clock buffer. Thus, the complexity of the recursive min-matching algorithm is  $O(|V|^4)$ . During each iteration of the min-matching algorithm the number of nodes reduces to half than its previous iteration. Thus, the actual number of nodes for most of the iterations is much smaller than |V|. Thus, the run time for the recursive min-matching algorithm is usually much faster than  $O(|V|^4)$ . We found the CPU run time for s35932 to be 0.603 sec, which is reasonable considering the size of the circuit. We implemented the data-structure in such way that, during each iteration the informations about the pair of matched nodes are stored in new memory location. The motivation behind this implementation is to reduce the execution time of the recursive algorithm. For this purpose, we need 2|V| extra memory nodes for the complete execution of the algorithm. The spatial complexity is acceptable considering the negligible run time of the recursive min-matching algorithm.

#### E. Buffer Type Selection and Post Processing

After buffer signal polarity assignment, we need to choose either inverting or noninverting type for each clock buffer. This procedure is straightforward. If a buffer has the same polarity as its parent buffer, it should use non-inverting type. Otherwise, an inverting type is applied.

In traditional clock tree designs, people prefer to use the same number of buffers on each source-sink path and use the same buffer type at each level [19]. This is illustrated in Figure 7(a). Such design can make clock skew robust to inter-die process variations. However, our buffer polarity assignment may result in different buffer types at a specific level (see Figure 7(b)). Therefore, we try to match the buffer types without affecting signal polarity in a post processing. After the buffer type matching, buffer sizing is performed to restore the original clock skew. Both the buffer type matching and buffer sizing are focused on flip-flops which are sequentially adjacent<sup>1</sup>,

<sup>&</sup>lt;sup>1</sup>A pair of flip-flops are sequentially adjacent if there is a pure combinational logic path in-between.

Subroutine:  $Polarity\_Assignment(G)$ **Input:** Graph G = (V, E)**Output:** Polarity assignment for each node  $v \in V$ 1. If  $|V| \leq 1$ , return 2. A set of node pairs  $P \leftarrow Min_Matching(G)$ 3. For each pair  $(u, v) \in P$  $p \leftarrow \text{centroid of } (u, v)$ 4. Select between  $(u_+, v_+)/(u_-, v_-)$ , 5. $(u_+, v_-)/(u_-, v_+)$ If  $(u_+, v_+)/(u_-, v_-)$  is selected 6.  $p_+ \leftarrow (u_+, v_+)$  $p_{-} \leftarrow (u_{-}, v_{-})$ 7. Else  $p_+ \leftarrow (u_+, v_-)$  $p_{-} \leftarrow (u_{-}, v_{+})$  $V \leftarrow V - \{u, v\} + \{p\}$ 8. 9.  $E \leftarrow$  all pairs in V  $10.Polarity\_Assignment(G)$

Fig. 6. Algorithm of recursive min-matching based polarity assignment.

because the fundamental timing constraints - setup time and hold constraints, are mainly for sequentially adjacent flip-flops.

#### 1. Buffer Type Matching

The buffer type matching is performed for a pair of sequentially adjacent flip-flops at a time. For such a pair i and j, we check the paths from the source to i and j. If there is any buffer type mismatch between the two paths at any level (like level 3 for i and j in Figure 7(b)), we swap the type of one mismatched buffers with the type of a nearby buffer while we try to maintain the signal polarity distribution unchanged. This procedure is repeated for every pair of sequentially adjacent flip-flops.

Fig. 7. (a) Original clock tree. (b) Buffer type mismatch occurs at level 2 and level 3 after polarity assignment.

The overall buffer type mismatch is evaluated by a mismatch-score defined as

$$MismatchScore = \sum_{i=1}^{n} criticality(i, j) \cdot diff(i, j)$$

where n is the total number of sequentially adjacent pairs, criticality(i, j) is the criticality between the sink pair (i,j) and diff(i,j) is the number of buffer types mismatches between the paths from sinks i and j to the root of the tree. For exam-

ple, the diff(i, j) and diff(j, k) values for the clock tree of Figure 7(b) is 1 and 2 respectively.

The clock skew between flip-flop i and j has to be within a permissible range  $[L_{ij}, U_{ij}]$  to satisfy setup time and hold time constraint. The size of the permissible range is represented by  $P_{ij} = U_{ij} - L_{ij}$ . The distance between i and j is denoted as  $D_{ij}$ . Then, the criticality for the pair i and j is estimated by [20]:

$$Criticality(i,j) = \alpha(\frac{P_{min}}{P_{ij}}) + (1-\alpha)(\frac{D_{ij}}{D_{max}})$$

where  $\alpha \in (0, 1)$  is the weight for permissible range,  $P_{min}$  is the minimum permissible range among all flip-flop pairs and  $D_{max}$  is the maximum distance among all pairs. This formula is based on the fact that the skew between a pair of flip-flops is critical if they have a small permissible range and/or they are far apart.

The algorithm for buffer type matching proceeds as follows. Initially, we calculate the most critical sink pair i and j that has the maximum product of criticality(i, j)and diff(i, j). The path from the two sinks to the root of the tree is is traversed in a bottom-up manner and the buffers at each level are compared subsequently. If a mismatch of the buffer type is found, the nearest neighbor of each buffer type is located. The mismatch-scores of the two buffers i.e. MS(i) and MS(j), are calculated assuming that the buffer has been swapped with its neighbor. The mismatch-scores of buffers are compared with the target mismatch-score (MS). The target mismatchscore is calculated once before the algorithm starts and it gets updated each time a buffer pair is swapped. If one or both of the mismatch-scores (MS(i), MS(j)) are smaller than the target scores then, the buffer pairs that minimizes the target score by greater amount is selected. If the selected buffer pairs on swapping maintain the initial polarity distribution intact, we qualify the buffers for swapping. A pair of buffers can retain the initial polarity distribution only if they have opposite polarities before swapping, then swapping of buffers would also cause a swapping of the polarities. Thus the initial polarity distribution is retained. However, if the swapped buffered nodes have same polarity, then the swap would cause both the polarities to invert and thus alters the initial polarity distribution. The swapping of buffer also affects polarity distribution of the subtree with the swapped buffers as its root. Thus we traverse from each swapped buffer in a top-down fashion and invert the buffer type of each buffer node in the subtree to maintain the original polarity.

If a buffer pair is qualified for swapping, we update the target mismatch-score with the updated scores i.e. either MS(i) or MS(j), and start over again by finding the critical most sink. On the other hand, if none of the buffer pair is qualified for swapping, then we continue the bottom-up traversal till next mismatch in the buffer type is found or the root node is encountered. If we reach the root then the next critical sink pair is selected and the same process is repeated for the selected sink pairs. If all the sink pairs are exhausted, then no further improvement in mismatch-score is possible and the algorithm stops.

# 2. Clock Skew Tuning

Since the original clock skew is changed due to the buffer type change in the polarity assignment, we run a clock skew tuning procedure after the buffer type matching to restore the original clock skew. This tuning procedure is same as [21] where the sizes of dummy capacitors are tuned toward desired clock skew. Therefore, the wirelength is not affected in this tuning. Although the area of dummy capacitance is increased, the buffer capacitance is often reduced when non-inverting buffers are replaced by inverting buffers in the polarity assignment. Hence, the overall capacitance is rarely increased as indicated in the experimental results.

# F. Experimental Results

The proposed procedure for power noise reduction was implemented in C on a Linux machine with 2 dual-core Intel Xeon processors of 3.2GHz and 8GB RAM. We performed experiments on two sets of benchmark circuits (a) ISCAS89 sequential circuits and (b) r1-r5 downloaded from GSRC Bookshelf [22]. The reason we employ ISCAS89 benchmark is that it has logic information and the reason for r1-r5 benchmark is that it is larger in size. The characteristics of the test cases are shown in Table II. The table indicates the number of clock sinks and the buffers for each test case.

For ISCAS89 benchmark circuits, the combinational logic gates were synthesized in Design Analyzer from Synopsys and placed using Silicon Ensemble from Cadence. The placement of the logic gates were done for 180nm library downloaded from the website [23]. The clock tree is then constructed using DME [24] and the clock buffers are placed similar as [19]. The logic gates were replaced by time-varying current sources connected between power and ground at grid points determined from the placement result of Silicon Ensemble. We replace the logic gates by current sources to make the power grid simulation feasible. The clock buffers are connected to the power and ground grids at locations determined from the clock tree construction. For SPICE simulation, we used 180nm model card obtained from [25] and  $V_{dd}$  was set to 2.5V. We chose 180nm model card for SPICE simulation to maintain consistency between placement result and the SPICE simulation.

r1-r5 benchmark circuits were obtained from [22]. The buffered clock tree was generated using the algorithm in [21]. Since r1-r5 does not have logic gate information, we conducted experiments on a standalone clock tree. For SPICE simulation, we used 65nm BSIM4 model card obtained from [25] and set  $V_{dd}$  to 1.0V.

| Case   | # Sinks | # Buffers |

|--------|---------|-----------|

| S9234  | 135     | 20        |

| S5378  | 164     | 25        |

| S13207 | 503     | 77        |

| S38584 | 1426    | 235       |

| S35932 | 1728    | 286       |

| r1     | 267     | 37        |

| r2     | 598     | 171       |

| r3     | 861     | 59        |

| r4     | 1903    | 303       |

| r5     | 3101    | 441       |

Table II. Characteristics of testcases

To measure the effectiveness of our technique, we perform simulations to determine the peak current, power supply noise, delay variation, power consumption, total capacitance and global skew. We measure the above mentioned parameters for base case (initial clock tree with no polarity assignment), previous work [10] and the three algorithms proposed. For each parameters, we insert several sampling points in the circuit to measure the value during SPICE transient simulation. We record the worst case at each sampling point. For power noise, peak current and power consumption parameters, the sampling points are on the power grid. The sampling points for skew measurement is set at the sink locations. For delay variation, we introduce few logic gates into our simulation structure. The logic gates are connected to power and ground grids at points selected randomly.

The results for ISCAS89 and r1-r5 benchmark circuits are summarized in the Tables on pages 28 through 32. Each table consists of set of 5 columns. The first set of columns presents the results of the base case. The second set presents the previous work [10]. This is followed by a set of three columns that present the the three proposed algorithms i.e. Partition, MST and Matching. In each table, we report either normalized average or average for both the benchmarks separately. The

final row in each table shows the normalized average or average for r1-r5 benchmark circuits, the other row with normalized average is for ISCAS89 benchmark. The normalized average is used to compare our procedure with the base case as well as the technique described in [10].

| Case     | Base  | Case  | Previo | us Work | Par  | tition | М    | ST    | Mat  | ching |

|----------|-------|-------|--------|---------|------|--------|------|-------|------|-------|

|          | Avg   | Max   | Avg    | Max     | Avg  | Max    | Avg  | Max   | Avg  | Max   |

| s5378    | 50.2  | 108.1 | 42.2   | 87.0    | 21.9 | 47.3   | 24.1 | 51.7  | 23.1 | 52.9  |

| s9234    | 41.30 | 69.4  | 34.6   | 60.1    | 22.0 | 40.1   | 19.1 | 33.4  | 18.0 | 32.0  |

| s13207   | 127.2 | 222.3 | 115.6  | 210.0   | 79.4 | 140.1  | 62.3 | 109.8 | 69.0 | 130.0 |

| s35932   | 95.1  | 154.1 | 90.3   | 180.5   | 53.0 | 92.4   | 52.4 | 85.5  | 51.4 | 94.4  |

| s38584   | 87.5  | 144.9 | 73.9   | 122.9   | 51.1 | 89.3   | 44.6 | 72.0  | 50.2 | 88.6  |

| Nor Ave. | 1.00  | 1.00  | 0.87   | 0.88    | 0.55 | 0.56   | 0.50 | 0.50  | 0.51 | 0.53  |

| r1       | 15.9  | 24.5  | 12.4   | 20.2    | 7.9  | 11.9   | 8.7  | 14.3  | 8.5  | 13.4  |

| r2       | 43.8  | 82.1  | 35.1   | 71.1    | 26.1 | 46.3   | 25.8 | 45.7  | 26.1 | 48.1  |

| r3       | 21.6  | 37.0  | 20.4   | 37.5    | 11.2 | 20.0   | 12.0 | 20.4  | 11.2 | 28.5  |

| r4       | 80.7  | 156.4 | 70.5   | 138.4   | 46.2 | 85.9   | 40.7 | 74.8  | 40.7 | 77.4  |

| r5       | 111.9 | 156.7 | 94.6   | 132.7   | 64.2 | 90.1   | 63.6 | 90.8  | 60.8 | 85.0  |

| Nor Ave. | 1.00  | 1.00  | 0.85   | 0.88    | 0.55 | 0.54   | 0.54 | 0.54  | 0.54 | 0.53  |

Table III. Results for peak current (mA)

Table IV. Results for power noise (mV)

| Case     | Base  | Case  | Previo | us Work | Par  | tition | M    | ST    | Mat  | ching |

|----------|-------|-------|--------|---------|------|--------|------|-------|------|-------|

|          | Avg   | Max   | Avg    | Max     | Avg  | Max    | Avg  | Max   | Avg  | Max   |

| s5378    | 42.2  | 92.8  | 39.8   | 83.8    | 21.5 | 48.8   | 23.1 | 46.6  | 22.7 | 45.8  |

| s9234    | 34.3  | 69.1  | 27.5   | 62.5    | 20.1 | 50.7   | 16.4 | 50.1  | 15.5 | 50.1  |

| s13207   | 170.0 | 247.8 | 149.2  | 239.0   | 97.5 | 143.1  | 80.9 | 125.6 | 91.2 | 91.2  |

| s35932   | 169.6 | 298.0 | 155.4  | 295.2   | 92.1 | 182.4  | 88.8 | 167.7 | 85.2 | 167.5 |

| s38584   | 140.0 | 255.0 | 114.0  | 219.4   | 76.4 | 183.1  | 67.2 | 143.1 | 73.9 | 159.2 |

| Nor Ave. | 1.00  | 1.00  | 0.87   | 0.92    | 0.55 | 0.63   | 0.50 | 0.57  | 0.51 | 0.60  |

| r1       | 6.2   | 10.1  | 5.4    | 9.2     | 3.0  | 4.4    | 3.4  | 4.9   | 3.2  | 4.3   |

| r2       | 15.6  | 25.7  | 12.8   | 23.2    | 10.0 | 16.5   | 10.0 | 16.1  | 10.2 | 17.7  |

| r3       | 9.6   | 13.4  | 8.8    | 13.0    | 5.0  | 8.1    | 5.6  | 8.9   | 5.2  | 7.6   |

| r4       | 36.5  | 51.7  | 30.2   | 43.3    | 22.5 | 32.8   | 18.8 | 27.2  | 18.5 | 26.0  |

| r5       | 61.4  | 79.1  | 53.4   | 75.4    | 32.4 | 43.8   | 43.8 | 30.5  | 41.2 | 42.7  |

| Nor Ave. | 1.00  | 1.00  | 0.86   | 0.91    | 0.56 | 0.57   | 0.55 | 0.56  | 0.54 | 0.54  |

| Case     | Base  | Case  | Previo | us Work | Part  | ition | М    | ST    | Mat  | ching |

|----------|-------|-------|--------|---------|-------|-------|------|-------|------|-------|

|          | Avg   | Max   | Avg    | Max     | Avg   | Max   | Avg  | Max   | Avg  | Max   |

| s5378    | 44.8  | 83.6  | 39.7   | 78.2    | 20.3  | 53.0  | 22.5 | 42.4  | 21.1 | 42.5  |

| s9234    | 31.3  | 63.2  | 27.4   | 60.1    | 19.5  | 39.6  | 14.5 | 39.3  | 13.4 | 39.4  |

| s13207   | 156.3 | 227.8 | 147.2  | 227.3   | 104.1 | 156.1 | 79.0 | 122.1 | 85.1 | 129.0 |

| s35932   | 154.0 | 295.0 | 152.0  | 290.0   | 87.7  | 174.5 | 88.1 | 176.7 | 87.8 | 184.9 |

| s38584   | 128.1 | 245.4 | 110.1  | 193.9   | 77.4  | 168.9 | 69.1 | 140.2 | 79.2 | 168.3 |

| Nor Ave. | 1.00  | 1.00  | 0.91   | 0.93    | 0.58  | 0.64  | 0.51 | 0.56  | 0.52 | 0.60  |

| r1       | 7.1   | 10.8  | 6.1    | 10.3    | 3.2   | 4.5   | 3.6  | 5.1   | 3.9  | 4.7   |

| r2       | 18.5  | 30.3  | 14.6   | 27.0    | 10.4  | 17.8  | 10.1 | 16.9  | 10.3 | 17.8  |

| r3       | 10.6  | 15.3  | 10.2   | 15.0    | 5.6   | 9.0   | 5.8  | 9.2   | 5.4  | 8.3   |

| r4       | 39.8  | 56.4  | 33.8   | 51.3    | 21.4  | 30.8  | 19.6 | 28.4  | 19.9 | 28.6  |

| r5       | 58.5  | 78.2  | 53.7   | 72.4    | 31.9  | 42.9  | 30.0 | 40.5  | 30.5 | 41.5  |

| Nor Ave. | 1.00  | 1.00  | 0.87   | 0.93    | 0.52  | 0.54  | 0.52 | 0.53  | 0.53 | 0.52  |

Table V. Results for ground noise (mV)

Table VI. Results for delay variation (ps)

| Case     | Base | Case | Previ | ous Work | Part | ition | Μ    | ST   | Mate | ching |

|----------|------|------|-------|----------|------|-------|------|------|------|-------|

|          | Avg  | Max  | Avg   | Max      | Avg  | Max   | Avg  | Max  | Avg  | Max   |

| s5378    | 0.72 | 0.96 | 0.52  | 0.73     | 0.33 | 0.36  | 0.28 | 0.30 | 0.25 | 0.29  |

| s9234    | 0.50 | 0.70 | 0.39  | 0.57     | 0.35 | 0.45  | 0.31 | 0.42 | 0.33 | 0.43  |

| s13207   | 1.60 | 2.10 | 1.40  | 2.00     | 1.05 | 1.20  | 0.80 | 0.91 | 0.81 | 0.93  |

| s35932   | 3.30 | 3.60 | 3.10  | 3.30     | 1.62 | 1.81  | 1.51 | 1.70 | 1.43 | 1.60  |

| s38584   | 2.80 | 2.90 | 2.56  | 2.71     | 1.55 | 1.70  | 1.41 | 1.59 | 1.50 | 1.70  |

| Nor Ave. | 1.00 | 1.00 | 0.84  | 0.87     | 0.57 | 0.53  | 0.49 | 0.46 | 0.50 | 0.48  |

| r1       | 0.41 | 0.48 | 0.38  | 0.40     | 0.21 | 0.24  | 0.19 | 0.23 | 0.22 | 0.25  |

| r2       | 1.29 | 1.33 | 1.23  | 1.32     | 0.75 | 0.77  | 0.80 | 0.83 | 0.76 | 0.78  |

| r3       | 0.53 | 0.6  | 0.42  | 0.47     | 0.28 | 0.33  | 0.27 | 0.32 | 0.25 | 0.30  |

| r4       | 2.00 | 2.16 | 1.95  | 2.10     | 1.05 | 1.15  | 1.02 | 1.06 | 1.10 | 1.21  |

| r5       | 2.98 | 3.24 | 2.71  | 2.95     | 1.54 | 1.62  | 1.65 | 1.80 | 1.70 | 1.82  |

| Nor Ave. | 1.00 | 1.00 | 0.91  | 0.90     | 0.53 | 0.53  | 0.53 | 0.53 | 0.54 | 0.54  |

In the data Tables III, IV, V, VI and VIII, we report the average and the maximum results among these worst case values from different sampling points. In the data Table IX, we report the resource consumption for both benchmark circuits. For each of the 5 cases in Table IX, we report average value of the total power consumption, total capacitance. The total capacitance is the sum of tuning capacitance and

| Case   | Base Case | Previous Work | Partition | MST  | Matching |

|--------|-----------|---------------|-----------|------|----------|

| s5378  | 4.9       | 15.7          | 16.0      | 17.7 | 20.0     |

| s9234  | 4.0       | 14.1          | 22.0      | 18.6 | 19.0     |

| s13207 | 10.2      | 12.4          | 15.5      | 18.3 | 19.8     |

| s35932 | 30.0      | 33.0          | 35.0      | 25.0 | 35       |

| s38584 | 28.0      | 35.0          | 29.0      | 35.0 | 32.0     |

| Ave.   | 15.4      | 22.0          | 23.5      | 22.9 | 25.2     |

| r1     | 5.4       | 7.2           | 9.6       | 9.0  | 10.2     |

| r2     | 31.5      | 31.4          | 35.2      | 31.5 | 35.0     |

| r3     | 20.0      | 18.5          | 19.0      | 14.1 | 18.6     |

| r4     | 12.5      | 27.2          | 19.4      | 22.8 | 19.3     |

| r5     | 12.8      | 12.4          | 11.7      | 19.6 | 17.8     |

| Ave.   | 16.5      | 19.3          | 19.0      | 19.4 | 20.2     |

Table VII. Results for nominal skew (ps)

Table VIII. Results for skew due to variation for ISCAS89 (ps)

| Case   | Base  | Case  | Previo | us Work | Part  | ition | M     | ST    | Mate  | ching |

|--------|-------|-------|--------|---------|-------|-------|-------|-------|-------|-------|

|        | Avg   | Max   | Avg    | Max     | Avg   | Max   | Avg   | Max   | Avg   | Max   |

| s5378  | 48.1  | 93.6  | 50.0   | 94.6    | 46.4  | 84.8  | 50.1  | 92.0  | 49.8  | 90.5  |

| s9234  | 5.5   | 6.8   | 17.9   | 19.0    | 19.2  | 20.1  | 18.7  | 19.2  | 19.0  | 19.4  |

| s13207 | 76.2  | 116.8 | 72.7   | 105.1   | 76.0  | 115.5 | 75.4  | 109.2 | 72.9  | 106.1 |

| s35932 | 184.6 | 265.0 | 173.4  | 278.9   | 181.1 | 265.0 | 166.5 | 248.7 | 183.5 | 267.0 |

| s38584 | 129.5 | 182.4 | 173.4  | 193.1   | 133.2 | 199   | 123.5 | 177.8 | 136.4 | 189.3 |

| Ave.   | 88.8  | 139.9 | 90.4   | 138.1   | 91.2  | 136.9 | 86.9  | 129.4 | 92.3  | 134.5 |

buffer capacitance. The CPU run time is reported in Table X. For CPU run time, we include the CPU run time to generate SPICE files for each of the algorithm and does not include the SPICE run time.

We post process the clock tree obtained (after assigning different polarities) to tune the skew by techniques suggested in [21]. By doing that, we bring the skew to be less than the required skew bound for all the test cases. The skew bound was set to 35*psec* for all the test cases. The skew results are reported in Table VII.

The skew due to variation was determined for ISCAS89 benchmark circuits. The result for skew was obtained by running 1000 Monte Carlo simulations for each case. The following parameters are varied (a) channel Length (b) threshold voltage and (c)

| Case     | Base  | Case  | Previo | us Work | Part  | ition | M     | ST    | Mate  | ching |

|----------|-------|-------|--------|---------|-------|-------|-------|-------|-------|-------|

|          | Pow   | Cap   | Pow    | Cap     | Pow   | Cap   | Pow   | Cap   | Pow   | Cap   |

| s5378    | 38.2  | 7.72  | 36.4   | 7.59    | 23.7  | 4.62  | 26.6  | 5.11  | 27.4  | 5.31  |

| s9234    | 31.8  | 6.10  | 30.2   | 5.71    | 25.0  | 4.86  | 22.3  | 3.81  | 21.0  | 3.46  |

| s13207   | 117.8 | 56.0  | 105.6  | 54.7    | 94.6  | 50.5  | 88.5  | 47.6  | 88.2  | 46.1  |

| s35932   | 526.0 | 129.2 | 548.0  | 157.3   | 480.0 | 97.9  | 443.6 | 130.0 | 471.0 | 127.2 |

| s38584   | 394.9 | 90.00 | 409.2  | 107.8   | 330.3 | 67.40 | 294.0 | 82.40 | 313.6 | 73.70 |

| Nor Ave. | 1.00  | 1.00  | 0.97   | 1.06    | 0.79  | 0.76  | 0.75  | 0.81  | 0.76  | 0.77  |

| r1       | 1.4   | 0.41  | 1.4    | 0.52    | 1.1   | 0.42  | 1.1   | 0.42  | 1.0   | 0.46  |

| r2       | 6.1   | 1.90  | 6.4    | 3.34    | 4.4   | 1.84  | 4.5   | 2.13  | 4.3   | 1.81  |

| r3       | 2.7   | 0.75  | 2.8    | 1.01    | 2.0   | 0.84  | 2.2   | 0.95  | 2.1   | 0.84  |

| r4       | 10.6  | 3.35  | 10.7   | 4.85    | 7.8   | 3.74  | 8.2   | 5.21  | 7.5   | 5.13  |

| r5       | 14.0  | 4.90  | 14.9   | 6.10    | 10.5  | 5.34  | 10.9  | 5.77  | 10.0  | 5.13  |

| Nor Ave. | 1.00  | 1.00  | 1.04   | 1.41    | 0.75  | 1.06  | 0.78  | 1.22  | 0.73  | 1.14  |

Table IX. Results for total resource consumption (power in mW and cap in pf)

temperature. The above parameters were varied with mean as nominal value and a standard deviation of 3%. In Table VIII, we report the average and maximum values of the skew due to variation.

The following observations could be drawn from the results:

- Our techniques clearly dominate the method suggested in [10] in terms of peak current, power supply noise, delay variation and power consumption.

- The reduction in peak current is significant, 46%-50% and 45%-47% respectively for ISCAS89 and r1-r5 benchmark circuits. In fact, in few cases it could lead up to more than 50% peak current reduction. Such high reductions in peak current have a direct positive impact on circuit reliability.

- The power supply noise and ground noise come down by 45-50% (45-46%) and 42-49% (47-48%) respectively for ISCAS89 (r1-r5) benchmark. For s38584, a power supply noise reduction of 52% is achieved. This result indicates that our algorithm is efficient in reducing power supply noise for even bigger circuits.

| Case     | Base Case | Previous Work | Partition | MST   | Matching |

|----------|-----------|---------------|-----------|-------|----------|

| s5378    | 0.200     | 0.210         | 0.253     | 0.275 | 0.245    |

| s9234    | 0.190     | 0.195         | 0.240     | 0.256 | 0.245    |

| s13207   | 0.249     | 0.301         | 0.320     | 0.331 | 0.315    |

| s35932   | 0.545     | 0.712         | 0.745     | 0.81  | 0.803    |

| s38584   | 0.539     | 0.695         | 0.701     | 0.750 | 0.719    |

| Nor Ave. | 1.00      | 1.17          | 1.29      | 1.38  | 1.32     |

| r1       | 0.340     | 0.350         | 0.480     | 0.460 | 0.440    |