# BASEBAND ANALOG CIRCUITS IN DEEP-SUBMICRON CMOS TECHNOLOGIES TARGETED FOR MOBILE MULTIMEDIA

A Dissertation

by

# VIJAYAKUMAR DHANASEKARAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

August 2008

Major Subject: Electrical Engineering

# BASEBAND ANALOG CIRCUITS IN DEEP-SUBMICRON CMOS

# TECHNOLOGIES TARGETED FOR MOBILE MULTIMEDIA

A Dissertation

by

# VIJAYAKUMAR DHANASEKARAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

| Co-Chairs of Committee, | Edgar Sanchez-Sinencio   |

|-------------------------|--------------------------|

|                         | Jose Silva-Martinez      |

| Committee Members,      | Shankar P. Bhattacharyya |

|                         | Duncan M. Walker         |

| Head of Department,     | Costas N. Georghiades    |

August 2008

Major Subject: Electrical Engineering

#### ABSTRACT

# Baseband Analog Circuits in Deep-Submicron CMOS Technologies Targeted for Mobile Multimedia. (August 2008)

Vijayakumar Dhanasekaran, B.E., Bharathiar University, Coimbatore, India

Co-Chairs of Advisory Committee: Dr. Edgar Sanchez-Sinencio Dr. Jose Silva-Martinez

Three main analog circuit building blocks that are important for a mixed-signal system are investigated in this work. New building blocks with emphasis on power efficiency and compatibility with deep-submicron technology are proposed and experimental results from prototype integrated circuits are presented.

Firstly, a 1.1GHz, 5th order, active-LC, Butterworth wideband equalizer that controls inter-symbol interference and provides anti-alias filtering for the subsequent analog to digital converter is presented. The equalizer design is based on a new series LC resonator biquad whose power efficiency is analytically shown to be better than a conventional Gm-C biquad. A prototype equalizer is fabricated in a standard 0.18µm CMOS technology. It is experimentally verified to achieve an equalization gain programmable over a 0-23dB range, 47dB SNR and -48dB IM3 while consuming 72mW of power. This corresponds to more than 7 times improvement in power efficiency over conventional Gm-C equalizers.

Secondly, a load capacitance aware compensation for 3-stage amplifiers is presented. A class-AB 16 $\Omega$  headphone driver designed using this scheme in 130nm

technology is experimentally shown to handle 1pF to 22nF capacitive load while consuming as low as 1.2mW of quiescent power. It can deliver a maximum RMS power of 20mW to the load with -84.8dB THD and 92dB peak SNR, and it occupies a small area of 0.1mm<sup>2</sup>. The power consumption is reduced by about 10 times compared to drivers that can support such a wide range of capacitive loads.

Thirdly, a novel approach to design of ADC in deep-submicron technology is described. The presented technique enables the usage of time-to-digital converter (TDC) in a delta-sigma modulator in a manner that takes advantage of its high timing precision while noise-shaping the error due to its limited time resolution. A prototype ADC designed based on this deep-submicron technology friendly architecture was fabricated in a 65nm digital CMOS technology. The ADC is experimentally shown to achieve 68dB dynamic range in 20MHz signal bandwidth while consuming 10.5mW of power. It is projected to reduce power and improve speed with technology scaling.

#### ACKNOWLEDGEMENTS

I would like to thank my committee co-chairs, Dr. Edgar Sanchez-Sinencio and Dr. Jose Silva-Martinez for their guidance and support during the course of my research. I am very thankful for their advice and numerous discussions on the research projects during my stay at Texas A&M. I also thank Dr. Shankar P. Bhattacharyya and Dr. Duncan M. Walker for serving on my committee.

I am grateful to MOSIS, UMC and TI for providing the fabrication support. I would like to thank Gaurav Chandra and Neeraj Nayak of Texas Instruments for the discussions and reviews on the design and layout of the time-domain ADC. I also thank my colleagues Manisha Gambhir and Mohamed Mostafa for their contribution to the ADC project. I am indebted to Chinmaya Mishra, Lei Chen and Erik Pankratz for the layout and verification help they provided.

I would like to extend my thanks to Dr. Aydin Karsilayan and Raghavendra Kulkarni for providing computer and design kit support.

Finally, thanks to my parents and brothers for their love and encouragement.

# TABLE OF CONTENTS

| I       INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ABSTRAC          | Τ                                                                                    | iii                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| LIST OF FIGURES<br>LIST OF TABLES<br>CHAPTER<br>I INTRODUCTION<br>1.1 Motivation and Goals<br>1.2 Organization<br>II A 1.1GHz 5th ORDER ACTIVE-LC BUTTERWORTH TYPE<br>EQUALIZING FILTER<br>2.1 Introduction<br>2.1.1 Previous Equalizer Solutions<br>2.1.2 Need for LC Equalizer<br>2.2 Analysis of Series Resonator Based Equalizer Section<br>2.2.1 Frequency Response<br>2.2.2 Noise<br>2.2.3 Relative Power Efficiency.<br>2.2.4 Effect of Quality Factor of the Inductor.<br>2.2.5 Linearity<br>2.2.6 Area<br>2.3 Proposed Architecture and Circuit Implementation<br>2.3.1 Biquad<br>2.3.2 Negative Capacitance<br>2.3.3 Common-mode Feedback<br>2.4.1 Test Setup<br>2.4.1 Test Setup | ACKNOWLEDGEMENTS |                                                                                      |                                                                                |

| LIST OF TABLES<br>CHAPTER I INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TABLE OF         | CONTENTS                                                                             | vi                                                                             |

| I       INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LIST OF FI       | GURES                                                                                | ix                                                                             |

| I       INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LIST OF T        | ABLES                                                                                | xvi                                                                            |

| 1.1 Motivation and Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHAPTER          |                                                                                      |                                                                                |

| 1.2 Organization         II       A 1.1GHz 5th ORDER ACTIVE-LC BUTTERWORTH TYPE<br>EQUALIZING FILTER         2.1 Introduction         2.1.1 Previous Equalizer Solutions         2.1.2 Need for LC Equalizer         2.2 Analysis of Series Resonator Based Equalizer Section         2.2.1 Frequency Response         2.2.2 Noise         2.2.3 Relative Power Efficiency         2.2.4 Effect of Quality Factor of the Inductor         2.2.5 Linearity         2.2.6 Area         2.3 Proposed Architecture and Circuit Implementation         2.3.1 Biquad         2.3.2 Negative Capacitance         2.3.3 Common-mode Feedback         2.4.1 Test Setup                               | Ι                | INTRODUCTION                                                                         | 1                                                                              |

| EQUALIZING FILTER         2.1 Introduction         2.1.1 Previous Equalizer Solutions         2.1.2 Need for LC Equalizer         2.2 Analysis of Series Resonator Based Equalizer Section         2.2.1 Frequency Response         2.2.2 Noise         2.2.3 Relative Power Efficiency         2.2.4 Effect of Quality Factor of the Inductor         2.2.5 Linearity         2.2.6 Area         2.3 Proposed Architecture and Circuit Implementation         2.3.1 Biquad         2.3.2 Negative Capacitance         2.3.3 Common-mode Feedback         2.4 Test Setup                                                                                                                    |                  |                                                                                      | 1<br>3                                                                         |

| <ul> <li>2.1.1 Previous Equalizer Solutions</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Π                |                                                                                      | 5                                                                              |

| 2.4.1 Test Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | <ul> <li>2.1.1 Previous Equalizer Solutions</li></ul>                                | 5<br>5<br>10<br>11<br>13<br>13<br>19<br>20<br>21<br>22<br>26<br>28<br>30<br>31 |

| 2.4.2 Measurements Results and Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | <ul><li>2.4.1 Test Setup</li><li>2.4.2 Measurements Results and Comparison</li></ul> | 36<br>36<br>38<br>43                                                           |

Page

|     | 2.5.1 Future Work                                                                                                                                 | 43                                                                                                 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| III | A 1.2mW 1.6Vpp SWING CLASS-AB 16Ω HEADPHONE<br>DRIVER CAPABLE OF HANDLING LOAD CAPACITANCE<br>UP TO 22nF                                          | 45                                                                                                 |

|     | <ul> <li>3.1 Introduction</li></ul>                                                                                                               | 45<br>48<br>53<br>53<br>60<br>69<br>80<br>81<br>82<br>83<br>85<br>86<br>89<br>90<br>91<br>96<br>96 |

| IV  | <ul> <li>A 20MHz SIGNAL BANDWIDTH 68dB DYNAMIC RANGE<br/>CONTINUOUS TIME ΔΣ ADC BASED ON TIME DOMAIN<br/>QUANTIZER AND FEEDBACK ELEMENT</li></ul> | 97<br>97<br>100<br>105<br>106<br>108<br>110<br>117<br>119<br>119                                   |

|          | 4.3.2 Impulse Response of PWM Generator and TDC      | 124 |

|----------|------------------------------------------------------|-----|

|          | 4.3.3 Excess Loop Delay                              | 126 |

|          | 4.3.4 Clock Jitter                                   | 129 |

|          | 4.4 Design of 20MHz BW, 10bit ADC Using the Proposed |     |

|          | Architecture                                         | 132 |

|          | 4.4.1 NTF Design and Loop Filter Topology            | 133 |

|          | 4.4.2 Loop Delay Compensation and Coefficient        |     |

|          | Calculations                                         | 135 |

|          | 4.4.3 PWM Generator Design                           | 136 |

|          | 4.4.4 TDC Design                                     | 139 |

|          | 4.4.5 Noise Contributors and Budgeting               | 142 |

|          | 4.5 Simulation and Experimental Results              | 145 |

|          | 4.6 Summary                                          | 156 |

|          | 4.6.1 Future Work                                    | 157 |

| V        | CONCLUSIONS                                          | 158 |

|          | 5.1 Summary                                          | 158 |

|          | 5.2 Possible Area for Future Work                    |     |

|          | 5.2 Possible Alea for Future work                    | 159 |

| REFERENC | CES                                                  | 160 |

| VITA     |                                                      | 168 |

|          |                                                      |     |

# Page

# LIST OF FIGURES

| FIGURE |                                                                                        |    |

|--------|----------------------------------------------------------------------------------------|----|

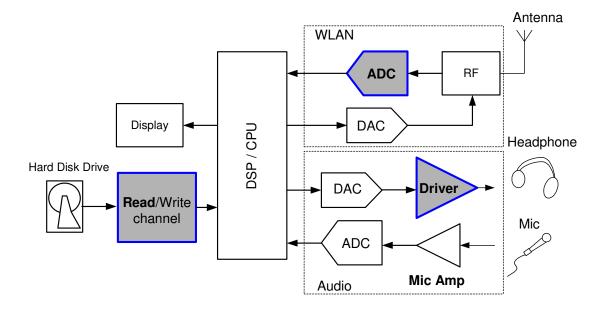

| 1.1    | Block diagram of a typical mobile multimedia device                                    | 2  |

| 2.1    | Boost architecture based on single terminated ladder reported in [5]                   | 6  |

| 2.2(a  | ) Biquad section of the boost filter reported in [8]                                   | 7  |

| 2.2(b  | ) Equivalent circuit                                                                   | 7  |

| 2.3    | Scheme used in [9] to realize equalization gain                                        | 9  |

| 2.4    | Gm-C biquad used to realize an equalizer section                                       | 10 |

| 2.5(a  | ) Series resonator prototype                                                           | 12 |

| 2.5(b  | ) Transistor implementation                                                            | 12 |

| 2.6    | Proposed Series resonator LC based equalizer section                                   | 12 |

| 2.7    | Impedance scaling of a Gm-C integrator                                                 | 14 |

| 2.8    | P <sub>Gm-C</sub> /P <sub>Gm11</sub> vs quality factor                                 | 17 |

| 2.9    | Normalized power-noise product for Lowpass path                                        | 17 |

| 2.10   | Normalized power-noise product for bandpass path                                       | 18 |

| 2.11   | Relative power efficiency versus quality factor                                        | 19 |

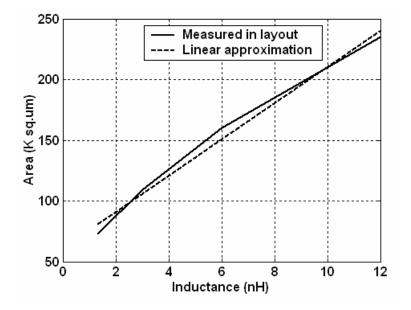

| 2.12   | Area of the inductor as a function of its value                                        | 23 |

| 2.13   | Area comparison for Gm-C and LC equalizer section                                      | 24 |

| 2.14   | Area of LC and Gm-C equalizer sections as a function of SNR at 2GHz                    | 25 |

| 2.15   | Simplified schematic (single-ended) of the 5 <sup>th</sup> order<br>Butterworth filter | 26 |

| FIGURE |         |                                                                                             |    |

|--------|---------|---------------------------------------------------------------------------------------------|----|

|        | 2.16    | Schematic of the proposed fully differential series<br>LC resonator based equalizer section | 29 |

|        | 2.17    | Negative capacitance emulation circuit                                                      | 30 |

|        | 2.18    | Implemented CMFB loop                                                                       | 32 |

|        | 2.19    | Proposed EA and split frequency current sources                                             | 33 |

|        | 2.20(a) | AC response of the CMFB loop                                                                | 35 |

|        | 2.20(b) | Poles and zeros in s-plane                                                                  | 35 |

|        | 2.21    | Chip micrograph                                                                             | 36 |

|        | 2.22    | Test setup for measurement of the transfer function of the equalizer                        | 37 |

|        | 2.23    | PCB used for testing the equalizer testchip                                                 | 38 |

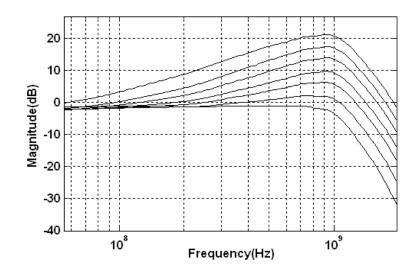

|        | 2.24    | AC magnitude across boost measured using network analyzer                                   | 39 |

|        | 2.25    | Measured group delay response                                                               | 40 |

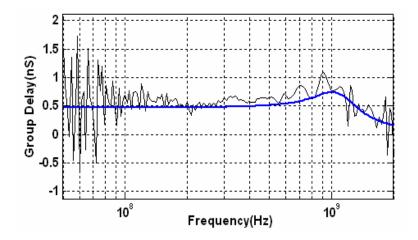

|        | 2.26    | Measured intermodulation distortion                                                         | 41 |

|        | 2.27    | Bandwidth programming of LC equalizer                                                       | 44 |

|        | 3.1     | Driver module to be deployed in a wide range of platforms                                   | 45 |

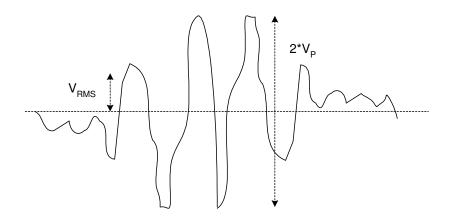

|        | 3.2     | Supply voltage utilization limit due to crest factor                                        | 47 |

|        | 3.3     | Folded mesh circuit for low voltage class-AB biasing                                        | 49 |

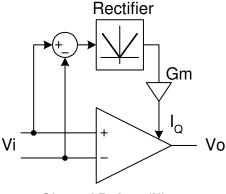

|        | 3.4     | Adaptive quiescent current generation                                                       | 50 |

|        | 3.5     | Nested miller compensation topology                                                         | 51 |

|        | 3.6(a)  | Simplified representation of 3-stage amplifier                                              | 55 |

|        | 3.6(b)  | Cc1 providing unity feedback around second and third stage                                  | 55 |

|        | 3.6(c)  | Equivalent circuit                                                                          | 55 |

Page

| FIGURE |

|--------|

|--------|

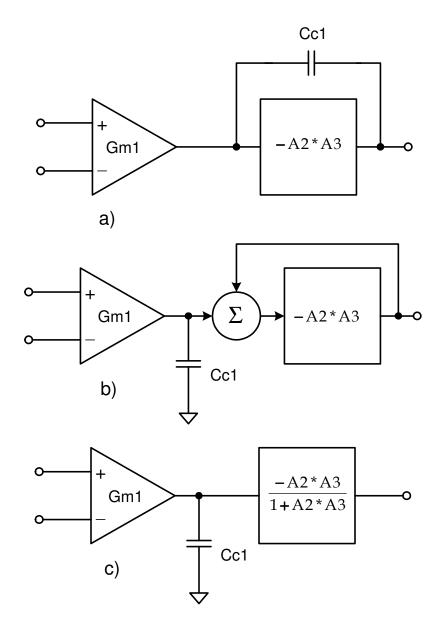

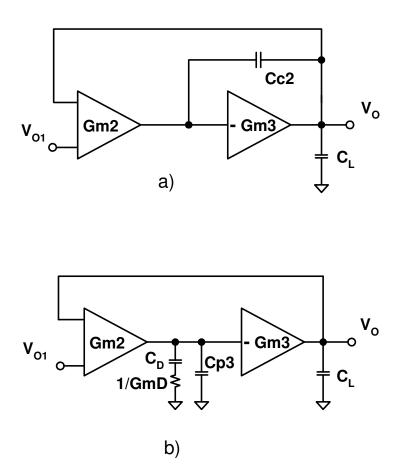

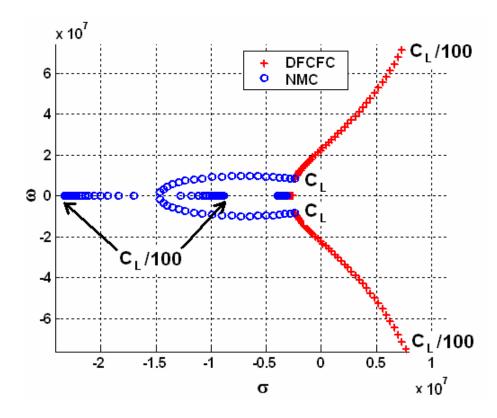

| 3.7(a) | Second and third stage in unity feedback loop - NMC                                                                                                | 57 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7(b) | Second and third stage in unity feedback loop - DFCFC                                                                                              | 57 |

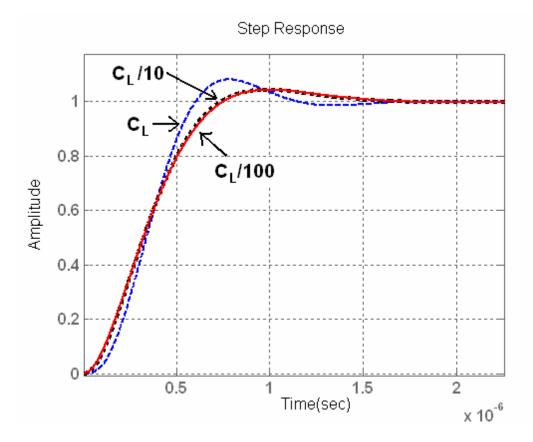

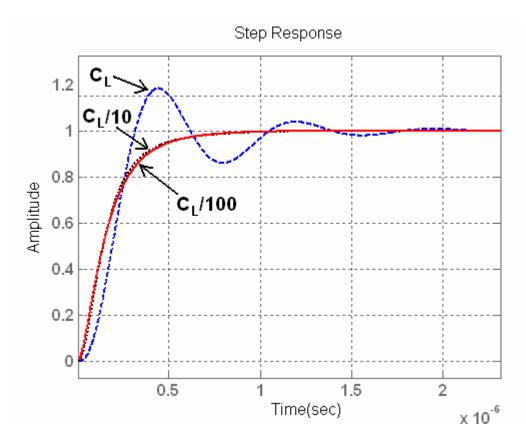

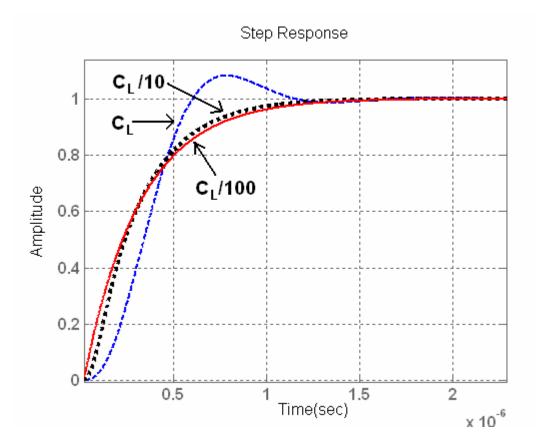

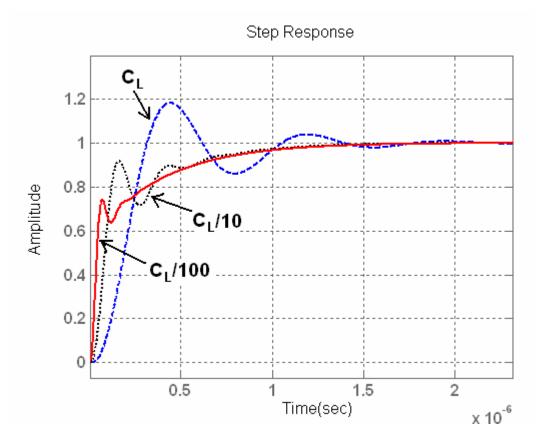

| 3.8    | Step response of NMC with Butterworth poles<br>for load capacitance = $C_L$                                                                        | 61 |

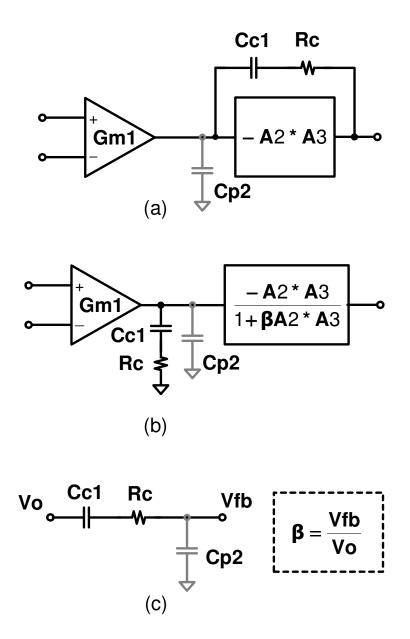

| 3.9(a) | 3-stage amplifier with LHP zero resistor                                                                                                           | 62 |

| 3.9(b) | Equivalent circuit                                                                                                                                 | 62 |

| 3.9(c) | Feedback factor for A2*A3                                                                                                                          | 62 |

| 3.10   | Step response of NMC with 45degrees phase margin for load capacitance = $C_L$                                                                      | 64 |

| 3.11   | Step response of DFCFC with Butterworth poles<br>for load capacitance = $C_L$                                                                      | 65 |

| 3.12   | Step response of DFCFC with 45degrees phase margin for load capacitance = $C_L$                                                                    | 66 |

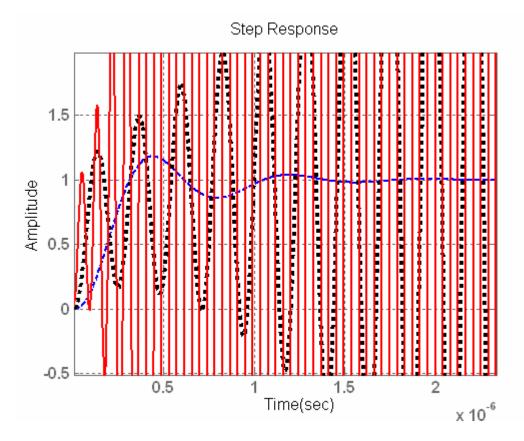

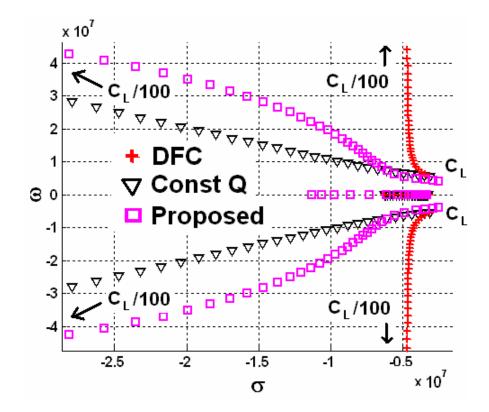

| 3.13   | Pole locus as load capacitance is varied from $C_L$ to $C_L/100$<br>(Butterworth pole constellation for load capacitance = $C_L$ )                 | 68 |

| 3.14   | Pole locus as load capacitance is varied from $C_L$ to $C_L/100$ (45degree phase margin design for load capacitance = $C_L$ )                      | 69 |

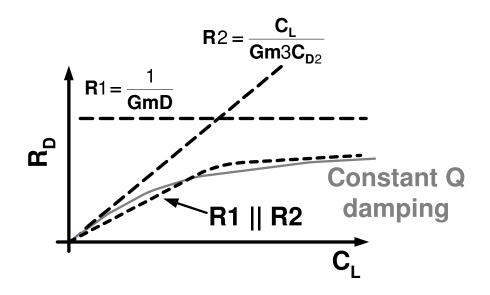

| 3.15   | Damping resistance requirement for constant Q complex poles                                                                                        | 70 |

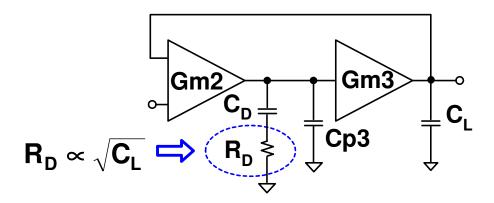

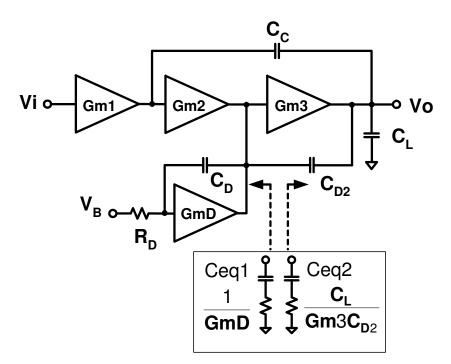

| 3.16   | Architecture of the proposed compensation scheme                                                                                                   | 71 |

| 3.17   | Piecewise approximation for proportional-to-square-root resistor                                                                                   | 73 |

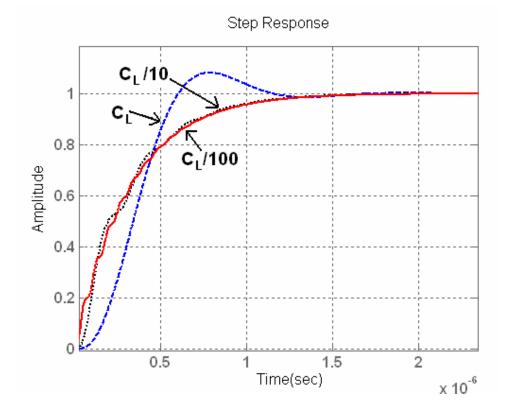

| 3.18   | Step response of proposed scheme with Butterworth poles for load capacitance = $C_L$                                                               | 74 |

| 3.19   | Step response of proposed scheme with 45degrees phase margin for load capacitance = $C_L$                                                          | 75 |

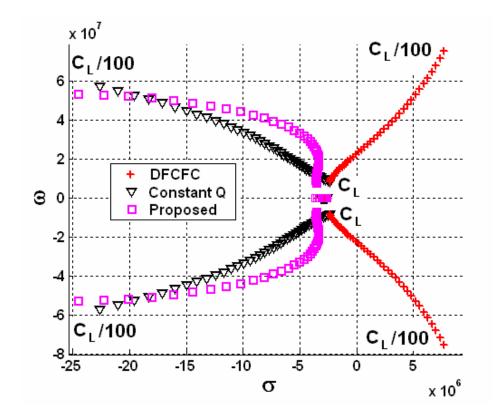

| 3.20   | Pole locus of proposed design as load capacitance is varied from $C_L$ to $C_L/100$ (Butterworth pole constellation for load capacitance = $C_L$ ) | 76 |

| 3.21    | Pole locus of proposed design as load capacitance is varied from $C_L$ to $C_L/100$ (45degree phase margin design for load capacitance = $C_L$ ) | 77  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

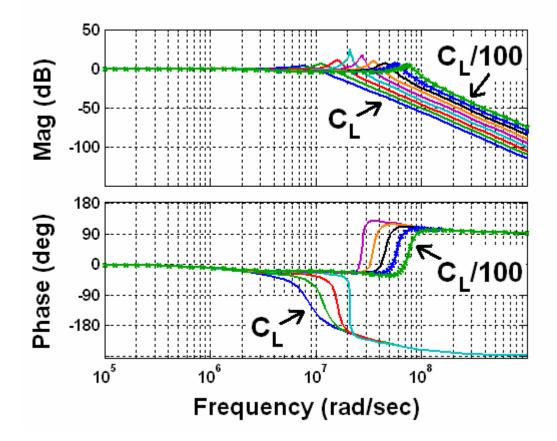

| 3.22    | Bode plot of DFCFC scheme as load capacitance is varied from $C_L$ to $C_L/100$ (45degree phase margin design for load capacitance = $C_L$ )     | 78  |

| 3.23    | Bode plot of proposed scheme as load capacitance is varied from $C_L$ to $C_L/100$ (45degree phase margin design for load capacitance = $C_L$ )  | 79  |

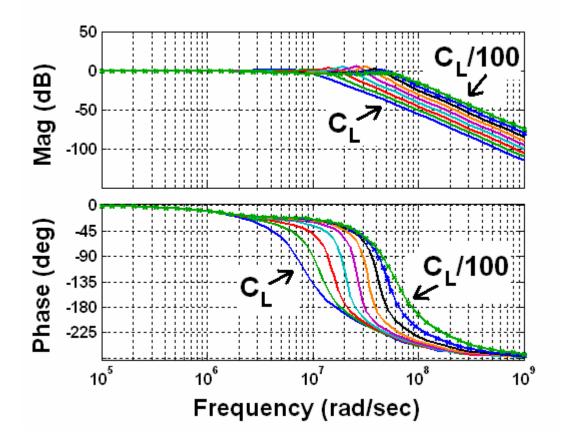

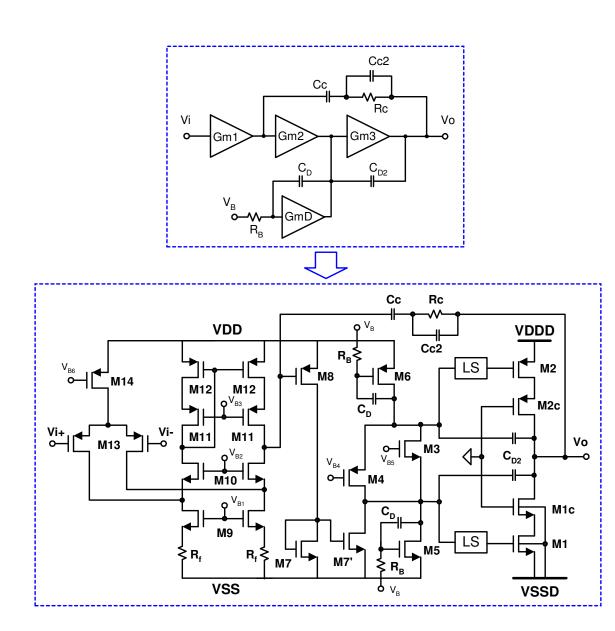

| 3.24    | Schematic of the proposed $16\Omega$ driver                                                                                                      | 80  |

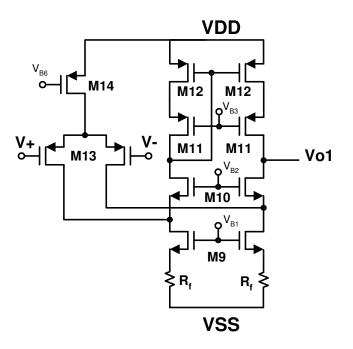

| 3.25    | Schematic of first stage of the driver                                                                                                           | 81  |

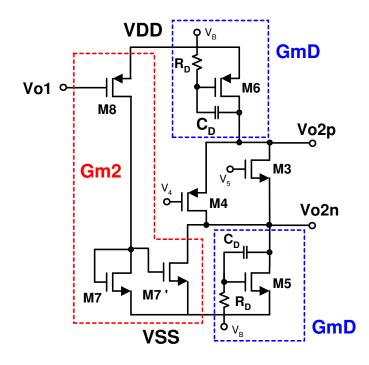

| 3.26    | Schematic of second and GmD stage of the driver                                                                                                  | 82  |

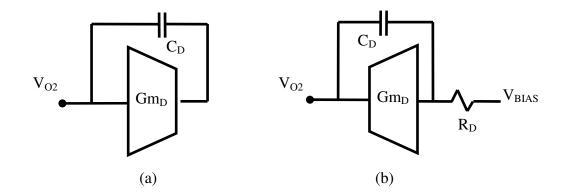

| 3.27(a) | Damping network used in [30]                                                                                                                     | 83  |

| 3.27(b) | Proposed damping network                                                                                                                         | 83  |

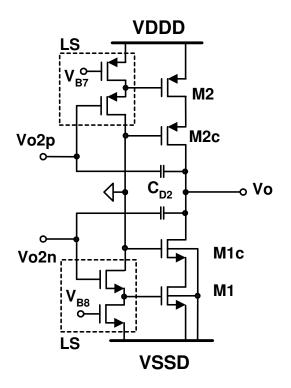

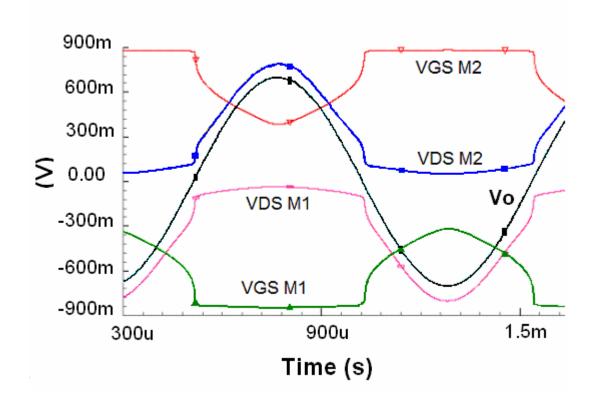

| 3.28    | Schematic of the output stage of the driver                                                                                                      | 85  |

| 3.29    | Voltage swings across gate-source and drain-source of driver transistors                                                                         | 86  |

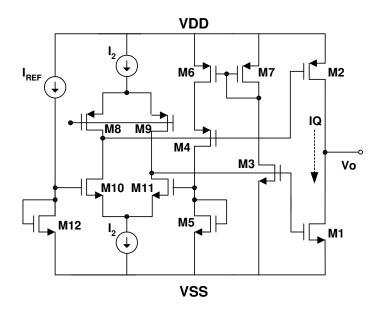

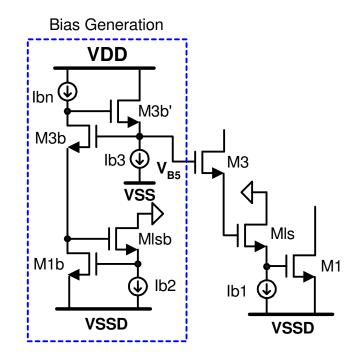

| 3.30    | Class-AB bias generation circuit                                                                                                                 | 88  |

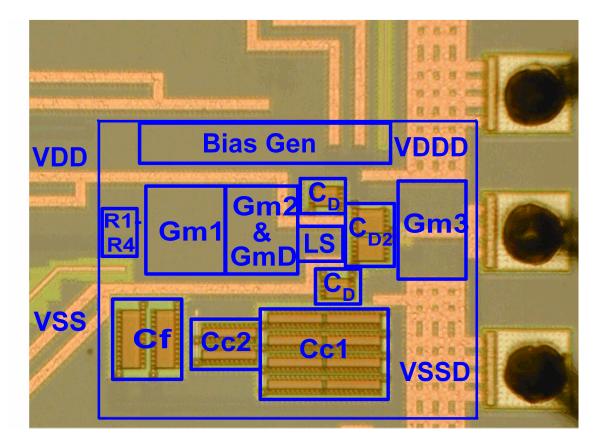

| 3.31    | Micrograph of the testchip                                                                                                                       | 89  |

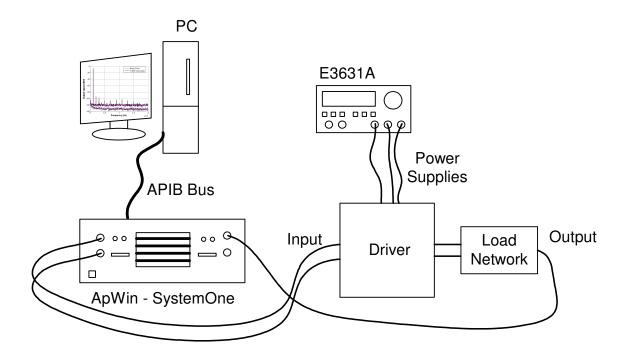

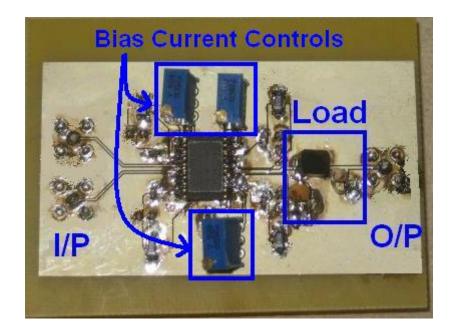

| 3.32    | Test setup for $16\Omega$ driver                                                                                                                 | 90  |

| 3.33    | PCB used for characterization of 16Ω driver                                                                                                      | 91  |

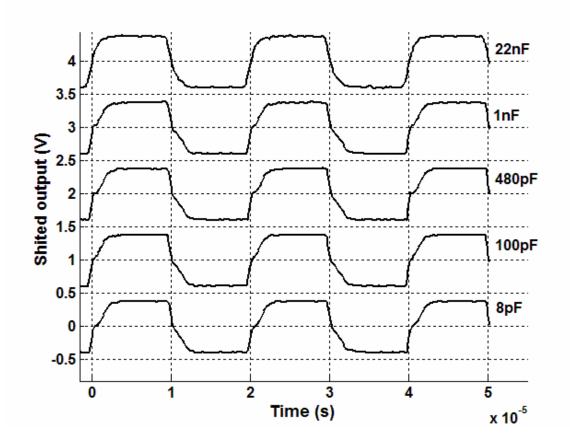

| 3.34    | Pulse response as load capacitance is varied from 8pF to 22nF                                                                                    | 92  |

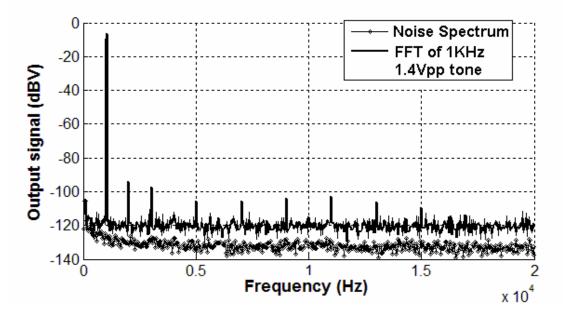

| 3.35    | Spectrum of 1KHz tone and noise                                                                                                                  | 93  |

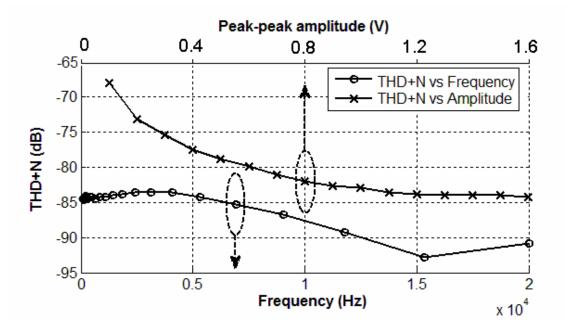

| 3.36    | THD+N as a function of frequency and amplitude                                                                                                   | 94  |

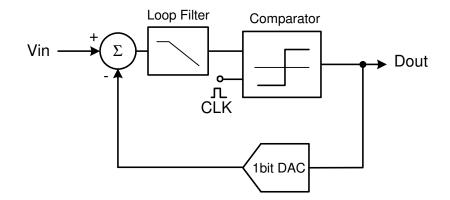

| 4.1     | Single-bit delta sigma modulator                                                                                                                 | 98  |

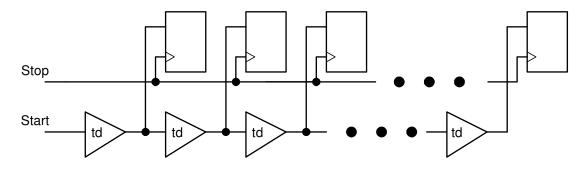

| 4.2     | Basic single-shot TDC                                                                                                                            | 101 |

Page

| ( | GURE    |                                                                | Page |

|---|---------|----------------------------------------------------------------|------|

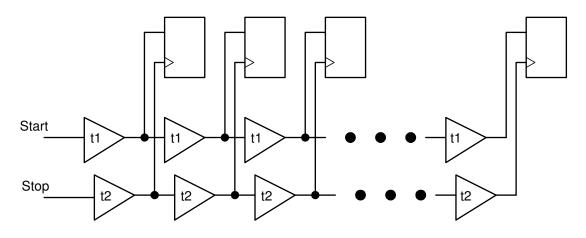

|   | 4.3     | Vernier delay line based TDC proposed in [46]                  | 102  |

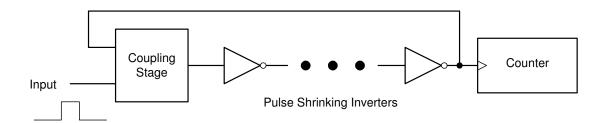

|   | 4.4     | Pulse shrinking inverter based TDC reported in [47]            | 102  |

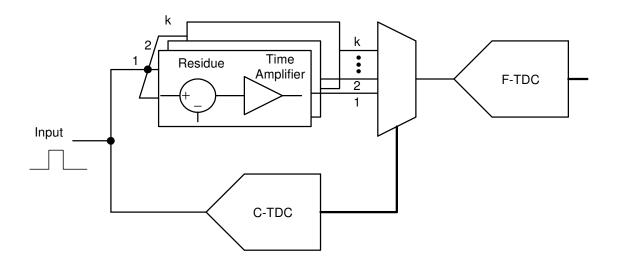

|   | 4.5     | Residue amplification based TDC proposed in [48]               | 103  |

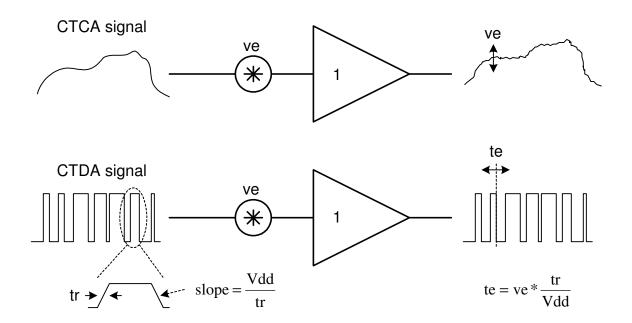

|   | 4.6     | Translation of voltage noise to timing noise                   | 107  |

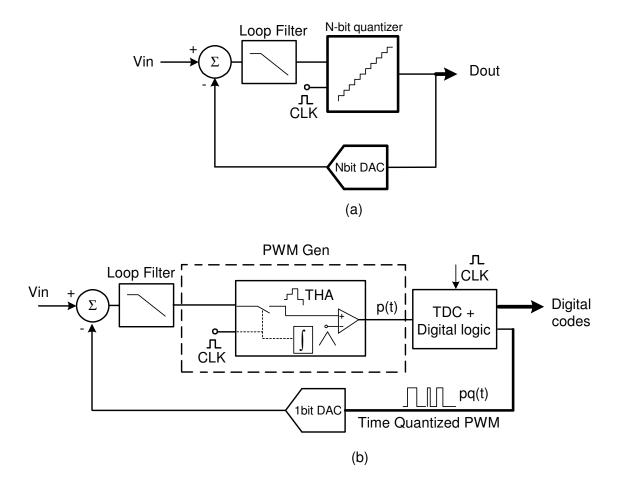

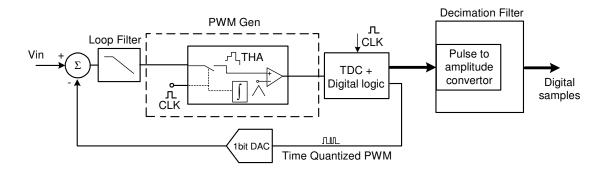

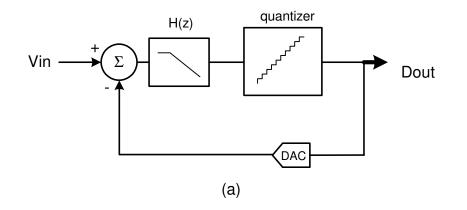

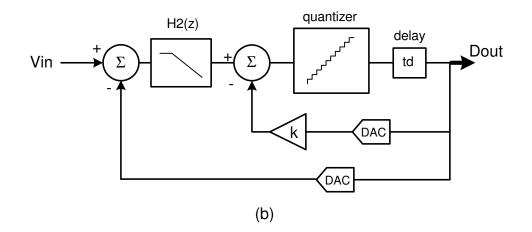

|   | 4.7(a)  | Conventional multi-bit delta sigma modulator                   | 109  |

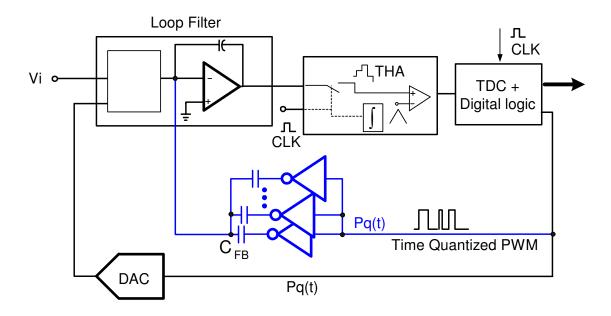

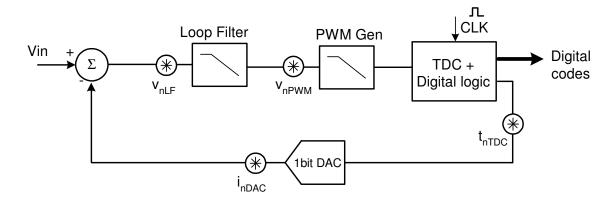

|   | 4.7(b)  | Proposed time-domain quantizer/DAC based delta sigma modulator | 109  |

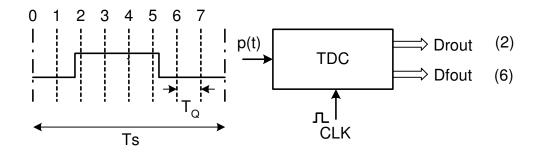

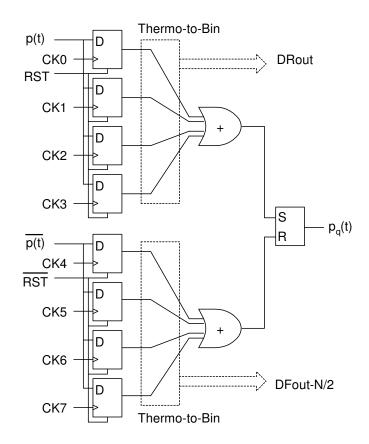

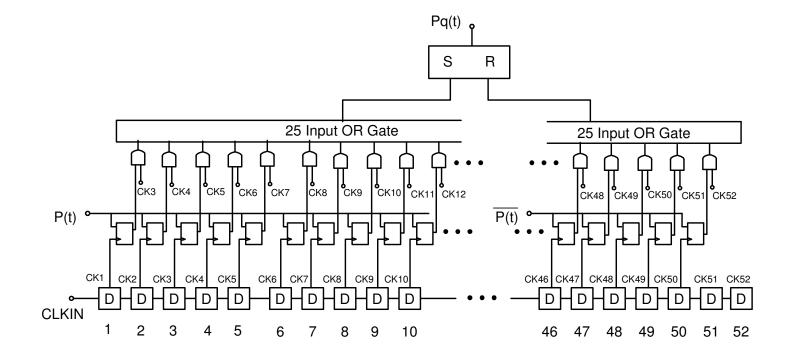

|   | 4.8     | TDC functionality                                              | 111  |

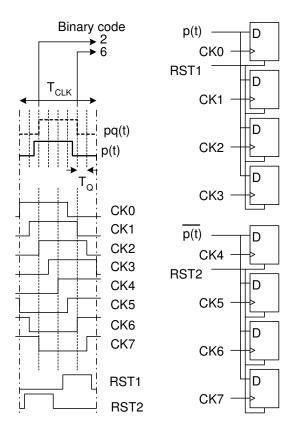

|   | 4.9     | Output code generation circuit                                 | 111  |

|   | 4.10    | Generation of feedback pulse using logical OR and SR latch     | 113  |

|   | 4.11    | Wired-NOR for equal systematic delay from input to output      | 114  |

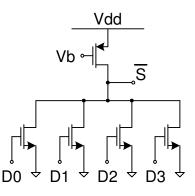

|   | 4.12    | Pulse to amplitude convertor / decimator                       | 115  |

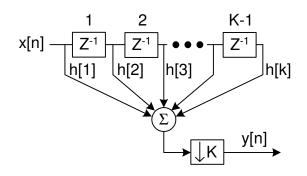

|   | 4.13    | FIR decimation filter – simplified block diagram               | 116  |

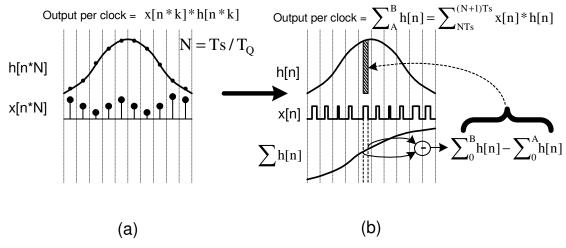

|   | 4.14(a) | Conventional multiply-accumulate-dump FIR filter               | 116  |

|   | 4.14(b) | Proposed FIR filter                                            | 116  |

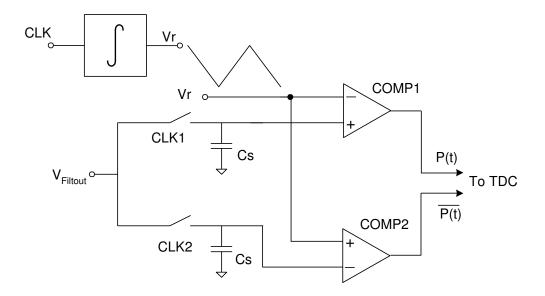

|   | 4.15    | Simplified block diagram of PWM generator                      | 118  |

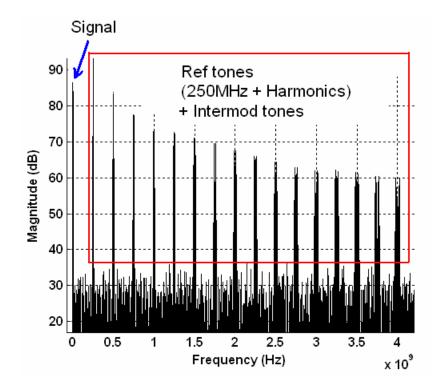

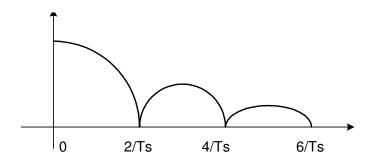

|   | 4.16    | Example spectrum of a PWM waveform                             | 120  |

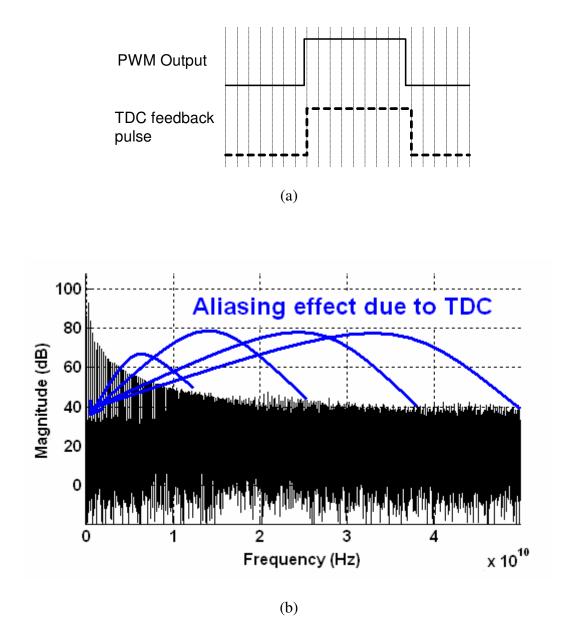

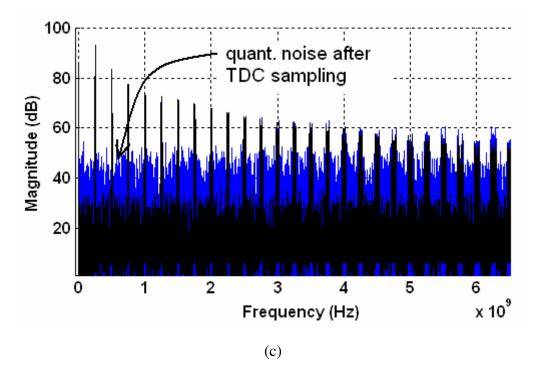

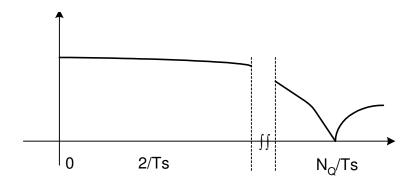

|   | 4.17(a) | "Time quantization" due to TDC                                 | 122  |

|   | 4.17(b) | Aliasing effect due to time quantization                       | 122  |

|   | 4.17(c) | Quantization noise floor due to aliasing                       | 123  |

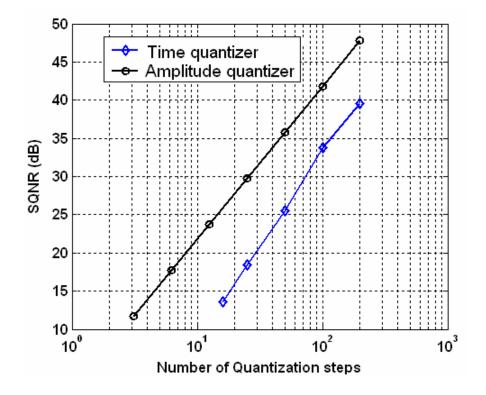

|   | 4.18    | SQNR of time and amplitude quantizer                           | 124  |

|   | 4.19    | Impulse response of the PWM generator                          | 125  |

| FIGURE |         |                                                                           |     |  |

|--------|---------|---------------------------------------------------------------------------|-----|--|

|        | 4.20    | Impulse response of the TDC                                               | 126 |  |

|        | 4.21(a) | Delta-sigma loop with no excess delay                                     | 128 |  |

|        | 4.21(b) | Delta-sigma loop compensated for excess delay                             | 128 |  |

|        | 4.22    | Proposed method for generating feedback around quantizer                  | 129 |  |

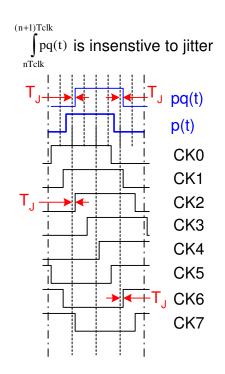

|        | 4.23    | Effect of clock jitter in proposed scheme                                 | 130 |  |

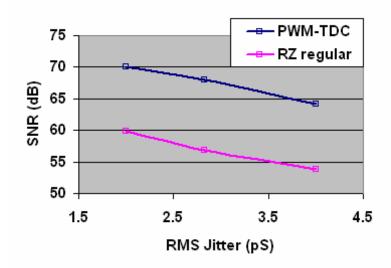

|        | 4.24    | SNR limitation due to clock jitter for RZ and proposed scheme             | 131 |  |

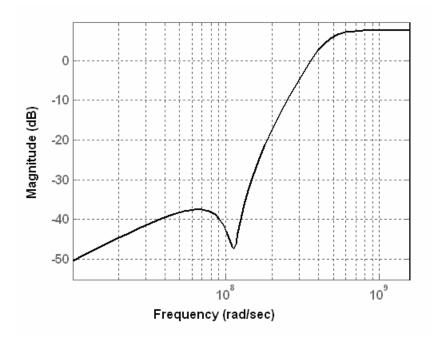

|        | 4.25    | Noise transfer function of the modulator                                  | 134 |  |

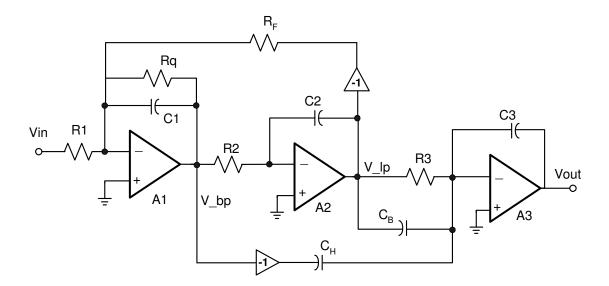

|        | 4.26    | Active-RC loop filter topology                                            | 135 |  |

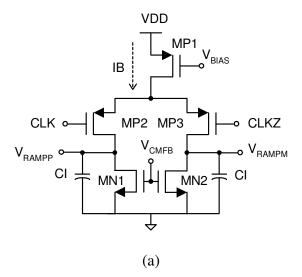

|        | 4.27(a) | Ramp generator                                                            | 137 |  |

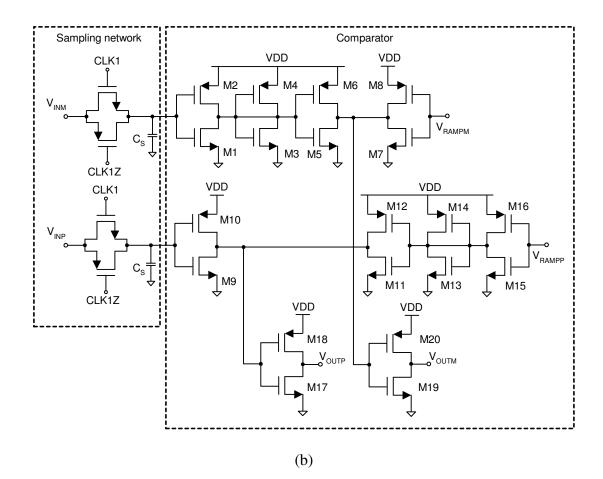

|        | 4.27(b) | Sampling network and comparator                                           | 138 |  |

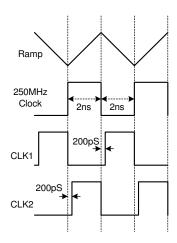

|        | 4.28    | Clock timing for the sampling switches of the PWM generator               | 139 |  |

|        | 4.29    | Simplified schematics of the TDC                                          | 141 |  |

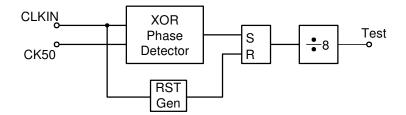

|        | 4.30    | Schematic of phase detection circuit for delay tuning                     | 142 |  |

|        | 4.31    | Noise contributors of the ADC                                             | 143 |  |

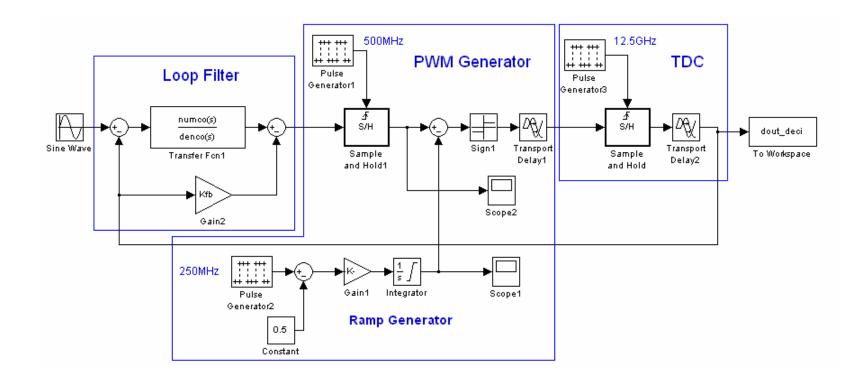

|        | 4.32    | SIMULINK model of the proposed ADC architecture                           | 146 |  |

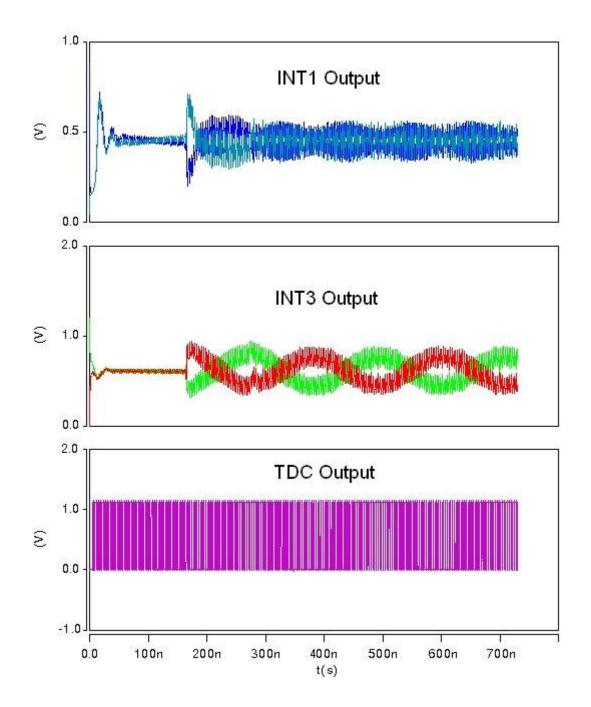

|        | 4.33    | Internal node waveforms from C-only netlist simulation<br>of the full ADC | 148 |  |

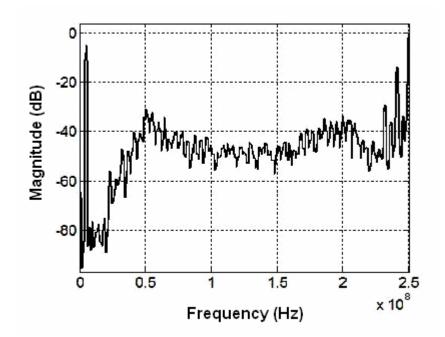

|        | 4.34    | FFT from simulation of full C-only ADC netlist with<br>4.7MHz -5dB input  | 149 |  |

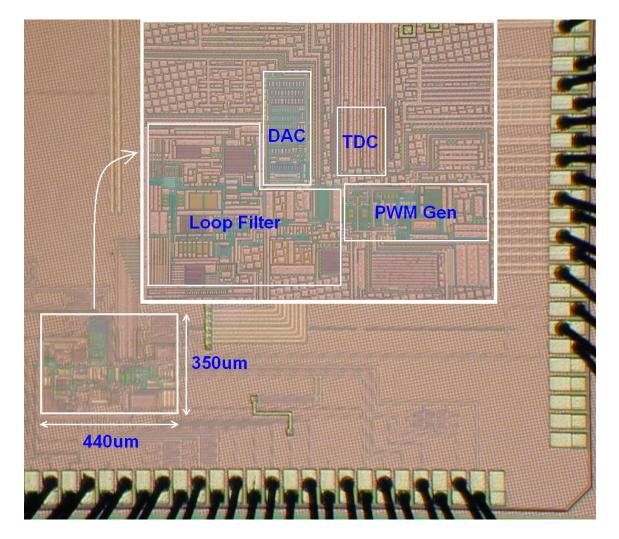

|        | 4.35    | Chip micrograph                                                           | 150 |  |

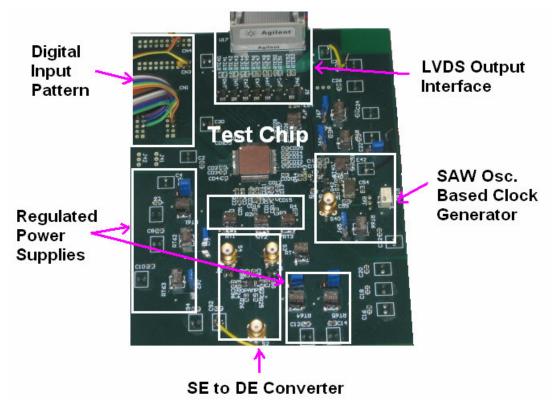

|        | 4.36    | Characterization board                                                    | 151 |  |

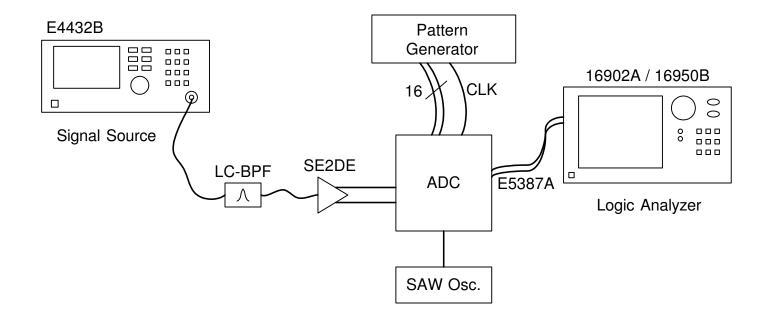

|        | 4.37    | Test setup used for characterization of the ADC                           | 152 |  |

| FIGURE                                     |     |  |  |

|--------------------------------------------|-----|--|--|

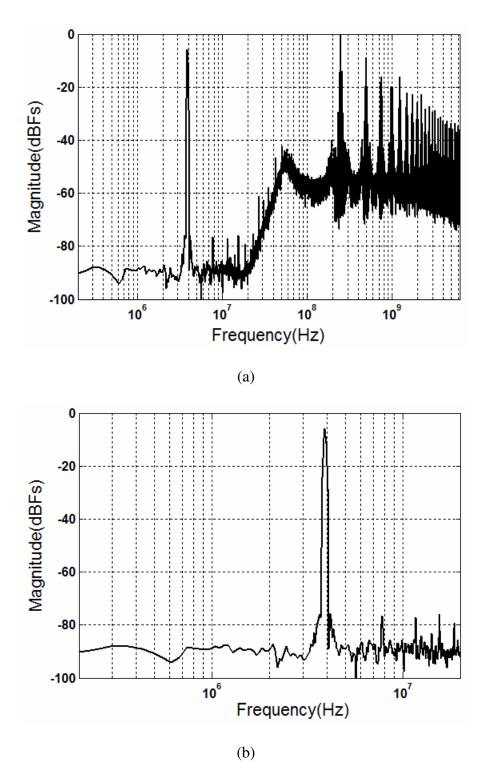

| 4.38(a) Output spectrum                    | 154 |  |  |

| 4.38(b) Spectrum in 20MHz frequency band   | 154 |  |  |

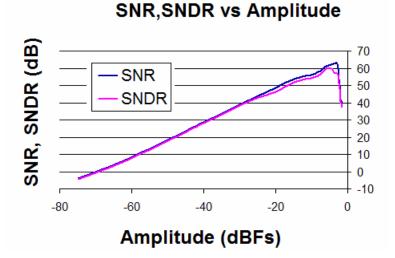

| 4.39 SNR and SNDR across signal amplitudes | 155 |  |  |

# LIST OF TABLES

| TABLE |                                                                      |     |

|-------|----------------------------------------------------------------------|-----|

| 2.1   | Inductor area as a function of L                                     | 22  |

| 2.2   | Experimental results for the proposed LC equalizing filter           | 41  |

| 2.3   | Comparison of proposed LC equalizing filter with                     |     |

|       | Gm-C equalizing filters                                              | 42  |

| 3.1   | Merits and demerits of existing headphone amplifier designs          | 52  |

| 3.2   | Comparison of measurement results with state-of-the-art              | 95  |

| 4.1   | Summary of various TDC techniques                                    | 105 |

| 4.2   | Scaling of various parameters with supply scaling under constant SNR | 106 |

| 4.3   | Noise contribution of various blocks                                 | 144 |

| 4.4   | Comparison of performance of the proposed ADC with state-of-the-art  | 156 |

#### CHAPTER I

#### INTRODUCTION

#### **1.1 Motivation and Goals**

Internet and computer technologies have revolutionized communication and entertainment in recent times. These technologies are expected to be available to a large population when low cost and long battery life are achieved by the ultra-mobile, wireless internet enabled multimedia devices [1]. The microprocessors that serve as the backbone of these ultra-mobile multimedia devices have constantly reduced cost and power consumption and improved performance due to technology scaling and innovative microprocessor architectures. Since these devices are targeted for communication over internet, they should also support low cost, low power data communication and analog interface circuit blocks. Since the device is targeted for a large user base it is preferable to have it flexible. While software can be easily made to adjust according to user preferences, there are several difficulties in making power-efficient circuit blocks that can work across a wide range of usage scenarios. These requirements open up opportunities for research in development of new circuit architectures that achieve high speed with low power while maintaining low cost through integration in digital CMOS technology along with the microprocessor.

This dissertation follows the style of IEEE Journal of Solid-State Circuits.

Fig. 1.1 Block diagram of a typical mobile multimedia device.

A block diagram of a typical mobile multimedia system with emphasis on mixedsignal circuit blocks is shown in Fig.1.1. Some of the circuit blocks take up a significant fraction of the overall power consumption of the system and poses serious design challenges in deep submicron technology. The focus of this work is to develop low power architectures for challenging circuit blocks like read-channel filters, analog-todigital converter (ADC) and versatile audio interface circuits in deep sub-micron digital CMOS technologies. Specifically, new architectures for the following circuit blocks that are compatible with digital CMOS technology were investigated and efficient solutions were proposed.

a) A 1.1GHz equalizing filter based on a new active-LC topology [2].

b) A low-power headphone driver based on a new compensation scheme that can handle a wide range of load conditions [3]. c) A novel ADC architecture suitable for integration in nanometric digital technologies[4].

### **1.2 Organization**

The design and implementation of the novel circuits blocks mentioned in section 1.1 are explained in a detailed manner in the following chapters. A 1.1GHz 5<sup>th</sup> order active-LC Butterworth type equalizing filter is presented in Chapter II. A series LC resonator based biquad is proposed and its frequency response, noise performance, power efficiency, linearity and area requirements are analyzed in detail. Transistor level implementation of the 5<sup>th</sup> order equalizer transfer function based on the proposed series resonator biquad is described in detail. Experimental results from the prototype built in 0.18µm CMOS technology are discussed and comparison with benchmark Gm-C equalizers is presented.

Chapter III describes a load capacitance aware compensation for 3-stage amplifiers. The behavior of the existing compensation schemes under large load variation is analyzed. The damping factor variation across load capacitance is found intuitively and a solution to maintain the damping factor roughly independent of the load capacitance is proposed. Implementation of a class-AB driver amplifier based on the proposed 3-stage compensation scheme is presented. Experimental results from the prototype fabricated in 130nm technology are discussed. The chapter concludes with a performance comparison with state-of-the-art headphone driver amplifiers. A continuous time delta-sigma analog to digital converter (ADC) based on a time domain quantizer and feedback element is described in Chapter IV. The benefit of processing signal in time domain is briefly discussed and a technique that enables the time domain quantizer by means of a pulse width modulation (PWM) generator and a time to digital converter (TDC) is presented. The realization of the proposed ADC architecture using various circuit techniques is described in detail. The quantization noise of the time domain quantizer, the impulse response of the PWM generator and the TDC, the excess loop delay, the effect of clock jitter and the overall noise transfer function are analyzed. Design of a 20MHz signal bandwidth 10-bit ADC based on the proposed architecture is presented. The simulation and experimental results from the prototype built using a 65nm digital CMOS technology are also discussed.

In Chapter V, conclusions are drawn and a possible area for future work related to the presented architectures is identified.

#### CHAPTER II

## A 1.1GHz 5th ORDER ACTIVE-LC BUTTERWORTH TYPE EQUALIZING FILTER

#### **2.1 Introduction**

On-chip inductors are routinely used for narrowband RF circuits. However, their use in broadband filtering has been limited. Emerging multi-Gbps data communication systems require wideband filtering and equalization with bandwidth in GHz range. In such systems, high equalization gain is incorporated to control Inter-Symbol-Interference (ISI) and maximize data rate for a given channel bandwidth. Realization of this high gain further imposes stringent noise and power requirements. High power efficiency and smaller size at GHz range make LC resonator based biquads more attractive and are thus considered in this work.

## 2.1.1 Previous Equalizer Solutions

A survey of previous equalizer solutions is presented in this section. The drawbacks associated with previous architectures when used for boost gain around 24dB and a large bandwidth in the range of several hundreds of MHz is examined.

A single terminated ladder based boost filter is reported in [5] for DVD applications. Its fifth order representation is shown in Fig. 2.1. The normalized transfer function H(s) is

$$H(s) = \frac{K_2(s^2 - 1) + K_1 - 1}{D(s)} = \frac{K_2s^2 - 1 + K_1 - K_2}{D(s)}$$

(2.1)

where  $K_1$  and  $K_2$  are the first and second feedforward path gains respectively. The intended numerator is of the form:  $K_2s^2 - 1$ . The input is directly gained and injected into the third integrating node to create the desired  $K_2s^2$  term in numerator of (2.1). However  $K_2$  path also introduces a low pass feed-through term  $-K_2$  which needs to be cancelled through the additional feedforward path consisting of  $K_1$  ( $K_1 = K_2$ ). Creating large gains at frequencies much lower than the filter's cut-off frequency and then canceling this undesired component (using an additional  $K_1$  path) results in loss of power efficiency. The second drawback of this structure is due to realizing entire boost gain in a single gain stage constituting of  $K_2$ . This implies that for 24dB boost gain, the transconductance of the boost OTA needs to be 16 times of that of main path OTA that injects current in to the same node.

Fig. 2.1 Boost architecture based on single terminated ladder reported in [5].

A differentiator is used in [6] to inject differentiated input signal into the low pass node of the biquad to generate two real zeros. While there is no injection of large low frequency signal currents, keeping the differentiator parasitic poles far away from significantly increases the power consumption [7]. Also, the entire boost gain is realized in a single stage using two zeros created by the differentiator, increasing power requirement. The topology employed in [7] makes use of the differentiator pole as a part of a third order cell and two such cells are used to realize the complete transfer function. However, this scheme introduces one real pole for each zero realized by the differentiator, limiting the types of filter responses that may be realized.

Fig. 2.2 (a) Biquad section of the boost filter reported in [8]. (b) Equivalent

## circuit.

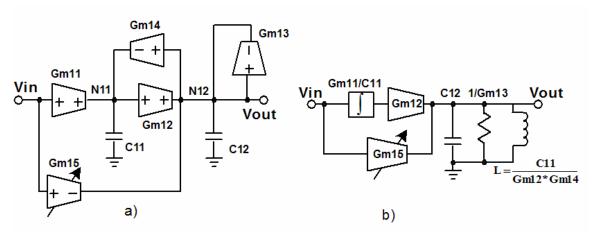

A cascade structure reported in [8] splits the boost gain between two biquads, realizing a zero each. Fig. 2.2 shows the biquad section of this architecture with a single

zero implemented and its equivalent circuit. Boost OTA (Gm15) injects unfiltered signal current from the input of the biquad into the output node N12. Low frequency component of this injected current is absorbed almost entirely by the emulated inductor (Gm12, Gm14, C11 gyrator). This superfluous low frequency current has an indirect impact on power efficiency. The current equation for node N12 at low frequency or DC, under the simplifying assumption that node N11 is lossless, is

$$Gm15*Vin = Gm12*V_{N11}$$

@ low frequencies (2.2)

Thus, to maintain voltage swing similar to Vin at node N11, the transconductor Gm12 has to be as large as Gm15. Notice that for 24dB boost, Gm15 is about four times as large as the input OTA and there are two such biquadratic blocks in the entire filter. Further, parasitic capacitance at node N12 become prohibitively large as it is driven by two large OTAs (Gm15 and Gm12). Thus, this scaling up of transconductors adversely affects the power efficiency of this architecture especially when used for wideband filters.

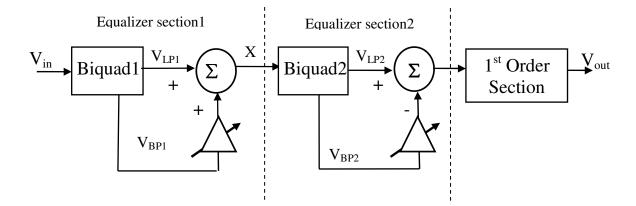

One of the efficient schemes for realizing equalization gain using Gm-C filters has been proposed in [9]. This scheme splits the boost gain between two biquad stages while solving the power disadvantage posed by other cascade architectures. The cascaded representation of the transfer function is given by:

$$H_{\text{boost}}(s) = \frac{\omega_{o}s\sqrt{K} + \omega_{o}^{2}}{s^{2} + \frac{\omega_{o}}{Q1}s + \omega_{o}^{2}} * \frac{\omega_{o}s\sqrt{K} - \omega_{o}^{2}}{Q2}s + \omega_{o}^{2}} * \frac{\omega_{o}}{s + \omega_{o}}$$

(2.3)

Here, Q1 and Q2 refer to the quality factor of biquad 1 and 2 and their values are 0.618 and 1.618 respectively. K determines the placement of zeros and its value ranges from 0

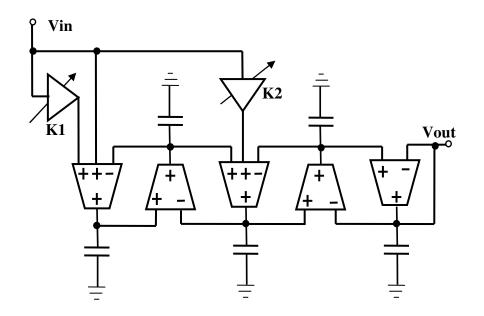

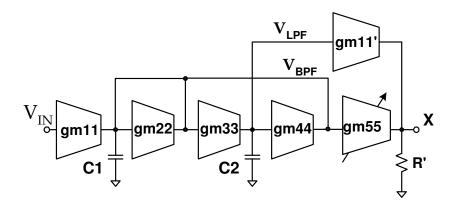

to 16 for 0 to 24dB high frequency boost. One way to implement the zeros is to add (subtract) lowpass and bandpass voltage signals. This is done in [8] by injecting amplified current proportional to the unfiltered input voltage into the bandpass impedance node (with parallel resonator of a resistor, capacitor and emulated inductor as in Fig. 3(b)). Alternately, if bandpass current is added (subtracted) from lowpass current, zeros can be directly constructed without creating the superfluous low frequency current. Hence, to achieve good power efficiency, the two real axis zeros are realized by combining bandpass and lowpass signals that are inherently available in Gm-C biquads (conceptual diagram shown in Fig. 2.3). OTA-C realization of such equalizer section is shown in Fig. 2.4.

Fig. 2.3 Scheme used in [9] to realize equalization gain  $(D_5(S)$  represents 5<sup>th</sup> order Butterworth poles).

Fig. 2.4 Gm-C biquad used to realize an equalizer section.

## 2.1.2 Need for LC Equalizer

It can be seen that the active elements used to emulate an inductor (in any Gm-C resonator section) would make these filters noisier than their LC counterpart. An active LC bandpass filter that improves the dynamic range over Gm-C bandpass filter was initially demonstrated in [10], and an alternative approach was adapted in [11]. So far, improved performance of LC filter over the Gm-C ones was demonstrated only for narrowband RF applications and the main focus of these filters was to achieve high-Q bandpass response. Although an 800MHz LC lowpass Butterworth filter has been demonstrated in [12], it is essentially a passive ladder filter unsuitable for realizing equalization gain. Thus, efficient circuit techniques are yet to be developed to exploit the high dynamic range of LC resonators for wideband low-Q filters.

For bandpass filters, it has been shown that filters employing parallel LC resonators are about 2Q+1 times more power efficient compared to their Gm-C counterpart [13]. This advantage, however, is diminished for filters that employ biquads with low Q values. Another expression, discussed in [14], predicts power efficiency as a

function of inductor's quality factor but this applies to Q-enhanced LC filter. In the following sections, the proposed series resonator is described and its superior power efficiency for low-Q filter realization is demonstrated. Circuit implementation of the complete 5<sup>th</sup> order Butterworth equalizing filter based on the proposed series LC resonator is discussed. Furthermore, a wide-band common mode feedback (CMFB) technique that provides high DC accuracy is discussed. Experimental results from the prototype design are also presented and are compared to state-of-the-art.

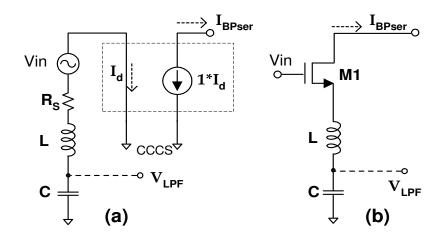

### 2.2 Analysis of Series Resonator Based Equalizer Section

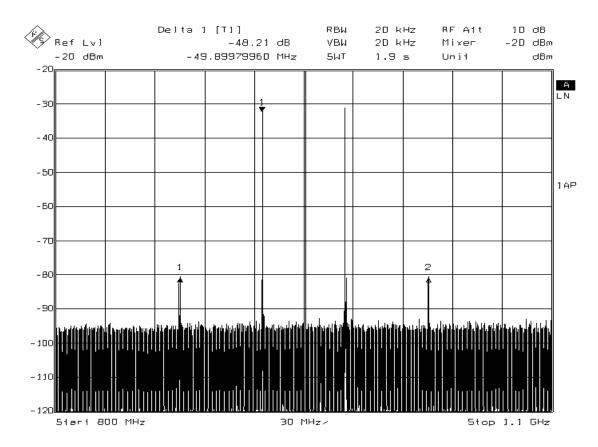

To implement the equalizer sections shown in Fig. 2.3, both 2<sup>nd</sup> order lowpass and bandpass signals are needed. An important property of series resonator prototype shown in Fig. 2.5(a) is that it generates both 2<sup>nd</sup> order bandpass current and 2<sup>nd</sup> order lowpass voltage as opposed to a parallel resonator which generates bandpass voltage alone. This property greatly simplifies the realization of the equalizer section. An active implementation of the series resonator prototype that uses just one transistor is proposed and is shown in Fig. 2.5(b). Transistor M1 generates bandpass current, acts as a buffer for the input and provides termination for the series resonator. Since large bandpass current is required to generate high equalization gain, re-use of M1 as termination element brings down the impedance level of the network. This factor in combination with reduced number of active elements results in superior noise performance and power efficiency.

Fig. 2.5 (a) Series resonator prototype. (b) Transistor implementation.

An equalizer section with required poles and zero can be constructed as shown in Fig. 2.6. Properties of this series resonator based equalizer section are examined below.

Fig. 2.6 Proposed Series resonator LC based equalizer section.

#### 2.2.1 Frequency Response

Summation of bandpass and lowpass current signals generates an equalizing zero besides a pair of complex poles. Neglecting inductor and transistor (M1's) parasitics and modeling M1 using a T-model, simplified expression for output current  $I_0$  is obtained as:

$$I_{O}(s) = \frac{Vin * sC}{\underbrace{s^{2}LC + s\frac{C}{gm1} + 1}_{I_{BPF}}} + \underbrace{\frac{Vin * gm2}{\underbrace{s^{2}LC + s\frac{C}{gm1} + 1}}_{I_{LPF}} = \frac{Vin * (sC + gm2)}{s^{2}LC + s\frac{C}{gm1} + 1}$$

(2.4)

where gm1(2) is the transconductance of M1(2). Since a real zero gives a gain increase at the rate of 6dB/Octave for high frequencies, the equalizing zero (gm2/C) is to be placed two octaves ahead of resonant frequency  $1/\sqrt{LC}$  ( $\omega_0=2\pi*1.1$ Grad/s) to achieve 12dB equalization gain per section. This implies gm<sub>2</sub>/C= $\omega_0/4$  or gm<sub>1</sub>=4\*Q\*gm<sub>2</sub>. The equalization gain can be programmed between 0-12dB by scaling down the bandpass current. R<sub>L</sub> acts as an I-V converter that converts I<sub>O</sub>(s) to V<sub>O</sub>(s). Due to the capacitance C<sub>L</sub>, the output voltage (V<sub>O</sub>) has a real pole in addition to the complex poles and equalization zero of I<sub>O</sub>(s). This real pole is assumed to be located at frequency 2 $\omega_O$  for rest of this section.

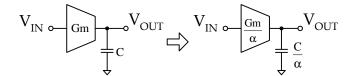

#### 2.2.2. Noise

In order to analyze the noise properties of the equalizer, the basic principle of impedance scaling must be understood. The transfer function of an electrical network remains unaltered if the impedance of all the elements is scaled by the same factor ( $\alpha$ ). In case an active element like transistor is used, the transconductance must be scaled by

$1/\alpha$  to retain the transfer function. Consider, for example, the Gm-C integrator in Fig. 2.7.

Fig. 2.7 Impedance scaling of a Gm-C integrator.

The transfer function of the integrator (Gm/sC) remains unaltered if both Gm and C are scaled by the factor 1/  $\alpha$ . How does one decide the absolute value of Gm and C since any scaled version will do equally well? This is where the noise performance of the circuit comes in to play. The integrated input referred noise (thermal) of the circuit in the bandwidth 0 to Gm/(2 $\pi$ C) is given by 8/3\* kT $\gamma$ /(2 $\pi$ C) where K is Boltzman constant, T is absolute temperature in Kelvins and  $\gamma$  is the noise factor of the transconductor. The Gm and C is typically scaled such that the total noise given by 8/3KT\*  $\gamma$  /C meets the noise specification. This is a very important principle that lets the designers "scale" a circuit according to the noise performance required off the circuit. Thus, the Signal to noise ratio (SNR) of a filter can be scaled up by factor ' $\alpha$ ' by scaling down all impedances by the same factor, which in turn increases power by the same factor. Impedance scaling can reduce noise only at the expense of power, leaving the product of power and noise unchanged [15]. Hence a quantity called 'power-noise product' is

introduced to asses the noise performance of the proposed circuit in the following analysis.

Since the total targeted boost gain is 24dB, a gain of 4 is assumed for the bandpass path (corresponding to a real zero at one-fourth of the resonant frequency  $\omega_0$  or a boost gain = 12dB per section).  $R_L = 1/gm2$  is assumed to ensure 0dB low frequency gain. Also, for noise calculations,  $R_L$  is assumed to be implemented by a transistor. The noise of  $I_{B1}$  is also considered since a common bias current for differential arms is not possible. Noise of all active elements is expressed in terms of  $V_{nGm2}^2$  (input referred noise density of gm2). Expressions for output referred noise density due to lowpass path ( $V_{nBPF}^2$ ) and bandpass path ( $V_{nBPF}^2$ ) of the series-LC equalizer section are thus derived as:

$$V_{nLPF-LC}^{2} = V_{nGm2}^{2} \left| \frac{2\omega_{o}}{s+2\omega_{o}} \right|^{2} \left\{ \frac{1}{4Q} \left| \frac{\omega_{o}^{2}}{D(s)} \right|^{2} + \frac{1}{4Q} \left| \frac{\omega_{o}(Qs+\omega_{o})}{D(s)} \right|^{2} + 1 + 1 \right\}$$

(2.5)

$$V_{nBPF-LC}^{2} = 4V_{nGm2}^{2} \left| \frac{2\omega_{o}}{s+2\omega_{o}} \right|^{2} \left\{ \frac{1}{Q} \left| \frac{s\omega_{o}}{D(s)} \right|^{2} + Q \left| \frac{\omega_{o}^{2}}{D(s)} \right|^{2} \right\}$$

(2.6)

where,  $D(s)=s^2 + \omega_0 s/Q + \omega_0^2$ , the terms within the curly braces in (2.5) correspond to the noise contribution of M1, I<sub>B1</sub>, M2 and R<sub>L</sub> in that order and the terms within the curly braces in (2.6) correspond to the noise contribution of M1 and I<sub>B1</sub> in that order. The total power consumed by the LC biquad is given by:

$$P_{LC} = (2+4Q)*P_{Gm2}$$

(2.7)

where  $P_{Gm2}$  is the power consumption of gm2. Similar analysis is also performed on Gm-C equalizer section shown in Fig. 2.4 for sake of comparison. Expressions for  $V_{nLPF-GmC}^2$ ,  $V_{nBPF-GmC}^2$  (noise density due to lowpass and bandpass path of the Gm-C equalizer section) and  $P_{GmC}$  (total power consumed by Gm-C equalizer section) are derived as follows.

A gain of 4 is assumed for the bandpass path (same as the LC equalizer case) yielding gm11=gm33=gm44=gm22\*Q=gm11'=gm55/4=R' and C1=C2. Noise of gm11' and R' are not included since they are usually a part of next biquad or first order section (inclusion of this would result in double-counting of noise). Expressions for output referred noise density in lowpass path ( $V_{nLPF-GmC}^2$ ) and bandpass path ( $V_{nBPF-GmC}^2$ ) are given by:

$$V_{nLPF-GmC}^{2} = V_{nGm11}^{2} \left| \frac{2\omega_{o}}{s+2\omega_{o}} \right|^{2} * \left\{ \left| \frac{\omega_{o}^{2}}{D(s)} \right|^{2} + \frac{1}{Q} \left| \frac{\omega_{o}^{2}}{D(s)} \right|^{2} + \frac{1}{Q^{2}} \left| \frac{\omega_{o}(Qs+\omega_{o})}{D(s)} \right|^{2} + \left| \frac{\omega_{o}^{2}}{D(s)} \right|^{2} \right\}$$

$$(2.8)$$

$$V_{nBPF-GmC}^{2} = 16 * V_{nGm11}^{2} \left| \frac{2\omega_{o}}{s+2\omega_{o}} \right|^{2} * \left\{ \left| \frac{s\omega_{o}}{D(s)} \right|^{2} + \frac{1}{Q} \left| \frac{s\omega_{o}}{D(s)} \right|^{2} + \left| \frac{\omega_{o}^{2}}{D(s)} \right|^{2} + \left| \frac{s\omega_{o}}{D(s)} \right|^{2} + \frac{1}{4} \right\}$$

$$(2.9)$$

Total power consumed by the Gm-C equalizer section is given by:

$$P_{Gm-C} = (7+1/Q) P_{Gm11}$$

(2.10)

where  $P_{Gm11}$  is the power consumed by OTA Gm11.

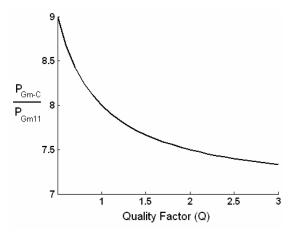

A simple plot of the ratio  $P_{Gm-C}/P_{Gm11}$  is shown in Fig. 2.8.

Fig. 2.8 P<sub>Gm-C</sub>/P<sub>Gm11</sub> vs quality factor.

The normalized power-noise products are found by taking the product of total power and total noise density and normalizing it by  $V_{nGm2}^2 * P_{Gm2} (V_{nGm11}^2 * P_{Gm11})$  in case of Gm-C equalizer).

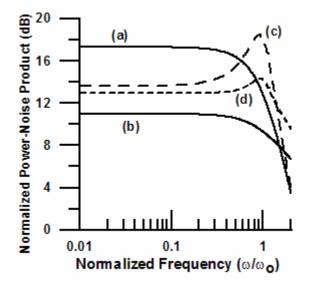

Fig. 2.9 Normalized power-noise product for Lowpass path (traces: (a) Gm-C, Q=0.618 (b) Series LC, Q=0.618 (c) Gm-C, Q=1.618 (d) Series LC, Q=1.618).

The normalized power-noise products for series-LC as well as the Gm-C equalizers are shown for lowpass path in Fig. 2.9 for Q=0.618 and 1.618. As expected the power-noise product of the series-LC equalizer section is significantly better than that of the Gm-C equalizer section. The slight degradation in out-of-band power-noise product in case of series-LC occurs due to the noise from  $I_{B1}$  having larger values near the resonant frequency.

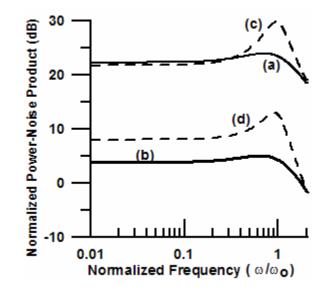

Fig. 2.10 Normalized power-noise product for bandpass path (traces: (a) Gm-C, Q=0.618(b) Series LC, Q=0.618 (c) Gm-C, Q=1.618 (d) Series LC, Q=1.618).

The normalized power-noise products for bandpass paths are plotted in Fig. 2.10. Trends similar to the lowpass case in improvement of power-noise product in case of series-LC equalizer section are observed. The results of the power-noise product analysis are used to formulate the relative power efficiency of different equalizing structures.

## 2.2.3. Relative Power Efficiency

Since Gm-C filter is commonly used for wideband equalization (in sub-GHz frequency range), it is chosen as a benchmark for power efficiency. The relative power efficiency of the proposed LC equalizer section ( $\eta$ ) is defined as the ratio of integrated power-noise product of Gm-C equalizer section to that of itself

$$\eta = P_{GmC} \int_{0}^{\omega_{0}} \left( V_{nLPF-GmC}^{2} + V_{nBPF-GmC}^{2} \right) d\omega / P_{LC} \int_{0}^{\omega_{0}} \left( V_{nLPF-LC}^{2} + V_{nBPF-LC}^{2} \right) d\omega$$

(2.11)

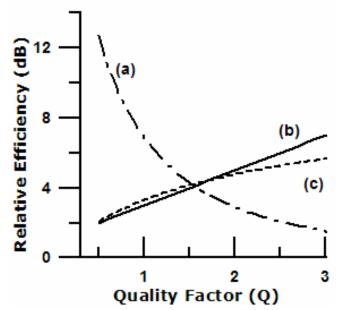

Fig. 2.11 (trace a) shows the plot for  $\eta$  for different values of Q. It is evident from the plot that the proposed LC biquads (with Q=0.618 and Q=1.618) are on an average about 7.3 times more power efficient than Gm-C biquads.

Fig. 2.11 Relative power efficiency versus quality factor (traces: (a) Series LC equalizer section -  $\eta$  (b) Parallel LC BPF -  $\eta_2$  (c) Parallel LC BPF -  $\eta_{par}$ ).

The relative power efficiency for parallel LC bandpass filter (BPF) with respect to Gm-C BPF ( $\eta_2$ ) is obtained in [13] as 2Q+1 (shown in Fig. 2.11 trace b for reference). This, however, is valid only at resonant frequency (since it is derived based on noise density at resonant frequency). An appropriate relative efficiency for parallel LC BPF for wideband case ( $\eta_{par}$ ) is found by integrating the noise across the pass-band and is plotted in Fig. 2.11 trace c for reference.

$$\eta_{\text{par}} = P_{\text{GmC}} \int_{0}^{\omega_0} \left( V_{\text{nBPF-GmC}}^2 \right) d\omega / P_{\text{LCpar}} \int_{0}^{\omega_0} \left( V_{\text{nBPF-LCpar}}^2 \right) d\omega$$

(2.12)

where  $V_{nBPF-LCpar}^{2}$  is output referred noise similar to (2.6) obtained for parallel LC BPF. From the plot it can be concluded that for low Q equalizer sections, the proposed LC biquad using series resonator is likely to be more efficient than a parallel LC based structure even if the problem of generating lowpass signal is solved for the latter.

## 2.2.4. Effect of Quality Factor of the Inductor

For a given value of L and  $\omega_{o}$ , the termination resistance  $R_{S}$  (see Fig. 2.5(a)) is fixed by the Q of the biquad. To account for the loss in the coil, gm1 has to be scaled such that gm1'=gm1 $\frac{Q_{L}}{Q_{L}-Q}$  (where  $Q_{L}$  is the quality factor of the inductor). This ensures 1/gm1'+R<sub>C</sub>=R<sub>S</sub> (where R<sub>C</sub> is the resistance of the coil). When this factor is accounted, the power consumption P<sub>LC</sub> in (2.7) changes to  $\left(2+4\frac{Q_{L}Q}{Q_{L}-Q}\right)*P_{Gm2}$ . Saving for the noise contribution of I<sub>B1</sub>, V<sub>nLPF-LC</sub><sup>2</sup> and V<sub>nBPF-LC</sub><sup>2</sup> remains almost unchanged since the effective termination resistance is preserved. For  $Q_L=7.5$  (used in this design),  $P_{LC}$  increases by 1.13 times (average between Q = 0.618 and 1.618) compared to (2.7). Just as additional data points, for  $Q_L=5$  and 10,  $P_{LC}$  increases by 1.22 and 1.09 times respectively. Note the weak dependence of power-noise product on  $Q_L$ , which is in sharp contrast with that of Q-enhanced LC filters (Q>>Q<sub>L</sub>) where the power-noise product is inversely proportional to  $Q_L^2$  [14]. Essentially, large  $Q_L$  is not useful for low-Q series resonator biquads since it does not improve the power efficiency significantly.

#### 2.2.5. Linearity

The differential implementation of the circuit shown in Fig. 2.6 (refer to Fig. 2.16) can be viewed as two differential pairs formed by M1 and M2. The differential pair formed by M1 takes advantage of the finite coil resistance of the inductor (Rc) to introduce source degeneration. The lowest value of source-degeneration factor in this case is gm1\*Rc. For differential pair formed by M2, the source degeneration is explicitly added using a poly resistor. The worst case HD3, which corresponds to lowest source degeneration factor, is given by

HD3

$$\approx \frac{\text{Vi}^2}{32*(1+\text{gm1}*\text{R}_{\text{C}})^2 \text{V}_{\text{GST}}^2}$$

(2.13)

where  $V_{GST}$  is the gate overdrive voltage of M1. Thus, the distortion performance can be improved by increasing  $R_C$  (reducing inductor's quality factor ( $Q_L$ )).

# 2.2.6. Area

Following analysis formulates the relationship between area of the proposed LC filter as a function of cut-off frequency (f) and SNR. Let  $A_{Co}$ ,  $A_{gmo}$  be the total area taken by capacitors and transistors of a LC equalizer section respectively for signal to noise ratio SNRo(47dB) and cut-off frequency fo(1.1GHz). C, L and gm values can be projected as a function of SNR and f by applying impedance scaling and frequency scaling (for constant noise) respectively. Capacitor and transistor area scales by the same factor as C and gm respectively. To find the inductor area as a function of L, inductors with same Q value (=7.5) but different L values were created using the TSMC 0.18um CMOS design kit. The L values and area (including shield) measured from layout are shown in Table 2.1.

Table 2.1 Inductor area as a function of L.

| L (nH) | Area (Kµm <sup>2</sup> ) |

|--------|--------------------------|

| 12     | 235                      |

| 6      | 160                      |

| 3      | 109                      |

| 1.33   | 73                       |

From this data the relation between L and area of inductor is fitted as  $A_L(L) =$  14.9\*L+61.3 where L is expressed in nH and  $A_L$  is expressed in Kµm<sup>2</sup>. The constant term in  $A_L(L)$  is due to fixed shield area. Although this approximation for  $A_L(L)$  tends to overestimate the area for large L, it is still used to keep the analysis simple and

insightful. A plot of  $A_L(L)$  measured from the layout and its linear approximation is shown in Fig. 2.12.

Fig. 2.12. Area of the inductor as a function of its value.

The area estimate for the series-LC equalizer section thus found from the above analysis is expressed as

Area<sub>LC</sub> (SNR, f) = A<sub>Co</sub> \*

$$\frac{SNR}{SNRo}$$

+ A<sub>gmo</sub> \*  $\frac{SNR * f}{SNRo * fo}$  + A<sub>L</sub>  $\left( Lo * \frac{SNRo}{SNR} * \left(\frac{fo}{f}\right)^2 \right)$  (2.14)

If  $\eta_{1,2}$  represent the value of  $\eta$  obtained for the two biquads (with Q<sub>1</sub>=0.618 and Q<sub>2</sub>=1.618), area of a corresponding Gm-C filter (as a function of SNR and f) can be expressed in terms of A<sub>Co</sub> and A<sub>gmo</sub> as:

Area<sub>GmC</sub>(SNR, f) =

$$\frac{1}{2} \sum_{i=1}^{2} \left[ A_{Co} * \frac{\eta_i (2+4Q_i)}{2(7+1/Q_i)} * \frac{SNR}{SNRo} + A_{gmo} * \eta_i * \frac{SNR*f}{SNRo*fo} \right]$$

(2.15)

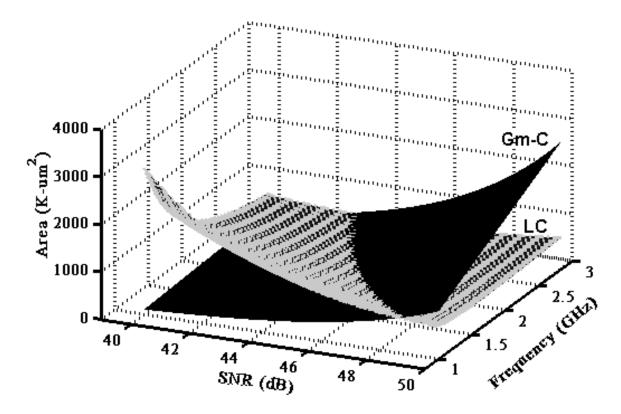

In 0.18um technology,  $Area_{LC}(46dB, 1.1GHz) = 630Kum^2$  (area occupied by present design) which is about twice of  $Area_{GmC}(46dB, 1.1GHz)$ . However, from (2.14) and (2.15) it is projected that  $Area_{GmC}$  would outrun  $Area_{LC}$  beyond certain f for a given SNR and beyond certain SNR for a given f. Fig. 2.13 captures this trend by plotting both the areas in K-µm<sup>2</sup> across SNR and f.

Fig. 2.13 Area comparison for Gm-C and LC equalizer section.

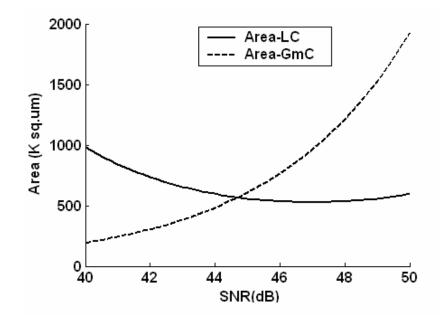

A cross section of the 3-D plot in Fig. 2.13 is provided at 2GHz in Fig. 2.14. Area<sub>LC</sub> initially reduces with increasing SNR due to the area reduction of the inductor. At SNR of about 47dB, Area<sub>LC</sub> gradually increases due to the dominance of area of the capacitors

and the transconductors. Area<sub>Gm-C</sub> equals Area<sub>LC</sub> for SNR of about 45dB and progressively increases for higher SNR. This trend suggests that the proposed LC biquad can achieve much better power efficiency without area penalty at sufficiently high frequencies or SNR.

Fig. 2.14 Area of LC and Gm-C equalizer sections as a function of SNR at 2GHz.

Another aspect worth mentioning is that the area of inductor can be reduced at the expense of  $Q_L$  [16]. In this design, inductors have a metal width of 15µm for  $Q_L$  of 7.5. By decreasing metal width to 6µm ( $Q_L$  to 4.9), area can be reduced to 69% of its present value at an expense of 11% additional power. Reduction in inductor sizes can also be achieved by using technology that has Cu interconnects.

# 2.3 Proposed Architecture and Circuit Implementation

In the proposed architecture, the 5<sup>th</sup> order Butterworth filter is realized by cascading two series-resonator based LC equalizer sections. Since a real pole is associated with each equalizer section, there are 6 poles in the overall transfer function. The two real poles are placed such that their overall effect in magnitude and phase response in the pass-band is close to that of the single real pole in 5<sup>th</sup> order Butterworth response. In this design, these real poles are placed at 3GHz and 2GHz so that the magnitude error (1.3dB) and phase error (3.9degrees) are minimal in the pass-band.

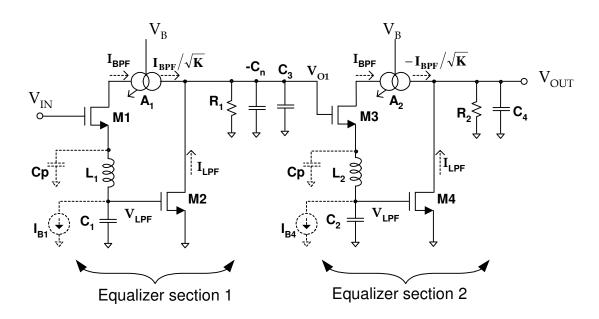

A simplified single-ended version of the complete filter that realizes fifth order Butterworth function is shown in Fig. 2.15.

Fig. 2.15 Simplified schematic (single-ended) of the 5<sup>th</sup> order Butterworth filter.

Currents from transistors M1 and M3 ( $I_{BPF}$ ) are required to be variable for programmability of equalization gain. This is achieved by variable gain current attenuators A<sub>1</sub> and A<sub>2</sub> controlled through V<sub>B</sub>. The real pole at 1<sup>st</sup> biquad output is pushed to 3GHz by using a negative capacitor -C<sub>n</sub> (similar to one proposed in [17]) which is designed to counter the parasitic and common-mode detector capacitance at the output node of the 1<sup>st</sup> biquad (C<sub>3</sub>). Ignoring the parasitic capacitance Cp, using (2.4) along with node equations at V<sub>O1</sub> and V<sub>OUT</sub>, the complete transfer function H(s)=V<sub>OUT</sub>(s)/V<sub>IN</sub>(s) can be written as:

$$H(s) = \frac{(sC_1 + gm2)}{s^2 L_1 C_1 + s \frac{C_1}{gm1} + 1} * \frac{(sC_2 + gm4)}{s^2 L_2 C_2 + s \frac{C_2}{gm3} + 1} * \frac{1}{1 + s(C_3 - C_n)R_1} * \frac{1}{1 + sC_4 R_2}$$

(2.16)

For exact analysis of a very high frequency filter, effect of node parasitic cannot be ignored. Replacing the inductor by its pi model [18] and accounting for the critical parasitic capacitances of M1, M2 and  $I_{B1}$ , bandpass current which was earlier shown in (2.4) can now be modified as:

$$I_{BPF1}(s) \approx Vin \frac{sC'[s^2L_1Cp + sR_cCp + 1]}{s^2L_1C' + s(R_c + 1/gm_1)C' + 1}$$

(2.17)

where  $Cp=Cp'+Csb_{M1}$ ,  $C'=C_1 + Cp'+Cdb_{IB1}+Cgs_{M2}$ , Cp' is the effective capacitance from each inductor terminal to substrate and  $R_c$  is the coil resistance. Here,  $Cdb_{IB1}$  refers to drain to bulk capacitance of the transistor that would realize  $I_{B1}$ . From (2.17), it can be seen that there is a pair of complex parasitic zeros whose frequency is slightly less than the self-resonant frequency of the inductor. Intuitively, this could be interpreted as the effect of the parasitic tank circuit formed by  $L_1$ ,  $R_c$  and Cp (present in any practical LC design). By choosing to connect current source  $I_{B1}$  at the capacitor-end of the inductor ( $V_{LPF}$  node) rather than the transistor-end,  $Cdb_{IB1}$  is absorbed in C<sup>'</sup> instead of Cp. This helps to keep the parasitic zeros far out from filter's pass-band. In the present design, parasitic zeros (complex) are located around 3.8GHz and 5.1GHz for biquad 1 and biquad 2, respectively, making their effect insignificant.

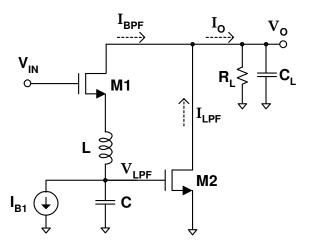

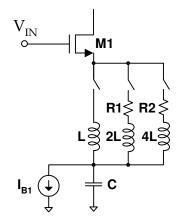

#### 2.3.1 Biquad

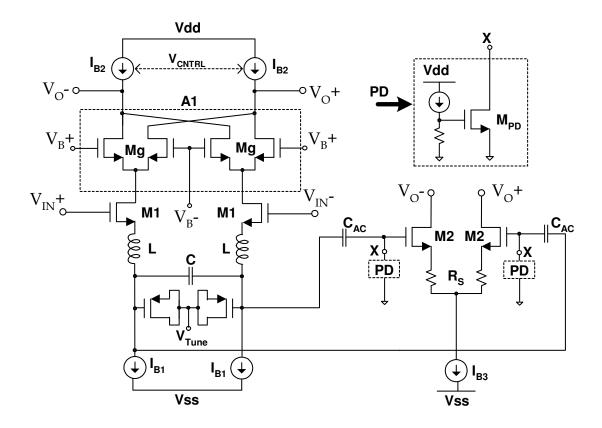

The fully differential circuit implementation of a single equalizer section (without the loads) is shown in Fig. 2.16. To make the circuit balanced and hence improve the common mode rejection, the differential arms share the same floating capacitor (C) for the resonator. Moderate frequency tuning is provided by PMOS varactors controlled by external voltage  $V_{TUNE}$ . The gain in the bandpass path is varied using a Gilbert-cell based attenuator (A<sub>1,2</sub> in Fig. 2.15). Transistors Mg (Fig. 2.16) form this Gilbert-cell, which is used to control the location of the real axis zero in the transfer function and thereby controlling the boost gain. Current sources (I<sub>B2</sub>) are controlled through a CMFB loop discussed in section B.

Fig. 2.16 Schematic of the proposed fully differential series LC resonator based equalizer section.

The differential pair formed by M2 implements the transconductor in the lowpass path. The differential pair is ac coupled to the resonator in order to minimize the voltage headroom requirement of the biquad. The ac coupling is achieved by using a blocking capacitor  $C_{AC}$  and a pull-down transistor (M<sub>PD</sub> in PD block) biased in deep-subthreshold. This approach is similar to the quasi-floating gate technique described in [19] but avoids completely cut-off transistors to ensure that the gate of M2 stays at common mode voltage (0V). Note that high threshold voltage of 700mV (source of M<sub>PD</sub> is connected to 0V instead of VSS) prevents device  $M_{PD}$  from 'turning on' even for the peak signal swing.

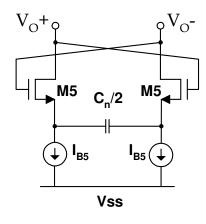

#### 2.3.2 Negative Capacitance

The negative capacitance emulation circuit (similar to one in [17]) is shown in Fig. 2.17. Assuming that this circuit is operated at a frequency well below the  $f_T$  of M5, the single ended admittance of this circuit can be approximated as  $\frac{-sCn*gm5}{gm5+sCn}$ . The pole of the admittance lies at frequency  $\omega_{Cn}=gm5/Cn$ , which makes this circuit appear like a capacitor –Cn at frequencies much less than  $\omega_{Cn}$ . When connected to node  $V_{O1}$ , this effectively pushes the first order pole to higher frequency ( $\omega_3=2\pi*3$ Grad/sec in this case).

Fig. 2.17 Negative capacitance emulation circuit (similar to one in [17]).

For this design, since  $gm5 \cong gm2$ , the noise density at the output of the equalizer section due to this circuit (including noise from M5 and  $I_{B5}$ ) can be expressed as

$$V_{nCn}^{2} = V_{nGm2}^{2} \left| \frac{\omega_{3}}{\omega_{3} + s} \right|^{2}$$

(2.18)

From (2.18) and plots in Fig. 2.9 and Fig. 2.10, it can be concluded that the noise contribution due to this circuit is insignificant. Also, the distortion contribution of the negative capacitance circuit is very small. The capacitor Cn/2 offers a reactive source degeneration factor of gm5/j $\omega$ Cn, which suppresses the distortion by >30dB at 1.1GHz and even more at low frequencies. This is expected since the voltage to current conversion, in the frequency of interest, is mostly performed by the linear element Cn, rather than gm5.

### 2.3.3 Common-mode Feedback

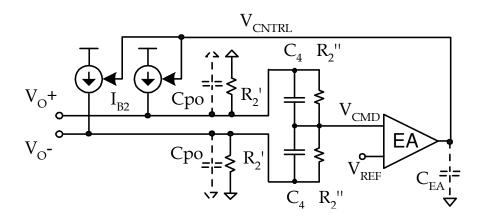

Although useful signal is present only up to filter's cut-off frequency (1.1GHz), the differential -3dB bandwidth increases to about twice the nominal value under application of large boost gain. In order to avoid boosting of common mode noise, a CMFB bandwidth of about twice the cutoff frequency is desirable. A new method is proposed to achieve such large bandwidth in common mode loop.

One of the main limitations of the CMFB loop bandwidth is the pole at the output of the equalizer section (V<sub>0</sub>+, V<sub>0</sub>- node in Fig.2.3.2). In the proposed technique, the load resistance (R<sub>2</sub> for second equalizer section) is split between the common-mode load resistance R<sub>2</sub>'=2\*R<sub>2</sub> and the common-mode detector resistance R<sub>2</sub>''=2\*R<sub>2</sub> as shown in Fig.2.3.4. This allows for high frequency pole at output node (Vo+, Vo-) as well as a common mode detector ( $R_2$ '' and  $C_4$ ) that is virtually frequency independent. The pole at output node for common-mode signals, determined by the  $R_2$ ' and the output parasitic capacitance (Cpo), is about  $2\pi$ \*2.6Grad/s for this design.

Fig. 2.18 Implemented CMFB loop.

If the error amplifier (EA) is a simple integrator with a single low frequency pole, two limitations occur. Firstly, the maximum unity gain frequency that can be achieved for the CMFB loop shown in Fig. 2.18 is about 1.5GHz for  $60^{\circ}$  phase margin (due to non-dominant pole 1/R<sub>2</sub>'Cpo located at 2.6GHz). Secondly, for the same phase margin, the transconductance of the current source I<sub>B2</sub> (Gm<sub>IB2</sub>) is upper bounded by

$$Gm_{IB2} \leq \frac{1}{1.5} \left( \frac{1}{R_2'Cpo} \right)^2 \frac{C_{EA}}{Gm_{EA}} Cpo$$

(2.19)

where  $C_{EA}$  and  $Gm_{EA}$  are the load capacitance and the transconductance of the EA. The usual implication of this upper bound is that not all bias current of the biquad can be

flown through the controlled source  $I_{B2}$ . Therefore, only a part of the bias current source can be controlled by the CMFB loop. Under extreme offset condition, control of only a fraction of bias current could result in significant variation of  $I_{B2}$ 's output conductance (due to large or small overdrive applied to part of the controlled current source). The proposed implementation of current source and EA circumvents the above limitations.

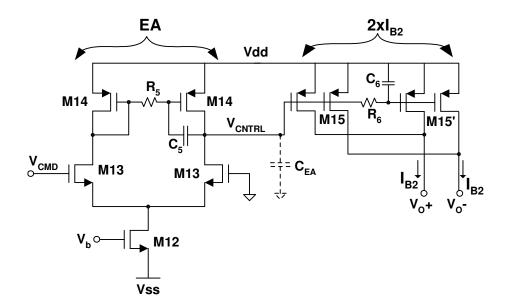

A split frequency current source (Fig. 2.19) used in [20] to avoid latching states in opamp is used in place of  $I_{B2}$ , It comprises of transistors M15 and M15' and R<sub>6</sub>-C<sub>6</sub> network. DC transconductance is determined by both M15 and M15' while high frequency behavior by M15 alone. Note that, by choosing  $1/R_6C_6$  well below unity gain frequency, the effective loading of EA at  $V_{CNTRL}$  node (C<sub>EA</sub>) is limited to gate capacitance of M15 (along with junction capacitance of M13 and M14).

Fig. 2.19 Proposed EA and split frequency current sources.

Combination of the low pass and the direct path driving M15' and M15 respectively results in a pole-zero pair in transconductance of  $I_{B2}$ , which is given by

$$Gm_{IB2}(s) = \frac{I_{B2}(s)}{V_{CNTRL}(s)} = \frac{gm_{15}(s + \omega_{z2})}{(s + \omega_{P3})} = \frac{gm_{15}(1 + k + sR_6C_{gs15'})}{(1 + sR_6C_6)}$$

(2.20)

where k (=2) is the ratio of sizes of M15' and M15 and  $C_{gs15'}$  is gate capacitance of M15'

It is preferred to have a high gain EA for well controlled operating points and DC accuracy. Also, the pole introduced by the split frequency current source needs to be cancelled in order to extend the bandwidth. To this end, the EA shown in Fig. 2.19 with  $R_5$  and  $C_5$  applied around M14 is used. Transfer function of the EA is given by

$$H_{EA}(s) = \frac{V_{CNTRL}(s)}{V_{CMD}(s)} = \frac{gm_{13}R_o(s/\omega_{z1}+1)}{(s/\omega_{P1}+1)(s/\omega_{P2}+1)}$$

$$= \frac{gm_{13}R_o(sR_5C_5/2+1)}{(gm_{14}R_0R_5C_5s+1)(sC_{EA}/gm_{14}+1)}$$

(2.21)

where  $C_{EA}$  refers to parasitic capacitance at  $V_{CNTRL}$  node and  $R_O = 1/(gds_{14}+gds_{13})$ .

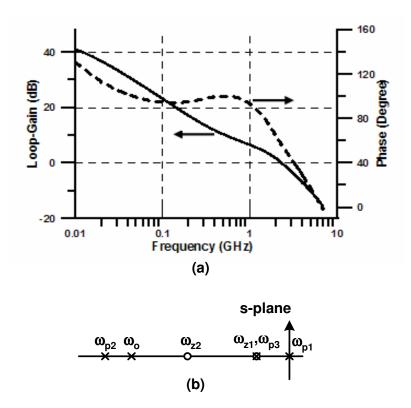

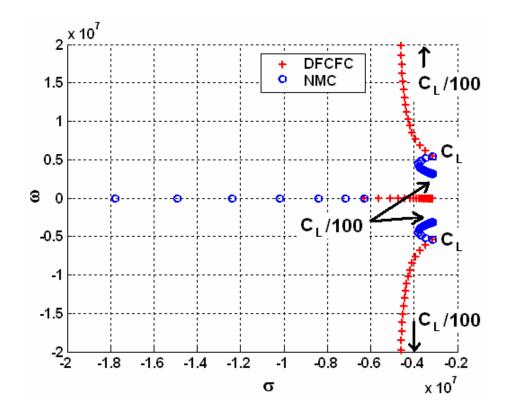

Fig. 2.20 (a) AC response of the CMFB loop. (b) Poles and zeros in s-plane.

AC response (open loop) of the complete CMFB loop is shown in Fig. 2.20(a). Also indicated in Fig. 13(b) are relevant poles and zeros.  $\omega_{p1}$  is the dominant pole located around  $2\pi$ \*13Mrad/s,  $\omega_{z1}$  and  $\omega_{p3}$  are situated around  $2\pi$ \*500Mrad/s.  $\omega_{z2}$ (introduced by R<sub>6</sub>-C<sub>6</sub> network) partially recovers the phase lost due to the dominant pole and extends the bandwidth. The output pole (1/R2'Cpo) is located around  $2\pi$ \*2.6Grad/s while  $\omega_{p2}$  is at about  $2\pi$ \*5Grad/s. Corner simulations show a minimum unity gain frequency of 2.2GHz and a worst case phase margin of 50<sup>o</sup>.

## **2.4 Experimental Results**

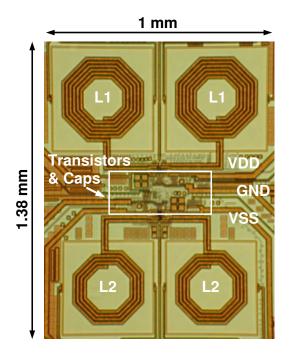

The prototype for 1GHz equalizing filter was fabricated using TSMC 1P6M 0.18µm standard CMOS technology. Thick Metal-6 layer is used for inductors. The filter layout is folded so as to minimize magnetic coupling between two biquads without sacrificing much area. The microphotograph of the chip is shown in Fig. 2.21.

Fig. 2.21 Chip micrograph.

## 2.4.1 Test Setup

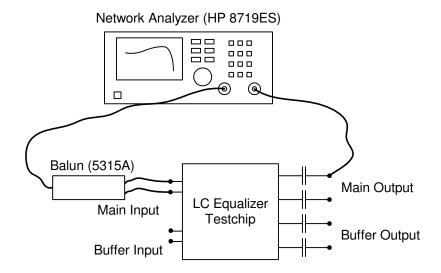

A schematic of the test setup is shown in Fig. 2.22. Differential input is generated by using wideband pulse inverter based balun (picoseconds 5315A). Measurement of the  $S_{21}$  of the equalizer, especially at the out-of-band frequencies, posed a particular difficulty due to feedthrough of input through the printed circuit board (PCB). Due to lack of good quality balun at the output, an offline difference method was used to accurately measure the transfer function. The  $S_{21}$  parameter of each of the single ended outputs was measured and saved as a complex vectors after averaging over a sufficient time. The complex vectors were then subtracted using a MATLAB program to generate the correct differential output that is free of a common-mode feedthrough component from the PCB.

Fig. 2.22 Test setup for measurement of the transfer function of the equalizer.

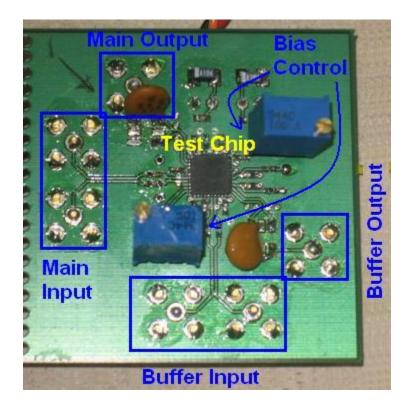

A photograph of the PCB used to make the measurements is shown in Fig. 2.23. The PCB is made as compact as possible and the ground planes were split between input and the output sides in order minimize the feedthrough of signal from input to output in the out-of-band frequencies.

Fig. 2.23 PCB used for testing the equalizer testchip.

# 2.4.2 Measurements Results and Comparison