# AN EFFICIENT LOGIC FAULT DIAGNOSIS FRAMEWORK BASED ON EFFECT-CAUSE APPROACH

A Dissertation

by

LEI WU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2007

Major Subject: Computer Engineering

# AN EFFICIENT LOGIC FAULT DIAGNOSIS FRAMEWORK BASED ON EFFECT-CAUSE APPROACH

A Dissertation

by

LEI WU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Duncan M. Walker

Committee Members, Jianer Chen

Rabinarayan Mahapatra

Weiping Shi

Head of Department, Valerie E. Taylor

December 2007

Major Subject: Computer Engineering

#### **ABSTRACT**

An Efficient Logic Fault Diagnosis Framework Based on Effect-Cause Approach.

(December 2007)

Lei Wu, B.S., Sichuan University, China;

M.S., Sichuan University, China;

M.S., McNeese State University

Chair of Advisory Committee: Dr. Duncan M. Walker

Fault diagnosis plays an important role in improving the circuit design process and the manufacturing yield. With the increasing number of gates in modern circuits, determining the source of failure in a defective circuit is becoming more and more challenging.

In this research, we present an efficient effect-cause diagnosis framework for combinational VLSI circuits. The framework consists of three stages to obtain an accurate and reasonably precise diagnosis. First, an improved critical path tracing algorithm is proposed to identify an initial suspect list by backtracing from faulty primary outputs toward primary inputs. Compared to the traditional critical path tracing approach, our algorithm is faster and exact. Second, a novel probabilistic ranking model is applied to rank the suspects so that the most suspicious one will be ranked at or near the top. Several fast filtering methods are used to prune unrelated suspects. Finally, to refine the diagnosis, fault simulation is performed on the top suspect nets using several common fault models. The difference between the observed faulty behavior and the simulated behavior is used to

rank each suspect. Experimental results on ISCAS85 benchmark circuits show that this diagnosis approach is efficient both in terms of memory space and CPU time and the diagnosis results are accurate and reasonably precise.

# **DEDICATION**

To my husband, parents and daughter

#### **ACKNOWLEDGMENTS**

I would like to express my gratitude to all those who gave me the possibility to complete this dissertation. Among the people who have contributed to this work, I would first like to thank my advisor and committee chair, Dr. Duncan M. (Hank) Walker. I am deeply indebted to Dr. Walker for his guidance, help, stimulating suggestions and encouragement throughout my research at Texas A&M University. His advice, novel ideas and understanding were critical for me to achieve the goal of this research.

I would also like to thank my committee members, Dr. Weiping Shi, Dr. Jianer Chen and Dr. Rabinarayan Mahapatra for their valuable comments and encouragement on this research. I would specially like to thank Dr. Weiping Shi and his group for generating coupling capacitance data for ISCAS85 benchmark circuits so that I can make use of it in my research.

Many thanks to my colleagues and friends: Wangqi Qiu, Bin Xue, Ziding Yue, Jing Wang, Zheng Wang, Sagar S. Sabade, Xiang Lu, and Vijay Balasubramanian for their encouragement and help. Especially I would like to thank Mr. Wangqi Qiu for use of his CodSim tool and many helpful discussions.

I would like to give my special thanks to my husband Gang whose love, encouragement, support and patience enabled me to complete this work. I am indebted to my parents, sisters and parents-in-law for their love and support all these years. I am very happy to have completed this work, and even happier to be able to dedicate this dissertation to my family.

# **TABLE OF CONTENTS**

|    |     |                                                       | Page |

|----|-----|-------------------------------------------------------|------|

| 1. | INT | RODUCTION                                             | 1    |

|    | 1.1 | Fault Diagnosis                                       | 1    |

|    | 1.2 | Diagnostic Data                                       |      |

|    | 1.3 | Two Diagnostic Approaches                             |      |

|    | 1.4 | Goals of Dissertation                                 |      |

|    | 1.5 | Dissertation Organization                             |      |

| 2. | PRE | VIOUS WORK                                            | 12   |

|    | 2.1 | Stuck-at Fault Diagnosis                              | 12   |

|    | 2.2 | Bridging Fault Diagnosis                              | 17   |

|    | 2.3 | Delay Fault Diagnosis                                 | 24   |

|    | 2.4 | I <sub>DDQ</sub> Fault Diagnosis                      | 25   |

|    | 2.5 | Per-Test Diagnosis                                    | 27   |

| 3. | CRI | TICAL PATH TRACING                                    | 30   |

|    | 3.1 | Overview                                              | 30   |

|    | 3.2 | Main Concepts and Definitions                         | 32   |

|    | 3.3 | Algorithm Flow of Improved Critical Path Tracing      | 37   |

|    | 3.4 | Stem Analysis                                         | 40   |

|    | 3.5 | Experimental Results                                  | 64   |

| 4. | SUS | PECT RANKING AND FILTERING                            | 70   |

|    | 4.1 | Phase 1: First-Level Filtering                        | 70   |

|    | 4.2 | Phase 2: First-Level Ranking                          | 72   |

|    | 4.3 | Phase 3: Second-Level Filtering                       | 73   |

|    | 4.4 | Phase 4: Second-Level Ranking                         | 74   |

| 5. | MO  | DEL-BASED FAULT SIMULATION                            | 78   |

|    | 5.1 | Motivation and Basic Structure                        | 78   |

|    | 5.2 | Line-to-Fault Mapping                                 |      |

|    | 5.3 | Fault Simulation                                      |      |

|    | 5.4 | Feedback Bridging Fault                               |      |

| 6. | EXP | PERIMENTAL RESULTS                                    | 90   |

|    | 6.1 | Run Time and Memory Usage Analysis                    |      |

|    | 6.2 | Diagnosis Accuracy and Resolution for Targeted Faults | 95   |

|     |      |                                                         | Page |

|-----|------|---------------------------------------------------------|------|

|     | 6.3  | Diagnosis Accuracy and Resolution for Untargeted Faults | 100  |

| 7.  | CON  | NCLUSIONS AND FUTURE WORK                               | 112  |

|     |      | Conclusions Future Work                                 |      |

| REF | EREN | ICES                                                    | 119  |

| VIT | 4    |                                                         | 135  |

# LIST OF FIGURES

|                                                                     | Page |

|---------------------------------------------------------------------|------|

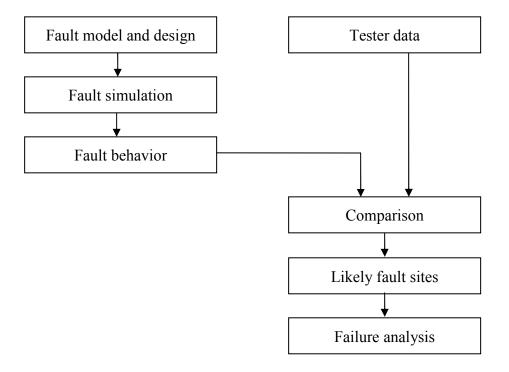

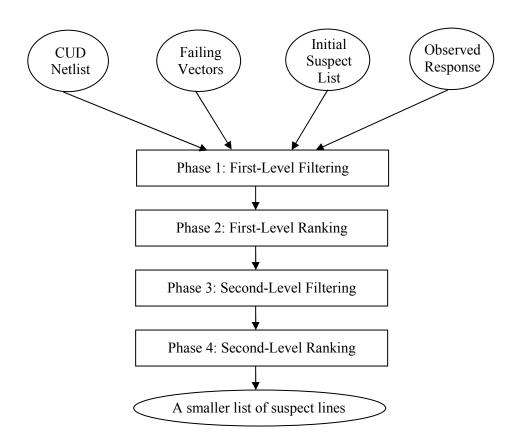

| Figure 1. Process of cause-effect fault diagnosis approach          | 6    |

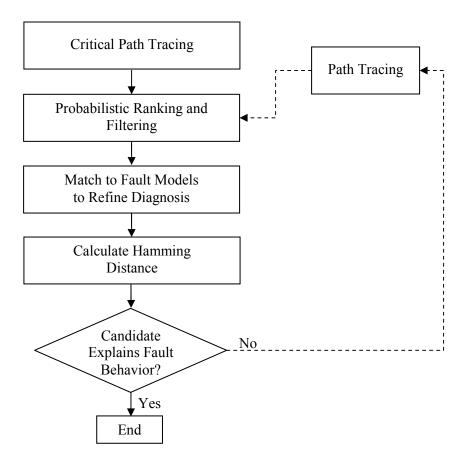

| Figure 2. General view of our diagnosis framework.                  | 9    |

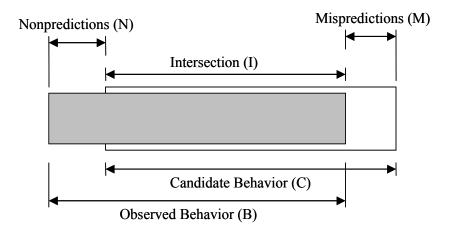

| Figure 3. Comparison of candidate behavior and observed behavior    | 20   |

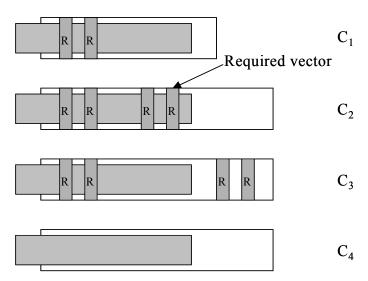

| Figure 4. Ranking for four candidates proposed in [2].              | 21   |

| Figure 5. A gate with unknown input value.                          | 33   |

| Figure 6. Critical and blocked input.                               | 34   |

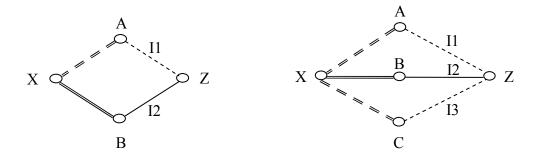

| Figure 7. Example of critical path graph.                           | 35   |

| Figure 8. Critical path tracing in a fanout-free circuit.           | 36   |

| Figure 9. Example of self-masking [71].                             | 37   |

| Figure 10. Example of multiple path sensitization.                  | 37   |

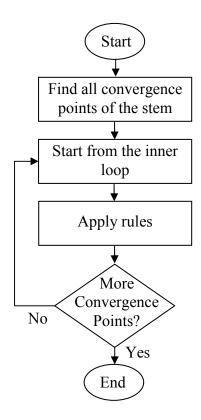

| Figure 11. Critical path tracing algorithm flow.                    | 39   |

| Figure 12. Example of rule A1 application.                          | 41   |

| Figure 13. Corresponding critical path graph of A1 application      | 41   |

| Figure 14. Critical path graph for rule A1 cases.                   | 42   |

| Figure 15. Example of rule A2 application.                          | 42   |

| Figure 16. Corresponding critical path graph of rule A2 application | 43   |

| Figure 17. Critical path graph for rule A2 cases.                   | 43   |

| Figure 18. Example of rule B application.                           | 45   |

| Figure 19. Corresponding critical path graph of rule B application  | 45   |

| Figure 20. Critical path graph for rule B cases.                    | 46   |

| Figure 21. Example of rule C application.                           | 47   |

|                                                                                  | Page |

|----------------------------------------------------------------------------------|------|

| Figure 22. Corresponding critical path graph of rule C application.              | 47   |

| Figure 23. Critical path graph for rule C cases.                                 | 48   |

| Figure 24. Example of rule D application.                                        | 49   |

| Figure 25. Corresponding critical path graph of rule D application               | 50   |

| Figure 26. Critical path graph of rule D cases.                                  | 50   |

| Figure 27. Example application of rule E.                                        | 51   |

| Figure 28. Corresponding critical path graph of rule E application.              | 51   |

| Figure 29. Critical path graph of rule E cases.                                  | 52   |

| Figure 30. Example application of rule F.                                        | 52   |

| Figure 31. Corresponding critical path graph of rule F.                          | 53   |

| Figure 32. Critical path graph of rule F cases.                                  | 54   |

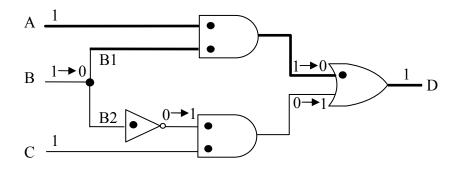

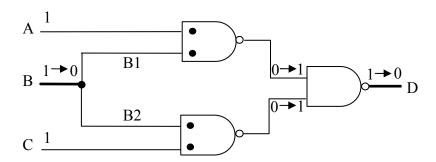

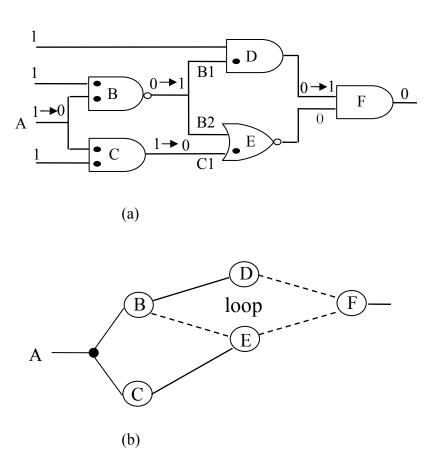

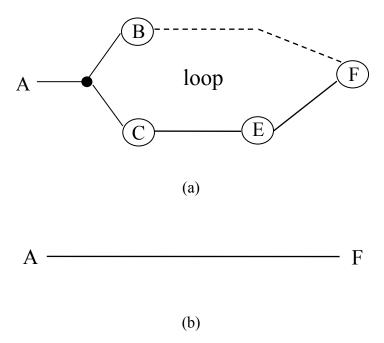

| Figure 33. Example of applying rules.                                            | 56   |

| Figure 34. Another example of applying rules.                                    | 58   |

| Figure 35. Critical path graph after applying rule on inner loop.                | 58   |

| Figure 36. Final critical path graph after applying rules .                      | 59   |

| Figure 37. Flowchart for determining stem criticality by applying rules          | 60   |

| Figure 38. Example of the reconvergence case that needs forward simulation       | 61   |

| Figure 39. Example of incorrectly determining stem criticality by applying rules | 62   |

| Figure 40. Algorithm that decides if a stem needs forward simulation             | 63   |

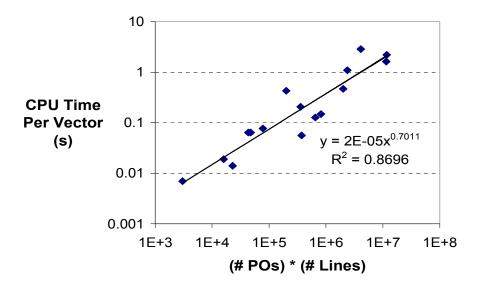

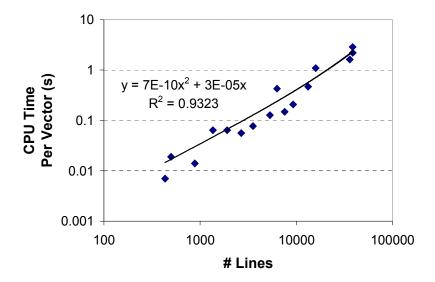

| Figure 41. Average CPU time per vector vs. (# lines · # POs)                     | 66   |

| Figure 42. Average CPU time per vector vs. # lines.                              | 67   |

| Figure 43. Average CPU time per vector vs. # critical nodes.                     | 67   |

|                                                                  | Page |

|------------------------------------------------------------------|------|

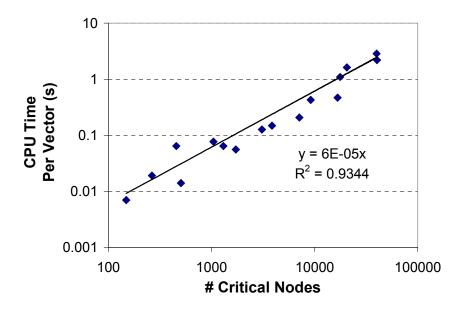

| Figure 44. Overall ranking and filtering process.                | 71   |

| Figure 45. Second-level ranking heuristic.                       | 75   |

| Figure 46. Example case for ranking analysis.                    | 76   |

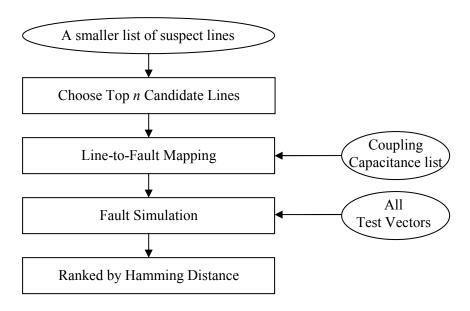

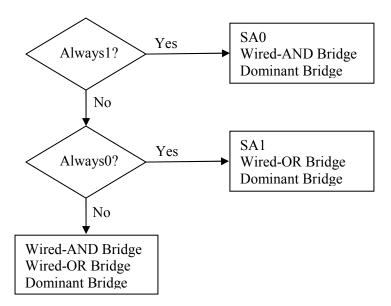

| Figure 47. Basic structure of model-based fault simulation step. | 79   |

| Figure 48. Metric to reduce fault candidate list.                | 80   |

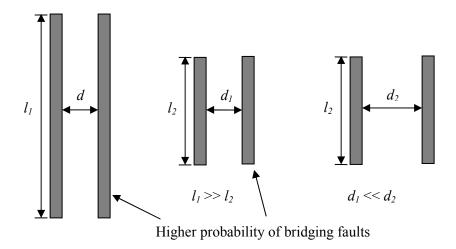

| Figure 49. Capacitance vs. probability of bridging faults [90]   | 82   |

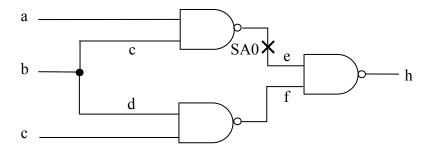

| Figure 50. Example of stuck-at fault model.                      | 84   |

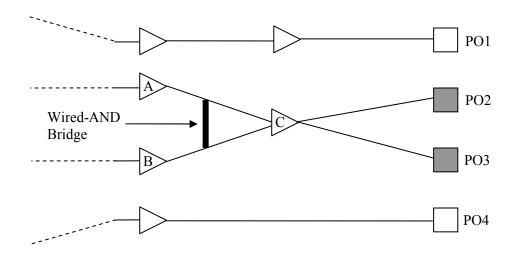

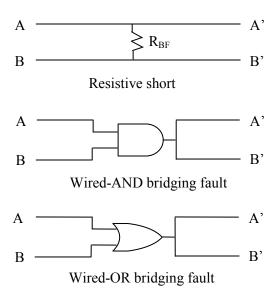

| Figure 51. Wired-AND and Wired-OR fault models.                  | 85   |

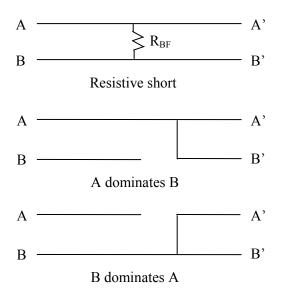

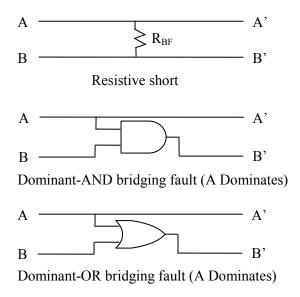

| Figure 52. Dominant bridging fault model.                        | 86   |

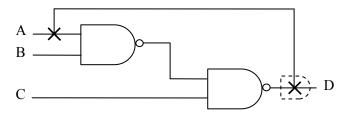

| Figure 53. Example of feedback bridging fault.                   | 87   |

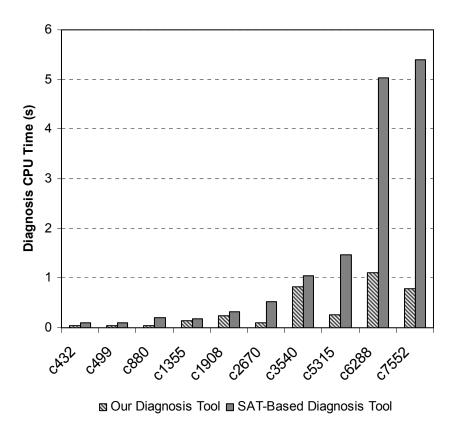

| Figure 54. Run time comparison with SAT-based diagnosis tool     | 93   |

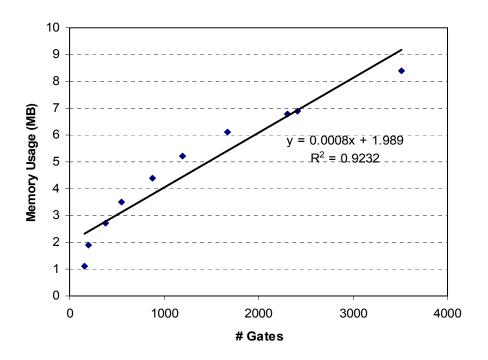

| Figure 55. Memory usage vs. circuit size.                        | 95   |

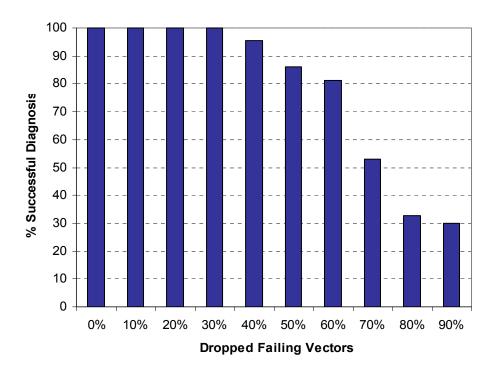

| Figure 56. % Successful diagnosis vs. % dropped failing vectors. | 102  |

| Figure 57. Dominant-AND and Dominant-OR fault models.            | 104  |

# LIST OF TABLES

|                                                                            | Page |

|----------------------------------------------------------------------------|------|

| Table 1. Table of previous, present and future semiconductor trends        | 2    |

| Table 2. Example of pass-fail fault signatures.                            | 4    |

| Table 3. Example of indexed full-response fault signatures.                | 5    |

| Table 4. Critical path tracing experimental result summary.                | 65   |

| Table 5. Our critical path tracing CPU time vs. FSIM CPU time              | 68   |

| Table 6. Percentage of candidate lines deleted after first-level filtering | 72   |

| Table 7. Logical behavior of wired-AND/OR Models                           | 85   |

| Table 8. Logical behavior of dominant model.                               | 86   |

| Table 9. Diagnosis time for ISCAS85 circuits.                              | 91   |

| Table 10. Run time analysis for ISCAS85 circuits                           | 92   |

| Table 11. Memory usage summary.                                            | 94   |

| Table 12. Diagnosis resolution and accuracy for targeted faults            | 96   |

| Table 13. ISCAS85 benchmark gate numbers summary                           | 97   |

| Table 14. Diagnosis resolution for different type of faults.               | 98   |

| Table 15. Diagnosis quality comparison with Sproing and MMA                | 99   |

| Table 16. Voting bridge defect diagnosis results.                          | 103  |

| Table 17. Behavior of dominant-AND/OR fault                                | 105  |

| Table 18. Diagnosis result for dominant-AND and dominant-OR fault          | 105  |

| Table 19. Diagnosis result for missing wire design error                   | 107  |

| Table 20. Diagnosis result for wrong gate type design error.               | 108  |

| Table 21. Diagnosis result for multiple faults.                            | 110  |

#### 1. INTRODUCTION

### 1.1 Fault Diagnosis

As integrated circuit (IC) manufacturing technology becomes more complex and feature size continues to shrink, more logic gates are being integrated into VLSI chips. Table 1 shows the past, present and future semiconductor technology roadmap [1]. The increasing complexity in IC designs makes the design and manufacturing process more vulnerable to defects, which cause deformation to the ideal IC.

Failure analysis has played an important role in improving the manufacturing process and yield. Failure analysis is the process of determining the actual failure cause for malfunctioning chips. Discovering the cause of failures in a circuit can often lead to improvements in circuit design or manufacturing process, with the subsequent production of higher-quality ICs.

Historically, failure analysis has been a physical process. Failure analysis engineers investigate the failing part using scanning electron microscopes, infrared sensors, particle beams, liquid crystal films and a variety of other expensive high-tech equipment to identify the cause of circuit failure. With the enormous number of circuit elements and the number of layers in modern ICs, physical search for defects cannot succeed without first having a small list of suspect locations [2]. This is the job of fault diagnosis. Fault diagnosis is the process of identifying the potential location of logic faults in

This dissertation follows the style and format of *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*.

malfunctioning chips, usually through analysis of the logic behavior of failing circuits. Physical failure analysis cannot be effectively conducted without considerable guidance from fault diagnosis. If the diagnosis is imprecise, the failure analysis engineer may waste time examining a large physical area. Even worse, if the diagnosis is inaccurate, the failure analysis engineer will be led to the wrong part of the chip, with the possible destruction of the actual defect site [3].

Table 1. Table of previous, present and future semiconductor trends.

| Year                                     | 1997-2001 | 2003-2006 | 2009-2012   |

|------------------------------------------|-----------|-----------|-------------|

| Feature size, nm                         | 250-180   | 130-70    | 45-32       |

| Millions transistors per cm <sup>2</sup> | 4-10      | 18-39     | 84-180      |

| Number of wiring layers                  | 6-7       | 7-9       | 9-10        |

| Pin Count                                | 100-1200  | 500-1936  | 780-3616    |

| Die size, mm <sup>2</sup>                | 50-385    | 60-520    | 70-750      |

| Clock rate, MHz                          | 200-1684  | 3088-5631 | 11511-19348 |

| Voltage, V                               | 1.2-2.5   | 0.9-1.2   | 0.9-1.0     |

| Power, W                                 | 1.2-61    | 2.8-98    | 3-138       |

Fault diagnosis is an important component of failure analysis. In principle, logic fault diagnosis is straightforward: based on the data available about the failing chip, the purpose of fault diagnosis is to produce a list of likely defect locations. However, with the enormous number of transistors in modern ICs and the number of layers in most complex circuits, defect localization is not an easy task. According to the International Technology Roadmap for Semiconductors (ITRS), the complexity of defect localization is expected to grow exponentially [1].

Previous-proposed strategies for VLSI fault diagnosis have a variety of limitations. Some techniques are limited to specific fault models and will fail on unmodeled behavior or unexpected data. Some techniques require very high memory usage, which is infeasible for large designs. Others apply ad hoc or arbitrary scoring mechanisms to rate fault candidates, making the result difficult to interpret or to compare with the results from other algorithms. The dissertation presents a fault diagnosis approach that is robust, comprehensive and practical. By introducing an extended critical path tracing method and a probabilistic ranking framework, the approach can produce accurate and precise diagnosis for stuck-at fault, wired-AND bridge fault, wired-OR bridge fault and dominant bridge fault. By using an effect-cause approach, it is designed to be memory efficient so that it can be applied to large designs.

#### 1.2 Diagnostic Data

Fault diagnosis is used to perform logical detective work. The evidence usually consists of a description of the circuit design, the tests applied and the pass-fail results of those tests [4]. In addition, more detailed per-test information may be provided.

The values applied at the circuit inputs and scanned into the flip-flops are referred to as the *input pattern* or *test vector*. The input vectors causing any mismatch between the outputs of the faulty chip and a fault-free chip are referred to as *failing input vectors*. The operation of scanning and applying an input pattern to the circuit and recording its output response is called a *test* [4], and a collection of tests designed to exercise part or all of the circuit is called a *test set*.

The output response of a defective circuit to a test set is referred to as the *observed* faulty behavior, and its logic representation is commonly known as a fault signature.

The fault signature is usually represented in one of the following two common forms.

The first is the pass-fail fault signature. It reports the result for each test in the test set, whether a pass or a fail. Typically the fault signature consists either of a bit vector for the entire test set in which by convention failing tests are represented as 1s and the passing tests by 0s, or the indices of the failing tests. Table 2 gives an example of a fault signature for a simple example of 10 tests, out of which 5 failing tests are recorded.

Table 2. Example of pass-fail fault signatures.

| Result for 10 tests: |          | Pass-fail signatures:     |  |

|----------------------|----------|---------------------------|--|

| 1: Pass              | 6: Pass  | By index: 2, 3, 7, 9, 10  |  |

| 2: Fail              | 7: Fail  | By bit vector: 0110001011 |  |

| 3: Fail              | 8: Pass  |                           |  |

| 4: Pass              | 9: Fail  |                           |  |

| 5: Pass              | 10: Fail |                           |  |

The second type of fault signature is the full-response fault signature, which reports not only what tests failed but also at which outputs (primary outputs and flip-flops) the differences are observed. Table 3 shows a simple example of indexed full-response fault signatures. Each failing test vector is recorded with a list of failing outputs. For example, the first row represents that primary outputs 3 and 5 are observed as faulty on failing test vector 2.

Table 3. Example of indexed full-response fault signatures.

Indexed full-response fault signatures:

2: 3, 5

3. 4

7: 2, 3

9: 2, 5

10: 3, 4

# 1.3 Two Diagnostic Approaches

Understanding how chips fail is the first step toward identifying and eliminating the causes of the failure. The objective of diagnosis is to pinpoint the fault location and analyze the defect causing it. There are two types of approaches available for fault diagnosis. The first approach is *cause-effect analysis*, which enumerates all the possible faults existing in an fault model and determines their corresponding output responses to a given set of tests before the test experiments [5]. The second type of approach is *effect-cause analysis*, in which the actual response of the failing chip is processed to determine its possible faults. The initial step of this type of approach is done in a model-independent fashion to avoid diagnostic failure due to an inadequate fault model.

### 1.3.1 Cause-Effect Approach

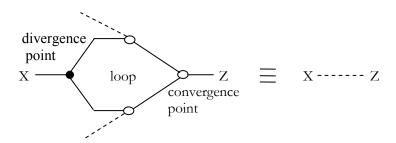

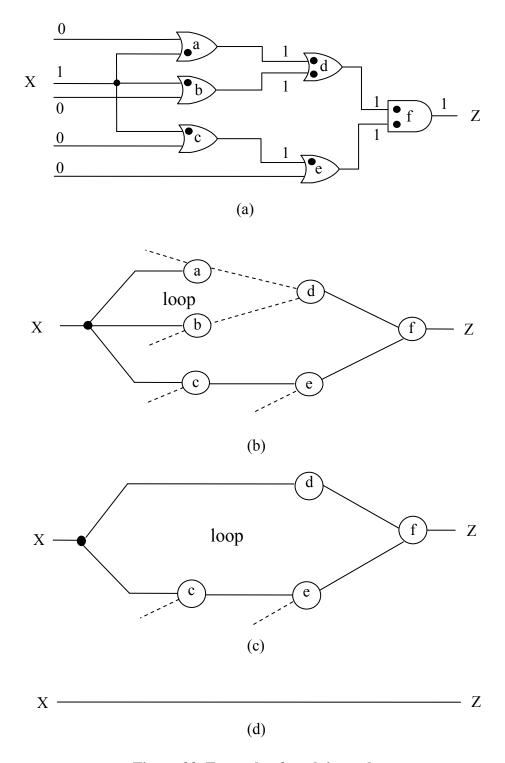

A cause-effect algorithm starts by using possible fault models (the "cause") to predict the behavior of faulty circuits through fault simulation, compares the observed faulty behavior (the "effect") to these predictions, each representing a fault candidate and identifies the candidate that most closely matches the observations. A cause-effect algorithm is characterized by the choice of the particular fault model(s) before any analysis of the actual faulty behavior is performed. All fault simulation is done ahead of time and all fault signatures stored in a database called a *fault dictionary*. Thus, it is also called *model-based diagnosis*. Figure 1 shows a simplified view of the process [6].

Figure 1. Process of cause-effect fault diagnosis approach.

One of the advantages of the cause-effect approach is that it can often provide a diagnosis result in less time in terms of analysis time per chip, simply because the fault simulation work has been done ahead of time and is therefore amortized over many diagnosis runs. This aspect is especially significant for high-volume situations in which a large number of parts must be diagnosed and in cases where a quick diagnostic result is

desired. In addition, this approach is successful if the actual defect behavior is accurately modeled by the selected fault model(s). However, it might be fooled by unmodeled faults. Since the type of fault is unknown beforehand, any single model-based diagnosis is unreliable. Another disadvantage of this approach is that fault simulation could become very expensive and the size of fault dictionary size could quickly become unmanageable for large designs. A classical fault dictionary includes a bit for detection or nondetection of each of n faults on a circuit with m outputs and v test vectors, with a total size of  $O(n \cdot m \cdot v)$ . Since modern VLSI circuits contains millions of gates, thousands of scan elements (which are considered outputs), and thousands of test vectors, a large amount of computational effort is involved in building a fault dictionary. Researchers have proposed several approaches to shrink the dictionary size, because dictionaries tend to be sparse, that is, most of their entries are zero [6]. Early methods usually used compaction, with resulting information loss [7]. In some cases, the information loss in compaction would dramatically reduce the diagnostic resolution [8]. More recent work has emphasized compression, with no information loss but with size reductions similar to the compaction techniques [9][10].

# 1.3.2 Effect-Cause Approach

The effect-cause approach analyzes the actual circuit responses and determines which fault(s) might have caused the observed failure effect. This class of methods does not need to build a fault dictionary.

The effect-cause algorithm starts from faulty outputs of the circuit (the "effect") and reasons back through the logic to identify possible sources of failure (the "cause") [4].

This class of methods usually traces backward from each primary output to determine the error-propagation paths for all possible fault candidates. The effect-cause diagnosis approach has several advantages. First, it does not depend on any particular fault model, so it is general enough to handle various fault types. This is an advantage over diagnosis methods that rely heavily on fault models. Second, it does not incur the significant overhead of simulating and storing the response of a large set of faults. Compared with the cause-effect methods, effect-cause techniques are more memory efficient and can cope with large designs. The disadvantage of effect-cause diagnosis is the inherent imprecision, most are conservative in their inference to avoid eliminating any candidate, but this usually leads to a large implicated area [4]. The other disadvantage is that the effect-cause approach is not suitable for products that are likely to be diagnosed in large quantities. As we discussed above, cause-effect approaches have less analysis time per chip than effect-cause approach because the fault dictionary is built in advance.

## 1.4 Goals of Dissertation

Since defect behavior is becoming more and more complex, cause-effect diagnosis even with multiple fault models may leave some faults unmodeled. To obtain an accurate and reasonably precise diagnosis that can be used to identify various faults, we propose an efficient fault diagnosis framework based on an effect-cause approach. Figure 2 shows the general view of the framework.

Figure 2. General view of our diagnosis framework.

In this approach, we first use an improved critical path tracing (CPT) algorithm to identify the initial suspect list. Then a probabilistic ranking method based on failing test patterns is used to rate each suspect. A filtering approach is applied to prune off unrelated fault candidates. Finally, a small list of highly ranked suspects is simulated with several commonly used fault models and matched to the observed behavior. For each fault candidate, the Hamming distance between the observed behavior and simulated behavior is calculated to determine how well each fault candidate can explain the faulty behavior. All the candidates are re-ranked in ascending order of Hamming

distance. If a candidate can explain the faulty behavior well, then we have obtained a successful diagnosis. Otherwise, this indicates there may be multiple fault sites and we will rely on path tracing.

Our diagnosis framework currently targets single defect diagnosis since our critical path tracing approach has a single fault assumption – that at most one fault is observed on each test pattern. It may not give an accurate prediction in the case of multiple faults, particularly when the multiple faults effect interfere each other. However, our diagnosis framework can be adapted to multiple fault diagnosis by incorporating a path tracing strategy. Compared to critical path tracing, path tracing is a more conservative approach, but guarantees that the potential source of error is included in the suspect list. Path tracing alone is not practical for general industry use because it sometimes produces too many fault candidates.

In general, the goal of this research work is to implement an effect-cause based diagnosis approach that is more efficient than common cause-effect diagnosis approaches both in terms of CPU time and memory, and more accurate and precise than common effect-cause diagnosis approaches.

# 1.5 Dissertation Organization

The dissertation is organized as follows. In section 2, we discuss previous diagnosis algorithms, their advantages and drawbacks. Section 3 presents the first stage of the proposed diagnosis approach - critical path tracing. An improved critical path tracing algorithm is proposed and its running time is compared with FSIM, a PPSFP fault

simulation approach. Section 4 discusses the second stage of diagnosis, in which a probabilistic ranking model is used to rank the suspects, which may then be filtered. Section 5 presents the third stage of diagnosis, in which fault simulation using various fault models is conducted to refine the diagnosis. Commonly used fault models are introduced and the parallel fault simulation procedure is described in this section. In section 6, the experimental results on ISCAS85 benchmarks show the accuracy and resolution of our diagnosis approach. Section 7 concludes the dissertation with future directions.

#### 2. PREVIOUS WORK

This section presents algorithms for VLSI diagnosis proposed by previous researchers, from the early 1980s to the present day. In general, the earliest algorithms were targeted solely at stuck-at faults and associated simple defects, while the later and more sophisticated algorithms have used more detailed fault models and targeted more complicated defects.

# 2.1 Stuck-at Fault Diagnosis

Many early VLSI diagnosis systems attempted to incorporate the concept of cause-effect diagnosis with a previous-generation physical diagnosis method called guided-probe analysis. Guided-probe analysis employed a physical voltage probe and feedback from an analysis algorithm to intelligently select accessible circuit nodes for evaluation [5]. Two examples were Western Electric Company's DORA [11] and an early approach of Teradyne, Inc. [12]. The DORA and Teradyne techniques attempted to supplement the guided-probe analysis with information from stuck-at fault signatures.

Both systems used relatively advanced matching algorithms for their time. The DORA system used a nearness calculation that is described as fuzzy match by the authors [2]. The Teradyne system employed the concept of prediction penalties. The signature of a candidate fault is made up of {output, vector} pairs, which is considered as a prediction of some faulty behavior. When matching with the actual observed behavior, the Teradyne algorithm scored a candidate fault by penalizing for each

{output, vector} pair found in the stuck-at fault signature but not found in the observed behavior, and penalizing for each {output, vector} pair found in the observed behavior but not the stuck-at fault signature. These are now commonly known as *misprediction* and *nonprediction* penalties, respectively.

While other early and less sophisticated algorithms applied the stuck-at fault model directly and expected exact matches to simulated behaviors, it became obvious that many failures in VLSI circuits do not behave exactly like stuck-at faults. Some stuck-at diagnosis algorithms increased the complexity and sophistication of their matching method to account for unmodeled effects. An algorithm proposed by Kunda [13] ranked matches by the size of intersection between signature bits. In the algorithm, misprediction was not penalized but there was a limit on the nonprediction. This reflects an implicit assumption that unmodeled behavior generally leads to over-prediction: any unmodeled behavior will cause fewer actual failures than predicted by simulation. This assumption likely arose from the intuitive expectation that most defects involve a single fault site with intermittent fault behavior, which could be wrong in case of multiple fault sites.

A more balanced approach was proposed by De and Gunda [14]. In this algorithm, users applied relative weights on misprediction and nonprediction. By modifying traditional scoring with these weights, the algorithm assigned a quantitative ranking to each stuck-at fault. The authors claimed that the method could be used to explicitly target defects that behave similar to but not exactly like the stuck-at fault model, such as some opens and multiple independent stuck-at faults, but it could diagnose bridging

defects only implicitly (by user interpretation). This algorithm was unique for its ability to allow the user to adjust the assumptions about unmodeled behavior that other algorithms made implicitly and was perhaps the most general of the simple stuck-at diagnostic algorithms.

Another stuck-at fault diagnosis algorithm was proposed by Waicukauski and Lindbloom [15]. This algorithm is very pervasive because the most popular commercial tools, Mentor Graphics FastScan [16] and Synopsys TetraMAX[17], are based on this algorithm. We refer to this algorithm as the *W&L algorithm*.

The W&L algorithm relies solely on stuck-at fault assumptions and simulations. It is best classified as a dynamic cause-effect algorithm. A cause-effect algorithm is static, in which all fault simulation is done ahead of time and all fault signatures stored in a fault dictionary; or, it can be dynamic, where simulations are performed only as needed. However, W&L algorithm does borrow some ideas from effect-cause approaches because it uses limited path tracing to reduce the number of simulations it needs to perform.

The W&L algorithm uses a simple scoring mechanism, relying mainly on exact matching. However, it performs the matching in an innovative way by matching fault signatures on a per-test basis. In this algorithm, each failing test pattern is considered independently. From the first failing pattern and the good-machine values, it uses path tracing to create a minimum fault list. It then simulates each fault in the fault list; if a candidate predicts a fail for the test and the outputs match exactly, then a "match" is found. All the matching fault candidates are then simulated against the remaining failing

patterns. The candidate that explains the most failing patterns is kept. Then all of the failing test patterns that have already been explained by this candidate are eliminated. The diagnosis process repeats until all failing tests are considered.

The W&L algorithm also conducts a post-processing step. It examines the final candidate set to classify the diagnosis. If the diagnosis consists of a single stuck-at fault (with any equivalent faults) that matches all failing test patterns, it then uses passing patterns to improve diagnosis resolution. If the stuck-at candidates can also explain all of the passing test patterns, the diagnosis is classified as a "Class I" diagnosis. If the diagnosis consists of a single candidate that explains all the failing test patterns but not all passing test patterns, e.g. there is some misprediction, then the diagnosis is classified as a "Class II" diagnosis. The authors indicated that the defect types could be diagnosed in "Class II" diagnosis include CMOS opens, dominant bridging and intermittent defects. Finally, "Class III" diagnosis consists of multiple stuck-at candidates with possible misprediction and nonprediction. The defects that could be diagnosed in this class of diagnosis included multiple stuck-at defects and wired logic bridging faults.

The two appealing features of the W&L algorithms are the per-test approach and the post-processing analysis. The matching algorithm is a greedy coverage algorithm over a set of failing tests. Moreover, the algorithm has the ability to address multiple simultaneous defects. However, it has an assumption that the fault effects from such defects are non-interfering. Therefore, the diagnosis would fail if the multiple defects always overlap on their fault effect propagation for all the failing test patterns.

Because of the huge overhead of fault dictionary size and simulation time in cause-

effect stuck-at diagnosis, some researchers introduced effect-cause stuck-at diagnosis. To our knowledge, the idea was first proposed by Breuer et al. [18]. Their approach is algebraic in nature and requires the solution of large systems of Boolean equations. This technique becomes impractical even for circuits of moderate complexity. Abramovici and Breuer later proposed a new effect-cause approach. The main tool of the algorithm is the Deduction Algorithm, which processes the actual response of the defective chip to deduce its internal values [19][20]. The Deduction Algorithm can also recognize a response generated by a fault situation that cannot be modeled as a stuck fault. Later Rajski and Cox proposed another effect-cause diagnosis technique [21]. Both algorithms attempt to identify all fault-free lines, and so can implicitly diagnose multiple faults and various fault types. However, the diagnostic results are pessimistic and imprecise.

The most widely used effect-cause approach is *path tracing*. It traces error propagation paths backward from failed primary outputs toward primary inputs. *Critical path tracing* is one of the popular path tracing methods. It will be discussed in detail in the next section. A design error diagnostic algorithm based on critical path tracing was proposed in [22]. The goal of this method is to find a single-fix net, which is a net where a change in logical value explains all failing outputs on all failing vectors but does not cause a change on any passing vectors. Each time a net is found as a fix net for each primary output on each failing vector, the suspicion level of this net is increased by 1. All of the candidate nets are ranked by the suspicion level; the one with the highest level is ranked highest. For defective circuits with multiple faults, there are several strong partial-fix nets that can partially explain the circuit faulty behavior. In this case, nets

with the highest suspicion level can be misleading since this method cannot guarantee that the best candidates are always ranked at the top in the case of multiple faults.

# 2.2 Bridging Fault Diagnosis

Since it has been shown repeatedly that the stuck-at fault model does not accurately reflect the behavior of silicon defects such as bridging [23][24][25][26][27], several methods have been suggested to improve the diagnosis of bridging faults using the stuck-at fault model [2][28][29][30].

Millman, McCluskey and Acken proposed an explicit bridging fault diagnosis technique using the single stuck-at fault model, which is henceforth called the MMA technique [29]. The authors introduced the idea of composite bridging fault signatures, which are created by concatenating the four stuck-at fault signatures for the two shorted nodes. The underlying idea is that any vector that detects a bridging fault will detect one of the four stuck-at faults associated with the two nodes. Therefore, the bridging fault signature must be included in the resulting composite signature. The matching algorithm used in MMA technique is simple subset matching: any candidate whose composite signature contains all the observed {vector, output} pairs is considered a match and appears in the final diagnosis.

A notable advantage of the MMA technique is that it relies on the single stuck-at fault model to create combined stuck-at fault signatures, instead of bridging fault simulation, which can be computationally expensive both in term of fault list sizes and fault simulation time complexity. However, the use of combined stuck-at fault signatures

over-predicts the bridge fault behavior because it includes stuck-at faults that do not appear on the bridged nets. For example, in order for a bridging fault to be detected, a test vector must stimulate opposite logic values on the two bridged nodes. Any vector in a composite signature that detects the same-valued stuck-at fault on both bridged nodes must stimulate the same value on both nodes; such a vector cannot detect the bridging fault. Therefore, the MMA algorithm results in a large, unranked suspect list, with no expression of preference or likelihood assigned to the candidates. In addition, the MMA technique may generate incorrect diagnosis results in the case of the Byzantine Generals Problem [28][31][32]. Because gate input logic thresholds are not identical, different downstream gates can interpret the voltage as different logic values. This phenomenon is known as the Byzantine Generals Problem. Since the MMA technique uses a strict matching algorithm in which the candidate is good if it contains the observed faulty behavior or is removed if it does not, this causes an unacceptable rate of failed diagnosis.

An approach similar to the MMA algorithm was presented by Chakravarty and Gong [33]. Their algorithm did not explicitly create composite stuck-at signatures but used a matching method on combinations of stuck-at signatures to create the same result. Both of these two bridging fault diagnosis techniques suffer from imprecision: the average sizes of both diagnosis results are very large, consisting of hundreds or thousands of candidates. Other researchers have continued to use and extend the idea of stuck-at based composite signatures for various fault models [34][35].

While the original MMA technique is attractive because of its use of simple stuck-at fault signatures for diagnosing bridging faults, it has been demonstrated to have several

inadequacies: large average diagnoses, unordered fault candidates, and a significant percentage of failed diagnoses. An improved bridging fault diagnosis technique was proposed by Lavo et al [2]. They tried to improve the MMA technique by addressing each of the issues mentioned above by using match restriction, match requirement and match ranking.

A weakness of the MMA technique is that a faulty signature is likely to be contained in a large number of composite signatures. The larger a composite signature, the larger the size of an average diagnosis. The match restriction employed in this improved technique eliminates from a composite signature any entries that cannot be used to detect the bridging fault. In order for a bridging fault to be detected, a test vector must stimulate opposite logic values on the two bridged nodes. Any vectors that place identical values on the bridged nodes are removed according to the match restriction, which results in a composite signature that more precisely contains the possible behavior of the bridging fault.

While the match restriction relied on identifying test vectors that cannot detect a particular bridging fault, the improvement presented in match requirement is based on vectors that should be able to detect a bridging fault — namely, those vectors that place opposite logic values on the bridged nodes and detect single stuck-at faults on both of the bridged nodes. Therefore, the second improvement is to enforce match requirement on vectors by identifying such vectors in the composite signatures.

The third improvement suggested by Lavo et al is match ranking. The original MMA technique did not order the candidates of a diagnosis; a diagnosis simply consists of an

unranked list of candidate faults, which is not very helpful to guide the physical search for defects. In addition, the original MMA technique had a strict matching criterion: either a candidate contained the observed behavior, or it was eliminated from consideration. The improved technique can order the candidates by assigning a measure of likelihood to every candidate. The idea behind ranking candidates is to turn the strict accept-or-remove criteria into a more quantitative measure of relative match goodness. Figure 3 [2] shows the comparison between the observed behavior (shaded) and a candidate fault behavior (unshaded).

Figure 3. Comparison of candidate behavior and observed behavior.

The observed behaviors that are correctly predicted by the candidate are represented as set I (Intersection), the output errors that are predicted by the candidate but not observed are represented as set M (Misprediction), and the output errors that are observed but not predicted by the candidate are represented as set N (Nonprediction) [2].

The primary ranking concern is that the best candidates are the ones that contain the largest amount of the faulty behavior. Therefore, the first quantitative measure of match

goodness is the size of the intersection of the observed behavior and the composite signature. If the first ranking cannot provide enough information to differentiate candidates, then the second measure is the number of required vectors; the candidate containing more required vectors is ranked higher. Additionally, there is a third measure to judge the quality of an individual match: the amount of misprediction. The candidate with less misprediction is more likely to be the better explanation for the faulty behavior. Figure 4 shows the ranking for four candidates C1, C2, C3 and C4. The candidate C1, C2 and C3 are ranked higher than C4 because they have a larger intersection set; C1 and C2 are ranked higher than C3 because they contains a higher percentage of required vectors; and C1 is ranked higher than C2 because it contains less misprediction. One drawback of this improved bridging fault diagnosis is the need to build a large fault dictionary [8].

Figure 4. Ranking for four candidates proposed in [2].

A more direct approach to bridging fault diagnosis was suggested by Aitken and

Maxwell [36]. Rather than the algorithm described above which used a simple stuck-at fault model paired with a complex fault diagnostic algorithm, the authors chose to use a complex and realistic bridging fault model paired with a simple diagnostic algorithm. This algorithm examined the behavior of actual bridging defects on silicon and performed simulation using biased voting [37], which is an extension of the voting model that takes logic gate thresholds into account. This is a cause-effect diagnosis approach for bridging faults. The authors reported excellent results, both in accuracy and precision. While there are obvious advantages to this approach, there are also significant disadvantages. The number of realistic two-line bridging faults is significantly larger than the number of single stuck-at faults in a circuit. The overall time spent in fault simulation can be prohibitive since the cost of simulating each of these faults can be expensive, especially if the simulation considers electrical effects.

All of the above bridging fault diagnosis techniques are based on the cause-effect approach. Venkataraman and Fuchs presented a deductive technique for diagnosis of bridging faults [38]. This effect-cause bridging fault diagnosis scheme first uses a path tracing procedure to deduce lines potentially associated with the bridging faults. An intersection graph is constructed dynamically from the information obtained through path tracing from failing outputs. An intersection graph is an undirected graph that shows the connection among sets that contain nets that lie on the path tracing and have at least one net in common. The intersection graph implicitly represents all candidate bridging faults under consideration. Two conditions are used to improve diagnostic resolution. When a controlling input is the branch of a stem, one of whose other

branches has been chose, then this input should be selected. The second condition is that the most easily controllable input is likely to give the smallest node set. The deductive algorithm has been experimentally shown to be efficient in both space and time. The drawback of the technique is that in about 25% of the cases, the diagnosis is partial; that is, only one of the bridge nodes can be determined with certainty. In such cases, if the suspect list is so large that bridging fault simulation cannot be performed, then other techniques [2][28][29][33] need to be incorporated to improve the resolution.

The diagnosis techniques presented so far do not use physical layout information to diagnose faults. Inductive fault analysis [39] is a method using the circuit layout to determine the relative probabilities of individual physical faults in the fabricated circuit. A bridging fault diagnosis approach based on inductive fault analysis was introduced in [40][41]. This approach is termed CAFDM (Computer-Aided Fault to Defect Mapping). The authors use physical design and test failure information combined with bridging and stuck-at fault models to localize defects in random logic. In order to get the list of realistic bridge faults, the authors developed the FedEx two-node bridge fault extractor [42]. The FedEx fault extractor analyses the chip layout and identifies the critical areas where short circuits could occur on the suspect nets, including their locations and layers. Then a structural procedure, backconing, was used to identify all the potential bridges in the intersection area. Those bridge faults were then injected in the Verilog netlist. Finally, the FastScan diagnosis engine was run to find suspect nets. If these are associated with fault models, they are then mapped to the bridge faults. One of the advantages of this diagnosis technique is that it uses physical layout to get a realistic

bridging fault list including the layer and locations, which efficiently aids failure analysis. Furthermore, the FedEx tool has proven to be much faster than all previous fault extractors [43][44][45][46][47][48][49]. The drawback of this approach is that it requires the physical layout information of the defective chip. In addition, the potential fault list generated by backconing is typically much larger than obtained using critical path tracing.

## 2.3 Delay Fault Diagnosis

Due to the increasing importance of timing-related defects in high-performance designs, researchers have proposed methods to diagnose timing defects with delay fault models. Two commonly used delay fault models are the transition fault model [50] and the path delay fault model [51]. The transition fault model assumes that the delay fault affects only one gate in the circuit, and the extra delay caused by the fault is large enough to prevent the transition from reaching any primary output within the specification time. Under the path delay fault model, a circuit is considered faulty if the delay of any of its paths exceeds the specification time.

A delay fault diagnosis method based on an effect-cause analysis was developed by Cox and Rajski [52]. However, this method is unrealistic due to the limitations of the transition fault model. A single gate delay fault diagnosis approach was presented in [53] and [54]. Their approach takes advantage of critical path tracing to identify the probable fault locations, so it is also effect-cause diagnosis. The simple two-valued logic simulation is used in [53], which misses delay faults caused by static hazards on lines. In

[54], a six-valued algebra is used to account for static hazards. However, the backtrace is performed along all fanin lines that can have transition under test and could lead to a conservative diagnosis. Since component delays are not considered, the probable fault location is not guaranteed.

In [55], the authors present an approach based on static timing information targeting multiple delay fault diagnosis. For each fault candidate, they try to use a robustly tested path and observe a fault-free situation to determine the upper and lower bounds for a suspect delay fault. The experimental results show a much-improved diagnostic resolution when compared to non-timing-based approaches. However, the resolution is still unsatisfactory for time-to-market requirements.

More recent work advocates using statistical timing information to guide the delay defect diagnosis [56][57], which produces good diagnostic results. In this method, it is assumed that the probability density functions of each internal cell or interconnect are known. In reality, the accurate probability density functions information may not be easily available.

## 2.4 I<sub>DDO</sub> Fault Diagnosis

Mainstream VLSI fault diagnosis has been concerned with logic failures at circuit outputs or scan flip-flops. Unlike the logic fault diagnosis techniques presented above,  $I_{DDQ}$  diagnosis uses the  $I_{DDQ}$  fault model, in which the presence of a defect causes an abnormally high amount of current to flow in the circuit in a normally quiescent or static state. The vectors used for  $I_{DDQ}$  diagnosis are designed to put the circuit in a static state,

in which no logic transitions occur [4].

Aitken presented a method of diagnosing faults when both logic fails and I<sub>DDQ</sub> fails are measured simultaneously [58], and he later made this approach more general by including fault models for intra-gate and inter-gate shorts [59]. Later Chakravarty and Suresh presented an approach which examines the logic value applied to circuit nodes during failing tests, and attempts to identify pairs of nodes with opposite logic values as possible bridging fault sites [60]. Both of the approaches rely on I<sub>DDQ</sub> measurements that can be definitively classified as either a pass or a fail, which limits their application in some situations. Then the application of current signatures was proposed to address the limitation [61][62], in which relative current measurements across the test set are used to infer the presence of a defect, instead of the absolute values of I<sub>DDQ</sub>. A diagnosis approach introduced in [63][64] attempts to use the presence of certain large differences between current measurements as a sign that certain types of defects are present. This idea was further extended by Thibeault [65]. He applied a maximum likelihood estimator to changes in I<sub>DDQ</sub> measurements to infer fault types.

The advantages of  $I_{DDQ}$  diagnosis are that the pass/fail  $I_{DDQ}$  signatures are easy to construct, and when  $I_{DDQ}$  diagnosis works, the resulting diagnoses are usually both precise and accurate [2]. The disadvantage is that not all circuits are  $I_{DDQ}$  testable. Furthermore, determining an  $I_{DDQ}$  diagnostic current threshold (i.e., the limit that distinguishes "passing" current levels from "failing" current levels) is not simple [66], which may cause ambiguity. Besides,  $I_{DDQ}$  diagnosis also requires a lot of manual intervention: the pass-fail current threshold may have to be repeatedly adjusted for each

chip until a perfect diagnostic match is found.

## 2.5 Per-Test Diagnosis

A recent methodology is based on the concept of "one test at a time," or per-test diagnosis [67]. Several previous works, such as Poirot [68], SLAT [69] and iSTAT [70], have adopted the per-test diagnosis concept where the test patterns are analyzed one at a time. In these approaches, test patterns are viewed as independent, and diagnosis is carried out on each test pattern and produces a candidate fault set for each of them.

In [69], a Single Location At-a-Time (SLAT) approach is presented by assuming that for any defective chip, there will be some tests for which the failing outputs will exactly match the predicted failing outputs of one or more simple (generally stuck-at) faults. Each of these test patterns (SLAT patterns) is then associated with a number of such single fault candidates, and each fault candidate can be used to explain the failing responses of that test pattern. These candidate faults are arranged into sets of faults that cover all the matched tests. The collections of faults are called multiplets.

Later in [70], an improved Single Test At-a-Time (iSTAT) approach is introduced. iSTAT still generates multiplets based on the SLAT strategy. However, it applies a scoring algorithm to rank the multiplets and only the ones with highest score are selected. It is shown that scoring can significantly reduce the number of candidate multiplets, hence improve the diagnostic resolution. Although iSTAT has shown a lot of strength on increasing the diagnostic resolution over SLAT, there still exist some problems. First, iSTAT can determine which multiplet is more likely to include a true

fault site. However, it cannot determine which fault within a multiplet is more likely to be the true fault site. Therefore, if the top-ranked multiplet contains a large number of fault candidates, iSTAT becomes less accurate. Second, while iSTAT reduces the candidate size compared to SLAT, the scoring algorithm and the choice of top-ranked multiplets in iSTAT can lead to a misleading diagnosis result, where the true fault sites are not included in the top-ranked multiplets.

In order to improve the diagnostic quality of SLAT and iSTAT, Liu proposed a new approach named Single Output At-a-Time (SOAT) [67]. SOAT uses the same strategy as iSTAT to produce scored multiplets. However, in addition to using the response of each failing test pattern, it also exploits the information associated with each failing output pin and produces a new list of scored multiplets. The multiplets from iSTAT and SOAT are then combined and a scored fault list is generated through a new scoring algorithm. This approach can achieve a diagnostic quality superior to both SLAT and iSTAT in accuracy and failure coverage. The tradeoff is the increased running time.

Another per-test diagnosis technique is the Poirot algorithm [68]. It also diagnoses test patterns one at a time. In addition, it employs stuck-at signatures, composite bridging fault signatures, and composite signatures for open faults on nets with fanout. Its scoring method is rudimentary, especially when it compares the scores of different fault models. The scoring algorithm always prefers the simpler model when two faults of different types equally explain failures.

There are several advantages to the per-test fault diagnosis approach. First, it explicitly handles pattern-dependence, which is often seen with complex fault behavior.

It also explicitly targets multiple fault behaviors. However, the primary assumption underlying the per-test diagnosis approach is that there will be some failing patterns for which all the observed failing outputs can be explained exactly be at least one stuck-at faults. This assumption immediately implies some limitations: what if there are many individual defects in the design, or the defect is so complex that no test pattern can be found whose fails can be explained by a single stuck-at fault [69]. In those cases, the diagnosis would fail.

#### 3. CRITICAL PATH TRACING

#### 3.1 Overview

Critical path tracing is very useful in fault and design error diagnosis [22], where fast observability calculations are important. Critical path tracing has also been proposed as an efficient alternative to fault simulation because it is faster and requires less memory than conventional fault simulation [71][72]. One of the key factors contributing to the increased efficiency of critical path tracing compared to fault simulation is that it deals directly only with the detected faults rather than all possible faults.

Critical path tracing is used to find faults detected by a specific test vector. It is a two-step procedure. First, it simulates the fault-free circuit and identifies sensitive gate inputs. Second, it traces paths from primary outputs (POs) toward primary inputs (PIs) along which faults are detected. Critical path tracing was proposed by Abramovici, Menon and Miller. The original implementation of this method is named CRIPT [71][73]. In this original critical path tracing approach, when a fanout is encountered, a simulation phase will determine if the effect of changing the value of a fanout stem will be marked as critical. In order to reduce the size of the section of the circuit that is simulated, a partitioning of the circuit is done to simulate only up to the point whose effect on the output is known. CRIPT was reported to be inaccurate due to multiple path sensitization [71]. In addition, CRIPT had  $O(G^2)$  time complexity in the worst case [74] where G is the number of gates in the circuit. CRIPT is inefficient because critical path tracing by this method requires much forward simulation and backward propagation in

an iterative fashion. In addition, partitioning of the circuit into isolated fanout-free regions (FFR) is a time consuming process. More recently, CRIPT was made exact with the introduction of stem analysis by forward propagation [73][75]. However, this exact critical path tracing algorithm was slow. Another critical path tracing approach [76][77] introduced a dynamic data structure, called the criticality constraint graph (CCG), which carries enough information during the backward pass to determine a stem's criticality from the criticality of its fanout branches. This algorithm is fast and exact, but its dynamic data management makes the algorithm much more complicated than CRIPT. Considering the problems associated with the above techniques, a simple method named one pass critical path tracing was proposed by Navabi et al [78]. This method is exact and runs in linear time. However, it has several problems. First, the stem analysis only considers AND, NAND, OR and NOR gates with two inputs. Second, the rules used to determine stem criticality do not cover all cases of reconvergence. Third, this method does not consider unknown X values. Thus, this method cannot be applied on real circuits.

We proposed a fast critical path tracing algorithm which extends one pass critical path tracing so that it can be applied on any combinational circuit. It avoids frequent iterative forward simulation and backward propagation [79][80]. Fault free simulation is only done once and supports three logic values of 0, 1 and X. For most cases, stem criticality is determined in one pass by applying seven rules. This improved critical path tracing algorithm is exact because it can handle any kind of recovergence in circuits.

### 3.2 Main Concepts and Definitions

This section introduces the key definitions and concepts in critical path tracing.

## 3.2.1 Critical Line

The concept of *critical line* is defined in [81]. A line l has a critical value v in the test vector t if and only if t detects the fault l s-a-v. A line with a critical value in t is said to be *critical* in t.

All primary outputs are critical due to their perfect observability. All critical lines for a given test vector form the *critical paths* [82] which are determined by backtracing from POs towards PIs.

#### 3.2.2 Sensitive Input

A gate input is *sensitive* if complementing its value would change the value of the gate output [71]. Sensitive inputs can be identified based on the Dominant Logic Value (DLV) [72]. A DLV at a gate input is one that forces the gate output to a value, regardless of the values on the other inputs. The DLV of AND and NAND gates is 0, while the DLV of OR and NOR gates is 1. XOR and XNOR gates have no DLV because any single input change will cause an output to change. The following rules are used to identify sensitivity [71] in a 2-valued simulation:

- 1. If only one input *i* has a DLV, then *i* is sensitive.

- 2. If all inputs have the complement of the DLV, then all inputs are sensitive.

- 3. If neither 1 nor 2 holds, then no input is sensitive.

- 4. All inputs on XOR and XNOR gates are sensitive.

These rules can be extended to handle 3-valued simulation. Figure 5 demonstrates such a case.

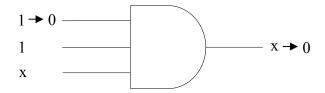

Figure 5. A gate with unknown input value.

In Figure 5, assume there is a SA0 (stuck-at-zero) fault at the top input; therefore the faulty output is 0. In traditional 3-valued simulation, the faulty '0' value is considered as a different value from the previous X (unknown) value. However, this cannot hold when we determine sensitive inputs. If the output of the good machine had actually been 0, it would be impossible to observe the difference between this value and the faulty machine '0' value [83]. Two rules below will be used to determine the sensitivity of a gate input when using 3-valued simulation:

- 1. If the gate output is X, then no input is sensitive.

- 2. If at least one input is X, there no input is sensitive.

With sensitive inputs identified, we can determine if a gate input is critical. A gate input is critical if the gate output is critical and the input is sensitive [71].

### 3.2.3 Blocked Line

If an input of a gate is non-critical, this line is a *blocked line*. As the name implies, a blocked line blocks the propagation of a fault from the gate output. A *blocked path* is a path with at least one blocked line [78].

Each line in the circuit has a blocked value *n*, which indicates how many blocked lines are on the path between the PO and the gate that has this line as output.

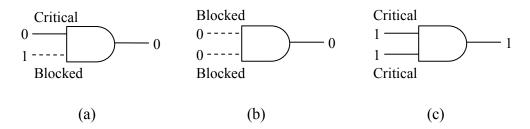

Figure 6 shows how an input line is identified as a critical line or blocked line for a simple two-input AND gate. In a two input AND gate, if only one of the inputs of the gate has a DLV, as shown in Figure 6(a), that input line is critical and the other is blocked. If both inputs have a DLV, as shown in Figure 6(b), then each input is blocked by the other input. Therefore, both inputs will be referred to as blocked. If both inputs of a gate have non-controlling values, as shown in Figure 6(c), then both inputs are critical, since changing either input will change the output value.

Figure 6. Critical and blocked input.

#### 3.2.4 Critical Path Graph

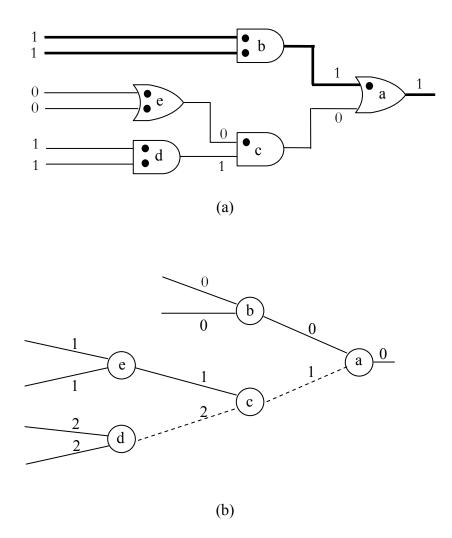

To simplify our analysis of critical path tracing, a *critical path graph* (CPG) [78] is used to describe the gate interconnection. In the graph, each gate is represented as a node while critical lines and blocked lines are shown as solid and dashed line respectively. The integer value on each line represents its blocked value. Figure 7 shows a simple circuit and its corresponding CPG. The dots indicate the sensitive inputs and the bold lines represent critical lines in Figure 7(a).

Figure 7. Example of critical path graph.

## 3.2.5 Self-Masking and Multiple Path Sensitization

If circuit does not contain any reconvergent fanout, critical path tracing is straightforward [72]. We illustrate critical path tracing in a fanout-free circuit, using the example in Figure 8. Critical path tracing in a fanout-free circuit is a simple tree traversal procedure that recursively marks every sensitive input of a gate with critical output from POs toward PIs. This uses the fact that if a gate output is critical, then its

sensitive inputs are critical.

Figure 8. Critical path tracing in a fanout-free circuit.

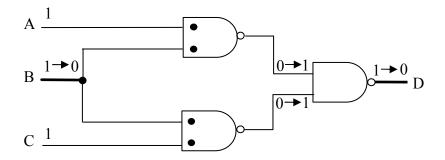

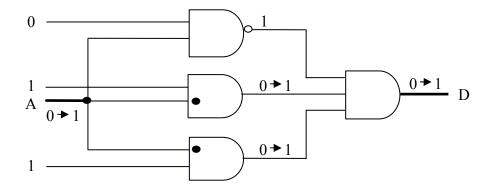

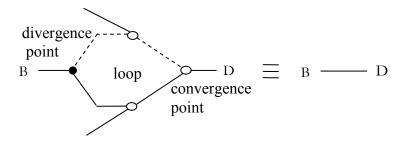

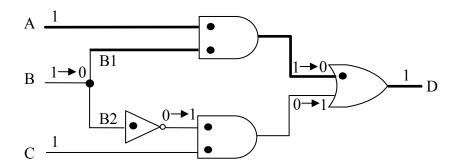

However, reconvergence occurs frequently in real digital circuits. Two problems caused by reconvergence are *self-masking* and *multiple path sensitization*.

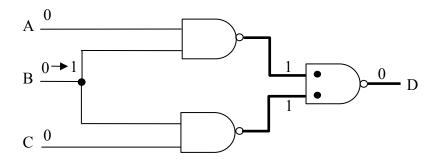

Self-masking is a phenomenon in which a fault effect propagates along two or more paths and reconverges with opposite parities at a gate, where the fault effects cancel out [72]. In Figure 9, we can see that the effect of the fault B SA0 propagating along two paths with opposite parities such that they cancel each other at reconvergence point D. Self-masking implies that a stem may be non-critical even though all of its fanouts are critical.

Figure 9. Example of self-masking [71].

Another problem caused by reconvergence is multiple path sensitization [71], which implies a stem may be critical even though all of its fanouts are non-critical. In Figure 10, although B1 and B2 are both non-critical, stem B is critical because the effect of fault B SA0 could be propagated to primary output D.

Figure 10. Example of multiple path sensitization.

## 3.3 Algorithm Flow of Improved Critical Path Tracing

Since the criticality of a stem cannot be directly deduced from the criticality of its fanouts, stem processing requires a great deal of analysis, and determining criticality of a stem takes up a major part of the computation time for critical path tracing [72][84][85].

In this section, the details of the fast critical path tracing algorithm will be described and the rules to determine stem criticality will be introduced.

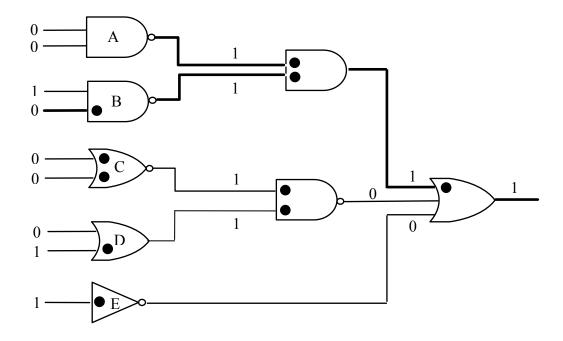

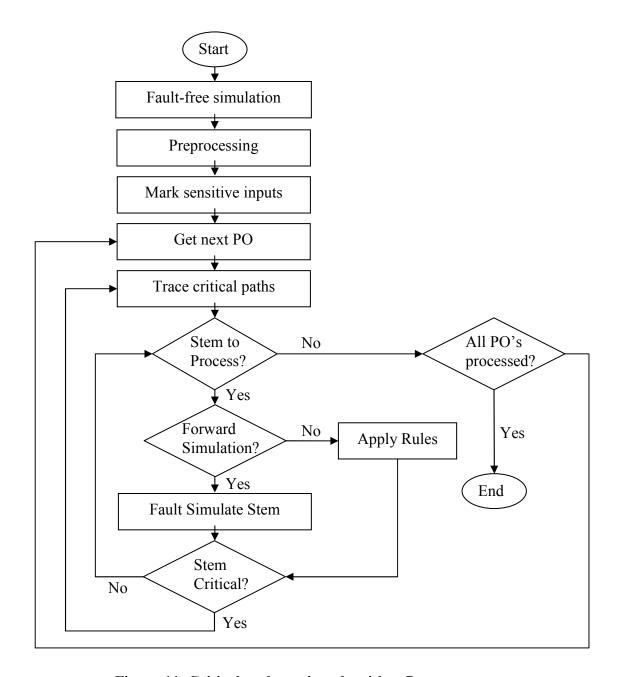

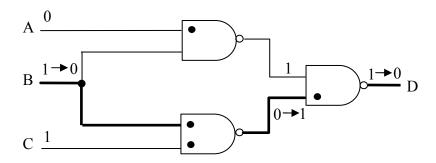

Figure 11 outlines the flow of the improved critical path tracing algorithm for a given test pattern. First, fault-free simulation is performed to determine the logic value for each line. Then the algorithm preprocesses the circuit to identify the logic cones feeding each primary output (PO). In each cone, sensitive inputs are marked according to the rules described in section 3.2.2. The algorithm then processes every cone starting at its PO. During the backtracing, there are two main operations on the inputs of the gate being evaluated. First, the sensitive input net has been directly marked as a critical line and inserted into the critical path if the gate output is critical and this input net is not a fanout of a stem. Second, if the input is a stem fanout, the stem is checked to see if its criticality has already been determined. If the stem is already known as critical, backtracing continues. If stem criticality is unknown, we must determine if it needs forward fault simulation to determine its criticality. If yes, fault simulation is performed between the stem and its convergence gates. The fault simulation stops as soon as the effect of a fault disappears. Otherwise, the algorithm checks whether all the information needed to compute stem criticality is available. If so, the stem analysis rules are applied to analyze the stem. The rules are described in the following section. Otherwise, the inputs in level n+1 of the circuit are processed, assuming the current level (rank) is n. The level of a net is computed in the standard fashion: a primary input is assigned level 0, and the level of a gate output is  $i_{max}+1$  where  $i_{max}$  is the highest level among the levels of the gate inputs. Thus, no stem is analyzed until all of its fanout branches (FOB) have been considered.

This process repeats until all inputs in the cone have been analyzed.

Figure 11. Critical path tracing algorithm flow.

#### 3.4 Stem Analysis

As discussed above, stem analysis is the major part of the critical path tracing algorithm. An efficient stem analysis strategy will significantly speed up the entire process. Before describing the details of the stem analysis, several important definitions are presented.

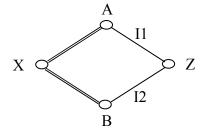

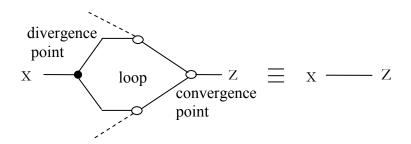

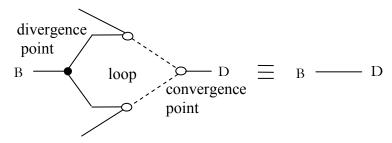

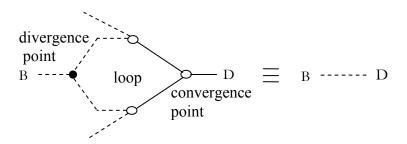

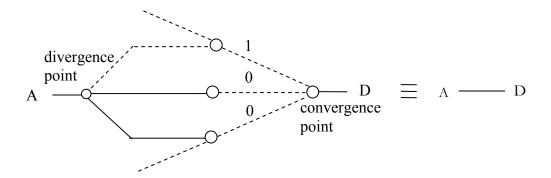

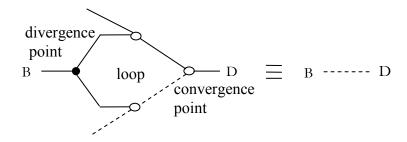

#### 1. Convergence Point and Divergence Point

If the fanouts of gate A reconverge at gate B, gate B is called the *convergence point* of gate A. Gate A is called a *divergence point*. A divergence point is just a stem.

### 2. Loop

The term *loop* is first defined in [78]. A reconvergent fanout not containing another reconvergent fanout is called a loop. A loop has only one divergence point and one convergence point.

A loop can either be replaced by a critical line or a blocked line in a critical path graph according to the following rules. The rules consider all common logic gate types except XOR and XNOR with more than 2 inputs because they rarely appear in circuits. The algorithm can be readily extended to handle multiple input XOR/XNOR gates, or such gates can be readily decomposed into two-input gates.

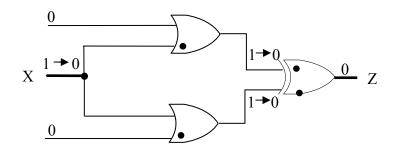

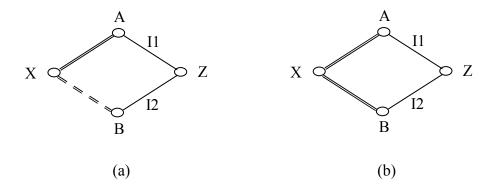

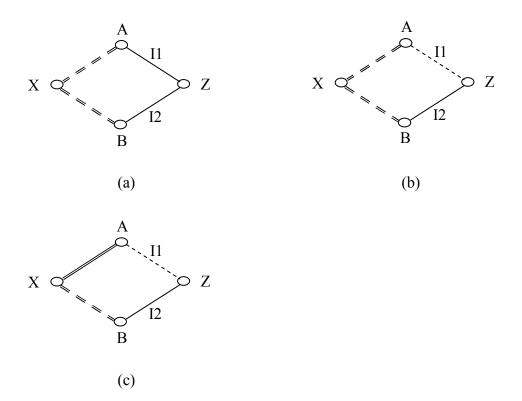

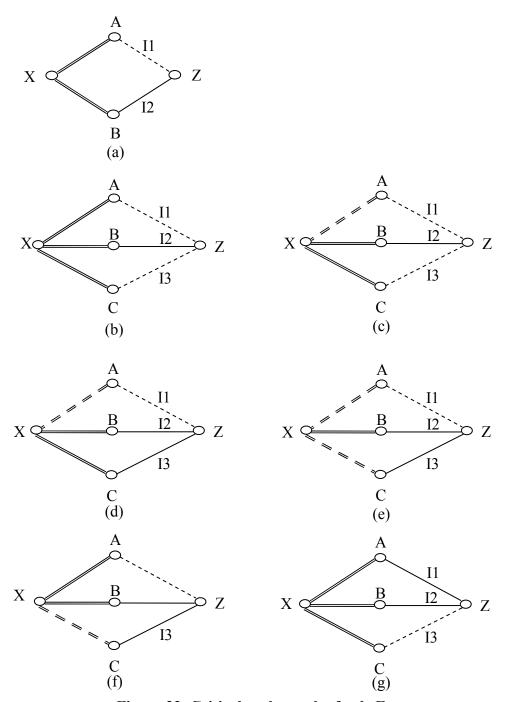

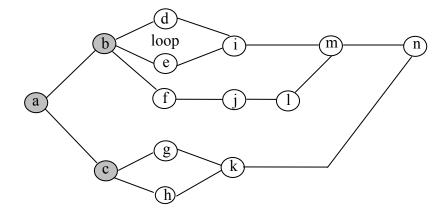

#### 3.4.1 Rule A1

Rule A1 is stated as follows: if the convergence point is an XOR/XNOR gate and all paths between convergence and divergence point are continuous paths, this loop can be replaced by a blocked line between convergence and divergence point. Figure 12 shows an application of rule A1. Since the fault effect at X cannot be propagated to Z, the loop

is equivalent to a blocked line between X and Z. Figure 13 shows the corresponding critical path graph of the circuit.

Figure 12. Example of rule A1 application.

Figure 13. Corresponding critical path graph of A1 application.

To prove rule A1, Figure 14 shows the critical path graph that summarizes all the cases covered by rule A1. In this graph, double solid lines represent a critical path, double dash lines represent a blocked path, on which there is at least one blocked line.

Figure 14. Critical path graph for rule A1 cases.

The justification of rule A1 is as follows: Since the paths between X and A and between X and B are both critical paths, the change at X will change both I1 and I2 which are input lines of Z. If both inputs of XOR/XNOR gates change, the output will not change. Therefore, the fault effect at X cannot be propagated to Z, and the loop between X and Z is replaced by a blocked line.

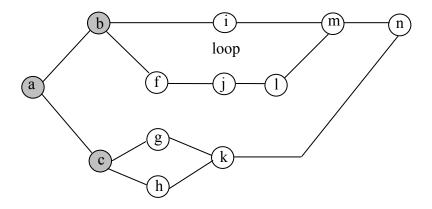

#### 3.4.2 Rule A2

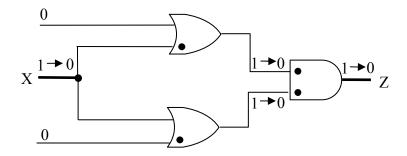

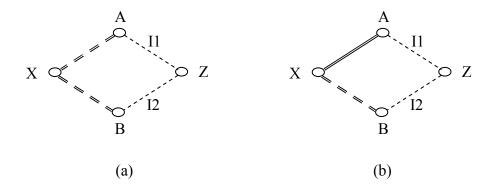

Rule A2 is stated as follows: a loop containing no blocked lines at a convergence point and at least one continuous path of critical lines between convergence point and divergence point, except if it is covered by rule A1, can be replaced by a critical line.

Figure 15. Example of rule A2 application.

Figure 15 shows an application of rule A2. Since the effect of a fault at divergence

point X can be propagated to convergence point Z, the loop is equivalent to a critical line between X and Z. Figure 16 shows the corresponding critical path graph of the circuit.

Figure 16. Corresponding critical path graph of rule A2 application.

To prove rule A2, Figure 17 shows the critical path graph that summarizes all the cases covered by rule A2.

Figure 17. Critical path graph for rule A2 cases.

The justification of rule A2 for case 1, which is summarized by Figure 17(a), is as follows:

If Z is a AND/NAND gate, then the inputs I1 and I2 must have logic value (1, 1). So the output of Z is 1 for an AND gate, 0 for a NAND gate, which is represented by O(Z) = 0/1. If the output value of X changes, I1 will change while I2 will remain the same because the path between X and A is critical and the path between X and B is blocked.

The new value of (I1', I2') is (1, 0), which means O'(Z) = 1/0. It has been shown that the fault effect at X could be propagated to Z, so rule A2 holds in this case.

If Z is an OR/NOR gate, then the inputs I1 and I2 must have logic value (0, 0). So the output of Z is 0 for an OR gate, 1 for a NOR gate, which is represented by O(Z) = 0/1. If the output value of X changes, I1 will change while I2 will remain the same. The new value of (I1', I2') is (1, 0), which means O'(Z) = 1/0. It has been shown that the fault effect at X could be propagated to Z, so rule A2 holds in this case.

If Z is a XOR/XNOR gate, then the output changes as long as one of the inputs changes. If the output of X changes, I1 changes so that the output of Z changes. Rule A2 also holds in this case.

For case 2, which is summarized by Figure 17(b), gate Z cannot be a XOR or XNOR gate, since that case is covered by rule A1. A similar justification can be applied to prove rule A2 also holds for case 2.

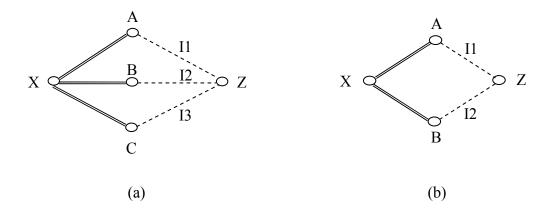

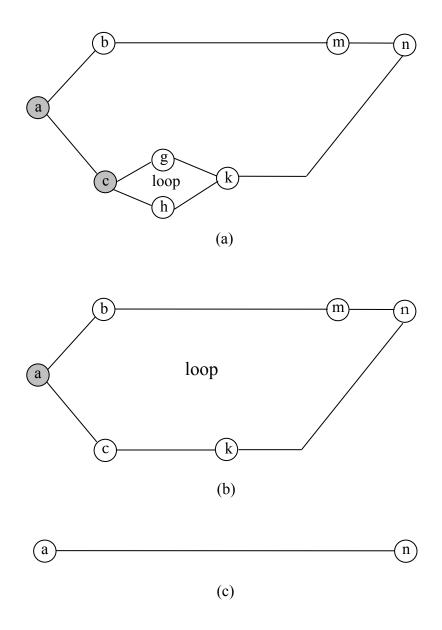

#### 3.4.3 Rule B

Rule B is stated as follows: a loop with all lines blocked at the convergence point and no other blocked lines is replaced by a critical line, if all inputs at the convergence point have dominant logic values. Otherwise, the loop is replaced by a blocked line. Figure 18 show an application of rule B. As we can see, the critical path is a discontinuous path.

Figure 18. Example of rule B application.

Figure 19 shows the corresponding critical path graph of the example circuit.

Figure 19. Corresponding critical path graph of rule B application.

Figure 20 summarizes the cases covered by rule B. Here we only show the cases with convergence points that have two or three inputs.

Figure 20. Critical path graph for rule B cases.

Here we only provide the proof for the cases with convergence points that have three inputs. A similar proof could be applied to justify other cases.

If Z is an AND/NAND gate, (I1, I2, I3) must be (0, 0, 0) or (0, 0, 1). First, we consider the case with (I1, I2, I3) = (0, 0, 0), in which all inputs have dominant logic value; then the output of Z is 0/1. If X changes, the new value set (I1', I2', I3') = (1, 1, 1). Therefore, the new output of Z is 1/0. Rule B holds at this point. Second, we consider the case with (I1, I2, I3) = (0, 0, 1); then the output of Z is 0/1. If X changes, the new value set (I1', I2', I3') = (1, 1, 0). The output of Z is still 0/1. Rule B still holds for this case.

If Z is an OR/NOR gate, (I1, I2, I3) must be (1, 1, 1) or (1, 1, 0). First, we consider the case with (I1, I2, I3) = (1, 1, 1), in which all inputs have dominant logic values; then the output of Z is 1/0. If X changes, the new value set (I1', I2', I3') = (0, 0, 0). Therefore, the new output of Z is 0/1. Rule B holds at this point. Second, we consider the case with (I1, I2, I3) = (1, 1, 0); then the output of Z is 1/0. If X changes, the new value set (I1', I2', I3') = (0, 0, 1). The output of Z is still 1/0. Rule B still holds for this case.

The convergence point cannot be an XOR/XNOR gate because the inputs of XOR/XNOR gates are always critical lines.

## 3.4.4 Rule C

Rule C is stated as follows: a loop with at least one blocked line on each path between divergence and convergence points, and at least one critical line at the convergence point, can be replaced by a blocked line between convergence and divergence points.

Figure 21. Example of rule C application.

Figure 21 shows an application of rule C. Figure 22 shows the corresponding critical path graph of the example circuit.

Figure 22. Corresponding critical path graph of rule C application.