## Contributions to the efficiency and safety of stand-alone DC microgrids

Sergio Ignacio Serna Garcés

Universidad Nacional de Colombia Facultad de Ingeniería y Arquitectura Departamento de Eléctrica, Electrónica y Computación Manizales, Colombia 2018

## Contributions to the efficiency and safety of stand-alone DC microgrids

Sergio Ignacio Serna Garcés

Thesis to obtain the degree of: Doctor of Engineering - Automatic Engineering

> Advisor Prof. Carlos Andrés Ramos Paja , Ph.D.

> > Research line: Renewable energies Group: GAUNAL

Universidad Nacional de Colombia Facultad de Ingeniería y Arquitectura Departamento de Eléctrica, Electrónica y Computación Manizales, Colombia 2018

### Abstract

Currently, the distributed generation based on renewable energy sources is mainly DC. Those DC systems are use diverse applications such as airplanes, automobiles, ships, spaceships, computers, servers, telecommunications stations, among others. This thesis considers an isolated DC microgrid architecture composed of a renewable source, an energy storage system, and a DC load. The thesis is aimed at identifying and solving efficiency and safety problems at the source, the DC bus, and the load. During the development of this Thesis six contributions to the state-of-the-art of DC microgrids were obtained. The first contribution is the mathematical model of a distributed maximum power point platform formed by multiple module-converter sets connected in series, which can be implemented in different programming languages and deployed on multiple platforms to evaluate optimization strategies. The second contribution is a vectorial MPPT algorithm for a distributed photovoltaic system, based in the perturb & observe algorithm. This algorithm provides a satisfactory trade-off between implementation cost and energy production since it uses a single I/V sensor. The third contribution is a reconfiguration algorithm that optimizes the electrical connections of a commercial photovoltaic array, which enables to maximize the energy extraction under arbitrary shading conditions. The fourth and fifth contributions are two control strategies, based on sliding-modes, designed for a charger/discharger DC/DC converter. Those solutions enable to regulate the voltage on the DC-bus of the microgrid to improve the microgrid safety. One of the strategies considers the current of the DC-bus into the sliding surface, which gives a better performance in terms of overshoot and settling time of the DC bus voltage. The final contribution concerns a control strategy, also based on sliding modes, to regulate a point-of-load DC/DC converter. Such a contribution enables to improve the conversion efficiency, and at the same time, to improve the load safety by reducing the current and voltage ripples delivered by the converter. Finally, those contributions improve the electrical efficiency and operational safety of DC microgrids based on renewable sources.

The results obtained in this thesis were published in five journals articles and three communications to conferences. From those, three articles were published in Q1 journals, one article was published in Q3 journal, and another one was published in a Colombian journal.

Keywords: DC-microgrid; sliding-mode; photovoltaic reconfigurator; distributed MPPT; vectorial MPPT; interleaving converter; POL; bus-DC regulation; bidirectional converter; charger/discharger; ripple; efficiency.

## Contribuciones a la eficiencia y seguridad de operación en microrredes DC aisladas

### Sergio Ignacio Serna Garcés

Tesis para obtener el grado de: Doctor en ingeniería - Ingeniería Automática

> Director Prof. Carlos Andrés Ramos Paja , Ph.D.

> > Línea de investigación: Energias Renovables Grupo: GAUNAL

Universidad Nacional de Colombia Facultad de Ingeniería y Arquitectura Departamento de Eléctrica, Electrónica y Computación Manizales, Colombia 2018

### Resumen

Actualmente, la generación distribuida basada en fuentes de energía renovable es principalmente DC. Estos sistemas DC son utilizados en aviones, automóviles, barcos, naves espaciales, computadores, servidores, estaciones de telecomunicaciones, etc. Esta Tesis considera una arquitectura de microrred DC aislada compuesta por una fuente renovable, un sistema de almacenamiento de energía y una carga DC. La tesis tiene como objetivo identificar y solucionar problemas de eficiencia y seguridad de operación en la fuente, en el bus DC y en la carga. Durante el desarrollo de esta Tesis se obtuvieron seis aportes al estado del arte en microrredes DC. La primera contribución es el modelo matemático de una plataforma de seguimiento del punto de máxima potencia formada por múltiples conjuntos panel-convertidor conectados en serie, el cual se puede implementar en diferentes lenguajes de programación y desplegar en múltiples plataformas para evaluar estrategias de optimización. La segunda contribución es un algoritmo MPPT vectorial para un sistema fotovoltaico distribuido, basado en el algoritmo de perturbar y observar. Este algoritmo proporciona una compensación satisfactoria entre el costo de implementación y la producción de energía, ya que utiliza un solo sensor de I/V. La tercera contribución es un algoritmo de reconfiguración que optimiza las conexiones eléctrica de un arreglo de paneles fotovoltaicos comercial, el cual permite maximizar la extracción de energía bajo condiciones arbitrarias de sombreado. La cuarta y quinta contribución son dos estrategias de control, basadas en modos deslizantes, diseñadas para un convertidor DC/DC cargador/descargador. Estas soluciones permiten regular el voltaje del bus DC de la microrred para mejorar la seguridad de su operación. Una de las estrategias considera la corriente del bus DC en la superficie deslizante, lo cual da un mejor desempeño en cuanto al sobreimpulso y el tiempo de establecimiento del voltaje del bus DC. La contribución final es una estrategia de control, también basada en modos deslizantes, para regular un convertidor DC/DC point-of-load. Esta contribución permite mejorar la eficiencia de la conversión y al mismo tiempo mejorar la seguridad operativa de la carga reduciendo el rizado de voltaje y corriente entregado por el convertidor. Finalmente, estas contribuciones mejoran la eficiencia eléctrica y la seguridad operativa de microrredes DC basadas en fuentes de energía renovable.

Los resultados obtenidos en esta Tesis fueron publicados en cinco artículo de revista y tres ponencias en conferencias. De estos, tres artículos fueron publicados en revistas clasificadas en Q1, un artículo fue publicado en una revista con clasificación Q3 y otro en una revista colombiana.

Palabras clave: microrred DC; modos deslizantes; reconfiguradores fotovoltaicos; MPPT distribuido; MPPT vectorial; convertidores entrelazados; POL; regulación bus DC; convertidor bidireccional; cargador/descargador; rizado; eficiencia.

## Preface

This thesis reports the results of my PhD studies at the Departamento de Ingeniería Eléctrica, Electrónica y Computación, Facultad de Ingeniería y Arquitectura, Universidad Nacional de Colombia. This work was carried out between Semester 2012-2 to Semester 2018-1, and it was supported by the Instituto Tecnológico Metropolitano. The developing of this thesis was supported by several research projects:

- Diseño, análisis y evaluación de estrategias de control para optimización de sistemas de generación basados en paneles fotovoltaicos (ITM code P10-102): Instituto Tecnológico Metropolitano and Universidad Nacional de Colombia.

- Maximización de extracción de energía en aerogeneradores para cogeneración urbana en el Valle de Aburrá (ITM code P10233): Instituto Tecnológico Metropolitano and Universidad Nacional de Colombia.

- Caracterización de convertidores conmutados DC/DC para aplicaciones industriales (ITM code P14215): Instituto Tecnológico Metropolitano and Universidad Nacional de Colombia.

- Desarrollo de un algoritmo MPPT con único sensor voltaje/corriente para maximización de potencia en la carga de sistemas fotovoltaico (ITM code P14220): Instituto Tecnológico Metropolitano and Universidad Nacional de Colombia.

- Diseño y control de microrredes basadas en fuentes renovables para el suministro de energía eléctrica a bajo costo en zonas no interconectadas de Colombia (Colciencias code 1118-669-46197): Universidad Nacional de Colombia, Universidad del Valle, Universidad Industrial de Santander and Instituto Tecnológico Metropolitano.

The results of this thesis were published in five articles and three conference papers (see appendix A). Four articles were published in international journals and another in a colombian journal. Two papers were published in international conferences and another in a colombian conference. This document was built thinking in making it easier for the reader to understand the overall work and to identify the improvements in the state of the art. Moreover, the eight publications significantly improve the diffusion of the thesis results.

The thesis follows common publishing guidelines given by international journals. Grayscale figures have been used to illustrate the simulation results. Color figures have been used only when strictly necessary, such as is the case of simultaneous plots of a high number of signals. Similarly, the bibliographical citations have been numbered in order of appearance, as have the equations, figures and tables. Both roman and italic fonts appear in the text, the latter being used to highlight important issues, differentiate nouns and mark non-English words.

Two experimental processes were developed in this thesis, one at the Universitat Rovira i Virgili - Spain, and another at Instituto Tecnológico Metropolitano - Medellín. In this last Institution also was developed the Hardware-In-the-Loop simulations. Likewise, simulations of the systems and power electronics circuits have been carried out by using Matlab/Simulink<sup>®</sup> and PSIM<sup>®</sup> software.

Finally, I want to thank the huge support of my Director, Professor Carlos Andrés Ramos Paja, who with his clarity on the topic was the best leader that I could have in the development of this thesis. Truly, I am very grateful to him.

Likewise, I want to thank to all the people who, in one way or another, helped me in this thesis, especially to Professor Daniel González and Master student Juan Pablo Villegas Ceballos.

This work was supported by the Universidad Nacional de Colombia and the Instituto Tecnológico Metropolitano under the project UNAL-ITM-39823/P17211.

## Contents

| Intro | oductio                                                                                         | n                                                                                                                                                                                                                                                                                   | 2                                                                                |

|-------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1.1.  | Power                                                                                           | extraction of the PV generator                                                                                                                                                                                                                                                      | 3                                                                                |

| 1.2.  | DC bu                                                                                           | s regulation and storage management system                                                                                                                                                                                                                                          | 7                                                                                |

| 1.3.  | Efficie                                                                                         | nt delivery of quality electric power to the load                                                                                                                                                                                                                                   | 9                                                                                |

| Imp   | roveme                                                                                          | nts in the power extraction of photovoltaic source                                                                                                                                                                                                                                  | 13                                                                               |

| 2.1.  | Mathe                                                                                           | matical model of distributed photovoltaic systems                                                                                                                                                                                                                                   | 14                                                                               |

|       | 2.1.1.                                                                                          | Model description                                                                                                                                                                                                                                                                   | 15                                                                               |

|       |                                                                                                 | 2.1.1.1. Mathematical model of two modules in series                                                                                                                                                                                                                                | 15                                                                               |

|       |                                                                                                 | 2.1.1.2. Model extension to $n > 2$ modules in series $\ldots \ldots \ldots$                                                                                                                                                                                                        | 17                                                                               |

|       |                                                                                                 | 2.1.1.3. Model parameterization process                                                                                                                                                                                                                                             | 20                                                                               |

|       | 2.1.2.                                                                                          | Model validation and application example                                                                                                                                                                                                                                            | 22                                                                               |

|       |                                                                                                 | 2.1.2.1. Validation of the mathematical model with three modules in                                                                                                                                                                                                                 |                                                                                  |

|       |                                                                                                 | series                                                                                                                                                                                                                                                                              | 22                                                                               |

|       |                                                                                                 | 2.1.2.2. Application example: simulation of a DMPPT system with                                                                                                                                                                                                                     |                                                                                  |

|       |                                                                                                 | 10 modules in series $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                 | 27                                                                               |

| 2.2.  | Vector                                                                                          | ial MPPT algorithm for distributed photovoltaic system                                                                                                                                                                                                                              | 29                                                                               |

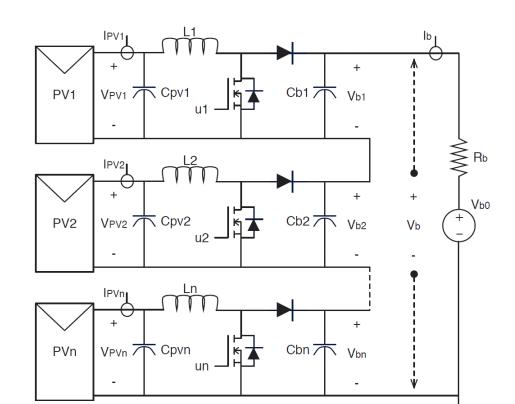

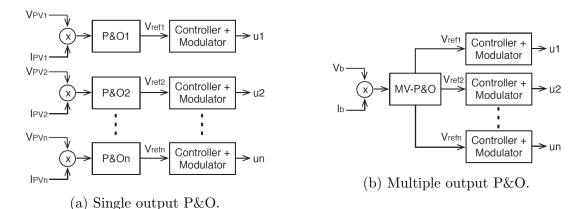

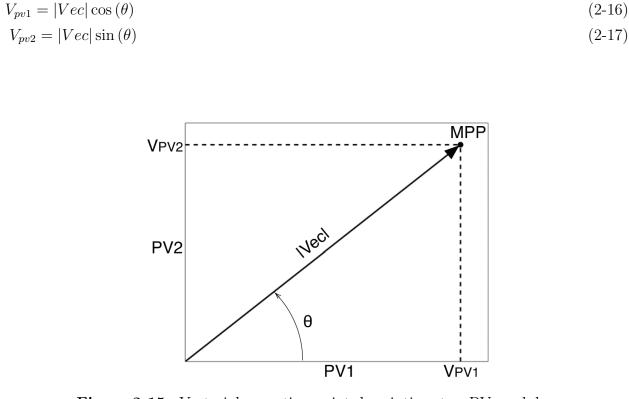

|       | 2.2.1.                                                                                          | PV system architecture for DMPPT                                                                                                                                                                                                                                                    | 30                                                                               |

|       | 2.2.2.                                                                                          | The vectorial MPPT algorithm                                                                                                                                                                                                                                                        | 31                                                                               |

|       | 2.2.3.                                                                                          | Simulation results                                                                                                                                                                                                                                                                  | 35                                                                               |

| 2.3.  | Photo                                                                                           | voltaic array reconfiguration                                                                                                                                                                                                                                                       | 37                                                                               |

|       | 2.3.1.                                                                                          | Reconfiguration of PV systems                                                                                                                                                                                                                                                       | 38                                                                               |

|       | 2.3.2.                                                                                          | Reconfiguration of panels based on experimental data                                                                                                                                                                                                                                | 40                                                                               |

|       |                                                                                                 | 2.3.2.1. Structure of the reconfiguration system                                                                                                                                                                                                                                    | 41                                                                               |

|       |                                                                                                 | 2.3.2.2. Evaluation of possible array configurations                                                                                                                                                                                                                                | 44                                                                               |

|       |                                                                                                 | 2.3.2.3. Application example based on commercial devices                                                                                                                                                                                                                            | 46                                                                               |

|       | 2.3.3.                                                                                          | Simulation platform implementation using commercial devices                                                                                                                                                                                                                         | 48                                                                               |

|       | 2.3.4.                                                                                          | Simulation results based on experimental data                                                                                                                                                                                                                                       | 51                                                                               |

|       |                                                                                                 | 2.3.4.1. Simulated shading conditions                                                                                                                                                                                                                                               | 51                                                                               |

|       |                                                                                                 | 2.3.4.2. Sampling time and time delay of the sweep device and switches                                                                                                                                                                                                              | 52                                                                               |

|       |                                                                                                 | 2.3.4.3. Dynamic simulation of the reconfiguration system                                                                                                                                                                                                                           | 55                                                                               |

|       |                                                                                                 | 2.3.4.4. Calculation burden of the reconfiguration algorithm                                                                                                                                                                                                                        | 57                                                                               |

|       |                                                                                                 | 2.3.4.5. Tests without accounting for array reconfiguration                                                                                                                                                                                                                         | 58                                                                               |

|       | <ul> <li>1.1.</li> <li>1.2.</li> <li>1.3.</li> <li>Implementation 2.1.</li> <li>2.2.</li> </ul> | <ul> <li>1.1. Power</li> <li>1.2. DC but</li> <li>1.3. Efficient</li> <li>Improveme</li> <li>2.1. Mather</li> <li>2.1.1.</li> <li>2.1.2.</li> <li>2.1.2.</li> <li>2.1.2.</li> <li>2.2.1.</li> <li>2.2.2.</li> <li>2.2.3.</li> <li>2.3.1.</li> <li>2.3.2.</li> <li>2.3.3.</li> </ul> | <ul> <li>1.3. Efficient delivery of quality electric power to the load</li></ul> |

| VI    | τ. |

|-------|----|

| - A I | v  |

|       |    |

|      |         | gulation                                                                              |

|------|---------|---------------------------------------------------------------------------------------|

| 3.1. |         | g-mode control of a charger/discharger DC/DC converter for DC-bus                     |

|      |         | tion in renewable power systems                                                       |

|      | 3.1.1.  | Sliding mode controller analysis                                                      |

|      |         | 3.1.1.1. Transversality condition                                                     |

|      |         | 3.1.1.2. Reachability conditions                                                      |

|      |         | 3.1.1.3. Equivalent control condition                                                 |

|      |         | 3.1.1.4. Sliding mode dynamics                                                        |

|      | 3.1.2.  | Design of the sliding mode dynamic behavior                                           |

|      |         | 3.1.2.1. Underdamped response                                                         |

|      |         | 3.1.2.2. Critically damped response                                                   |

|      | 3.1.3.  | Controller design and operation                                                       |

|      |         | 3.1.3.1. Normalized equations for the sliding mode controller                         |

|      |         | $3.1.3.1.1.$ Constraint equations $\ldots$                                            |

|      |         | 3.1.3.1.2. Underdamped behavior equations                                             |

|      |         | 3.1.3.1.3. Critically damped behavior equations                                       |

|      |         | 3.1.3.2. Switching frequency                                                          |

|      |         | 3.1.3.3. Summary of the design procedure and operation                                |

|      | 3.1.4.  | Simulation Results                                                                    |

|      | 3.1.5.  | Experimental validation                                                               |

| 3.2. | Contro  | ol of a charger/discharger DC/DC converter with improved disturbance                  |

|      | rejecti | on for bus regulation                                                                 |

|      | 3.2.1.  | Improved sliding mode controller                                                      |

|      |         | 3.2.1.1. Converter model and sliding function expressions $\ldots$ $\ldots$           |

|      |         | 3.2.1.2. Transversality condition                                                     |

|      |         | 3.2.1.3. Reachability conditions                                                      |

|      |         | 3.2.1.4. Equivalent control $\ldots$                                                  |

|      |         | 3.2.1.5. Summary                                                                      |

|      | 3.2.2.  | Design of the sliding mode dynamics                                                   |

|      |         | 3.2.2.1. Selection of the type of dynamic response                                    |

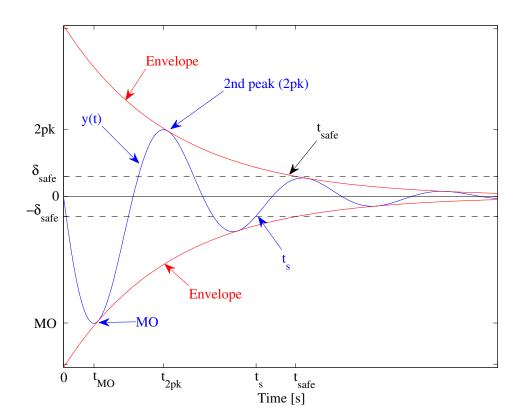

|      |         | 3.2.2.2. Design of the maximum overshoot                                              |

|      |         | 3.2.2.3. Design of the settling time                                                  |

|      |         | 3.2.2.4. Calculation of parameters $k_p$ and $k_i \ldots \ldots \ldots \ldots \ldots$ |

|      |         | 3.2.2.5. Summary                                                                      |

|      | 3.2.3.  | Implementation and operation analysis                                                 |

|      |         | 3.2.3.1. Control law and switching circuit                                            |

|      |         | 3.2.3.2. Synthesis of the sliding function                                            |

|      |         | 3.2.3.3. Speed limitation under perturbations                                         |

|    | 3.2.4. Design example and simulation results                                  |    | 110 |

|----|-------------------------------------------------------------------------------|----|-----|

|    | 3.2.5. Experimental validation                                                |    | 116 |

|    | 3.3. Conclusions                                                              |    | 118 |

| 4. | . Point-of-load converter with reduced current ripple and increased efficiend | сy | 121 |

|    | 4.1. POL regulator based on a post-filter                                     |    | 121 |

|    | 4.1.1. Post-filter based on parallel buck converters                          |    | 122 |

|    | 4.1.2. POL converter                                                          |    | 126 |

|    | 4.2. Sliding mode current control                                             |    | 129 |

|    | 4.3. Application example                                                      |    |     |

|    | 4.4. Conclusions                                                              |    |     |

| 5. | Conclusions                                                                   |    | 140 |

| Α. | . Appendix: Publications                                                      |    | 144 |

|    | A.1. Journal articles                                                         |    | 144 |

|    | A.2. Conference papers                                                        |    | 145 |

|    | Bibliography                                                                  |    | 146 |

## **List of Figures**

| <b>1-1</b> . | Stand-alone power system based on renewable energy sources                                                                          | 3  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>1-2</b> . | Shading profiles affecting PV systems.                                                                                              | 4  |

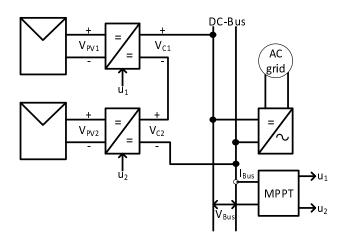

| <b>1-3</b> . | Centralized and distributed control of a photovoltaic system                                                                        | 5  |

| <b>1-4</b> . | PV array with multi-variable MPPT                                                                                                   | 6  |

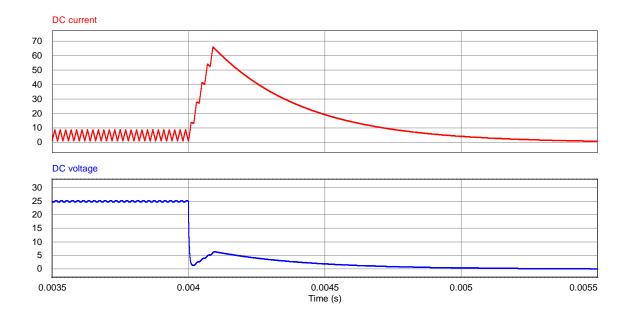

| <b>1-5</b> . | Current waveform when the device is powered up                                                                                      | 10 |

| <b>1-6</b> . | Current and voltage characteristics during a DC short-circuit fault                                                                 | 11 |

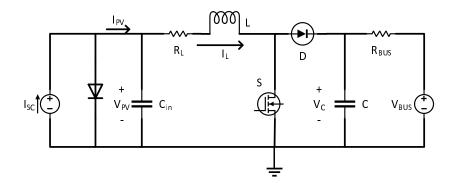

|              | Boost converter scheme.                                                                                                             | 15 |

| <b>2-2</b> . | Connection diagram of two modules in series with MPPT                                                                               | 16 |

|              | Block diagram of the model of n modules in series.                                                                                  | 18 |

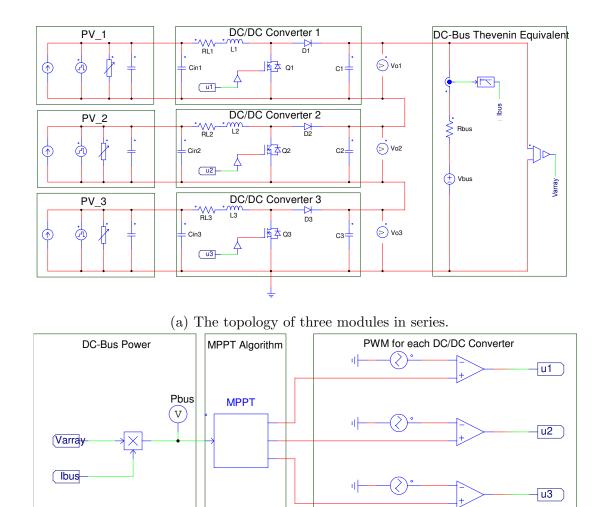

| <b>2-4</b> . | Simulation scheme in $PSIM^{\mathbb{R}}$ of three modules in series. $\ldots \ldots \ldots \ldots$                                  | 23 |

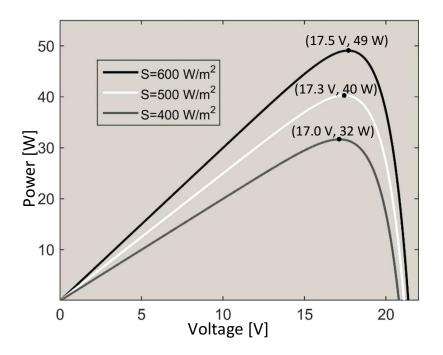

| <b>2-5</b> . | Simulated power profile of the BP 585 module based on (2-1)                                                                         | 24 |

| <b>2-6</b> . | Flowchart of the MPPT MOPOC algorithm.                                                                                              | 25 |

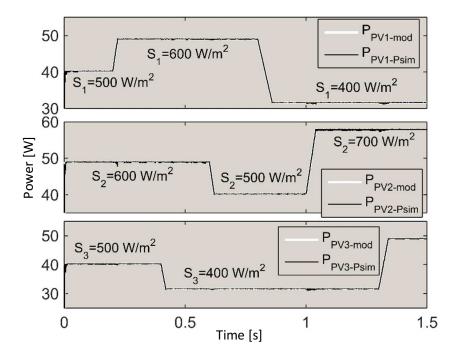

| <b>2-7</b> . | Simulation of power generated by the system with three modules                                                                      | 26 |

|              | Simulation of current generated by the system with three modules                                                                    | 26 |

| <b>2-9</b> . | Simulation of condenser voltage for the system with three modules                                                                   | 27 |

| 2-10         | Simulation of power generated by the system with 10 modules                                                                         | 28 |

| 2-11         | Simulation of current generated by the system with 10 modules                                                                       | 28 |

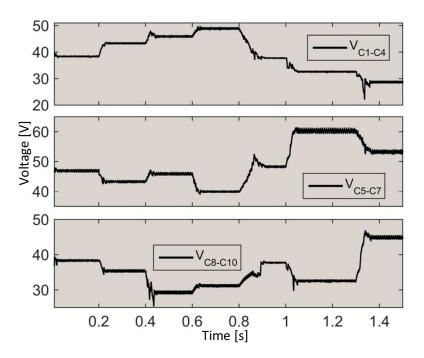

| 2-12         | Simulation of condenser voltage for the system with 10 modules                                                                      | 29 |

| 2-13         | Granular PV modules control architecture: power processing stages                                                                   | 31 |

| 2-14         | Granular PV modules control architecture: control strategy.                                                                         | 31 |

| 2-15         | Vectorial operating point description: two PV modules                                                                               | 32 |

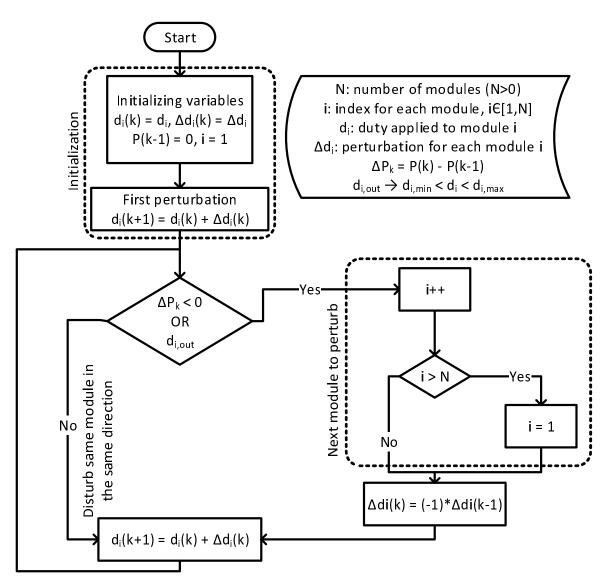

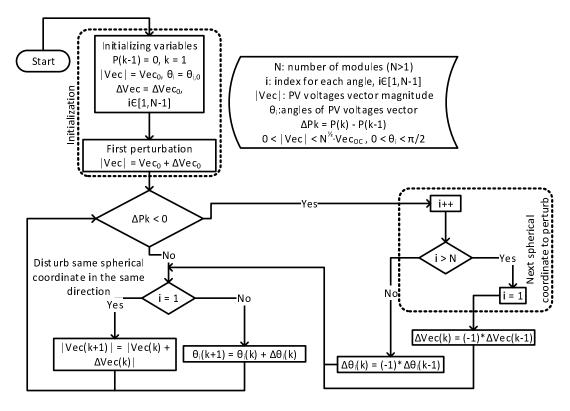

| 2-16         | 5. Flowchart of the MPPT MOPOV algorithm                                                                                            | 33 |

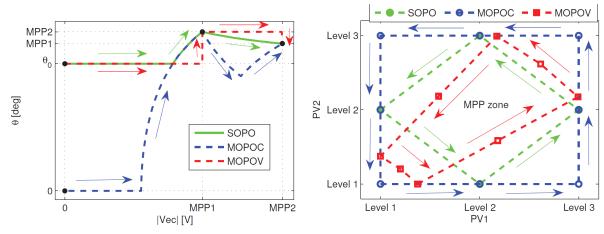

| 2 - 17       | MPPT trajectories and steady state profiles for single-output and multi-                                                            |    |

|              | output algorithms.                                                                                                                  | 34 |

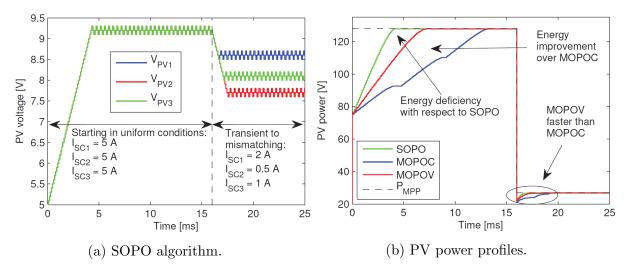

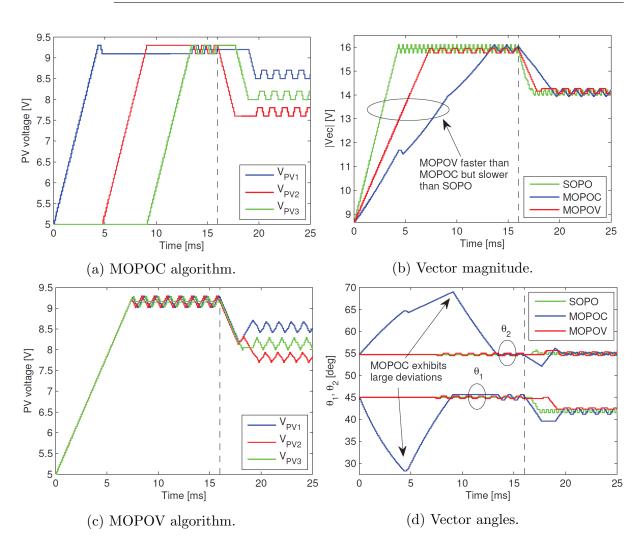

| 2-18         | Simulation of a 3 PV module system: SOPO algorithm and PV power profiles.                                                           | 35 |

| 2-19         | Simulation of a 3 PV module system                                                                                                  | 36 |

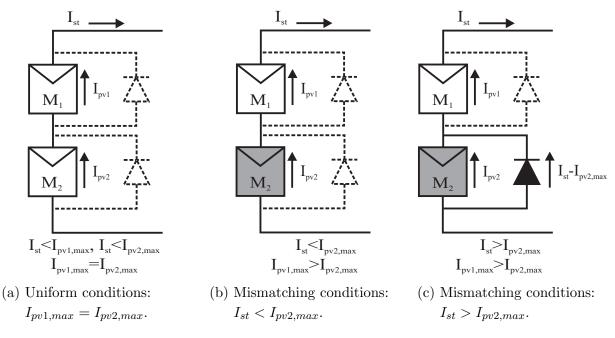

| 2-20         | Series-connected PV modules with bypass diodes under uniform and mismat-                                                            |    |

|              | ching conditions.                                                                                                                   | 38 |

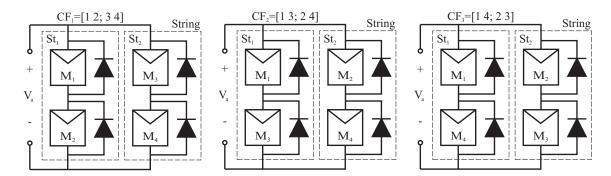

| 2-21         | .Possible configurations of a series-parallel (SP) array with two strings of two                                                    |    |

|              | modules each                                                                                                                        | 39 |

| 2-22         | $A_{1}(\mathbf{a})$ : I-V curves of $M_{1}$ , $M_{2}$ , $M_{3}$ and $M_{4}$ . (b): P-V curves of $CF_{1}$ , $CF_{2}$ and $CF_{3}$ . | 40 |

| 2-23         | Proposed reconfiguration system                                                                                                     | 41 |

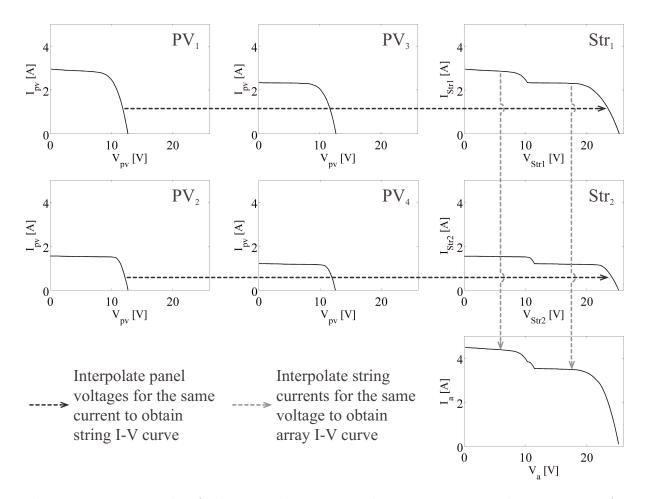

| 2-24.Example of the interpolation procedures to construct the I-V curve of one                          |     |

|---------------------------------------------------------------------------------------------------------|-----|

| configuration for an SP array with two strings of two modules each. $\ldots$ $\ldots$                   | 45  |

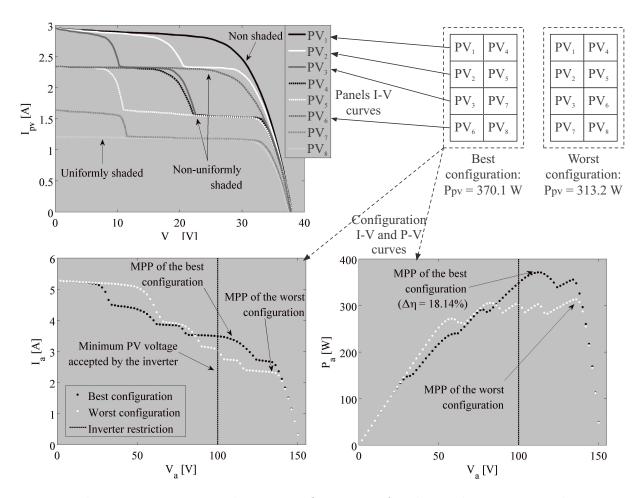

| <b>2-25</b> .Best and worst configurations for the application example.                                 | 47  |

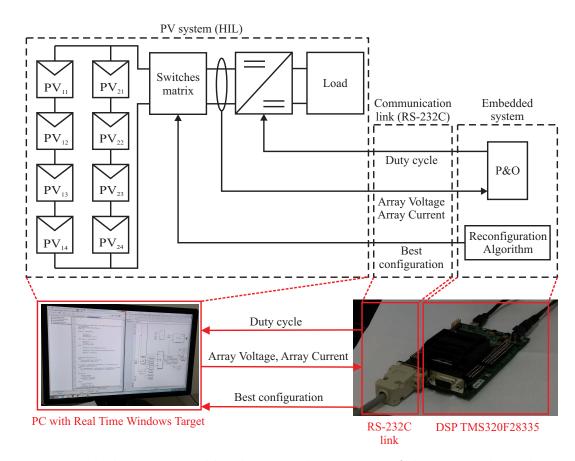

| 2-26.Block diagram and hardware implementation of the proposed simulation plat-                         |     |

| form                                                                                                    | 49  |

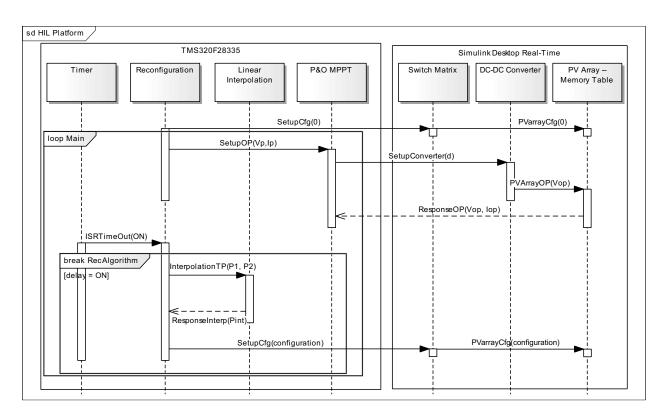

| 2-27. Sequence diagram of the simulation platform.                                                      | 50  |

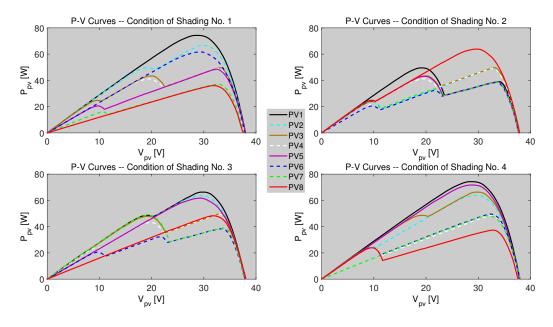

| <b>2-28</b> .P-V curves of the PV panels for the shading conditions                                     | 52  |

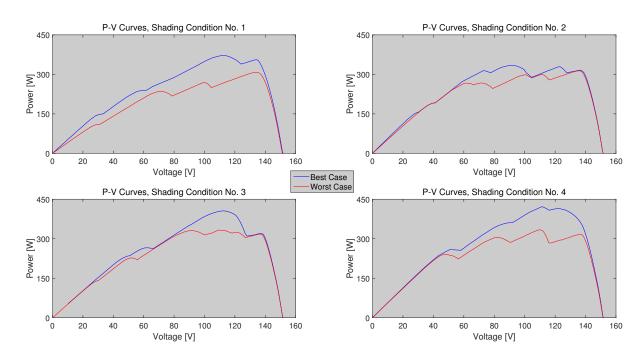

| 2-29. Array P-V curves for best and worst configurations for each shading condition.                    | 53  |

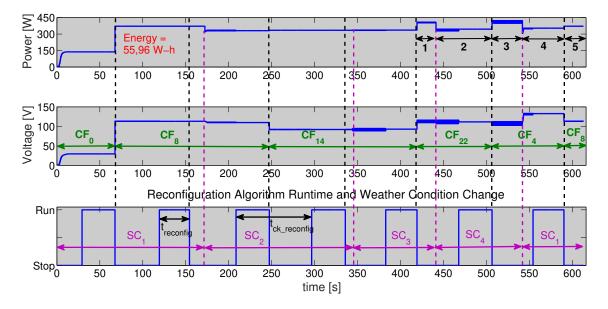

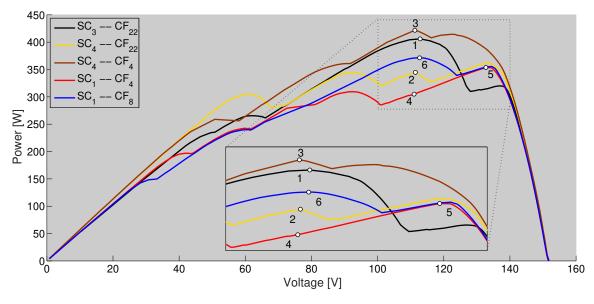

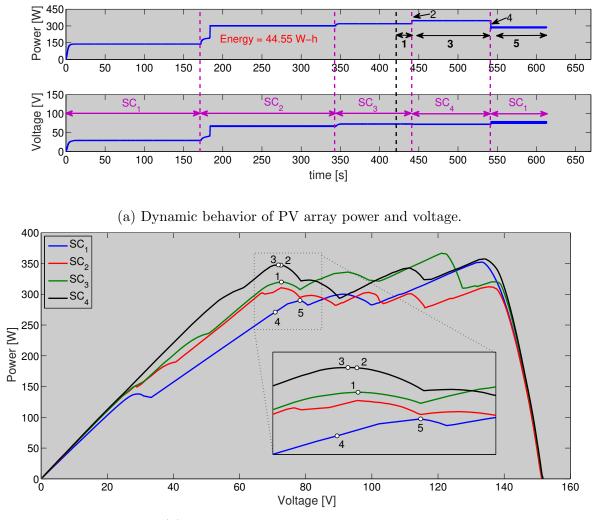

| <b>2-30</b> .Behavior of the PV array with the proposed reconfiguration algorithm                       | 56  |

| <b>2-31</b> .Behavior of the PV array with fixed configuration                                          | 59  |

| <b>3-1</b> . Stand-alone power system with bus voltage regulation.                                      | 64  |

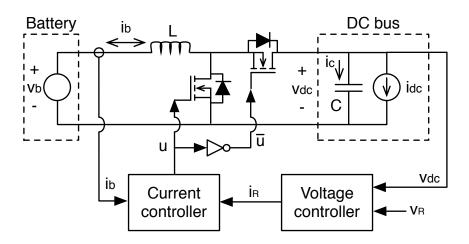

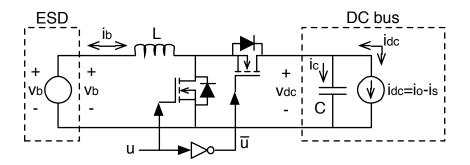

| <b>3-2</b> . Structure of a cascade control of the charger/discharger.                                  | 66  |

| <b>3-3</b> . Charger/discharger based on a bidirectional DC/DC converter                                | 66  |

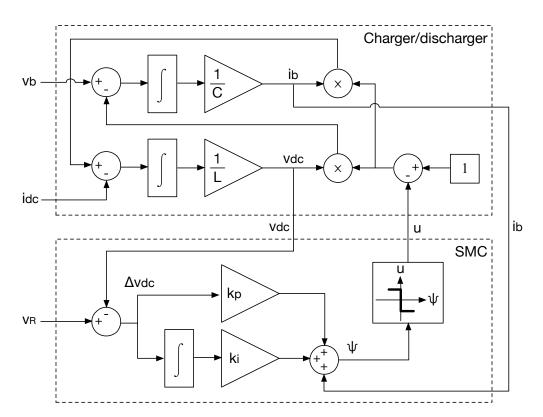

| <b>3-4</b> . Block diagram of the sliding-mode control                                                  | 67  |

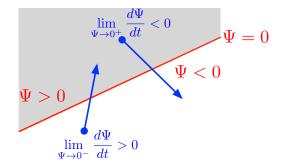

| <b>3-5</b> . Concept of reachability conditions.                                                        | 69  |

| <b>3-6</b> . Time response of an underdamped second-order system with a zero                            | 75  |

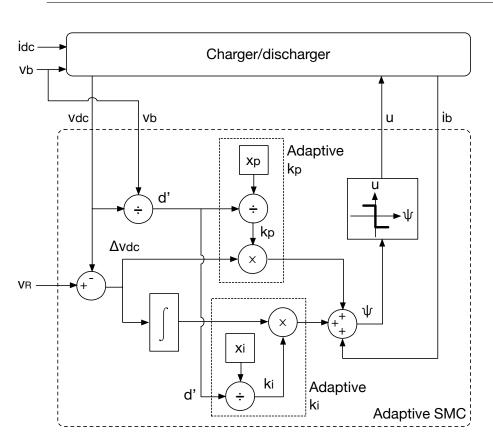

| <b>3-7.</b> Block diagram of the adaptive sliding-mode controller (Adaptive SMC)                        | 78  |

| <b>3-8</b> . Switching circuit.                                                                         | 80  |

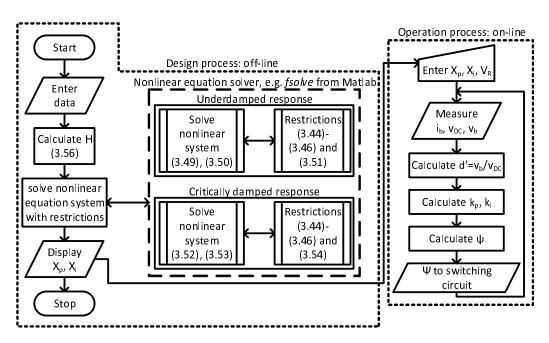

| <b>3-9.</b> Procedure to design and operate the SMC.                                                    | 82  |

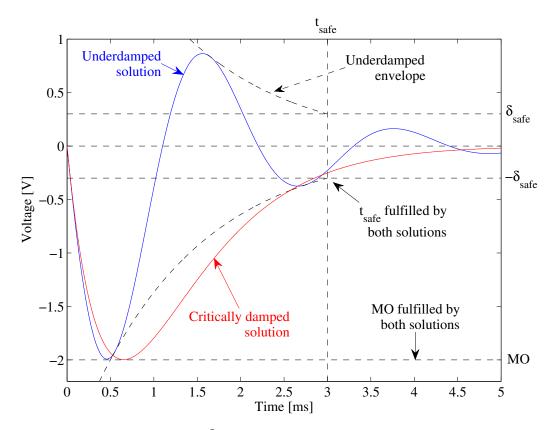

| <b>3-10</b> .Matlab <sup>®</sup> simulation of the sliding-mode dynamics. $\ldots$                      | 83  |

| <b>3-11</b> .PSIM <sup>®</sup> simulations of the sliding-mode control system.                          | 85  |

| <b>3-12</b> .Open loop operation of the charger/discharger                                              | 86  |

| <b>3-13</b> .Experimental setup.                                                                        | 88  |

| <b>3-14</b> .Voltage regulation of the DC-bus for 1 A current steps.                                    | 89  |

| <b>3-15</b> .Voltage regulation of the DC-bus under ESD voltage perturbations                           | 90  |

| <b>3-16</b> .Structure of the unified sliding-mode controller for the charger/discharger                |     |

| proposed in Section 3.1                                                                                 | 91  |

| <b>3-17</b> . Simulation of the controller presented in section 3.1                                     | 93  |

| <b>3-18</b> . Proposed structure of a sliding-mode controller with improved disturbance                 |     |

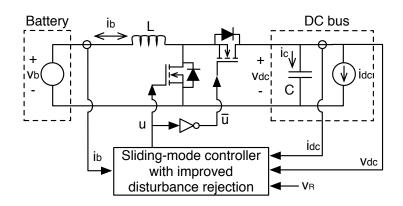

| rejection for the charger/discharger                                                                    | 94  |

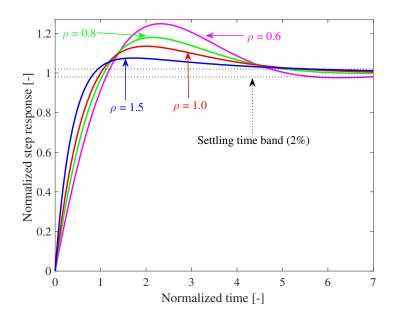

| <b>3-19</b> . Effect of damping ratio on the dynamic response of $G_{dc}(s)$                            | 100 |

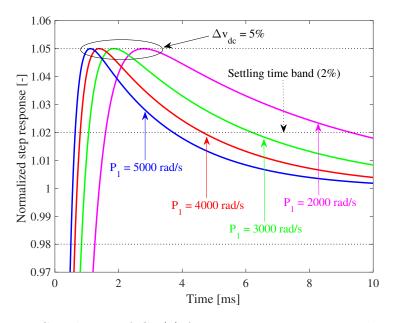

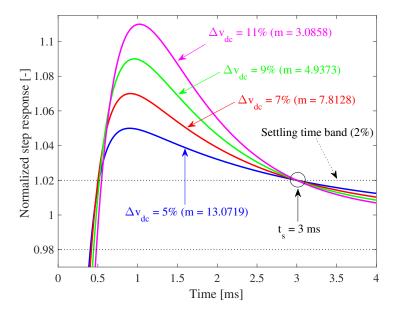

| <b>3-20</b> . Simulation of $G_{dc}(s)$ for $m = 0.0765$ to ensure that $\Delta v_{dc} = 5\%$ .         | 103 |

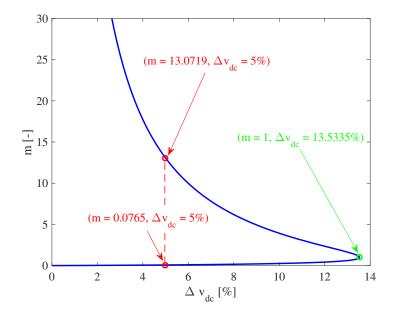

| <b>3-21</b> . Values of $m$ to provide a desired $\Delta v_{dc}$ .                                      | 103 |

| <b>3-22</b> . Simulation of $G_{dc}(s)$ with values of $P_1$ to ensure that $t_s = 3 ms$ for a settling |     |

| time band $\epsilon = 2\%$ .                                                                            | 104 |

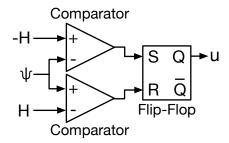

| <b>3-23</b> .Switching circuit implementing the control law in (3-101)                                  | 106 |

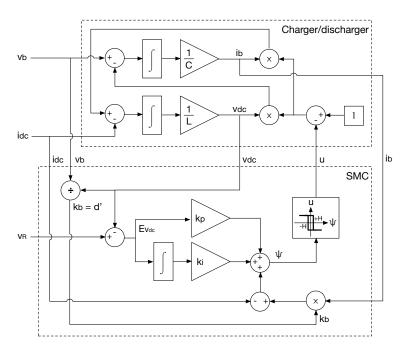

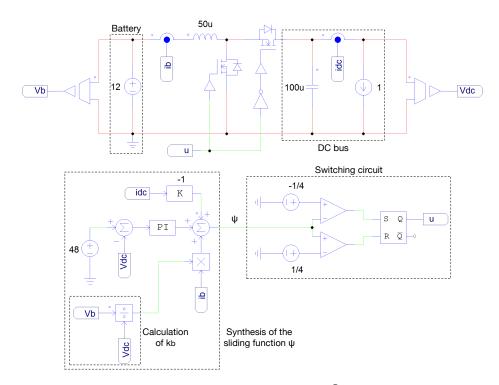

| 3-24.Block diagram of the charger/discharger and the sliding-mode controller (SMC).                     | 109 |

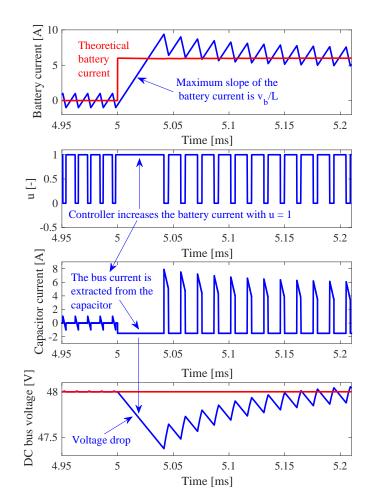

| <b>3-25</b> .Simulation of the proposed controller with a step perturbation in the DC bus               |     |

| $\operatorname{current.}$                                                                               | 110 |

| <b>3-26</b> .Circuit implemented in $PSIM^{\mathbb{R}}$ electrical simulator                  |

|-----------------------------------------------------------------------------------------------|

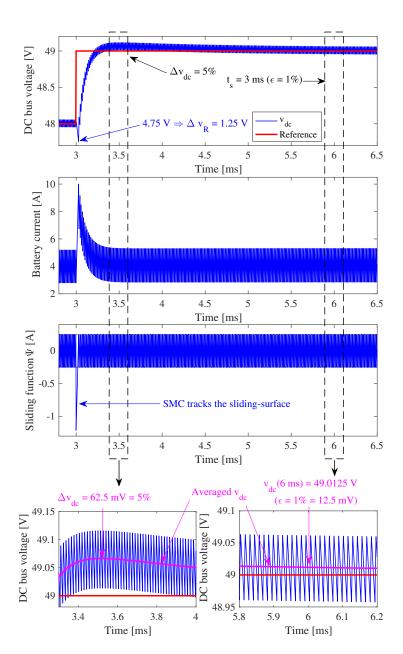

| <b>3-27</b> .Simulation of the proposed SMC with changes in the reference                     |

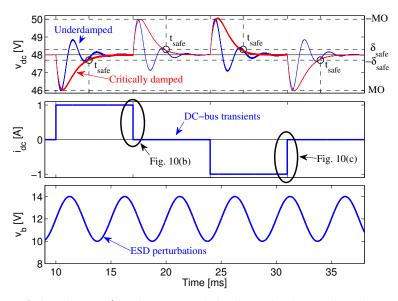

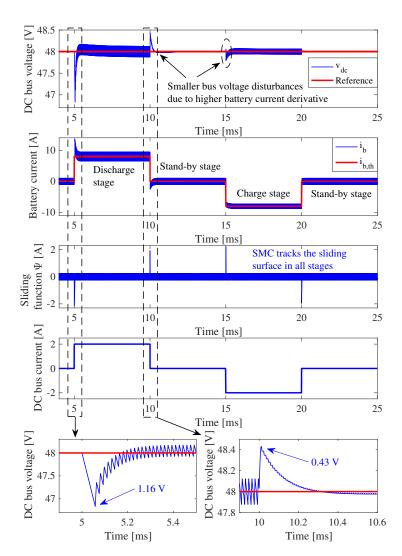

| <b>3-28</b> .Simulation of the proposed SMC with perturbations in the bus current 114         |

| <b>3-29</b> .<br>Simulation of both the proposed SMC and the SMC without measuring $i_{dc}$   |

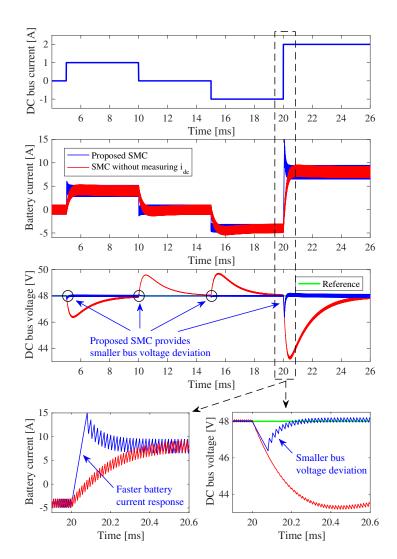

| presented in Section 3.1. $\ldots$ 115                                                        |

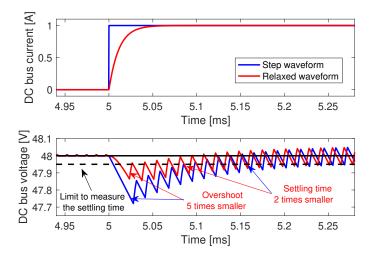

| <b>3-30</b> .Behavior of the proposed SMC for both step and relaxed current perturbations.116 |

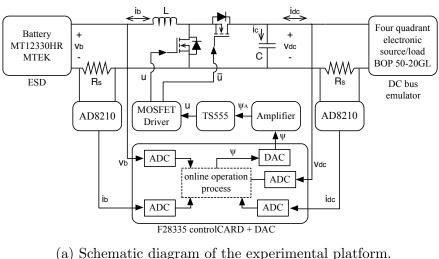

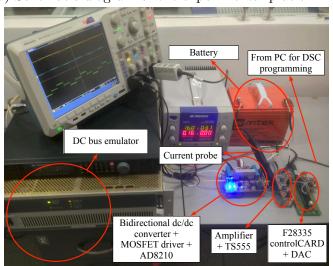

| <b>3-31</b> .Experimental platform                                                            |

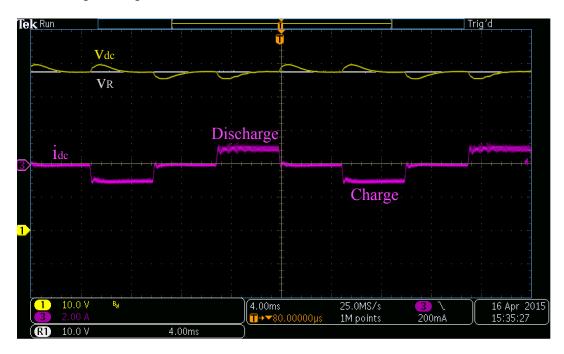

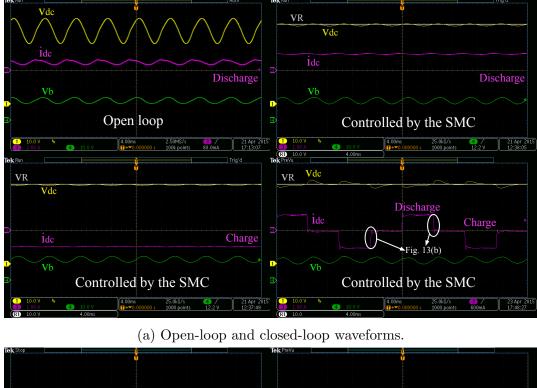

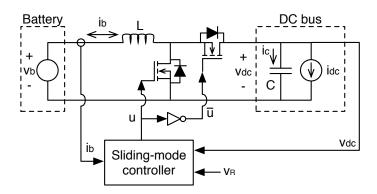

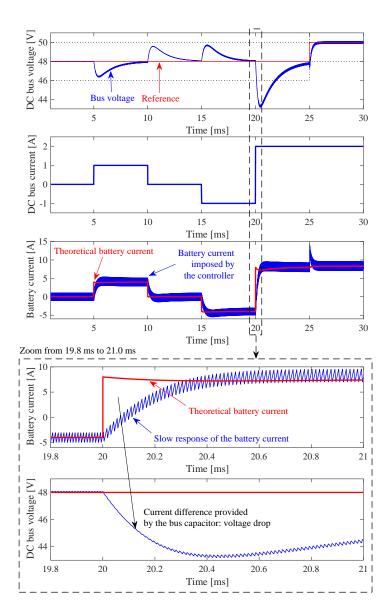

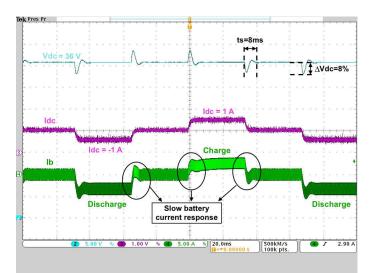

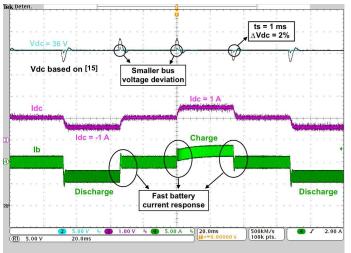

| <b>3-32</b> .Experimental results for 1 A steps in the bus current                            |

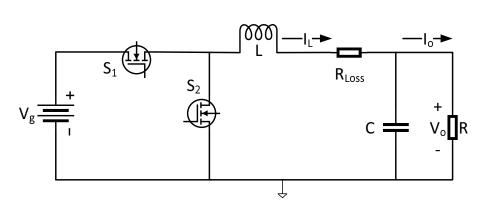

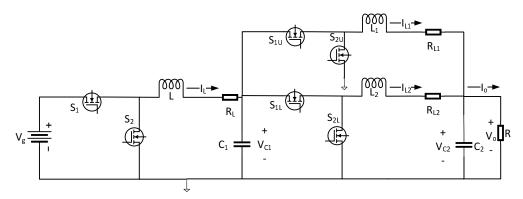

| <b>4-1</b> . Typical structure of a Buck converter (BuckS)                                    |

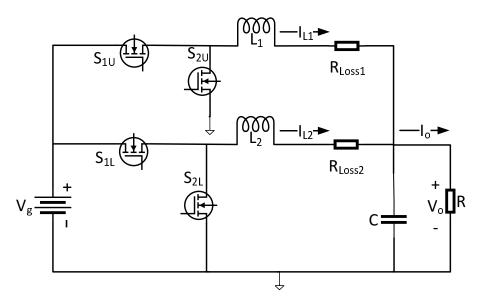

| <b>4-2</b> . Buck converter in interleaved topology                                           |

|                                                                                               |

| <b>4-3</b> . Inductors currents waveform                                                      |

| 4-4. Synchronized Buck converter with post-filter in interleaved operation (BuckPS).126       |

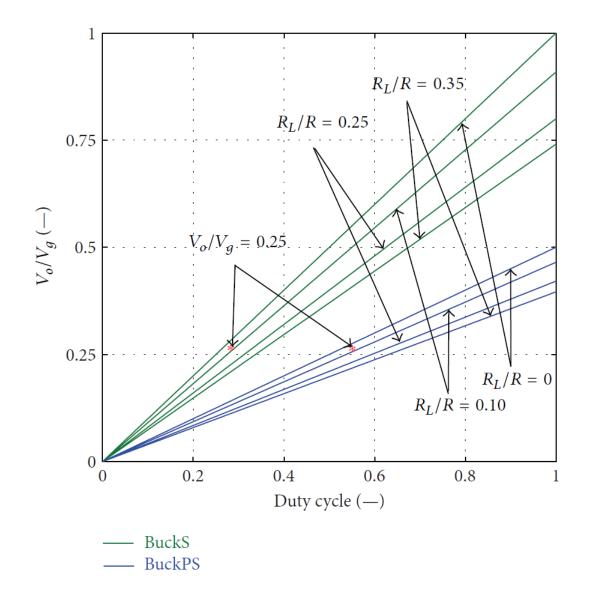

| 4-5. Conversion ratio of BuckPS and BuckS                                                     |

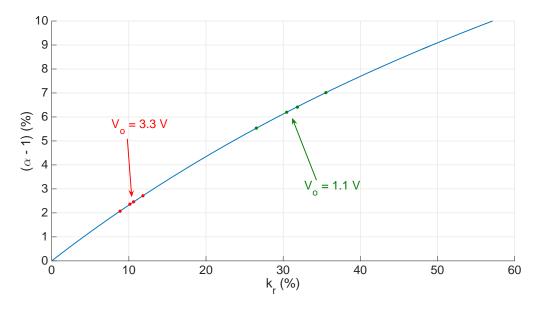

| <b>4-6</b> . Improvement efficiency factor                                                    |

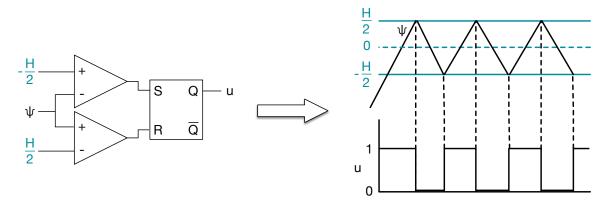

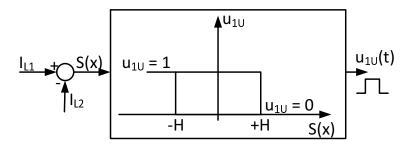

| 4-7. Logic scheme of sliding-mode controller                                                  |

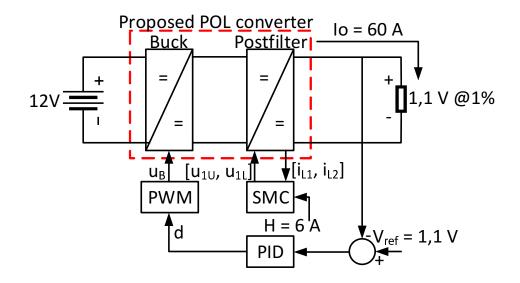

| 4-8. Practical implementation of the proposed Core 2 Duo POL regulator 134                    |

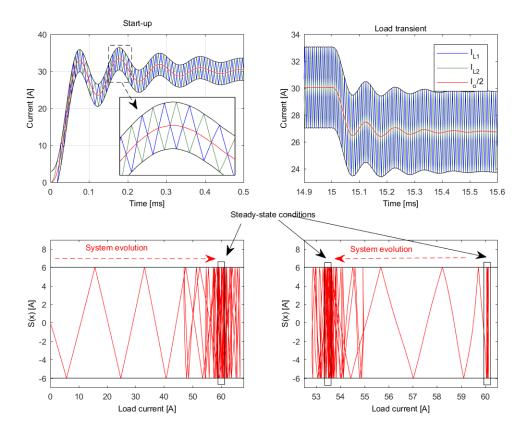

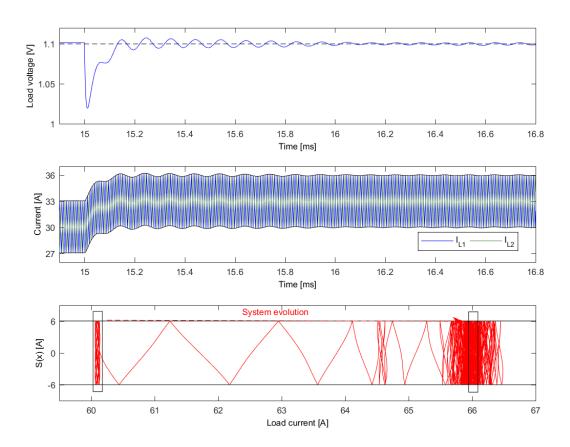

| 4-9. Post-filter simulation: start-up and load transient conditions                           |

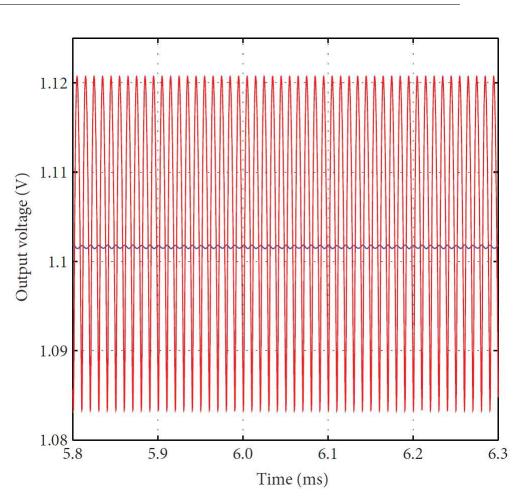

| 4-10.Output voltage ripple comparison between BuckS and BuckPS                                |

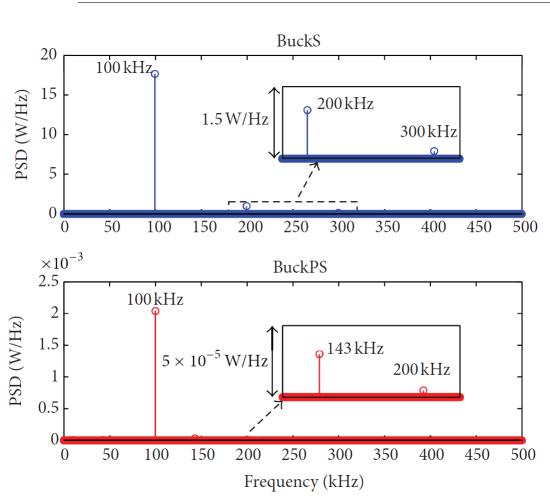

| 4-11.Power spectral density of BuckS and BuckPS                                               |

| 4-12.Dynamic behavior of the BuckPS output voltage                                            |

|                                                                                               |

\_\_\_\_\_

## 1. Introduction

The growth of the world economy has also increased the demand for electric power, which has led to the decrease of fossil fuel reserves and to increase  $CO_2$  emissions. This situation has been addressed by governments, research centers, industry and energy supply companies by using renewable sources [1, 2, 3, 4, 5, 6, 7, 8]. However, the introduction of renewable energy sources presents major challenges in political, social and technology sectors. The political sector is mainly affected by the electricity prices and regulation of the electrical companies [9, 10, 11]. At the societal level, the renewable sources decrease the greenhouse gas emissions, improve the distribution system by increasing the population coverage, and provide service for both off-grid areas and stand-alone applications [10, 12, 13]. The technological level presents many challenges: on one hand, it is required to improve the conversion device, namely, more efficient and reliable the photovoltaic (PV) panels or fuel cells [14, 15, 16, 17]; on the other hand, it is required to improve the strategies for maximizing the energy production [18, 19, 20], improve the power quality [21, 22, 23] and fulfill some non-functional requirements such as reliability, scalability, size, cost, etc. [24, 25, 26, 27].

One of the economic sectors with bigger growth is the mobile telecommunication. Due to competition in the market, telecommunication companies need to provide better and cheaper services to the customers. That requires to install base stations in zones that have not access to electrical power infrastructure. Therefore, the typical solution to provide electric power to those systems is based on diesel power. However, due to the high costs and pollution produced by such a solution, recently the telecommunication companies have focused on renewable energies as the main power source for the base stations.

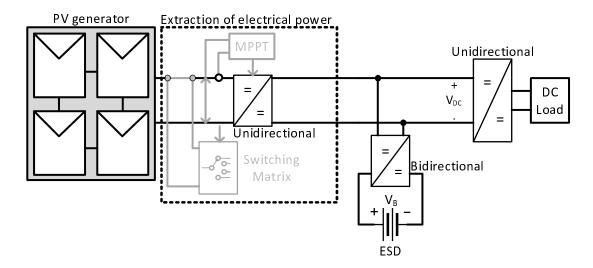

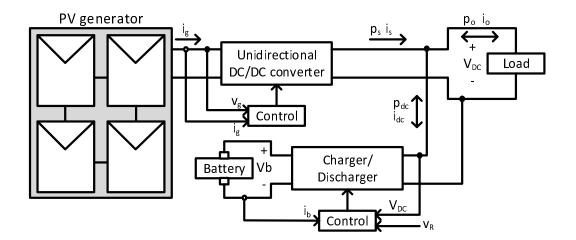

A common structure used for power systems based on renewable generators is presented in Figure 1-1, which is based on a PV array, an energy storage device (ESD) and DC-loads. This stand-alone power system has been extensively used in energy supply systems for telecommunication equipment [28, 29, 30]; but also in other applications such as electric vehicles [25, 31, 32, 33, 34, 35, 36], irrigation systems [37, 38], heating systems [39], among others. The system considers an unidirectional DC/DC converter, whose purpose is to operate the renewable generator in its optimal conditions, according to an optimization strategy devoted to performing a maximum power point tracking (MPPT). In addition, a charger/discharger power converter interfaces the ESD with the DC-bus. Such a charger/discharger controls the power exchanged between the ESD and the DC-bus, and at the same time, it is in charge of regulating the DC-bus voltage. The main advantages of this topology are: the capability of storing the energy-in-excess produced by the generator; the capability of releasing the stored energy when it is needed; and the impedance decoupling between the renewable source and the other elements, which enable to optimize the source operation. Finally, a unidirectional DC/DC power converter is connected to the DC-load, which is aimed at increasing the efficiency, and to ensure the DC power quality required by most modern loads such as data centers, computer equipment, modern televisions, standard home appliances, DC lighting systems, and telecommunication power systems.

In the remain of this Chapter, the issues of extracting the maximum power of the renewable source, the DC-bus voltage regulation, power flow control between the ESD and the DC-bus, and the regulation of the energy delivery to the DC-load with highly efficient and quality, are described.

Figure 1-1.: Stand-alone power system based on renewable energy sources.

#### 1.1. Power extraction of the PV generator

The PV generator of Figure 1-1 is formed, in general, by PV panels driven by a power converter connected to a DC-bus. Moreover, the PV panels are connected in a series-parallel (SP) configuration [40, 41, 42], which enables to reach the large DC voltage (or current) required by the power converter. A challenge in this type of PV arrays is to obtain the maximum power under any operating condition. Therefore, Chapter 2 proposes a solution to improve the power generation of the PV array in SP configuration. Despite the existence of other array configurations, such as total cross-tied (TCT), bridge-linked (BL) or honey-comb (HC) [43], the SP configuration is the most widely adopted due to its simplicity and reduced number of connections [44]. Hence, the SP configuration is considered to develop this Thesis. In uniform conditions, i.e. all the PV panels exhibiting the same parameters, temperature and solar irradiance, the electrical characteristics of the PV array are proportional to the

ones of any panel, just scaled in voltage by the number of panels in series and scaled in current by the number of strings in parallel. Thus, there exists a single optimal operating condition despite the connection between the PV panels [45, 46, 47]. However, if some (or all) PV panels exhibit different parameters, e.g. due to different irradiance caused by shades, as it is observed in Figure 1-2, the PV array produces a different maximum power depending on the electrical connections between the panels. Moreover, in those mismatched conditions, the PV array exhibits multiple maximum power points (MPP) instead of a single one, as in uniform conditions [48, 49, 50]. Mismatched conditions commonly occur in PV installations due to shades generated by objects adjacent to the array, e.g. trees, buildings, posts, other PV arrays, etc. Furthermore, since the Sun moves along the day, a PV panel can be fully irradiated, partially shaded or completely shaded depending on the hour of the day.

Figure 1-2.: Shading profiles affecting PV systems.

The effect of the shades must be carefully analyzed, otherwise, the power production of the PV array might be overestimated, leading to a subsequent non-viability of the system due to low profitability [51]. Hence, the effect of shading conditions should be reduced to increase the profitability and viability of a PV array subjected to those conditions, e.g. urban PV systems.

Under shading conditions, the current of an unprotected array is the lowest available PV current; as a result, the most productive PV modules suffer from an internal power dissipation as heat, which has a negative impact on the module lifetime. The traditional solution is to connect bypass diodes in anti-parallel to each PV module in the array. Those diodes short-circuit the PV module with lowest current production, thus protecting the whole array [52]. This solution generates multiple local maximum in the power-voltage curve of the array, which may confuse the power maximization algorithms that would lead those to be trapped in a local maximum, hence operating with non-optimal power production.

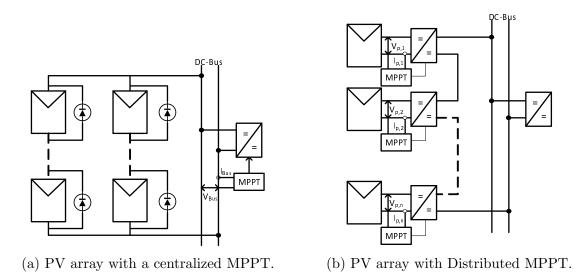

There exist some methods to improve the power extraction from PV arrays under shading conditions. One solution is to adjust the operating point on the I-V curve of the PV array, which is conducted with optimization algorithms that modify the input impedance of the DC/DC converter to maximize the power delivered to the load. Traditionally, a single algorithm that maximizes the power of the whole PV array is used to track the MPP; this scheme is known as a centralized system [53], e.g. Figure 1-3a. Nevertheless, an dedicated MPPT algorithm and converter can be used for each PV module, as it is illustrated in Figure

1-3b; this begin called a distributed MPPT system or DMPPT [54, 55, 56].

Figure 1-3.: Centralized and distributed control of a photovoltaic system.

Each solution presents advantages and disadvantages. The main benefit of the centralized method is the use of one MPPT controller and a single power converter (DC/DC or inverter), which reduces costs compared with the DMPPT [55]. However, the power converter used in the centralized system requires higher design complexity due to its multiple functions: boosting or reducing the voltage of the PV modules to the level required by the application, and performing the actions commanded by the MPPT algorithm [57].

Moreover, the centralized control architecture also introduces a disadvantage regarding implementation cost and complexity compared to typical MPPT algorithms. However, if such a high complexity always ensures the operation of the system at the maximum power point, then it might be acceptable. On the other hand, it is necessary to consider that a complex algorithm might not be viable due to processing hardware limitations [58, 59].

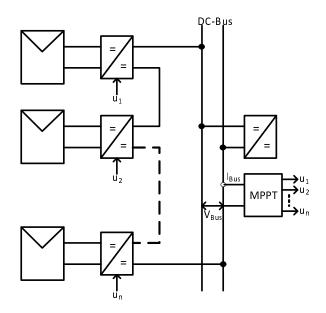

In contrast, the DMPPT solution guarantees the operation of each PV module at the corresponding MPP (maximum power point), therefore, it extracts the maximum available power from the array [60]. Nevertheless, this solution requires an elevated number of DC/DC converters (one per PV module), as well as a considerable amount of MPPT controllers and V/I sensors (one per each DC/DC converter) [61]. This characteristic introduces a high cost due to the large number of power conversion elements, sensors and processing platforms, as well as the complexity of the design, and the associated installation procedure. In any case, with the development of new technologies for data processing (DSPs, microcontrollers, FPGAs, processors, etc.) and multi-variable MPPT (MV-MPPT) algorithms, e.g. the one reported in Figure 1-4 [54, 62, 63, 64], some of the problems of this type of systems can be mitigated, thus finding a satisfactory balance between installation cost and power production.

Figure 1-4.: PV array with multi-variable MPPT.

reduce both the hardware and system costs by using only one V/I sensor pair and a single processing device. To evaluate those type of algorithms it is necessary to have a general mathematical model for DMPPT systems, it including the electrical equations for each PV module and the dynamics imposed by the associated converters. Therefore, Section 2.1 introduces a model for DMPPT systems, while Section 2.2 proposes a MV-MPPT algorithm aimed at reducing the hardware requirements. Those are the first and second contributions of this Thesis.

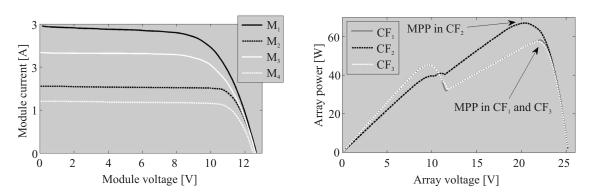

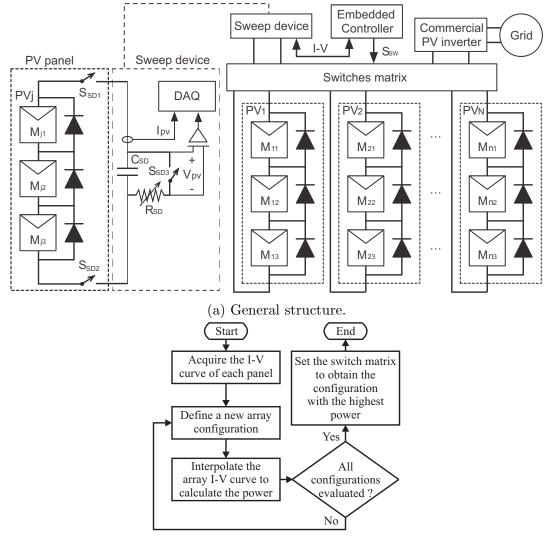

Another approach to increase the power extraction of PV arrays is the adoption of switching matrices. Those devices change dynamically the electrical connections between the PV panels, which enable to reduce the adverse effects of operating under mismatching conditions [65, 66]. A large amount of solutions to this problem use analytical models to evaluate the best set of connections for a given shading profile [67, 68, 69, 70]. Nevertheless, such a solution requires full-size computers at high cost, which decreases the profitability in commercial applications.

Instead, Section 2.3 proposes a new solution for determining the best configuration of a PV array, connected in a series-parallel (SP) structure, without using complex mathematical models. Such a procedure uses the experimental voltage/current curves of the PV panels to construct the power/voltage curves of all of the possible configurations to identify the optimal one. The main advantage of this method is the low computational effort required to reconstruct the power/voltage curves of the array. This characteristic enables one to implement the reconfiguration solutions using inexpensive embedded devices, like FPGAs or DSPs, which are widely adopted in industrial applications.

#### 1.2. DC bus regulation and storage management system

The use of renewable energy sources, or any other non-reversible source with limited bandwidth, requires the use of an additional Energy Storage Device (ESD) to store and release energy depending on the generator and load profiles: for example, slow sources (e.g., fuel cells) require ESD to support fast load transients [17]; non-predictable sources (e.g., photovoltaic panels) require ESD to support stand-alone loads during low irradiance conditions or during the nights [8].

In such a context, and due to the accelerated growth of the market for energy storage systems [71], this Thesis proposes a solution for the management of an energy storage system based on batteries. The solution considers both the bidirectional control of the energy flow to/from the battery and the voltage regulation of the DC-bus.

The common structure, based on renewable generators and ESD, used to supply electric power to the stand-alone telecommunications systems was already presented in Figure 1-1. That system considers a charger/discharger power converter to interface the ESD with the DC-bus. Such a charger/discharger controls the power exchanged between the ESD and the DC-bus, and at the same time, it is in charge of regulating the DC-bus voltage.

Multiple solutions based on the topology presented in Figure 1-1 have been reported in the literature. For example, the work reported in [72] presents a power system based on a fuel cell and an ESD (supercapacitor and battery). That solution adopts a sliding-mode controller to regulate a bidirectional Buck-Boost converter with the aim of imposing the DC-bus voltage and the supercapacitor current. Moreover, the system includes a Boost converter to regulate the fuel cell, which is controlled by a PI structure to deliver a constant power flow without power peaks. However, this system does not include an optimization algorithm to improve the fuel cell operation, hence a fraction of the stored hydrogen could be wasted. Furthermore, the adopted sliding surface does not include the integration of the DC-bus voltage error, therefore it is difficult to guarantee a null steady-state error.

Similar topologies have been used in automotive engine/battery hybrid power systems. An example is presented in [73], which is based on a bidirectional DC/DC converter controlled with a variable current limiter. Similarly, the work presented in [74] proposes a three-level bidirectional converter for fuel-cell/battery hybrid power systems. In this case, the converter operates in both Buck and Boost modes controlled by a cascade of a voltage regulator and a current limiter.

In this kind of systems, one of the main challenges is to properly regulate the bidirectional power converter (charger/discharger) associated with the ESD, namely, the controller must operate with both positive and negative power flows with minimum disturbances, even at zero power. However, the non-linear system model changes with the direction of the current, but the DC-bus voltage must be regulated in the three conditions with minimum disturbances. Linear controllers (PI, PID or lead-lag) can be designed to mitigate such perturbations [75]. However, the main problems associated with these kinds of controllers are the reduction of the closed-loop bandwidth, and the requirement to use a linearized model of the system that makes impossible to ensure the same performance, or even global stability, in all the operating conditions [76, 77, 78]. Therefore, other control techniques, mainly non-linear, are required to ensure stability in any operation condition, which is mandatory for a safe load operation. For example, sliding-mode control (SMC) has been widely investigated and has demonstrated to be a suitable solution for power converter regulation [79, 80, 81].

SMC requires the definition of a sliding surface with a desired equilibrium point, and towards to which the system must to converge: the objective is to force the system to operate within the surface at any given time [79, 82]. Most control systems based on sliding-mode include into the sliding surface the error between reference and one, or multiple, system states [83, 84, 85, 22, 86].

In the charger/discharger context, a solution based on SMC was reported in [83], in which it is proposed a cascade control of a DC/DC converter with a half-bridge bidirectional topology. In this case, the current control is designed with a fixed-frequency SMC to reduce electromagnetic interferences (EMI). In [85], a cascade control for a battery charger of an electric vehicle was proposed, but in this case, the converter is a unidirectional implementation. In that work, the inner inductor current control is designed with a discrete-time SMC, while the outer control loop calculates the current reference such that a power factor correction (PFC) stage regulates the DC-link voltage, and simultaneously, the current reference of a buck-type cells is determined depending on the state of charge (SOC) of the battery.

Similarly, the work reported in [86] is based on SMC and it is aimed at controlling a buckboost charger/discharger converter with a cascade structure: an outer voltage loop based on a PI structure defines the reference of an inner current loop based on an SMC, in which the sliding surface is formed by the inductor current error. This solution is oriented to electric vehicles applications.

Other sliding-mode controllers adopt more complex sliding surfaces, e.g., the works reported in [87, 88], which will be reviewed in Chapter 3. Also, the work reported in [89] considers a sliding surface based on the output power error, hence it is a non-linear surface. This approach was used to provide constant power to the load and, at the same time, to reduce instability due to the negative impedance of the power converter. Similarly, the controller reported in [90] propose a sliding surface formed by the output voltage error and both the time integral and the derivative of that error, this to stabilize a Buck converter with constant power load. Since such a surface can be written as a second-order differential equation, the mathematical analyses required to guarantee stability are extensive despite the relative simplicity of the system model. Another SMC for controlling a bidirectional DC/DC converter, used to interface a parallel-connected hybrid energy storage system with a DC-bus, was proposed in [91]. That system is formed by a vanadium redox battery, a supercapacitor and a renewable power source. Moreover, in that work, the sliding-surface is similar to the one introduced in Chapter 3 of this Thesis, but without any adaptability to compensate for the duty cycle variation. Another complex surface is presented in [92], which is based on the output voltage error and the square of the output capacitor current in a Buck converter. This surface is intended to improve the settling time and steady-state error of the output voltage regulation.

Chapter 3 of this Thesis proposes an adaptive sliding-mode controller for the ESD charger/discharger to regulate the load voltage in any power flow condition. The solution considers the topology presented in Figure 1-1 with a controller designed to fulfill both steadystate and dynamic performance criteria, which are defined in terms of the safe margins required for the correct load operation. This is the third contribution of the Thesis.

#### 1.3. Efficient delivery of quality electric power to the load

The power quality must be a design criterion for any efficient and reliable micro-grid. Considering only DC micro-grids, low-quality power produces high losses due to undesirable oscillations on current and voltage signals [22]. Those losses also increase the cost of the energy, hence of the micro-grid. At the same time, the voltage and current oscillations also affect the reliability of the power converters.

The power supplies designed for telecommunication systems must provide sharp requirements: low voltage, high current, and low ripple at the load terminals. Such conditions are imposed to ensure a high performance of the processing devices of those types of equipment, namely, microprocessors, DSP, ASIC, or memory devices [93]. Likewise, the efficiency also can be increased guaranteeing DC-electrical-power-quality [94]. This issue is addressed in Chapter 4 of the Thesis, which proposes an active post-filter for a Buck converter aimed at reduce the ripple at the load terminals.

The fundamental elements that must be taken into account to ensure DC power quality are the inrush currents, fault currents, grounding and harmonic currents [94].

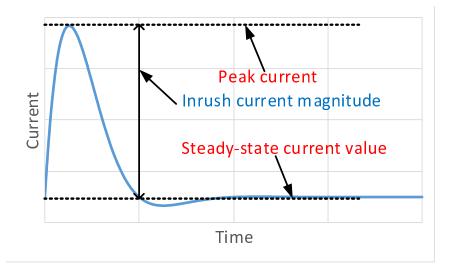

Inrush currents are associated to the turn-on of some equipment, mainly transformers and induction motors, which are AC loads. However, transients in the sources and loads of a micro-grid could introduce these inrush currents on the DC-bus as the one depicted in Figure 1-5. Typically, this issue is faced with EMI filters placed between the DC-bus and ground, also by using an inrush current limiter (Surge Limiter), which is a special type of negative temperature coefficient (NTC) thermistor.

AC inrush current limiters are not the topic of this Thesis. However, they are widely known and there exist many works on this topic [95, 96, 97, 98, 99, 100, 101, 102, 103].

In the case of DC systems, the difference between the start output voltage and the regulated output voltage creates a high current demand. This, in turn, produces a large inrush current through the inductor of a DC/DC converter. The inrush current is a serious concern, since it can exceed the current derivative limitations of the source. To eliminate this undesired condition, some soft-start methods for DC/DC converters have been proposed [104, 105, 106, 107, 108, 109, 110]. Soft-start ensures that the maximum acceptable current is reached slowly, and not at once.

9

Figure 1-5.: Current waveform when the device is powered up.

In DC-systems, the fault current can be produced by a load, through a power converter, by a source or by the capacitance forming the DC bus. In any case, the fault current is limited by the power ratings of the converter, the source limitations or the charge stored in the distributed capacitance forming the DC-bus. Figure **1-6** shows both peak current and voltage droop of a Buck converter after a ground fault occurs, depicting also the subsequent activation of the protection. Those currents are generally detected by overcurrent relays. However, at higher voltage levels, the interruption of direct current by mechanical separation is an open research topic [111, 112].

On the other hand, an appropriate grounding configuration for a DC distribution system is very important for the power quality and safety of the system. The type of grounding used, e.g. TN-S, TT or IT grounding [113], determines the path of current for a ground fault, which impacts the level of fault current.

Finally, by definition, the DC-systems do not experience harmonic currents and voltages, since their fundamental frequency is 0Hz. However, the presence of current and voltage oscillations generated by power converters, make possible to extend the harmonic term to a DC-system. Such DC-systems have converters at the Point-Of-Load (POL), at the source, at the storage device, and at the connection point with the AC-grid. Those converters non-linear effects create oscillations on the currents and voltages, which can produce damaging resonance currents and unacceptable EMI on equipment near the transmission lines, as well as overloading and physical damaging the transmission system itself [114, 115].

Considering that in telecommunication systems the loads operate at low voltage and high current, Buck converters are widely adopted for those applications. However, the quality of both current and voltage signals generated by a Buck converter is affected by the variations of the load, the source, or the parameters tolerance, which change the ripple magnitudes, among other problems [116, 117, 118].

Figure 1-6.: Current and voltage characteristics during a DC short-circuit fault.

Several solutions have been proposed in the literature to improve the quality of the current and voltage generated by a Buck-based POL regulators. In [119], the ripple of a POL converter is reduced by means of a L-C output filter with two stages, which is classically regulated using a controller with two feedback points: the first point sensing the capacitor voltage of the first L-C stage and the second point sensing the capacitor voltage of the second L-C stage, that is, the load voltage. In such a solution, the authors demonstrate that a controller with a single feedback point could be used to stabilize the POL converter, but it requires adjusting one L-C filter to cancel out the zeros of the other L-C filter. In any case, the ripple magnitudes depend on the load impedance, which could change depending on the application conditions.

In [120] the performance of Buck-based POL with different current controllers is analyzed, taking into account the bandwidth of the voltage loop and the changes in the input voltage. But such a solution does not analyze the ripple behavior with load variations.

A different approach was presented in [121], where a digital controller is used to reduce the load current ripple in a non-isolated POL converter. Such a solution is based on peak current and average current controllers implemented in an FPGA. This controller scheme requires an Analog-to-Digital (A/D) converter, which increases the system cost in comparison with analog implementations. In the same way, [122] proposes a self-oscillating digital modulator to change instantaneously the duty cycle of the PWM signal driving the converter switch. Thus, it is possible to achieve the sampling frequency of the output voltage required in the control loop, which is higher than the switching frequency of the power converter. In this way, a short time response is achieved in the compensation of load variations. However, such

a solution does not introduce current or voltage ripples analyses.

In [123], a method to design the output filter of a low-voltage/high-current synchronous Buck converter, using performance boundary curves, is proposed. Such curves constrain the regions in the space of parameters to ensure an acceptable output voltage ripple. But, similar to the previous solutions, the load and source changes affecting the ripple magnitudes are not analyzed.

The previous solutions address the current and voltage ripple requirements by means of passive filters, which are impossible to be modified during operation time. Hence, those solutions are sensible to changes in the load impedance, source voltage, and tolerances of the electronic component parameters. Therefore, Chapter 4 of this Thesis proposes a POL solution based on a synchronous Buck converter operating in cascade with an active post-filter, which provides an almost ripple-free current to the load. The post-filter is formed by two parallel-connected Buck converters operating in complementary interleaving [124], and it is regulated using a sliding-mode controller to ensure its correct operation. The proposed POL compensates changes in the load impedance, source voltage, and electronic component parameters. Moreover, the proposed solution improves the electrical efficiency of the classical Buck-based POL. This correspond to the fourth contribution of the Thesis.

In conclusion, this Thesis will face three issues identified above for the architecture reported in Figure 1-1. First, the improvement of generated power by the PV array (Chapter 2); second, the DC-bus regulation by controlling the storage management system (Chapter 3); finally, efficient power delivery to the load with high-quality electric power (Chapter 4). Those solutions introduce four state-of-art contributions, which have been reported in five (5) Journal papers: three Q1 (Scopus) papers and one Q3 (Scopus) paper. Those papers are also indexed by Publindex as three A1 papers and two A2 papers.

# 2. Improvements in the power extraction of photovoltaic source

This Chapter proposes two solutions to increase the power production of a PV array operating under mismatched conditions. The first solution is a distributed MPPT algorithm, while the second solution is a PV reconfigurator.

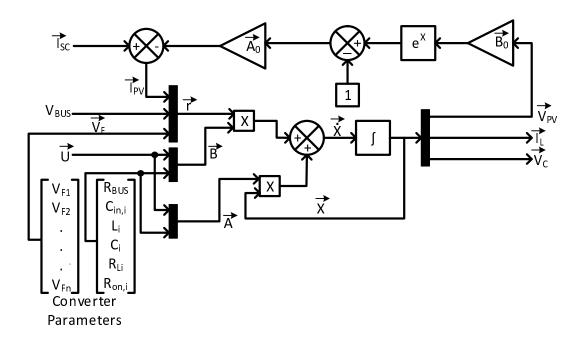

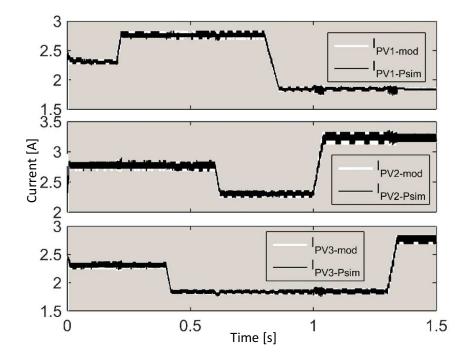

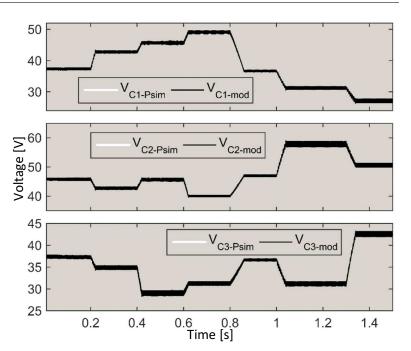

Design and simulation of distributed MPPT techniques require a model of the photovoltaic generation system. Therefore, this Chapter proposes a model considering the connection of a module-converter set in series with other sets, which can be sized depending on the particular application. The model is described by a series of equations that can be implemented on any mathematical software or programming language to solve them. Those equations include the static behavior of the photovoltaic module described in terms of the voltage-current relation. In addition, the model takes into account the dynamics of the boost converter, including losses in the inductor, to approximate the model behavior to a realistic situation. The simulations of the model, compared with the system implementation in a traditional circuital simulator, have an excellent fit.

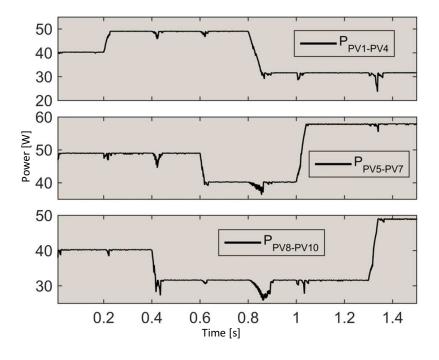

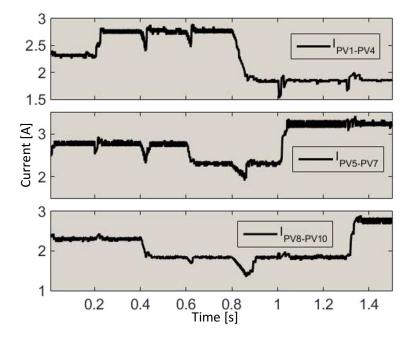

The model was used in the design of a vectorial control with the aim of increasing the PV power transferred to the DC-link. This algorithm is a multivariable MPPT that perturbs the operating point of all the DC/DC converters at the same time. Simulation results confirm that the proposed technique performs better than other multivariable controllers presented in the literature.

Another method developed in this Chapter, aimed at increasing the maximum power of a PV array operating under mismatching conditions, is based on the dynamic electrical reconfiguration of the array connected in a series-parallel structure without using complex mathematical models. Instead, it is based on the experimental current vs. voltage curves of the PV panels, which are composed by multiple PV modules. Such curves are used to construct the power vs. voltage curves of all of the possible configurations, which is needed to identify the optimal one. The main advantage of this method is the low computational effort required to reconstruct the power vs. voltage curves of the array. This characteristic enables one to implement the proposed solution using inexpensive embedded devices, which are widely adopted in industrial applications. The proposed method and its embedded implementation were tested using a hardware-in-the-loop simulation of the PV system. Finally, the real-time operation and benefits of the proposed solution were illustrated using a practical example

based on commercial devices.

The methods developed in this Chapter were reported in [54, 125, 126, 127].

## 2.1. Mathematical model of distributed photovoltaic systems

DMPPT are the architectures, methods and algorithms dedicated to the maximization of the power produced by a PV array in presence of mismatching conditions [56]. In particular, according to this approach, each PV module has its own switching converter in charge of tracking the module MPP. The DMPPT can be implemented using micro-inverters or, as in the case described in [56], by means of DC/DC converters, each one of them working independently from the others. In this way, the maximum level of modularity is obtained, because each DC/DC converter tracks the best operating point of the PV module it is dedicated to, hence the power produced by the whole PV system is maximized.

The power delivered by a photovoltaic (PV) module is inherently DC, and it is generally at low voltage. However, in many applications it is necessary to connect the PV modules to a high voltage DC-bus or an AC grid. In both cases, the electric power generated by a PV module must be converted to high voltage levels with the highest efficiency possible. To raise the PV modules voltage it is necessary to connect them in series [128, 129, 130, 52], each one of them interfaced by its corresponding DC/DC converter.

Once the size of the PV array grows, validation process of this system design becomes very difficult, hence simulations are mandatory to predict power generation. Therefore DMPPT (Distributed MPPT) systems are traditionally evaluated using an electric simulator, e.g. PSPICE<sup>®</sup> or PSIM<sup>®</sup>.

Those constraints result in the need to develop a mathematical model to predict the behavior of a DMPPT system in a detailed and accurate way. Such a model must not be based on a particular simulation software, instead it should enable its implementation in any programming language, e.g. C or Matlab<sup>®</sup>. Some authors have developed this type of mathematical models for DMPPT systems that can be implemented in nonlinear systems of equations [128, 129, 131]. For example, the work reported in [131] propose the model for PV-converter set, where the converter is a four-switch buck-boost converter used for distributed maximum power point tracking (DMPPT) in series-connected PV system applications. Likewise, [129] presented a model of two module-boost converter sets used for non-linear control of DMPPT applications. Similarly, the study presented in [128] describes a DMPPT system modeling a PV array-inverter set as part of a DC micro-grid based on renewable energy. Nevertheless, those works do not present a general model for N module-power converter sets enabling easy implementation in any programming language.

Therefore, this section proposes a general mathematical model for DMPPT systems, which includes the electrical equations for each PV module and the dynamics imposed by the associated converters. Such level of detail makes this model an ideal tool for evaluating safety levels and MPPT algorithms. The results of this work were reported in [54, 125].

#### 2.1.1. Model description

The functional unit of a DMPPT system is composed by a PV module and a DC/DC converter [56]. The mathematical model of the PV module is reported in [75, 66] and it is described by (2-1), in which  $I_{PV}$  is the current of the module,  $I_{SC}$  is the short-circuit current,  $V_{PV}$  is the voltage of the module and  $A_0$  and  $B_0$  are parameters depending on the irradiance and temperature.

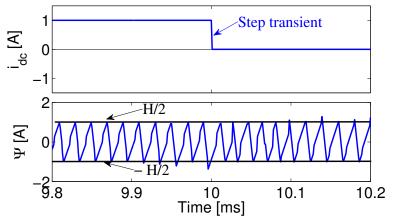

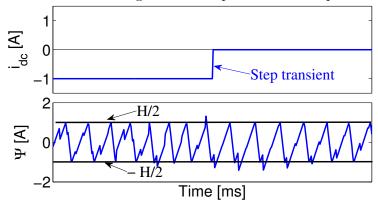

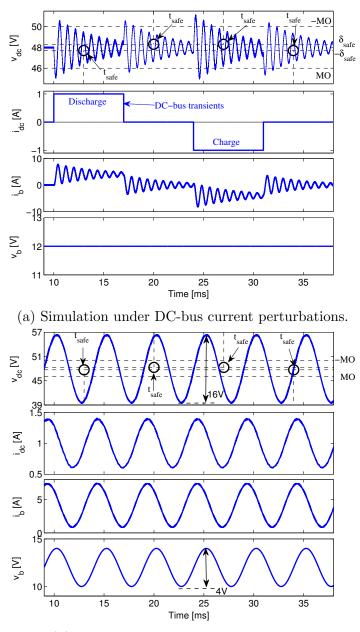

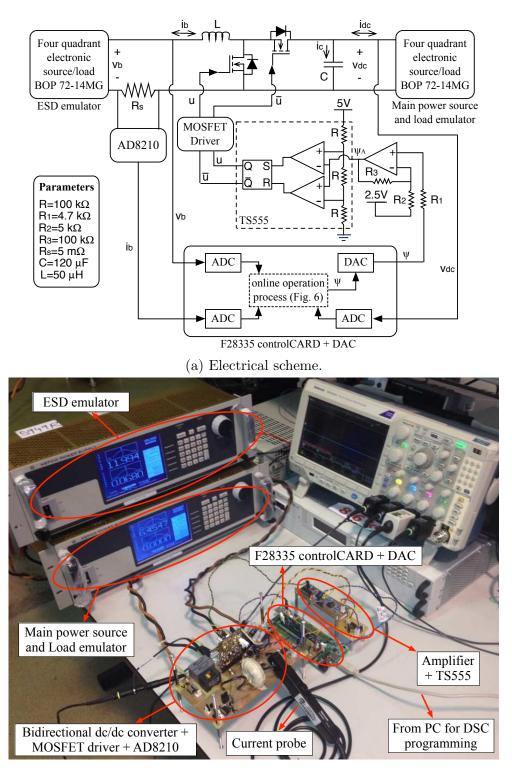

$$I_{PV} = I_{SC} - A_0 \left( e^{B_0 \cdot V_{PV}} - 1 \right) \tag{2-1}$$