# ARCHITECTURAL SUPPORT FOR EFFICIENT COMMUNICATION IN FUTURE MICROPROCESSORS

A Dissertation

by

YU HO JIN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2009

Major Subject: Computer Engineering

## ARCHITECTURAL SUPPORT FOR EFFICIENT COMMUNICATION IN FUTURE MICROPROCESSORS

A Dissertation

by

YU HO JIN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee,

Eun Jung Kim Duncan M. H. Walker Committee Members,

Rabi N. Mahapatra A. L. Narasimha Reddy

Valerie E. Taylor Head of Department,

May 2009

Major Subject: Computer Engineering

## ABSTRACT

Architectural Support for Efficient Communication in Future Microprocessors. (May 2009)

Yu Ho Jin, B.S., Korea Advanced Institute of Science and Technology;

M.S., Korea Advanced Institute of Science and Technology

Chair of Advisory Committee: Dr. Eun Jung Kim

Traditionally, the microprocessor design has focused on the computational aspects of the problem at hand. However, as the number of components on a single chip continues to increase, the design of communication architecture has become a crucial and dominating factor in defining performance models of the overall system. On-chip networks, also known as Networks-on-Chip (NoC), emerged recently as a promising architecture to coordinate chip-wide communication.

Although there are numerous interconnection network studies in an inter-chip environment, an intra-chip network design poses a number of substantial challenges to this well-established interconnection network field. This research investigates designs and applications of on-chip interconnection network in next-generation microprocessors for optimizing performance, power consumption, and area cost. First, we present domain-specific NoC designs targeted to large-scale and wire-delay dominated L2 cache systems. The domain-specifically designed interconnect shows 38% performance improvement and uses only 12% of the mesh-based interconnect. Then, we present a methodology of communication characterization in parallel programs and application of characterization results to long-channel reconfiguration. Reconfigured long channels suited to communication patterns enhance the latency of the mesh network by 16% and 14% in 16-core and 64-core systems, respectively. Finally, we discuss an adaptive data compression technique that builds a network-wide fre-

quent value pattern map and reduces the packet size. In two examined multi-core systems, cache traffic has 69% compressibility and shows high value sharing among flows. Compression-enabled NoC improves the latency by up to 63% and saves energy consumption by up to 12%.

To My family

#### ACKNOWLEDGMENTS

This dissertation is dedicated to my parents. They were always with me when I started the PhD journey in Texas. I am deeply honored by their patience, understanding, and commitment throughout my life. I am in debt for their tremendous moral and financial support.

I would like to thank my two sisters and non-Texas A&M friends. They have provided many experiences and perspectives to last a lifetime. They always supported my endeavors, never doubted my abilities, and deserve much thanks.

My education at Texas A&M University, College Station has been a life-changing experience. I would like to thank my advisor Eun Jung Kim for her many years of patience, wisdom, and encouragement. I sincerely appreciate all her advice and anecdotes, and she has certainly made my graduate experience an enjoyable one. I thank Duncan Walker, Rabi Mahapatra, and Narasimha Reddy. I appreciate their time and advice on all aspects of my research, and for providing insightful feedback on my research and presentations. I also thank Ki Hwan Yum for providing excellent technical advice and teaching me essential skills for good writing.

I thank the numerous students in High-Performance Computing Lab, where a multitude of people with lots of talent come together for a common purpose. I am grateful to have met a wonderful group of people, including Hogil Kim, for listening to my various rants and raves over the years, Manhee Lee, for encouraging me in various ways, Heungki Lee, for always showing confidence in me, Minseon Ahn, for helping me jump into a new simulation tool, and, Baiksong An, for arranging everything in a perfect way during hectic examination times. I also thank other students, Inchoon Yeo, Lei Wang, Babatunde Azeez, Gopinath Vageesan, Varrian Hall, Jay Iyer, Sungho

Park, Chih-Chun Liu, and Poornachandran Kumar. They have been always good colleagues in the lab.

I thank the professors that influenced me to pursue the field of Computer Science in KAIST and Texas A&M University. Jin Hyung Kim, my master degree advisor, offered my first opportunity for conducting research. Lastly, I thank Jian Li for his mentoring and stimulating my work when I had internship in IBM Research.

## TABLE OF CONTENTS

| CHAPTER |                                                                                                                | Page            |

|---------|----------------------------------------------------------------------------------------------------------------|-----------------|

| I       | INTRODUCTION                                                                                                   | 1               |

|         | A. Networks-on-Chip                                                                                            | 1               |

|         | B. Dissertation Contributions                                                                                  | 2               |

|         | <ol> <li>NoC Designs for Large Cache Systems</li> <li>Communication Characterization Towards Recon-</li> </ol> | 3               |

|         | figurable NoCs                                                                                                 | 3               |

|         | 3. Adaptive Data Compression in NoCs                                                                           | 5               |

|         | C. Dissertation Organization                                                                                   | 6               |

| II      | BACKGROUND: NETWORKS-ON-CHIP                                                                                   | 7               |

|         | A. NoC Building Blocks                                                                                         | 7               |

|         | 1. Topology                                                                                                    | 7               |

|         | 2. Router                                                                                                      | 7               |

|         | 3. Link                                                                                                        | S               |

|         | B. NoC Applications                                                                                            | 10              |

| III     | NOC DESIGNS FOR LARGE CACHE SYSTEMS                                                                            | 14              |

|         | A. Overview                                                                                                    | 14              |

|         | B. Related Work                                                                                                | 17              |

|         | C. Designing Communication for Cache Architecture                                                              | 19              |

|         | 1. Fast-LRU Replacement                                                                                        | 19              |

|         | 2. Performance Gain Estimation                                                                                 | 24              |

|         | D. Interconnection Network Topology and Layout                                                                 | 27              |

|         | E. Designing Multicast Single-Cycle Router                                                                     | 33              |

|         | F. Experimental Methodology                                                                                    | 36              |

|         | G. Experimental Results                                                                                        | 39              |

|         | 1. Performance of Multicast Fast-LRU Replacement                                                               | 39              |

|         | 2. Performance Comparison of Different Interconnection Network Designs                                         | 42              |

|         |                                                                                                                |                 |

|         | <ol> <li>Area Comparison of Different Network Designs</li> <li>Performance Model Evaluation</li> </ol>         | $\frac{46}{47}$ |

|         |                                                                                                                | 41              |

| IV      | COMMUNICATION CHARACTERIZATION TOWARDS RE-                                                                     |                 |

|         | CONFIGURABLE NOCS                                                                                              | 50              |

| APTER |                                                        |

|-------|--------------------------------------------------------|

|       | A. Motivation                                          |

|       | B. Related Work                                        |

|       | C. Characterization Methodology                        |

|       | D. Characterizing Spatio-Temporal Behavior             |

|       | E. Phase-based Characterization                        |

|       | 1. Feature Vector Construction                         |

|       | 2. Phase Classification                                |

|       | 3. Phase-Classified Performance and Power Behavior     |

|       | 4. Network Topology Effects                            |

|       | F. Applying Characterized Results to Long Channel Con- |

|       | figuration                                             |

| V     | ADAPTIVE DATA COMPRESSION IN NOCS                      |

|       | A. Motivation                                          |

|       | B. Related Work                                        |

|       | C. Data Compression in On-Chip Networks                |

|       | 1. On-Chip Network Architecture                        |

|       | 2. Compression Support                                 |

|       | 3. Table Organization                                  |

|       | D. Optimizing Compression                              |

|       | 1. Shared Table                                        |

|       | 2. Streamlined Encoding                                |

|       | 3. Dynamic Compression Management                      |

|       | E. Methodology                                         |

|       | F. Experimental Results                                |

|       | 1. Compressibility and Value Pattern                   |

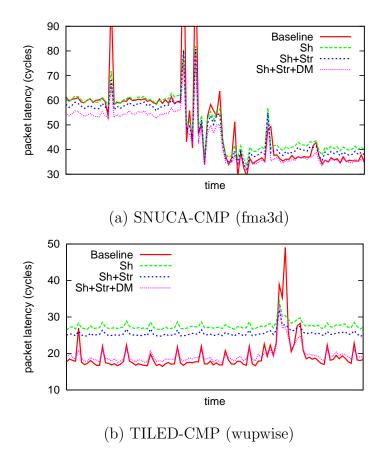

|       | 2. Effect on Packet Latency                            |

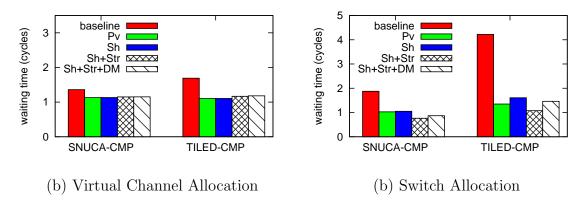

|       | 3. Effect on Contention in Router                      |

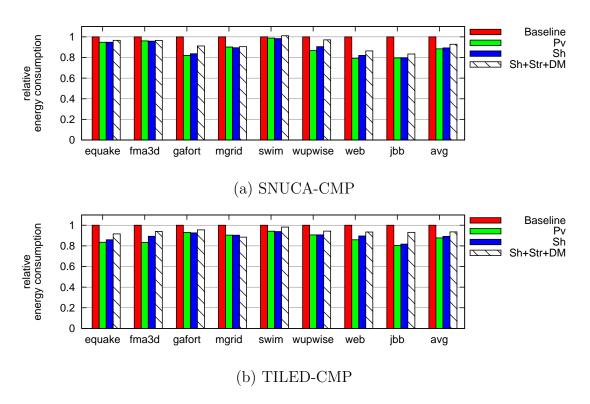

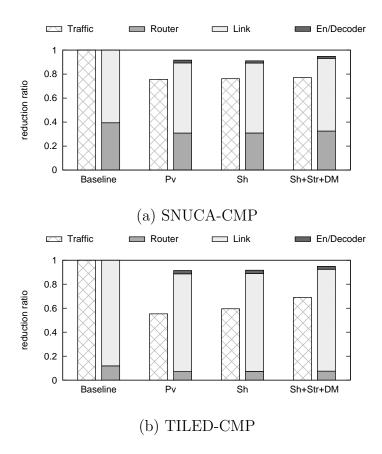

|       | 4. Effect on Network Power Consumption                 |

|       | 5. Comparison with Wide- and Long-Channel Networks .   |

| VI    | CONCLUSIONS                                            |

|       | ES                                                     |

## LIST OF TABLES

| TABLE |                                                        | Page |

|-------|--------------------------------------------------------|------|

| I     | Global Interconnect Characteristic                     | 11   |

| II    | Global Interconnect Delay/Power                        | 12   |

| III   | NoC Design Parameters in Existing CMPs                 | 12   |

| IV    | System Parameters                                      | 37   |

| V     | Latencies and Energies for Bank Access                 | 38   |

| VI    | SPEC2000 Benchmarks Used for Experiments               | 39   |

| VII   | Different Interconnection Network Designs              | 43   |

| VIII  | Area Analysis of Network Designs                       | 46   |

| IX    | 16-core and 64-core System Parameters                  | 56   |

| X     | Summary of Executed Benchmarks                         | 58   |

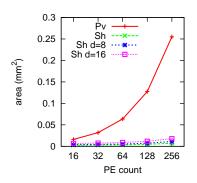

| XI    | Value Table Area Analysis                              | 90   |

| XII   | CMP System Parameters for Data Compression             | 95   |

| XIII  | Delay and Power for Interconnect for Data Compression  | 96   |

| XIV   | Encoding Table Hit Rates for Private and Shared Tables | 102  |

## LIST OF FIGURES

| FIGURI | ${f E}$                                                                   | Page |

|--------|---------------------------------------------------------------------------|------|

| 1      | Two Unicast LRU Replacement Schemes in a Networked Cache                  | 20   |

| 2      | Fast-LRU Replacement with Multicast Support                               | 22   |

| 3      | An $8 \times 8$ Mesh Network for a Large Scale Cache System               | 28   |

| 4      | XYX Routing Algorithm                                                     | 29   |

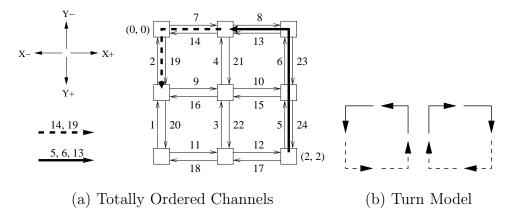

| 5      | Deadlock Freedom in XYX Routing                                           | 30   |

| 6      | Domain-Specific Development of Network Designs for Large Cache<br>Systems | 31   |

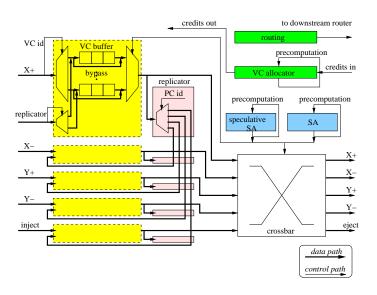

| 7      | Single-Cycle Router Architecture with Multicast Support                   | 33   |

| 8      | Latency Distributions of L2 Cache Accesses in the Unicast LRU Environment | 40   |

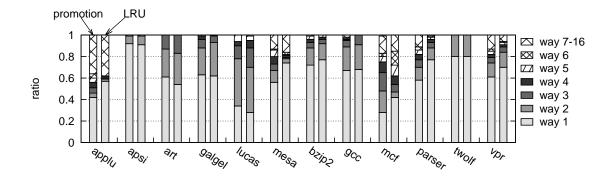

| 9      | Way Distributions of Promotion and LRU                                    | 40   |

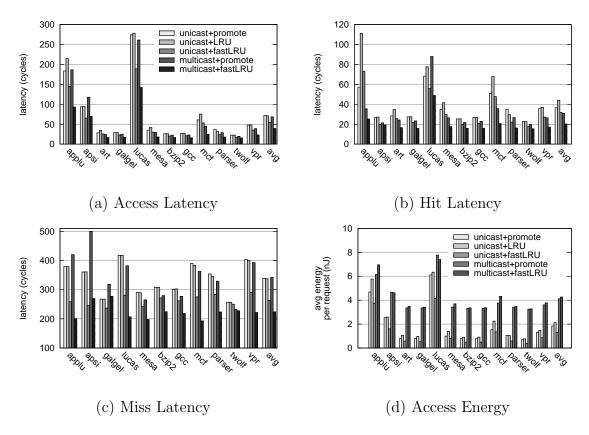

| 10     | L2 Cache Access Latency and Energy Comparison                             | 41   |

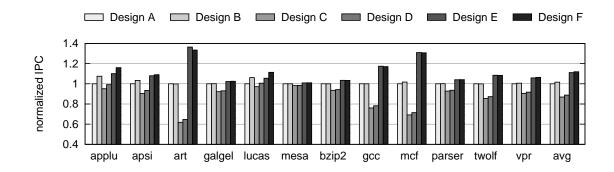

| 11     | Performance Comparison in Different Designs                               | 44   |

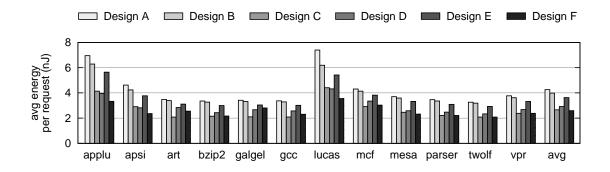

| 12     | Energy Comparison in Different Designs                                    | 45   |

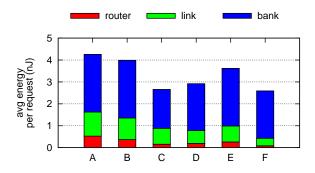

| 13     | Energy Breakdown in Different Designs                                     | 45   |

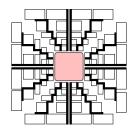

| 14     | Spike-5 Halo Network Design for L2 Cache                                  | 47   |

| 15     | Performance Gain Estimation Using Analytical Model                        | 48   |

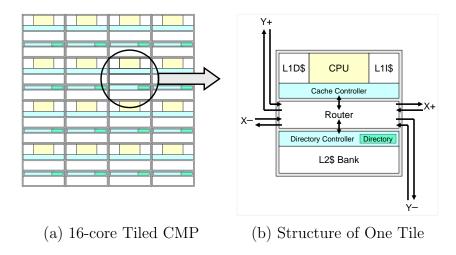

| 16     | Tiled CMP with On-Chip Networks                                           | 51   |

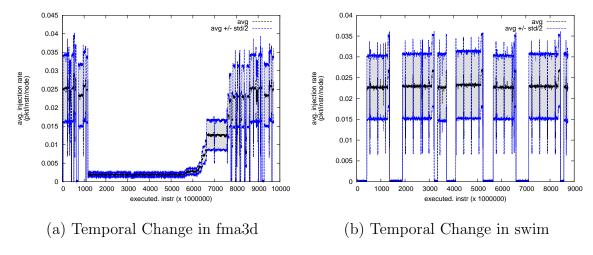

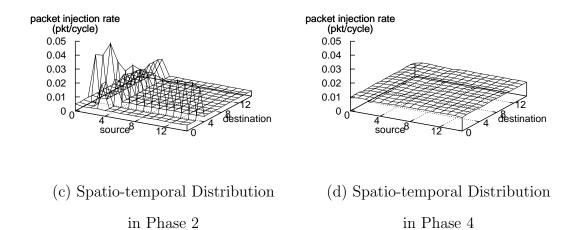

| 17     | Spatio-Temporal Traffic Change in 16-Core                                 | 59   |

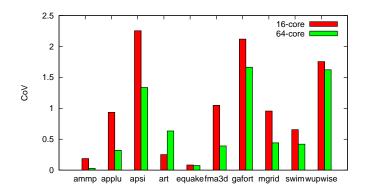

| 18     | Temporal Variation Summary                                                | 60   |

| FIGURI | E                                                                       | Page |

|--------|-------------------------------------------------------------------------|------|

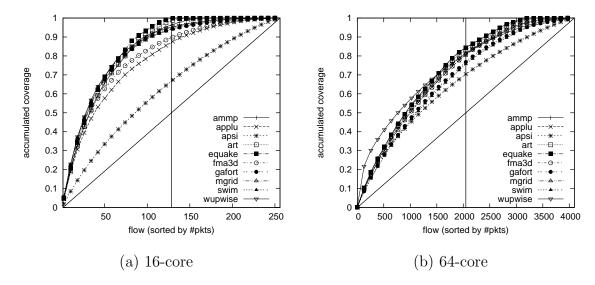

| 19     | Flow Dominancy Analysis                                                 | 61   |

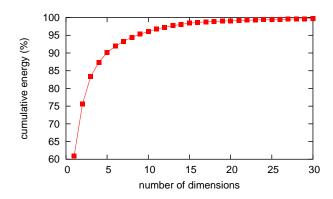

| 20     | Dimension Reduction in Flow Feature Vector                              | 62   |

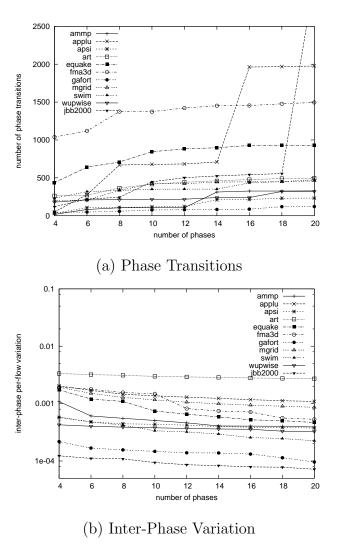

| 21     | Clustering Result Comparison for Different Number of Phases             | 64   |

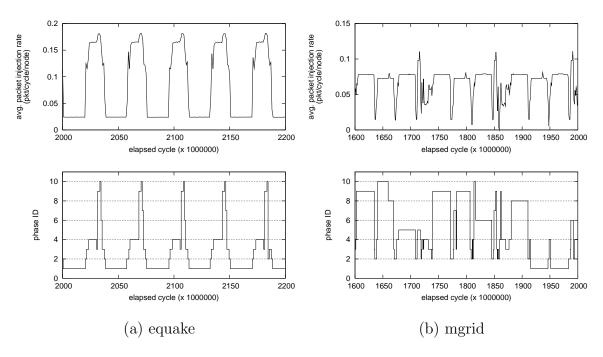

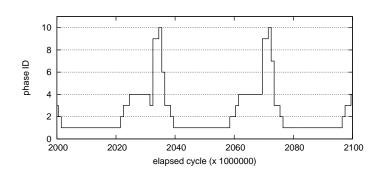

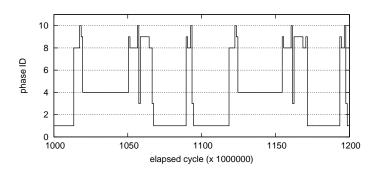

| 22     | Phase Classification Toward Time-Varying Analysis                       | 65   |

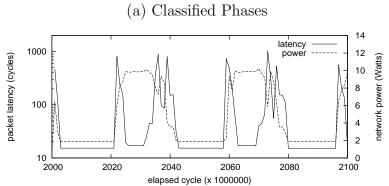

| 23     | Relation between Phases and Performance Behaviors in $\it equake$       | 68   |

| 24     | Relation between Phases and Performance Behaviors in $swim$             | 69   |

| 25     | Time-Varying Packet Latency and Power Consumption in Different Networks | 70   |

| 26     | Performance Comparison in Different Topologies                          | 71   |

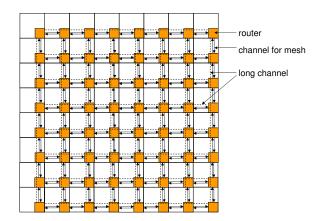

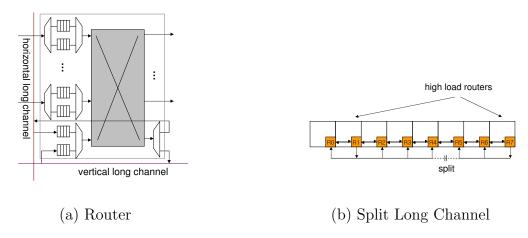

| 27     | Mesh Network with Long Channels                                         | 72   |

| 28     | Hybrid Network Architecture                                             | 73   |

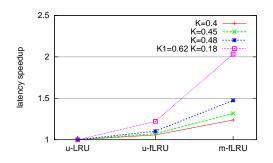

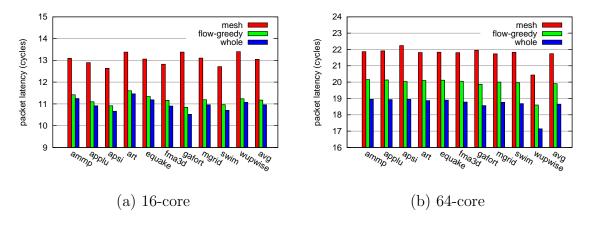

| 29     | Performance for Mesh with Reconfigured Long Channels                    | 75   |

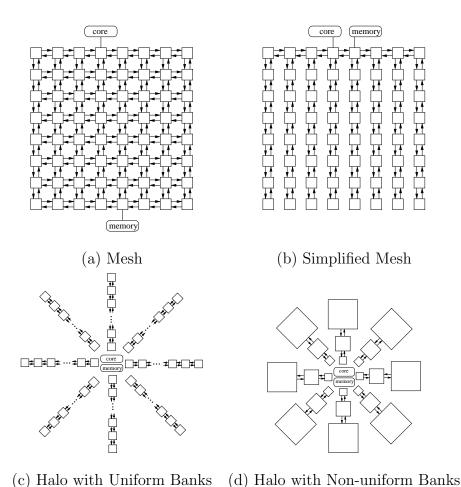

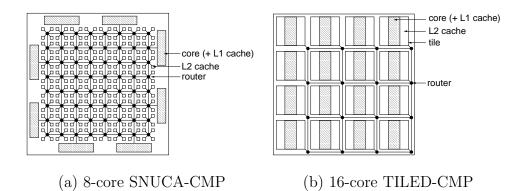

| 30     | On-Chip Networks in CMPs                                                | 80   |

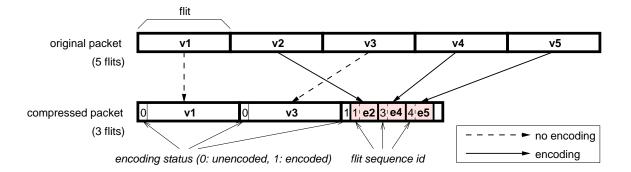

| 31     | Packet Compression Example                                              | 83   |

| 32     | Shared Table Structure                                                  | 87   |

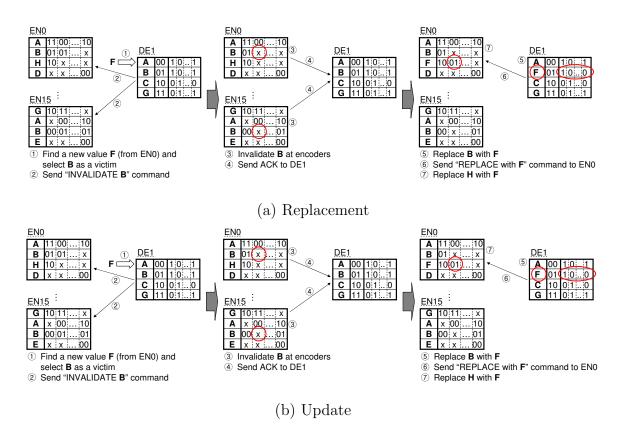

| 33     | Shared Table Management                                                 | 88   |

| 34     | Area Comparison for Private and Shared Tables                           | 90   |

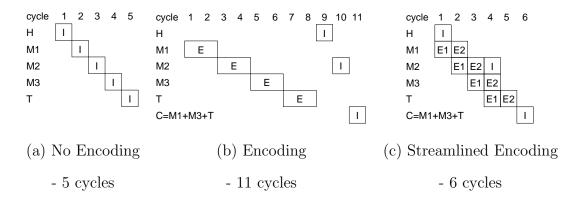

| 35     | Streamlined Encoding Example                                            | 91   |

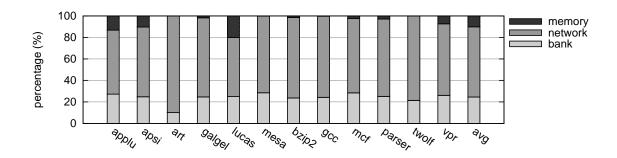

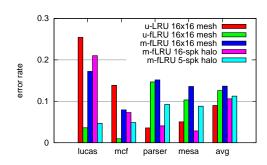

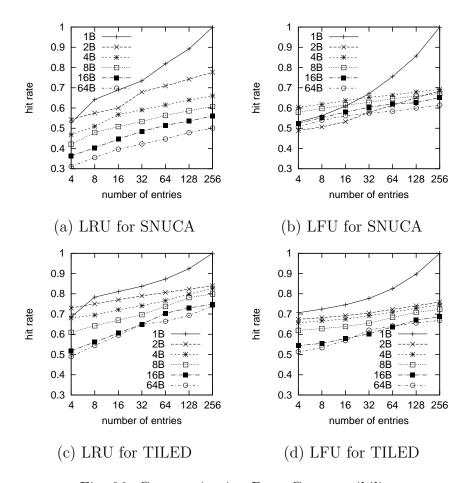

| 36     | Communication Data Compressibility                                      | 98   |

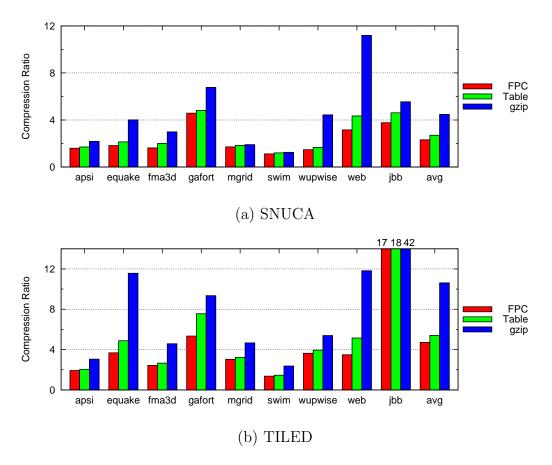

| 37     | Compression Ratios                                                      | 99   |

| 38     | Value Spatial Distribution                                              | 100  |

| 39     | Data Compression: Latency Comparison                                    | 101  |

| FIGURE |                                                     | Page |

|--------|-----------------------------------------------------|------|

| 40     | Behavior of Dynamic Compression Management          | 103  |

| 41     | Data Compression: Waiting Time in Router Components | 104  |

| 42     | Data Compression: Energy Comparison                 | 105  |

| 43     | Data Compression: Traffic and Energy Relationship   | 106  |

| 44     | Data Compression: Network Comparison for TILED-CMP  | 107  |

## CHAPTER I

#### INTRODUCTION

The advancement of microprocessors is driven by Moore's Law, which predicts that the number of transistors on microprocessors doubles every two years. The substantial performance improvement for the past decade has been mined from increasing clock frequency, which currently almost stopped due to power consumption constraint. In these scaling trends, current microprocessor designs attain performance from parallel processing by integrating a large number of cores in a single die.

Achieving performance for multi-core or many-core has embarked on a design paradigm shift from computation-centric to communication-centric aspects. Future chip multiprocessors (CMPs) that have tens or hundreds of cores and multi-megabyte on-chip caches will require a communication substrate interconnecting components and coordinating data exchange among them. Without well-designed interconnect, the multi-core system will lose the design merits and deteriorate performance advantage.

## A. Networks-on-Chip

Traditional interconnects such as shared buses and dedicated wiring suffer from scalability as well as increase complexity of chip designs [1, 2]. Networks-on-Chip (NoC) is a proposal to use a switched network by abstracting a communication unit as a packet. NoC is used for a communication architecture in next-generation chips such as Intel Teraflop 80-core [3], Tilera 64-core [4], RAW [5], and TRIPS [6].

Though NoC is conceptually similar to the chip-to-chip network, NoC has dif-

This dissertation follows the style of IEEE Transactions on Computers.

ferent characteristics for chip-wide communication support. First, the end-to-end latency is ultra-low, taking a few clock cycles per hop. Routers and links share a high frequency clock with processors. Next, abundant metal resources enable wide-channel links and thus achieve high-bandwidth. Increasing metal layers in future technology may provide another opportunity for high-bandwidth networks. Finally, the cost of NoC is constrained in terms of power and area. In fact, NoC power consumption is significant at 28% of the tile power in Teraflop [3] and 36% of the total chip power in 16-tile RAW chip [5]. In the operand network of TRIPS, the router takes up 10% of the tile area mostly due to FIFO buffers [7].

The design of a low-latency, high-bandwidth, low-power, and area-efficient NoC can be extremely challenging, because different objectives conflict with each other. Generally, high-bandwidth networks achieve low latency by using much resource but tend to consume more power and take more area. In other words, NoC design must be carefully considered for better performance with power and area envelopes of a chip. NoC must be co-designed with other chip components and its design must be evaluated in a total system perspective. Application-driven workload is essential to compare different designs and show the NoC effect on the system. Variability such as injection rates and traffic patterns in real applications also provides excellent opportunities for implementing adaptive hardware in NoC.

#### B. Dissertation Contributions

This section describes the research contributions of the dissertation. Although each contribution targets a differently configured system, the developed techniques easily adapt to other designs.

## 1. NoC Designs for Large Cache Systems

Chapter III develops a domain-specific NoC design in a large-scale cache systems. Taking a network-oriented approach to a last-level cache design reduces a growing wire delay in a cache access time [8]. The monolithic cache is broken into multiple banks that can be accessed at different latencies through an NoC. NoC plays a key role in managing cache operations as well as determining the cache access latency. However, using a general-purpose NoC to a specific problem domain may cause large network delay and under-utilization of network resources, since the network is not optimized for the domain. Reducing both latency and resource of the network requires re-examination of NoC design, particularly how NoC interacts with the rest of the multi-bank cache architecture.

The primary contribution includes: (i) a single-cycle router architecture with multicast support as the basic building block of the interconnection networks; (ii) Fast-LRU replacement that can reduce the network latency; (iii) appropriate deadlock-free XYX routing algorithm that requires no horizontal links in a mesh except the first row to save area and power; (iv) a new network topology, called a *halo* network, where the MRU banks are of the same distance from the core; and (v) a halo network with non-uniform sized banks, thus reducing the wasted area on the processor die.

## 2. Communication Characterization Towards Reconfigurable NoCs

For NoCs towards CMPs, characterizing communication in multi-threaded applications can bring many new optimization opportunities. Assessment of real application behavior in NoC is still in nascent stage. There are no standard benchmarks for NoC study, and even previous work depends on results of synthetic traffic from outdated applications. Therefore, understanding communication in applications is a first step to design efficient interconnects. Scientific and commercial workloads are good candidates for CMP applications. Chapter IV presents a characterization method in OpenMP-style parallel applications. The OpenMP programming model achieves performance enhancement mainly by exploring parallelism in a loop. Furthermore, every loop iteration exhibits quite consistent behavior. Communication behavior is understood as multiple phases, where each phase represents a unique spatio-temporal property. This method can capture time-varying traffic variation of one loop iteration in the same application. We explore the recurring behavior of loop execution and use this property to reconfigure an interconnect.

We build a traffic model for the fixed interval of executed instructions. We construct a traffic matrix, where each element has the amount of traffic for one flow, and each row and column specifies source and destination address, respectively. The matrix is regarded as a feature vector for grouping similar intervals as a phase. We use a machine learning technique that clusters similar intervals and classifies each interval as a phase. After this step, one loop iteration behavior is summarized as a sequence of phases.

In each phase, we identify hot flows or hot sources that require a large volume of communications. Additionally, we identify long-distance communications based on a physical distance between a source and a destination. We use this information in a hybrid network, which has a well-designed topology with multiple long channels to overcome limitation of the physical topology. These long channels are dynamically reconfigured to reduce the packet latency by allocating each of them to a router and hence providing an express path.

## 3. Adaptive Data Compression in NoCs

In cache traffic for cache-coherent multi-core systems, a packet data that includes a long cache line exhibits frequent bit patterns [9, 10, 11, 12]. Exploiting this property enables a long packet payload to be compressed (encoded) as a short index, hence reducing a packet size. Packet compression increases the designed network bandwidth at runtime, and reduces power consumption by resulting in less switching activity in routers and links.

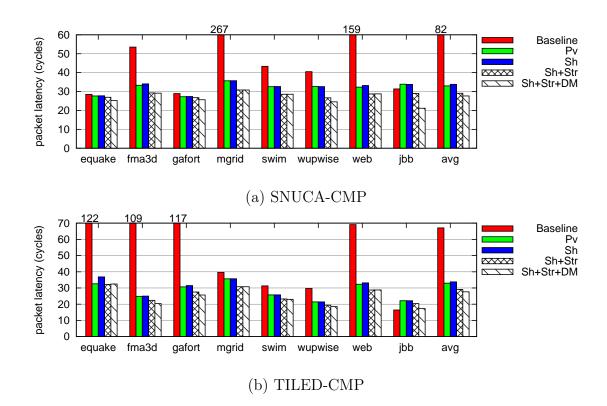

Chapter V presents the main contributions as co-designing compression architecture with NoC architecture to enhance performance and power consumption with a small cost of the compression hardware. First, we propose the shared table scheme, which stores identical values into a single entry from different sources or destinations and removes the network-size dependence. We also present the efficient table management protocol for consistency. Next, we propose performance improvement schemes. Streamlined encoding reduces the encoding latency by overlapping encoding with flit injection. Finally, we present the dynamic compression management that compresses packets on-demand in varying workloads to maximize the performance.

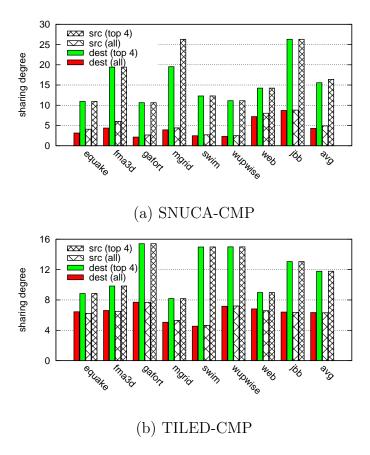

We identify 69% compressibility of cache traffic in a suite of scientific and commercial benchmarks for two CMP designs; 8-core with NUCA and 16-core tiled. Additionally, we observe that a large portion of communication data is shared among different flows. Finally, the detailed simulation results show that data compression improves the latency by 55% and saves the energy by 12%. Furthermore, dynamic compression management achieves 63% latency improvement with 7% energy saving.

## C. Dissertation Organization

This dissertation is organized as follows. Chapter II presents architectural components for NoC and examines exploratory NoC-enabled chips. Chapter III presents NoC design consideration in wire-delay dominated cache systems. Chapter IV presents traffic characterization methods with its use for long-link reconfiguration. Chapter V develops data compression for two CMP systems, followed by the conclusion of the research in Chapter VI.

## CHAPTER II

## BACKGROUND: NETWORKS-ON-CHIP

## A. NoC Building Blocks

## 1. Topology

The network topology determines the various characteristics of the network, such as the average hop count and bisection bandwidth. Because every topology needs to be laid out on 2D die, regular networks such as mesh, torus, or ring are mostly adopted for NoCs. Ring is a simple topology for moderately-sized networks, but the linear hop count dependency and poor bandwidth support make it undesirable for large networks. Torus provides the higher bisection bandwidth and the smaller average hop count than mesh, but power dissipation goes up to almost two times of mesh due to the long links [13]. High radix topology networks which have express channels, such as butterfly [14] or fat trees, require high wiring resource and increase router complexity for a large number of ports. Moreover, it is shown that no single network provides optimal performance across different traffic patterns [15].

## 2. Router

The router design plays a vital role in switched networks. The pipelined router uses wormhole switching for small buffer requirement, virtual-channels (VCs) to alleviate Head-Of-Line (HOL) blocking, and credit-based flow control. The pipeline stages of a conventional router consist of route computation (RC), virtual channel allocation (VA), switch allocation (SA), and switch traversal (ST) [16]. First, RC stage directs a packet to the proper output port of the router by looking up the packet destination address. Next, VA stage allocates one available VC of the downstream router deter-

mined by RC. SA stage arbitrates input and output ports of the crossbar, and then successfully granted flits traverse the crossbar (ST). After ejecting from the router, the flit crosses over a link to the next router (LT). Therefore, for each hop, head flits require four cycles (RC+VA+SA+ST), while middle/tail flits require two cycles (SA+ST).

Even though an aggressive design can merge adjacent operations into a single-cycle operation, this dependency still exists. Moreover, recent results show that the operating clock cycle for the router is 12 fanout-of-four (FO4) delays [17], which is close to the optimal pipeline delay of the modern superscalar processor [18]. To minimize and break the serial dependency, we use the following techniques.

- Lookahead routing: The routing decision is made one hop ahead of the current router. It eliminates the routing delay by removing the serial dependency between routing and VC allocation like the SGI SPIDER chip [19]. The routing outcome is stored in a flit and hence used to allocate VC or the switch output port in the next router.

- Buffer bypassing: If the input buffer designated for the VC is empty, a flit directly goes to the crossbar or the VC allocator (if it is a head flit) through a bypass path without being stored at the tail entry of the input buffer. It can remove the delay for the read and write operations of buffer.

- Speculative switch allocation: Switch allocation is performed speculatively at the same instance of VC allocation so that a head flit enters into the crossbar right after VC allocation [20]. This speculative switch allocator is only applied to head flits and cannot be granted if the normal switch allocator reserves all the available ports. In this way both VC and switch allocations can be performed at the same cycle.

• Arbitration precomputation: Arbitration of competing requests for a VC or a switch port is precomputed and stored for the next arbitration after one output VC in VC allocator or input/output port of the crossbar in switch allocator is granted [17]. The grant signals of the arbiter are generated as the product of the precomputed grant enable signals and incoming arbitration requests. Hence arbitration outcomes are prepared one cycle ahead and latched for the next cycle.

All these techniques except lookahead routing work well in a lightly loaded network where the possible cases for each scheme occur frequently. Our router design maximizes these chances and eventually delivers a flit in a single clock cycle by reducing the critical path in a traditional pipelined router.

Router buffers are instrumental in the NoC design, because the buffer space takes up silicon area and dissipates the significant portion of the router power. Though wormhole switching makes a buffer size less than a packet size, it lowers down buffer utilization. Deadlock avoidance routing algorithms that separate flows into different VCs also incur imbalance of VC utilization for some traffic patterns. Sharing buffer space [21] and controlling the number of VCs [22] reduce expensive cost of the buffer.

## 3. Link

Links that connect neighbor routers use parallel global wires. Compared with small pin bandwidth limitation in off-chip networks, multi-layer fabrication processes enable the use of wide links in on-chip networks. However, high wiring density will give less space for logic such as cores or caches. Because long wires are implemented as buffered wires with repeaters and latches, the global long wires are difficult to be routed over logic [23]. Over-providing metals to the links for an on-chip network may

easily exhaust top-level metal resources, hence making it hard to route and place power/ground interconnects.

The number  $(h_{opt})$  and sizing  $(k_{opt})$  of repeaters and one segment delay  $(\tau_{opt})$  are determined as following RC equations [24].

$$h_{opt} = \sqrt{\frac{2r_s(c_0 + c_p)}{r_w c_w}} \qquad k_{opt} = \sqrt{\frac{r_s c_w}{r_w c_0}} \qquad \tau_{opt} = 2\sqrt{r_s c_0 r_w c_w} (1 + \sqrt{\frac{1}{2}(1 + \frac{c_p}{c_0})}) \quad (2.1)$$

where  $c_0$ ,  $c_p$ , and  $r_s$  are the input capacitance, the output capacitance, and the output resistance of the minimum size repeater, and  $c_w$  and  $r_w$  are the unit length capacitance and resistance of the wire. Then, the delay of uniformly buffered wire for a given length L is  $\log 2 \times \tau_{opt} \times \frac{L}{h_{opt}}$ . Also power consumption of a buffered wire comes from charging and discharging both wire and repeater capacitances. For  $V_{dd}$  supply voltage, unit length for a buffered wire consumes the following power  $(E_w)$ .

$$E_w = 0.5V_{dd}^2 \left(\frac{k_{opt}}{h_{ont}}(c_0 + c_p) + c_s + c_i\right)$$

(2.2)

We model the wire capacitance  $(c_w)$  into two parts: wire-substrate capacitance  $(c_s)$  and inter-wire coupling capacitance  $(c_i)$ .

We obtain the wire property from ITRS [2] and PTM model [25], and the repeater property from [26]. Table I shows interconnect property from 65nm to 22nm. Table II presents delay, power, and area of global wire for each technology generation.

## B. NoC Applications

Several forms of NoC designs have been proposed to interconnect processing components on a die. *Tile networks* have high scalability to many-core designs because an identical tile having a core and a SRAM memory can be replicated easily [3, 4]. *Cache networks* are another trend in a large-scale L2 cache design to mitigate increased wire

Table I. Global Interconnect Characteristic

| Year                                | 2007            | 2010            | 2013            | 2016            |

|-------------------------------------|-----------------|-----------------|-----------------|-----------------|

| Technology                          | $65\mathrm{nm}$ | $45\mathrm{nm}$ | $32\mathrm{nm}$ | $22\mathrm{nm}$ |

| supply voltage, Vdd (V)             | 1.1             | 1.0             | 0.9             | 0.8             |

| clock freq. (GHz)                   | 6.73            | 11.51           | 19.3            | 28.8            |

| pitch (nm)                          | 210             | 135             | 96              | 66              |

| aspect ratio                        | 2.3             | 2.4             | 2.5             | 2.6             |

| width (nm)                          | 105             | 68              | 48              | 33              |

| spacing (nm)                        | 105             | 68              | 48              | 33              |

| thickness (nm)                      | 241.5           | 163.2           | 120             | 85.8            |

| height(ILD) (nm)                    | 241.5           | 163.2           | 120             | 85.8            |

| dielectric permittivity             | 2.85            | 2.65            | 2.25            | 2.15            |

| Rw (Ohm/mm)                         | 867.593         | 1982.41         | 3819.444        | 7770.007        |

| $c_s \text{ (fF/mm)}$               | 21.955          | 19.569          | 15.948          | 14.647          |

| $c_i 	ext{ (fF/mm)}$                | 81.354          | 79.297          | 70.425          | 70.251          |

| $c_w = 2c_s + 2c_i \text{ (fF/mm)}$ | 206.618         | 197.732         | 172.746         | 169.796         |

delay and share a large capacity effectively [27, 28]. Bypass networks are intended to connect multiple ALUs to overcome increased complexity and delay of bypass path in microprocessors [5, 6]. Communication in tile networks or cache networks are cache traffic that transports cache lines and manages coherence in shared data, while short operand traffic moves in bypass networks.

Table III shows the main NoC features in recent designs. RAW is the proposal to schedule operands in ALU networks and overcome the wire-delay problem for superscalar processors [5]. A mesh network connecting 16 tiles has two physical networks (static and dynamic). The static network controls operands among distributed ALUs, and the dynamic network transports all other traffic such as memory, interrupts, and user-level message passing codes. TRIPS is a distributed processor consisting of multiple tiles connected through two networks [6]. The L2 cache consists of 24 network tiles and 16 memory tiles in on-chip network (OCN), while a processor has 16 execution tiles and other 9 tiles in operand network (OPN). TRIPS prototype shows that an OPN router takes up a significant chip area (10% of the execution tile and 14% of

Table II. Global Interconnect Delay/Power

| Year                              | 2007            | 2010            | 2013            | 2016    |

|-----------------------------------|-----------------|-----------------|-----------------|---------|

| Technology                        | $65\mathrm{nm}$ | $45\mathrm{nm}$ | $32\mathrm{nm}$ | 22nm    |

| $h_{opt} \text{ (mm)}$            | 0.491           | 0.318           | 0.268           | 0.190   |

| $k_{opt}$                         | 47.113          | 38.248          | 36.794          | 36.536  |

| one segment wire delay (ps)       | 59.175          | 58.086          | 66.528          | 66.528  |

| unit length delay (ps/mm)         | 20.542          | 182.750         | 247.896         | 350.543 |

| unit length delay (FO4/mm)        | 5.151           | 11.281          | 21.519          | 44.260  |

| unit length dynamic power (mW/mm) | 2.045           | 1.513           | 1.119           | 0.869   |

| unit length leakage power (uW/mm) | 1.441           | 1.625           | 1.777           | 2.338   |

| unit length sc power (mW/mm)      | 0.331           | 0.257           | 0.214           | 0.184   |

| unit length total power (mW/mm)   | 2.378           | 1.771           | 1.336           | 1.056   |

Table III. NoC Design Parameters in Existing CMPs

| Architectures | Topology     | Router           | Link (bits)    | Routing        | Flow control | Clock  |

|---------------|--------------|------------------|----------------|----------------|--------------|--------|

| RAW           | 2 4x4 meshes | 3/5-stage, no VC | 256/32         | static         | credit-based | 425MHz |

| TRIPS OPN     | 5x5 mesh     | 1-stage, no VC   | 142            | static (YX)    | on-off       | 400MHz |

| TRIPS OCN     | 4x10 mesh    | 1-stage, no VC   | 138            | static (YX)    | credit-based | 400MHz |

| Tilera chip   | 5 8x8 meshes | 1/2-stage, no VC | 32 (per mesh)  | static         | credit-based | 1GHz   |

| Cell EIB      | 4 rings      | -                | 128 (per ring) | minimal        | PCS          | 1.6GHz |

| Teraflop      | 8x10 mesh    | 5-stage, 2 VCs   | 39             | source routing | on-off       | 5GHz   |

| UltraSparc T1 | crossbar     | -                | 103            | -              | -            | 1.2GHz |

a processor core) mainly because the router has 2.2 kilobits storage for buffers [7].

Tile processor recently announced by Tilera has 5 physical 2D mesh networks to connect 64 cores [4]. The five networks are user dynamic network (UDN), I/O dynamic network (IDN), static network (STN), memory dynamic network (MDN), and tile dynamic network (TDN). The rationale behind this design comes from the benefit of logical networks from independent physical networks, which allows for privilege isolation of traffic, independent flow control, and traffic priotization. Cheap wiring due to multi-layer metal resources makes this realization cost effectively free, while inexpensive buffering (1.1% of tile area for each network) is achieved by excluding use of virtual channels in a router.

Cell processor uses Cell Element Interconnect Bus (EIB) as an on-chip intercon-

nect [29]. In four 16B ring-networks for data bus, two networks are dedicated for data transport of one direction. Cell has an additional shared command bus structured as a tree and a star-like central data bus arbiter. Analytical characterization of EIB shows that the command phase, which coordinates connection-oriented end-to-end transfers, consumes almost 50% of the total zero-load packet latency and that the sustainable network throughput is reduced by a single element causing hot spot or circuit switching.

The Intel Teraflops Processor architecture contains 80 tiles arranged in 2D array and connected by a mesh network [3]. Mesh network provides two virtual channels for instruction and data to prevent short instruction packets from being mixed with long data packets. Experimental results in 65-nm process technology fabrication shows that a 5-port router requires 17% of the total  $3-mm^2$  tile and its power dissipation is 28% of the tile power. Because this significant network power consumption does not meet the chip power envelope (less than 10% of the total chip power), they concluded that pipeline reduction techniques such as speculation and bypassing in the router are not desirable and fine-grained power management schemes are necessary.

Sun's 32-way Multithreaded Sparc Processor has a single crossbar for communication among Sparc pipes, L2 cache banks, and I/O subsystem [30]. Crossbar interconnect provides 200GB/s bandwidth and queues up to 96 transactions each way. Global arbitration based on age-based priority scheme enables memory ordering for the machine <sup>1</sup>.

$<sup>^{1}</sup>$ In Table III, link width is calculated from a 200GB/s bandwidth crossbar and 13 ports (8 Sparc pipes, 4 L2 cache banks, 1 I/O).

## CHAPTER III

## NOC DESIGNS FOR LARGE CACHE SYSTEMS

#### A. Overview

With the current rate of technology advancement, increasing wire delays in modern microprocessor designs [31, 1] leads to various techniques to minimize the impact of slow on-chip communication. Typically, on-chip communication has been conducted via shared buses or dedicated wires. Dedicated wires can provide the best customization to applications. However, these interconnects are influenced by various parasitic capacitance and crosstalk from adjacent wires that cannot be predicted until the actual layout and routing are performed [32]. For shared buses, a single communication exclusively uses the whole bus even if multiple communications could operate simultaneously on different parts of the bus. Using global buses is not a scalable solution because the bus bandwidth may become a major bottleneck as the number of chip components increases.

Another way to design an on-chip communication is with a switched network. All the components are connected to the network that routes packets among them, which has the advantages of structure, performance, and modularity [33, 34, 35, 36]. There has been much research on the architectures of future chip multiprocessor (CMP) designs [37, 6, 38] using switched networks for better scalability and resource sharing. Furthermore, these networks have been adopted to overcome wire delay in specific domains such as large scale cache designs [8, 27].

The regular topologies, such as meshes and tori, have been used in on-chip network designs. However, a general-purpose network with regularly distributed network resources can cause problems in the following two cases: under-provisioning and over-provisioning of network resources. Under-provisioning network resources below com-

munication requirement causes poor performance. On the other hand, when network resources are over-provisioned, underutilization of the network resources occurs and large network delays are caused by the increased network size. Furthermore, over-providing network resources results in wasting the chip area. Therefore, it is critical to design an optimal network for a specific domain by breaking the regularity of the interconnection network. It is also important to exploit the potential parallelism of the interconnection networks in the problem domain. Achieving these two goals requires specific knowledge of both interconnection networks and the application domain.

In some large scale cache designs [8, 27], 2D mesh networks have been adopted to interconnect small cache banks to overcome wire delays. For example, in Non-Uniform Cache Architectures (NUCAs) [8], the cache is broken into multiple banks that can be accessed at different latencies through an on-chip network. D-NUCA (Dynamic NUCA) allows cache blocks to migrate among cache banks in such a way that recently accessed cache blocks can move towards the core, which helps reduce the average cache access time. However, the network delay is still a dominant portion of the cache access time. A 16MB D-NUCA using a 16×16 mesh network demonstrated an average access time of 17 cycles without network contention while the bank access time is only 3 cycles. The worst case is when the requested cache block is not found in the L2 cache. In this case, all the cache banks in the bank set <sup>1</sup> must be checked sequentially before memory is accessed. In addition, 20% of the total links in a mesh network are never used, while the network occupies 41% of the total cache area.

The main purpose of this research is to investigate the design in the interconnection framework and, particularly, how it interacts with the rest of the multi-bank cache architecture. The research proceeds as follows: first, we propose a single-cycle

<sup>&</sup>lt;sup>1</sup>To implement a set associative cache in a networked cache system, a set is distributed across multiple banks. This is named a bank set [8].

wormhole router architecture that supports multicast efficiently. Because multicast can significantly reduce large network delay, it decreases the total cache access time dramatically. Unlike the existing multicast routers proposed before, the proposed router takes only one cycle in each hop and does not require any extra storage. It becomes the basic building block of the interconnection network design for the proposed large scale cache systems.

Next, we present Fast-LRU replacement in which cache replacement occurs concurrently with tag-matching. We investigate detailed operations in the network including tag-matching, replacement, and placement for a cache hit and miss. Fast-LRU can be further improved by parallelizing required operations with multicast support. The proposed networked cache system performs best when it uses Multicast Fast-LRU replacement.

Finally, we propose a deadlock-free XYX routing algorithm and a new halo network topology to reduce the cache access time and minimize the number of links in the cache system. We discuss how the L2 cache layout on the processor die can help reduce the cache access time. In the XYX routing algorithm, the normal XY routing is used for delivering cache requests from the core to the banks while the replies from each bank to the core are transfered in the Y direction first. Compared with XY routing, the XYX routing algorithm saves most horizontal links in a mesh network. Removing horizontal links leads to the removal of all the associated input buffers and the simplification of both arbiter and crossbar designs. Incorporating small radix routers also results in short pipeline stage latency as well as small chip area. With the halo topology, all the closest banks of each column in the mesh network are placed in the same one-hop distance from the core.

Simulation results with SPEC2000 benchmarks show that the networked cache system with all of the proposed techniques improves the IPC by 38% and uses only

12% of the interconnection area of the D-NUCA system with Multicast Promotion replacement [8]. Specifically, Multicast Fast-LRU replacement improves the IPC by 20% in the mesh network and the halo network further improves it by 18%. We also present analytical models for different communication network designs, which further verifies the performance improvement shown through simulation.

## B. Related Work

Several studies explore the large on-chip cache designs to overcome the wire delay problem. NUCA [8] shows that the traditional large cache based on partitioned subbanking is ineffective because its access latency is determined by the slowest (i.e. farthest from the core) subbank. One of the proposed designs, Static NUCA (S-NUCA), uses dedicated wires to each bank and incurs significant area overhead. In another Dynamic NUCA (D-NUCA) design that organizes banks with a switched network, they exploited cache block migration, partial-tag search for early miss detection, and multicast for fast bank access. NuRAPID [39], which accesses tag and data sequentially, decouples each placement in separate storages. This flexible management increases energy-efficiency in NUCA by filtering most misses from only tagarray accesses. However, it has an overhead to maintain pointer structures in the existing bank architecture. TLC (Transmission Line Caches) [40] uses communication medium for banks as a fast transmission line having short inductive-capacitance (LC) delays. Although transmission line can provide express channels, its application is limited due to the high area requirement. Heterogeneous interconnects are used to improve performance for NUCA such as sending critical address bits on fast L-wires for early bank look-up [41]. Wire and router designs are considered in the cache model used in CACTI 6.0 [42]. Additionally, some of those designs were examined for cache sharing environment in CMPs [27, 43, 28].

An on-chip network that enables low-latency from its high bandwidth is used in partitioned architectures such as CMPs [37, 6] and Networks-on-Chips (NoCs) [33, 34, 35, 36]. A few research showed that the network design must be tailored to the communication behavior of applications running on the network for resource saving and performance improvement. A mesh network was optimized to each parallel application by analyzing its requirement of both links and routers [44]. Instead of assigning buffering resources uniformly in a 2D mesh network, the allocation of different buffering size in each channel reduces the implementation cost and increases performance in the NoC design of media applications [45].

Router design directly impacts the performance of the on-chip network. It is difficult to achieve one-cycle flit delivery in a conventional pipelined router due to dependencies between pipeline stages. Speculative switch allocation breaks the dependency chain between virtual channel allocation and switch allocation [20]. A recently proposed low-latency router delivers a flit in a single cycle [17]. It eliminates control overheads (routing and arbitration logic) from the critical path by input buffer bypassing, lookahead routing, and pre-computation of arbitration decisions.

To support one-to-many communication primitives, multicast routers have been designed especially for multistage networks and 2D mesh/hypercube topologies [46, 47]. Due to the nature of multicast, we need to provide extra storage to hold packets and a deadlock prevention mechanism. In a chip-to-chip domain, the central-buffer-based design showed better performance over the input-buffer-based design, because the queuing capability of the central buffer is superior for unicast packets [46]. However, the additional storage is not desirable in the on-chip domain where area budget is very tight. There are two ways to prevent deadlock: deadlock avoidance/recovery and complete packet buffering. While deadlock avoidance routing causes inefficient resource utilization and deadlock recovery mechanisms are highly complex, complete

buffering requires large buffer storage. Therefore, the main challenge of multicast support in an on-chip network is to prevent deadlock without extra storage requirements.

## C. Designing Communication for Cache Architecture

In this section, we explain communication operations in mesh-connected banks to manage blocks for LRU replacement. We present Fast-LRU replacement that merges tag matching and replacement operations in a single packet. During the course of this work, fast LRU replacement is extended with a multicast network. Finally, we develop an analytical performance model for different communication designs.

## 1. Fast-LRU Replacement

In this section, we propose Fast-LRU replacement with multicast to reduce the long latency of the LRU replacement scheme after examining its optimization with unicast.

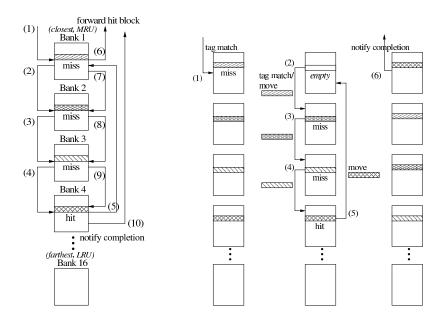

We briefly explain cache operations in D-NUCA [8]. As shown in Figure 1 (a), the cache is broken into multiple banks that can be accessed through a mesh network. One column of the mesh represents a set of a set-associative cache, which is statically determined by the low-order bits of the block address. Cache blocks in a set are spread across multiple banks in the column. Each set distributed in a column is called a bank set. Thus, the cache system searches for a block by first selecting the column, selecting the set within the column using direct-mapping, and finally performing a tag-match on distributed blocks. Note that each way has a different network latency depending on the distance from the core. Although a bank set can be distributed on every column to give approximately equal access time across all bank sets, we do not consider this configuration due to the larger hop count.

- (a) LRU Replacement

- (b) Fast-LRU Replacement

Fig. 1. Two Unicast LRU Replacement Schemes in a Networked Cache

To reduce the average access time, we should place frequently used data in the banks closer to the core, which can be achieved with LRU replacement. The LRU generates 14% higher cache hit rate than Promotion [8], which swaps the hit block with a block in the bank that is next closest to the core. Therefore, it makes the first way and the last way be placed on the closest (MRU) bank and the farthest (LRU) bank, respectively. However, maintaining the LRU order in a bank set requires a large overhead because it incurs many swaps of blocks between banks.

Figure 1 (a) shows the LRU replacement policy by depicting the required communications among banks. Assuming that a data request is a hit in Bank 4, the request traverses from Bank 1 to Bank 4 ((1)  $\sim$  (4)). Then the hit block is sent to Bank 1 ((5)), resulting in the corresponding blocks in Bank 1, 2, and 3 being moved to Bank 2, 3, and 4 ((7)  $\sim$  (9)), respectively. In this example, the total communication

time is 21 hops including the notification of completion; the initial tag-match time to find a hit bank is 7 (1+2+2+2) hops and the remaining part is 14 (4+2+2+2+4) hops. It is clear that the cache hit latency can be decomposed into two parts—tagmatch and move (replace) operations. Therefore, the total communication time for block movement after finding a hit can easily exceed the initial tag-match time. A cache miss needs tag-match along all banks and a new block placement to the MRU bank incurs multiple block movements.

In Figure 1 (b), the proposed Fast-LRU replacement allows the tag-match operation to overlap with the replace operation. If there is a miss in a bank, the corresponding block in the bank is evicted and immediately transferred to the next bank with the data request  $((1) \sim (4))$ . Unless the request is a hit in the MRU bank, the corresponding block in the bank is pushed to the next bank consecutively until the final (LRU) bank. Once there is a hit in a bank, that block is transferred to the MRU bank where its corresponding frame is already empty ((5)). If all the banks generate misses, the request is forwarded to the off-chip memory, and the requested memory block is read. Then this new block is stored in the MRU bank and sent to the core. Since the invariant property of LRU is that all the banks ahead of the hit bank generate misses, the total communication time of the Fast-LRU replacement scheme is 12(1+2+2+2+4+1) hops in Figure 1 (b). In addition, this scheme almost halves the number of bank accesses since both tag-match and replacement are performed simultaneously.

Next, we further investigate how to reduce the cache access time by exploiting the multicast router proposed in Section E. Even though Fast-LRU replacement reduces the hit latency, a hit on the LRU bank or a miss on a cache (i.e. all banks produce misses) still suffers from the long latency, which is the sum of the bank access time over all banks in a bank set and the network latency. Multicast relieves this problem

(a) Cache Hit with Time Diagram

(b) Cache Miss with Time Diagram

Fig. 2. Fast-LRU Replacement with Multicast Support

by allowing concurrent accesses of multiple banks for tag-match.

Figure 2 (a) illustrates a cache hit for Multicast Fast-LRU replacement with the time diagram of each operation. When the multicast router attached to the MRU bank (Bank 1) receives a data request, it forwards the request to two destinations, the MRU bank and the second MRU bank (Bank 2), at the same time. The router attached to the second MRU bank (Bank 2) also forwards the request to the attached bank and the next bank (Bank 3), and so on. If the requested block is found in the MRU bank, no block replacement is required and the core is notified of a cache hit. Otherwise, the MRU bank initiates Fast-LRU replacement by sending its evicted block to the second MRU bank. Each non-MRU bank that experienced a cache miss waits for the evicted cache block from the next closest bank from the core. As soon as it receives the evicted block, it also sends its own evicted block to the next LRU bank. This operation stops at the bank where the requested block is found, since the requested block is sent to the MRU bank, not the next LRU bank. Note that the replacement packet (including an evicted block) can never catch the data request packet and that the data request packet always reaches the LRU bank if the router performs arbitration in a FIFO manner. Each non-MRU bank should not initiate its evicted block transfer to the next LRU bank unless it receives an evicted block from the previous bank.

A cache miss occurs when all the banks in the bank set produce misses as depicted in Figure 2 (b). It incurs the off-chip memory access and write-back from the LRU bank (Bank 16) to the memory, if necessary. The core waits for all the banks to report misses, and then invokes the memory access. When the memory sends a new block to the MRU bank, the MRU bank sends this newly incoming block to the core. The block movement is similar with that of a cache hit, except the LRU bank notifies the core of the replacement completion and writes back the victim to the memory if the

block is dirty.

In this scenario, more optimization techniques can be used to improve the performance further.

- In a cache hit, the hit notification and the hit block can be merged into a single packet. This packet is replicated at the router that is attached to the MRU bank. Then the original packet goes to the MRU bank for LRU replacement while the replica is sent to the core.

- In a cache miss, the core does not have to wait for the miss notifications from all the banks, if some banks have invalid cache blocks. Initially the cache is empty and all the blocks are invalid. As cache blocks are read into the banks, all the invalid blocks are pushed down towards the LRU bank. Therefore, the core receives a miss notification from an invalid block, thus implying that all the banks farther than this bank have invalid blocks. In fact, the core should keep track of miss notifications from all the banks that are closer to the core than the bank that produces a compulsory miss. This can expedite the memory access and deliver the required data to the core earlier.

#### 2. Performance Gain Estimation

We build an analytical model of communications for each replacement policy and estimate the efficiency of Multicast Fast-LRU replacement. It can be used as an early design tool to estimate the networked cache performance. Furthermore, it can be generalized to other replacement policies and be applicable to predict performance for other workloads.

A c-bank, w-way cache system requires a  $c \times w$  mesh network. We can break down its access latency into bank access latency  $(l_b)$ , memory access latency  $(l_m)$ , and network latency  $(l_n)$ . The network latency  $(l_n)$  is proportional to the hop count, d. It also can be represented as  $l_n(i \to j)$  between two communication entities, i and j, and each entity is one of core (C), banks  $(\{b_{x,y}|x \in [1,c], y \in [1,w]\})$ , or off-chip memory (M). Bank  $b_{x,y}$  stands for y-th way in x-th column of the mesh.

We show how the average access time can be estimated in the memory hierarchy including a L2 cache and an off-chip memory with different communication designs.

Average Access Latency: To estimate the average L2 cache access latency  $(L_P)$  for a replacement policy (P), we consider hit latency  $(H_P)$  and miss latency  $(M_P)$  separately. When the request comes into the network, it accesses banks in only one column x of the mesh network. Let  $h_{x,y}$  be the hit rate of bank  $b_{x,y}$  and  $H_P(x,y)$  be the hit latency. Summing up each hit rate of all banks is less than 1  $(\sum_{x=1}^c \sum_{y=1}^w h_{x,y} \leq 1)$ . Then, column x's portion for the average access latency is addition of two parts: the sum over each bank's hit latency weighted by its hit rate, and the product of the miss rate and miss latency. The miss rate is computed by subtracting the sum of the hit rate of all banks in column x. The miss rate is later weighted by the ratio of requests going to the column x to total requests,  $r_x$   $(\sum_{x=1}^c r_x = 1)$ . We calculate  $L_P$  as:

$$L_p = \sum_{x=1}^{c} \left[ \sum_{y=1}^{w} (h_{x,y} \cdot H_p(x,y)) + (r_x - \sum_{y=1}^{w} h_{x,y}) \cdot M_p(x) \right]$$

Unicast LRU, Unicast Fast-LRU, and Multicast Fast-LRU policies are denoted as u-LRU, u-fLRU, and m-fLRU.

Unicast LRU: The cache hit on the MRU bank (the first way,  $b_{x,1}$ ),  $H_{u-LRU}(x,1)$ , does not need block movement. Its latency includes a single bank access,  $l_b$ , and a network round-trip between core and the MRU bank, which is the sum of  $l_n(C \to b_{x,1})$

<sup>&</sup>lt;sup>2</sup>For simplicity, we assume that our network is contention free.

and  $l_n(b_{x,1} \to C)$ . However, the cache hit on other banks,  $H_{u-LRU}(x,y)$ , needs multiple bank accesses. The hit on the bank  $b_{x,y}$  causes banks from  $b_{x,1}$  to  $b_{x,y-1}$  to generate misses and each network latency to the neighbor is 2 hops, which is  $l_n(2)$ . Additionally it needs recursive block movements from the hit bank to the MRU bank to maintain the order for LRU replacement.

$$H_{u-LRU}(x,1) = \underbrace{l_{n}(C \to b_{x1}) + l_{b} + l_{n}(b_{x,1} \to C)}_{hit}$$

$$H_{u-LRU}(x,y) = \underbrace{l_{n}(C \to b_{x,1}) + l_{b} + (y-1) \cdot (l_{n}(2) + l_{b})}_{(y-1) \text{ misses} + y - th \text{ bank hit}}$$

$$+ \underbrace{l_{n}(y) + l_{b} + (y-1) \cdot (l_{n}(2) + l_{b}) + l_{n}(b_{x,y} \to C)}_{move}$$

The cache miss latency,  $M_{u-LRU}(x)$ , has three components. It detects cache miss by visiting all w banks, goes to the memory controller to fetch a new block, and then places it to the MRU bank. This placement of a new block incurs additional block movement until the bank does not have a valid block. If the y'-way bank is the last one for movement, the number of additional movements is y'.

$$M_{u-LRU}(x) = \underbrace{l_n(C \to b_{x,1}) + l_b + (w-1) \cdot (l_n(2) + l_b)}_{w \text{ misses}} + \underbrace{l_n(b_{x,w} \to M) + l_m}_{memory} + \underbrace{l_n(M \to b_{x,1}) + l_b + y' \cdot (l_n(2) + l_b) + l_n(b_{x,y'} \to C)}_{place}$$

Unicast Fast-LRU: Fast-LRU replacement has no extra movements caused by placing the hit block to the MRU bank, because the block is already moved to its neighbor. Furthermore, in case of a miss, when a new block from the memory is placed on the MRU bank, the corresponding frame in the MRU bank is already invalid. Therefore, it does not have y' movements for Unicast LRU policy.

$$H_{u-fLRU}(x,1) = \underbrace{l_n(C \to b_{x,1}) + l_b + l_n(b_{x,1} \to C)}_{hit}$$

$$H_{u-fLRU}(x,y) = \underbrace{l_n(C \to b_{x,1}) + l_b + (y-1) \cdot (l_n(2) + l_b)}_{(y-1) \text{ misses} + \text{move} + y - \text{th bank hit}} + \underbrace{l_n(y) + l_b + l_n(b_{x,1} \to C)}_{move}$$

$$M_{u-fLRU}(x) = \underbrace{l_n(C \to b_{x,1}) + l_b + (w-1) \cdot (l_n(2) + l_b)}_{w \text{ misses}} + \underbrace{l_n(b_{x,w} \to M) + l_m}_{memory}$$

$$+ \underbrace{l_n(M \to b_{x,1}) + l_b + l_n(b_{x,1} \to C)}_{place}$$

Multicast Fast-LRU: Because multicast packets for the cache request produce a copy at each router and each of them arrives at a bank concurrently, the hit latency consists of the hit bank access and the round-trip starting at the core. Note that block movements for LRU replacement initiated by the hit bank are not on the critical path compared with the Unicast Fast-LRU scheme. When the miss notification from the last bank arrives at the core, the corresponding request is identified as a miss, and hence, the core directly asks the memory for sending a new block to the MRU bank.

$$H_{m\text{-}fLRU}(x,y) = \underbrace{l_n(C \to b_{x,y}) + l_b + l_n(b_{x,y} \to C)}_{hit}$$

$$M_{m\text{-}fLRU}(x) = \underbrace{l_n(C \to b_{x,w}) + l_b + l_n(b_{x,w} \to C)}_{miss} + \underbrace{l_n(C \to M) + l_m}_{memory}$$

$$+ \underbrace{l_n(M \to b_{x,1}) + l_b + l_n(b_{x,1} \to C)}_{place}$$

## D. Interconnection Network Topology and Layout

We analyze the utilization of the interconnection network for large scale cache systems and explore a few alternatives for simplification and optimization. The limited chip resource should be efficiently distributed to both computational and communication units. Over-provisioning causes the waste of valuable chip resources, while under-

provisioning incurs performance degradation. Therefore, the chip design needs a careful analysis of each unit's resource requirement and their interactions to draw the optimal configuration.

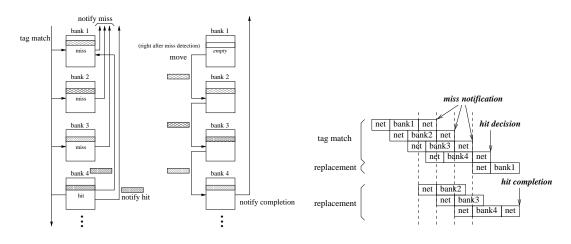

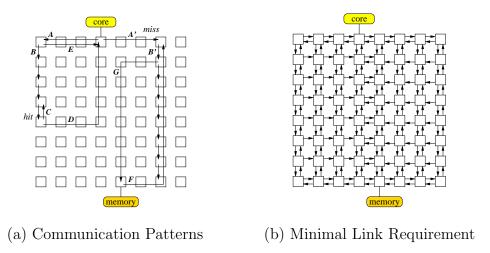

Fig. 3. An  $8 \times 8$  Mesh Network for a Large Scale Cache System

Figure 3 (a) shows all possible XY routing communication patterns of a large scale L2 cache system on an 8 × 8 mesh network. The core is attached to the fourth router on the top row and the memory is attached to the fifth router on the bottom row. Forwarding a data request to the appropriate bank set needs the traversal of the first row (**A**) and the traversal of banks within a column (**B**) until there is a hit in one bank. When a bank replies the requested cache block to the core, the communication path is either **D** from a non-MRU bank or **E** from a MRU bank. The data movement between two banks occurs only in one column of the mesh (**B** or **C**). While a cache miss has the same communication patterns (**A**' and **B**') as a cache hit, it fetches a new data block from the memory and places it on the MRU bank (**F**). After this new block placement, an evicted dirty block is replaced with the block in the next farther bank (**B**') or is written back to the memory (**G**), if dirty.

One observation of these patterns is that a single direction is used in most horizontal links except on the first row, the last row, and links between the core-attached column and the memory-attached column. Figure 3 (b) shows the minimum set of links after removing all the unnecessary horizontal links. In general, we can remove  $(n-2)^2$  links among the total  $4(n-1)^2$  links of an  $n \times n$  mesh, which reduces the link area by 25%.

Another observation is that the horizontal links except on the first row, are infrequently used, because they are used only when a bank needs to communicate with the core (i.e. the cache controller) or the memory. Considering the data locality, horizontal link utilization for the last row becomes low because those links are only used for the memory accesses. The number of these underutilized links<sup>3</sup> is  $n^2 - 2$ .

```

Inputs: coordinates of source bank(X_{src}, Y_{src})

coordinates of destination bank(X_{dest}, Y_{dest})

Outputs: Selected output Channel

Procedure:

X_{offset} := X_{dest} - X_{src};

Y_{offset} := Y_{dest} - Y_{src};

if Y_{offset} \ge 0 then

if X_{offset} > 0 then Channel := X + ;

else if X_{offset} < 0 then Channel := X - ;

else if Y_{offset} = 0 then Channel := Internal;

else Channel := Y + ;

endif

else

Channel := Y - ;

endif

```

Fig. 4. XYX Routing Algorithm

They can be eliminated at the expense of small bandwidth loss. This simplified

$<sup>^{3}</sup>$ In a mesh network requiring a minimal number of links, rows from the second to the last second have n vertical links. The last row has 2(n-1) vertical links. Therefore, the total number of underutilized links is n(n-2) + 2(n-1).

Fig. 5. Deadlock Freedom in XYX Routing

mesh can remove additionally 25% of total links. However, it causes the change of the routing scheme since communications from the banks to the core/memory start in the Y direction first, which violates the XY routing rule. Thus, we propose a new routing scheme called XYX routing to overcome this problem. XYX routing is deadlock-free because we enforce the total order of channels in the mesh network.

Figure 4 shows the XYX routing algorithm for k-ary 2-cubes. The routing function routes packets in the X dimension first and in the Y dimension next for the XY direction or in the Y dimension first and in the X dimension next for the YX direction. Figure 5 (a) and (b) show the deadlock freedom in a  $3 \times 3$  mesh network. When all the channels are ordered totally in Figure 5 (a), packets that lie on the different channels do not produce a cycle in the network. Any path in XYX routing follows increasingly numbered channels such as two paths, (14, 19) and (5, 6, 13). XYX routing algorithm allows only four turns out of total eight turns in the turn model [48]. Cycles are prevented by prohibiting four of the turns, as shown in Figure 5 (b).

In the view of the router design, expunging horizontal links leads to the elimination of all the input buffers associated with those links and to the simplification of both the arbiter and the crossbar. This simplified router also reduces the pipeline latency as well as saves its area.

(c) Halo with Chiloffin Banks (d) Halo with Iton annothin Banks

Fig. 6. Domain-Specific Development of Network Designs for Large Cache Systems

One of the disadvantages in a mesh network is uneven network latencies for MRU banks depending on the distance from the core. Since there is only one path between the core and one special MRU bank, the leftmost or rightmost MRU banks cannot avoid suffering from long network latency (Figure 6 (a) and (b)). So it is crucial to provide a direct communication path between the core and each MRU bank. For this purpose, we choose a topology in which the core is located in the same distance

from all the MRU banks. We call this topology a halo network shown in Figure 6 (c). The core plays a role of a hub to control the departure and the arrival of cache requests. A bank set is distributed over multiple banks within a spike branched from a hub, which bidirectionally connects all the banks in the order of the way. In this design, we assume that the cache controller supports multiple ports/interfaces to the networked cache. We put a small queue for each spike such as a multiple issue queue. Thus, a cache request is first stored in each spike queue to be subsequently forwarded to the L2 cache. When the size of these queues becomes very high to connect many spikes, multiple spikes can share one queue with an address decoding logic. Spike queue sharing will reduce the cost of queues and reduce the concentration degree to the core/memory, hence achieving better scalability. However, the spike access will be delayed when there are multiple cache requests for different spikes in the queue.

When the size of all banks that build a spike is identical, the banks positioned at the end of the spike cannot fill the increased area entirely in Figure 6 (c). Although we can curve a spike and connect banks within a spiral spike, this layout incurs the longer wire delay than the straight spike layout. If the bank size increases along the spike, we can reduce the wasted area and draw a compact design by tightly integrating banks on a chip die as shown in Figure 6 (d). As a bank is located farther from the core, its size becomes larger and its access time increases due to the increased capacity. Therefore, capacity-increased banks have more than one way. A halo network incorporated with non-uniform size banks has a topological benefit by giving the same access time to all the MRU banks, and it enjoys a better area utilization over a halo network with the uniform size banks. Note that the memory controller is located in the center of the cache. To access the off-chip memory from the memory controller, the wire delay in a halo is longer than in a mesh network.

Mathematical model described in Section 2 can be directly applied to the halo

network with small modification. The required change is that the halo network has zero hop count in x direction due to the direct links for each bankset. Thus all the latency components account for only the y coordinate in the mesh network. Adoption of non-uniform banks in the halo network requires different bank latency  $l_b$  and network latency, resulting in an accumulated form for miss latency calculation.

## E. Designing Multicast Single-Cycle Router

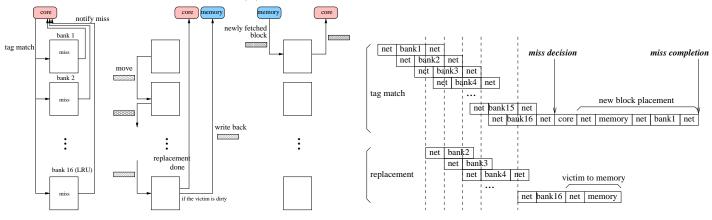

Fig. 7. Single-Cycle Router Architecture with Multicast Support

In this research, we use wormhole routers due to small buffer requirement and high throughput. Figure 7 shows the major components of a wormhole router. It has 5 Physical Channels (PCs) that connect four neighbors and one injection/ejection unit, and each PC is divided into multiple Virtual Channels (VCs). VCs from the same PC share one crossbar port to reduce the crossbar complexity. While middle/tail flits require three operations (input buffering, switch allocation, and switch traversal),

head flits require two additional operations (routing and VC allocation).

Although an aggressive design can merge adjacent operations into a single-cycle operation, this dependency still exists. The design of the router pipeline has a high impact on the internal clock time of the router. Recent results of the different single cycle router designs [17, 49, 50], showed 12 – 35 (fanout-of-four) FO4 delays, which is larger than the optimal pipeline delay (6 – 8 FO4) in the modern superscalar processor [18]. Although increasing complexity of the router pipeline may increase the clock cycle time, the following techniques can break and reduce the serial dependency between different operations, thus achieving a single-cycle router.

- Lookahead routing: The routing decision is made one hop ahead of the current router. It eliminates the routing delay by removing the serial dependency between routing and VC allocation like the SGI SPIDER chip [19]. The routing outcome is stored in a flit and hence used to allocate VC or the switch output port in the next router.

- Buffer bypassing: If the input buffer designated for the VC is empty, a flit directly goes to the crossbar or the VC allocator (if it is a head flit) through a bypass path without being stored at the tail entry of the input buffer. It also removes the delay for the read and write operations of buffer.

- Speculative switch allocation: Switch allocation is performed speculatively at the same instance of VC allocation so that a head flit enters into the crossbar right after VC allocation [20]. This speculative switch allocator is only applied to head flits and cannot be granted if the normal switch allocator reserves all the available ports. In this way both VC and switch allocations are performed at the same cycle.

• Arbitration pre-computation: Arbitration of competing requests for a VC or a switch port is pre-computed and stored for the next arbitration after one output VC in VC allocator or input/output port of the crossbar in switch allocator is granted [17]. The grant signals of the arbiter are generated as the product of the pre-computed grant enable signals and incoming arbitration requests. Hence arbitration outcomes are prepared one cycle ahead and latched for the next cycle.

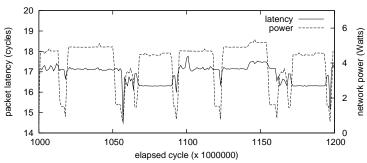

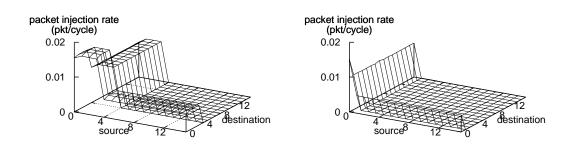

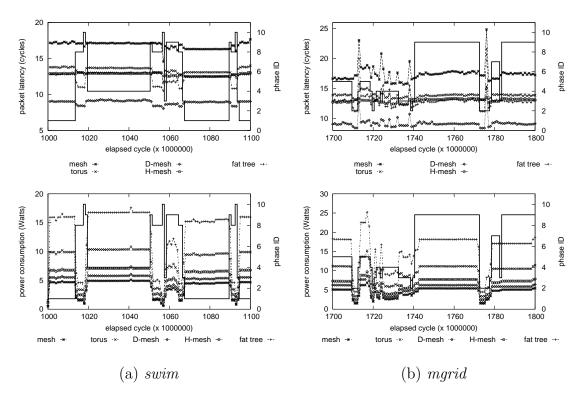

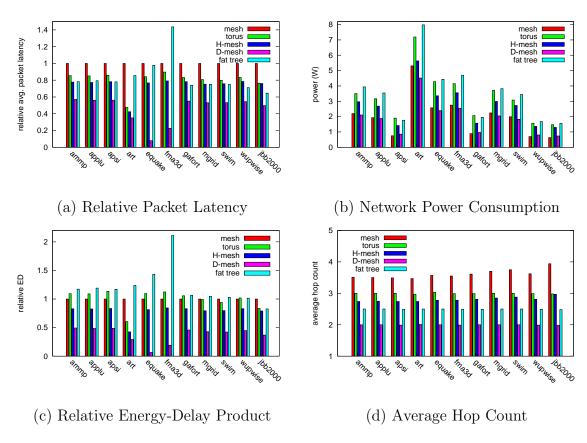

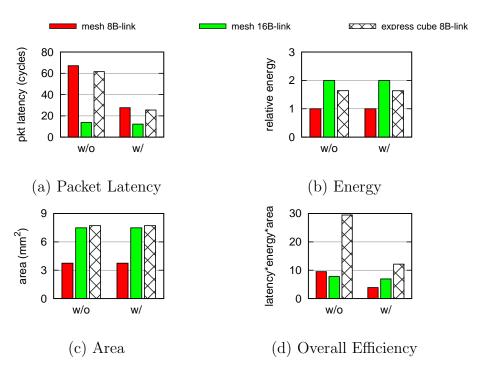

Our router design maximizes these chances and eventually delivers a flit in a single clock cycle by shortening the critical path in a traditional pipelined router. All these techniques except lookahead routing work well in a lightly loaded network where the possible cases for each scheme occur frequently. However, when the router experiences high contention, the router cannot transfer flits in one cycle. For example, when speculative switch allocation is failed, switch allocation and VC allocation are done with different cycles. Additionally, when the switch arbiter does not grant this request due to port contention for other requests, switch allocation cannot be performed at the same cycle of the switch traversal.