# HIGH PERFORMANCE CMOS INTEGRATED CIRCUITS FOR

# **OPTICAL RECEIVERS**

A Dissertation

by

# MOHAMMADREZA SAMADIBOROUJENI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2006

Major Subject: Electrical Engineering

# HIGH PERFORMANCE CMOS INTEGRATED CIRCUITS FOR

## **OPTICAL RECEIVERS**

A Dissertation

by

# MOHAMMADREZA SAMADIBOROUJENI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee,<br>Committee Members, | Aydin Karsilayan<br>Jose Silva-Martinez |

|-------------------------------------------|-----------------------------------------|

|                                           | Reza Langari<br>Prasad Enjeti           |

| Head of Department,                       | Costas Georghiades                      |

December 2006

Major Subject: Electrical Engineering

#### ABSTRACT

High Performance CMOS Integrated Circuits for Optical Receivers.

(December 2006)

MohammadReza SamadiBoroujeni, B.S., Isfahan University of Technology; M.S., University of Tehran

Chair of Advisory Committee: Dr. Aydin Karsilayan

Optical communications is expanding into new applications such as infrared wireless communications; therefore, designing high performance circuits has gained considerable importance. In this dissertation a wide dynamic-range variable-gain transimpedance amplifier (TIA) is introduced. It adopts a regulated cascode (RGC) amplifier and an operational transconductance amplifier (OTA) as the feed forward gain element to control gain and improve the overload of the optical receiver. A fully-differential variable-gain TIA in a 0.35 $\mu$ m CMOS technology is realized. It provides a bit error rate (BER) less than 10<sup>-12</sup> for an input current from 6 $\mu$ A-3mA at 3.3V power supply. For the transimpedance gain variation, from 0.1k $\Omega$  to 3k $\Omega$ , -3dB bandwidth is higher than 1.7GHz for a 0.6pF photodiode capacitance. The power dissipations for the highest and the lowest gains are 8.2mW and 24.9mW respectively.

A new technique for designing uniform multistage amplifiers (MA) for high frequency applications is introduced. The proposed method uses the multi-peak bandwidth enhancement technique while it employs identical, simple and inductorless stages. It has several advantages, such as tunability of bandwidth and decreased sensitivity of amplifier stages, to process variations. While all stages of the proposed MA topology are identical, the gain-bandwidth product can be extended several times. Two six-stage amplifiers in a TSMC 0.35µm CMOS process were designed using the proposed topology. Measurements show that the gain can be varied for the first one between 16dB and 44dB within the 0.7-3.2GHz bandwidth and for the second one between 13dB and 44dB within a 1.9-3.7GHz bandwidth with less than  $5.2nV/\sqrt{Hz}$  noise. Although the second amplifier has a higher gain bandwidth product, it consumes more power and occupies a wider area.

A technique for capacitance multiplication is utilized to design a tunable loop filter. Current and voltage mode techniques are combined to increase the multiplication factor (M). At a high input dynamic range, M is adjustable and the capacitance multiplier performs linearly at high frequencies. Drain-source voltages of paired transistors are equalized to improve matching in the current mirrors. Measurement of a prototype loop filter IC in a 0.5 $\mu$ m CMOS technology shows 50 $\mu$ A current consumption for M=50. Where 80pF capacitance is employed, the capacitance multiplier realizes an effective capacitance varying from 1.22nF up to 8.5nF. To my wife, Homayra

#### ACKNOWLEDGEMENTS

I would like to acknowledge the many individuals who have contributed to the completion of my research. First, I would like to thank my advisor, Dr. Aydin Karsilayan, for his guidance, encouragement, and support. He has been extremely generous in his time and resources and has provided valuable assistance in every single step of my research and writing. I am also grateful to my committee members, Dr. Jose Silva-Martinez who has kept me focused and provided me with insight from his own experiences, Dr. Reza Langari who has been a real mentor to me and has generously spent time on guiding me, and Dr. Prasad Enjeti who agreed to be on my committee, but who retired before my defense. I thank you all for your dedication toward helping me attain this goal. Furthermore, I would like to extend my appreciation to Dr. Edgar Sanchez-Sinencio who, in the first place, provided the opportunity for me to come to Texas A&M and continued supporting and guiding me throughout my studies.

In the University's Department of Engineering Technology and Industrial Distribution Dr. Rainer Fink and Dr. Ben Zoghi have helped me in countless ways. They have always had encouraging words, bright smiles, helping hands and positive outlooks. While pursuing my studies, I was fortunate to work as a graduate assistant to them.

I wish also to express my sincere appreciation and gratitude to Advanced Micro Devices (AMD) in South Austin for generously letting me use their lab equipment and instruments to carry out my tests for my dissertation. I give special thanks to my supervisors and colleagues in the Physical Design Group who have been extremely understanding, patient and cooperative during the time I have been working on my dissertation.

Next, I want to express my deepest gratitude to my wife without whose love, patience, encouragement and support, I would have been unable to survive in this doctoral process. Truly I cannot find the words to express my appreciation of her and what she has done for me.

Finally I would like to thank my parents for giving me the value of life. They have always encouraged me to be persistent and fight for what I believe in.

Completing this dissertation was a journey that I did not have to take alone due to the patience and unwavering support provided by all those mentioned.

# TABLE OF CONTENTS

| ABSTRACTiii                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEDICATIONv                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ACKNOWLEDGEMENTSvi                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LIST OF TABLESxviii                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NOMENCLATURExix                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CHAPTER                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A       Introduction and Motivation       1         B       Optical Communications Systems       2         C       Optical Receiver       4         1.       Transimpedance Amplifier (TIA) and Limiting Amplifier (LA)       5         2.       Clock Data Recovery (CDR) Circuits       5         D       General Concepts       7         1.       Bandwidth       7         2.       Eye Diagram       8         E       Organization of Dissertation       9 |

| II TRANSIMPEDANCE AMPLIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1. Parameters of TIA                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D The Proposed TIA                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E The Proposed Variable Gain TIA                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>2. Fully Differential Variable Gain RGC TIA Circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| CHA | PTE | R                                                                                         | Page  |

|-----|-----|-------------------------------------------------------------------------------------------|-------|

|     |     | <ol> <li>Measurement Results</li></ol>                                                    |       |

|     |     | 2. Simulation of the Differential Variable Gam TIA in CWOS 0.35µm Technolo                | gy Jy |

| III | LI  | MITING AMPLIFIER                                                                          | 42    |

|     | А   | Multistage Amplifier                                                                      | 43    |

|     |     | Conventional Multistage Amplifier                                                         |       |

|     |     | Gain Bandwidth Product (GBP)                                                              |       |

|     | D   | Conventional Multistage Amplifier with Passive Feedback                                   | 48    |

|     | Е   | Expanding the Bandwidth                                                                   | 49    |

|     |     | 1. Conventional Peaking Technique                                                         |       |

|     | F   | Proposed LA                                                                               |       |

|     |     | Chained Multistage Amplifier                                                              |       |

|     | Η   | Uniform Chained Multistage Amplifier (CMA)                                                |       |

|     |     | 1. Peaking in 6-stage and 8-stage CMA                                                     |       |

|     |     | 2. Gain and Bandwidth                                                                     |       |

|     |     | <ol> <li>Group Delay</li> <li>Sensitivity</li> </ol>                                      |       |

|     |     | 5. Stability                                                                              |       |

|     |     | 6. Noise                                                                                  |       |

| IV  | IN  | IPLEMENTATION OF CMA TOPOLOGY                                                             | 86    |

|     | А   | Designing an <i>n</i> -stage CMA                                                          | 86    |

|     |     | Realization of the Uniform CMA                                                            |       |

|     |     | 1. Amplifier Stages                                                                       | 87    |

|     |     | 2. Reducing the Miller Effect of Gate-Drain Capacitance of Transistors                    |       |

|     |     | 3. Design and Implementation of the First 6-stage Uniform CMA                             |       |

|     |     | 4. Sensitivity Simulation                                                                 |       |

|     | ~   | 5. Noise Simulation                                                                       |       |

|     | С   | Second Uniform Implementation of an <i>n</i> -stage CMA                                   |       |

|     |     | 1. Simulation Results                                                                     |       |

|     |     | <ol> <li>Design of the Second Uniform 6-stage CMA</li> <li>Measurement Results</li> </ol> |       |

|     |     | 5. Measurement Results                                                                    | 112   |

| V   | А   | CAPACITANCE MULTIPLICATION TECHNIQUE COMBINING                                            |       |

|     | V   | OLTAGE AND CURRENT MODE                                                                   | 116   |

|     | А   | Introduction                                                                              | 116   |

|     |     | 1. Tuning Loop Filter                                                                     |       |

|     |     | 2. DC Offset Cancellation                                                                 |       |

|     |     | 3. Capacitance Multiplier                                                                 | 122   |

|     | В   | Proposed Capacitance Multiplication Technique                                             |       |

|     |     | 1. Admittance                                                                             |       |

|     |     | 2. Complete Scheme                                                                        |       |

|     |     | 3 Stability                                                                               | 128   |

# CHAPTER

| 4 Swing                     |         | 130 |

|-----------------------------|---------|-----|

| 5. Noise                    |         |     |

|                             |         |     |

| VI CONCLUSION               |         |     |

| A Conclusion                |         |     |

| B Suggestions for Further S | Studies |     |

| REFERENCES                  |         |     |

| VITA                        |         |     |

Page

# LIST OF FIGURES

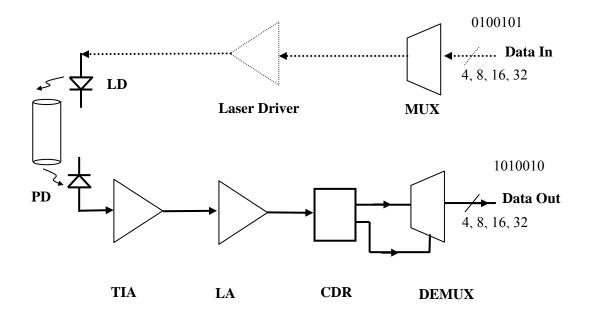

| Fig. 1-1  | An optical communications system                                                                                                                                                                  | 3  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

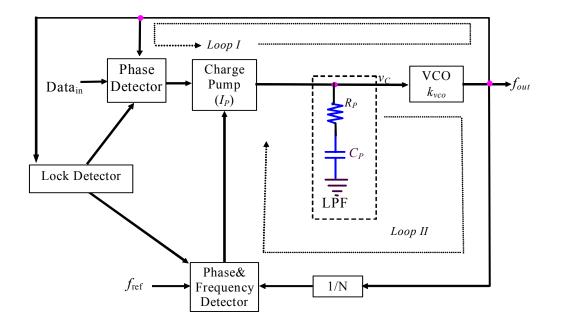

| Fig. 1-2  | A two-loop CDR architecture                                                                                                                                                                       | 6  |

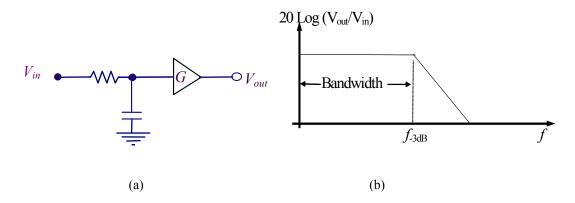

| Fig. 1-3  | (a) The model of a wideband amplifier (b) Magnitude of the gain transfer function of a wideband amplifier.                                                                                        | 7  |

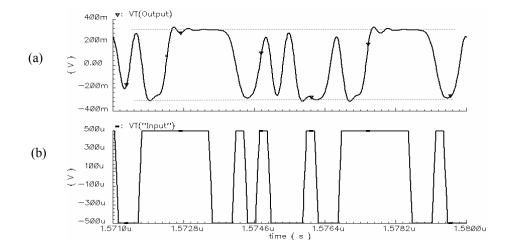

| Fig 1-4   | Amplifying a signal by an amplifier with a limited bandwidth (a) Output (b) Input                                                                                                                 | 8  |

| Fig. 1-5  | Eye diagram                                                                                                                                                                                       | 9  |

| Fig. 2-1  | Sensitivity of transimpedance amplifier, sensed current via bandwidth of transimpedance                                                                                                           | 13 |

| Fig. 2-2  | Small signal model of photo detector                                                                                                                                                              | 14 |

| Fig. 2-3  | Common gate (CG) transimpedance amplifier with g <sub>m</sub> -boosting amplifier (a) simple amplifier (b) cascode amplifier                                                                      | 15 |

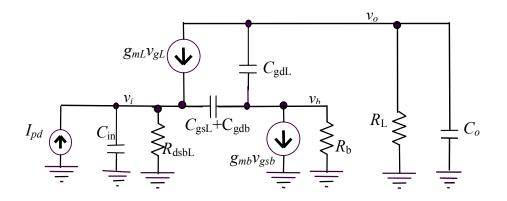

| Fig. 2-4  | Small signal model of common gate (CG) transimpedance amplifier                                                                                                                                   | 17 |

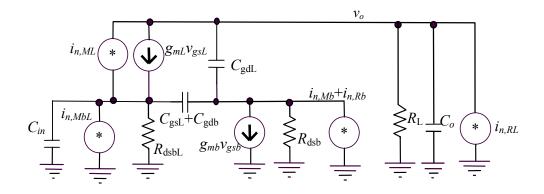

| Fig. 2-5  | A scheme for modeling the noise model of CG TIA with $g_m$ -boosting amplifier.                                                                                                                   | 19 |

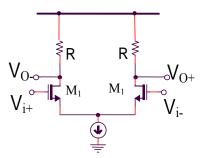

| Fig. 2-6  | Single input differential ended CG TIA                                                                                                                                                            | 21 |

| Fig. 2-7  | Magnitude of transimpedance gain of single input differential ended RGC TIA.                                                                                                                      | 23 |

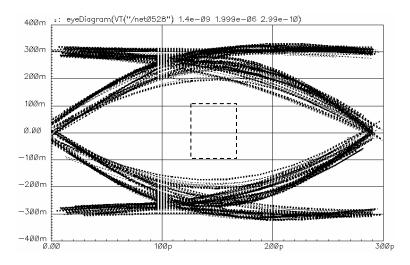

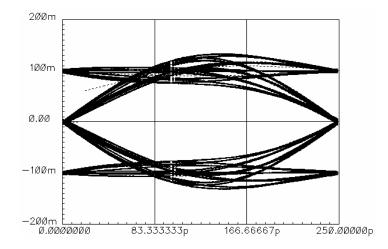

| Fig. 2-8  | Eye diagram at 200uA and 4Gbits/s for 16000 random bits of single input differential ended RGC TIA for a $C_{PD}$ =0.5pF                                                                          | 24 |

| Fig. 2-9  | Eye diagram for 2.5Gbits/s (for 10000 random bits) of single input differential ended RGC TIA (a) at 0.5mA (b) at 2.5mA.                                                                          | 25 |

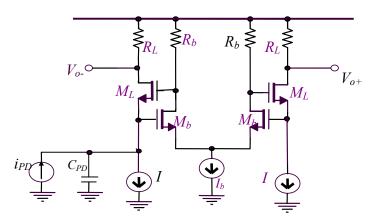

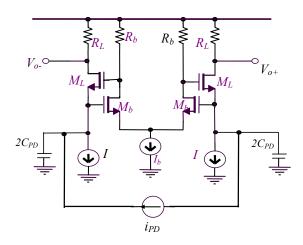

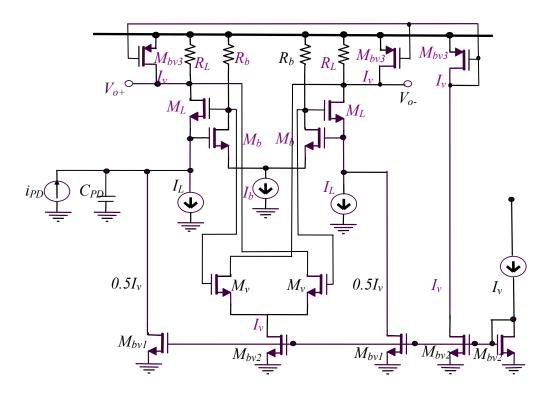

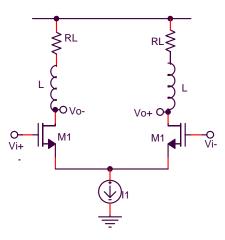

| Fig. 2-10 | Fully differential RGC TIA                                                                                                                                                                        | 26 |

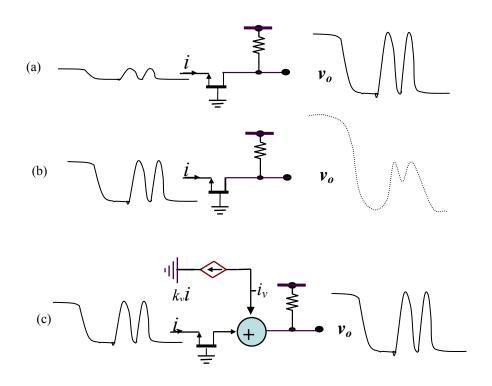

| Fig. 2-11 | Scheme of CG TIA (a) the conventional CG TIA when the input current is low (b) the conventional CG TIA when the input current is high (c) the proposed TIA when the input current is high and low | 27 |

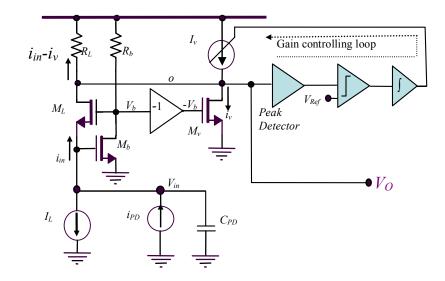

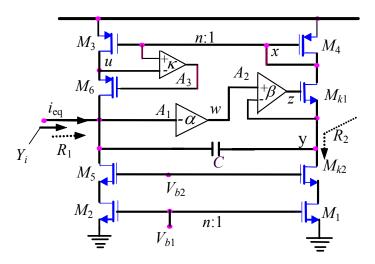

| Fig. 2-12 | Variable gain RGC TIA with gain controlling loop                                                                                                                                                  | 28 |

| Fig. 2-13 | Circuit of the fully differential variable gain RGC TIA                                                                                                                                                                                                                                   | 29 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

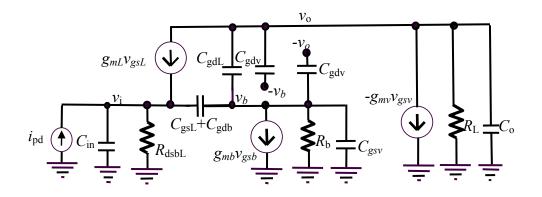

| Fig. 2-14 | A small signal model of the fully variable gain RGC TIA                                                                                                                                                                                                                                   | 29 |

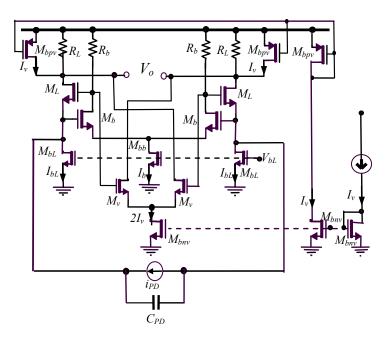

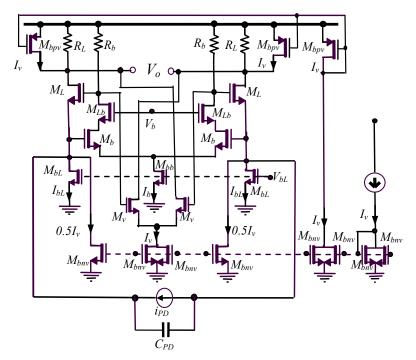

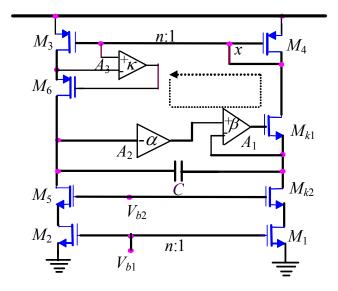

| Fig. 2-15 | Implemented fully differential variable gain RGC TIA                                                                                                                                                                                                                                      | 33 |

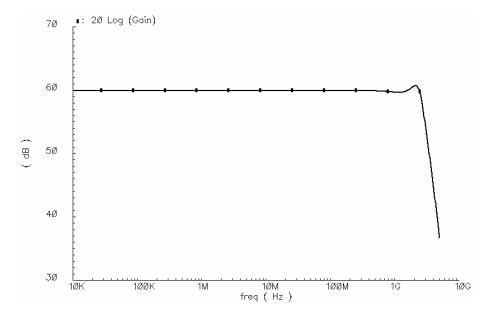

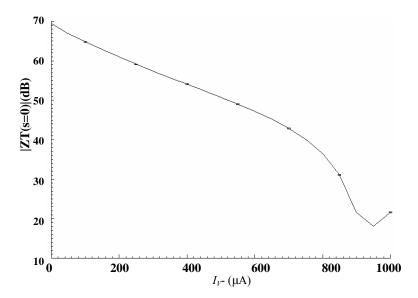

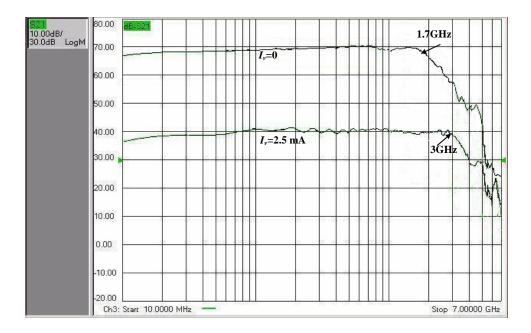

| Fig. 2-16 | Simulation results of the midband gain of the fully differential variable gain RGC TIA                                                                                                                                                                                                    | 34 |

| Fig. 2-17 | Simulation results of the input impedance of the fully differential variable gain RGC TIA                                                                                                                                                                                                 | 34 |

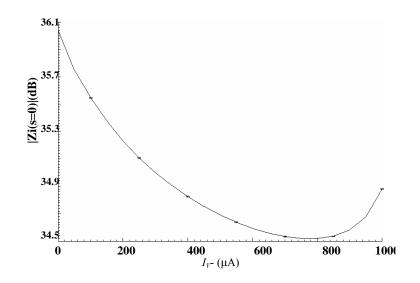

| Fig. 2-18 | Simulation results of the input referred current noise of the fully differential variable gain RGC TIA                                                                                                                                                                                    | 35 |

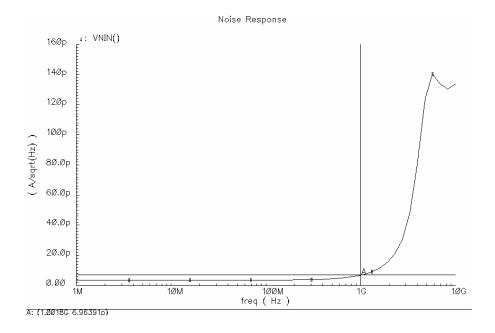

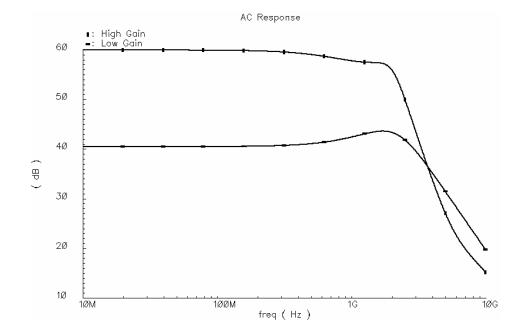

| Fig. 2-19 | Measurement results of the magnitude of TIA for $I_v=0$ . $I_v=2.5$ mA when $I_{bL}=0.5$ mA                                                                                                                                                                                               | 37 |

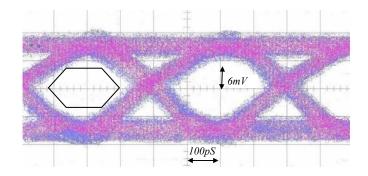

| Fig. 2-20 | Eye diagram measurement results for $I_{\nu}=0$ and $i_{p-p}=6uA$ when $I_{bL}=0.5mA$ at BER=10 <sup>-12</sup> for an input test pattern of 2 <sup>31</sup> -1 pseudo-random bits stream (PRBS)                                                                                           | 37 |

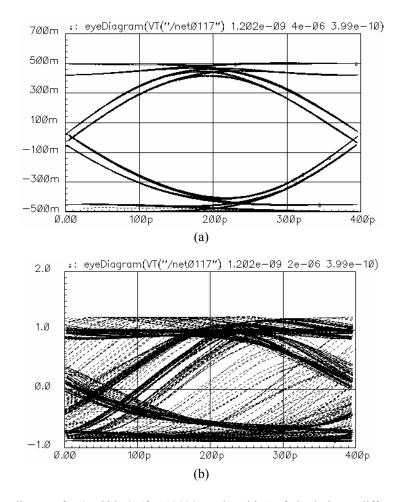

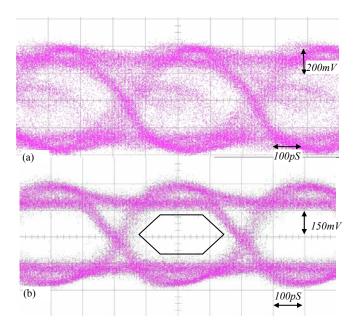

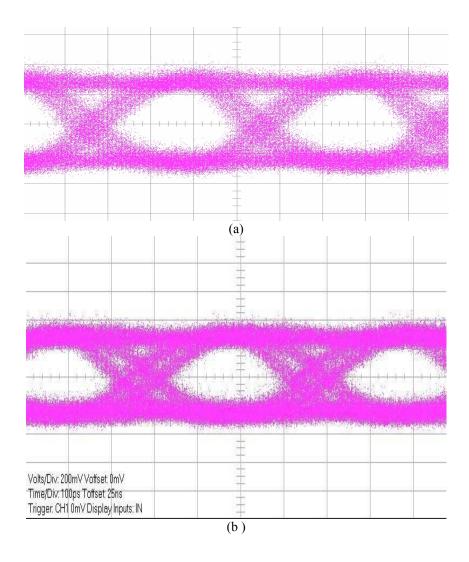

| Fig. 2-21 | Eye diagram measurement results for $i_{p-p}=3\text{mA}$ (a) when $I_{bL}=0.5\text{mA}$ and $I_{v}=0$ eye is closed (b) when $I_{bL}=0.5\text{mA}$ and $I_{v}=2.5\text{mA}$ it is open and BER=10 <sup>-12</sup> for a test pattern of 2 <sup>31</sup> -1 pseudo-random bit stream (PRBS) | 38 |

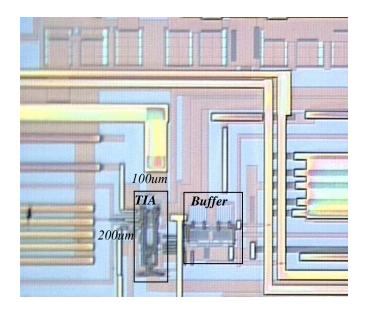

| Fig. 2-22 | TIA die microphotograph                                                                                                                                                                                                                                                                   | 38 |

| Fig. 2-23 | Differential variable gain RGC TIA                                                                                                                                                                                                                                                        | 40 |

| Fig. 2-24 | Magnitude simulation results of the differential variable gain RGC TIA                                                                                                                                                                                                                    | 40 |

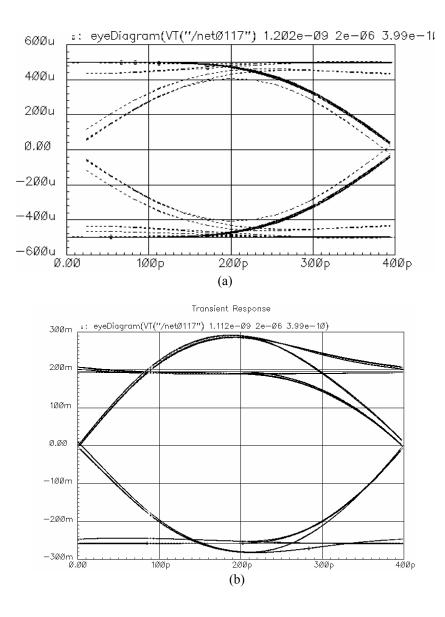

| Fig. 2-25 | Eye diagram for 2.5Gbits/s for 10000 random bits of the differential variable gain RGC TIA. (a) at 1uA (b) at 4mA                                                                                                                                                                         | 41 |

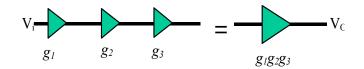

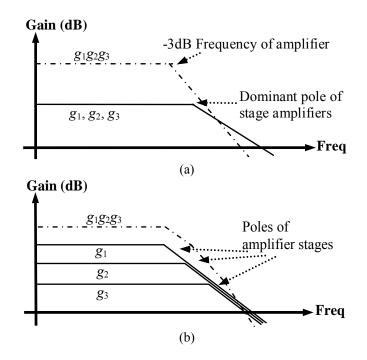

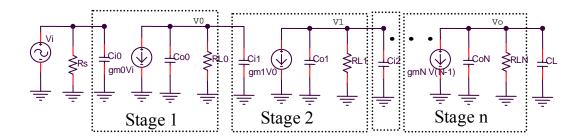

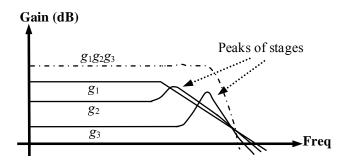

| Fig. 3-1  | 3-stage conventional multistage amplifier (MA)                                                                                                                                                                                                                                            | 43 |

| Fig. 3-2  | Implementation of amplifier stages in Fig. 3-1 (a) all stages are identical (b) gains as well as dominant poles are different                                                                                                                                                             | 44 |

| Fig. 3-3  | A simple stage for an <i>n</i> -stage conventional MA                                                                                                                                                                                                                                     | 45 |

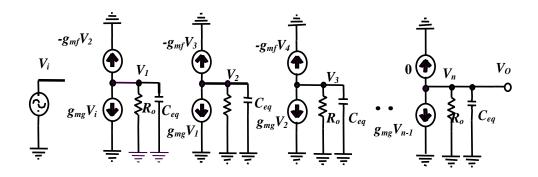

| Fig. 3-4  | A small signal model for <i>n</i> -stage amplifier, each stage modeled by the current source, load resistor and two capacitors (output capacitor of the stage and input capacitor of the next stage)                                                                                      | 45 |

# Page

| Fig. 3-5  | <i>N</i> -stage conventional MA with passive local feedback [63]                                                                                           | 48 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3-6  | An enhanced stage of limiting amplifier                                                                                                                    | 50 |

| Fig. 3-7  | (a) An enhanced stage of limiting amplifier with active load (b) a model for active load (c) the simplified model of the active load                       | 51 |

| Fig. 3-8  | Implementation of amplifier stages in Fig. 3-2 peaking is used within amplifiers                                                                           | 52 |

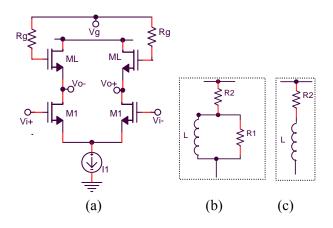

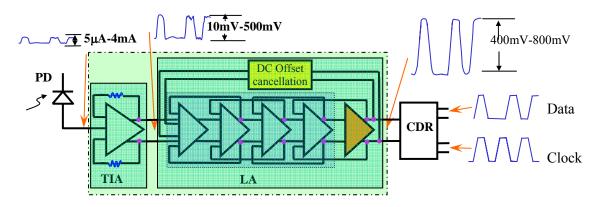

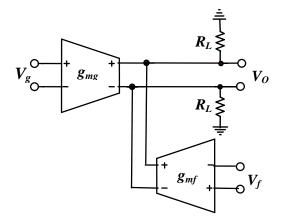

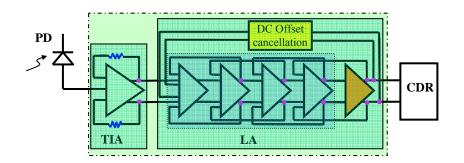

| Fig. 3-9  | Proposed TIA, LA and DC offset cancellation circuit                                                                                                        | 54 |

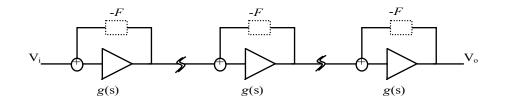

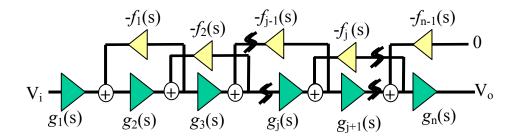

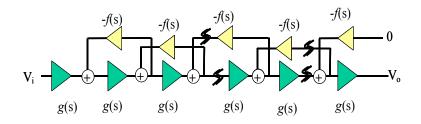

| Fig. 3-10 | General form of CMA topology                                                                                                                               | 54 |

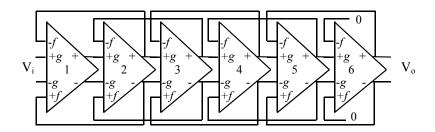

| Fig. 3-11 | Topology of the proposed MA (the uniform <i>n</i> -stage CMA)                                                                                              | 55 |

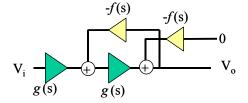

| Fig. 3-12 | Topology of a uniform 2-stage CMA                                                                                                                          | 56 |

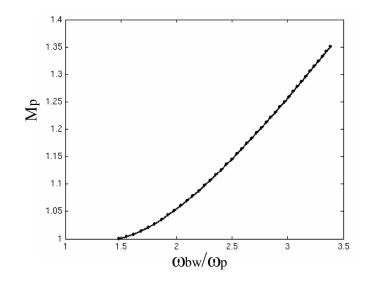

| Fig. 3-13 | $M_p$ vs. $\omega_{bw}/\omega_p$ of the 2-stage CMA                                                                                                        | 57 |

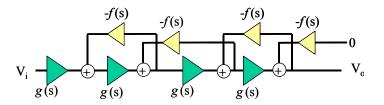

| Fig. 3-14 | Topology of the uniform 4-stage CMA                                                                                                                        | 58 |

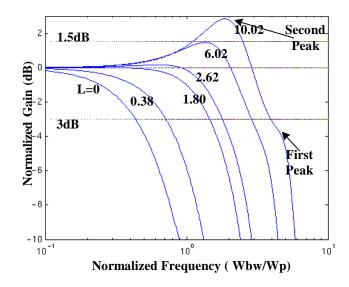

| Fig. 3-15 | A Matlab plot of the normalized gain of a 4-stage CMA for <i>L</i> =0, 0.38, 1.80, 2.62, 6.02 and 10.02                                                    | 59 |

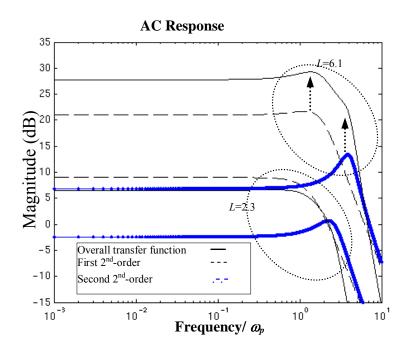

| Fig. 3-16 | A Matlab plot of magnitude of two 2 <sup>nd</sup> -order transfer functions and the overall function of 4-stage CMA                                        | 60 |

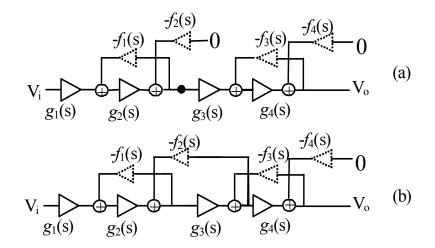

| Fig. 3-17 | The schemes of (a) cascaded two 2-stage CMAs, (b) 4-stage CMA                                                                                              | 61 |

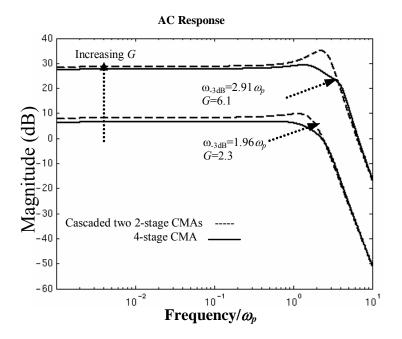

| Fig. 3-18 | A Matlab plot of magnitude of transfer functions of schemes in Figure 3-17 for different $G_s$ and $F=1$                                                   | 62 |

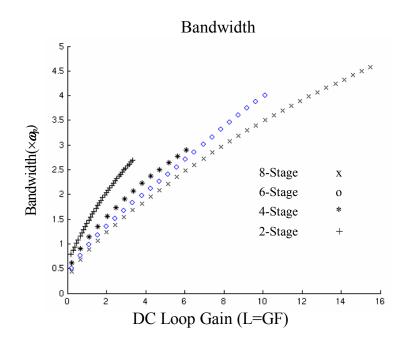

| Fig. 3-19 | A Matlab plot of the bandwidth of 2, 4, 6 and 8-stage CMA in $\omega_p$ for different DC loop gains (L).                                                   | 65 |

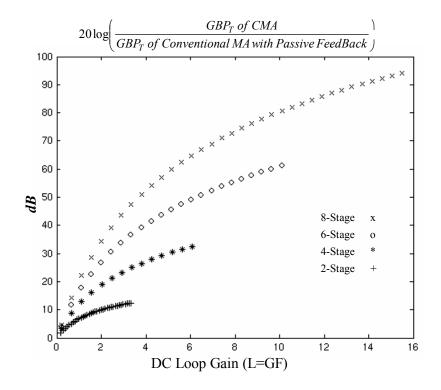

| Fig. 3-20 | A Matlab plot of the ratio of $GBP_T$ of <i>n</i> -stage CMA and conventional MA with passive feedback illustrated in Fig. 3-5 for <i>n</i> =2, 4, 6 and 8 |    |

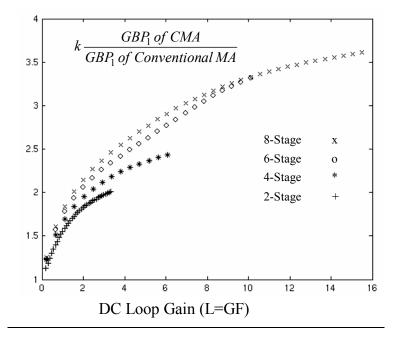

| Fig. 3-21 | A Matlab plot of the ratio of $GBP_1$ of 2, 4, 6 and 8-stage CMA and conventional MA for different $Ls$                                                    | 68 |

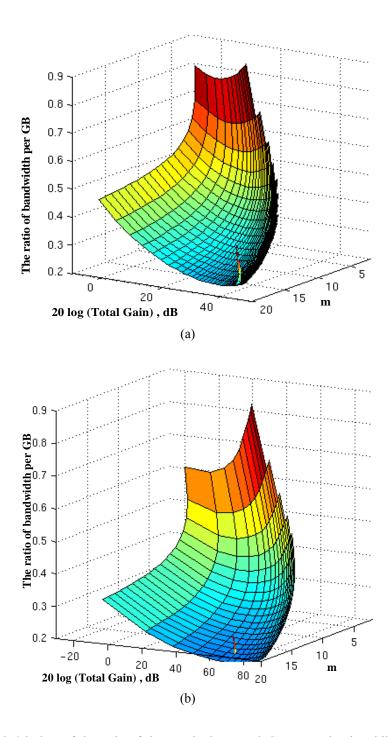

| Fig. 3-22 | Matlab 3d-plots of the ratio of the acquired $\omega_{bw}$ and <i>GB</i> vs. total gain while <i>m</i> is changed from 2 to 20 (a) 4-stage (b) 8-stage     | 69 |

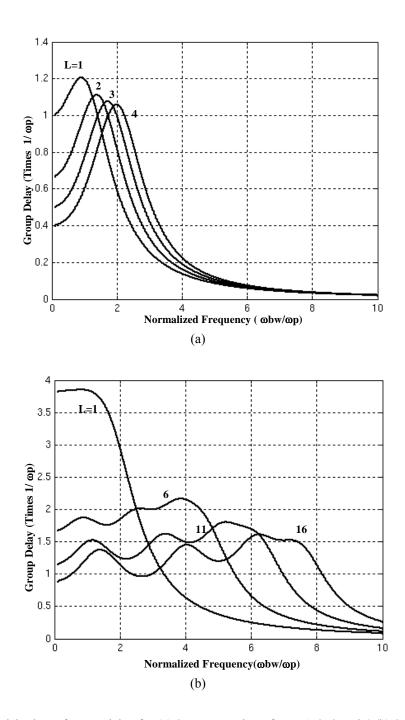

| Fig. 3-23 | Matlab plots of group delay for (a) 2-stage topology for $L=1, 2, 3$ and 4 (b) 8-stage topology for $L=1, 6, 11$ and 16                                                                                                                                                    | 73 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

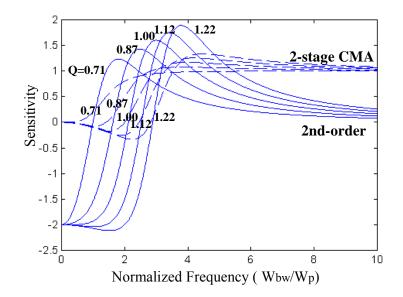

| Fig. 3-24 | A Matlab plot of the sensitivity of a 2-stage CMA with respect to the variation of corner frequency of one of its stages and sensitivity of a stage with $2^{nd}$ -order transfer function to the variation of the natural frequency. Q= 0.707, 0.866, 1, 1.118 and 1.225. | 75 |

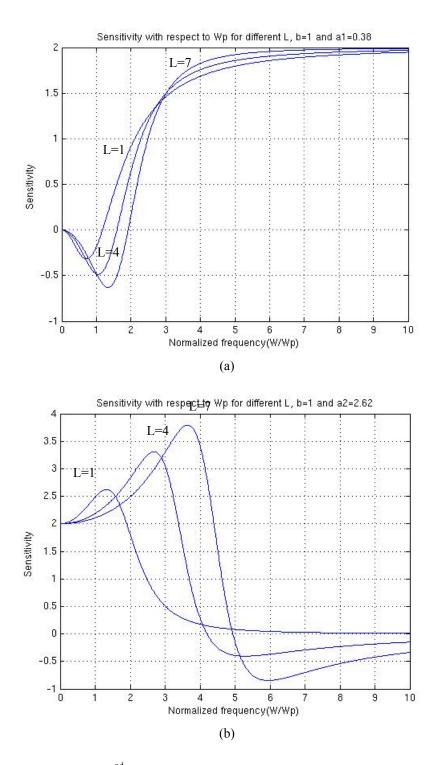

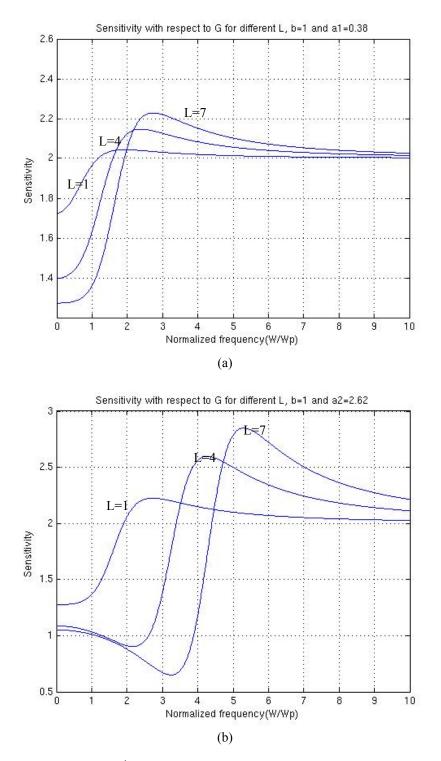

| Fig. 3-25 | Sensitivity of the 2 <sup>nd</sup> -order transfer functions of the gain of a 4-stage CMA with respect to $\omega_p$ when $L=1, 4, 7$                                                                                                                                      | 78 |

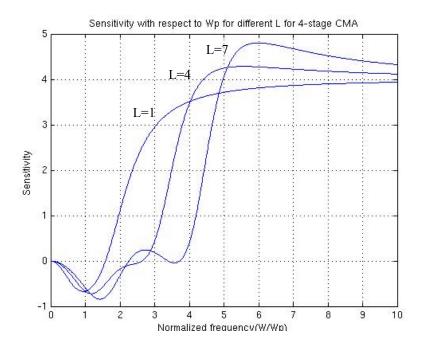

| Fig. 3-26 | Sensitivity of the gain transfer function of a 4-stage CMA with respect to $\omega_p$ when $L=1, 4, 7$                                                                                                                                                                     | 79 |

| Fig. 3-27 | Sensitivity of the $2^{nd}$ - order transfer functions of a 4-stage CMA's gain with respect to G when L=1, 4, 7                                                                                                                                                            | 80 |

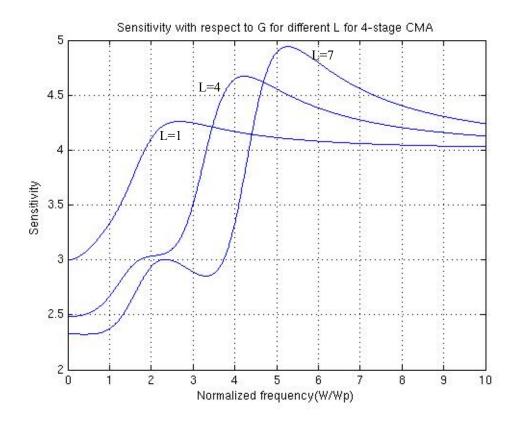

| Fig. 3-28 | Sensitivity of the gain of a 4-stage CMA with respect to G when $L=1, 4, 7$                                                                                                                                                                                                | 81 |

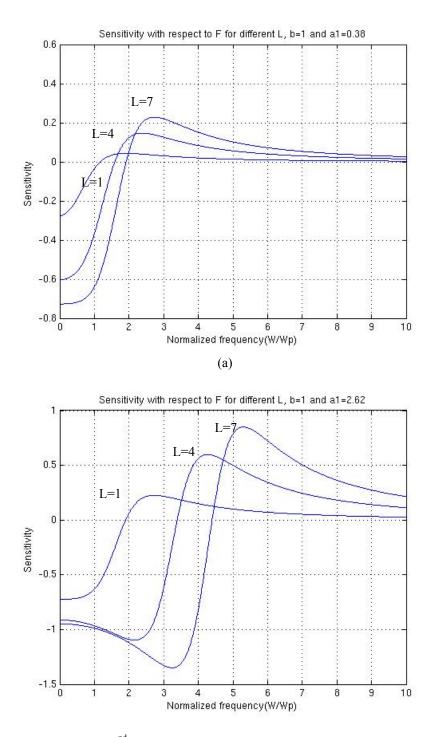

| Fig. 3-29 | Sensitivity of the $2^{nd}$ - order transfer functions of a 4-stage CMA's gain with respect to <i>F</i> when <i>L</i> =1, 4, 7                                                                                                                                             | 82 |

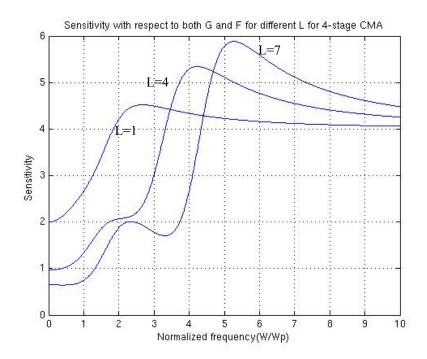

| Fig. 3-30 | Sensitivity of the transfer function of a 4-stage CMA's gain with respect to $F$ when $L=1, 4, 7$                                                                                                                                                                          | 83 |

| Fig. 3-31 | Sensitivity of the transfer function of a 4-stage CMA's gain with respect to $F$ and G (when they have the same variation) when $L=1, 4, 7$                                                                                                                                | 83 |

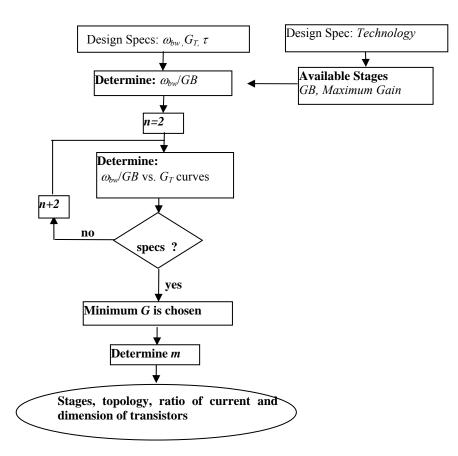

| Fig. 4-1  | Design flow chart of the CMA                                                                                                                                                                                                                                               | 87 |

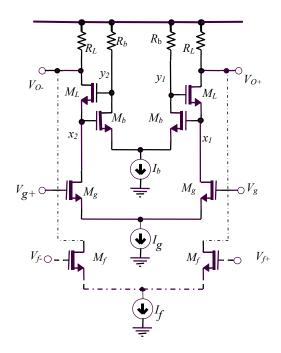

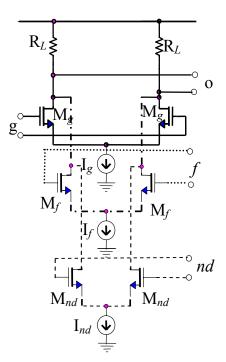

| Fig. 4-2  | CMA's single stage implementation                                                                                                                                                                                                                                          | 88 |

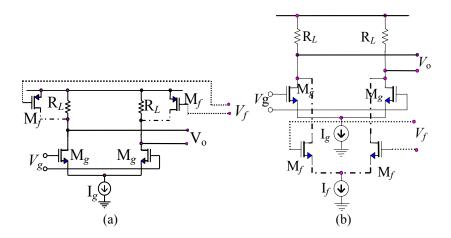

| Fig. 4-3  | Examples for circuits of stages of a simple <i>n</i> -stage CMA (a) with non-<br>controllable feedback amplifier (b) with controllable feedback amplifier                                                                                                                  | 89 |

| Fig. 4-4  | Circuitry of a 6-stage CMA                                                                                                                                                                                                                                                 | 89 |

| Fig. 4-5  | Small signal circuit of a simple uniform <i>n</i> -stage CMA with $G=g_{mg}R_o$ and $F=g_{mf}R_o$                                                                                                                                                                          | 90 |

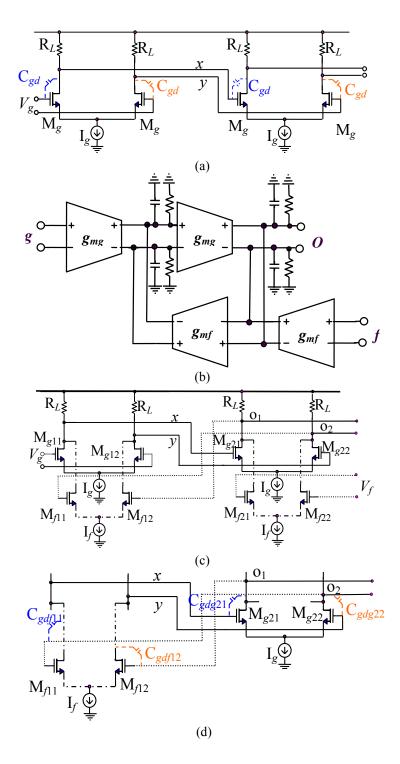

| Fig. 4-6  | Miller capacitances of gate-drain in an MA and a CMA (a) two stage of an MA (b) two stage of a CMA with output node capacitance of stages (c) a circuit implementation of two stages of CMA (d) a loop of circuit in (c)                                                   | 92 |

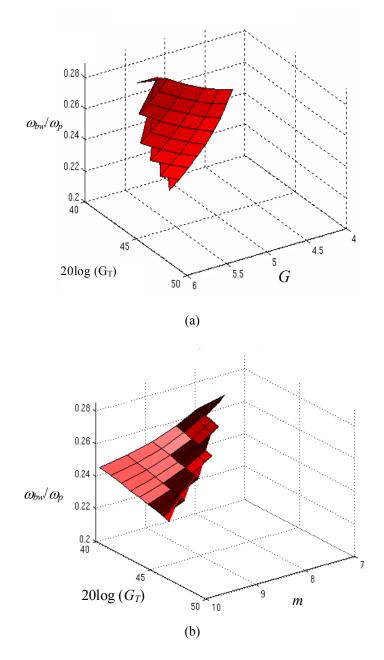

| Fig. 4-7  | A Matlab plot of $\omega_{bw}/GB$ vs. $G_T$ for the 6-stage CMA while group delay's ripple is less than 8% for (a) varying $G$ (b) varying $m$                                                                                                                             | 93 |

xv

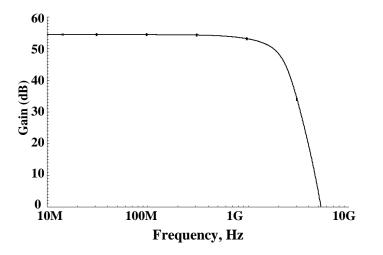

| Fig. 4-8  | Gain of the 6-stage CMA using the amplifier in Fig. 4-3(b) in 0.35µm CMOS                                                                                                                                                                                                                                                                                                              | 95  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

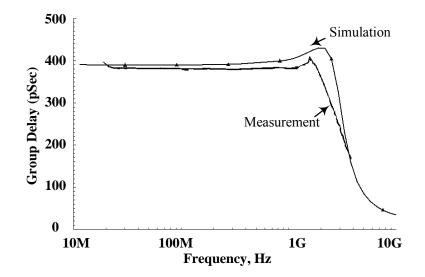

| Fig. 4-9  | Group delay of the 6-stage CMA using the amplifier in Fig. 4-3(b) in $0.35\mu m$ CMOS                                                                                                                                                                                                                                                                                                  | 96  |

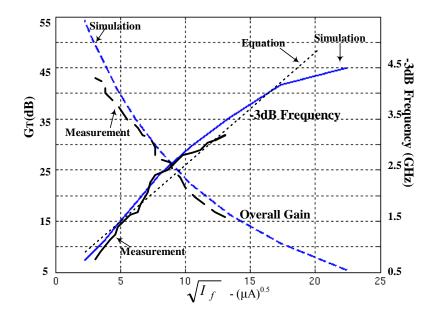

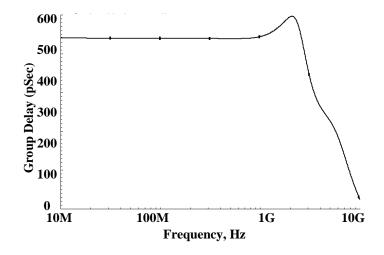

| Fig. 4-10 | Transistor level simulation of the overall gain and the bandwidth of the 6-stage CMA using the circuit in Fig. 4-3(b) as the amplifier stage, $I_f$ is swept from 5uA to 500uA while $I_g$ =2mA and $G$ =4.                                                                                                                                                                            | 96  |

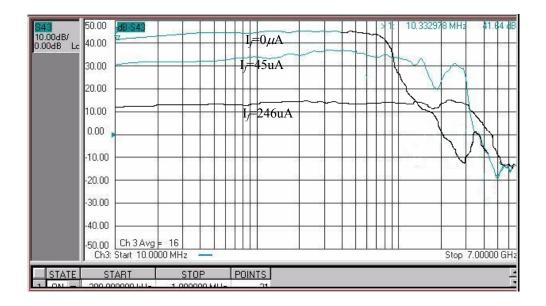

| Fig. 4-11 | The magnitude measurement for $I_g=2mA$ while $I_f$ is changed                                                                                                                                                                                                                                                                                                                         | 97  |

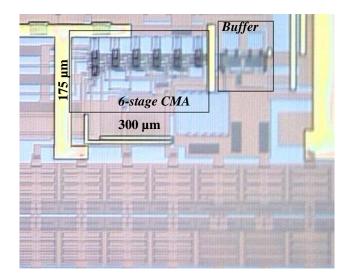

| Fig. 4-12 | The first 6-stage CMA's die microphotograph                                                                                                                                                                                                                                                                                                                                            | 98  |

| Fig. 4-13 | Eye diagram measurement results of the 6-stage CMA for $I_g=3mA$ and (a) 10mV peak-to-peak input voltage (b) 1V peak-to-peak input voltage                                                                                                                                                                                                                                             | 99  |

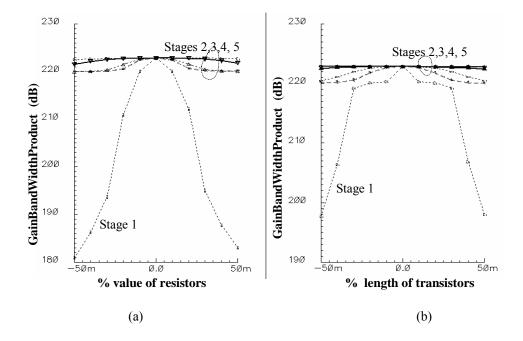

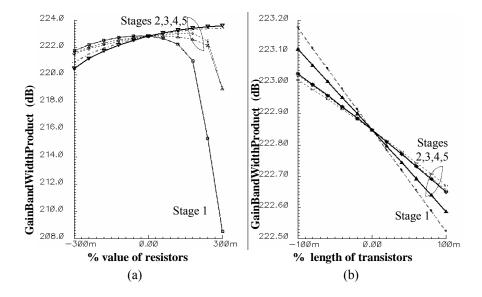

| Fig. 4-14 | Transistor level simulation results of the gain bandwidth product of the 6-<br>stage CMA using the circuit in Fig. 4-3(b) as the amplifier stage, $I_f = 24\mu A$ ,<br>$I_g = 2mA$ and $G=4$ while a mismatching of between pair load resistors and<br>length of paired transistors from stage 1, 2,,5, were swept from-5% to<br>5%. Mismatching in (a) resistors (b) transistors      | 100 |

| Fig. 4-15 | Transistor level simulation results of the gain bandwidth product of the 6-<br>stage CMA using the circuit in Fig. 4-3(b) as the amplifier stage, $I_f = 24\mu A$ ,<br>$I_g = 2mA$ and G=4 while the varying between load resistors and length of<br>transistors from stage 1, 2,, 5 were swept from-30% to 30% and -10% to<br>10%. Variation in (a) resistors (b) size of transistors | 101 |

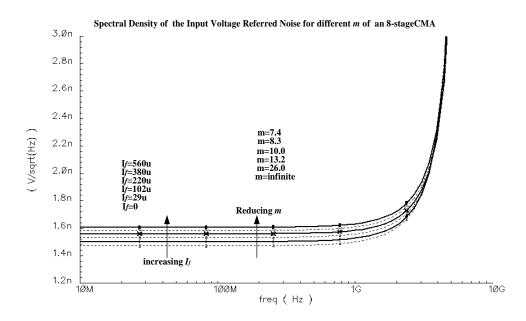

| Fig. 4-16 | Transistor level simulation of the input voltage referred noise of an 8-stage CMA while <i>m</i> is reduced from infinite to 26.0, 13.2,10.0,8.3 and 7.4 when $I_g=2mA$ and $G=4.3$                                                                                                                                                                                                    | 102 |

| Fig. 4-17 | A stage for the uniform implementation of CMA with minimum input capacitance.                                                                                                                                                                                                                                                                                                          | 103 |

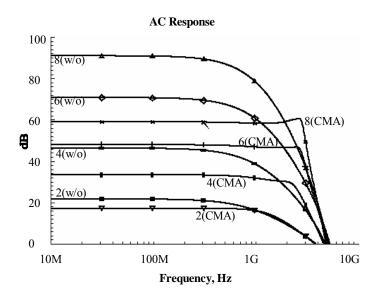

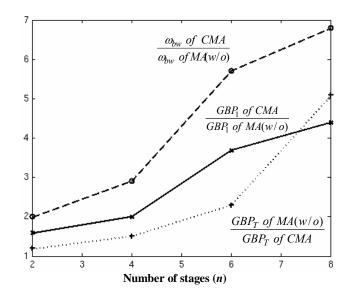

| Fig. 4-18 | AC response simulation of the gain of the CMAs and the conventional MAs (without) for $n=2, 4, 6$ and 8                                                                                                                                                                                                                                                                                | 105 |

| Fig. 4-19 | Ratio of bandwidth and $GBP_1$ of <i>n</i> -stage CMA and <i>n</i> -stage conventional MA (without) and the ratio of total gain bandwidth product (GBP <sub>T</sub> ) of <i>n</i> -stage conventional MA (without) and an <i>n</i> -stage CMA                                                                                                                                          | 105 |

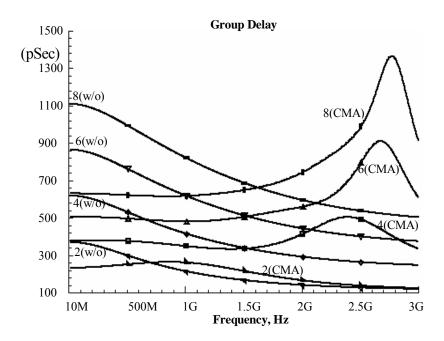

| Fig. 4-20 | Group delay simulation result of an <i>n</i> -stage conventional MA (without) and an <i>n</i> -stage CMA for $n=2, 4, 6$ and 8                                                                                                                                                                                                                                                         | 107 |

| Fig. 4-21 | Gain of the 6-stage CMA in 0.35um CMOS technology is made from Fig. 4-17                                                                                                                                       | 108 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4-22 | Group delay of the 6-stage CMA in 0.35um CMOS technology is made from Fig. 4-17                                                                                                                                | 109 |

| Fig. 4-23 | The magnitude of AC response simulation of the second 8-stage CMA using circuit in Fig. 4-17 as stage amplifier, $I_f$ is swept from 5uA to 875uA, while $I_g$ =2mA and $G$ =4                                 | 109 |

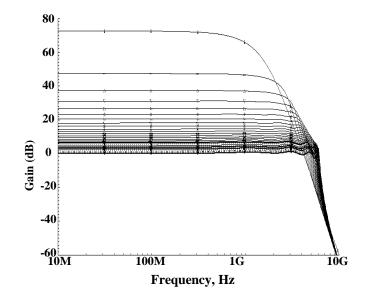

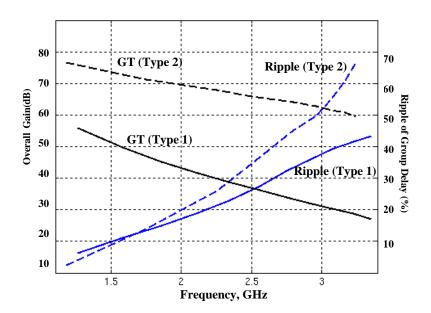

| Fig. 4-24 | Transistor level simulation of the overall gain of two 6-stage CMA, stages are circuit in Fig. 4-3(b) and in Fig. 4-18, the overall gain and the percentage of the ripple of the group delay vs. the bandwidth | 111 |

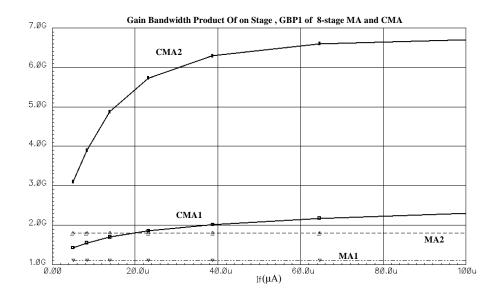

| Fig. 4-25 | The simulation results of the gain bandwidth product of one stage of 8-stage amplifiers of MA and CMA, stages are circuit in Fig. 4-3(b) and in Fig. 4-18 when $I_g=2$ mA.                                     | 111 |

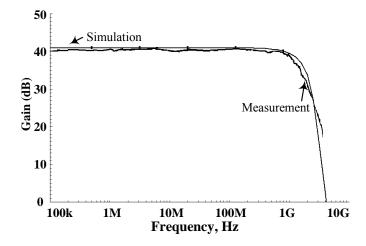

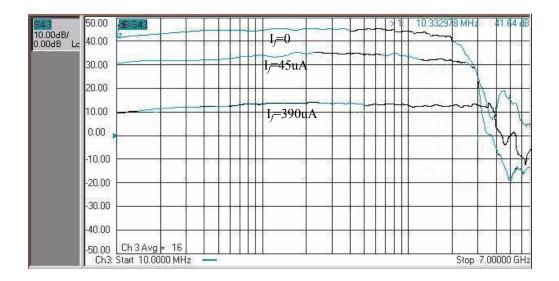

| Fig. 4-26 | The amplitude measurement results of the 6-stage CMA in 0.35um CMOS technology is made from circuit shown Fig. 4-17 when $I_b=1mA$ and $I_g=2mA$                                                               | 113 |

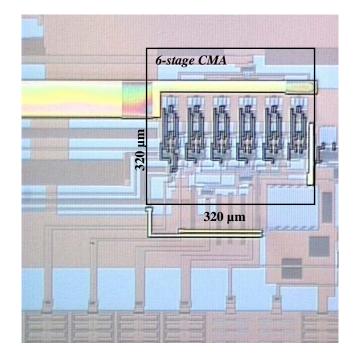

| Fig. 4-27 | Die microphotograph of the second 6-stage CMA                                                                                                                                                                  | 113 |

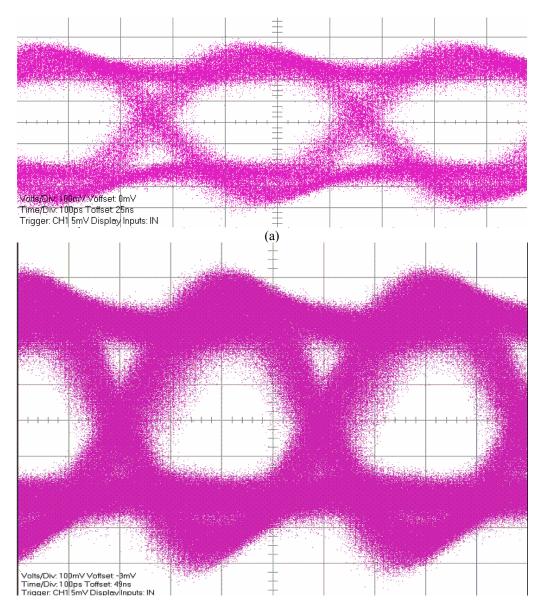

| Fig. 4-28 | Eye diagram measurement results when $I_g=2.47$ mA, $I_b=1.53$ mA for input voltage (a) Vi=2mV, $I_f=0$ (b) Vi=2V, $I_f=263$ uA (Div X=100pSec and Div Y=100mV).                                               | 115 |

| Fig. 5-1  | Proposed CDR architecture with an external reference                                                                                                                                                           | 117 |

| Fig. 5-2  | Proposed TIA, LA and DC offset cancellation circuit                                                                                                                                                            | 118 |

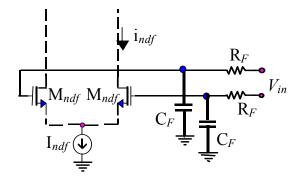

| Fig. 5-3  | The first stage of the CMA (see section IV-B-3)                                                                                                                                                                | 119 |

| Fig. 5-4  | The DC negative feedback scheme                                                                                                                                                                                | 120 |

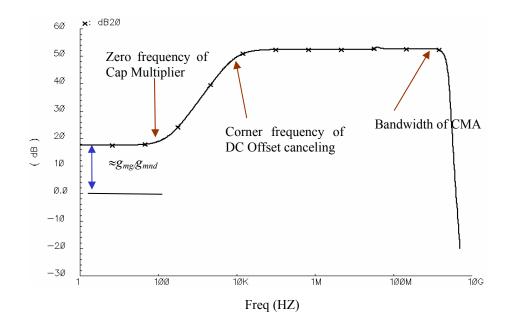

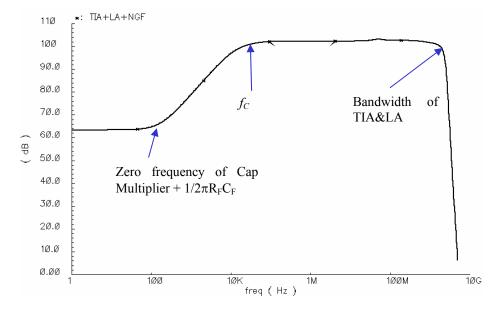

| Fig. 5-5  | Magnitude simulation results of the transfer function of a CMA while a DC negative feedback is used                                                                                                            | 121 |

| Fig. 5-6  | The magnitude of the transfer function of a front end amplifier of optical communication, a TIA and an LA when the LA employs a DC negative feedback in input stage                                            | 121 |

| Fig. 5-7  | Current mode capacitance multiplication technique                                                                                                                                                              | 122 |

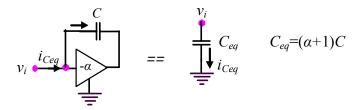

| Fig. 5-8  | Voltage mode capacitance multiplication techniques                                                                                                                                                             | 123 |

xvii

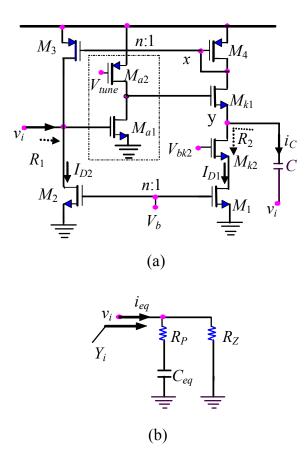

| Fig. 5-9  | The proposed capacitance multiplication technique                                                                                                                 | 123 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5-10 | Simplified circuit of the proposed capacitance multiplication, (a) circuit (b) equivalent model                                                                   | 124 |

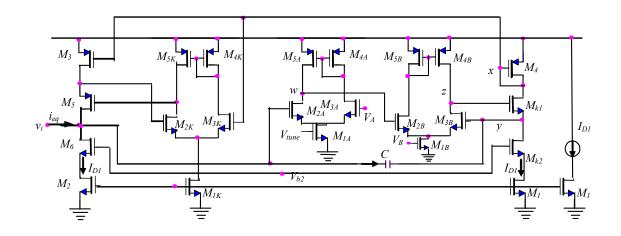

| Fig. 5-11 | Complete schematic of the capacitance multiplication circuit                                                                                                      | 128 |

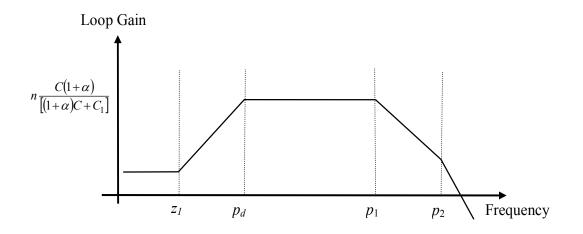

| Fig. 5-12 | Main loop of cap multiplier                                                                                                                                       | 129 |

| Fig. 5-13 | Amplitude of the main loop gain                                                                                                                                   | 130 |

| Fig. 5-14 | The capacitance multiplier circuit                                                                                                                                | 132 |

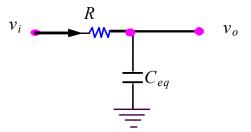

| Fig. 5-15 | The first order low pass filter used to measure capacitance multiplier                                                                                            | 132 |

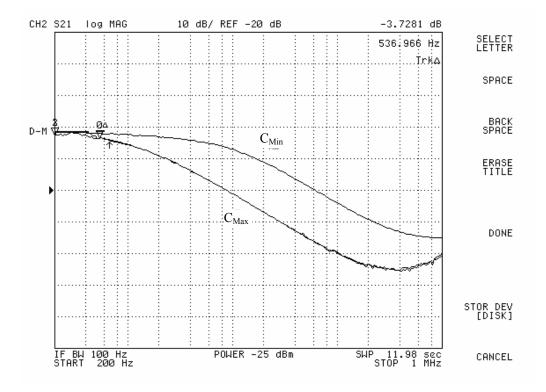

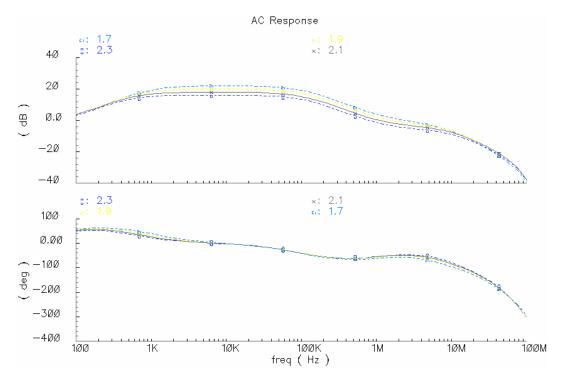

| Fig. 5-16 | The amplitude of transfer function $v_o(f)/v_i(f)$ of Fig 5-13, $C_{Min}$ : $\alpha \sim 0.39$ , n=10 and M=11, $C_{Max}$ : $\alpha \sim 8.7$ , n=10 and M=106.3  | 133 |

| Fig. 5-17 | The amplitude of transfer function $v_0(f)/v_i(f)$ of Fig. 5-13, $C_{Min}$ : $\alpha \sim 0.39$ , n=10 and M=11, $C_{Max}$ : $\alpha \sim 8.7$ , n=10 and M=106.3 | 134 |

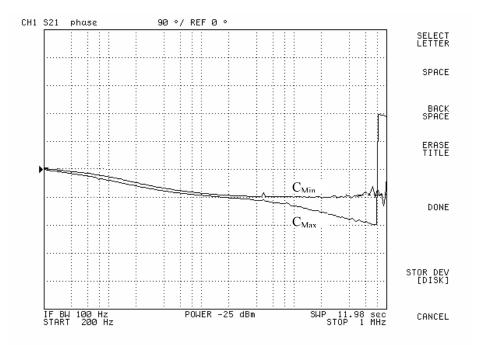

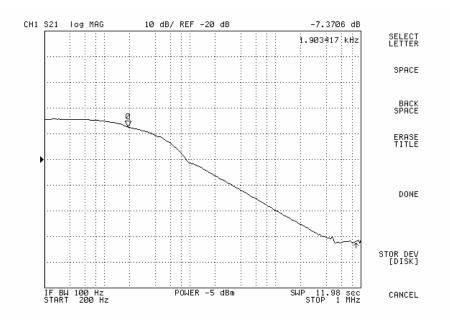

| Fig. 5-18 | The amplitude of transfer function $v_0(f)/v_i(f)$ of Fig. 5-13, $\alpha \sim 3$ , $n=10$ and $M=44$ and swing is 400mV peak-to-peak.                             | 135 |

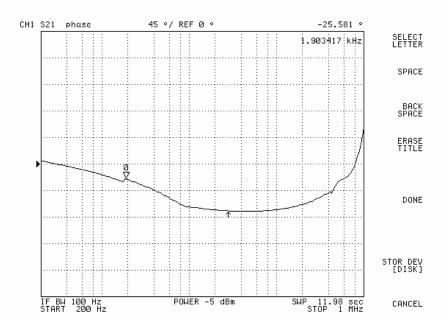

| Fig. 5-19 | The phase of transfer function $v_0(f)/v_i(f)$ of Fig. 5-13, $\alpha \sim 3$ , $n=10$ and $M=44$ and swing is 400mV peak-to-peak.                                 | 136 |

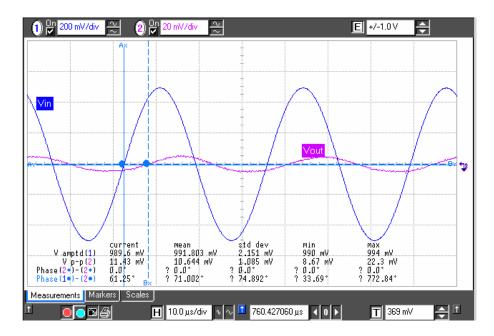

| Fig. 5-20 | The signals of $v_o(t)$ and $v_i(t)$ of Fig. 10, $\alpha \sim 17$ , $n=10$ and $M=200$ and swing is 990mV peak-to-peak and frequency is 30KHz.                    | 136 |

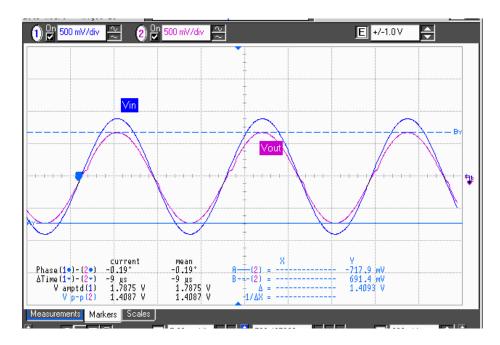

| Fig. 5-21 | The signals of $v_o(t)$ and $v_i(t)$ of Fig. 10, $\alpha \sim 5$ , $n=10$ and $M=66$ and swing is 1785mV peak-to-peak at 60Hz.                                    | 137 |

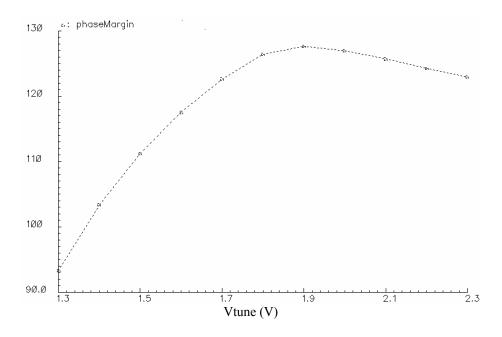

| Fig. 5-22 | Magnitude and phase of the loop I for different $V_{tune}$ (1.7-2.3) when C=80pF and <i>n</i> =10                                                                 | 137 |

| Fig. 5-23 | Phase margin of the loop I for different $V_{tune}$ (1.3-2.3) when C=80pF and $n=10$                                                                              | 138 |

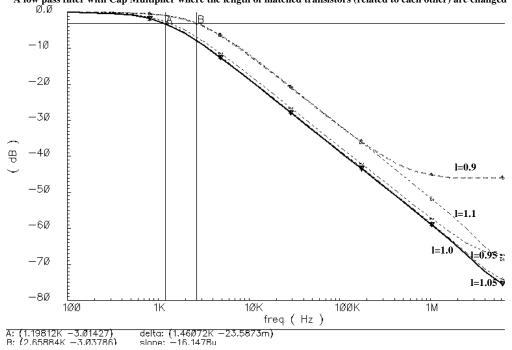

| Fig. 5-24 | Magnitude of the low pass filter's transfer function when the length of transistor $M_4$ is varied from -10% to 10%                                               | 138 |

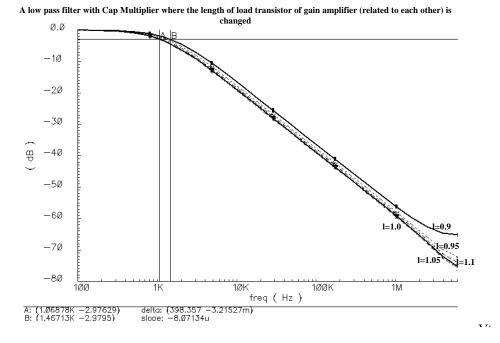

| Fig. 5-25 | Magnitude of the low pass filter's transfer function when the length of transistor $M_{5A}$ is varied from -10% to 10%                                            | 139 |

# LIST OF TABLES

| Table 2-1: Comparison of measurement results with existing reports                                                | . 39  |

|-------------------------------------------------------------------------------------------------------------------|-------|

| Table 3-1: A comparison of the maximum achievable bandwidth for the simple uniform         4, 6 and 8-stage CMA   | . 70  |

| Table 4-1: Parameters of the 6-stage CMA (stages are shown in Fig. 4-3 (b))                                       | . 97  |

| Table 4-2: The designed results of the 6-stage CMA (stages are shown in Fig. 4-3(b))                              | .97   |

| Table 4-3: Parameters of the <i>n</i> -stage CMA (stages are shown in Fig. 4-17)                                  | . 108 |

| Table 4-4: The simulation results of the 6-stage CMA with stage in Fig. 4-17 simulated in 0.35um CMOS Technology. | . 108 |

| Table 4-5: A comparison of measurement results with some recent reports                                           | . 114 |

# NOMENCLATURE

| AM               | Amplitude Modulation                |

|------------------|-------------------------------------|

| BER              | Bit Error Rate                      |

| BOM              | Burst Mode Optical Receivers        |

| CG               | Common Gate                         |

| CD               | Chromatic Dispersion                |

| CDR              | Clock and Data Recovery             |

| СМА              | Chained Multistage Amplifier        |

| CMOS             | Complementary Metal Oxide Silicon   |

| DEMUX            | Demultiplexer                       |

| GBP              | Gain Bandwidth Product              |

| $GBP_1$          | Gain Bandwidth Product of one stage |

| GBP <sub>T</sub> | Total Gain Bandwidth Product        |

| HBT              | Hetero junction-Bipolar Transistor  |

| ILD              | Injection-Laser Diode               |

| ISI              | Inter symbol interference           |

| LA               | Limiting Amplifier                  |

| LD               | Laser Driver                        |

| LED              | Light-Emitting Diode                |

| MA               | Multistage Amplifier                |

| MUX              | Multiplexer                         |

| OC               | Optical Communications              |

| OLT              | Optical line Terminal               |

| PD               | Photo Detector                      |

| PDA              | Personal Digital Assistants         |

| PM               | Phase Modulation                    |

| PMD              | Polarization Mode Dispersion        |

| PON              | Passive Optical Network             |

| RGC              | Regulated Cascode                   |

| SDH              | Synchronous Digital network         |

|                  |                                     |

| SERDES | serialization and deserialization |

|--------|-----------------------------------|

| SNR    | Signal to noise Ratio             |

| SONET  | Synchronous Optical Network       |

| TIA    | Transimpedance Amplifier          |

| VCO    | Voltage Controlled Oscillator     |

| XAUI   | Extent Attachment Unit Interface  |

|        |                                   |

### CHAPTER I

## INTRODUCTION

#### A Introduction and Motivation

The increasing demand for transferring higher volumes of data at higher speeds leads to the adoption of high speed wideband systems. High speed data cannot travel through copper (Cu) or over radio waves at fiber optic speeds [1]; besides, for wideband communications, signal-to-noise ratio (SNR) on copper (Cu) medium is insufficient, especially for large distances. Moreover, as speed increases the attenuation over Cu traces sharply increases, which causes signal loss and intersymbol interference (ISI) [2]. Fiber optical links can provide low attenuation at high speed and wideband communications for long-haul and short-haul systems without the electromagnetic interference from which coaxial and twisted pair cables suffer. Optical interconnections designed for low power consumption at high bit rates, offer an excellent means of overcoming data rate limitations imposed by conventional wiring between chips [1], [3]. Although networks of fiber-optic links have become a main stream for long-haul high speed communications, recent advances in laser diode output power combined with the global deployment of communications satellites and the need for more efficient communications have made free-space optics (or fiberless optics) very attractive.

Free-space optic links help fiber optic links in high traffic of data in short distance interconnections (<100m) such as cabinet level (1–100m), backplane level between boards (10cm–1m), chip to chip on a board (<10cm) and on-chip (<2cm) communications [3]. Demonstrations of high-bandwidth, long-range systems under realistic operating conditions further validate free-space optical communications, showing that it can provide high bandwidth,

This dissertation follows the style of IEEE Transactions on Circuits and Systems I.

and secure inexpensive communications for a variety of applications [4]. Using infrared beams [5], free-space optical interconnections find applications in laptop computers, cellular phones, digital cameras, computer peripherals, personal digital assistants (PDAs), and many other consumer electronics equipment [4].

Further demand for fiber and free-space optical communications and generation of highspeed networks, such as gigabit Ethernet, has led to the need for more flexible, low-cost and high performance circuits. Although using GaAs or Si-bipolar technologies for very high bandwidth designs is dominant, cost-effective optical link consumer products require low-power dissipation and small silicon area CMOS receivers. Furthermore, high performance wideband circuits can be designed on baseline CMOS processes with heterojunction-bipolar-transistors (HBTs) [6]. Designs based on standard ("generic") CMOS process technology are the main incentive in the consumer applications market [7].

CMOS technologies have already been used for the standard receivers, especially for portable systems and consumer devices because of their low-cost, small size, low-power and highly integrated analog and digital circuits, still though, further designs are needed for less power consumption and area occupancy.

## **B** Optical Communications Systems

An optical communications system is similar to the copper wire communications system in which fiber or free space replaces wire. Fig. 1-1 shows an optical communications system. At one end of the system there is a transmitter, where the digital data in different lines are combined by a multiplexer (MUX) in a single line. The digital signal is converted to electronic pulses to drive light-emitting diode (LED) or an injection-laser diode (ILD) to generate the light pulses. The light pulses are grouped into the fiber (or air), where they transmit themselves down the line [8]. The light bounces back and forth as it travels down the core in the fiber.

The attenuation of the light in fiber depends on several parameters, such as distance and wavelength of the light [8]. As the distance increases, the delivered power reduces. Several factors result in dispersion in transferring light waves in fiber links such as polarization mode dispersion (PMD) and chromatic dispersion (CD), which lead to intersymbol interference (ISI). In most free-space applications, the optical signal must be transmitted over long distances at high speed, and its signal level varies over a wide range due to fluctuations of attenuation in the atmosphere in different weather conditions [9]-[10] caused by fog, rain or snow.

Fig. 1-1 An optical communications system

In Fig. 1-1 when the light leaves the fiber, a photo detector (PD) in a receiver converts the light into an electrical signal for processing. The power of the electrical signal depends on several parameters such as distance, power of transmitter and parameters of transferring light (fiber or air), and also the power reduction in the photo detector [11]. The electrical signal is further amplified by two amplifiers: TransImpedance Amplifier (TIA) or preamplifier and Limiting Amplifier (LA) or main amplifier. Then from the amplified signal, clock and data

recovery (CDR) circuit retimes data and extracts the clock [12]. Finally, demultiplexed digital data and clock in different lines (see Fig. 1-1) are sent to signal processing systems. Fiberless optic links work in the same way. For example, low-power infrared beams transmit digital data through the air. Transmission is done between transceivers that are mounted on rooftops or behind windows.

There are a couple of well-known standards for transmission of digital data in optical communications systems. One of them is Synchronous Optical Network (SONET) specified in ANSI T1.105 [13]. A similar standard, Synchronous Digital Hierarchy (SDH), has been also established in Europe by UTI-T. SONET and SDH are technically consistent standards. Besides using SONET for short distance optical communications, the standards of serialization/deserialization (SERDES) for range DC bit rate up to 3.7Gbits/S [14] and XAUI (an 8/10 bits 3.1247Gbits/S, an IEEE 802.3ae interface for chip to chip) [15] are very popular.

In the Burst-Mode Optical Receivers (BOM) (the IEEE 802.3ah PX10 and PX20 standards [16]), on point-to-multipoint optical network configuration with no active elements in the interconnection, a single fiber can be shared among multiple users [17]. The power of the injected light of each subscriber's transmitters is different. Thus, at the optical line terminal (OLT) of a passive optical network (PON), the time-division multiplexed optical signal from the users is a sequence of burst data packets with varying powers [18]-[19]. Therefore, in addition to high sensitivity [e.g. -28dBm], high overload [e.g. 0dBm] must be handled to support these variable power burst packets in a wide input dynamic range of the OLT receivers [18], [20]-[21].

### C Optical Receiver

To clarify the operation of an optical receiver, a brief description of receiver components is presented here.

1. Transimpedance Amplifier (TIA) and Limiting Amplifier (LA)

As mentioned before, TIA's output voltage must be further amplified by a LA to reach the proper voltage swing necessary to drive the clock and data recovery (CDR) circuits. TIA must be sensitive enough to detect the weakest wideband signal (when receiver is far from transmitter). In other words, noise of TIA must be so low that the signal with a weak power can be amplified. Furthermore, when the power of the received signal is very high, the receiver must not be saturated and overloaded. So, the most challenging problem in TIA is to increase input dynamic range and extend bandwidth to reduce the jitter and distortion of the amplified signal [11].

The LA is a multistage amplifier with a high gain and a wide bandwidth with frequency response from DC range to several GHz. It provides the following decision circuit with uniform output level regardless of input swing level. Also, low phase shift deviation and small crossing point fluctuations must be insured over a wide input dynamic range to avoid degrading the sensitivity of the receiver system including the decision system [11]. The major challenges for the design of LA are to remove the DC offset (CMOS based circuits) with the minimum number of external components, to increase bandwidth and input voltage dynamic range.

To have a receiver with the capability to work at different bit rates and input powers, adjustable circuits are needed. This dissertation is proposing adjustable structures for TIA and LA and offers solutions to the challenges, mentioned in the previous paragraphs, that lead to performance enhancement of TIA and LA. Furthermore, an on chip circuit for DC offset cancellation circuit which employs a new capacitance multiplier is introduced.

### 2. Clock Data Recovery (CDR) Circuits

To extract data from the received distorted signals and synchronize them, a clock and data recovery (CDR) circuit is used. The CDR circuit has two main functions. First, it recovers the clock of data. Second, it transfers the synchronized data and the recovered clock to multiplexers

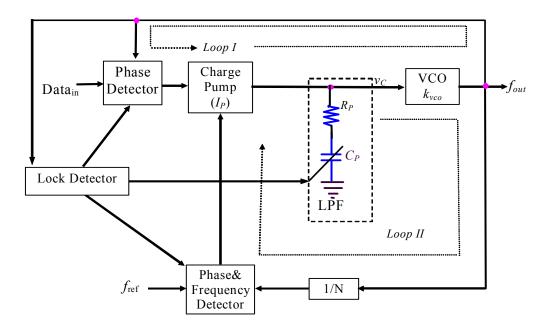

(see Fig. 1-1). CDR circuits have been implemented employing one or two loops. Each loop of a CDR circuit consists of a frequency and phase detector, a charge pump, a loop filter and a voltage controlled oscillator (VCO). A Two-loop CDR structure with external clock is shown in Fig. 1-2. One loop does phase-locking (loop I) and the other one does frequency-locking (loop II) [23].

Fig. 1-2 A two-loop CDR architecture

The lock detector monitors the difference between  $f_{out}$  and  $Nf_{ref}$  in the circuit in Fig. 1-2. It enables loop II and locks the oscillator to  $Nf_{ref}$ . When frequency error (the difference between  $f_{out}$  and  $Nf_{ref}$ ) is small, it disables loop II and enables loop I. Since each loop has a different bandwidth and damping factor, low pass filter needs different values of capacitances and resistors (this will be described more in chapter V). It means the capacitors and resistors must be switched or tuned. This dissertation proposes to use a tunable loop filter in CDR circuits.

### D General Concepts

To provide a better understanding of the goal of this dissertation, the following concepts are clarified:

## 1. Bandwidth

A wideband amplifier usually behaves as a low pass filter with some passband gain. The input signal is limited by amplifier's bandwidth as shown in Fig. 1-3. The frequency at which the voltage gain drops by -3dB in a wideband amplifier is referred to as bandwidth.

Fig. 1-3 (a) The model of a wideband amplifier (b) Magnitude of the gain transfer function of a wideband amplifier

An amplifier with limited bandwidth prevents a high frequency signal from reaching the maximum amplitude and it does not let the voltage drop to its lowest level in a short time. This is shown in simulation results illustrated in Fig. 1-4. This figure shows an input voltage and the output voltage of a wide bandwidth amplifier. As seen, there is a delay time between the input voltage and the output voltage. Depending on the sequence of "0"s and "1"s, the delay time is different; furthermore, the output voltage swings between different peaks. For example, during 1.5746uSec to 1.5764uSec (see Fig. 1-4(b)) the output voltage could not reach the 300mV and -

300mV. This is because of the amplifier is slow and the time needed for the output voltage to reach the maximum and the minimum voltage is more than unity interval time (bit time).

Fig 1-4 Amplifying a signal by an amplifier with a limited bandwidth (a) Output (b) Input

## 2. Eye Diagram

The performance of a high bit rate link can be measured from the eye diagram of the system [23]. The eye-pattern measurement is a time-domain measurement which is based on measuring signals in unity time interval (the bit time). An eye diagram simulation result is shown in Fig. 1-5. As explained for a limited bandwidth, signals cannot reach the peaks in the bit time. Furthermore, the transition times (rise and fall times) are slow and depending on the sequence of bits delay times are different. As a result the bits are overlapped and eye diagram of data would be closed. In CDR circuits, the horizontal opening gives a better sampling time interval for the received signal without error from intersymbol interference (ISI). Typically CDR circuit can tolerate higher than 50% horizontal closing [23]. The vertical height of eye opening is a measurement of the amplitude distortion of the signal. As the bandwidth is reduced, the vertical height of the eye's opening decreases and the eye closes [24]. In the digital gates of CDR circuits, the vertical closing converts to horizontal closing and it increases the jitter in CDR circuits.

In characterization of the wideband amplifiers, small signal model behaviors are employed. But using AC response, obtained from small signal analysis, cannot be very accurate in the characterization of amplifiers with high swing signals; while, time domain measurements such as eye diagram measurements do not suffer from this shortcoming.

Fig. 1-5 Eye diagram

## E Organization of Dissertation

Chapter I introduces briefly the optical communication systems with emphasis on receiver blocks. The concept and necessities of designing a TIA, and a new variable gain differential TIA are described in Chapter II. Chapter III discusses a simple design-oriented method used to design a multistage amplifier (MA) as a wideband amplifier. An introduction for the design of an LA will be presented. Also the concept of a new amplifier for LA, called chain multistage amplifier (CMA), is introduced. Design description and measurement results will be described further in chapter IV. The design principles of the new capacitance multiplier and its usage in tunable loop filters of CDR circuits and the DC offset cancellation circuit in the main amplifier will be presented in chapter V. Measurement results of the capacitance multiplier will be discussed in the same chapter. Finally, summary of the results and suggestions for further studies and research are given.

## **CHAPTER II**

## **TRANSIMPEDANCE AMPLIFIER**

#### A Introduction

In a typical optical receiver, the combination of a photo detector and transimpedance amplifier is called "Front End of Optical Receiver". The overall performance of an optical receiver crucially depends on the transimpedance amplifiers (TIA) performance. For example, the receiver sensitivity is a strong function of the noise and the bandwidth of TIA. In addition to the wide bandwidth, the transimpedance amplifier requires high transimpedance gain in conjunction with low input referred noise for reliable operation at low photodiode input currents. High overload current imposes more jitter in a high transimpedance gain and requires higher power consumption. Therefore, design of high-sensitive, low-jitter, low-power, wide-band and wide input dynamic range TIAs forms a group of conflicting performance requirements that sets the TIA for a challenging CMOS design problem.

In recent years various CMOS transimpedance amplifier architectures have been reported that essentially explore various input stages for isolating the large input capacitance of the photodiode from bandwidth determination, such as common-source (CS) [25]-[26], common-gate (CG) [27], or common-drain (CD) [28] stage. Further bandwidth extension techniques in TIA, such as capacitive, inductive or transformer [29]-[30] peaking techniques [7], capacitive feedback [26] and using positive feedback to emulate a negative capacitance [31] have been adopted. A commonly used topology is the Regulated Cascode Transimpedance Amplifier (RGC TIA). Its relatively low input impedance, wide bandwidth and high stability have made it very attractive for wideband communications applications; however, low overload current is the most important drawback of this amplifier.

As discussed, a wide range of input current is possible especially for wireless and burstmode optical receivers [16] in order to accommodate variable link distances. The combination of varying link lengths and channel losses (due to propagation through fiber or free space) requires wide input dynamic range of the preamplifier. However, finding a balance between dynamic range and power consumption requirements can be a challenge, since keeping bias currents small degrades the preamplifier's ability to handle large signals. To overcome overloading and nonlinearity, some designers have used transistor switching to adjust the feedback impedance [31]-[32]. Nonetheless, a flexible variable gain with a large gain dynamic range could not be easily implemented utilizing switching transistors in high frequency applications.

This chapter introduces a new architecture for a variable gain CMOS TIA. The proposed topology uses a modified regulated cascode (RGC) TIA stage to obtain an efficient, high-speed variable-gain TIA. The principle by way of gain, bandwidth, and input-referred noise analysis is developed in detail for this TIA. In addition, a fabricated prototype chip implementation of the proposed TIA using the low-cost TMSC 0.35µm CMOS process technology is reported.

## B Circuit Design and Analysis

#### 1. Parameters of TIA

The sensitivity of a TIA is the minimum input current which can be converted to voltage when the bit error rate (BER) is acceptable. The maximum tolerated noise can be calculated via the desirable BER of the application. The BER is given [23] by

$$BER = \frac{1}{2} \operatorname{erfc}\left(\frac{Q}{\sqrt{2}}\right) = \frac{1}{Q\sqrt{2\pi}} \exp\left(\frac{Q^2}{\sqrt{2}}\right)$$

(2-1)

where

$$Q = \frac{I_{\min}}{I_{n,rms}}$$

(2-2)

$I_{\min}$  is the minimum input current and  $I_{n,rms}$  is the *rms* (root of mean-square) of the input referred current noise ( $\overline{i_{n,in}}^2$  is the spectral density of the input referred current noise) of TIA. The maximum noise of transimpedance amplifier can be obtained from BER and  $I_{\min}$ . To have a specific bit error rate, noise must be less than what is calculated from equations 2-1 and 2-2 for the minimum current.

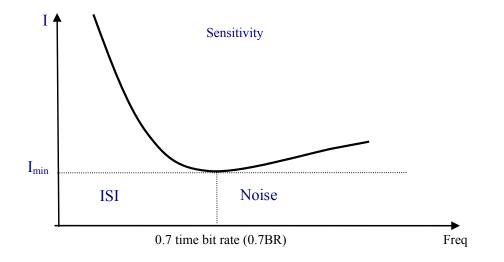

As the bandwidth is reduced, intersymbol interference increases, however, using a higher bandwidth collects more noise. Fig. 2-1 depicts sensitivity (detectable current) as a function of bandwidth.

Fig. 2-1 Sensitivity of transimpedance amplifier, sensed current via bandwidth of transimpedance

In addition to TIA's noise, the shot noise of photo detector, which can be considerably big, depending on technology and implementation of the detector increases the minimum required light power in a receiver [24]. To reduce the total integrated noise, the bandwidth must be minimized. As explained, reducing the bandwidth introduces the intersymbol interference in random data and it closes the eye diagram both vertically and horizontally. There is a rule of thumb used for intuitively estimating the required bandwidth for a special bit rate. This is obtained via modeling TIA as a first order transfer function with a slight amount of ISI while performance of TIA is still acceptable in practical applications. Based on this rule for an amplifier, the bandwidth must be approximately 0.7 times bit rate [23]. For example, for SONET OC-48 a bandwidth of 1.75GHz is recommended for TIA.

The third important parameter of a TIA is offering a high current to voltage conversion. Increasing transimpedance gain increases the chance of amplifying a weaker signal to a level detectable by the main amplifier; however, at a high photodiode input current a low gain is required. In SERDES (serialization and deserialization) [14] implementations, such an amplifier (TIA) has to work in a wide input current dynamic range from 100uA to 4mA [22], [33], and for OC-48 applications a 5uA to 0.5mA input current must be amplified.

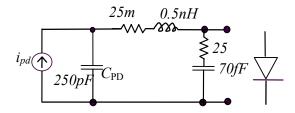

## C TIA's Circuit Design Principles

The received optical pulse signal is converted by a reverse-biased p-i-n photodiode (or other types of photodiodes such as *pn* and Avalanche [23] diode etc.) into an input electron–hole drift current ( $i_{in}$ ) driving the input node of TIA. A typical lumped circuit model for a real p-i-n photodiode [30], [34]-[38] is illustrated in Fig. 2-2. In this dissertation for simulation, a simplified model consisting of a capacitance ( $C_{PD}$ =500*fF*) and current source ( $i_{PD}$ ) is used and the other parasitic elements of photodiode are ignored.

Fig. 2-2 Small signal model of photo detector

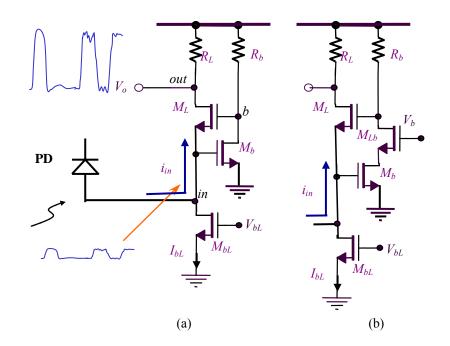

# 1. Common Gate TIA (CG TIA) with $g_m$ -boosting Amplifier

The topology of the common gate (CG) transimpedance amplifier with  $g_m$ -boosting amplifier is shown in Fig. 2-3 (a). This type of TIA is also called regulated cascode (RGC) TIA. RGC TIAs were previously reported in [33]–[38]. The input node of CG TIA is the source node of the CG nMOS device ( $M_L$ ). The -3dB bandwidth of the overall amplifier is determined by the low input impedance of the CG TIA and the high photodiode input capacitance (and hence, its poor intrinsic bandwidth). The energy of light converted to current  $i_{in}$  passes through transistor  $M_L$  and develops a voltage drop on resistor  $R_L$ . In Fig. 2-3 (b), a cascode amplifier is used as the boosting amplifier.

Fig. 2-3 Common gate (CG) transimpedance amplifier with  $g_m$ -boosting amplifier (a) simple amplifier (b) cascode amplifier

# 2. Bandwidth and Transimpedance Gain

Figure 2-4 illustrates a small signal model of CG TIA with  $g_m$ -boosting amplifier (illustrated in Fig. 2-3(a)). The equations for the current in nodes *in*, *out* and *b* can be written as

$$v_{i} = \left(\frac{1}{g_{dsbL} + sC_{in}}\right) \left\{ i_{pd} + \left(v_{b} - v_{i}\right) \left[ g_{mL} + s\left(C_{gsL} + C_{gdb}\right) \right] \right\}$$

(2-3)

$$v_{O} = \left(\frac{1}{g_{L} + sC_{o}}\right) \left[ \left(-v_{b} + v_{i}\right) g_{mL} + \left(v_{b} - v_{o}\right) sC_{gdL} \right]$$

(2-4)

$$g_{b}v_{b} + v_{i}g_{mb} = (-v_{b} + v_{i})s(C_{gsL} + C_{gdb}) + (-v_{b} + v_{o})sC_{gdL}$$

(2-5)

The transimpedance can be approximated as

$$\frac{g_{mL}(g_{mb}R_{b}+1)}{\left[g_{L}+s(C_{o}+C_{gdL})\right]\left[g_{dsbL}+g_{mL}+s(C_{in}+C_{gsL}+C_{gdb})\right]\left[1+sR_{b}(C_{gdL}+C_{gsL}+C_{gdb})\right]\left[+\left[g_{mL}+s(C_{gsL}+C_{gdb})\right]R_{b}g_{mb}-sR_{b}(C_{gsL}+C_{gdb})\right]\right]}$$

(2-6)

Equation 2-6 can be simplified as

$$z_{T}(s) \approx \frac{g_{mL}(1+g_{mb}R_{b})}{\left[g_{L}+s(C_{o}+C_{gdL})\right]\left[g_{dsbL}+g_{mL}(1+g_{mb}R_{b})+s\left[C_{in}+(1+g_{mL}R_{b})(C_{gsL}+C_{gdb})\right]\right]}$$

(2-7)

where  $g_{mL}$  and  $g_{mb}$ , are transconductance of  $M_L$  and  $M_b$ ;  $C_{gdb}$  and  $C_{gdL}$  are gate-to-drain capacitances of  $M_L$  and  $M_b$ , respectively. Also  $C_{gsL}$  is the gate-source capacitance of  $M_L$  and  $g_L=1/R_L$ .  $C_{in}$  is contributed from photodiode capacitance, capacitances of gate-source of  $M_b$ , source-substrate junction of  $M_L$  and drain-substrate junction of  $M_{bL}$  (If the photo detector is an external chip component, the pad and ESD protection capacitance would be added to  $C_{in}$ .). The low frequency transimpedance gain (called midband gain) of the amplifier is

$$z_T(s)\Big|_{s=0} \approx R_L \tag{2-8}$$

Fig. 2-4 Small signal model of common gate (CG) transimpedance amplifier

The dominant pole of the transimpedance gain can be given as

$$p_{1} \approx \frac{g_{mL}(1 + g_{mb}R_{b})}{C_{in} + (1 + g_{mL}R_{b})(C_{gsL} + C_{gdb})}$$

(2-9)

For a practical case, the second term of the denominator of Eq. (2-6) can be ignored. Then the dominant pole can be approximated as

$$p_1 \approx \frac{g_{mL}(1 + g_{mb}R_b)}{C_{in}}$$

(2-10)

The dominant pole of CG TIA is  $p_d = g_{mL} / sC_{in}$ . That means using  $g_m$ -boosting amplifier can expand the bandwidth  $(1 + g_{mb}R_b)$  times that of the regular CG TIA. Equation 2-10 shows that using booster expands the bandwidth, when  $C_{in}$  (the equivalent of the capacitance in input of TIA) is comparable or bigger than  $(1 + g_{mL}R_b)(C_{gsL} + C_{gdb})$ . The DC input impedance can be calculated from

$$z_{in}|_{s=0} \approx \frac{1}{g_{mL}(1+g_{mb}R_b)}$$

(2-11)

To match the input impedance with low resistivity impedance (like 50 Ohms transmission lines), the gain of boosting amplifier can be adjusted. Increasing the current of bias of the transistor  $M_L$  and using a bigger transistor ( $M_L$ ) would somewhat help to reduce input impedance. Also using cascode amplifier as shown Fig. 2-3 (b) would help to reduce input capacitance and to increase boosting gain that helps to lower input impedances.

To have a higher transimpedance gain, a bigger  $R_L$  must be used. This shifts the pole (in equation 2-7) related to output node to lower frequencies and even makes it closer to the dominant pole. Therefore, it degrades the phase of the transimpedance gain in frequencies around corner frequency. For a limited power supply, to keep transistor  $M_L$  in saturation region when using a big  $R_L$ , bias current of  $M_L$  ( $I_L$ ) must be reduced. On the other hand, decreasing  $I_L$ reduces  $g_{mL}$  and shifts the dominant pole to lower frequencies. Thus, that mandates a tradeoff between transimpedance gain and bandwidth.