Universidade Estadual de Campinas Instituto de Computação

### Jonathas Evangelista da Silveira

### **Exploring Associative Processing** with the RV-Across simulator

### Uma exploração de Processamento Associativo com o simulador RV-Across

CAMPINAS 2021

#### Jonathas Evangelista da Silveira

#### Exploring Associative Processing with the RV-Across simulator

#### Uma exploração de Processamento Associativo com o simulador RV-Across

Dissertação apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Dissertation presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Master in Computer Science.

#### Supervisor/Orientador: Prof. Dr. Lucas Francisco Wanner

Este exemplar corresponde à versão final da Dissertação defendida por Jonathas Evangelista da Silveira e orientada pelo Prof. Dr. Lucas Francisco Wanner.

#### CAMPINAS 2021

#### Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Ana Regina Machado - CRB 8/5467

| Si39e | Silveira, Jonathas Evangelista da, 1996-<br>Exploring associative processing with the RV-Across simulator / Jonathas<br>Evangelista da Silveira. – Campinas, SP : [s.n.], 2021.                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Orientador: Lucas Francisco Wanner.<br>Dissertação (mestrado) – Universidade Estadual de Campinas, Instituto de<br>Computação.                                                                                                                                                                     |

|       | <ol> <li>Sistemas de memória de computadores.</li> <li>Processamento associativo.</li> <li>Eficiência energética.</li> <li>Wanner, Lucas Francisco,</li> <li>1981</li> <li>Universidade</li> <li>Estadual de Campinas.</li> <li>Instituto de Computação.</li> <li>III.</li> <li>Título.</li> </ol> |

#### Informações para Biblioteca Digital

Título em outro idioma: Uma exploração de processamento associativo com o simulador **RV-Across** Palavras-chave em inglês: Computer storage devices Associative processing Energy efficiency Área de concentração: Ciência da Computação Titulação: Mestre em Ciência da Computação Banca examinadora: Lucas Francisco Wanner [Orientador] Alba Cristina Magalhães Alves de Melo Rodolfo Jardim de Azevedo Data de defesa: 12-03-2021 Programa de Pós-Graduação: Ciência da Computação

Identificação e informações acadêmicas do(a) aluno(a) - ORCID do autor: https://orcid.org/0000-0002-7398-3947 - Currículo Lattes do autor: http://lattes.cnpq.br/2403081259708319

Universidade Estadual de Campinas Instituto de Computação

#### Jonathas Evangelista da Silveira

#### Exploring Associative Processing with the RV-Across simulator

### Uma exploração de Processamento Associativo com o simulador RV-Across

#### Banca Examinadora:

- Prof. Dr. Lucas Francisco Wanner IC/UNICAMP

- Profa. Dra. Alba Cristina Magalhães Alves de Melo CIC/Universidade de Brasília

- Prof. Dr. Rodolfo Jardim de Azevedo IC/UNICAMP

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

Campinas, 12 de março de 2021

### Acknowledgements

First, I thank God for providing me all the knowledge I have (*Prv* 1 : 7) and for the salvation (*Eph* 2 : 8) for the grace. As Abraham Kuyper (ex-minister of the Netherlands) once said, and I agree: "There is not a square inch (including the *bits*) in the whole domain of our human existence over which Christ, who is sovereign over all, does not say: 'Mine!'".

Second, I thank my family for providing me with all the necessary spiritual, emotional and financial support. I am grateful to my wife Camila Silveira who was with me throughout my master's degree holding me and acting graciously towards me. I thank my parents Denilson Silveira and Claudiane Silveira for being models of effort, work and dedication. Something that science cannot explain. I am also grateful for the support of my brother Alexander Silveira and his wife Edna, who have always been around in difficult times. I am grateful for the unconditional support of my father-inlaw João Filho, my mother-in-law Dona Leonice Abreu and my brother-in-law João Paulo. Finally, I thank two great men, Laysson Luz and Ramon Nepomuceno, who helped me a lot and that I consider as my family.

Third, I thank my advisor prof. dr. Lucas Wanner for giving me the opportunity to learn more about computing and for guiding me through these two years of learning. I also thank my undergraduate advisor prof. dr. Ivan Silva for teaching about computing and life. I thank my companions Isaías Felzmman and João Filho who helped me in my work, especially in scientific production. Finally, I thank my colleagues at LSC who taught me a lot about science and made this period lighter.

Finally, I thank Unicamp for all its support as an institution. This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001.

### Resumo

Múltiplos trabalhos apontam para um gargalo de desempenho entre o processador e a memória. Esse gargalo se destaca na execução de aplicações, como o Aprendizado de Máquina, que processam uma grande quantidade de dados. Nessas aplicações, a movimentação de dados representa uma parcela significativa tanto em termos de tempo de processamento quanto de consumo de energia. O uso de novas arquiteturas multi-core, aceleradores e Unidades de Processamento Gráfico (*Graphics Processing Unit* — GPU) pode melhorar o desempenho desses aplicativos por meio do processamento paralelo. No entanto, a utilização dessas arquiteturas não elimina a necessidade de mover dados, que passam por diferentes níveis de uma hierarquia de memória para serem processados.

Este trabalho explora o Processamento em Memória (*Processing in Memory* — PIM), especificamente o Processamento Associativo, como alternativa para acelerar as aplicações, processando seus dados em paralelo na memória permitindo melhor desempenho do sistema e economia de energia. O Processamento Associativo fornece computação paralela de alto desempenho e com baixo consumo de energia usando uma Memória endereçável por conteúdo (*Content-Adressable Memory* — CAM). Através do poder de comparação e escrita em paralelo da CAM, complementado por registradores especiais de controle e tabelas de consulta (*Lookup Tables*), é possível realizar operações entre vetores de dados utilizando um número pequeno e constante de ciclos por operação.

No trabalho, analisamos o potencial do Processamento Associativo em termos de tempo de execução e consumo de energia em diferentes *kernels* de aplicações. Para isso, desenvolvemos o RV-Across, um simulador de Processamento Associativo baseado em RISC-V para teste, validação e modelagem de operações associativas. O simulador facilita o projeto de arquiteturas de processamento associativo e próximo à memória, oferecendo interfaces tanto para a construção de novas operações quanto para experimentação de alto nível. Criamos um modelo de arquitetura para o simulador com processamento associativo e o comparamos este modelo com as alternativas baseadas em CPU e *multi-core*. Para avaliação de desempenho, construímos um modelo de latência e energia fundamentado em dados da literatura. Aplicamos o modelo para comparar diferentes cenários, alterando características das entradas e o tamanho do Processador Associativo nas aplicações.

Nossos resultados destacam a relação direta entre o tamanho dos dados e a melhoria potencial de desempenho do processamento associativo. Para a convolução 2D, o modelo de Processamento Associativo obteve um ganho relativo de 2x em latência, 2x em consumo de energia, e 13x no número de operações de *load/store*. Na multiplicação de matrizes, a aceleração aumenta linearmente com a dimensão das matrizes, atingindo 8x para matrizes de 200x200 bytes e superando a execução paralela em uma CPU de 8 núcleos. As vantagens do Processamento associativo evidenciadas nos resultados revelam uma alternativa para sistemas que necessitam manter um equilíbrio entre processamento e gasto energético, como os dispositivos embarcados. Finalmente, o ambiente de simulação e avaliação que construímos pode habilitar mais exploração dessa alternativa em diferentes aplicações e cenários de uso.

### Abstract

Many works have pointed to a performance bottleneck between Processor and Memory. This bottleneck stands out when running applications, such as Machine Learning, which process large quantities of data. For these applications, the movement of data represents a significant fraction of processing time and energy consumption. The use of new multi-core architectures, accelerators and Graphic Processing Units (GPU) can improve the performance of these applications through parallel processing. However, utilizing these architectures does not eliminate the need to move data, which are transported through different levels of a memory hierarchy to be processed.

Our work explores Processing in Memory (PIM), and in particular Associative Processing, as an alternative to accelerate applications, by processing data in parallel in memory, thus allowing for better system performance and energy savings. Associative Processing provides high-performance and energy-efficient parallel computation using a Content-Addressable Memory (CAM). CAM provides parallel comparison and writing, and by augmenting a CAM with special control registers and Lookup Tables, it is possible to perform computation between vectors of data with a small and constant number of cycles per operation.

In this work, we analyze the potential of Associative Processing in terms of execution time and energy consumption in different application kernels. To achieve this goal we developed RV-Across, an Associative Processing Simulator based on RISC-V for testing, validation, and modeling associative operations. The simulator eases the design of associative and near-memory processing architectures by offering interfaces to both building new operations and performing high-level experimentation. We created an architectural model for the simulator with associative processing and evaluated it by comparing it with the CPU-only and multi-core models. The simulator includes latency and energy models based on data from literature to allow for evaluation and comparison. We apply the models to compare different scenarios, changing the input and size of the Associative Processor in the applications.

Our results highlight the direct relation between data length and potential performance and energy improvement of associative processing. For 2D convolution, the Associative Processing model obtained a relative gain of 2x in latency, 2x in energy, and 13x in the number of load/store operations. For matrix multiplication, the speedup increases linearly with input dimensions, achieving 8x for 200x200 bytes matrices and outperforming parallel execution in an 8-core CPU. The advantages of associative processing shown in the results are indicative of a real alternative for systems that need to maintain a balance between processing and energy expenditure, such as embedded devices. Finally, the simulation and evaluation environment we have built can enable further exploration of this alternative for different usage scenarios and applications.

# **List of Figures**

| <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ol> | Associative Processor overview                                                                                                                          | 20<br>20<br>23<br>23<br>24<br>25 |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 5.2<br>5.1<br>5.3<br>5.4                                                                 | RV-Across architectural model.RV-Across design flow.RoCC instructions library.Output of RV-Across with the last cycle of the associative addition oper- | 33<br>33<br>34                   |

| 5.5                                                                                      | ation and the report of that operation                                                                                                                  | 36<br>40                         |

| 6.1                                                                                      | Associative algorithm for matrix multiply using custom instructions for implementing row parallelism.                                                   | 41                               |

| 6.2<br>6.3                                                                               | Overview of the behavior of matrix multiply in associative processing<br>Matrix extracted from the first element of the image operating with part       | 42                               |

| 6.4<br>6.5                                                                               | of the kernel                                                                                                                                           | 43<br>44<br>44                   |

| 6.6<br>6.7                                                                               | Associative algorithm for ReLU using special instruction                                                                                                | 45<br>46                         |

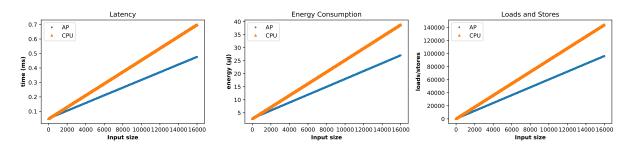

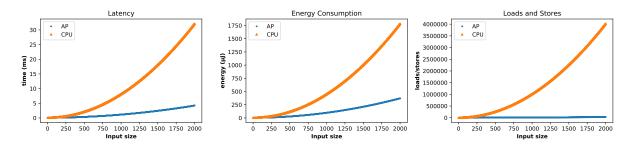

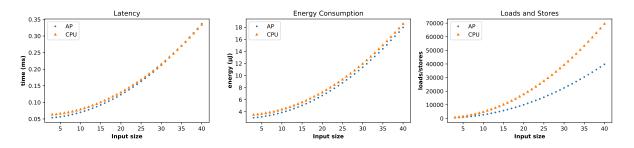

| 7.1                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both performing bitcount.                                                               | 48                               |

| 7.2                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both performing checksum.                                                               | 48                               |

| 7.3                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both performing 1D convolution.                                                         | 49                               |

| 7.4                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both performing hamming distance calculation.                                           | 49                               |

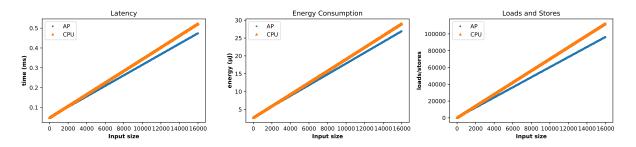

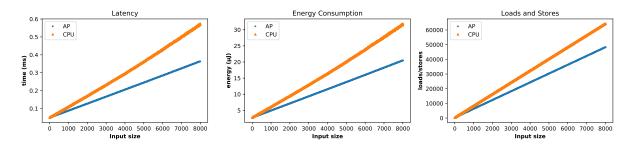

| 7.5                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both executing Manhattan distance.                                                      | 50                               |

| 7.6                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both executing ReLU.                                                                    | 50                               |

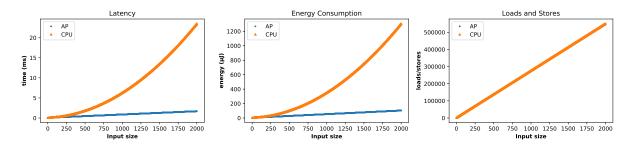

| 7.7                                                                                      | Latency, energy consumption and memory accesses for AP and CPU, both performing matrix multiply.                                                        | 51                               |

|                                                                                          |                                                                                                                                                         |                                  |

| 7.8  | Latency, energy consumption and memory accesses for AP and CPU.         |    |

|------|-------------------------------------------------------------------------|----|

|      | The CPU performing naive 2D convolution algorithm.                      | 51 |

| 7.9  | Latency, energy consumption and memory accesses for AP and CPU.         |    |

|      | The CPU performing optimized 2D convolution algorithm.                  | 52 |

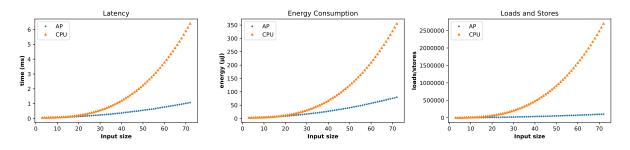

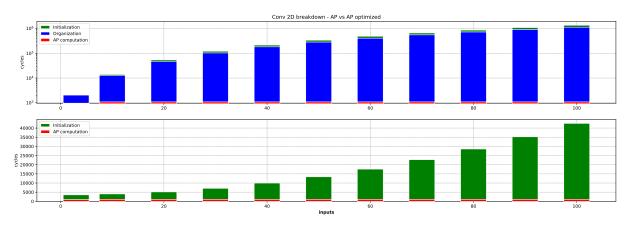

| 7.10 | Comparison in number of cycles between the normal and optimized         |    |

|      | version of the 2D convolution in the AP, separating the executions in   |    |

|      | phases for initialization, data organization and computation in the AP. | 52 |

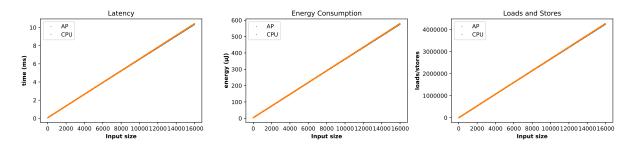

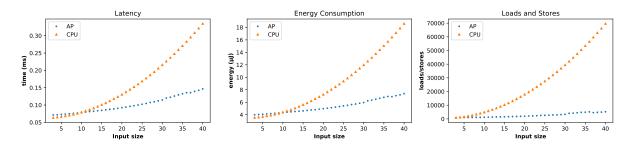

| 7.11 | Latency, energy consumption and memory accesses for AP and CPU.         |    |

|      | The AP and CPU, both performing optimized 2D convolution algorithm.     | 53 |

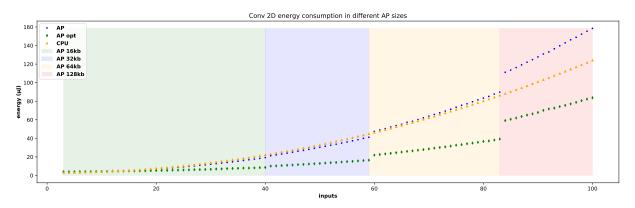

| 7.12 | Energy consumption for different AP sizes, comparing the normal and     |    |

|      | optimized for AP and optimized version for CPU                          | 53 |

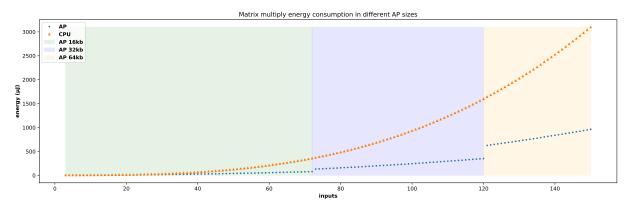

| 7.13 | Energy consumption for different AP sizes, comparing AP and CPU,        |    |

|      | performing matrix multiply                                              | 54 |

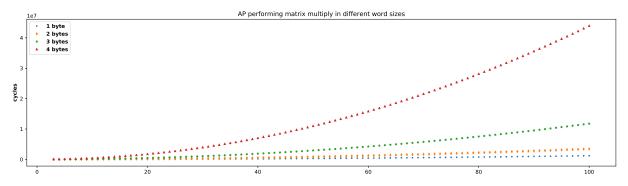

| 7.14 | AP performing matrix multiply with different word sizes.                | 54 |

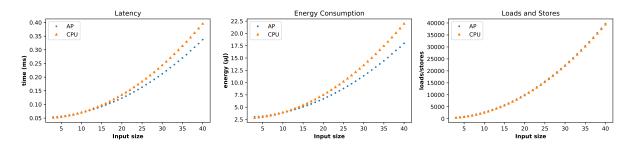

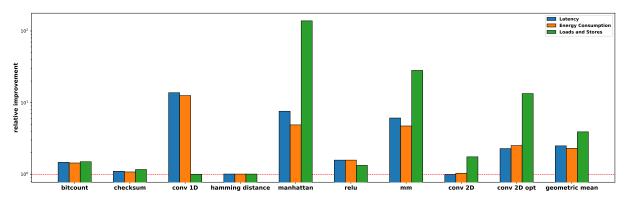

| 7.15 | The relative improvement in terms of latency, energy consumption and    |    |

|      | load/stores for all applications evaluated.                             | 55 |

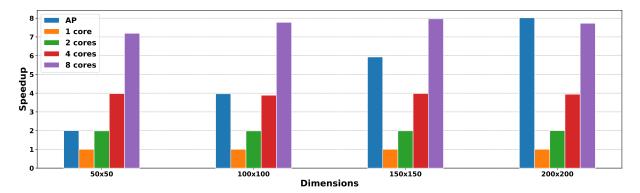

| 7.16 | Associative Processing matrix multiplication speed-up over a single-    |    |

|      | core CPU baseline, compared with speed-up for multi-threading with 2,   |    |

|      | 4, and 8 cores                                                          | 55 |

## Contents

| 1 | Introduction 13                                                                                                                                               |                                                                                    |  |  |  |  |  |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 2 | Background2.1RISC-V2.2Processing in Memory2.33D Memory2.4Alternative Solutions2.5Associative Processing                                                       | <b>15</b><br>15<br>16<br>16<br>17<br>18                                            |  |  |  |  |  |  |  |  |

| 3 | Associative Processing3.1Associative Processor3.2Constructing operations3.3Logic operations3.4Arithmetic operations3.5Web AP simulator                        | <b>19</b><br>19<br>22<br>22<br>24<br>25                                            |  |  |  |  |  |  |  |  |

| 4 | Related Work4.1Processing in Memory                                                                                                                           | 26<br>27<br>28<br>28<br>29                                                         |  |  |  |  |  |  |  |  |

| 5 | RV-Across: An Associative Processing Simulator5.1Overview.5.2User interface.5.3Output.5.4Latency model.5.5Energy model.5.6Customizing associative operations. | <ul> <li>32</li> <li>34</li> <li>35</li> <li>36</li> <li>38</li> <li>39</li> </ul> |  |  |  |  |  |  |  |  |

| 6 | Case studies6.1Matrix Multiplication6.22D Convolution6.3ReLU                                                                                                  | <b>41</b><br>41<br>43<br>45                                                        |  |  |  |  |  |  |  |  |

| 7 | Demonstration and Results7.1AP vs CPU7.2AP vs Multicore                                                                                                       | <b>47</b><br>47<br>54                                                              |  |  |  |  |  |  |  |  |

|   | 7.3 | Simulation performance | 56 |

|---|-----|------------------------|----|

| 8 | Con | clusion                | 57 |

# Chapter 1 Introduction

Researchers have sought to develop solutions in hardware that achieve high performance in terms of execution time, for specific or general purposes, while at the same time optimizing energy consumption. Many of these solutions are based on *Von Neumann* architectures, and therefore, rely on processing separated from memory. Since memory is utilized just for storage, multiprocessors, accelerators, and GPUs need to transport the data from memory for computation, spending a lot of time and energy in data movement.

Emerging data-intensive workloads, such as *Neural Network*, *Image Processing*, *Graphs* and *DNA Alignment* require fast data transfers for efficient computation. Because data transfer rates are typically much lower than maximum processing rates, CPUs often must wait for data, limiting system throughput. This difference in data transfer rates and processing speeds, known as the Von Neumann bottleneck [35], has been increasing with subsequent hardware generations, leading to the so-called *memory wall* [37, 42]. In addition to potentially limiting performance, the movement of data consumes a significant amount of the overall energy of the system. Data movement between the core and off-chip memory incurs ~100x higher energy than a floating-point operation [34, 39]. In Google Docs scrolling, for example, moving data represents more than 30% of energy consumption [6], and memory can account for up to 41% of the energy consumption of an entire server system [30].

Given this scenario, *Processing in Memory* (PIM) is an alternative for saving energy by avoiding data transfers and getting better performance using parallel computation. With the breakdown of Dennard Scaling and the eminent end of Moore's Law, academy and industry have shown increased interest in this alternative [35]. PIM is an approach that aims to take computing into memory, reducing data movement and overcoming the *Von-Neumann bottleneck*. Processing directly in memory reduces memory access time by mitigating the physical distance and increasing the bandwidth between CPU and memory. PIM also eliminates load and store cycles, increasing energy efficiency. In this paradigm, an operation can be executed on all words in memory in parallel, in a *Single Instruction Multiple Data* (SIMD) approach. Thus the execution time is fixed for any data length. PIM has been used to accelerate the processing of DNA, Neural Networks, and Graphs [12, 18, 29, 36]. Associative Processing, a PIM approach, performs in-memory parallel, logical, and arithmetic operations using lookup tables, special registers, and a *Content-Addressable Memory* (CAM). Recent advances in *Non-Volatile Memories* (NVMs) reduced the cost of implementing associative processing and attracted interest to this research area [20, 26, 51]. However, the lack of a flexible simulation infrastructure for the test and validation of in-memory operations is still an obstacle to enable its adoption [35].

In this work we show how Associative Processing works and how to build an algorithm in this approach and its performance, assessing speed and energy. To achieve these contributions, we developed the RV-Across (RISC-V <u>Associative Processing</u> <u>Simulator</u>). RV-Across is a simulator developed with the aim of providing easy programming, test, and evaluation of Associative Processing or near-memory processing context. Thus, taking its advantages, we implement applications in different scenarios and compare with a CPU approach to observe the potential of Associative Processing as well as its trade-off. The main contributions we present in this work are:

- Exploration and detailing of Associative Processing Algorithms for matrix multiplication, 2D convolution and ReLU function;

- An extensible simulation tool that enhances associative processing evaluation;

- An architectural model to interface PIM operations with an Associative Processor;

- A simple programming model for Associative Processing;

- Case studies using Associative Processing operations in application kernels;

- A performance analysis of applications in the Associative Processing model.

Our experiments highlight the potential of Associative processing and how the simulator works. In a model using Associative Processing, in most cases, resulted in fewer accesses to memory and consequently higher performance. For matrix multiply, associative processing obtained a relative improvement of 6x to latency, 4x to energy and 28x to load/store operations. For 2D convolution, in the best scenario 2x, 2x and 13x to latency, energy consumption and load/stores respectively. When considering a multi-core scenario, the associative processing model achieves up to 8x of speed-up on matrix multiplication, overcoming an 8-core CPU in the 200x200 bytes matrices computation. We evaluate the Associative Processor in various sizes to balance area and energy consumption. Processor with 16 KB or 32 KB is ideal, occupying an area smaller than a RISC-V core, proving to be a viable alternative for embedded systems.

This work is structured in eight chapters from introduction. The Chapter 2 provides key concepts to understand the work context. The Chapter 3 contains the implementation and simulation of a logic/arithmetic Associative Processing operation. Chapter 4 describes and classify related works, indicating similarities and differences among them and our work. Chapter 5 details the RV-Across from overview until the output of simulator. The Chapter 6 presents cases of applications adapted for associative processing using RV-Across. Chapter 7 shows the evaluation modes and performance results of Associative Processing in different scenarios. Lastly, Chapter 8 displays our conclusions and future work.

# Chapter 2 Background

This Chapter explains in detail the fundamentals to understand our work and its context. The first section explains what is RISC-V, and its benefits. After, it is described the concept of Processing in Memory and a summary of the main approaches as well as works related to each branch. The third section talks about 3D memories and works that utilize them to get better performance. The fourth section shows works about PIM which are out of 3D memory and Associative scope. Finally, we explore how an Associative Processor is designed and how it works.

#### 2.1 RISC-V

RISC-V is an *Instruction Set Architecture* (ISA) which follows the *Reduced Instruction Set Computing* (RISC) pattern and was designed with the didactic and scientific goals. The name RISC-V was chosen to represent the fifth RISC ISA developed by UC Berkley. RISC-I, RISC-II, SOAR and SPUR, in sequence, were the other versions [2].

This ISA has been adopted due to its benefits. It is an ISA open-source for industry and academy. There are free RISC-V cores with *Field Programmable Gate Array* (FPGA) support. RISC-V has float-point support and can be 32 or 64 bits. Rocket Chip, a RISC-V system on chip (SoC), for example, can be easily extended to a multi-core. Also, it is a platform where it is possible to add modules and instructions, creating variations. Also, RISC-V has a powerful tool-chain contained simulators, compilers and open documentation. These resources led to industry to fabricate chips using RISC-V.

The RISC-V obtains an interface for binding accelerator and additional modules. In the case of Rocket Chip, the custom instructions fulfill this role. The most used RISC-V models that can be extended are BOOM and Rocket Chip. In view of the present work, we utilized RISC-V and custom instructions for communication with the Associative Processing module on RV-Across. Chapter 5 explains in details about that programming interface and how to use it.

### 2.2 Processing in Memory

*Processing In Memory* (PIM) is a model that increases hardware performance in terms of bandwidth (about memory and CPU), latency, and energy consumption. It performs the computation in memory, where the application data is located. The PIM concept goes in the opposite direction to processing model adopted currently, the *Von Neummann model*. PIM is an approach applied in different ways, all looking for the same goal, of processing without data movement.

Initially, in the 70's, STARAM was developed, which is based on PIM model. This architecture was built by Goodyear and had as the purpose to change the processing manner. STARAM is constructed for a bunch of Associative Processors (APs). Recently, researches are joining associative processing with new memory trends as *Non Volatile Memories* (NVMs) and approximate computing [51, 54]. ReCAM, for example, is an implementation of a CAM using resistive memory.

Following the same fashion of associative computing, *Content-Addressable Memory* (CAM), other PIM production, is applied in routers, specifically on network layer for high performance *Internet Protocol* (IP) comparisons. The CAM indexes its contents using other content, as in a hash table. Thus, a router, after extracting the packet's IP address, inserts this address in the CAM, and it quickly returns (1 cycle) the destination address.

In addition to AP and CAM, recently academy and industry try to implement Processing in Memory in both, DRAM and 3D memories [10]. These components execute logic and arithmetic operations in their storage without undergoing major architectural modifications [35]. However, there are barriers that all approaches need to overcome: Making programming possible and easy for PIM systems, providing data coherency among PIM module and other system's modules, and building a simulation infrastructure for analogical and digital simulation. Our work has as goals to afford knowledge about associative processing and to provide a tool that is able to give a programming interface and application for validation of the potential of PIM. The same has been done in the context of 3D memories. There are many works of simulators and interfaces for programming and testing the resources provided by 3D logic.

#### 2.3 3D Memory

3D memory is a new technology that stacks vertically the logic layer of the memory in three dimensions. That new memory makes better use of die space with storage stacked. *Through Silicon Vias* (TSV), which are the interconnections within a die stack, enable high bandwidth, lower latency, and energy savings on communications among dies. 3D memory is able to access data in parallel due to three-dimensional architecture and components as TSV.

The 3D memory structure creates a perfect environment for Processing in Memory. For that reason, some 3D memories already support logical and arithmetic operations in parallel. An adverse effect of stacking in-memory 3D is increased peak temperature. Also, volatile and non-volatile 3D memories have been produced by industry on large scale, aiming for high-performance.

Researchers have used the 3D memory capabilities in different scenarios and applications [16, 24, 27, 44]. For example, the architecture of Ahn et. al [1] and Zhang et. al. [59] utilized *Hybrid Memory Cube* (HCM), a 3D memory with PIM support, to accelerate data-intensive applications. Besides developing architecture, both created an interface (programming model) and treated coherency problems. Compared to *Graphics Processing Unit* (GPU), both achieved better performance in execution time and energy consumption. Dai et. al. [12], Zhang et. al. [60] and Nai et. al. [36] used the 3D memory potential to process graphs in parallel. Similarly, Kim et. al. [29] applied PIM with 3D memory in the DNA sequence alignment. They developed a simulation platform for test, validation, and evaluation of systems with 3D memories, providing a programming interface to the user.

The RV-Across, our simulation platform, has similarities with PIM-gem5, work produced by Santos et. al. [44], by given a flexible way of simulation. But, instead of 3D memory, our simulator has Associative Processing features. In general, our work, as 3D memories works, uses PIM concept, but focused in a specific technique.

#### 2.4 Alternative Solutions

Some works used PIM, but do not even fit in 3D memory or Associative Processor. Chi et al. [8] proposed a PIM architecture, called PRIME, to accelerate *Neural Network* (NN) applications in *Resistive random-access memory* (ReRAM) based main memory. In PRIME, they insert *full functions* accelerators into memory that executes NN operations like search and convolutions. They designed complete software/hardware full functions for developers.

Gupta et al. [18] created an architecture, NNPIM, with full support, in terms of operations, to execute the inference phase inside the memory. They design a crossbar memory architecture that supports fast addition, multiplication, and search operations inside the memory. For search, they took advantage of the inherent characteristics of capacitors. Shafiee et al. [46] explored processing in approach, where memristor crossbar arrays not only store input weights but also perform dot-product operations in an analog manner.

Imani et al. [19] constructed a PIM accelerator, GenPIM, in an NVM which supports bitwise operations, search operation, addition, and multiplication. In GenPIM, conventional cores are connected to PIM accelerators. The GenPIM replaces DRAM with non-volatile memory since NVM can support both memory and processing functionalities. Seshadri et. al. [45] proposed Ambit, an accelerator in memory for bulk bitwise operations. Ambit exploits the analog operation of DRAM technology to execute bitwise operations inside DRAM, thereby exploiting the full internal DRAM bandwidth. Ambit consists of two features: simultaneous activation of three DRAM rows that share the same set of sense amplifiers, enabling the system to perform bitwise AND and OR operations, and the ability to use the inverters present inside the sense amplifier to perform bit-wise NOT operations.

Our work has the same intention and motivation as those of the aforementioned researches, however, using associative processing to accelerate applications. Associative processing is a way of doing PIM already applied and implemented, with well-defined behavior, being utilized in various memory technologies.

#### 2.5 Associative Processing

Associative processing is a way of parallel processing in an associative memory structure. Utilizing sequences of comparisons and writings based on Lookup Table, which represents the truth table of the operation, the AP executes arithmetic and logical operations between vectors in parallel spending a constant number of cycles [52, 54]. To enable associative processing, the AP takes advantage of a completely associative memory, the CAM. By adding a small overhead of special registers, the states of the implemented operations and the controller containing the algorithms, the AP acquires the ability to perform operations in parallel. We explained the structure, the algorithm and their behavior in the Chapter 3.

Nowadays scientists are utilizing associative processing in NVMs, in order to get a smaller cell area, a lower leakage power, and an increased overall chip area efficiency [3, 52, 55]. Also, associative processing, in academy, is applyed to accelerate various applications as DNA alignment, Database operations and CNN [32, 51, 57]. We, in this work, implemented application kernels and evaluated energy and time, simulating, on RV-Across, CPU model versus the AP model, in order to get a vision about Associative Processor potential.

## Chapter 3

## **Associative Processing**

This Chapter explains the structure used to perform associative processing and how to build operations on it with or without optimizations. The entire structure is detailed as well as its function in the execution of a generic operation, which is illustrated both in the diagram and in pseudo-code. Moreover, it shows step by step how to construct an operation from scratch. Also, the Chapter illustrates simple simulations of logic and arithmetic associative operations, containing the Associative Processor state for each cycle.

### 3.1 Associative Processor

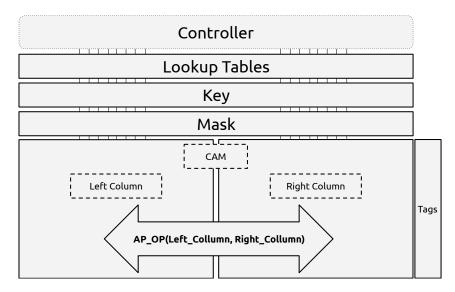

An *Associative Processor* (AP) is a CAM that provides additional processing capabilities, retrieving data from part of the content and operating through logical and arithmetic operations without moving data to a separate processor [52, 54]. In an AP, the operations can be made in several words of the memory simultaneously, reading, comparing, and writing inside the associative module without content transition. This processor needs the following components to perform computation:

- *Controller*: Module which is responsible for instruction decoding and configuration of other components for associative operation.

- *CAM*: Associative Memory in which the data will be stored. A CAM is able to recover data from its content.

- *Lookup Table (LUT)*: Table containing the values of the bits that will be compared and written, resulting in the operation.

- *Mask*: Register designed to select the columns that the processor will compare.

- *Key*: Register used to represent the bits of the *LUT* that are used for comparison.

- *Tag*: A bit that represents the **Match** state. This state indicates that the *LUT* comparison bits, represented by the *Key*, are the same as those of the operators. Then, the bits determined in the *LUT* in the result are written.

Figure 3.1: Associative Processor overview.

Figure 3.1 illustrates the Associative Processor overview with its components. As shown in Figure 3.1, the CAM is divided into data columns where one column can reference another. The CAM executes a search in one cycle by the capability to manipulate every bit (comparison and writing) of its storage. The CAM search is powerful, but it generates high area overhead. The AP takes advantage of CAM functionalities to perform operations. It uses those columns as vectors, and through the logic of comparison and writings based on LUT, which works like a truth table, does parallel operations between vectors in a constant number of cycles (AP\_OP in Figure 3.1).

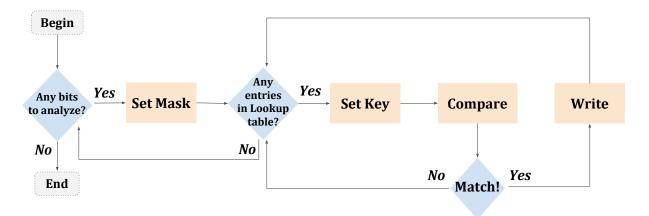

Figure 3.2: Associative processing diagram.

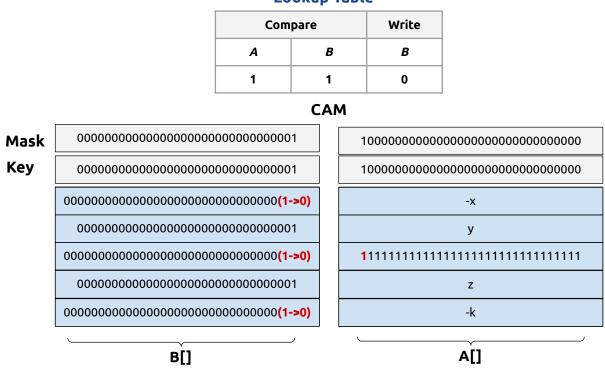

Associative processing can be summarized in three phases: selection, comparison, and writing of bits. First, the *Mask* register is set to select the columns (operands) to be compared. Then, the *Key* is configured, representing the *LUT* comparison bits. If the bits of the *Key* and the bits selected by the *Mask* are the same, there is a **Match**, and therefore, the bit *Tag* related to the operation becomes 1. Finally, it is verified which lines had a match looking at the *Tag*. If the *Tag* is 1, the corresponding value defined in the *LUT* is written in the result. The *Mask* is set for all bits of the word, depending on the associative operation, and the *Key* for all passes of the *LUT*. Figure 3.2 illustrates a diagram showing this operation flow.

| Alg | <b>gorithm 1</b> Generic associative processing algorithm (R[] = A[] OP B[]) |

|-----|------------------------------------------------------------------------------|

| 1:  | <b>for</b> <i>i</i> = 0, 1, , wordSizeA <b>do</b>                            |

| 2:  | <b>for</b> $j = 0, 1, \dots, $ wordSizeB <b>do</b>                           |

| 3:  | setMask(R, i, j)                                                             |

| 4:  | <b>for</b> $pass = 1, 2, \dots, sizeLUT$ <b>do</b>                           |

| 5:  | setKey(LUT[ <i>pass</i> ], R, i, j)                                          |

| 6:  | Compare(Key, Mask, A[i], B[j])                                               |

| 7:  | Write(LUT[ <i>pass</i> ], R)                                                 |

| 8:  | end for                                                                      |

| 9:  | end for                                                                      |

| 10: | end for                                                                      |

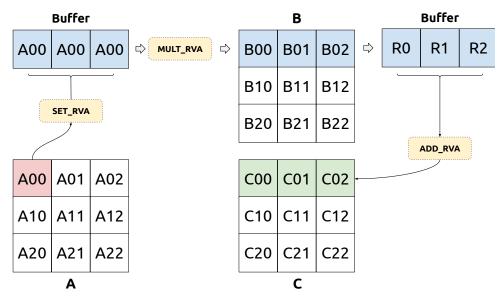

Algorithm 1 is the implementation of a generic associative processing algorithm performing an operation between two vectors (R[] = A[] OP B[]). Notice that the two external loops with the mask setting represent the selection phase (line 2). In other words, the bit selection, of vectors A and B, will be operated. After selection, for each pass from LUT, in an interval of two cycles, the key is configured, compared to bits selected, and the writing is triggered if **Match** happens. So, finalizing the comparison and writing phase. The algorithm ends when all passes are compared and/or written on all bits.

The algorithm shown represents a common shape of an associative algorithm. It is important to emphasize that associative processing does not have a unique algorithm format. The way the associative algorithm is designed changes according to the operation. Both the mask and the key registers can be configured via the controller, depending on the associative operation. The AP is flexible for building the LUTs and modifying the registers, however, there is a rigid data organization format for correct execution.

This section was based on works produced by Yantir et al. [51]. Our simulator, RV-Across, implements the associative addition and multiplication described in their work, as well as the cycle model. We used the same mechanism as Yantir at al. to build other LUTs, and thus create new operations (subtraction, AND, OR, XOR, and NOT).

#### 3.2 Constructing operations

Associative operations are powerful due to the capability of applying the same function into all data in parallel without data movement, just using comparisons and writings. For the construction of the operation, the developer needs, initially, to understand the behavior of its operation to set mask and key registers correctly. Another step is to define inputs and outputs as a truth table. The truth table will be the LUT. The input values represent the comparison bits and output values the bits that will be writing.

There are two optimizations for associative operation [52]. The first decrease the number of passes from LUT. The developer could exclude entries of the LUT by initializing the output vector with zeros or ones, depending on which is the majority among the outputs. For example, if the output vector starts with zeros, the developer would exclude the three passes with output '0' of AND operation. It is as if the vector already had the pre-written results. The second optimization saves storage by doing destructive operations. Instead of, for example, *C*[] = *A*[] + *B*[], the performed operation would be A[] = A[] + B[]. That technique saves a third of storage space per individual operation. For example, a non-destructive add operation, with one byte of word size, between two vectors containing 4 elements each, spends 12 bytes of the AP. Using the optimization, the operation would spend just 8 bytes.

Applying or not the optimizations, it is important to verify the order of LUT passes, because it influences directly over the result. One pass can interfere with another pass by writing at the wrong moment. For a correct associative operation, it is fundamental to test a bunch of samples, following and verifying cycle by cycle the results. In the next sections, associative logic and arithmetic operation are detailed through simulations.

#### 3.3 Logic operations

Associative logic operations are simple to design and implement. It is just to use the standard truth table as LUT, and apply overall bits. Figure 3.3 represents the simulation of an associative XOR between two vectors: A [1,2,3] XOR B [0,1,2]. See that the *LUT* summarizes an XOR truth table. The resulting vector C is initialized as [0,0,0], thus the entries of A and B that result in 0 are excluded from the *LUT*. Note that the *Mask* is the same for all passes computed for the same bit of the operands.

| Begin |   |          |          | Bit  | 0   Pa | ss: 1    |        | Bit  | : 0   Pa   | ass: 2   |        |      |    |     |    |   |

|-------|---|----------|----------|------|--------|----------|--------|------|------------|----------|--------|------|----|-----|----|---|

|       |   |          |          | Mask | 00     | 00       | 00     | Mask | 01         | 01       | 01     | Mask | 01 | 01  | 01 |   |

|       |   |          |          | Key  | 00     | 00       | 00     | Key  | 00         | 01       | 00     | Key  | 00 | 00  | 01 |   |

|       |   |          |          |      | 00     | 01       | 00     | 0    | 00         | 01       | 00     | 1    | 01 | 01  | 00 | 0 |

| Le    |   | X0<br>un | R<br>Tab | le   | 00     | 10       | 01     | 0    | 00         | 10       | 01     | 0    | 00 | 10  | 01 | 1 |

|       |   | -        | Write    |      | 00     | 11       | 10     | 0    | 00         | 11       | 10     | 1    | 01 | 11  | 10 | 0 |

| Pass  | A | В        | С        |      | C[]    | A[]      | B[]'   | Гаg  |            |          |        |      |    |     |    |   |

|       |   |          |          | ļ    | Bit    | : 1   Pa | ass: 1 |      | Bit        | : 1   Pa | ass: 2 |      |    | End |    |   |

| 1     | 1 | 0        | 1        | Mask | 10     | 10       | 10     | Mask | 10         | 10       | 10     | Mask | 00 | 00  | 00 |   |

| 2     | 0 | 1        | 1        | Key  | 00     | 10       | 00     | Key  | 00         | 00       | 10     | Key  | 00 | 00  | 00 |   |

|       |   |          |          |      | 01     | 01       | 00     | 0    | 01         | 01       | 00     | 0    | 01 | 01  | 00 | 0 |

|       |   |          |          |      | 01     | 10       | 01     | 1    | <b>1</b> 1 | 10       | 01     | 0    | 11 | 10  | 01 | 0 |

|       |   |          |          |      | 01     | 11       | 10     | 0    | 01         | 11       | 10     | 0    | 01 | 11  | 10 | 0 |

Figure 3.3: Associative XOR operation.

Consider the first pass executed on the bit zero of the operands. The *Mask* selects the first bit of each operand, and the *Key* is read from the *LUT* for the first pass. Comparing the *Key* and the values, for the selected bit, two Matches occur (lines 1 and 3), and the *Tag* is set accordingly. The respective bits on vector C are written to 1 in the next pass (bit 0, pass 1), and the process is repeated for each bit and pass. In the end, after comparing all the passes with all the bits, the vector C will have the resulting associative XOR. Thus, the operation can be performed in constant time for N elements of a vector without moving data.

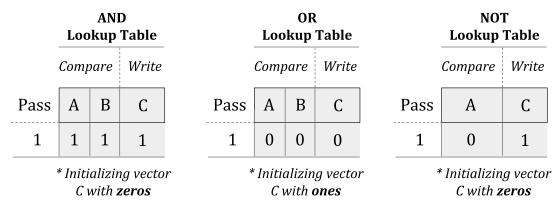

Figure 3.4: LUTs for AND, OR and NOT operations.

Figure 3.4 presents optimized LUT for AND, OR and NOT. With those tables and adopting the same shape of the mask of the XOR operations simulated, it is possible to perform each one. For the arithmetic operations, this shape can change depending on the operation. The next section explains the difference between arithmetic and logic associative operations.

#### 3.4 Arithmetic operations

Unlike logic associative operations, arithmetic operations require more complexity to be implemented. In addition to considering the operands and results for comparison and writing, it is necessary to deal with the carry. The carry influences directly on the optimization that reduces LUT passes, because its columns can not be removed even with pre-written results. In general, the carry is written in the most significant bit, far from the main computation that occurs in other bits.

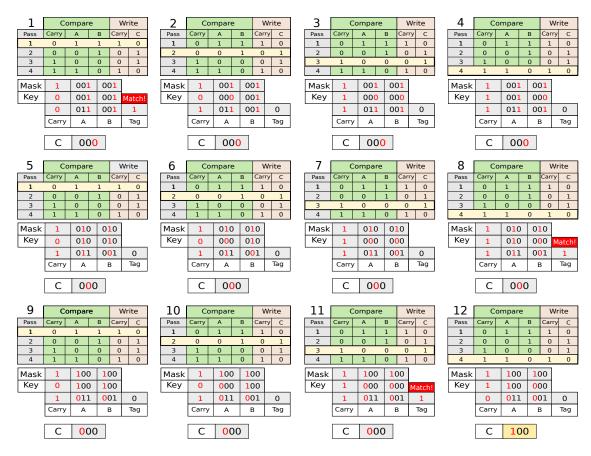

Figure 3.5: Associative ADD operation.

Figure 3.5 shows a simulation of an associative ADD operation between (C[0] = A[3] + B[1]). As in the XOR example, the ADD works in parallel. But in this case, to facilitate the understanding, the simulation was reduced for execution between two operands. The Figure is divided into 12 subfigures with the state for each pass. In the subfigure, the LUT, the full adder truth table summarized (operation states), is above the table of operands. The table of operands contains the state of special registers and the operands. For each bit, all passes from the LUT are applied for comparisons, therefore, in the case of addition which has 4 passes, will be  $4 \times n$  comparisons to finish the operation (n number of bits). In this example, the ADD operation has 12 comparisons.

In this operation, the AP selects the bits, through mask register, like XOR operation. Starting from LSB to MSB, the AP does comparisons and writings based on the LUT. Notice that the selection of the mask is represented in the table of operands by the bits highlighted in red. Also, the comparison bits from LUT (green area) are represented for the Key aligned with the Mask bits. When the Key bits aligned with Mask are equals to operands bits (A, B and Carry), occurs a Match and the Tag is set to 1. Hence, the writing bits from LUT (pink area) referring to the current pass are written in both carry and C. We can see a Match in the first subfigure, the Key bits equal to operands bits and the Tag receiving 1 to signalize the writing in the next cycle. In the next subfigure, observe that the writing bits for the pass 1, which are 1 to Carry and 0 to C, were applied.

The AP performs massive parallel selections, comparisons, and writings through the controller and special registers. This means that AP spends a constant latency (oriented by the word size of the CAM) to execute an operation regardless of the amount of data. Also, the AP parallelism provides high throughput in addition to saving energy. This kind of computation into the memory serves to accelerate applications that perform the same procedure in a set of data several times. In this work, we need to simulate an AP, with all logic and arithmetic operations, in an architectural model, aiming to compare with CPU alone and multi CPU approaches. For this purpose, we built the RV-Across which is the Spike, a standard RISC-V ISA simulator and adding an extension that contains the AP behavior. In the next Chapter, the RV-Across is explained in detail.

#### 3.5 Web AP simulator

Because of the difficulty of understanding associative algorithms, the *WebAP*, a web tool, was developed to easy the study of associative operations (Link). It provides a cycle-by-cycle simulation of an ADD associative operation, showing the states of all AP components for each step. The simulator was developed using the Angular framework. It is an open tool that serves as a support for teaching associative processing.

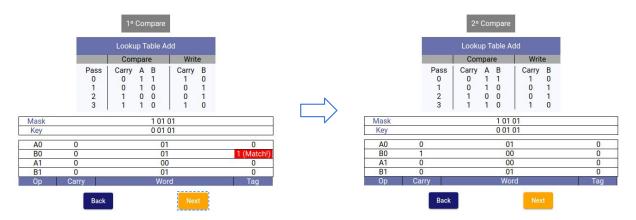

Figure 3.6: Cycle by cycle simulation on the WebAP.

To start the simulation in the *WebAP*, the user needs to set the word size of CAM, the number of values inside CAM, and, therefore, fill with values the CAM. Starting the simulation, two tables and two buttons appear, as shown in Figure 3.6. The first table represents the Lookup table and the second the data in the CAM. The buttons are used to access previous and later cycles of the simulation to analyze the algorithm step by step. The next chapter will deal with a simulator, the RV-Across, which also implements these functionalities in more operations.

# Chapter 4 Related Work

*Processing in Memory* (PIM) is an approach that increases hardware performance by putting computations inside the memory. The PIM concept can be implemented in different ways. One of them is using a 3D memory and its reading and writing capabilities in parallel to perform logical and arithmetic operations. Another one is using the associative processing, which, through a *Content-Addressable Memory* (CAM), can compute employing comparisons and writings. Moreover, other alternatives can add features or processing units within the memory to do operations.

Research involving Processing in Memory has been increasing in the last years, mainly because of its efficiency in performing big-data applications. In the literature, our work has an intersection with PIM architectures, accelerators, programming interfaces for PIM, and simulators. They can be associated with 3D memory, Associative Processor, or other alternatives to do PIM that were developed for a general or specific purpose, evaluating latency and/or energy. In this Chapter, we start with the alternative approaches, passing through 3D memory works and finalizing with AP.

#### 4.1 **Processing in Memory**

Gokhale et al. [17] in the '90s proposed a PIM model like a *Single Instruction Multiple Data* (SIMD) near memory, with an array of PIM chips, each one containing 2 kb and 64 *Arithmetic logic units* (ALUs) for computing. *Data-Intensive Architecture* (DIVA) was created by Drapper et. al. [14]. It unifies a set PIM chips as co-processors to a conventional microprocessor, using specific instruction to communicate among them, just like the Gokhale's model. DIVA has high bandwidth interconnection to be able to supply the multimedia applications demands.

Chi et. al. [8] proposed the PRIME architecture to improve the performance of NN applications utilizing ReRAM. Unlike the previous ones, PRIME has a specific purpose. The PRIME has full functions accelerators to perform search and convolution in memory, it achieves an energy relative improvement of 895x compared to other neural processing units. Shafiee et. al. [46] modified eDRAM, adding accumulation and multiplication operations within memory, to create the ISAAC accelerator. ISAAC has the power to perform matrix multiplication, accelerating the performance of NN

processing. Seshadri et. al. [45] exploited the analog operation of DRAM technology to perform bitwise operations (AND, OR, and NOT) without data movement.

The GenPIM architecture model was developed by Imani et. al. [19] to be a PIM general-purpose solution, providing memory banks capable of performing logical, searching, adding, and multiplying operations. GenPIM is composed by conventional cores linked to a main memory containing banks of PIM blocks. The authors of PIM abstracted the technique utilized. The NNPIM architecture supports the same operations as GenPIM, but explaining the mechanism of computing the operations and focusing on NN applications. The addition is inspired in Wallace-tree, the multiplication is performed through Bernstein's Algorithm and the search operation works like a CAM, using hamming distance.

PIM-Aligner is an accelerator that was made to execute DNA short read alignment. PIM-Aligner has its sense-amplifiers customized to perform XNOR, for comparison, and addition, for counting, in parallel [4]. The same group of researchers, using the same way of PIM, developed AlignS platform to execute DNA alignment in *Spin-Orbit Torque Magnetoresistive Random-Access Memory* (SOT-MRAM) [3].

#### 4.2 3D Memories

Among the works featuring 3D memories, TOP-PIM is an architecture that is composed by 3D stacked DRAM replacing GPU and using the same interface for simulation [59].

Ahn et al. [1] proposed a programming model using custom instructions to trigger PIM in HMC (Hybrid Memory Cube). They show how to program a real application using their framework and prove low overhead generated .

The XNOR-POP architecture, created by Jiang et. al. [24], has support to PIM in Wide-IO2 DRAMs (3D memory) to process binary CNN. The Tetris accelerator follows the same line of the processing inside 3D memory, partitioning all steps of NN processing to accelerate its execution [16].

GraphP and GraphH are PIM architectures that utilize 3D memory capabilities to accelerate the processing of graph and both are HMC-based [12, 60]. Both created mechanisms in software (barriers) to facilitate the programming of search algorithms. Kim et al. proposed an algorithm called GRIM-Filter to accelerate read mapping (filtering) by reducing the number of required alignments using a 3D-stacked memory and its features [29]. Finally, Santos et al., built a framework which uses new instructions, to experiment with IoT applications using PIM in 3D memory, varying the architecture and technology of memory [44].

Several simulators have been developed for experimentation in the context of 3D memories. Leidel and Chen [31] built HMC-Sim, a cycle-accurate simulator that offers to the users an infrastructure of experiments with HMC 1.0 and 2.0, implementing a model to replace traditional thread mutexes with custom HMC mutex commands. Besides, the extension of HMC-Sim enables the users to craft Custom Memory Cube (CMC) operations and the evaluation of their efficacy through user applications. The

HMC also provides a discrete tracing allowing users to see exactly how and where memory operations progressed through the device or devices.

Jeon and Chung [23] developed CasHMC which is a C++ simulator that allows a cycle-by-cycle simulation of every module in an HMC and generates analysis results including a bandwidth graph and statistical data. This simulator enables parallel execution of other simulators that generate memory access patterns. For each HMC transaction, the simulator generates a log like HMCSim.

Clapps is an HMC simulator as well, made by Oliveira et. al. [38] using SystemC. The Clapps has an interface through specific instructions for the users to perform vector PIM operations in applications. That simulator is a parallel simulator that implements all of the HMC instructions.

PIMSim and PIM-gem5 are PIM simulators with HMC that share many characteristics [44, 50]. Both simulators provide processor simulation with HMC, analyze the impact of PIM in the memory hierarchy, simulate full-system with cycles and energy counters, and are configurable. PIMSim integrates DRAMSim2, HMCSim, NVMain, and Gem5 for simulation at different levels (fast, instrumentation-driven, and fullsystem simulation) and provides an interface for the user via directives. Pim-Gem5 implements PIM support in Gem5 and creates a methodology for prototyping PIM accelerators.

#### 4.3 Associative Processors

Most of the Associative Processor works have been combining NVM due to its lowoverhead of area and energy consumption. Imani et al. and Yantir developed an approximate *Resistive Content Addressable Memory* (ReCAM) and evaluated [20, 51]. Imani et al. designed an accelerator model, the DigitalPIM, using associative processing to big-data applications [22].

Yantir et al. explored approximate techniques such as bit trimming and power scaling to save energy. Also, the authors explained how works an associative operation; however, they did not show how to construct the algorithms in real applications. [52, 53].

PRINS is an architecture based on ReCAM to be a programmable CAM, providing instructions and algorithms of real applications (Graphs and Machine Learning) [57]. Saikia et al. implemented a CAM with *Static Random-Access Memory* (SRAM) to accelerate the KNN algorithm and achieve 1.2 GHz of frequency spending low energy [43]. Finally, the ReSQM architecture combines arrays linked to ReCAM accelerators to do database operations [32].

#### 4.4 Simulators

There are also works in the literature involving CAM simulators or associative processing. Khoram et. al. [28] developed an analytical model to analyze run-time, energy, and storage for a set of architectures, including Associative Processor. Specifically, the proposed method asymptotically evaluates the computational metrics in a specific architecture, ignoring constants and low-level factors.

In NVSIM-CAM, the NV-Sim simulator is adapted as a tool that estimates the performance, area, and energy of CAM and other types of NVMs [33]. Yantir et. al. [51] proposed a methodology that combines approximate computing and associative processing and developed an in-house simulator for associative operations. Yavits et. al. [54, 55] also developed an associative processor in-house simulator, in which the associative processor is at the last cache level. It also estimates energy based on associative processing events.

Finally, Santos et al. [41] designed *SIM*<sup>2</sup>*PIM*, an agnostic PIM simulator, based on the Gem-5, which implements hardware performance counters and multi-thread support for PIM devices.

#### 4.5 Comparison

We designed an architecture model that contained a RISC-V core that can send commands to an *Associative Processor* (AP) module via custom instructions provided by RISCV instructions set. With the instructions, it is possible to load the AP with a set of data and trigger logic/arithmetic operations in parallel. This AP is linked to main memory via *Direct Memory Access* (DMA) and therefore spending fewer cycles to access the data. Thus, the way of computing in memory of our work is different from the first two groups. The custom instructions and the framework that we built are similar to works as DIVA, PRIME, TOP-PIM, and others. Our model has a general-purpose like Ambit, GenPIM, TOP-PIM, DigitalPIM, etc. Besides, we provide software support, explaining how to utilize and apply in real applications.

Some works, such as GenPIM, NNPIM, Tetris, and GraphP, create an architectural model but do not build a programming model. Others, as the architecture of Gokhale and DigitalPIM, have no assessment of energy or latency. We created a simple evaluation model for latency and energy of our architecture and with it, we evaluate a set of application kernels, even in different AP sizes.

None of the studies cited in this section used RISC-V as the base *Instruction Set Architecture* (ISA). Our work uses custom instructions, which are already geared towards acceleration, as communication support for the Associative Processor.

Most of the works targeting PIM implement are in-house simulators. This methodology might hurt the overall productivity, and it can also preclude replicability [38]. This is one of the reasons that we built RV-Across. RV-Across is an open simulator, focused on Associative Processor, which also allows the addition of customized operations such as HMC-Sim, implemented in C++ as CasHMC, and uses special instructions to inmemory processing as Clapps. With the events counted by the simulator, the user will be able to extract energy statistics based on a separate model. RV-Across allows modeling extended operations and provides an interface for associative processing experiments. RV-Across uses a similar format of an associative algorithm, allowing operations between vectors. However, our tool offers the freedom to build and experiment with

|                           |     | Ot | oject |      | A  | pproa | ch  | Pur | pose | Evalu | ation |

|---------------------------|-----|----|-------|------|----|-------|-----|-----|------|-------|-------|

| Works                     | Sim | Sw | Acc   | Arch | 3D | AP    | Alt | Gen | Spec | Lat   | En    |

| Gokhale [17]              | -   | X  | -     | X    | -  | -     | X   | X   | -    | -     | -     |

| DIVA [14]                 | -   | X  | -     | X    | -  | -     | X   | X   | -    | X     | -     |

| PRIME [8]                 | -   | X  | -     | X    | -  | -     | X   | -   | X    | X     | X     |

| ISAAC [46]                | -   | -  | X     | -    | -  | -     | X   | -   | X    | X     | X     |

| Ambit [45]                | -   | -  | X     | -    | -  | -     | X   | Х   | -    | X     | X     |

| GenPIM [19]               | -   | -  | -     | Х    | -  | -     | Х   | X   | -    | Х     | X     |

| NNPIM [18]                | -   | -  | -     | X    | -  | -     | Х   | -   | X    | X     | X     |

| PIM-Aligner [4]           | -   | -  | X     | -    | -  | -     | Х   | -   | X    | X     | X     |

| AlignS [3]                | -   | -  | Х     | -    | -  | -     | Х   |     | Х    | Х     | X     |

| Top-PIM [59]              | -   | X  | -     | X    | X  | -     | -   | Х   | -    | X     | X     |

| Ahn [1]                   | -   | X  | -     | X    | X  | -     | -   | Х   | -    | X     | X     |

| XNOR-POP [24]             | -   | -  | -     | X    | X  | -     | -   | -   | X    | Х     | X     |

| Tetris [16]               | -   | -  | Х     | -    | X  | -     | -   | -   | X    | Х     | X     |

| GraphP [60]               | -   | -  | -     | X    | X  | -     | -   | -   | X    | X     | X     |

| Grim-Filter [29]          | -   | X  | -     | -    | X  | -     | -   | -   | Х    | Х     | -     |

| IoT PIM [44]              | -   | X  | -     | X    | X  | -     | -   | -   | X    | X     | -     |

| GraphH [12]               | -   | -  | -     | X    | x  | -     | -   | -   | X    | X     | X     |

| HMCSim [31]               | X   | -  | -     | -    | x  | -     | -   | х   | -    | X     | -     |

| Clapps [38]               | X   | -  | -     |      | X  | -     | -   | Х   | -    | X     | -     |

| CasHMC [23]               | X   | -  | -     | -    | X  | -     | -   | Х   | -    | X     | -     |

| PIM-Sim [50]              | X   | X  | -     | -    | x  | -     | -   | х   | -    | X     | X     |

| PIM-Gem5 [40]             | X   | X  | -     | -    | X  | -     | -   | Х   | -    | X     | X     |

| Imani [21]                | -   | -  | -     | X    | -  | X     | -   | X   | -    | X     | X     |

| Yantir Approx [51]        | -   | -  | -     | X    | -  | x     | -   | х   | -    | X     | X     |

| PrinS [57]                | -   | X  | -     | X    | -  | X     | -   | Х   | -    | X     | X     |

| KNN Acc [43]              | -   | -  | X     | -    | -  | X     | -   | -   | X    | X     | X     |

| DigitalPIM [22]           | -   | -  | X     | -    | -  | x     | -   | X   | -    | -     | -     |

| ReSQM [32]                | -   | X  | -     | X    | -  | X     | -   | -   | X    | X     | X     |

| Yantir Sim [51]           | X   | -  | -     | -    | -  | X     | -   | X   | -    | X     | X     |

| Yavits Sim [56]           | X   | -  | -     | -    | -  | X     | -   | X   | -    | X     | X     |

| NV-Sim [33]               | X   | -  | -     | -    | -  | X     | -   | X   | -    | X     | X     |

| Khoram Sim [28]           | X   | -  | -     | -    | -  | X     | -   | X   | -    | X     | X     |

| Sim <sup>2</sup> PIM [41] | X   | X  | -     | -    | -  | X     | -   | X   | -    | X     | X     |

| Our work                  | X   | X  | -     | X    |    | X     |     | X   | -    | X     | X     |

Table 4.1: Summary of related works, classified by what was produced, the PIM approach used, the purpose and what was evaluated.

Sim: Simulator, Sw: Software interface, Acc: Accelerator, Arch: Architecture, 3D: 3D memory AP: Associative Processing, Alt: Alternatives, Gen: General, Spec: Specific, Lat: Latency En:Energy.

customized operations. Our tool delivers an interface to high-level programming (via RISC-V custom instruction) and enables experiments to evaluate latency and energy. In terms of architecture, RV-Across uses a scratch-pad memory and does not consider memory coherence. RV-Across performs associative processing in a low-latency scratch-pad memory closely tied to the main processor, with direct access to the main memory, bypassing the cache hierarchy and avoiding memory accesses by favoring DMA bulk transfers. *SIM*<sup>2</sup>*PIM* is a simulator similar to RV-Across that has the advantage of providing multi-thread support for the PIM device, which RV-Across does not yet provide. However, RV-Across provides in addition to agnostic support, a cycle-by-cycle simulation of an AP and a model for evaluating latency and energy that can be adapted for other architectural models. *SIM*<sup>2</sup>*PIM* is extensible like our simulator, but by using native instructions from RISC-V, the flexibility to customize in RV-Across becomes easier. For better visualization of the related works, two tables were made. Table 4.1 refers to all works related to ours and Table 4.2 to simulators similar to RV-Across.

Our work goes beyond RV-Across. We provide case studies with associative application kernels, showing how AP works to perform them and how to implement these

|                           |          |           | Evalu        | ation      |            |         |        |

|---------------------------|----------|-----------|--------------|------------|------------|---------|--------|

| Works                     | Approach | Interface | Architecture | Algorithms | Extensible | Latency | Energy |

| HMC-Sim [31]              | 3D       | X         | -            | X          | X          | Х       | -      |

| CasHMC [23]               | 3D       | -         | X            | -          | -          | -       | -      |

| Clapps [38]               | 3D       | X         | -            | -          | X          | Х       | -      |

| PIM-sim [50]              | 3D       | X         | X            | -          | X          | Х       | X      |

| PIM-gem5 [40]             | 3D       | X         | X            | -          | X          | Х       | X      |

| Khoram [28]               | AP       | -         | -            | -          | -          | Х       | X      |

| NVSIM [28]                | AP       | -         | -            | -          | -          | Х       | X      |

| Yavits [56]               | AP       | -         | X            | -          | -          | Х       | X      |

| Yantir [51]               | AP       | -         | -            | X          | -          | Х       | X      |

| SIM <sup>2</sup> PIM [41] | AP       | X         | -            | -          | X          | Х       | X      |

| Our work                  | AP       | X         | X            | X          | X          | X       | X      |

Table 4.2: Selection of PIM simulators that have similarities with RV-Across.

kernels (Chapter 6). Furthermore, we simplify the performance evaluation by developing experimentation models. Using these models, we simulate the kernels to highlight the potential of the AP model over CPU and multi-CPU models (Chapter 7).

### Chapter 5

## **RV-Across: An Associative Processing Simulator**

The current Chapter describes the purpose of the RV-Across simulator, its structure, the implemented architectural model, the access interface for the simulator, the operations supported, and the output generated from the simulator. Also, the latency and energy consumption models developed and the basis in the literature for the construction of the evaluation models are explained. The models served as a basis for the generation of results and conclusions of the work, which are in Chapters 7 and 8.

#### 5.1 Overview

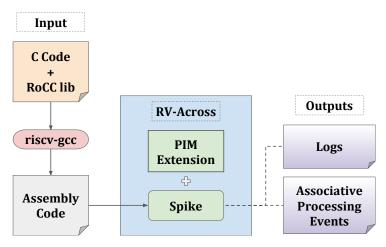

RV-Across is a high-level simulator for the design and validation of in-memory operations, built as an extension of the Spike reference RISC-V ISA Simulator. RV-Across provides a framework to extend, implement, and test PIM operations based on RISC-V custom extensions and instructions. Furthermore, RV-Across generates a step-by-step log of the simulation for enhanced user control. The simulator counts and logs events of comparison, writing, match, and mismatch in associative processing. These statistics are offered to the user as a mean to calculate latency and energy. That is, the simulator is not just an addition of an extension, it is the modification of the Spike to enable the simulation of the processing in memory behavior.

Figure 5.1 shows an overview of the simulator's structure with its inputs and outputs. As input, the simulator receives the RISC-V binary that can be generated from the compilation (RISC-V tool-chain) of a C code using the library that we created to perform the operations. The output is the logs with each cycle of the CAM and the states of the Mask and Key registers in addition to showing the number of comparisons, writings, matches, and mismatches that occurred during the processing.

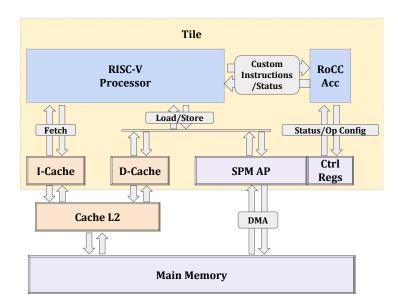

RV-Across is based on an associative processing architectural model to support PIM. Figure 5.2 shows the overall architecture that our simulator represents. Inside the Tile, the processing components and instructions and data caches are located, and off the Tile, the L2 cache and main memory. The main processor is a RISC-V core connected to the extension module (RoCC Accelerator), that provides control support

Figure 5.2: RV-Across architectural model.

for associative operations. The main core communicates with the RoCC Accelerator using custom instructions.

Figure 5.1: RV-Across design flow.

The RoCC Accelerator, when triggered, sends setup and command information to the control registers coupled to the Associative Processor, such as the addresses of the operands and output vectors and which operation will be performed. After configuring the registers, the operation is executed while the CPU waits for a response on the status of the operation. The AP receives commands to load data from memory or trigger logical or arithmetic operations previously implemented. The complete process for associative processing is using these two steps in sequence: loading the data to be operated and finally triggering the execution at the determined addresses. The AP contains the Lookup-Table for the associated operations and the configured algorithms. For simplification in both hardware and software simulation, the associative operations and CPU instructions do not run in parallel. The AP works as a *Scratch-Pad Memory* (SPM). In addition to reading and writing, this SPM serves as a support for data processing. The AP can access the main memory using *Direct Memory Access* (DMA). This reduces data movement since the main core does not need to act as a bridge to transport data from the main memory to the AP. To use the AP, the user must configure the data to be processed in the SPM and activate the associative operations using custom instructions. To gain simplicity in the implementation, the SPM is small in size, since its cost in the area can be high. For most scenarios, an AP of size 16 KB was used, because in that size there is a lower cost of area and power for the CAM. However, the execution of application kernels in different AP sizes was also evaluated to understand the impact of CAM power on the system (Chapter 7).

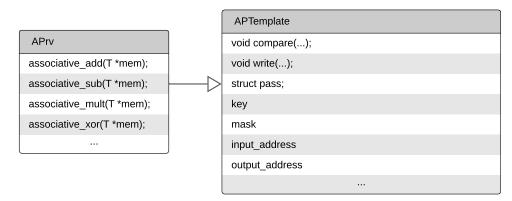

### 5.2 User interface

RISC-V RoCC instructions are used to communicate with the accelerator module attached to the RISC-V processor. Such instructions are used in the RV-Across for communication with the accelerator module that configures associative operations. Then, for the use of associative operations, it is necessary to insert the RoCC instructions in the application. For this purpose, RV-Across includes a library with predefined macros, at which it is possible to enter the parameters of what instruction to use, the value for the registers, and the operation code.

```

1 #define ROCC_INSTRUCTION(x, rd, rs1, rs2, funct) ...

2 #define ADD_RVA(in_a, in_b, out, length, word_size) \

3 ROCC_INSTRUCTION(2, 0, in_a, in_b, 0); \

4 ROCC_INSTRUCTION(2, 0, length, out, (word_size << 3) | 1);</pre>

```

Figure 5.3: RoCC instructions library.

The code in Figure 5.3 shows the shape of the generic macro ROCC\_INSTRUCTION, which represents the default type-R RISC-V instruction used in the RoCC extension. The first parameter, *x*, indicates which of the four RoCC custom instructions is used in the implementation. In RV-Across, a vectorized associative operation is triggered after two steps: the first configures the position of two input vectors (*rs1* and *rs2*) and the second configures the length of the vectors (*rs1*) and the position of the output vector (*rs2*). The output register *rd*, not used in this implementation, is reserved for future use. The *funct* field is used to send additional information to the AP control. If the *funct* is '0', the AP loads the pointers of the input vectors. If it is different from '0', the AP control extracts the operation that will be executed, from the 3 least significant bits and the word size from the remaining 4 most significant bits. For example, ADD\_RVA (addition) is an associative operation that receives the pointers of the input vectors, the size of the vectors, and the word size in bytes. The operation is implemented using the RoCC *custom-2* instruction, and addition is defined by the operation code '1' in the *funct* field. Thus, using this interface and considering that no other RoCC

| Associative operations             | Number of passes |

|------------------------------------|------------------|

| Unsigned multiplication            | $4 \times n^2$   |

| Addition, Subtraction              | $4 \times n$     |

| XOR                                | $2 \times n$     |

| AND, OR, NOT, Shift Right and Left | п                |

| RELU                               | 1                |

| SET                                | 1                |

| СОРҮ                               | k                |

Table 5.1: Number of comparison passes for associative operations implemented in RV-Across to a word size of *n* bits. The variable *k* means the size of the vector copied.

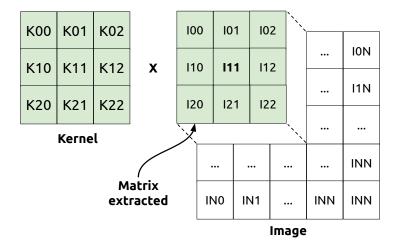

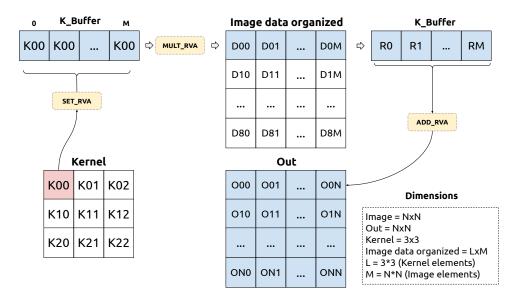

extension accelerator coexists in the target system, a designer can define up to 32 distinct associative operations, that load up to two vectors and write to one, of arbitrary length and word size of up to 15 bytes.