## HIGH FREQUENCY AND HIGH DYNAMIC RANGE

## CONTINUOUS TIME FILTERS

A Dissertation

by

## ARTUR JULIUSZ LEWINSKI KOMINCZ

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

May 2006

Major Subject: Electrical Engineering

# ALL RIGHTS RESERVED

# ARTUR JULIUSZ LEWINSKI KOMINCZ

© 2006

## HIGH FREQUENCY AND HIGH DYNAMIC RANGE

## CONTINUOUS TIME FILTERS

A Dissertation

by

## ARTUR JULIUSZ LEWINSKI KOMINCZ

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Committee Members, Jose Silva Martinez Edgar Sanchez Sinencio Frederick Strieter Wayne Lepori Costas Georghiades

Head of Department,

May 2006

Major Subject: Electrical Engineering

#### ABSTRACT

High Frequency and High Dynamic Range Continuous Time Filters. (May 2006) Artur Juliusz Lewinski Komincz,

B.S., Instituto Tecnologico de Queretaro, Mexico Chair of Advisory Committee: Dr. Jose Silva Martinez

Many modern communication systems use orthogonal frequency division multiplexing (OFDM) and discrete multi-tone (DMT) as modulation schemes where high data rates are transmitted over a wide frequency band in multiple orthogonal subcarriers. Due to the many advantages, such as flexibility, good noise immunity and the ability to be optimized for medium conditions, the use of DMT and OFDM can be found in digital video broadcasting, local area wireless network (IEEE 802.11a), asymmetric digital subscriber line (ADSL), very high bit rate DSL (VDSL) and power line communications (PLC). However, a major challenge is the design of the analog frontend; for these systems a large dynamic range is required due to the significant peak to average ratio of the resulting signals. In receivers, very demanding high-performance analog filters are typically used to block interferers and provide anti-aliasing before the subsequent analog to digital conversion stage. For frequencies higher than 10MHz, Gm-C filter implementations are generally preferred due to the more efficient operation of wide-band operational transconductance amplifiers (OTA). Nevertheless, the inherent low-linearity of open-loop operated OTA limits the dynamic range. In this dissertation, three different proposed OTA linearity enhancement techniques for the design of high frequency and high dynamic range are presented. The techniques are applied to two filter implementations: a 20MHz second order tunable filter and a 30MHz fifth order elliptical low-pass filter. Simulation and experimental results show a spurious free dynamic range (SFDR) of 65dB with a power consumption of 85mW. In a figure of merit where SFDR is normalized to the power consumption, this filter is 6dB above the trend-line of recently reported continuous time filters.

To my wife Isabel, my parents Juliusz and Grazyna

and my brother Pawel.

#### ACKNOWLEDGMENTS

This work would not have been possible without the support and help of many people; my appreciation goes out to the following:

First, I would like to thank my advisor and committee chair, Dr. Jose Silva, for his outstanding guidance and knowledge during the course of this research. Also, thanks to all my committee members, Dr. Edgar Sanchez Sinencio, Dr. Frederick Strieter and Dr. Wayne Lepori for their great support and attention. It was an honor to work with all of them.

During the course of my Ph.D., the best thing happened to me: I married the love of my life, Isabel. Through good or hard times, she was always cheering me on and bringing joy to my life. There are no words to express my appreciation for that. I love her very much.

I want to give special thanks to Dr. Rainer Fink, for whom I had the opportunity to work in a remarkable and enjoyable project. Not only has he been a great supervisor and professor, but also a good friend who was always there to listen and advise.

Many thanks to my friends and former roommates David and Alberto; we shared together the glory and pain of graduate work, and we learned a lot from each other. To my friends Ari, Marcia, Pedro, Marta, Antonio and Adriana, thank you for your good advice, and for your kind help in times of need.

To Chinmaya, Faisal, Chava, Didem, Feyza, Sebastian, Peyman, Alexander, Hezam, Ranga, Rhadika, Alejandro, Wennie, Julio, Rida, Ahmed, Reza, Sathya, Taner, Abraham, John, Lorena, Felipe, Gavillero, Pankaj, Sualp, Devrim, Fikret, Elvis, Itza; thanks for great shared moments.

I also want to thank my father for inspiring me to do this, and my mother for always believing in me. Thanks also to my wife's parents for their constant support.

Many thanks go to Mrs. Cook, Nancy and Angela at Sponsored Student Services and Tammy, Jeannie and Ella at the Department of Electrical Engineering for their assistance.

Finally, I want to thank CONACYT for the invaluable financial support that made the achievement of this degree possible.

## TABLE OF CONTENTS

| 1. INTRODUCTION                                    |    |

|----------------------------------------------------|----|

| 1.1 The need of analog filters                     |    |

| 1.2 Challenges in continuous-time filters          |    |

| 1.3 State of the art in continuous time filters    |    |

| 1.4 Contributions                                  |    |

| 1.5 Organization                                   |    |

| no organization                                    |    |

| 2. LINEARITY ENHANCEMENT TECHNIQUES BASED ON NON-  |    |

| LINEARITY CANCELLATION                             |    |

|                                                    |    |

| 2.1 The differential pair                          |    |

| 2.1.1 Distortion                                   | 16 |

| 2.1.2 Noise                                        |    |

| 2.2 The double differential pair                   |    |

| 2.2.1 Analysis                                     |    |

| 2.2.2 Improvement comparison                       |    |

| 2.3 A 20 MHz second order low-pass filter          |    |

| 2.3.1 OTA design                                   |    |

| 2.3.2 Filter design                                |    |

| 2.3.3 Experimental results                         |    |

| 2.4 The triple differential pair                   |    |

| 2.4.1 Analysis                                     |    |

| 2.4.2 Advantages of the topology                   |    |

| 2.4.3 Complete OTA                                 |    |

| 2.4.4 Experimental results                         |    |

| 2.4.5 Comparison with reported OTAs                |    |

|                                                    |    |

| 3. LINEARITY TECHNIQUES BASED ON NON-LINEAR SOURCE |    |

| DEGENERATION                                       | 61 |

|                                                    |    |

| 3.1 Non-linear degeneration principle              |    |

| 3.2 A 30-MHz low-pass filter implementation        |    |

| 3.2.1 Design considerations                        |    |

| 3.2.2 Filter structure.                            |    |

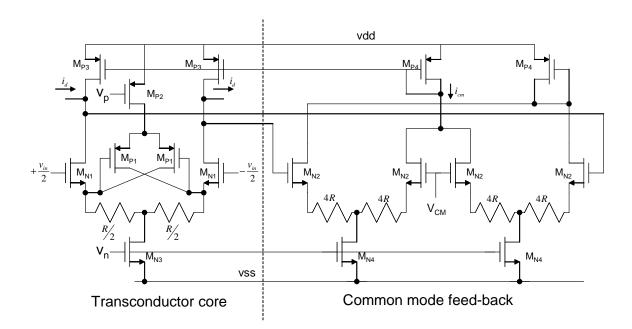

| 3.2.3 Transconductors                              |    |

| 3.2.4 Common mode feedback                         |    |

| 3.2.5 Self-bias circuit                            |    |

| 3.2.6 Capacitors                                   |    |

| 3.3 Automatic tuning                               |    |

| 3.3.1 Master circuit                            |  |

|-------------------------------------------------|--|

| 3.3.1 Analog section                            |  |

| 3.3.2 Digital tuning circuit                    |  |

| 3.3.3 Non-idealities                            |  |

| 3.3.3.1 Jitter and mismatch (offset)            |  |

| 3.3.3.2 Output resistance                       |  |

| 3.3.3 Parasitic capacitances                    |  |

| 3.3.4 Overall accuracy                          |  |

| 3.4 Experimental results                        |  |

| 3.4.1 Frequency response                        |  |

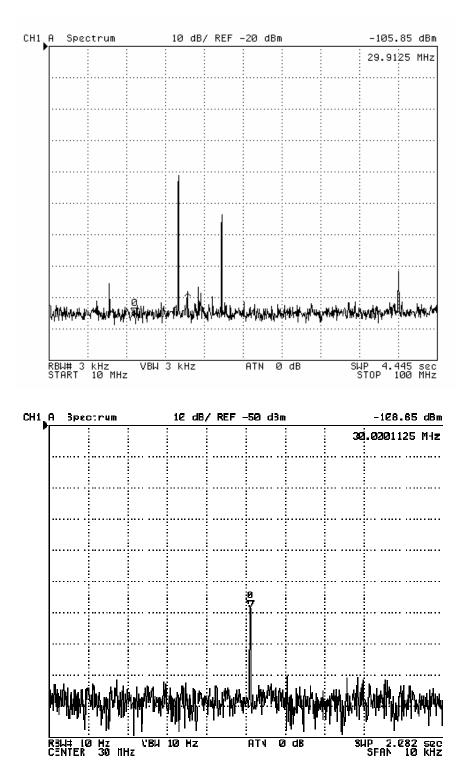

| 3.4.2 Linearity                                 |  |

| 3.5. Comparison with state of the art solutions |  |

| 4. CONCLUSION                                   |  |

| REFERENCES                                      |  |

| VITA                                            |  |

## LIST OF FIGURES

| Fig. 1.1 The use of filters to reduce the input range of an ADC                                         |    |

|---------------------------------------------------------------------------------------------------------|----|

| Fig. 1.2. The use of filters to avoid the aliasing problem                                              |    |

| Fig. 1.3. Simplified schematic of a DSL modem.                                                          |    |

| Fig. 1.4. OFDM signal in a) frequency domain and b) time domain                                         | 7  |

| Fig. 1.5 Intermodulation components caused by the distortion of the filter                              |    |

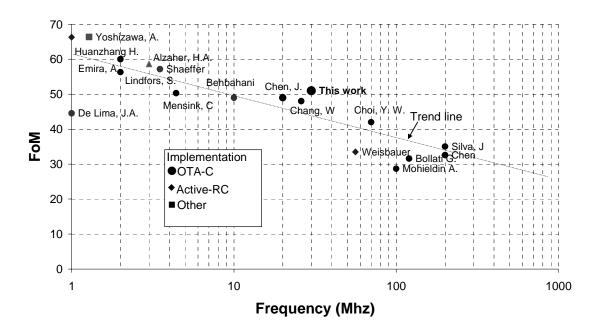

| Fig. 1.6 Figure of merit of recent publications about filters                                           |    |

| Fig. 2.1. The differential pair.                                                                        |    |

| Fig. 2.2. Differential pair with tail current transistor.                                               |    |

| Fig. 2.3. Differential pair with source degeneration                                                    |    |

| Fig. 2.4. Noise sources in the degenerated differential pair                                            |    |

| Fig. 2.5. Pseudo-differential pair with the tail current in the middle                                  |    |

| Fig. 2.6. The double differential pair                                                                  |    |

| Fig. 2.7. Cadence IM3 simulations for the circuit of figure 2.6                                         |    |

| Fig. 2.8. Relation between $I_{T1}$ and $I_{T2}$ for optimal linearity.                                 |    |

| Fig. 2.9. SDP and DDP designs for comparison with same transconductance,<br>Vdsat and power consumption |    |

| Fig. 2.10. Improvement in IM3 of the DDP over the SDP.                                                  |    |

| Fig. 2.11 IM3 plot vs. frequency                                                                        |    |

| Fig. 2.12 OTA design                                                                                    |    |

| Fig. 2.13. Second order ladder low-pass prototype                                                       |    |

| Fig. 2.14. Low-pass OTA implementation of the ladder filter                                             | 40 |

| Fig. 2.15. Linearity adjustment using a test OTA (TOTA)                                                 |    |

| Fig. 2.16. Micrograph of the chip                                                                                                         | 42 |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.17. IM3 of the filter and TOTA for several currents IT1 and IT2.                                                                   | 43 |

| Fig. 2.18. Effect of the transconductance control over the IM3                                                                            | 44 |

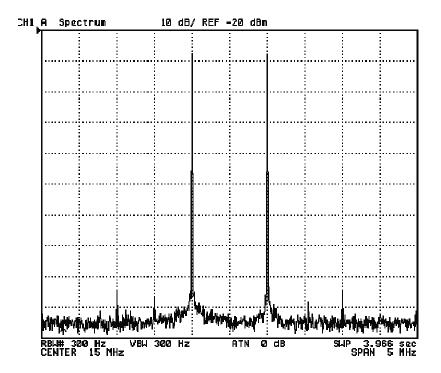

| Fig. 2.19. IM3 measurement at 20Mhz, 1.3 Vpp input.                                                                                       | 44 |

| Fig. 2.20. Programmable frequency responses of the filter.                                                                                | 45 |

| Fig. 2.21. Figure of merit of the filter in comparison with the state of the art in filters.                                              | 47 |

| Fig. 2.22. The triple differential pair block diagram                                                                                     | 48 |

| Fig. 2.23. (a) Degenerated DP, (b) degenerated DP with the tail current in the middle of the resistor and (c) proposed triple DP          | 50 |

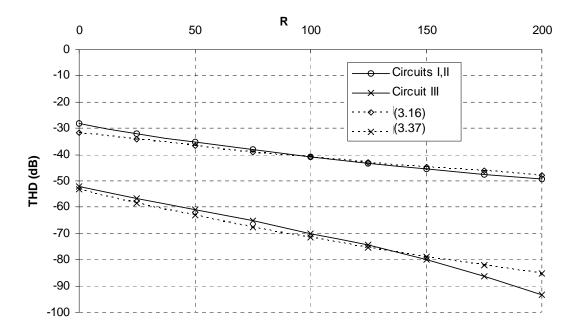

| Fig. 2.24. Simulated and theoretical THD for circuits in fig. 2.23                                                                        | 51 |

| Fig. 2.25. Simulations of circuits in fig. 2.23 for different values of R                                                                 | 53 |

| Fig. 2.26. Complete OTA using complementary triple-DP.                                                                                    | 55 |

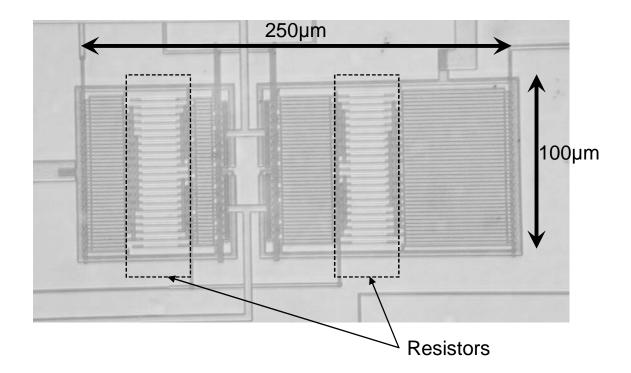

| Fig. 2.27. Micrograph of the OTA.                                                                                                         | 56 |

| Fig. 2.28. Intermodulation test for a 1.3Vpp input at 20MHz                                                                               | 58 |

| Fig. 2.29. IM3 vs. frequency.                                                                                                             | 58 |

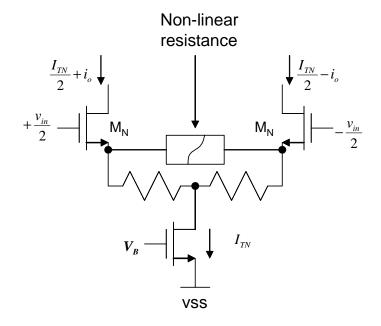

| Fig. 3.1. Non-linear degeneration resistance DP concept.                                                                                  | 62 |

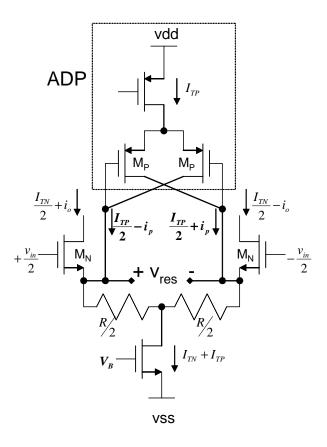

| Fig. 3.2. Implementation of the non-linear resistor using an auxiliary differential pair (ADP).                                           | 63 |

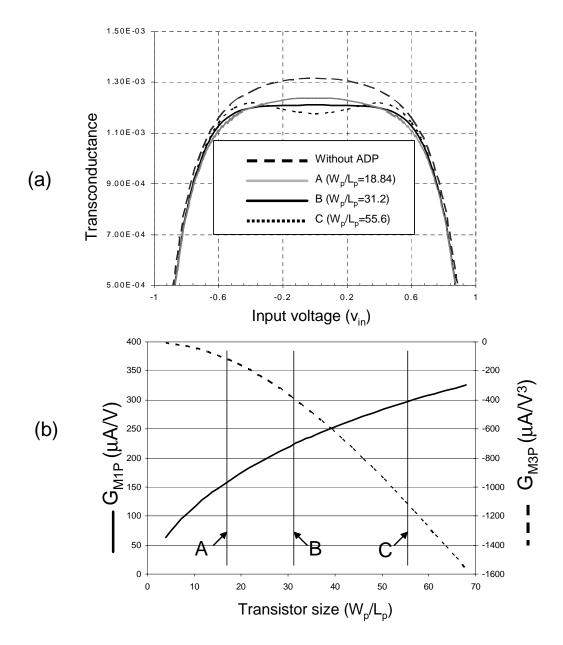

| Fig. 3.3. (a) Transconductance plots for different sizes of $M_P$ . (b) Values of $G_{M1P}$ and $G_{M3P}$ for different transistor sizes. | 68 |

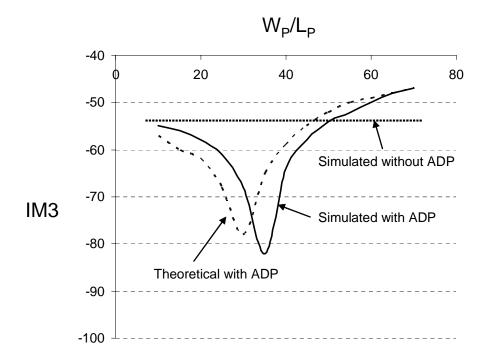

| Fig. 3.4. Theoretical and practical IM3 for different $W_p/L_p$ ratio.                                                                    | 69 |

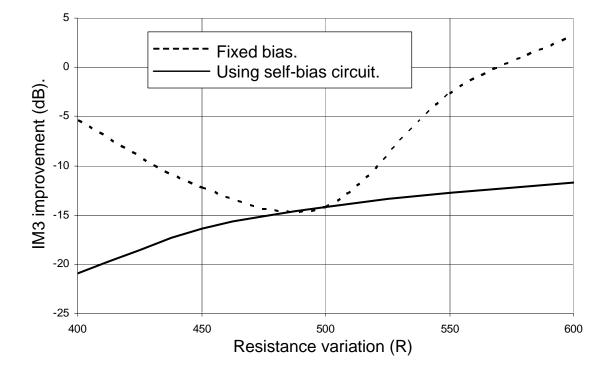

| Fig. 3.5. IM3 improvement variations with and without the self-bias circuit                                                               | 71 |

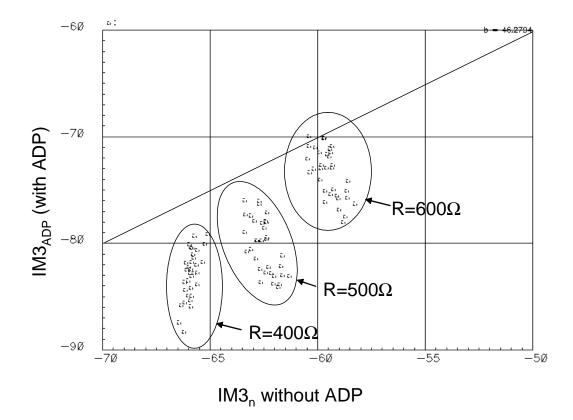

| Fig. 3.6. Scatter plot of Monte Carlo simulation of IM3 with and without ADP including process parameter variations. It is shown that at least 10dB improvement in IM3 can be guaranteed. | 72    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                                                                                                                                                                           |       |

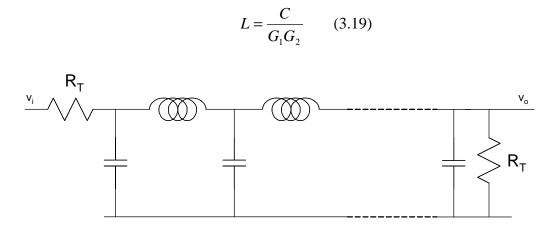

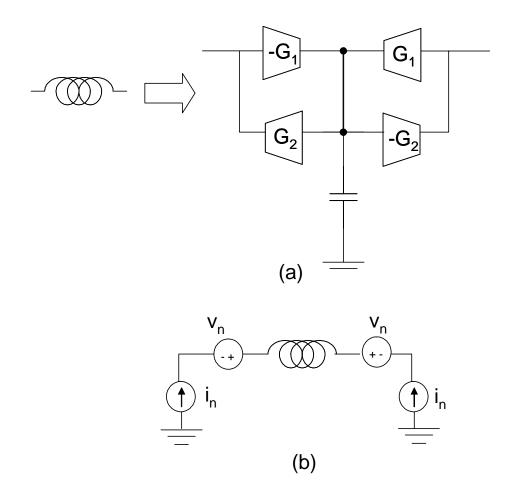

| Fig. 3.7. A generic ladder low-pass filter.                                                                                                                                               | 75    |

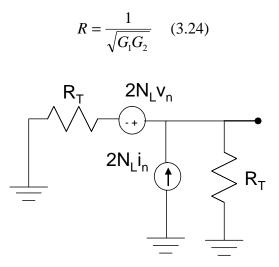

| Fig. 3.8. (a) Active inductance simulation using transconductors. (b) Noise representation of the active inductor                                                                         | 76    |

| Fig. 3.9. Noise model of a ladder low-pass filter at low frequencies                                                                                                                      | 77    |

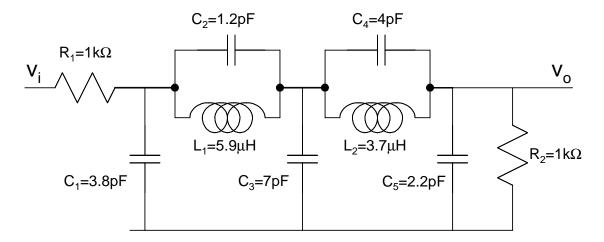

| Fig. 3.10. Ladder implementation of the elliptic filter 5 <sup>h</sup> order                                                                                                              | 79    |

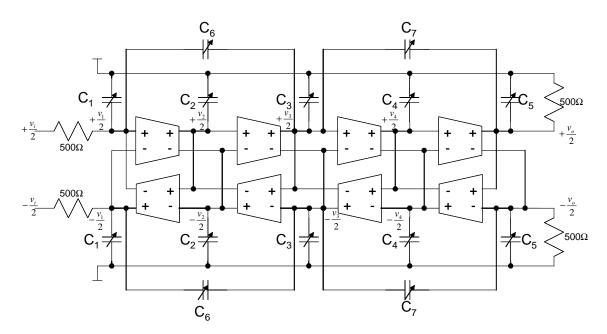

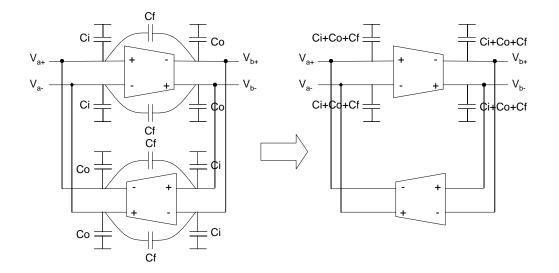

| Fig. 3.11. OTA-C implementation of the filter.                                                                                                                                            | 80    |

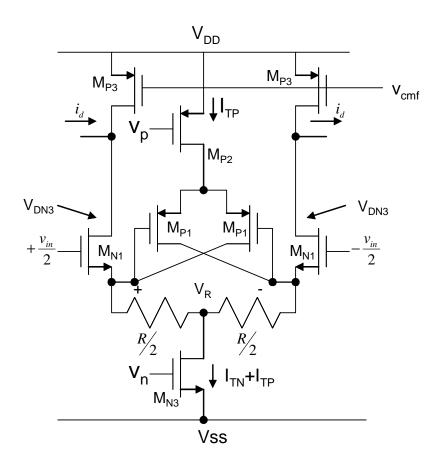

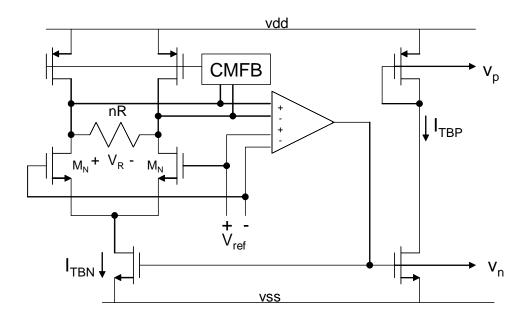

| Fig. 3.12 OTA design                                                                                                                                                                      | 81    |

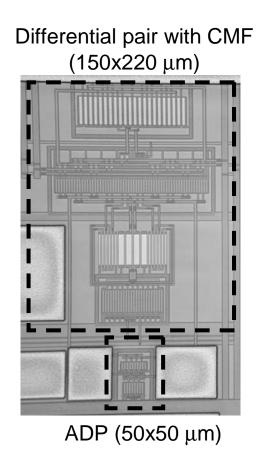

| Fig. 3.13. Micrograph of the OTA.                                                                                                                                                         | 85    |

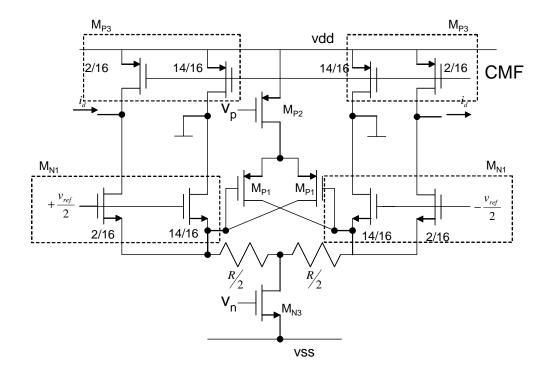

| Fig. 3.14. Diagram of the OTA with the common mode feed-back                                                                                                                              | 86    |

| Fig. 3.15. Auto-bias circuit concept.                                                                                                                                                     | 88    |

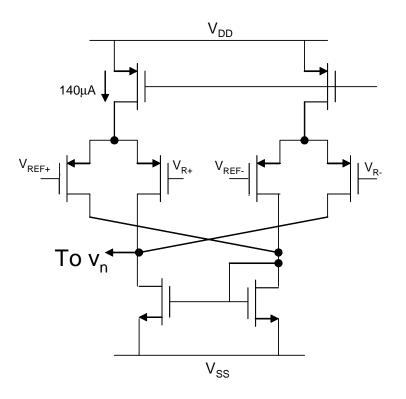

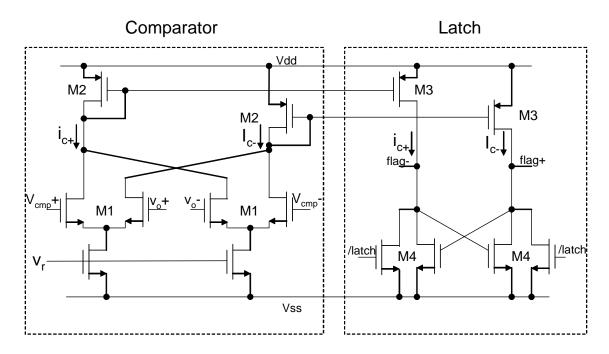

| Fig. 3.16. Comparator schematic.                                                                                                                                                          | 89    |

| Fig. 3.17 . IM3 vs. offset voltage in the comparator ( $V_{off}$ ).                                                                                                                       | 90    |

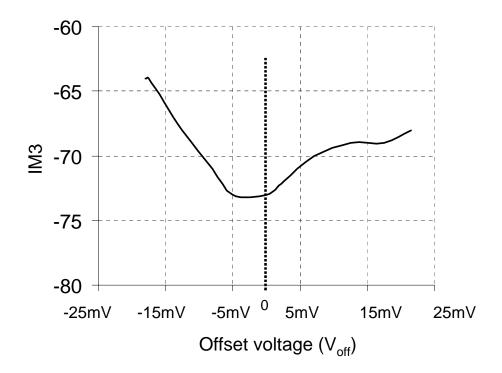

| Fig. 3.18. Switched capacitor array for frequency tuning. $C_{nominal} = 1.5*C$ . On grounded capacitors $C_B$ is connected to ground.                                                    | 92    |

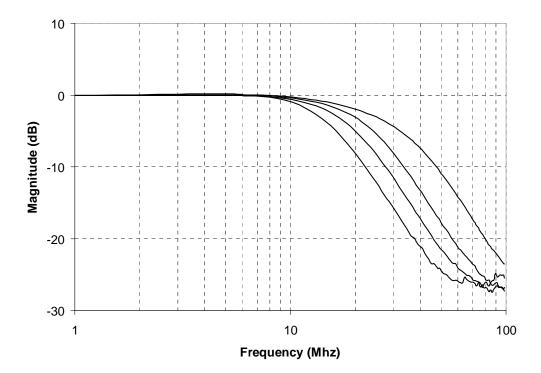

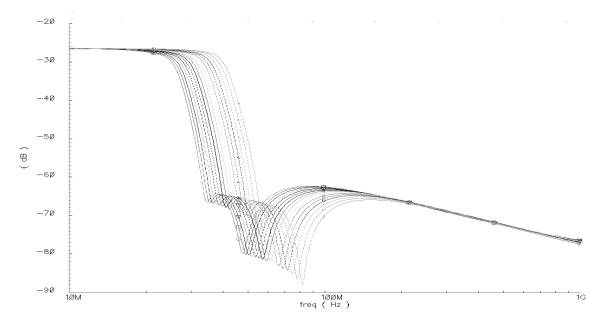

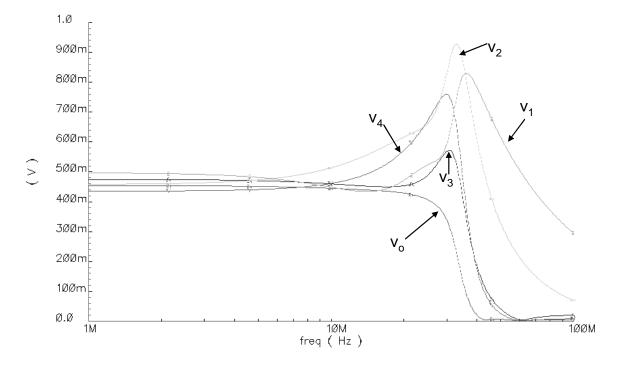

| Fig. 3.19. Programmable AC responses in the filter.                                                                                                                                       | 94    |

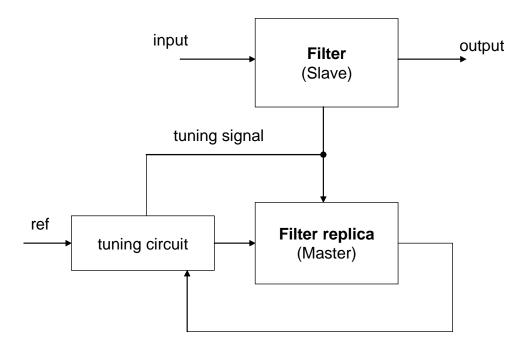

| Fig. 3.20. Master-slave approach.                                                                                                                                                         | 95    |

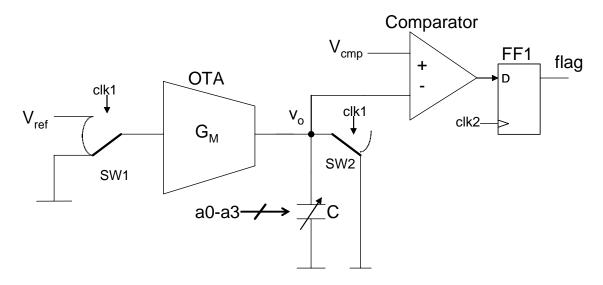

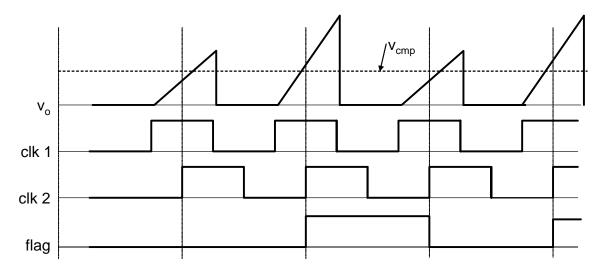

| Fig. 3.21. Automatic tuning (analog section)                                                                                                                                              | 98    |

| Fig. 3.22. Typical timing waveforms.                                                                                                                                                      | 98    |

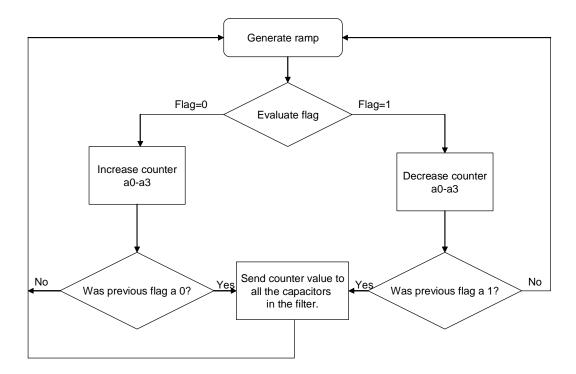

| Fig. 3.23. Block diagram of the digital control loop                                                                                                                                      | 99    |

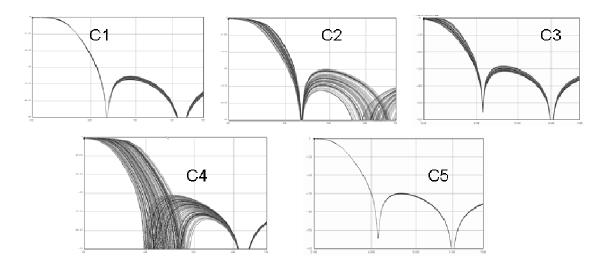

| Fig. 3.24. Transfer function changes with variations in individual capacitances                                                                                                           | . 100 |

| Fig. 3.25. OTA used in the automatic tuning system.                                                                                                                                       | . 102 |

|                                                                                      | Page |

|--------------------------------------------------------------------------------------|------|

| Fig. 3.26. Comparator used in the automatic tuning.                                  | 103  |

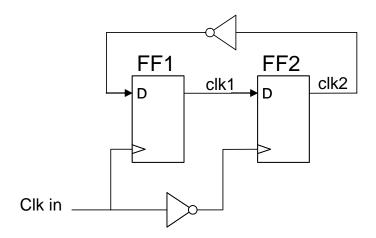

| Fig. 3.27. Clock generator.                                                          | 104  |

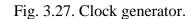

| Fig. 3.28. Digital control section                                                   | 104  |

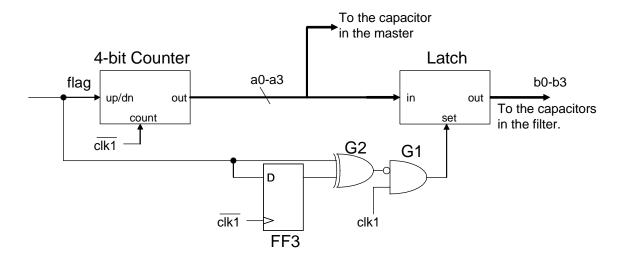

| Fig. 3.29. Deviation of the ideal ramp due to the finite output resistance           | 106  |

| Fig. 3.30. Parasitic capacitances in an OTA pair.                                    | 108  |

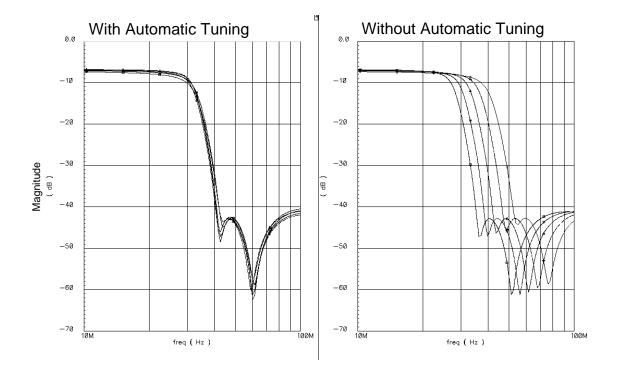

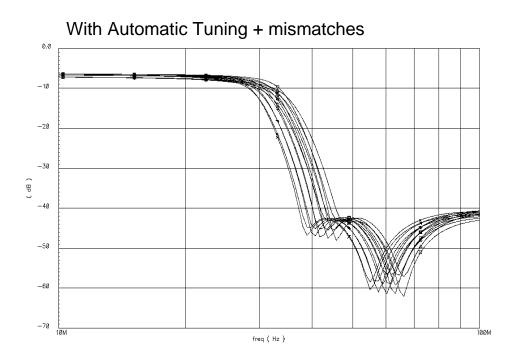

| Fig. 3.31. Variations of the magnitude response with and without automatic tuning.   | 109  |

| Fig. 3.32 Variations of the magnitude response with automatic tuning and mismatches. | 110  |

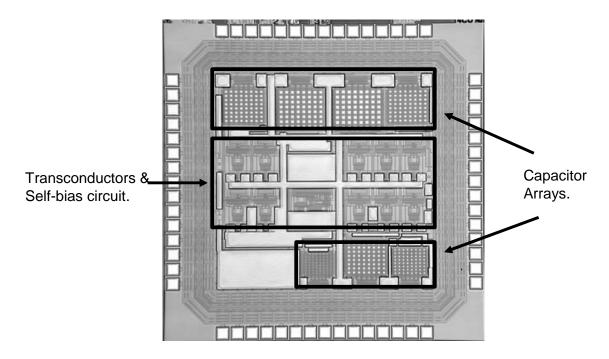

| Fig. 3.33. Micrograph of the chip                                                    | 111  |

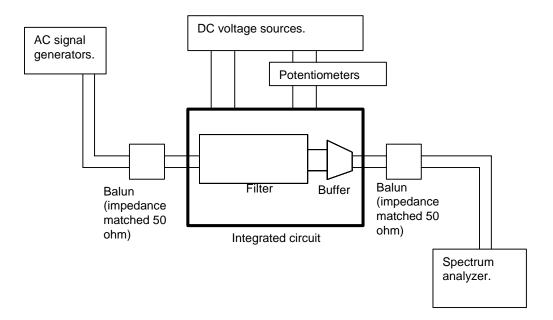

| Fig. 3.34. Test set-up.                                                              | 112  |

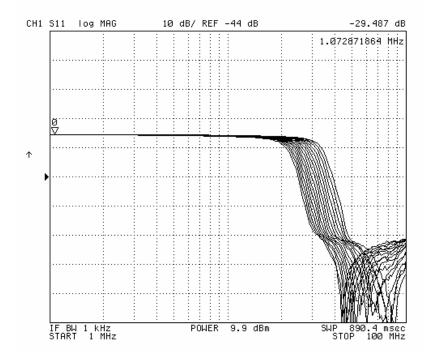

| Fig. 3.35. Measured AC responses                                                     | 113  |

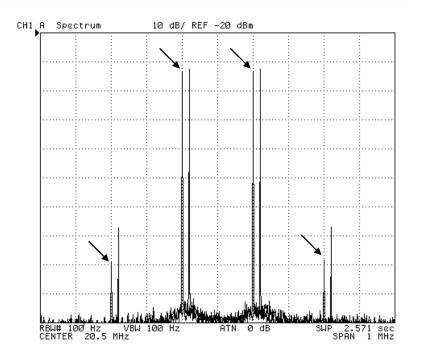

| Fig. 3.36. Intermodulation tests at 20MHz                                            | 114  |

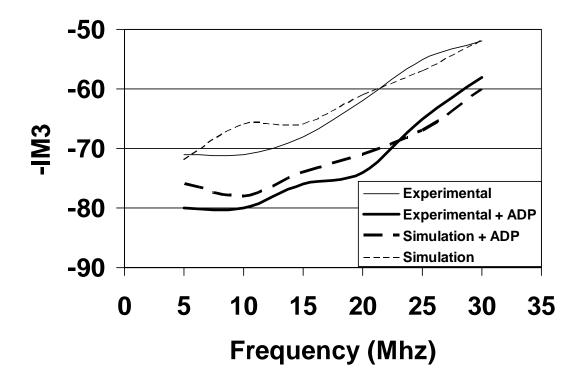

| Fig. 3.37. IM3 vs. frequency.                                                        | 115  |

| Fig. 3.38. Internal node AC response.                                                | 116  |

| Fig. 3.39. Out of band IM3 test.                                                     | 117  |

| Fig. 3.40. Figure of merit of recently reported filters vs. frequency                | 120  |

## LIST OF TABLES

| Table 2.1. Results for the comparison between SDP and DDP.                        | 33 |

|-----------------------------------------------------------------------------------|----|

| Table 2.2. Transistor sizes for the OTA. Length for all transistors is $1\mu m$ . | 38 |

| Table 2.3. Summary of experimental results of the filter                          | 45 |

| Table 2.4. Summary of experimental results                                        | 57 |

| Table 2.5. Comparison with recently reported OTAs.                                | 60 |

| Table 3.1 Approximation results.                                                  | 78 |

| Table 3.2. Transistor sizes.                                                      | 84 |

| Table 3.3. OTA: simulated parameters with $R=500\Omega$ .                         | 84 |

| Table 3.4. Nominal capacitor values.                                              | 92 |

| Table 3.5. Summary of experimental results                                        | 19 |

#### 1. INTRODUCTION

#### 1.1 The need of analog filters

With low-power and small integrated circuits based on microprocessors, microcontrollers and digital signal processors (DSP), much of the electrical functionality previously implemented with analog electronics, is now efficiently done with digital circuits. This rapid grow in digital electronics deluded to a common misconception that electronic circuits known as "analog" are eventually going to disappear. However, in order to acquire and generate natural signals such as audio, video, radio waves and many others, the need of an analog to digital and digital to analog interfaces remains a must.

Before an analog signal enters the analog to digital converter (ADC), it must be preprocessed by analog continuous time filters (CTF) or a combination between continuous time filters (CTF) and switched capacitors. The CTF serves two main purposes: i) it rejects unwanted frequency signals to avoid overloading the ADC and ii) prevents aliasing by attenuating components with higher frequency components.

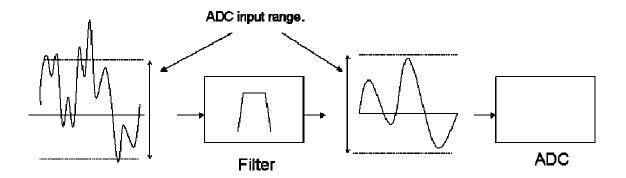

Figure 1.1 shows a typical signal in time domain where the amplitude is larger than the input range of the ADC marked with dashed lines. This signal may contain media noise, adjacent frequency channels not intended to be used by the end user, a DC signal, etc. A band-pass filter removes the undesired information, maintaining in-band information

This dissertation follows the style of the IEEE Circuits and Systems II Journal.

intended for the application. An alternative to the use of analog filters is the removal of out of band signals using digital processing after the ADC, but a larger requirement in the number of bits would be necessary. For example, it has been shown in [1] that the additional necessary number of bits (N) of an ADC to accommodate out of band signals is:

$$N = \frac{Int\left(\frac{I}{S} + 3\right)}{6dB} \tag{1.1}$$

where I is the power (in dB) of the out of band signals and S is the power of the data to be captured. (Int stands for the integer function) Without the filter, an additional number of bits would complicate the ADC implementation.

Fig. 1.1 The use of filters to reduce the input range of an ADC.

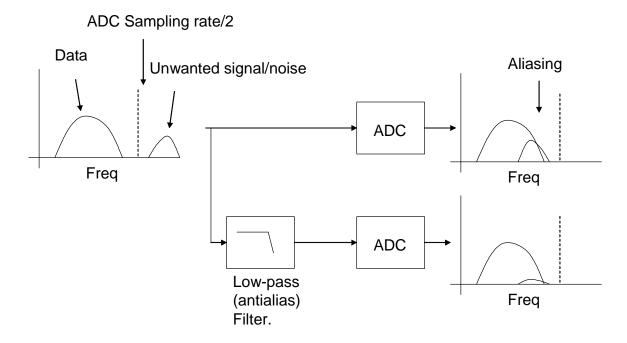

Whenever a continuous signal is sampled, all the frequencies above half the sampling rate are aliased back to the band of interest; this effect is known as aliasing . Figure 1.2 shows the frequency spectrum of a signal with higher frequency components higher than the half of the sampling rate of the ADC. Once the entire signal is sampled,

the undesired frequency components are aliased back into low frequency, tampering the useful data. To avoid this effect, a low-pass filter is necessary to remove higher frequency components.

Fig. 1.2. The use of filters to avoid the aliasing problem.

Although there is interest in developing powerful ADCs to remove analog filters and other analog blocks, technological limitations prevent this from being possible [2]. For low frequency operations, high resolutions can be achieved but as frequency increases higher power consumption designs are required to deal with parasitic capacitances that introduce bandwidth limitation; mismatch is also a limiting factor to the accuracy of an ADC. Digital to analog interfaces, also require continuous time analog filters at the end of the signal path to smoothen the output generated by the digital to analog converter (DAC).

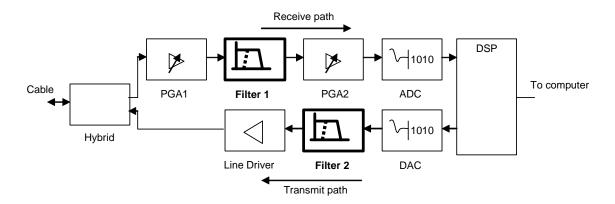

Figure 1.3 shows a block diagram of a typical modern communication system used in wired applications: a DSL modem. In the receive path, the incoming signal, which is weak due to attenuation in the cable, is amplified by a programmable gain amplifier (PGA1). A continuous time filter passes the required range of frequency spectrum while attenuating the out of band information and minimizing the alias signals for the subsequent analog to digital conversion. A second programmable gain amplifier (PGA2) may be used to further adjust the level of the signal to meet the input range of the analog to digital converter (ADC). The signal is then demodulated in the digital domain by the digital signal processor (DSP) and sent out to the user.

Fig. 1.3. Simplified schematic of a DSL modem.

In the transmit path, the digital data to be sent through the cable is modulated and converted to an analog signal by the use of a digital to analog converter (DAC). The continuous time filter smoothes the pulse-shaped analog DAC output. Finally, a line driver sends the signal through the cable.

#### 1.2 Challenges in continuous-time filters

The first filters that used resistors, inductors and capacitors are commonly known as RLC filters. These passive components occupied a very large area, especially at audio frequencies where heavy coils and big capacitors were the most noticeable components in the circuit board. Other applications, such as frequency division multiplexing telephone systems, required cheaper and smaller implementations. This gave rise to miniaturized piezoelectric technologies such as mechanical and crystal filters. Another similar technology based on acoustic waves, is the Surface Acoustic Wave (SAW) filter which is widely used in today's wireless communication circuits. A detailed description of the previous mentioned filters can be found in [3].

Since the invention of the integrated circuit in 1958, more and more external circuitry was merged into a single chip and, as the resolution of integration increases, the concept of having an entire system on a chip (SoC) became possible. Circuit blocks such as the microcontroller, digital signal processor, analog to digital converters and filters can be now integrated into a single chip resulting in cost savings, space reduction and simple interface. Thanks to these features, it is possible to have affordable compact cell phones, miniaturized biomedical implants, portable computers and many other devices.

Although feasible, the integration of continuous time filters presents several problems. The integration of inductors in a small semiconductor die is not possible for frequencies lower than several hundreds for megahertz due to very large area requirements and the considerable resistivity of metal layers used to build an inductor. Therefore, active elements based on transistors have to be used to emulate inductors to implement equivalent transfer functions. Unfortunately, active elements introduce additional noise, harmonic distortion components and consume static power. Another problem is that integrated capacitors, resistors and active elements are sensitive to temperature and process parameters variations which affect the selectivity and precision of the filter.

The aforementioned disadvantages present a stringent challenge for many modern communication systems. Actually, integrated continuous time filters have been referred by some authors as "the bottleneck" of communication circuits [4]. This is especially the case of systems using orthogonal frequency division multiplexing (OFDM) and discrete multi-tone (DMT) as modulation schemes. In these schemes, high data rates are transmitted over a wide frequency band in multiple orthogonal sub-carriers. Due to its many advantages such as flexibility, good noise immunity and the ability to be optimized for medium conditions [5],[6] its use can be found in wireless and wireline applications: Digital video broadcasting, local area wireless network (IEEE 802.11a), Asymmetric Digital Subscriber Line (ADSL), Very High Bit Rate DSL (VDSL) and Power Line Communications (PLC). However, the large peak to average ratio of these signals is a design issue [7].

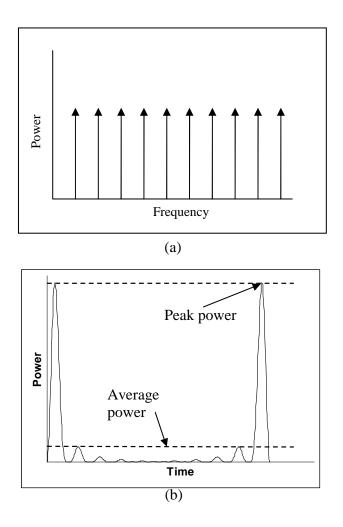

Figure 1.4 shows a typical OFDM signal in frequency and time domain. Figure 1.4(a) shows the signal in frequency domain with ten subcarriers equally spaced. In time domain, (figure 1.4(b)) the signal contains big peaks that occur at the moment when the maximums of all subcarriers coincide in time. Although the average power is small, the input range of the filter has to be large enough in order to accommodate these large peaks.

Fig. 1.4. OFDM signal in a) frequency domain and b) time domain.

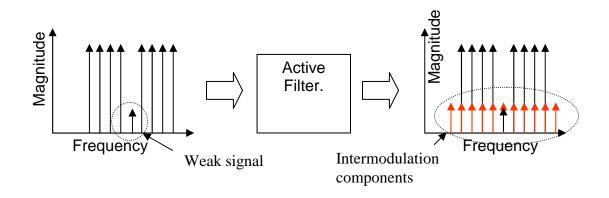

Figure 1.5 shows an OFDM spectrum with a weak sub-carrier before and after being passed through an active non-linear filter. The non-linearities of the filter causes the big sub-carriers to modulate between each other causing intermodulation components that interfere with neighboring sub-carriers. Thus, intermodulation components act as noisy interferers.

Fig. 1.5 Intermodulation components caused by the distortion of the filter.

The power of the signal divided by the power of the noise, is commonly referred as the Signal to Noise Ratio (SNR). Larger signals permit better SNR but it must be measured within the range such that the distortion of the filter does not generate enough intermodulation components to damage the information contained in the signal. The highest level of the signal divided by the power of noise is the Dynamic Range (DR).

To understand why DR is important, one may simply consider the analogy of a conversation in a noisy room, where the listener may misunderstand or not get some information from the speaker. A larger DR means that either the speaker may talk loudly or there is less noisy conversation or traffic around improving the clarity of the information. The same happens for communication systems where the information received is corrupted due to the noise generated by the media or electronic devices. Fortunately, communication systems contain error detection algorithms that reply to the transmitter inquiring the repetition of a damaged packet of information. However, the repetition of information degrades the speed of transmission, something that is not desirable in applications given the rapid advancing trend for higher data rates.

In many current and future generation applications, a high DR requirement forces to use external filters such as RLC or SAW. If off-chip solutions are used, besides the higher cost and larger area, internal buffers are also necessary to drive the low impedance usually found in this type of filters as well as the parasitic capacitances and inductances present in the bounding wires and pads. All these factors present a motivation for the search and improvement of the dynamic range of integrated continuous time filters.

As for the problem of temperature and process variations that modify the characteristics of integrated filters, on-chip self-tuning circuits have to be used. The function of this additional circuit is to calibrate the filter to exhibit a desired frequency response. There are many issues in the implementation of this circuit, especially at high frequencies [8].

1.3 State of the art in continuous time filters

Low and medium frequency active filters can be categorized depending of its basic building block implementation. The most popular building blocks are the Operational Amplifier (OP-AMP) and Operational Transconductance Amplifier (OTA).

Ideally, an OP-AMP is a voltage controlled voltage source with infinite gain but in practice the gain of the OP-AMP is finite and decreases for higher frequencies due to internal parasitic capacitances. The linearity of OP-AMPs is excellent for low-frequency applications, however the low gain at high frequencies may not effectively limit the nonlinearities. Furthermore, since OP-AMPs work in a closed-loop fashion, they are prone to be unstable which complicates the design for high performance.

Operational transconductance amplifiers (OTA) or simply "transconductors" are voltage controlled current sources. Since a simple transistor is inherently a voltage to current converter; the implementation of OTAs is simpler than OP-AMPs. In most cases, an OTA can be considered as an unbuffered OP-AMP.

Since the internal nodes of an OTA are mostly low-impedance, the bandwidth of operation is quite large allowing its use for high frequencies. The OTA operates in open loop without any local feed-back path and not raising stability problems as in the case of OP-AMPs. However, the non-linear behavior of transistors introduce distortion and a large number of techniques to deal with this problem have been reported in the literature.

To have a general panorama of today's state of art in active continuous-time filters, the most recent breakthroughs reported in the literature are evaluated. To this end, a figure of merit can be defined. A parameter that considers both SNR and linearity, is the spurious free dynamic range (SFDR) [9]. SFDR is defined as the dynamic range for an input voltage, such that the power of the harmonic distortion components is equal to the noise power.

The figure of merit consists of the SFDR normalized to the power consumption of a filter per pole in mW:

$$FoM = SFDR - 10\log(P/n_p)$$

(1.2)

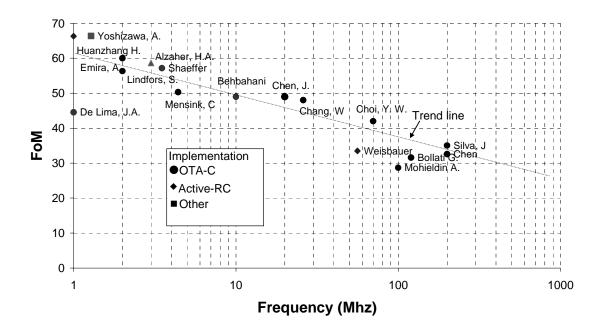

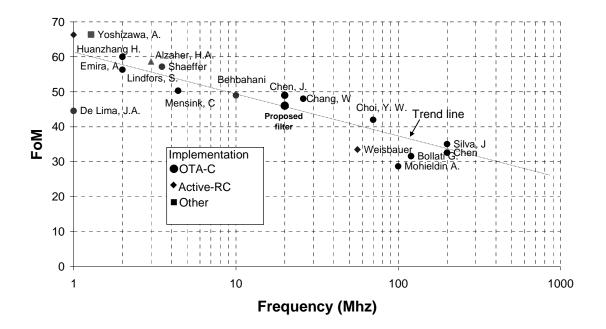

The FoM does not consider other parameters such as the quality factors (Q) or other additional features that a reported filter may have, but it gives an indication of the trend of this technology. Figure 1.6 shows FoM vs. frequency of operation for the most recent journal filter publications [10]-[24]. There is a decaying trend line as frequency increases because there is more integrated thermal noise and many linearity techniques cannot be applied for higher frequencies efficiently. The dynamic range depends on the frequency of operation; also reported linearization techniques are not very effective at higher frequencies.

It is interesting to see that most of the reported high frequency techniques use OTAs. This is due to the fact that OTA-C implementations are simpler for frequencies of tenths of MHz and more reliable in terms of stability if compared to Active-RC.

Arising technologies require higher circuit performances and this is the case for analog interfaces requiring continuous time filters. For instance, in ADSL (Asymmetrical Digital Subscriber Lines) cable modem applications, the linearity has to be better than 60dB [25]-[26] and video applications require at least 60 dB of linearity at 5 MHz [27]. Future trends pushing towards higher data transfers will require higher frequency ranges with equal or better linearity.

Fig. 1.6 Figure of merit of recent publications about filters.

#### **1.4 Contributions**

In this dissertation, three techniques for the design of high dynamic range OTA-C filters are proposed. These techniques are based in the linearization of the most important contributor to the distortion in the OTA: The differential pair.

First, the double differential pair is introduced where the distortion due to one differential pair is cancelled by the auxiliary circuit. If properly dimensioned and biased, the double differential pair offers an advantage of more than 10dB of linearity for the same power consumption and transconductance compared to the typical differential pair with a very small noise 1-2dB increase. An OTA based on the double differential is presented featuring 25% continuous transconductance tuning with minimal linearity degradation. The OTA is tested in a 20-MHz second order low-pass ladder filter prototype. With a 10.5mW of power per OTA, the filter achieves -65dB IM3 for 1.3Vpp.

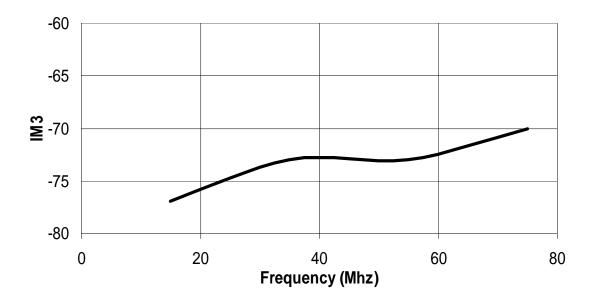

The second proposed technique is a triple differential pair architecture. it offers a more robust linearity cancellation with the drawback of reduced transconductance per power. Experimental results for an OTA fabricated in the TSMC 0.35 $\mu$ m CMOS process are presented and compared with recently reported topologies. Draining 2.8mA from a single supply voltage of 3.3V, the transconductor achieves IM3<-70dB for a two-tone input signal of 1.3Vpp measured at 70 MHz. The input referred noise density is only 7nV/ $\sqrt{Hz}$ , leading to a SNR of 75dB.

Finally, the non-linear source degeneration differential pair is presented. The linearity of a typical source degenerated structure is improved by more than 10 dB while the overall small signal transconductance is reduced by less than 10%; the additional power needed by the auxiliary circuitry is less than 10 % of the OTA's power, and the noise level increases by no more than 1 dB. A self-bias circuit is used to match the transconductance to polysilicon resistor values serving two purposes: i) ensuring the linearity of the OTA against process parameter variations and ii) allowing the use of polysilicon resistors for filter's terminations. The technique is tested in a 30MHz 5th order elliptic filter consuming 85mW of static power and achieving a spurious free dynamic range (SFDR) of 65dB. With these results, this filter is 6dB above the trend

line shown in figure 1.6. An automatic frequency tuning circuit to is included to reduce the low-pass frequency cut-off with process parameter variations.

#### 1.5 Organization

Section 2 starts by describing the main noise and linearity issues of a simple differential pair. Then, the double differential pair is introduced and studied. A full OTA design using the double differential is described and incorporated in a second order 20-MHz low-pass filter. Simulated and experimental results are included. Finally, the triple differential pair is analyzed. Simulation and experimental results are shown and are compared with previously reported topologies.

Section 3 discusses the non-linear source degeneration technique. A 30-MHz elliptic low-pass filter design is presented suitable for next generation Power Line Communication Systems. Details of the OTA, filter tuning, automatic bias and other issues are addressed. The design of an automatic tuning circuit is explained. Experimental results are shown and compared with previous publications. Finally, section 4 presents the conclusions and summarizes the contributions of this work.

# 2. LINEARITY ENHANCEMENT TECHNIQUES BASED ON NON-LINEARITY CANCELLATION

Distortion occurs in the voltage to current conversion due to the non-linear behavior of transistors in the differential pair. The first part of this section addresses the linearity and noise issues of the differential pair. Then, the techniques based on nonlinearity cancellation are presented: The double differential pair and the triple differential pair. The double differential pair is discussed and an OTA and filter implementation is presented. The last part of the section discusses the triple differential pair and describes simulation and experimental results.

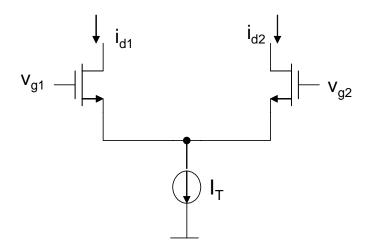

#### 2.1 The differential pair

The differential pair is the most popular structure used in the implementation of differential OTAs (Figure 2.1). One of the more important properties of the differential pair is that it has a very good rejection to common mode signals; however the linearity is limited due to the tail current transistor. In this subsection the analysis of distortion and noise of the differential pair is presented. The outcomes are used as the basis for the evaluation of the proposed techniques.

Fig. 2.1. The differential pair.

#### 2.1.1 Distortion

For a MOS transistor working in saturation, the drain current is given by:

$$i_d = K(v_g - v_s - V_T)^2$$

(2.1)

where  $V_T$  is the threshold voltage and K is a physical constant given by:

$$K = \frac{1}{2}\mu C_{ox}\left(\frac{W}{L}\right) \qquad (2.2)$$

W and L are the width and length of the transistor respectively;  $\mu$  is the mobility of carriers (electrons for N-type transistors and holes for P-type transistors) and C<sub>ox</sub> is the oxide capacitance per unit area.

For the differential pair shown in fig. 2.1, the input voltage of each transistor is:

$$v_{g1} = v_{cm} + \frac{v_{in}}{2}$$

$v_{g2} = v_{cm} - \frac{v_{in}}{2}$

(2.3)

where  $v_{cm}$  is the common mode voltage and  $v_{in}$  the differential input voltage. Defining  $v_c=v_{cm}-v_s-V_T$  and using (2.2),  $i_{d1}-i_{d2}$  is given by:

$$i_{d1} - i_{d2} = -2Kv_{in}v_c \quad (2.4)$$

Due to the current source, the sum of  $i_{d1}$  and  $i_{d2}$  must be equal to  $I_T$ , then:

$$i_{d1} + i_{d2} = I_T = 2K \left( \frac{v_{in}^2}{4} + v_c^2 \right)$$

(2.5)

Solving for  $v_c$  in (2.5) and using the outcome in (2.4) yields:

$$\dot{i}_{d1} - \dot{i}_{d2} = 2Kv_{in}\sqrt{\frac{I_T}{2K} - \frac{v_{in}^2}{4}}$$

(2.6)

Defining differential current as  $i_0 = (i_{d1} - i_{d2})/2$ , (2.6) can be expressed as:

$$i_{o} = \frac{g_{m}v_{in}}{2} \sqrt{1 - \frac{v_{in}^{2}}{4V_{dssat}^{2}}}$$

(2.7)

where  $g_m$  is the transconductance of the transistor given by:

$$g_m = 2KV_{dssat} \tag{2.8}$$

and  $V_{dssat}$  is the DC saturation voltage given by:

$$V_{dssat} = V_G - V_S - V_T = \sqrt{\frac{I_T}{K}} \quad (2.9)$$

For a simplified distortion analysis, the above expression can be expanded in taylor series around  $v_{in}=0$ , such that:

$$i_o = \sum_{n=0}^{\infty} G_{M(2n+1)} \cdot v_{in}^{2n+1}$$

(2.10)

where,

$$G_{Mj} = \frac{g_m}{2^{2(j-1)} V_{dssat}^{j-1}}$$

(2.11)

$G_{M1}$  is the linear coefficient and  $G_{M3}, G_{M5},...$  are undesired non-linear terms. For weak signals, the distortion is mainly produced by the third order term; therefore higher terms can be ignored leading to:

$$i_o \approx G_{m1} v_{in} + G_{m3} v_{in}^{3}$$

(2.12)

The linearity can be measured in terms of intermodulation distortion. Two sinusoidal tones are used for the input such that:

$$v_{in} = \frac{A}{2}\cos(\omega_1 t) + \frac{A}{2}\cos(\omega_2 t) \qquad (2.13)$$

where A is maximum amplitude and  $\omega_1$  and  $\omega_2$  are the angular frequencies of each tone. Using (2.13) in (2.12) and trigonometric identities, one arrives at:

$$i_{o} = \left(\frac{G_{m1}A}{2} + \frac{9G_{M3}A^{3}}{32}\right) (\cos(\omega_{1}t) + \cos(\omega_{2}t)) + \left(\frac{3G_{M3}A^{3}}{32}\right) (\cos((2\omega_{1} - \omega_{2})t) + \cos((2\omega_{2} - \omega_{1})t)) + \cos((2\omega_{1} + \omega_{2})t) + \cos((2\omega_{2} + \omega_{1})t))$$

(2.14)

$$+ \left(\frac{G_{M3}A^{3}}{32}\right) (\cos((3\omega_{1}t) + \cos((3\omega_{2}t))))$$

The second term contains the intermodulation products. Since these components are caused by the third order term in (2.12) it is referred as the third order intermodulation distortion symbolized IM3 and it is measured as the power ratio of one of the intermodulation products to one fundamental tone. Therefore:

$$IM3 = \frac{\frac{3G_{M3}A^3}{32}}{\frac{G_{m1}A}{2} + \frac{9G_{M3}A^3}{32}} \qquad (2.15)$$

Since  $G_{M3}$  is usually very small compared to  $G_{M1}$ , then:

$$IM3 = \frac{3G_{M3}A^2}{16G_{m1}}$$

(2.16)

Applying (2.11) in (2.16) results in:

$$IM3 = \frac{3A^2}{128V_{dssat}^2} \qquad (2.17)$$

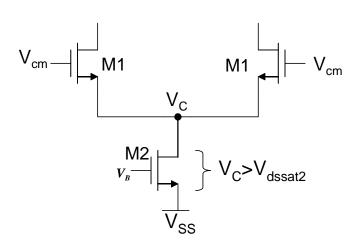

According to (2.17), using larger  $V_{dssat}$  yields a better linearity. However, in order to keep all the transistors working in saturation,  $V_{dssat}$  has to be limited as shown in fig. 2.2 to:

$$V_{dssat1} < (V_{cm} - V_{ss}) - (V_{dsat2} + V_T)$$

(2.18)

Fig. 2.2. Differential pair with tail current transistor.

To further reduce the distortion, a resistor connected between the sources of transistors M1 and M2 can be used as shown in fig. 2.3. To simplify the analysis, the middle node of the resistor is referred as  $v_r$ , then the voltage at the sources of M1 and M2 is.

$$v_{s1} = v_r + \frac{v_{res}}{2}$$

(2.19)

$v_{s2} = v_r - \frac{v_{res}}{2}$  (2.20)

where  $v_{res}$  is the voltage drop across the resistor. Using (2.1), (2.19) and (2.20) the drain currents are:

Fig. 2.3. Differential pair with source degeneration.

Defining vc=V<sub>cm</sub>-v<sub>r</sub>-V<sub>T</sub>, and following the same procedure as (2.4) to (2.7), one arrives at:

$$i_{o} = \frac{g_{m}(v_{in} - v_{res})}{2} \sqrt{1 - \frac{(v_{in} - v_{res})^{2}}{4V_{dssat}^{2}}} \quad (2.23)$$

where the taylor expansion is given by:

$$i_o = \sum_{n=0}^{\infty} G_{M(2n+1)} \cdot (v_{in} - v_{res})^{2n+1} \qquad (2.24)$$

Notice that the only difference between (2.24) and (2.10) is that  $v_{res}$  is subtracted to  $v_{in}$ . The current passing through the resistance is  $i_{res}=i_{d1}-I_T/2 = -(i_{d2}-I_T/2)$ ; Clearing  $I_T$ yields,

$$i_{res} = \frac{i_{d1} - i_{d2}}{2} = i_o \qquad (2.25)$$

Then the voltage across the resistance is:

$$v_{res} = i_o R \qquad (2.26)$$

If (2.26) is used in (2.23), a fourth order equation would result that can be very complex and tedious to solve  $i_0$  in terms of  $v_{in}$ . An alternative is to obtain the solution directly in a series expansion which for the purpose of studying the linearity is more useful. The solution in a series expansion can be expressed as:

$$i_o = \sum_{k=0}^{\infty} C_{2k+1} v_{in}^{2k+1} \qquad (2.27)$$

where  $C_k$  are unknown coefficients. To find these, (2.27) can be plugged in (2.24) resulting in:

$$\sum_{k=0}^{\infty} C_{2k+1} v_{in}^{2k+1} = \sum_{n=0}^{\infty} G_{M(2n+1)} \cdot (v_{in} - R \sum_{k=0}^{\infty} C_{2k+1} v_{in}^{2k+1})^{2n+1}$$

(2.28)

Notice in the right hand expression that terms in the summatory with  $v_{in}$  will only be produced when n=0, terms with vin<sup>3</sup> when n=0 and n=1, terms with vin<sup>5</sup> with n=0, n=1 and n=2. Therefore, if we are only interested to solve C<sub>1</sub>,C<sub>3</sub> and C<sub>5</sub> we can perform the summatory up to n=2 and k=2 and ignore terms elevated to a power higher than five. Then, (2.28) becomes:

$$C_{1}v_{in} + C_{3}v_{in}^{3} + C_{5}v_{in}^{5} = G_{M1}((1 - RC_{1})v_{in} - RC_{3}v_{in}^{3} - RC_{5}v_{in}^{5}) + G_{M3}((1 - RC_{1})v_{in} - RC_{3}v_{in}^{3} - RC_{5}v_{in}^{5})^{3} + G_{M5}((1 - RC_{1})v_{in} - RC_{3}v_{in}^{3} - RC_{5}v_{in}^{5})^{5}$$

(2.29)

Expanding and ignoring terms vin with order higher than five yields,

$$\left( \left( 1 + G_{M1}R \right)C_1 - G_{M1} \right) v_{in} + \left( C_3 G_{m1}R + G_{M3} \left( 1 - C_1 R \right)^3 \right) v_{in}^{\ 3} + \left( \left( 1 + G_{M1}R \right)C_5 + 3G_{M3} \left( 1 - RC_1 \right)^2 RC_3 + G_{M5} \left( 1 - RC_1 \right) \right) v_{in}^{\ 5} = 0$$

$$(2.30)$$

For this equation to hold, each of the coefficient has to be zero, then it is straightforward to solve  $C_1$ , the  $C_3$  and finally  $C_5$ , thus:

$$C_{1} = \frac{G_{M1}}{(1 + RG_{M1})}$$

(2.31)

$$C_{3} = \frac{G_{M3}}{(1 + RG_{M1})^{4}}$$

(2.32)

$$C_{5} = \frac{G_{M5} + R(G_{M1}G_{M5} - 3G_{M3}^{2})}{(1 + RG_{M1})^{7}} \qquad (2.33)$$

Finally the output current can be expressed as:

$$i_{o} = \frac{G_{M1}}{(1 + RG_{M1})} v_{in} + \frac{G_{M3}}{(1 + RG_{M1})^{4}} v_{in}^{3} + \frac{G_{M5} + R(G_{M1}G_{M5} - 3G_{M3}^{2})}{(1 + RG_{M1})^{7}} v_{in}^{5}$$

(2.34)

For weak non-linearities, the third term is higher than the fifth order term being the larger contributor to distortion, then using (2.13) in (2.34) results in:

$$IM3 = \frac{3A^2}{128V_{dssat}^2 (1+N_r)^3} \quad (2.35)$$

where  $N_r$  is the degeneration factor given by  $N_r=G_{M1}R$ . Higher degeneration factors improve the linearity at the cost of reduced linear transconductance given by:

$$G_{M} = \frac{G_{M1}}{(1+N_{r})}$$

(2.36)

2.1.2 Noise

Figure 2.4 presents the degenerated differential pair with all the equivalent noise sources.

Fig. 2.4. Noise sources in the degenerated differential pair.

Each noise source is given by:

$$\frac{i_{n1}^{2}}{Hz} = 4kT\gamma g_{m1} \qquad (2.37)$$

$$\frac{i_{n2}^{2}}{Hz} = 4kT\gamma g_{m2} \qquad (2.38)$$

$$\frac{i_{r}^{2}}{Hz} = \frac{4kT}{R} \qquad (2.39)$$

where k is the Boltzman constant, T the temperature,  $\gamma$  is typically in the range of 0.7 to 2,  $g_{m1}$  and  $g_{m2}$  the transconductance of M1 and M2 respectively. The total output noise current can be found as:

$$\frac{i_{no}^{2}}{Hz} = 4kT \left( \frac{2}{\left(2 + g_{m1}R\right)^{2}} \gamma g_{m1} + \frac{g_{m1}^{2}R}{\left(2 + g_{m1}R\right)^{2}} + 2\frac{\left(g_{m1}R\right)^{2}}{\left(2 + g_{m1}R\right)^{2}} \gamma g_{m2} \right)$$

(2.40)

Using the definition in (2.11) where  $G_{M1}=g_{m1}/2$ , yields:

$$\frac{i_{no}^{2}}{Hz} = 4kT \left( \frac{1}{\left(1 + G_{M1}R\right)^{2}} \gamma G_{M1} + \frac{G_{m1}^{2}R}{\left(1 + G_{M1}R\right)^{2}} + 2\frac{\left(G_{M1}R\right)^{2}}{\left(1 + G_{M1}R\right)^{2}} \gamma g_{m2} \right) \quad (2.41)$$

Since  $Nr=G_{M1}R$ , the input referred noise is:

$$\frac{v_{no}^{2}}{Hz} = \frac{\frac{\dot{I}_{no}^{2}}{Hz}}{\frac{G_{m1}^{2}}{(1+N_{r})^{2}}} = \frac{4kT}{G_{m1}} \left(\gamma + N_{r} + 2N_{r}^{2}\gamma \frac{g_{m2}}{G_{m1}}\right)$$

(2.42)

The third term inside the parenthesis is due to the noise of the tail current sources. This term can be minimized by reducing  $g_{m2}$  with respect to  $G_{m1}$ . However, this term can be eliminated if the differential pair is arranged as shown in figure 2.5. Then,

the noise due to the tail current is equally injected to both branches appearing as common-mode rather than differential.

Fig. 2.5. Pseudo-differential pair with the tail current in the middle.

The input referred noise density of the DP of fig. 2.5 is then given by:

$$v_{in}^{2} = \frac{4kT}{G_{m1}} (\gamma + N_{r}) \quad (2.43)$$

$$V_r = \frac{I_T R}{4} \qquad (2.44)$$

This voltage drop limits the voltage headroom for Vdsaat1 and Vdssat2 and therefore Nr must be limited.

From the analysis shown here, it can be seen that the distortion can be improved by using larger  $V_{dssat1}$  but the supply voltage limits this value. The increase of the degeneration factor (Nr) is then a good alternative for improved linearity but the drawback is that excessive degeneration factors reduce the total transconductance (for the same amount of power) and increase the noise.

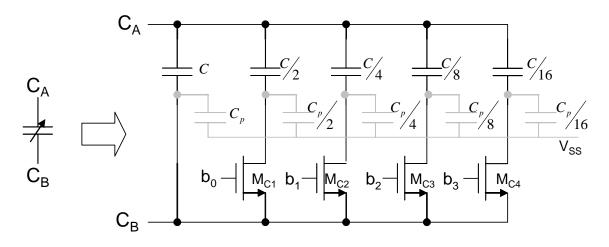

## 2.2 The double differential pair

The double differential pair consists of two differential pairs with cross-coupled outputs such that the third order distortion components are cancelled. The following subsections present the analysis and performance comparison with the conventional simple differential pair.

### 2.2.1 Analysis

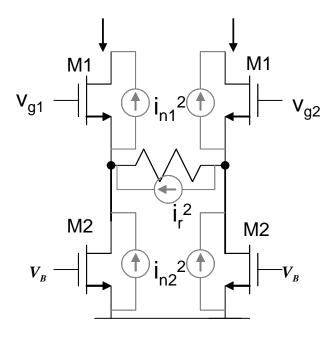

Figure 2.6 shows the double differential pair where the total output is given by,

$$i_{oT} = i_{o1} - i_{o2}$$

(2.45)

Fig. 2.6. The double differential pair.

Based on (2.34),  $i_0$  is then given by (the fifth order component is neglected for simplicity):

$$i_{aT} = (\frac{G_{M1,1}}{G_{M1,1}} - \frac{G_{M1,2}}{G_{M1,2}})v_{in} + (\frac{G_{M3,1}}{G_{M3,1}} - \frac{G_{M3,1}}{G_{M3,1}})v_{in}$$

$$i_{oT} = \left(\frac{G_{M1,1}}{(N_{r1}+1)} - \frac{G_{M1,2}}{(N_{r2}+1)}\right)v_{in} + \left(\frac{G_{M3,1}}{(N_{r1}+1)^4} - \frac{G_{M3,2}}{(N_{r2}+1)^4}\right)v_{in}^{3}$$

(2.46)

For cancellation of the third order component, which is the main contribution to distortion component, the following condition has to be met,

$$\frac{G_{M3,1}}{(N_{r1}+1)^4} = \frac{G_{M3,2}}{(N_{r2}+1)^4}$$

(2.47)

Using (2.8) and (2.2), the above expression can be presented as:

$$\frac{I_{T1}}{I_{T2}} \left( \frac{2 + \sqrt{I_{T1}K_1} (R_1 + R_{\theta 1})}{2 + \sqrt{I_{T2}K_2} (R_2 + R_{\theta 2})} \right)^8 = \left( \frac{(W/L)_1}{(W/L)_2} \right)^3$$

(2.48)

Equation (2.48) also includes an additional resistance  $R_{\theta}$  in series with the degeneration resistance to consider the mobility degradation effect. This effect has an important contribution in the linearity, especially for small channel lengths. The equivalent resistance due to mobility degradations [28] is:

$$R_{\theta} = \frac{\theta}{\left(\frac{W}{L}\right)\mu_{o}C_{ox}} \qquad (2.49)$$

where  $\mu_0$  is the low-field mobility and  $\theta$  the mobility constant given by:

$$\theta = \frac{1}{L \cdot E_c} + \theta_T \qquad (2.50)$$

The first term of (2.50) represents the mobility degradation due to the lateral electric field where Ec is the lateral critical electric field.  $\theta_T$  is a fitting parameter to also consider the mobility due to the transversal electric field. Typical values of  $\theta$  are in the order of 0.3 V<sup>-1</sup> to 2 V<sup>-1</sup> for sub-micron technologies.

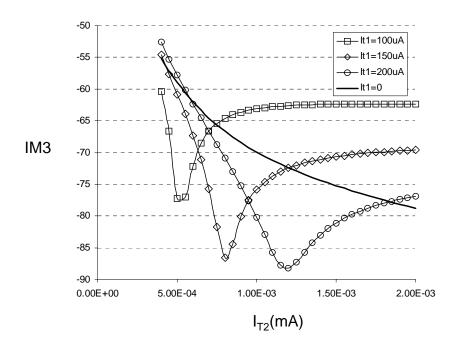

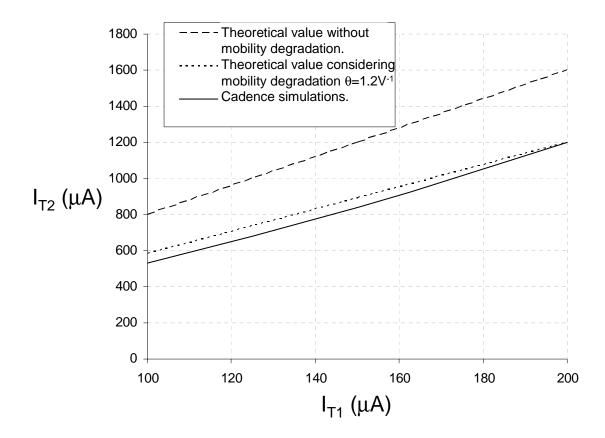

To corroborate (2.48), the circuit of fig. 2.6 was simulated using Cadence with the following values:  $(W/L)_1=20\mu m/1\mu m$ ,  $(W/L)_1=40\mu m/1\mu m$ ,  $\mu C_{ox}=120\mu A/V$ ,  $R_1=2k\Omega$ and  $R_2=500\Omega$ . Figure 2.7 shows the IM3 vs.  $I_{T2}$  for an input voltage of  $200_{mVpp}$  around 20MHz for three different  $I_{T1}$ . A fourth curve depicted with a wide line shows the IM3 of the larger differential pair for reference. Notice that for the three values of  $I_{T1}$  there is a  $I_{T2}$  at which IM3 is improved by almost 20dB. To verify that (2.48) agrees with simulated results, fig 2.8 shows the relationship between  $I_{T2}$  and  $I_{T1}$  where the maximum linearity is achieved. Notice that if mobility degradation is not considered (eg  $R_{\theta_1}=R_{\theta_2}=0$ ), (2.48) significantly deviates from simulated results. This is due to the fact that the term in the parenthesis of the left-hand side of (2.48) is elevated to the power of eight and any small variations, such as the mobility degradation resistance, produce a significant deviation. However, if mobility degradation is considered ( $\theta=1.2V^{-1}$ ), then (2.48) is close to the simulation result.

Fig. 2.7. Cadence IM3 simulations for the circuit of figure 2.6.

Fig. 2.8. Relation between  $I_{T1}$  and  $I_{T2}$  for optimal linearity.

As shown in the above analysis, to effectively suppress the third order component, one must consider  $\theta$ . Similar reported structures that do not consider the mobility degradation effect are subject to large errors and the linearity improvement may not be optimal. Even if considered, the mobility degradation factor  $\theta$  is a process dependent parameter and cannot be accurately predicted nor controlled.

### 2.2.2 Improvement comparison

Since the outputs of the differential pairs are subtracted, the effective transonductance  $G_{mT}$  of the DDP is reduced by:

$$G_{MT} = \frac{G_{M1,1}}{(N_{r1}+1)} - \frac{G_{M1,2}}{(N_{r2}+1)} \quad (2.51)$$

In addition, the noise increases due to the contribution of both differential pairs and additional current sources. Adding all noise components it can be shown that the input referred noise of the DDP is:

$$\frac{v_{no}^{2}}{Hz} = 4kT \frac{G_{M1}(1+N_{r2})^{2} \left(\gamma + N_{r1} + 2N_{r1}^{2} \gamma \frac{g_{m3}}{G_{m1}}\right) + G_{M1}(1+N_{r2})^{2} \left(\gamma + N_{r2} + 2N_{r2}^{2} \gamma \frac{g_{m4}}{G_{m2}}\right)}{G_{M1}^{2} (1+N_{r2})^{2} - G_{M2}^{2} (1+N_{r1})^{2}}$$

(2.52)

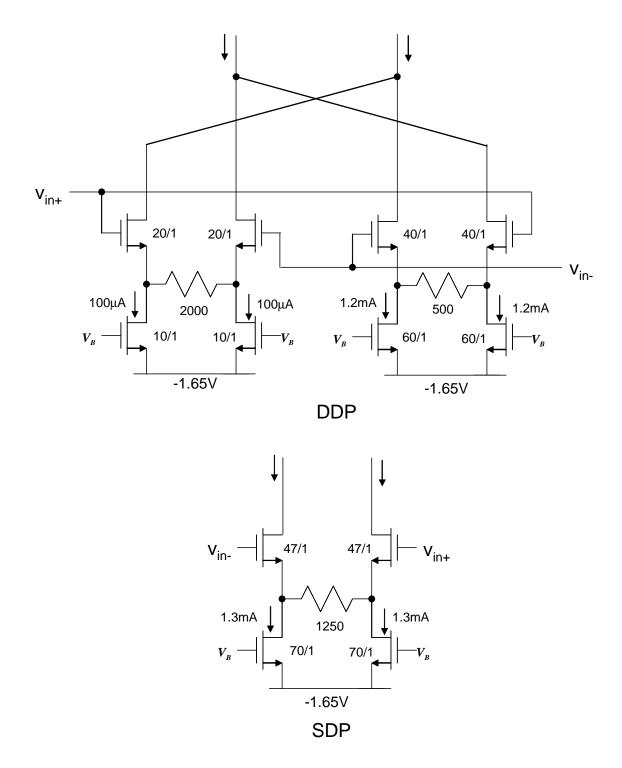

Although the DDP presents reduced harmonic distortion, the transconductance is decreased and noise increases. Then, it is not clear if there is a real improvement in the overall signal to noise ratio compared to the conventional simple differential pair (SDP). To this end, a simulation was performed to give to compare the DDP and the SDP for the same power consumption and the same transconductance (Fig. 2.9). The SDP is designed to use the same Vdsat as the transistors in the DDP but it uses a larger degeneration factor in order to present equal transconductance.

Fig. 2.9. SDP and DDP designs for comparison with same transconductance, Vdsat and power consumption.

Table 2.1 presents the main design parameters for both circuits. The degeneration factor for the SDP is higher by 2.5 times in order to achieve the same transconductance as the SDP. This larger Nr improves the distortion of the SDP but also increases the input referred noise due to the tail current transistors resulting in just a slightly smaller input referred noise density compared to the DDP. The transconductance for both structures is 500µA/V.

| Table 2.1. Results for the comparison between SDP and DDP. |          |          |  |

|------------------------------------------------------------|----------|----------|--|

| Parameter                                                  | SDP      | DDP      |  |

| Degeneration factor                                        | 1.75     | 0.75     |  |

| Vdsat                                                      | 350mV    | 350mV    |  |

| Input referred noise density                               | 6.8nV/Hz | 7.8nV/Hz |  |

| Current consumption                                        | 1.4mA    | 1.4mA    |  |

| Transconductance                                           | 500µA/V  | 500µA/V  |  |

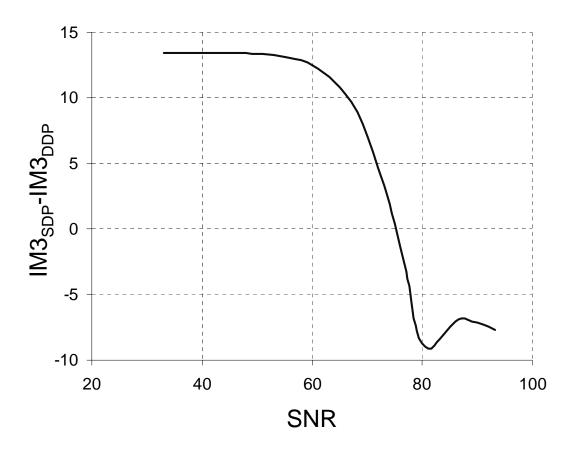

Both structures in fig. 2.9 were simulated for different input amplitudes and the IM3 was measured. Fig 2.10 shows a plot of the linearity improvement of the DDP over the SDP ( $IM3_{SDP}$ - $IM3_{DDP}$ ) for the same SNR. The SNR was calculated for a bandwidth of 10MHz. Up to 60dB of SNR, the DDP achieves more than 10dB of linearity improvement over the SDP. However as the input signal is larger (In this example SNR>60dB), the linearity improvement worsens due to the fifth order non-linearities caused by the smaller V<sub>dsat</sub> differential pair used in the DDP.

Fig. 2.10. Improvement in IM3 of the DDP over the SDP.

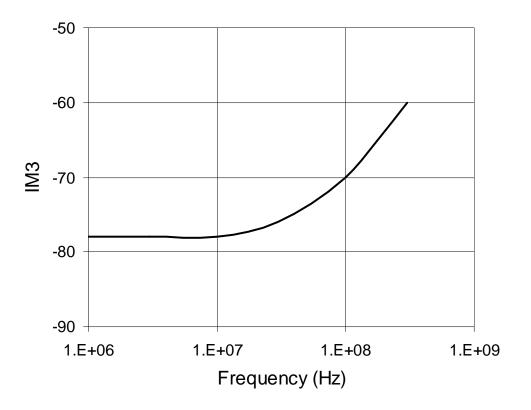

The frequency limits to achieve high linearity are mainly dictated by the decay of degeneration resistance due to effective parasitic capacitances at the source of transistors M1. If Cs is the parasitic capacitance at the source of transistors M1, the frequency limit to hold the linearity is approximately wl=2/(RCs) where R is the degeneration resistor. Figrure 2.11 shows the IM3 plot vs. frequency for the circuit in figure 2.9.

Fig. 2.11 IM3 plot vs. frequency.

# 2.3 A 20 MHz second order low-pass filter

The double differential technique is used in an OTA-C low-pass filter ladder prototype to verify its application. The following subsections describe the OTA and filter design. At the end of this subsection, experimental results are presented.

# 2.3.1 OTA design

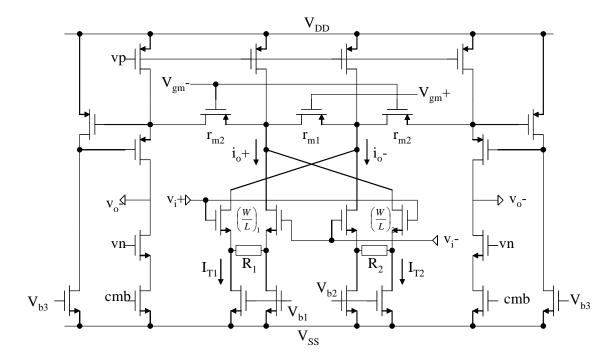

Figure 2.12 shows the overall OTA design. For the input stage, the double differential pair is used in order to achieve the non-linearity cancellation as described in

the previous section. Transistors M1 and M2 use a  $V_{dsat}$  a 280mV and 330mV, respectively, and the degeneration factors are Nr=1.

Fig. 2.12 OTA design.

A transconductance control is incorporated in order to provide frequency tuning for the filter. For that matter, the variation of  $I_{T1}$  and  $I_{T2}$  is not a good option because it modifies  $V_{dsat1}$  and  $V_{dsat2}$  changing the linearity properties and also it affects the optimal linearity cancellation point. To provide independent transconductance control while maintaining a constant linearity, a current division approach is used as described in [26],[29]. Tail currents  $I_{T1}$  and  $I_{T2}$  are fixed and optimized for best linearity, and the transconductance is varied with the aid of triode operating transistors M3 and M4. The output current of the DDP is attenuated by a factor  $\alpha$  which is given by:

$$\alpha = \frac{r_{m3}}{r_{m3} + 2r_{m4}} \tag{2.53}$$

where  $r_{m3}$  and  $r_{m4}$  are the resistance values of the triode region operating transistors M3 and M4, respectively. These resistances are given by:

$$r_{m3} = \left(2K_{m3}(V_{gs3} - V_T)\right)^{-1} \qquad (2.54)$$

$$r_{m4} = \left(2K_{m4}(V_{gs4} - V_T)\right)^{-1} \qquad (2.55)$$

Since the gate voltages of M3 and M4 are controlled by  $V_{gm+}$  and  $V_{gm-}$ ,  $\alpha$  is a function of  $V_{gm+}$  -  $V_{gm-}$ . Equation (2.53) holds provided that the voltage at the source of M6 remains almost constant for any current changes thus it is desired to have a large  $g_{m6}$ . To accomplish this an inverter formed with transistors M9 and M10 provide a negative voltage gain from the source to the gate of M6 boosting its transconductance to A\*gm6; A is the gain of the inverter composed by transistors M9 and M10 which in this case is around 30dB. Transistors M5-M8 form a regulated cascode output stage to enhance the output resistance.

The dimensions of the transistors were chosen using the following considerations: M1 and M2 were dimensioned to achieve 280mV and 330mV with bias currents of 250µA and 330µA which results in the optimal linearity condition. Transistors M3 and M4 are designed using (2.54) and (2.55) to obtain resistances in the order of 500 ohms for optimal noise performance. The current through the transistors cascode transistors M6,M7 and M8 uses the same bias current as It1 and It2 for minimum power consumption yet enough to supply current at maximum output swings. M11 supply 1mA of current and are designed to keep a Vdsat of less than 500mV to

allow the swing at nodes x and y. Table 2.2 shows the final transistor dimensions of the OTA.

| Table 2.2. Transistor sizes for the OTA. Length for all transistors is $1\mu m$ . |            |         |  |  |

|-----------------------------------------------------------------------------------|------------|---------|--|--|

| Transistor                                                                        | Width (µm) | Id (µA) |  |  |

| M1                                                                                | 20         | 250     |  |  |

| M2                                                                                | 40         | 330     |  |  |

| M3                                                                                | 20         | 0       |  |  |

| M4                                                                                | 40         | 0       |  |  |

| M5                                                                                | 80         | 230     |  |  |

| M6                                                                                | 160        | 455     |  |  |

| M7, M8                                                                            | 40         | 450     |  |  |

| M9                                                                                | 60         | 200     |  |  |

| M10                                                                               | 80         | 200     |  |  |

| M11                                                                               | 80         | 1000    |  |  |

The noise at the output of the OTA is a combination of the noise of the OTA core (transistors M1 and M2), the resistor divider (M3 and M4) and the cascode transistors. The approximate output thermal noise density of the OTA is given by:

$$\frac{I_o^2}{Hz} = 8 \gamma kT \left[ g_{m8} + g_{m5} + g_{m11} \alpha^2 + 4 \frac{g_{m9} + g_{m10}}{(g_{m10}r_a)^2} + \frac{2}{\gamma \cdot r_a} + \alpha^2 \left( \frac{(N_{r1}/(2\gamma) + 1)g_{m1} + N_{r1}^2 g_{mT1}}{(1 + N_{r1})^2} + \frac{(N_{r2}/(2\gamma) + 1)g_{m2} + N_{r2}^2 g_{mT2}}{(1 + N_{r2})^2} \right) \right]$$

(2.56)

where  $r_{\alpha}=r_{m3}+2r_{m4}$ . There are several observations in this expressions: the larger  $r_{\alpha}$  the lower the noise but a large increase in these resistances brings the parasitic pole  $w_p=1/(\alpha r_{m4}C_p)$  to lower frequencies limiting OTA's frequency response;  $C_p$  is the overall parasitic capacitance at the nodes x and y. The noise of transistors M9 and M10 is attenuated by the gain  $A=g_{m10}r_a$  which is around 30, therefore its noise contribution is not important.

### 2.3.2 Filter design

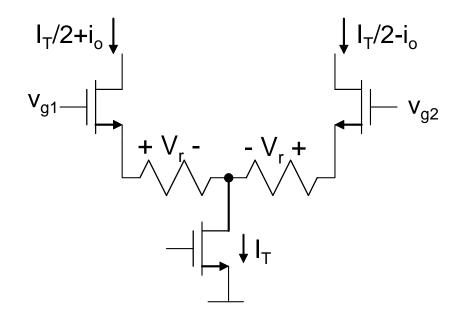

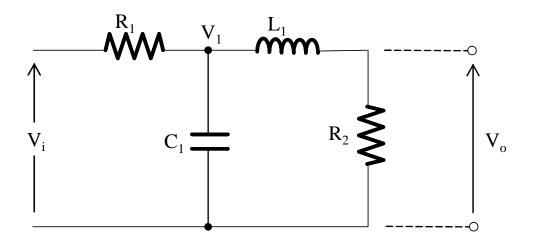

Wire line applications, such as VDSL, contemplate next generation bandwidths up to 20MHz. To test the double differential pair concept, a 20MHz second order lowpass filter is designed. The filter is based on a ladder prototype presented in fig. 2.13.

Fig. 2.13. Second order ladder low-pass prototype.

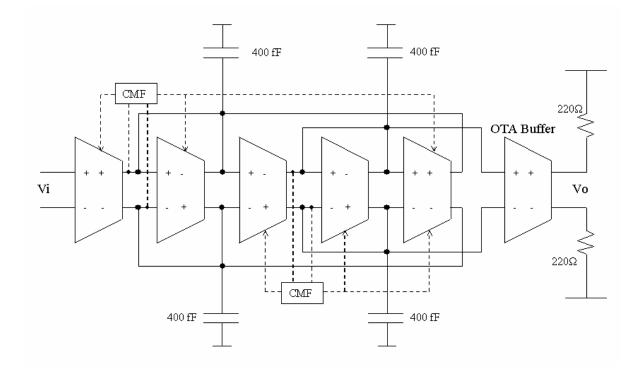

The filter is simulated using five identical OTAs as shown in Figure 2.14. The OTA transconductance can be adjusted between 70 to  $160\mu$ A/V; The capacitor values are 400 fF each. An output buffer based on the same OTA is used to measure the output voltage. Due of the differential nature of the OTAs, common mode feedback (CMF) blocks are used to keep the output stages balanced around the reference voltage.

Fig. 2.14. Low-pass OTA implementation of the ladder filter.

The relation between  $(R_1+R_{\theta 1})$  and  $(R_2+R_{\theta 2})$  in (3.32) can varies from die to die (process variations) because of tolerances in both sheet resistance (used to implement the polysilicon resistance) and mobility degradation factor. An extra test OTA (TOTA) is used to provide information about the linearity as illustrated in fig. 2.15. Based on this, a fine bias external adjustment is possible; since all OTA's used in the filter are the same, the adjustment of the bias condition for maximum linearity in the TOTA optimizes the linearity of the overall filter as well. For testing purposes, the linearity observation of the TOTA is done by applying two tones at the input and measure the IM3 using a spectrum analyzer at the output. For future versions, on-chip precision circuits (such as switched capacitor) are contemplated to implement the linearity adjustment in automatically.

Fig. 2.15. Linearity adjustment using a test OTA (TOTA).

### 2.3.3 Experimental results

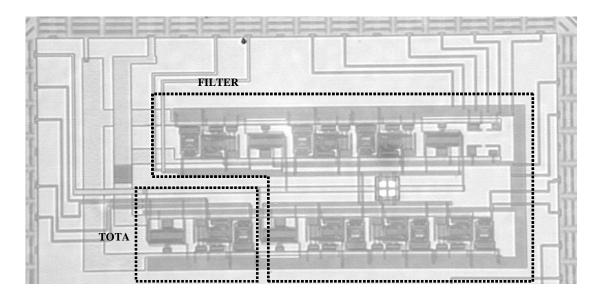

Figure 2.16 shows the micrograph of the chip where the active area is 0.45mm<sup>2</sup>. The chip was fabricated in a standard CMOS 0.35µm process through the MOSIS educational service. In the test set-up, waveform generators are used to provide the input

signals and a balun is used to convert them from single-ended to differential. At the output, 50 ohm resistances are used as load for the OTA buffer and another balun is used to convert the differential output signal into single-ended; the signal is then analyzed using a spectrum analyzer.

Fig. 2.16. Micrograph of the chip.

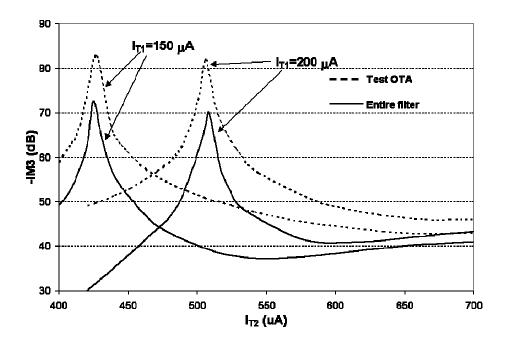

Two sinusoidal tones separated by 100kHz around 20MHz with a total amplitude of 1.3 Vpp were used to test the circuits. Figure 2.17 shows the IM3 of the TOTA and the entire filter as function of the current  $I_{T2}$ ;  $I_{T1}$  has been fixed at 150  $\mu$ A and 200  $\mu$ A, respectively. The tail current at which optimal IM3 is achieved for the TOTA optimizes the linearity of the entire filter as well.

Fig. 2.17. IM3 of the filter and TOTA for several currents IT1 and IT2.

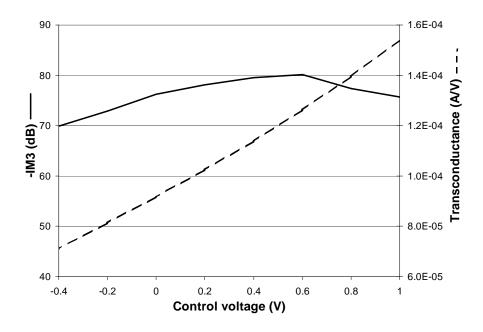

The IM3 measurement of the TOTA is below -70dB for the whole range of frequencies up to 50 MHz. Figure 2.18 shows the effect of the transconductance control on IM3. The transconductance can be controlled from 70  $\mu$ A/V to 160  $\mu$ A/V and IM3 is better than -70 dB. This corroborates that the transconductance control is indeed almost independent of linearity.

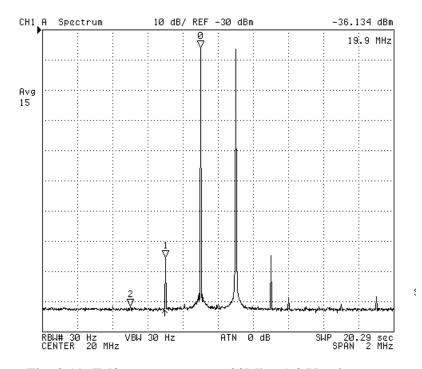

Figure 2.19 shows the IM3 measurement at 20MHz for the filter at 1.3Vpp input. Here, IM3 remains below -65dB over the entire filter's pass-band. The transconductance control allows to change the cut-off frequency from 12 to 24 MHz as shown in figure 2.20. The noise floor that can be appreciated at high frequencies is caused by parasitic capacitances present in the circuit board. Table 2.3 summarizes experimental results of the TOTA and the filter.

Fig. 2.18. Effect of the transconductance control over the IM3.

Fig. 2.19. IM3 measurement at 20Mhz, 1.3 Vpp input.

Fig. 2.20. Programmable frequency responses of the filter.

| Technology.                                                      | CMOS 0.35 µm            |

|------------------------------------------------------------------|-------------------------|

| Supply voltage.<br>OTA                                           | 3.3 V                   |

| Power consumption per OTA.                                       | 10.5 mW                 |

| Transconductance range.<br>OTA IM3<br>up to 50MHz @1.3Vpp input. | 70 – 160 µA/V<br><-70dB |

| Input referred noise                                             | 75 nV/√Hz               |

| SNR @ 20 MHz                                                     | 62 dB                   |

| Filter                                                           |                         |

| Filter's IM3 at 20MHz                                            |                         |

| PSRR+, PSRR-                                                     | >50 dB                  |

| Input referred noise                                             | $6 \mu V / \sqrt{Hz}$   |

| SNR of the filter. (20 Mhz bandwidth)                            | 55 dB                   |

Table 2.3. Summary of experimental results of the filter.

For the purpose of comparing the filter performance with reported schemes, the same figure of merit as defined in (1.2) will be used. Figure 2.21 shows where the described filter stands in reference to others. The proposed scheme, however, has several features that other filters do not:

- Due to the transconductance control incorporated with transistors M3 and M4, there is a nominal loss of half the transconductance because part of the output differential current flows intro transistor M3 rather. However, this feature allows a large continuous tuning range of about ±30% with minimal linearity degradation.

- Thanks to the regulated cascode output stage, the output resistance is considerably large; therefore this OTA can be used for high-Q applications. The drawback, is that the regulated cascode stage consumes 6mW which is 60% of the overall OTA power. Without the regulated cascode stage, the filter would consume half the power at the expense of lower output impedance.

Although the OTA require power consumption and has increased noise to incorporate the above mentioned features, it is still on the trend line in filters thanks to the proposed linearity techniques using the DDP.

Fig. 2.21. Figure of merit of the filter in comparison with the state of the art in filters.

# 2.4 The triple differential pair

# 2.4.1 Analysis

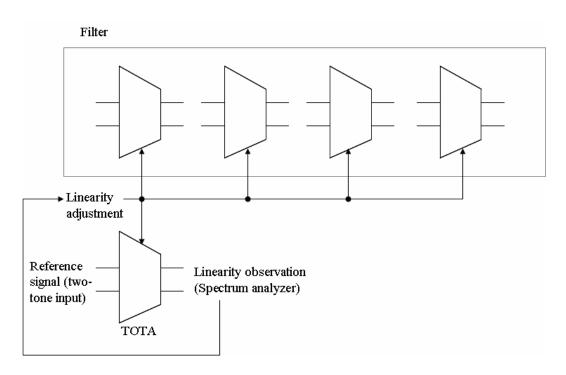

It has been shown that the double differential can be used to reduce OTA nonlinearities but the optimal cancellation is very sensitive to process variations and requires external adjustment. This is due to the fact that the cancellation relies on matching physical parameters such as  $V_{dsat}$ ,  $R_{\theta}$  and  $G_m$  that cannot be accurately controlled or predicted.

The alternative is to use equal DPs with same linear properties but different input voltages. This can be done exploiting the differential nature of the DPs; if one of the inputs of the DP is grounded, the output will be the function of half of the input voltage.

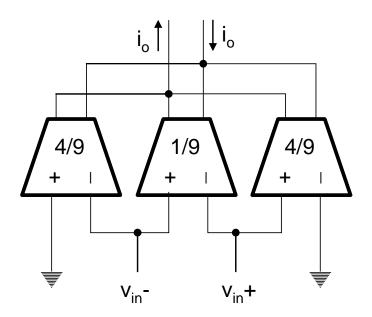

Figure 2.22 shows the block diagram of one degenerated differential pair split in three. The three DPs use the same saturation voltage and equal degeneration factors but different transistor aspect ratios. Two of the DP's (most left and most right) have one of the input terminals connected to ground and, due to the differential nature of DPs, their output current is a function of both differential and common-mode input signal. The overall circuit, however, behaves as a true differential circuit because any common mode input produces differential output current in the DPs with one terminal grounded, but due to the cross-coupled connection they cancel each other. The third DP located at the middle, is connected to both inputs as a conventional DP with tail current and uses the full input signal.

Fig. 2.22. The triple differential pair block diagram.

For the analysis of the topology, it is considered that the input signals are composed by differential and common-mode signal components such as  $v_{in+} = v_{in}/2 + v_{cm}$

and  $v_{in-} = -v_{in}/2 + v_{cm}$  (where  $v_{cm}$  is the common mode input voltage). Using (2.34) the AC single-ended output current of the circuit III is computed as:

$$i_{o} = \frac{G_{m1}}{(1+G_{m1}R)} \left( \frac{4}{9} \left( \frac{v_{in}}{2} + v_{cm} \right) - \frac{4}{9} \left( -\frac{v_{in}}{2} + v_{cm} \right) - \frac{1}{9} v_{in} \right) - \frac{G_{m3}}{(1+G_{m1}R)^{4}} \left( \frac{4}{9} \left( \frac{v_{in}}{2} + v_{cm} \right)^{3} - \frac{4}{9} \left( -\frac{v_{in}}{2} + v_{cm} \right)^{3} - \frac{1}{9} v_{in}^{3} \right) - \frac{G_{m5} + R(G_{M1}G_{M5} - 3G_{M3}^{2})}{(1+G_{m1}R)^{7}} \left( \frac{4}{9} \left( \frac{v_{in}}{2} + v_{cm} \right)^{5} - \frac{4}{9} \left( -\frac{v_{in}}{2} + v_{cm} \right)^{5} - \frac{1}{9} v_{in}^{5} \right)$$

(2.57)

yielding:

$$i_{o} = \frac{1}{3} \frac{G_{m1}}{(1+G_{m1}R)} v_{in} - \frac{4}{3} \frac{G_{m3}}{(1+G_{m1}R)^{4}} v_{in} v_{cm}^{2} - \frac{1}{3} \frac{G_{m5} + R(G_{M1}G_{M5} - 3G_{M3}^{2})}{(1+G_{m1}R)^{7}} \left(\frac{20}{3} v_{in} v_{cm}^{4} + \frac{10}{3} v_{in}^{3} v_{cm}^{2} - \frac{1}{4} v_{in}^{5}\right)$$

(2.58)

Since  $v_{cm}$  is considerably smaller than  $v_{in}$ , (2.58) can be approximated as:

$$\dot{i}_{o} \approx \frac{1}{3} \frac{G_{m1}}{(1+G_{m1}R)} v_{in} + \frac{1}{12} \frac{G_{m5} + R(G_{M1}G_{M5} - 3G_{M3}^{2})}{(1+G_{m1}R)^{7}} v_{in}^{5}$$

(2.59)

Notice that the third order component is effectively cancelled regardless of physical parameters provided that  $v_{cm}$  is very small. Therefore, the non-linearities are caused mainly by the fifth order component where the THD is given by:

$$THD = \frac{5G_{m5}}{48G_{m1}(1+G_{m1}R)^5} v_{amp}^{4} \qquad (2.60)$$

Then the THD improvement over the simple differential pair is:

$$THD_{imp} = \frac{THD_3}{THD_{1,2}} = \frac{5G_{m5}}{12G_{m1}(1+G_{m1}R)^3} v_{amp}^2$$

(2.61)

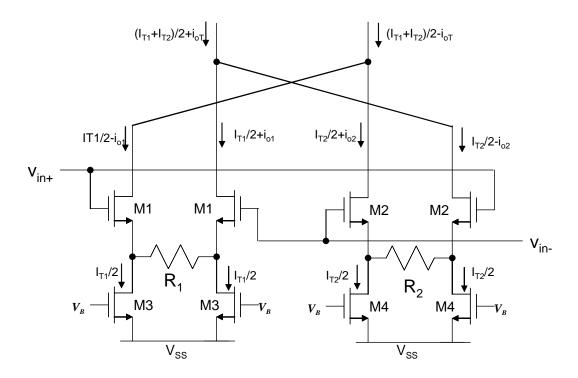

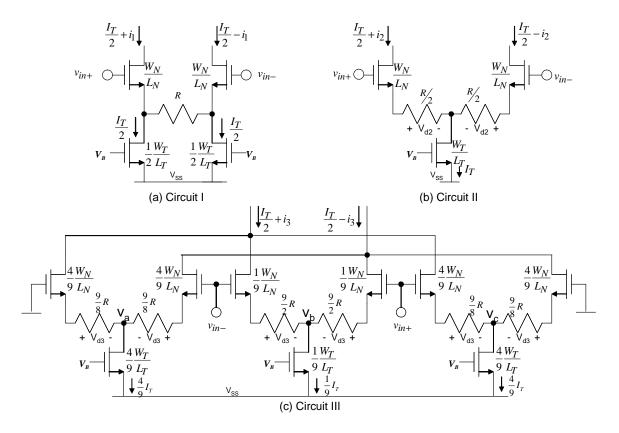

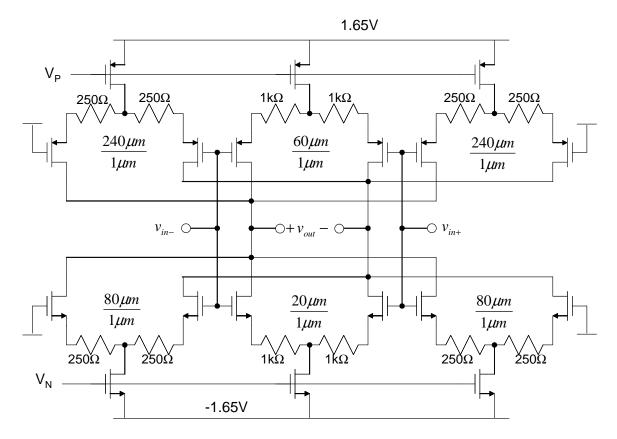

Figure 2.23 shows the circuit implementations of the degenerated DP (Circuit I), the degenerated DP with the tail current at the middle (Circuit II) and the proposed differential triple differential pair (Circuit III). A BSIM simulation was performed on these three circuits. Transistor dimensions are  $W_N/L_N = 180/1$ ,  $V_{dssatN} = 270$ mV,  $W_T/L_T = 720/1$  and  $V_{dssatT} = 200$ mV yielding  $G_{m1}=4.25$ mA/V,  $G_{m3}=3.6$ mA/V<sup>3</sup> and  $G_{m5}=6$ mA/V<sup>5</sup>. The common mode voltage is 1.65V above  $V_{SS}$  and  $v_{amp} = 0.35$ V. Figure 2.24 shows the total harmonic distortion case of circuits I, II and III. On the same graph theoretical results are overlapped, showing a good agreement with the simulated ones.

Fig. 2.23. (a) Degenerated DP, (b) degenerated DP with the tail current in the middle of the resistor and (c) proposed triple DP.

Fig. 2.24. Simulated and theoretical THD for circuits in fig. 2.23.

The advantage of this topology is that very low-distortion figures can be achieved with modest source degeneration factors that result in a small voltage drop across the resistors R; on top of that, the zero generated by R and the parasitic capacitors lumped to transistor's source is located at higher frequencies for smaller resistors. The small signal transconductance is reduced by a factor of three, as shown in (2.59), causing an increase of 9dB in the input referred noise resulting in a degradation of 9 dB in the signal to noise ratio of the topology. It will be shown that even with this drawback, better performances are achieved when compared with circuits I and II.

#### 2.4.2 Advantages of the topology

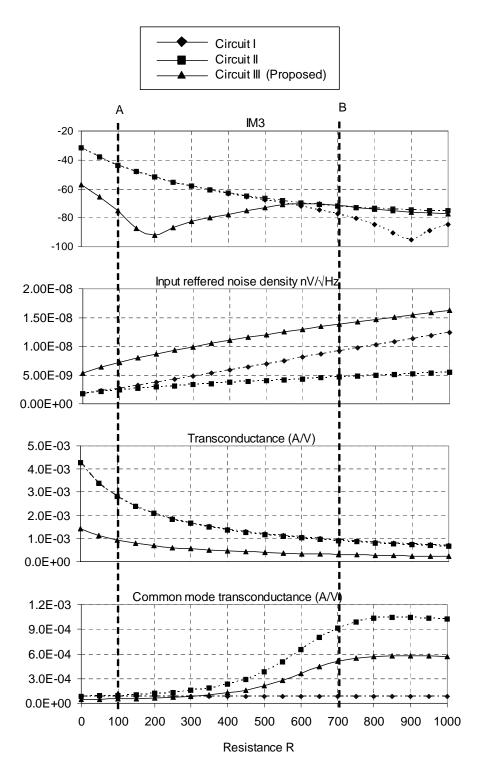

Figure 2.25 shows Cadence simulations comparing the circuits shown in fig. 2.23. The current consumption is fixed to 3mA for all topologies. To characterize OTA's transconductance, the outputs are grounded and differential output current is measured. The parameters considered in fig. 2.25 are transconductance, third intermodulation distortion (IM3), input referred noise, and common mode transconductance. The IM3 is measured using two input tones of 0.35Vpp each one centered at 10MHz and separated by 200KHz. The common mode transconductance is defined as the ratio of the common mode output current and the common mode input voltage. Notice that for the proposed topology, the best linearity is achieved at R=200 $\Omega$ . As R is larger the DC voltage drop across it increases, limiting the signal swing at nodes v<sub>a</sub> and v<sub>c</sub>, the tail currents might go out of saturation region increasing the harmonic distortion components.

In order to compare the topologies, let us consider the design of an OTA with a small signal transconductance of 1 mA/V. The differential transconductance value for circuit III is obtained by using a resistor of R=100 $\Omega$ ; the results for this value are marked on fig. 2.25 by the vertical line A. The IM3 obtained for circuit III is around -75dB, the input referred noise density is 7.5nV/ $\sqrt{Hz}$  and the common mode transconductance is 60µA/V.

Fig. 2.25. Simulations of circuits in fig. 2.23 for different values of R.

For R=100 $\Omega$ , the transconductance of circuit III is three times smaller than the one obtained for circuits I and II; as a result of the transconductance degradation, the signal to noise ratio decreases by around 9 dB. However, circuit III exhibits a superior linearity; notice that for R=100 $\Omega$  (line A), an improvement in IM3 of more than 30dB is achieved; since the main limiting factor in continuous-time filters is the linearity, better balance between signal to noise ratio and signal to distortion ratio can be obtained with the proposed OTA.