# DATA INTEGRITY FOR ON-CHIP INTERCONNECTS

A Dissertation

by

# ROHIT SINGHAL

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2007

Major Subject: Computer Science

# DATA INTEGRITY FOR ON-CHIP INTERCONNECTS

## A Dissertation

by

# ROHIT SINGHAL

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Co-Chairs of Committee, Rabi Mahapatra

Gwan Choi

Committee Members, Duncan M. Walker

Eun Jung Kim

Jiang Hu

Madhav Pappu

Head of Department, Valerie Taylor

May 2007

Major Subject: Computer Science

#### ABSTRACT

Data Integrity for On-Chip Interconnects. (May 2007)

Rohit Singhal, B. Tech., Indian Institute of Technology;

M.S., Texas A&M University

Co-Chairs of Advisory Committee: Dr. Rabi Mahapatra

Dr. Gwan Choi

With shrinking feature size and growing integration density in the Deep Sub-Micron (DSM) technologies, the global buses are fast becoming the "weakest-links" in VLSI design. They have large delays and are error-prone. Especially, in system-on-chip (SoC) designs, where parallel interconnects run over large distances, they pose difficult research and design problems. This work presents an approach for evaluating the data carrying capacity of such wires. The method treats the delay and reliability in interconnects from an information theoretic perspective. The results point to an optimal frequency of operation for a given bus dimension for maximum data transfer rate. Moreover, this optimal frequency is higher than that achieved by present day designs which accommodate the worst case delays.

This work also proposes several novel ways to approach this optimal data transfer rate in practical designs. From the analysis of signal propagation delay in long wires, it is seen that the signal delay distribution has a long tail, meaning that most signals arrive at the output much faster than the worst case delay. Using communication-theory, these "good" signals arriving early can be used to predict/correct the "few" signals that arrive late. In addition to this correction based on prediction, the approaches use coding techniques to eliminate high delay cases to generate a higher

transmission rate.

The work also extends communication theoretic approaches to other areas of VLSI design. Parity groups are generated based on low output delay correlation to add redundancy in combinatorial circuits. This redundancy is used to increase the frequency of operation and/or reduce the energy consumption while improving the overall reliability of the circuit.

To My Parents, Anuja, Richa, Anil, Ravi and Shubha.

## ACKNOWLEDGMENTS

This research work would not have been possible without the support and guidance of my advisors Dr. Gwan Choi and Dr. Rabi Mahapatra. Almost every day, they went out of their way to help me in all aspects of my life and work. There is so much that I've learnt from them and their experiences.

The valuable inputs and advice that I got from my committee members, Dr. Walker, Dr. Kim, Dr. Hu, and Dr. Pappu, throughout the duration of my research is very much appreciated. The students of the computer engineering group were equally helpful to my research effort. In particular I'd like to mention Rupak Samanta, Pankaj Bhagawat, Euncheol Kim, Sanghoan Chang, Kiran Gunnam, and Frank Wang. I really enjoyed working with them.

I would like to thank all my friends who made my stay at Texas A&M very enjoyable. In particular I'd like to thank Waqar, Dali, Veera, Upali, Bhoj, Percy, Gaurav, Pingla, Sudha, Rahul for their constant support and affection. Outside the university, Tiwary, Amina, Michael, and Gullu gave me a lot of pleasant memories.

I'd like to thank my family for giving me unconditional love during the course of this work. My parents, my sister Richa, and brother-in-law Anil were always with me. Ravi and Shubha were like family to me in times of joy and sorrow, never leaving me alone. I can never forget the sacrifices that my lovely wife Anuja made to help make this happen. I couldn't have done this without her. She gave me the strength that I needed to walk, until the last mile ... and more.

And last, but not the least, I'd like to thank Dr. Ben Zoghi. Without his help and guidance, I'd have quit before even hitting the half-way mark!

Thank you all!

# TABLE OF CONTENTS

| CHAPTER | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| I       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1<br>2<br>5                                  |

| II      | B. Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                            |

|         | A. Resistance, Capacitance and Inductance B. The Mathematical Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7<br>8<br>10<br>15                           |

| III     | INFORMATION THEORETIC CAPACITY OF ON-CHIP BUSES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S 19                                         |

|         | A. Channel Capacity of Binary Symmetric Channels  1. Self-Information  2. Entropy  3. Conditional Entropy  4. Capacity of Memory-less BSC Channels  5. Capacity of BSC with Memory  B. Bus Capacity in the Presence of Capacitive Coupling  1. Interconnect States and Capacity  2. The Mathematical Model and Calculations  C. Bus Capacity in the Presence of Capacitive and Inductive Coupling  1. Capacity in the Presence of Capacitive and Inductive Coupling  2. Capacity in the Presence of Capacitive and Inductive Coupling | 19<br>19<br>20<br>20<br>21<br>22<br>27<br>29 |

| IV      | A. Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41<br>45<br>45<br>46<br>50<br>52<br>58       |

| V       | LDPC CODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63                                           |

| CHAPTER  |                                                       | Page |

|----------|-------------------------------------------------------|------|

|          | A. LDPC Decoding Process                              | 65   |

|          | 1. The Variable Node                                  |      |

|          | 2. The Check Node                                     |      |

|          | B. LDPC Decoder Design Issues                         |      |

|          | 1. Routing Complexity                                 |      |

|          | 2. Quantization                                       |      |

|          | a. Performance of LDPC Codes                          |      |

|          | C. Decoder Architecture for On-chip Interconnects     | 72   |

|          | 1. Bubble Sort Algorithm                              | 73   |

|          | 2. The Switching Cell and Computing Nodes             |      |

|          | 3. The Decoder Architecture                           | 76   |

| VI       | OTHER APPLICATIONS OF CODING - COMBINATORIAL CIRCUITS | 79   |

|          | A. Error Correction Coding                            | 84   |

|          | 1. Generating Parity Groups                           |      |

|          | 2. Proposed Architecture                              | 85   |

|          | B. Simulations and Benchmark Results                  |      |

|          | C. Comparison Against Existing Methods                | 97   |

| VII      | CONCLUSION                                            | 99   |

|          | A. Future Work                                        | 101  |

| REFERENC | CES                                                   | 102  |

| VITA     |                                                       | 110  |

# LIST OF TABLES

| TABLE |                                                                         | Page |

|-------|-------------------------------------------------------------------------|------|

| I     | The Interconnect States                                                 | 37   |

| II    | The Code Construction [15] for a 4-Bit Wide Bus                         | 42   |

| III   | The Data Per Wire Rates for Different Codes                             | 43   |

| IV    | Wire Requirement for Various Codes as a Function of Information Width   | 54   |

| V     | An Example 4B5W Code for 3C Elimination                                 | 55   |

| VI    | An Example 4B11W Code for 2C Elimination and Single Error Correction    | 56   |

| VII   | Comparison of Speedups and Overheads of Different Codes for a 4-Bit Bus | 58   |

| VIII  | The ISCAS'85 Circuits                                                   | 86   |

| IX    | The Delay of a NAND Gate for Different Input Combinations               | 87   |

| X     | The Clock Frequencies for Different Error Probabilities                 | 95   |

| XI    | The Prohibited Output Groups Based on Delay Correlations                | 95   |

# LIST OF FIGURES

| FIGUR | E                                                                                             | Page |

|-------|-----------------------------------------------------------------------------------------------|------|

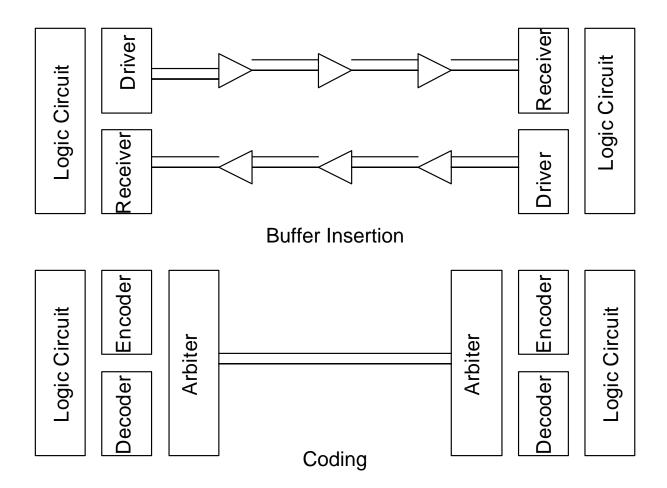

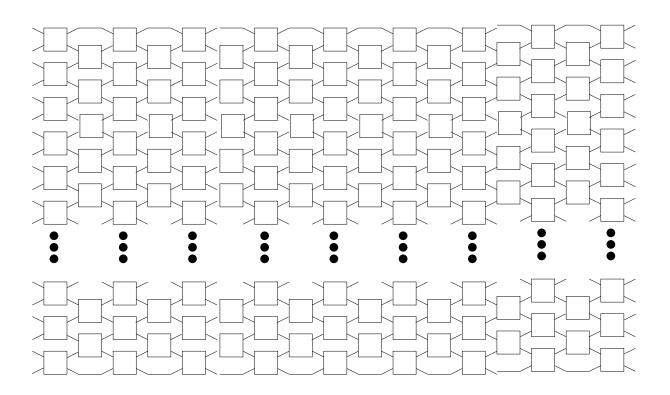

| 1     | Schematics of buffer insertion and coding schemes                                             | 3    |

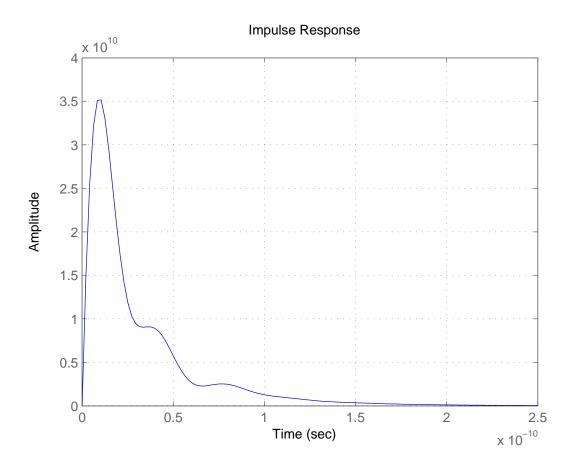

| 2     | The impulse response of a 1 mm long wire in a 8-bit wide bus                                  | 11   |

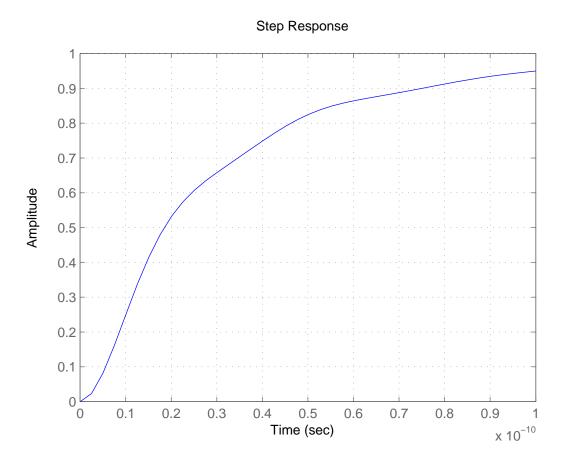

| 3     | The step response of a 1 mm long wire in a 8-bit wide bus                                     | 12   |

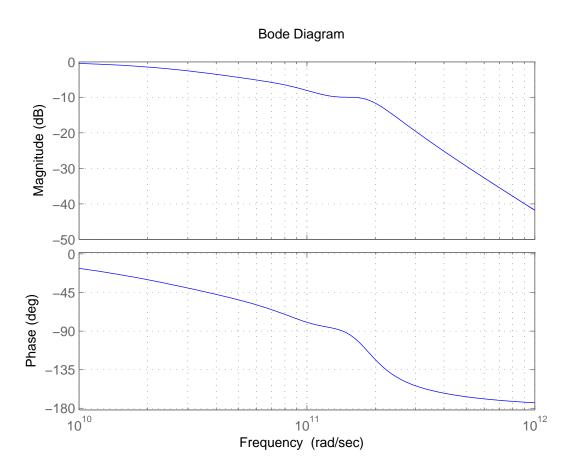

| 4     | The frequency response of a 1 mm long wire in a 8-bit wide bus                                | 13   |

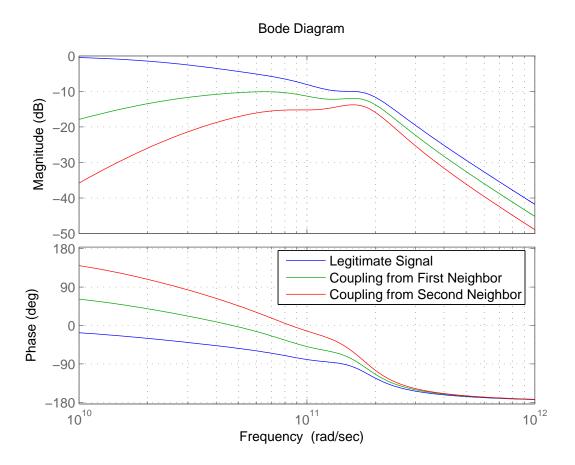

| 5     | The frequency response of a wire's input compared to the coupling response from the neighbors | 14   |

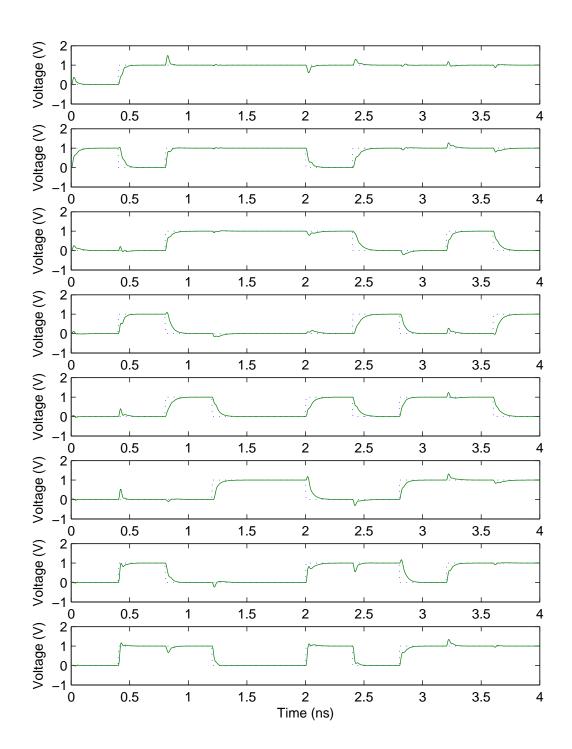

| 6     | The waveform for a 8 bit wide 1 mm long bus                                                   | 16   |

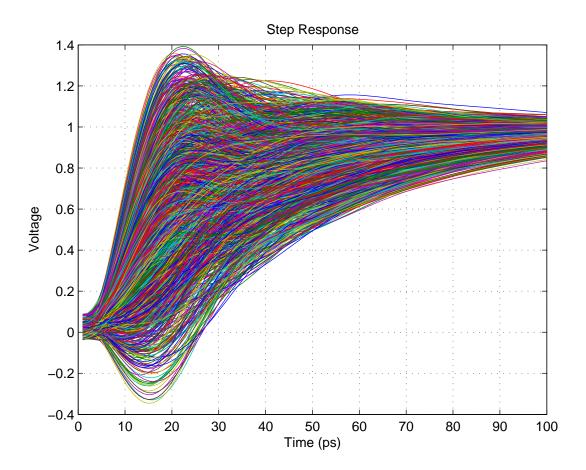

| 7     | The step response of one wire in a 8-bit wide bus when all inputs are active                  | 17   |

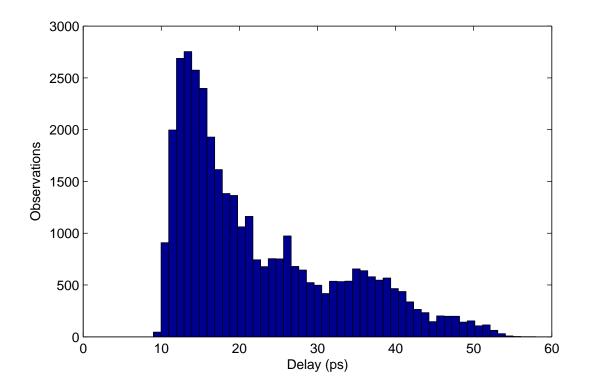

| 8     | The signal delay distribution of an 8-bit wide 1 mm long bus                                  | 18   |

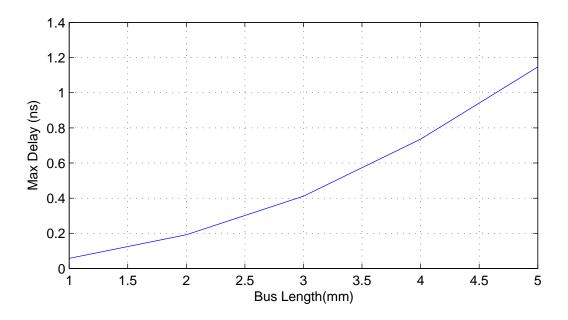

| 9     | The worst case signal delay of an 8-bit wide bus                                              | 18   |

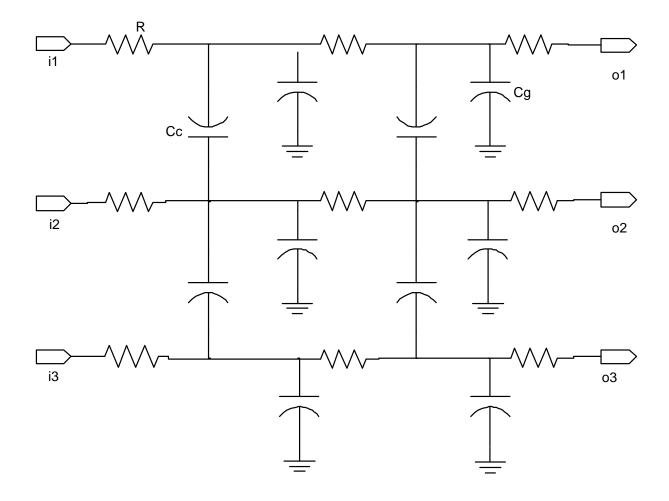

| 10    | The RC model for a bus                                                                        | 23   |

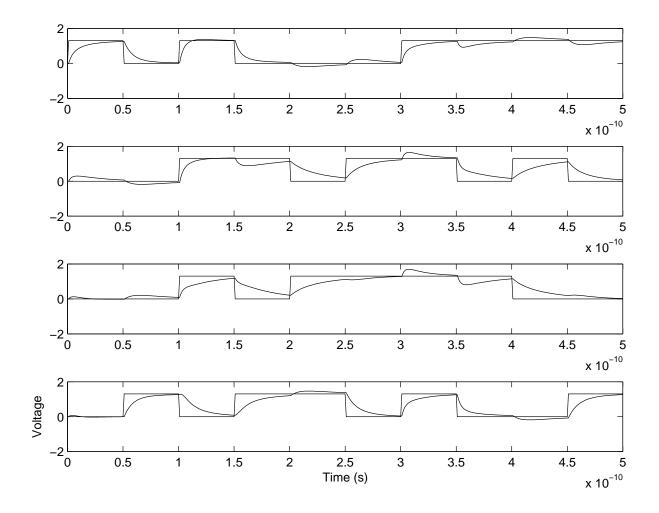

| 11    | The waveform for a 4 bit wide bus                                                             | 24   |

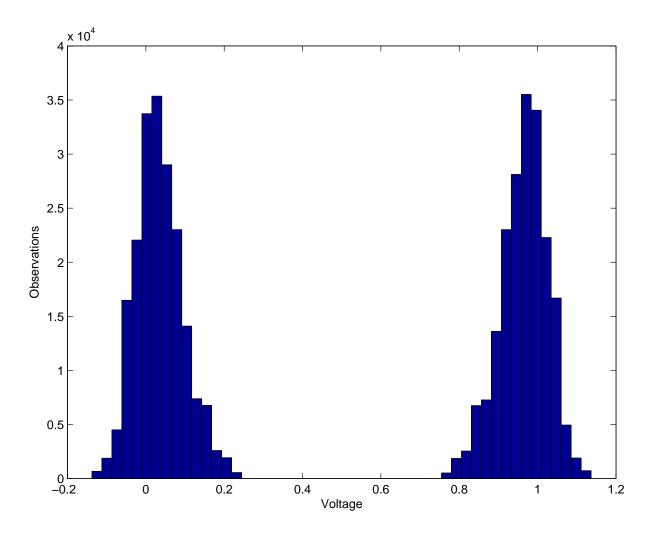

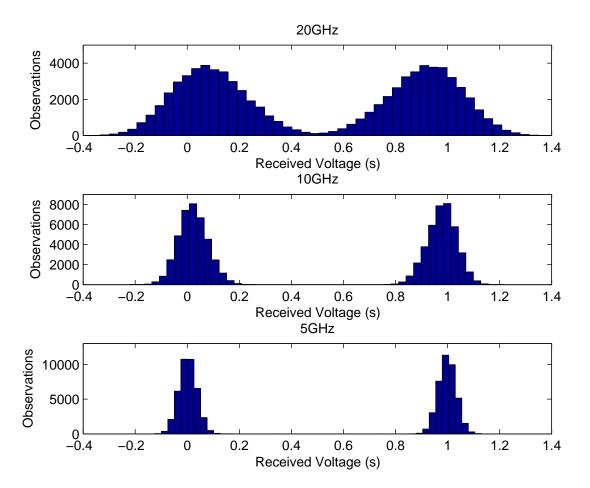

| 12    | Histogram of the output received from a 0.5mm long, 16-bit wide bus running at 10GHz          | 25   |

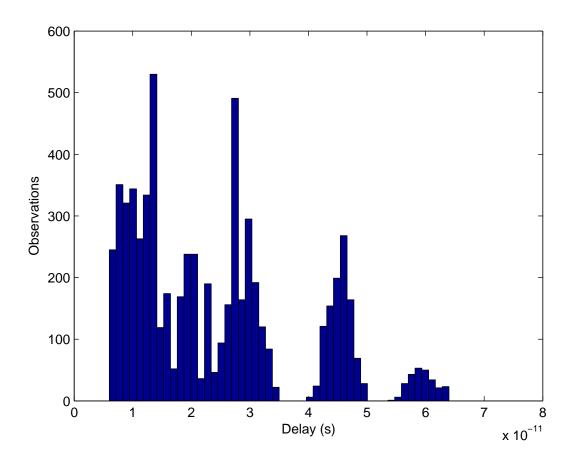

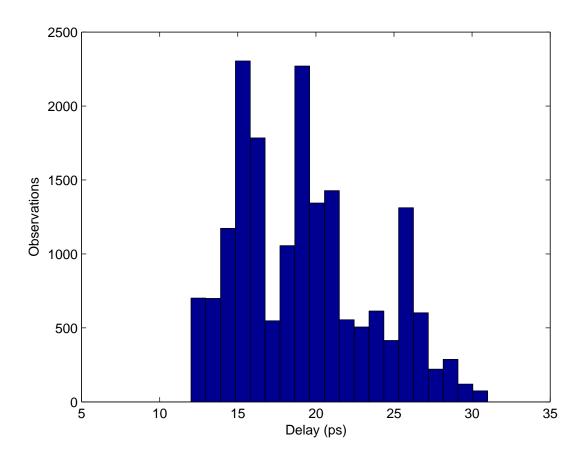

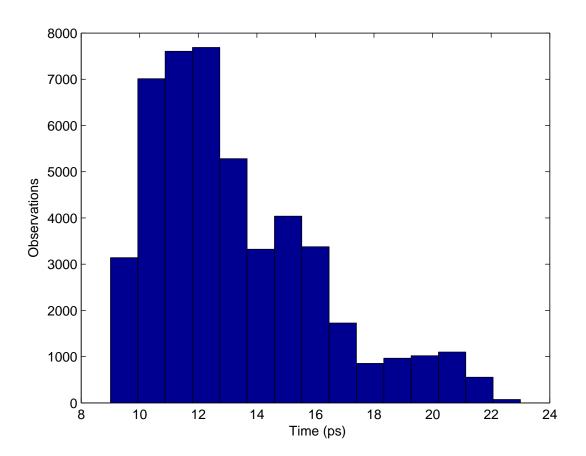

| 13    | Histogram of the signal propagation delay of a 1mm long, 16-bit wide bus                      | 26   |

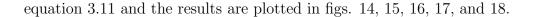

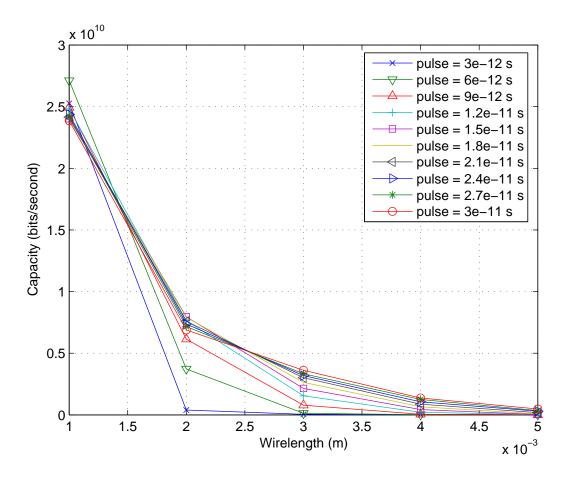

| 14    | The channel capacity as a function of wire length and clock speed                             | 30   |

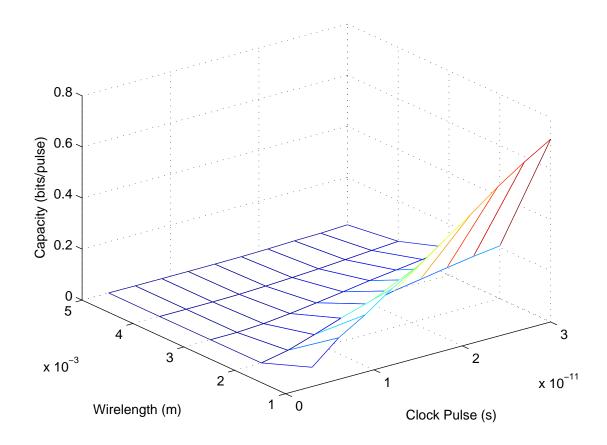

| 15    | The channel capacity in bits per period as a function of wire length                          | 31   |

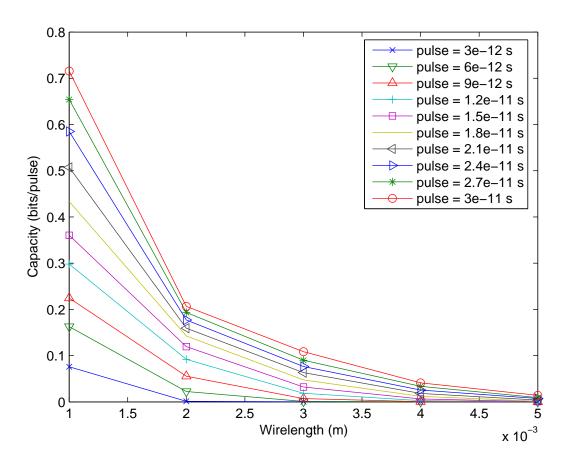

| 16    | The channel capacity in bits per second as a function of wire length.                         | 32   |

| 17    | The channel capacity in bits per period as a function of clock speed.                         | 33   |

| FIGURE |                                                                                                                         | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------|------|

| 18     | The channel capacity in bits per second as a function of clock speed.                                                   | 34   |

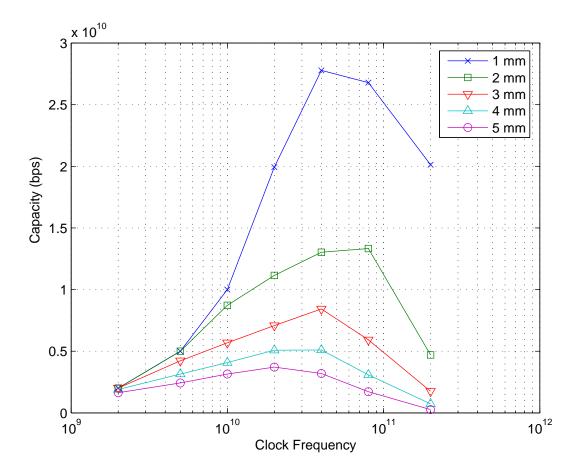

| 19     | The capacity of 8 bit wide bus as a function of clock frequency and length                                              | 38   |

| 20     | The data rate limits of 8-bit wide bus as a function of clock frequency and length                                      | 40   |

| 21     | The comparison of various codes against capacity                                                                        | 44   |

| 22     | The signal delay distribution of a 1 mm long "Shielded" bus                                                             | 48   |

| 23     | The signal delay distribution of a 1 mm long bus with "AND" code                                                        | 49   |

| 24     | The output voltage distribution of an 8 bit wide 1 mm long bus                                                          | 51   |

| 25     | The signal delay distribution of a 1 mm long bus with 4B11B code. $$ .                                                  | 57   |

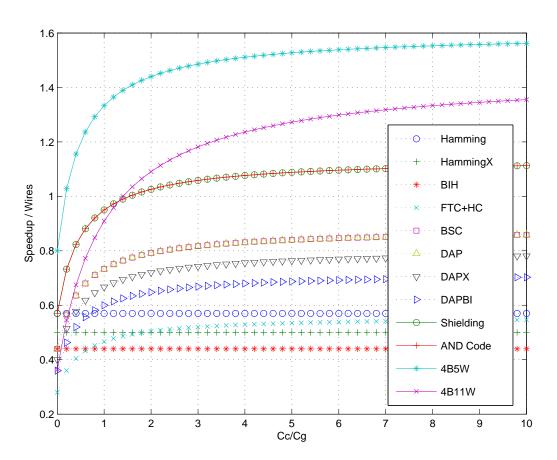

| 26     | The comparison of speedups/overhead of the various codes                                                                | 59   |

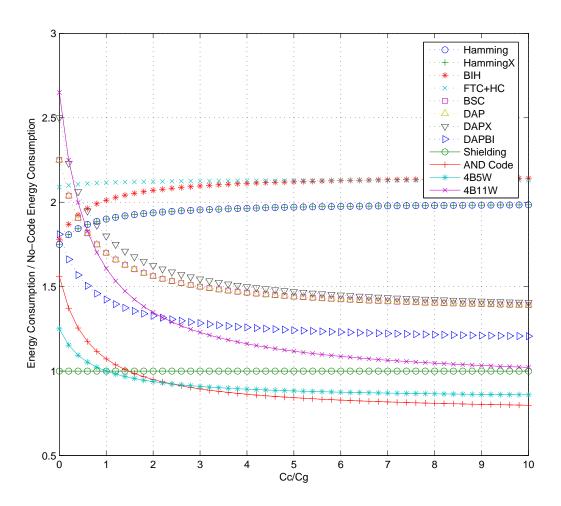

| 27     | The comparison of energy consumption of the various codes                                                               | 60   |

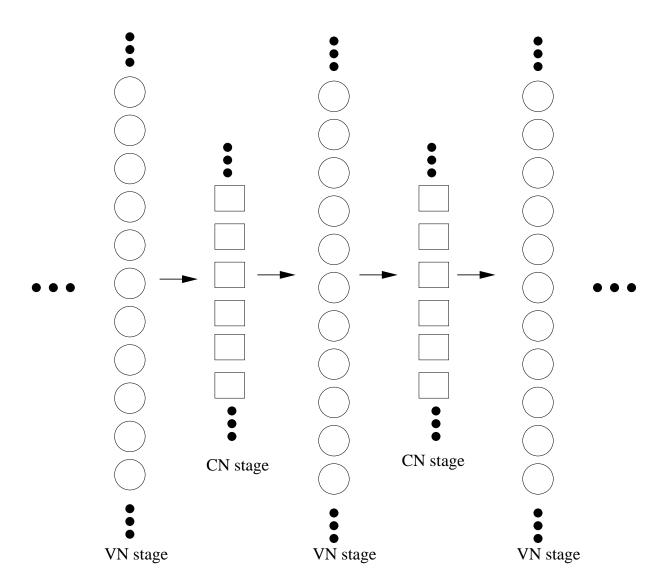

| 28     | Schematic of the LDPC decoder                                                                                           | 64   |

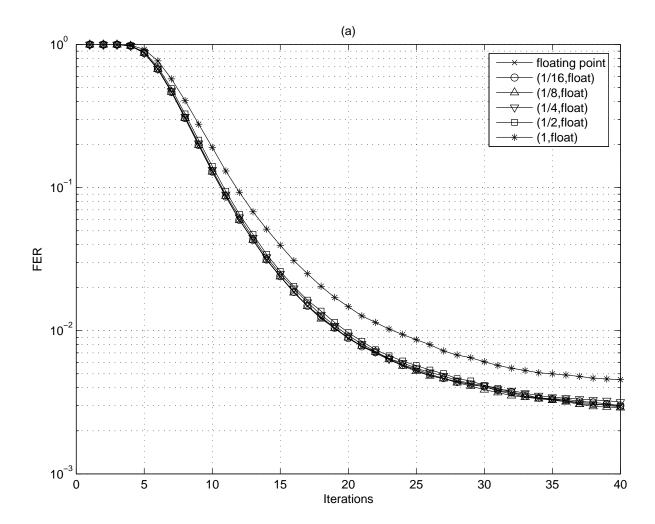

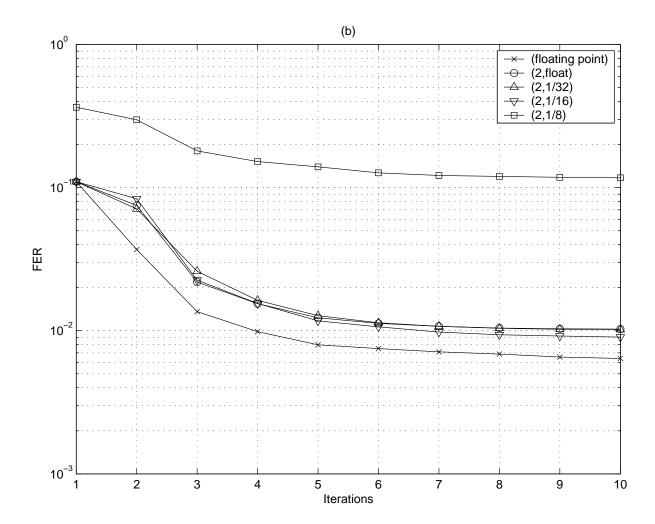

| 29     | The comparison of various implementations of the LDPC decoder with varying $\epsilon_{vn}$ at 2.3dB SNR AWGN channel    | 68   |

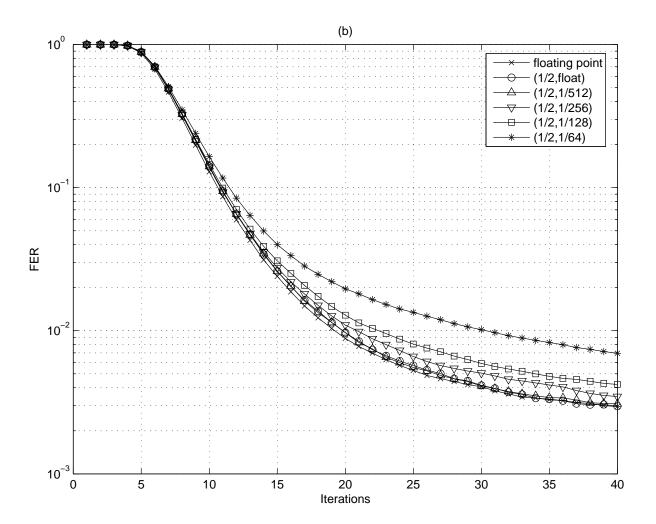

| 30     | The comparison of various implementations of the LDPC decoder with varying $\epsilon_{cn}$ at 2.3dB SNR AWGN channel    | 69   |

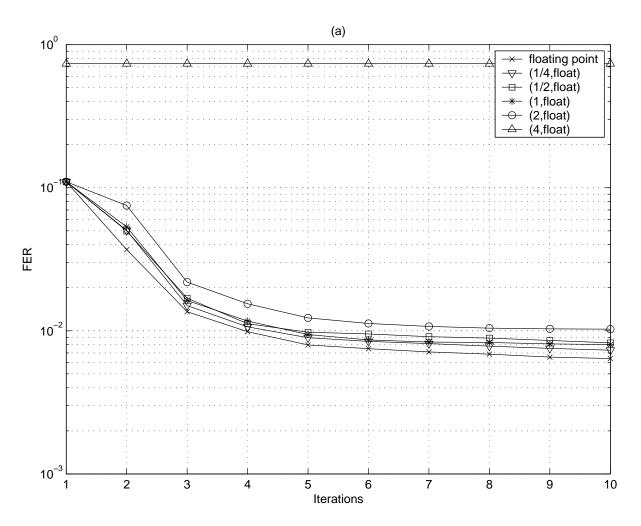

| 31     | The comparison of various implementations of the LDPC decoder with varying $\epsilon_{vn}$ at $10^{-2}$ BER BSC channel | 70   |

| 32     | The comparison of various implementations of the LDPC decoder with varying $\epsilon_{cn}$ at $10^{-2}$ BER BSC channel | 71   |

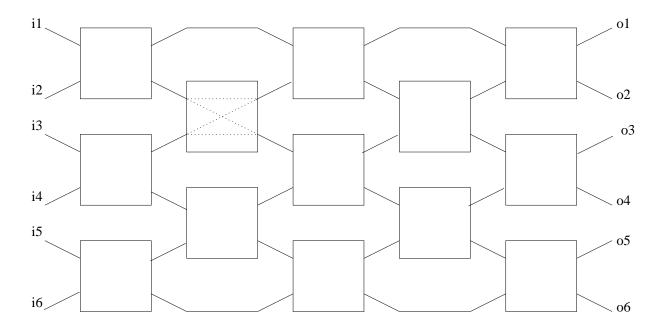

| 33     | A schematic for the Bubble Sort Algorithm                                                                               | 74   |

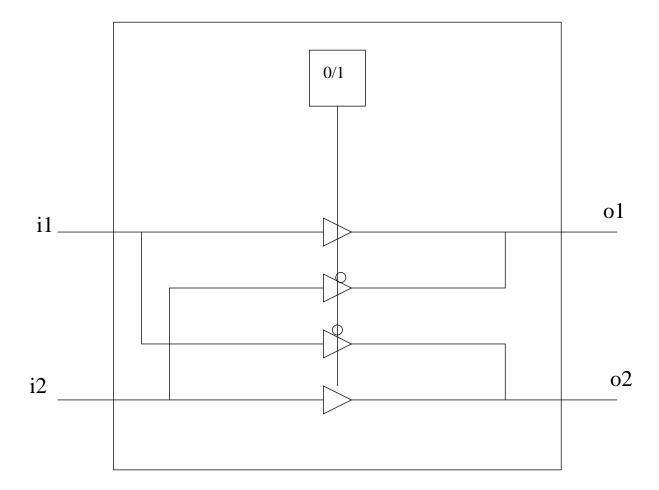

| 34     | The schematic for the switching cell                                                                                    | 75   |

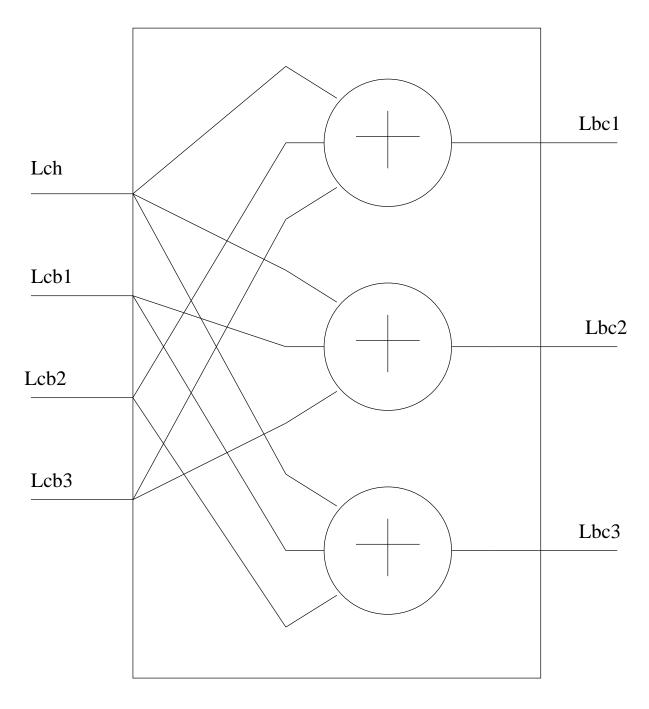

| 35     | The schematic for the VN                                                                                                | 77   |

| FIGURE | $\Xi$                                                                          | Page |

|--------|--------------------------------------------------------------------------------|------|

| 36     | The schematic for a single pipeline stage of the decoder                       | 78   |

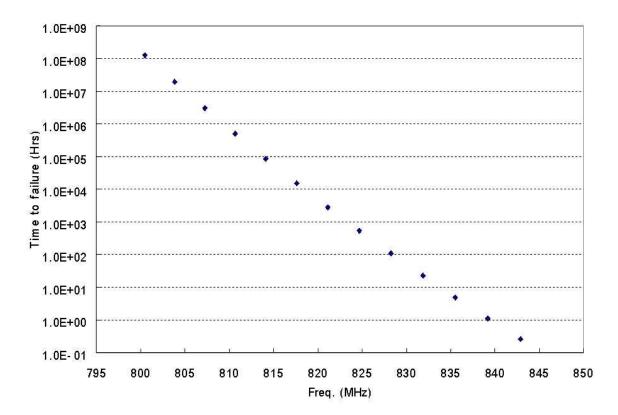

| 37     | TTF v/s clock for a 800 MHz Duron Processor                                    | 82   |

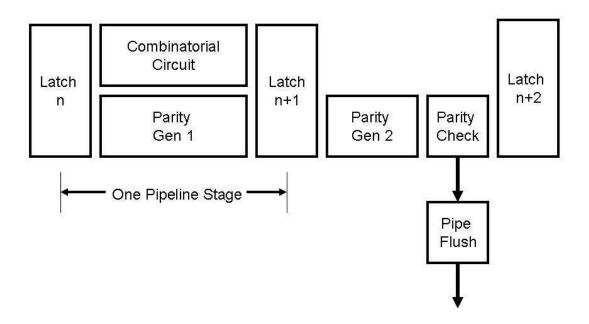

| 38     | The schematic of a error detection system                                      | 85   |

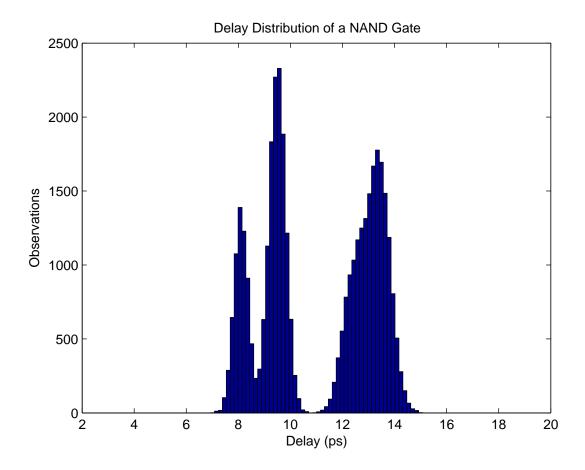

| 39     | Delay distribution of a 2-input NAND gate loaded by another 2-input NAND gate  | 87   |

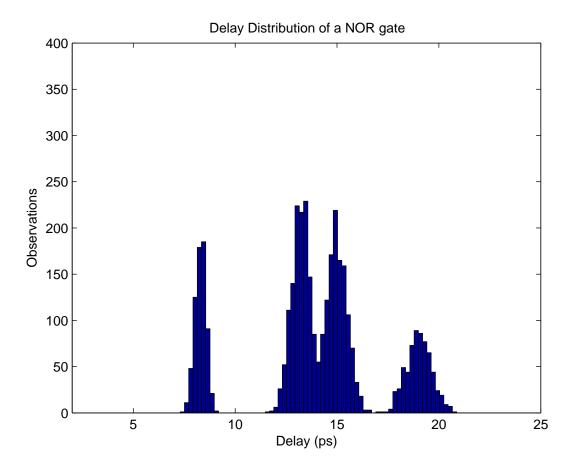

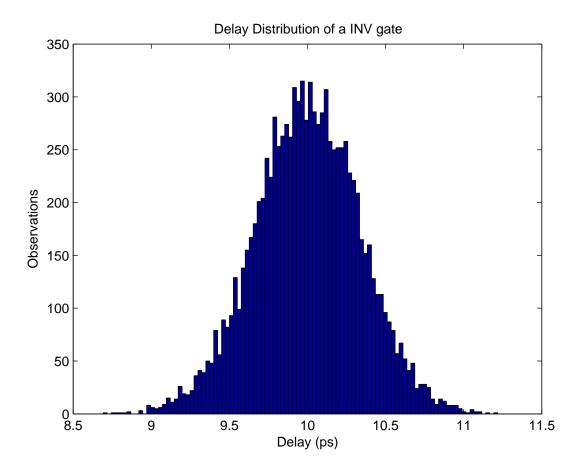

| 40     | Delay distribution of a 2-input NOR gate loaded by another 2-input NOR gate    | 88   |

| 41     | Delay distribution of an inverter loaded by another inverter                   | 89   |

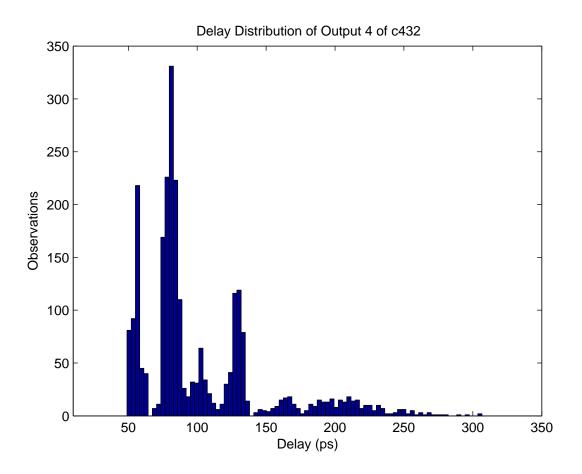

| 42     | Delay distribution of output 4 of c432 circuit                                 | 91   |

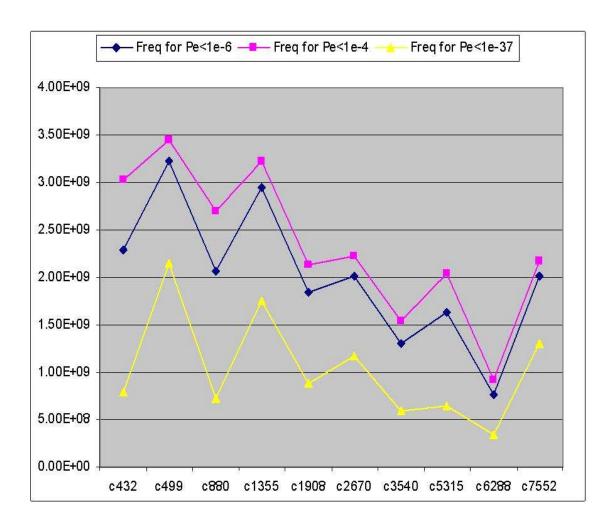

| 43     | The frequencies of operation of the ISCAS'85 circuits                          | 92   |

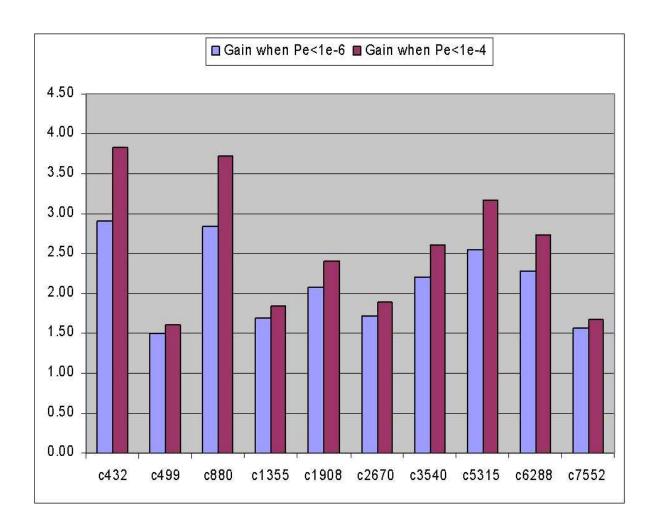

| 44     | The gain in frequency due to error correction coding in the IS-CAS'85 circuits | 94   |

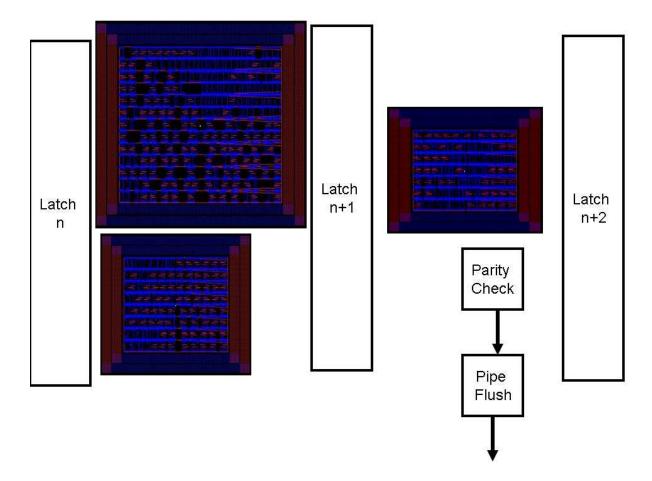

| 45     | A layout for error detection in c499                                           | 96   |

# CHAPTER I

#### INTRODUCTION

Recent advances in the System-on-Chip (SoC) technology have given rise to complex communication systems between different modules on a chip. Even though the problems arising due to the size and magnitude of the logic have been alleviated by Moore's law, the high speed data transfer over long distances poses difficult research problems. Moreover, the emergence of networks-on-chips (NoC) as the communication infrastructure alternative to bus-based communication in SoC has presented the SoC design community with numerous challenges. Designing energy efficient, high performance, reliable on-chip communication systems requires the formulation of strategies to rectify operational glitches.

The long interconnecting wires in such NoC are traditionally modeled as RC networks [1, 2]. More recently, with the high speed of switching, the inductive effects have become increasingly significant [3–6]. The most important problem that has been identified in long interconnects is of Cross-talk, where adjacent signals interfere with each other resulting in not only errors and large delays, but also high energy consumption. In addition to cross-talk, the signal flowing through a wire is also affected by  $Power\ Noise$  and  $Process\ Variations$  [7]. Process variations result in imperfect wire dimensions, while power noise results in imperfect  $V_{dd}$  and  $V_{ss}$  values. Both result in errors at the receiver. Other external noises like thermal noise, electromagnetic noise, slot noise and alpha-particle induced noise also adversely affect the signals.

The major factors that influence the NoC designer's decisions are

This thesis follows the style of IEEE Transactions on VLSI Systems.

- 1. Data and signal reliability

- 2. Signal propagation delays and delay variations.

- 3. Energy consumption

## A. Motivation and Objectives

The design of low power systems has highlighted the contribution of interconnect power, which is upto 50% of total system power [8]. To reduce the interconnect energy consumption, voltage scaling schemes are being used, which in turn reduce the circuit's noise margin. The decrease in noise margin makes the interconnect less immune to errors during transmission. On the other hand, the traditional techniques for noise mitigation and speedup, like buffer insertion [9–11] shown in fig 1 (a), have a very high energy consumption. Other techniques like variable cycle design [12] and wave-piepelining [13] have been explored without significant success. Combining low-power strategies with data reliability in on-chip interconnects has become a daunting task for the designers.

As identified in [14], there are two approaches to address these reliability concerns

1. Noise mitigation, and

#### 2. Tolerance

In [15] it is shown, using simulations, that coding is a better alternative to buffer insertion as it not only reduces wire-delays but also reduces the power consumption for data transmission and improves reliability. Another important advantage of coding over repeater/buffer insertion that is missing in [15], is that buffers usually limit the data-flow in one direction, while coding allows the buses to operate in both directions as shown in fig. 1.

Fig. 1. Schematics of buffer insertion and coding schemes.

A lot of research [15–24], has been done to make use of coding for on-chip interconnects. A coding technique to minimize the inductive crosstalk in *off-chip interconnects* has been presented in [25]. The coding techniques however, improve just one of the factors out of reliability, energy and speed. The problem that remains is to design a coding scheme that accomplishes all three tasks of low energy, low delay and low error rates.

The codes that aim to aggressively achieve speedup [16,17,20], ignore energy and reliability considerations. Some others improve the energy consumption [22–24, 26] while leaving out the other two factors. Still others, just improve the reliability by making use of either error detecting codes (EDC) or error correcting codes (ECC).

VLSI self-checking circuits use error detection codes such as parity, two-rail and other unidirectional EDCs (m-out-of-n and Berger codes) [27]. Since crosstalk is bidirectional [28], these codes would not be sufficient. The authors in [29] make a case for the use of Hamming code [30] on on-chip data buses, highlighting its capability to handle single, double errors, its low complexity and flexibility as a purely detecting code or a purely correcting code.

For on-chip networks, authors in [31] suggest using Hamming code for error detection and in [32] cyclic redundancy check (CRC) [33] is used to detect errors over every hop. Retransmissions are then used to correct the detected errors. When it comes to using ECCs in a design, [29] compares the energy efficiency of forward error correction (FEC) versus error detection and retransmission for on-chip data buses. The reported results indicate that FEC is energy inefficient in described applications.

However, the overhead for FEC is expected to subside in emerging NoCs that span large devices using increasing number of hops and complex buffering/signaling structures. Use of FEC may be cost inefficient when the size of the network is small and the cost of the FEC codecs is high. But as the network size increases and error

rates increase, error detection and retransmission schemes become unacceptable with respect to energy use and latency.

The aim of this research effort is three fold,

- Estimate the data handling limits of long on-chip interconnects and buses.

- Design communication theoretic systems and schemes that achieve this limit on interconnects.

- Extend communication theoretic schemes to improve speed and reliability in other aspects of VLSI design.

#### B. Contributions

Two distinct approaches are employed to calculate the capacity of interconnects. The first approach models a single interconnect as a linear time invariant (LTI) system. This is discussed more in Ch. II. The impulse response, step response and frequency response of this system are studied to determine the optimal data transfer frequency given appropriate pulse shapes for signal transmission.

The second approach makes use of the Shannon's capacity theorem like [34,35], also discussed in Ch. III. The data limits derived here are for the wire component of the bus only. The approaches discussed can be used in conjunction with the existing techniques, i.e., buffer insertion, wire tapering, etc. to provide even better results.

Results for the data limits of a 1 mm long, 8-bit wide bus in  $0.1\mu m$  technology are presented. The worst case delay for this bus configuration from end-to-end is 57 ps. While the traditional design methods, that rely on accommodating the worst case delay, would have resulted in a maximum data transfer rate of 17Gbps (1/57ps), a capacity of about  $\approx 30$ Gbps is established using both techniques.

Codes that achieve this limit even with significant gains in energy consumption and reliability are also presented herein. The example codes "4B5W" and "4B11W" are discussed in Ch. IV. The names 4B5W and 4B11W mean that the 4 bit information is spread on-to 5 and 11 wires respectively to achieve reliability, speedup and energy savings. The codes achieve up-to 2.7x speedup and 14% energy savings over a no-code system. A more elaborate coding scheme, the Low Density Parity Check (LDPC) Code, is discussed in Ch. V. A decoder design is also presented that can be applied to on-chip interconnects.

This work also aims to open up the communication theoretic solutions to other aspects of chip design. Ch. VI discusses the use of coding theory on combinatorial circuits to have upto 4x speedup in the clock frequencies.

# CHAPTER II

#### A LINEAR TIME INVARIANT MODEL FOR A WIDE BUS

In the modern VLSI processes, there are multiple metal layers that can be utilized for laying out the interconnects. According to [7], the dimensions of a global bus in a  $0.1\mu m$  technology are as follows

$$\rho = 2.2 \times 10^{-8} \pm 30\% \text{ Ohm-m};$$

$$d, w = 237 \times 10^{-9} \pm 20\% \text{ m};$$

$$t, h = 498 \times 10^{-9} \pm 15\% \text{ m};$$

(2.1)

where  $\rho$ , w, d, t, h are the resistivity of copper, wire width, separation between two wires, the wire height, and the height of the wire above the substrate respectively.

## A. Resistance, Capacitance and Inductance

Each global wire possesses a resistance R, a capacitance C and an inductance L. These parameters determine the time and energy required to change the signal on the wire from one voltage level to another. The resistance R can be calculated simply by the equation,

$$R = \frac{\rho L}{wt};\tag{2.2}$$

where L is the length of the interconnect.

The capacitance C in a long wire is two-fold. There is a wire-to-substrate capacitance  $C_g$ , and then there is an inter-wire capacitance called the coupling capacitance  $C_c$ . Traditionally, the  $C_c$  has been negligible compared to the  $C_g$ , but as the fabrication technologies advance into deep sub-micron (DSM) region, the inter-wire capacitance  $C_c$ , not only becomes significant, it becomes dominant compared to the

wire-to-substrate capacitance  $C_g$ .

$$C = C_g + C_c;$$

$$C_g = \frac{\epsilon L w}{h};$$

$$C_c = \frac{2\epsilon L t}{d}.$$

(2.3)

where  $\epsilon$  is the permittivity of the oxide between wires.

As more advances are made into the DSM region, and as the speed of signaling approaches multi-GigaHertz, the inductive effects become increasingly significant [3–6]. Each interconnecting wire has a Self-Inductance  $L_s$  and a Mutual-Inductance  $L_m$ , with its neighbors given by

$$L_s = 2 \times 10^{-7} L \left( 0.5 + \log \left( \frac{2L}{w+t} \right) + 0.11 \frac{w+t}{L} \right),$$

(2.4)

$$L_m = 2 \times 10^{-7} L \left( \log \left( \frac{d+w}{d} \right) \right). \tag{2.5}$$

All the equations above assume that the wires are of constant width, height and thickness throughout their length. This assumption is reasonable in light of the fact that the wires being considered are expected to carry bidirectional data. Techniques like wire-tapering etc. will result in uneven characteristics in the two directions.

## B. The Mathematical Model

The small section of an n-bit wide bus can be described as a multi-input-multi-output (MIMO) linear time invariant (LTI) system [16,34,35]. The term MIMO comes from the fact that each wire has a separate driver (input) and a distinct receiver (output). The transfer function of this MIMO system can be described in Laplace domain as

an  $n \times n$  matrix F(s) given as

$$F(s) = (I + L(s)C(s))^{-1}, (2.6)$$

where, the size of I, L(s) and C(s) is also  $n \times n$ . L(s) defines the inductance and resistance while C(s) defines the capacitance of the wires as follows,

$$L(s) = \begin{bmatrix} A & B & 0 & \dots & 0 & 0 \\ D & A & B & \dots & 0 & 0 \\ 0 & D & A & \dots & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \dots & A & B \\ 0 & 0 & 0 & \dots & D & A \end{bmatrix},$$

$$A = R + sL_s,$$

$$(2.7)$$

$$A = R + sL_s, (2.8)$$

$$B = sL_m, (2.9)$$

$$D = -sL_m. (2.10)$$

$$C(s) = \begin{bmatrix} Y & Z & 0 & \dots & 0 & 0 \\ Z & X & Z & \dots & 0 & 0 \\ 0 & Z & X & \dots & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \dots & X & Z \\ 0 & 0 & 0 & \dots & Z & Y \end{bmatrix}, \tag{2.11}$$

$$X = s(2C_c + C_g), (2.12)$$

$$Y = s(C_g + C_c), (2.13)$$

$$Z = -sC_c. (2.14)$$

# Impulse, Step and Frequency Response

In order to study the input response of a wire, based on the transfer function F(s) described above, the input of a single wire is excited, while the inputs of the other wires are kept constant. The characteristics that are studied include an impluse response, a step response and a frequency response shown in figs. 2, 3 and 4 respectively.

- The *Impulse Response* in fig. 2 describes the voltage at the receiver of a single wire when the input of that wire rises sharply to infinity and falls back to zero. It is seen that an emf of  $3.5 \times 10^{10}$  V develops at the output. This is enough to burn the chip, therefore it is recommended that the signals transmitted on the wires should not contain sharp edges. In practical systems, it is usually impossible to generate these sharp edges, due to the limitations in the driver capacities.

- The Step Response in fig. 3 describes the voltage at the receiver of a single wire when the input of that wire rises sharply to voltage level 1. It is seen that it takes

Fig. 2. The impulse response of a 1 mm long wire in a 8-bit wide bus.

the wire at least 18ps to crossover the half voltage point when transiting from one level to another, even without any disturbances from neighboring wires.

Fig. 3. The step response of a 1 mm long wire in a 8-bit wide bus.

• The Frequency Response in fig. 4 describes the voltage at the receiver of a single wire when the input of that wire is a sine wave of a variety of frequencies. The plot measures the ratio of the magnitude of the voltages, and the phase differences at the input to the output at different frequencies. The frequency response plot suggests that the wire acts as a Low Pass Filter (LPF) with less

Fig. 4. The frequency response of a 1 mm long wire in a 8-bit wide bus.

than  $10 dB^1$  attenuation at frequencies below  $2 \times 10^{11}$  radian per second, or  $\approx 30$  GHz.

Fig. 5. The frequency response of a wire's input compared to the coupling response from the neighbors.

Fig. 5 shows the frequency dependence of the output of a particular wire to the input in the same wire as well as the first and second neighbors. A single wire acts as a low pass filter with a cut-off of about  $\approx 30$  GHz, as seen in both figs. 4 and 5. The coupling is negligible at low frequencies, and also at very high frequencies. However,

<sup>&</sup>lt;sup>1</sup>The 10dB cut-off is a reasonable value, as opposed to the 3dB mark usually used in communication theory, because the threshold voltage  $V_{th}$  and the noise margins in modern technologies are both about 10dB lower than the  $V_{dd}$  values.

the coupling interference is significant compared to the reference signal above  $2 \times 10^{11}$  radian per second. In this light, the ideal transmission frequency should be  $\approx 30$  GHz.

In addition to the input of the wire under study, when all other inputs are excited with a randomly generated data set, the output waveforms are illustrated in fig. 6. The input pulses are shaped as square waves as is customary in current technologies. It is seen that the output of a wire is not only affected by the input on that wire, but the signals on the neighboring wires as well. Some interferences are constructive while others are destructive. Also seen in fig. 6 are temporary glitches at the output, even when the input of the wire is not switching. This happens due to *coupling* with the adjacent wires. This phenomenon is better known as cross-talk.

For the same set-up, fig. 7 shows the receiver voltage corresponding to an input switching from a 0 to 1, when the neighboring signals switch arbitrarily. Note the large variations in this step response compared to fig. 3. These variations are due to cross-talk. Some interference speed-up the signal, while others slow it down. Certain bad patterns not only slow the signal, but also result in a high power consumption.

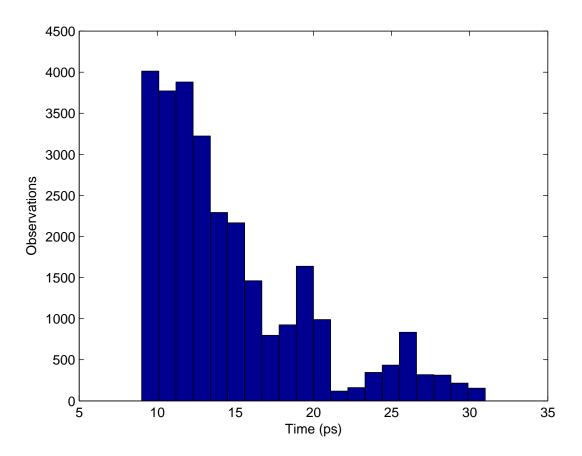

## D. Delay Distribution

The variation in the step response of fig. 7 can be seen as a propagation delay variation as shown in fig. 8. Propagation delay is defined as the time taken for a signal to reach the half-way point of the desired value. In other words, it is the time required before the receiver can make a decision whether the transmitted signal is a 0 or a 1. The long tail of the distribution is clearly visible. This means that even without any data preprocessing, most signals arrive much faster than the worst case. Fig. 9 plots the worst case delays for different bus lengths. It is seen that the worst case delay increases as the square of length.

Fig. 6. The waveform for a 8 bit wide 1 mm long bus

Fig. 7. The step response of one wire in a 8-bit wide bus when all inputs are active.

Fig. 8. The signal delay distribution of an 8-bit wide 1 mm long bus.

Fig. 9. The worst case signal delay of an 8-bit wide bus

# CHAPTER III

## INFORMATION THEORETIC CAPACITY OF ON-CHIP BUSES

## A. Channel Capacity of Binary Symmetric Channels

A Binary Symmetric Channel (BSC) is a communication medium, the inputs to which are from the binary set  $\{0,1\}$  at the transmitter. The channel transmits this signal from the transmitter to a geograhically separated receiver. During this transmission of signals, errors happen resulting in flipping of some bits from 0 to 1 and 1 to 0. Let the probability with which this happens be  $p_e$ . So, if a 0 was transmitted, it will be received as a 0 or a 1 with probability  $1 - p_e$  and  $p_e$  respectively.

Before proceeding to the definition of a BSC channel capacity, consider the following definitions.

## 1. Self-Information

For any random event E, which occurs with a probability p(E), the self-information  $I(E) = -\log_2 p(E)$  defines the information conveyed in bits by the occurrence of that event. For example, the information conveyed by the occurrence of heads in an unbiased coin is  $\log_2 1/2 = 1$  bit. In the BSC context, where the bits 1 and 0 occur with probabilities  $p_1$  and  $p_0 = 1 - p_1$  respectively, the information conveyed by the occurrence of 1 or 0 is defined as,

$$I(1) = -\log_2 p_1 \tag{3.1}$$

$$I(0) = -\log_2 p_0 = -\log_2(1 - p_1) \tag{3.2}$$

Now, if  $p_1 = p_0 = 1/2$ , the self-information  $I(1) = I(0) = -\log_2(1/2) = 1$  bit. This means that whenever a 1 or a 0 occurs in a equiprobable distribution, 1 bit of information is conveyed by their occurrence.

# 2. Entropy

The entropy H(s) of the system S of n random events  $E_1, E_2, \ldots, E_n$ , with probabilities of occurrence  $p_1, p_2, \ldots, p_n$  is the measure of the system's uncertainty and is given as

$$H(S) = \sum_{k=1}^{n} p_k I(E_k).$$

(3.3)

The uncertainty in a system consisting of an unbiased coin with heads and tails as the events is 1 bit. The uncertainty in a system with a six faced dice is 2.58 bits. Again, in the BSC context, where the system S has only two possible outcomes 0 and 1,

$$H(S) = p_0 I(0) + p_1 I(1),$$

$$H(S) = -p_0 \log_2 p_0 - p_1 \log_2 p_1.$$

(3.4)

Now, if  $p_0 = p_1 = 1/2$ , H(S) = 1 meaning that there is an uncertainty of 1 bit in the system. Also, if  $p_0 = 0$ ,  $p_1 = 1$ , H(S) = 0 meaning that there is no uncertainty in the system, because obviously the outcome will always be 1.

## 3. Conditional Entropy

The conditional entropy of the system  $S_1$  given the outcome of another random system  $S_2$ , is defined as

$$H(S_1|S_2) = -\sum_{j=1}^{n} \sum_{k=1}^{m} p_{jk} \log_2 p_{jk} / p_k$$

(3.5)

where  $p_{jk} = p(E_j \cap F_k)$ , and  $p_k = p(F_k)$ . n and m are the number of possible outcomes E and F of system  $S_1$  and  $S_2$  respectively. In simple words, conditional entropy is the uncertainty remaining in system  $S_1$  given the outcome of  $S_2$ . If system  $S_1$  is

defined as a system with two coins, and system  $S_2$  is defined as one of the coins, then before any coin toss, the uncertainty in the system  $S_1$  is  $H(S_1) = 2$  bits. Once the outcome of the system  $S_2$  is known, the remaining uncertainty in the system  $S_1$  is  $H(S_1|S_2) = 1$  bit.

## 4. Capacity of Memory-less BSC Channels

For a communication channel, let the input and output be two different random systems  $S_1$  and  $S_2$  respectively. The capacity is defined as the reduction in uncertainty about the input given the channel output [36].

$$C = H(S_1) - H(S_1|S_2) (3.6)$$

For a BSC  $H(S_1) = 1$  when  $p_0 = p_1 = 1/2$

$$C = 1 - H(S_1|S_2) (3.7)$$

$$C = 1 + \sum_{j=1}^{2} \sum_{k=1}^{2} p_{jk} \log_2 p_{jk} / p_k$$

(3.8)

$$C = 1 + p_e \log_2(p_e) + (1 - p_e) \log_2(1 - p_e)$$

(3.9)

where,  $p_e$  is the bit-error-rate (BER) of the channel.

The units of capacity can be either bits per second or bits per transmitted symbol. The latter is a more popular notation and will be used in this work (like above), unless otherwise stated.

Another interpretation of capacity is the maximum rate of the code that is required to produce a *zero* probability of error. The rate of a code is the ratio of the total useful information bits to the total transmitted symbols. As an example, if a code takes 7 bits and converts them into a code of 10 bits, the rate is 0.7. Not all codes at this maximum code rate will exhibit a low probability of error, but theoret-

ically, it is possible to construct at least one error correction code that can achieve this.

# 5. Capacity of BSC with Memory

The bit error rate in some channels is altered significantly, based on the past transmissions. Such channels, called the "Gilbert-Elliot Channels" [37] seem to have a multiple set of operating conditions or states. Consider a channel with n states  $A_1, A_2, \ldots, A_n$ , with each state having a bit-error-rate  $p_{ei}$  and a probability of the occurrence  $p_i$ . The capacity of each state  $C_i = 1 + p_{ei} \log_2(p_{ei}) + (1 - p_{ei}) \log_2(1 - p_{ei})$  and the overall [37] channel capacity is

$$C = \sum_{i=1}^{n} p_i C_i. (3.10)$$

## B. Bus Capacity in the Presence of Capacitive Coupling

In order to better understand the calculation of the capacity of a wide on-chip bus, lets take a step back and assume that there are no inductive effects on the wires. The wires are modeled as low-pass RC circuits [1,2,16,19,22], with each wire having wire-to-substrate capacitance  $C_g$  and inter-wire capacitance  $C_c$  as shown in fig. 10.

Fig. 11 shows the signal waveforms in a 0.5 mm long, 4 bit wide bus in a 0.1  $\mu$ m fabrication process. The effect of crosstalk is seen when the inputs are switching. For example, when the adjacent signals are switching in the same direction, the crosstalk results in a speeding up of the output signal. On the other hand, when the adjacent signals are switching in the opposite direction, crosstalk results in the undesirable slow-down of the output signal. This may lead to increased errors in detection. Fig. 12 shows the histogram of the output received on the same crosstalk infested bus. The nature of errors is symmetric on both electrical levels. Due to this symmetric

Fig. 10. The RC model for a bus

Fig. 11. The waveform for a 4 bit wide bus

Fig. 12. Histogram of the output received from a 0.5mm long, 16-bit wide bus running at  $10\mathrm{GHz}$ .

Fig. 13. Histogram of the signal propagation delay of a 1mm long, 16-bit wide bus.

nature of the output distribution, the crossover probabilities and hence the number of errors are minimum if  $V_{swing} = 2 \times V_{trip}$ , i.e., the swing voltage in the bus is twice of the receiver's decision making switching voltage. Fig. 13 shows the delay distribution of a 16-bit wide, 1 mm long bus. The signal propagation delay is defined as time required to charge the output voltage level to 50% of the steady-state value. Note the difference compared with the delay histogram in fig. 8 where inductive effects were also present.

#### 1. Interconnect States and Capacity

Based on this understanding of the interconnects, the operating conditions can be broadly classified into the following states [19] that differ from each other primarily in terms of the capacitance that the input signal experiences.

- 1. State  $A_1$  ( $\mathbf{0C_c} + \mathbf{C_g}$ ) occurs when the input and both neighbor signals are switching in the same direction. Probability of Occurrence is 1/32.

- 2. State  $A_2$  ( $\mathbf{1C_c} + \mathbf{C_g}$ ) occurs when the input and one neighbor signal switches in the same direction. The other neighbor signal stays constant. Probability of Occurrence is 1/8.

- 3. State  $A_3$  ( $2\mathbf{C_c} + \mathbf{C_g}$ ) occurs when the input is switching and the neighboring signals are either both constant or switching in mutually opposite directions. Probability of Occurrence is 3/16.

- 4. State A<sub>4</sub> (3C<sub>c</sub> + C<sub>g</sub>) occurs when the input is switching and one neighboring signal switches in the opposite direction, while the other stays constant. Probability of Occurrence is 1/8.

- 5. State  $A_5$  ( $4\mathbf{C_c} + \mathbf{C_g}$ ) occurs when the input is switching and the neighboring signals are switching in the opposite direction. Probability of Occurrence is 1/32.

- 6. State A<sub>6</sub> (0C<sub>c</sub>) occurs when the input is constant and the neighboring signals are either constant or switching in mutually opposite directions. Probability of Occurrence is 3/16.

- 7. State  $A_7$  (1 $\mathbf{C_c}$ ) occurs when the input is constant and one neighboring signal is switching. Probability of Occurrence is 1/4.

- 8. State  $A_8$  (2C<sub>c</sub>) occurs when the input is constant and both neighboring signals are switching in the same direction. Probability of Occurrence is 1/16.

Apart from these broad states, there are other factors like process variations, interference from the non-adjacent wires, leakage, power noise, etc. These can be considered as noise and do not change the broad classifications of the interconnect states. Based on these states, the interconnect capacity can be calculated according to equation 3.10 as,

$$C = \sum_{i=1}^{8} p_i C_i \tag{3.11}$$

where,  $p_i$  is the probability of the occurrence of state  $A_i$ , and

$$C_i = 1 + p_{ei} \log_2(p_{ei}) + (1 - p_{ei}) \log_2(1 - p_{ei}),$$

(3.12)

is the capacity of information transfer, while  $p_{ei}$  is the crossover probability in each of these states.

## 2. The Mathematical Model and Calculations

In the absence of inductive effects, equation 2.6 changes to

$$F(s) = T^{-1}(s), (3.13)$$

where

$$T(s) = \begin{bmatrix} Y & Z & 0 & \dots & 0 & 0 \\ Z & X & Z & \dots & 0 & 0 \\ 0 & Z & X & \dots & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & \dots & X & Z \\ 0 & 0 & 0 & \dots & Z & Y \end{bmatrix},$$

(3.14)

and

$$X = 1 + sR(2C_c + C_a), (3.15)$$

$$Y = 1 + sR(C_g + C_c), (3.16)$$

$$Z = -sRC_c. (3.17)$$

The bus parameters i.e. R,  $C_g$  and  $C_c$  are calculated as before.

To calculate the capacity, a large number of input signal patterns are passed through this transfer function, and errors are recorded at the receiver. The errors in this "monte-carlo" experiment are then classified into the 8 states mentioned above, depending on the input sequence. To attain a statistical closure on the results, a large number of frames having a random sequence of 16 bits were generated. These frames were passed through the transfer function F(s) for various lengths L of the bus. Also, the input sequences should be switched at an arbitrary frequency f. Based on these errors and their probabilities, the interconnect capacity is calculated according to

Fig. 14. The channel capacity as a function of wire length and clock speed.

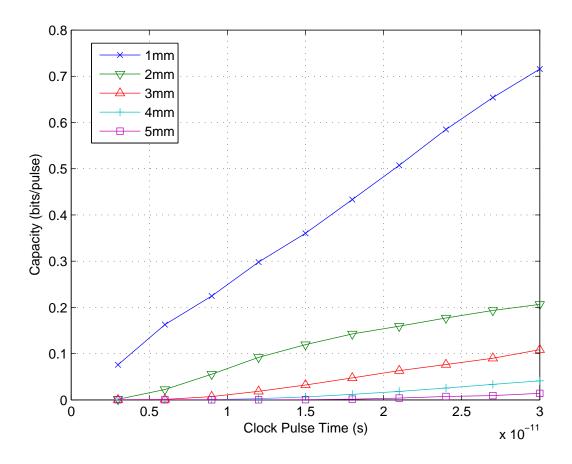

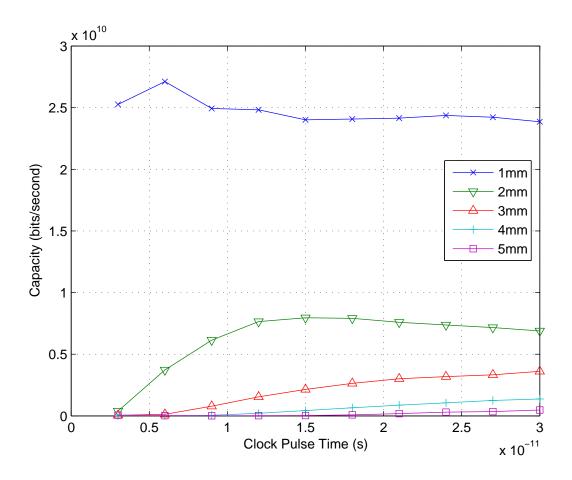

Fig. 14 shows the channel capacity as a function of wire length and the clock speed. Figs. 15 and 16 show the channel capacity as a function of wire length in both bits per pulse and bits per second respectively. Figs. 17 and 18 show the channel capacity as a function of clock pulse time in both bits per clock pulse and bits per second respectively.

From figs. 14, 17, and 18, it is observed that the capacity of the channel in bits per second does not vary much as a function of clock speed. This means that the end result in terms of throughput will remain the same no matter how fast the clock is

Fig. 15. The channel capacity in bits per period as a function of wire length.

Fig. 16. The channel capacity in bits per second as a function of wire length.

Fig. 17. The channel capacity in bits per period as a function of clock speed.

Fig. 18. The channel capacity in bits per second as a function of clock speed.

run. If the clock is very fast, there will be significant number of errors that have to be corrected with appropriate redundancy. While, on the other hand, a slower clock rate will require a lesser redundancy and will therefore achieve similar results.

It is also observed that the channel capacity decreases monotonically for all clock speeds with wire length, implying that the longer the wire, the lesser is its data handling capacity.

This capacity can be used to design better interconnects capable of handling "near capacity" data rates. For example, from fig. 18, for a wire length of 1mm, it is possible to transmit upto 25 Gbps on a single wire, using a faster clock and some error correction coding. On the other hand from fig. 13, for the same wire and same operating conditions, from the worst case timing analysis, a design engineer would design a clock rate of 14 GHz, resulting in a maximum data-rate of 14 Gbps. This design is too pessimistic and tries to accommodate very rare worst case delays. Error correction coding should be employed to compensate for any errors in the tail-end of the delay curve, and thereby significantly increasing the operation frequency and the data rates on interconnects.

It is also worth noting that the results for capacity do not make use of any buffers in the wire length. This makes the findings even more remarkable. Error correction coding can not only speed up the data-rates significantly but also save the power consumed in the buffers. This is an important find in light of the knowledge that the majority of the power in the communication systems is not consumed by the interconnects themselves but by supporting circuitry like buffers etc. [38].

# C. Bus Capacity in the Presence of Capacitive and Inductive Coupling

It is apparent from the "multi-modal" distribution in fig. 8 that an interconnect operates in several different distinct conditions. These conditions can be broadly classified into the states [34,35] listed in table I<sup>1</sup>. There are more states compared to [34] and section B, because unlike capacitive coupling, which is symmetric from the left and the right neighbor, inductive coupling is asymmetric. The probability of occurrence  $p_i$  of each state  $A_i$  is given in table I. Let  $C_i$  be the capacity of the channel when in state  $A_i$ , then

$$C = \sum_{i=1}^{13} p_i C_i. (3.18)$$

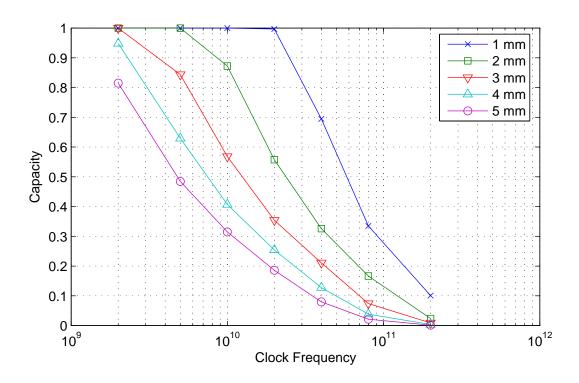

Simulations are conducted to calculate the bit-error-rates observed in the bus in each of the operating states mentioned in table I. From figs. 4 and 5, it is seen that the output signal power is a function of the clock frequency and the length of the wire. Fig. 19 plots the capacity (bits per clock period per wire) as a function of bus length and the clock frequency. It is seen that the capacity falls down as the clock rate or the length increases. Note the similarity of this figure to figs. 4 and 5.

Fig. 20 plots the capacity as bits per second per wire as a function of the bus length and the clock frequency. It is observed that a given bus has an optimal operation frequency at which the data rate is maximum. This optimal frequency of operation is much higher than the worst case pessimistic design. As an example, the worst case clock design for a 1mm long bus would be 17.5 GHz resulting in 17.5 Gbps data through all the wires. It is possible to drive the bus at 40 GHz to achieve up to 28 Gbps with a rate 0.7 code. Again, a rate 0.7 code means that for every 7 bits of

$<sup>^{1}</sup>$ ↑ means a 0 to 1 transition,  $\downarrow$  means a 1 to 0 transition, and - means no transition

| Tab      | le I. Th     | <u>ne Intercon</u> | nect St      | ates |

|----------|--------------|--------------------|--------------|------|

| State    | Left         | Relevant           | Right        | Prob |

|          | Wire         | Wire               | Wire         |      |

| $A_1$    | 1            | <b>↑</b>           | 1            | 1/32 |

|          | ↓ ↓          | $\downarrow$       | $\downarrow$ |      |

| $A_2$    | 1            | <b>↑</b>           | -            | 1/16 |

|          | $\downarrow$ | $\downarrow$       | _            |      |

| $A_3$    | 1            | <b>↑</b>           | $\downarrow$ | 1/32 |

|          | ↓            | $\downarrow$       | 1            |      |

| $A_4$    | -            | <b>↑</b>           | <u> </u>     | 1/16 |

|          | _            | $\downarrow$       | ↓            |      |

| $A_5$    | -            | <b>↑</b>           | -            | 1/8  |

|          | _            | $\downarrow$       | -            |      |

| $A_6$    | -            | <b>↑</b>           | $\downarrow$ | 1/16 |

|          | -            | $\downarrow$       |              |      |

| $A_7$    | $\downarrow$ | <b>↓</b>           | <u>↑</u>     | 1/32 |

|          | 1            | $\downarrow$       | ↓            |      |

| $A_8$    | $\downarrow$ | <u>↓</u>           | -            | 1/16 |

|          | 1            | $\downarrow$       | _            |      |

| $A_9$    | $\downarrow$ | <b>↑</b>           | $\downarrow$ | 1/32 |

|          | 1            | $\downarrow$       | <b>↑</b>     |      |

| $A_{10}$ | 1            | -                  | <u> </u>     | 1/16 |

|          | $\downarrow$ | -                  | ↓            |      |

| $A_{11}$ | 1            | -                  | -            | 1/4  |

|          | <b>1</b>     | -                  | -            |      |

|          | _            | -                  | <b>↑</b>     |      |

|          | _            | -                  | ↓            |      |

| $A_{12}$ | 1            | -                  | <b></b>      | 1/16 |

|          | $\downarrow$ | -                  | <b>↑</b>     |      |

| $A_{13}$ | -            | -                  | -            | 1/8  |

Fig. 19. The capacity of 8 bit wide bus as a function of clock frequency and length

information, there are 3 parity bits to recover errors, resulting in a rate 7/10 = 0.7

Another important observation is that the optimal frequencies for different wire-lengths require different code rates. For example, running a 1mm long wire at the optimal frequency requires only a rate 0.7 Code while running a 5 mm wire at its own optimal frequency requires a rate 0.18 code. While the coding scheme for the 1 mm wire results in only a 50% overhead, the coding scheme for the 5 mm wires results in more than 500% overhead. Though constructing rate 0.7 codes is fairly simple, constructing rate 0.2 codes to provide error correction in a 5 mm wire may prove tricky if not impossible. This may be a trade-off requiring operation at non-optimal frequencies at a higher rate code. Also, at a very high wire-length buffer insertion may be coupled with coding schemes to become an ideal option.

Fig. 20. The data rate limits of 8-bit wide bus as a function of clock frequency and length

## CHAPTER IV

#### CODES FOR ON-CHIP BUSES

#### A. Previous Work

The problem associated with crosstalk and other error inducing factors is 3 fold.

- High bit error rates

- Large delays and delay variations.

- High energy consumption

While buffers reduce the delays and improve the reliability, they lead to high energy consumption. The coding techniques discussed in [16, 17, 20, 22–24] improve just one of the aspects mentioned above. The codes that aim to aggressively achieve speedup [16, 17, 20], ignore energy and reliability considerations. Some others improve the energy consumption [22–24] while leaving out the other two factors.

The problem that remains is to design a coding scheme that accomplishes all three tasks of low energy, low delay and low error rates. In [15] an attempt has been made to achieve all of the three improvements by employing a series of coders at the driver side. There is a "low delay" code, followed by a "low power" code(LPC), followed by an "error correcting code" (ECC). While the objective of improving delay, energy and reliability is achieved, this happens at a huge overhead. Each code adds its own redundancy to achieve its goal. The total redundancy overhead in the end is prohibitive for any real implementation. These codes are listed in table II.

All codes are consructed using a cascade of crosstalk avoidance codes (CAC), and LPC followed by ECC. The various techniques used in the construction of these

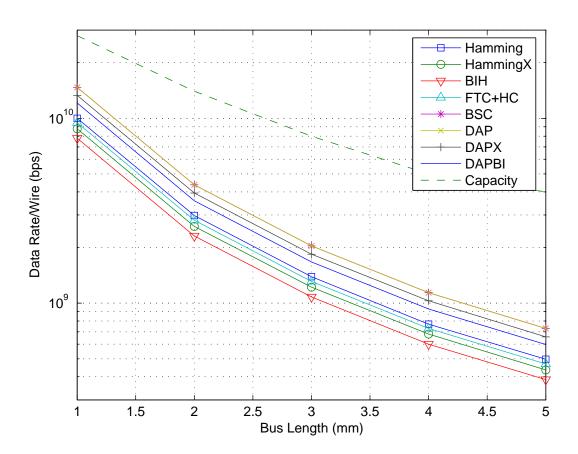

codes are BI <sup>1</sup>, Shielding <sup>2</sup>, and Duplication <sup>3</sup>. Speedups are only offered where CAC is present. The CAC reduces the worst case capacitive coupling from  $4C_c$  to  $2C_c$  resulting in a speedup of  $\frac{C_g+4C_c}{C_g+2C_c}$ . Table III list the properties of these codes. In the table, the data rates per wire is calculated by multiplying the reference frequency (of the no code system) by the speed-up and the code rate. To calculate the speed-up the assumption is  $C_c = 4C_g$ . Fig. 21 shows a comparison of all codes against the information capacity. It is seen that BSC and DAP are the best codes in terms of data rate v/s overhead comparison.

Table II. The Code Construction [15] for a 4-Bit Wide Bus

|          |             |     | 5] 101 a 4-Bit <b>v</b> | Total |

|----------|-------------|-----|-------------------------|-------|

| Code     | CAC         | LPC | ECC                     | Extra |

|          |             |     |                         | Wires |

| Hamming  | -           | -   | Hamming                 | 3     |

| HammingX | -           |     | Hamming &               | 4     |

|          |             |     | parity                  |       |

| BIH      | -           | BI  | Hamming                 | 5     |

| FTC+HC   | CAC [20]    |     | Hamming                 | 10    |

| BSC      | Shielding   | -   | -                       | 5     |

| DAP      | Duplication |     | Parity                  | 5     |

| DAPX     | Duplication | _   | Parity with             | 6     |

|          |             |     | shielding               |       |

| DAPBI    | Duplication | BI  | Parity                  | 7     |

$<sup>^1\</sup>mathrm{Bus}$  Invert Codes [24] as LPC

<sup>&</sup>lt;sup>2</sup>Insert a Vdd or Gnd Wire between data lines as a CAC

<sup>&</sup>lt;sup>3</sup>Duplication as a CAC

| Table III. The Data Per Wire Rates for Different Codes |      |       |      |      |      |      |

|--------------------------------------------------------|------|-------|------|------|------|------|

|                                                        |      |       | 1mm  | 2mm  | 3mm  | 4mm  |

| Code                                                   | Rate | Speed | d/w  | d/w  | d/w  | d/w  |

|                                                        | [15] | Up    | Gbps | Gbps | Gbps | Gbps |

| No Code                                                | 1    | 1     | 17.5 | 5.21 | 2.43 | 1.36 |

| Hamming                                                | 0.57 | 1     | 10.0 | 2.98 | 1.39 | 0.77 |

| HammX                                                  | 0.5  | 1     | 8.77 | 2.60 | 1.22 | 0.68 |

| BIH                                                    | 0.44 | 1     | 7.80 | 2.31 | 1.08 | 0.60 |

| FTC+HC                                                 | 0.28 | 1.88  | 9.47 | 2.81 | 1.31 | 0.73 |

| BSC                                                    | 0.44 | 1.88  | 14.7 | 4.37 | 2.04 | 1.14 |

| DAP                                                    | 0.44 | 1.88  | 14.7 | 4.37 | 2.04 | 1.14 |

| DAPX                                                   | 0.4  | 1.88  | 13.3 | 3.94 | 1.84 | 1.03 |

| DAPBI                                                  | 0.36 | 1.88  | 12.1 | 3.58 | 1.67 | 0.93 |

| Capacity                                               |      |       | 28   | 14   | 8    | 5    |

Fig. 21. The comparison of various codes against capacity

# B. Bus Properties

As in Ch. II, the small section of an n-bit wide bus can be described as a multi-input-multi-output (MIMO) system, the transfer function of which can be described in Laplace domain as an  $n \times n$  matrix  $F(s) = (I + L(s)C(s))^{-1}$ , where, the size of I, L(s) and C(s) is  $n \times n$ . L(s) defines the inductance and resistance while C(s) defines the capacitance of the wires.

# 1. Delay

The signal delay of the  $l^{th}$  wire, (1 < l < n) in an n-bit wide bus is given in [17] as

$$T_d \propto C_q \left\{ (1+2\lambda)|\Delta_l| - \lambda \Delta_l(\Delta_{l-1} + \Delta_{l+1}) \right\} \tag{4.1}$$

where,  $\Delta_l$  is the transition in the  $l^{th}$  wire of a bus and  $\lambda = C_c/C_g$ . This delay equation is not accurate in the presence of inductive effects. However,  $R >> \omega L_s > \omega L_m$  for  $\omega < 2\pi$  100 GHz, especially for small wire lengths. This equation is therefore a good approximation for low frequencies. The various various delay patterns [20] are summarized below. In all the patterns  $\Delta_l = \pm 1$ .

$$\begin{bmatrix} \Delta_{l-1} \\ \Delta_{l+1} \end{bmatrix} = \begin{cases} \begin{bmatrix} -\Delta_{l} \\ -\Delta_{l} \end{bmatrix} & , 4C \\ \begin{bmatrix} -\Delta_{l} \\ 0 \end{bmatrix}, \begin{bmatrix} 0 \\ -\Delta_{l} \end{bmatrix} & , 3C \\ \begin{bmatrix} -\Delta_{l} \\ \Delta_{l} \end{bmatrix}, \begin{bmatrix} \Delta_{l} \\ -\Delta_{l} \end{bmatrix}, \begin{bmatrix} 0 \\ 0 \end{bmatrix}, 2C \\ \begin{bmatrix} \Delta_{l} \\ 0 \end{bmatrix}, \begin{bmatrix} 0 \\ \Delta_{l} \end{bmatrix} & , 1C \\ \begin{bmatrix} \Delta_{l} \\ \Delta_{l} \end{bmatrix} & , 0C \end{cases}$$

$$(4.2)$$

• 4C Patterns -  $T_d \propto C_g(1+4\lambda)$ .

- 3C Patterns  $T_d \propto C_g(1+3\lambda)$ .

- 2C Patterns  $T_d \propto C_g(1+2\lambda)$ .

- 1C Patterns  $T_d \propto C_g(1+\lambda)$ .

- 0C Patterns  $T_d \propto C_q$ .

As seen in the patterns above, neighboring signals switching in opposite directions lead to slower signals while neighboring signals switching in the same direction have a "speed-up" effect on each other. The delay of a bus is the worst case coupling pattern. There may be a large number of 1C patterns, but if there is a single 4C pattern, the delay of the bus is 4C. Any coding scheme that aims to speed-up the signal propagation should therefore avoid the worse patterns.

# 2. Energy

The total energy consumed by the drivers of a bus [18] when transmitting the  $k^{th}$  frame is

$$E_k = \frac{V_{dd}^2}{2} S_k^T \frac{C(s)}{s} \left[ S_k - S_{k-1} \right]. \tag{4.3}$$

Here s is the laplace variable,  $V_{dd}$  is the supply voltage,  $S_k$  is a column vector of n binary values in the  $k^{th}$  frame.  $S_k^T$  is the transpose. The energy consumed by the driver of a single wire l for transmitting the  $k^{th}$  bit is

$$E_{l,k} = \frac{C_g V_{dd}^2}{2} s_{l,k} \begin{bmatrix} -\lambda & 1 + 2\lambda & -\lambda \end{bmatrix} \begin{bmatrix} \Delta_{l-1} \\ \Delta_l \\ \Delta_{l+1} \end{bmatrix}, \tag{4.4}$$

where,  $s_{l,k} \in \{0,1\}$  is the final binary value of the  $l^{th}$  wire. The energy consumed for the various patterns discussed above are as follows.

- 4C Patterns  $E_{l,k} \propto C_g(1+4\lambda)$ .

- 3C Patterns  $E_{l,k} \propto C_g(1+3\lambda)$ .

- 2C Patterns  $E_{l,k} \propto C_g(1+2\lambda)$ .

- 1C Patterns  $E_{l,k} \propto C_g(1+\lambda)$ .

- 0C Patterns  $E_{l,k} \propto C_g$ .

Based on the equations above, it might seem that any coding scheme that aims to eliminate the bad delay patterns will have a similar effect on energy consumed and that the energy problem need not be independently considered while designing codes. This is however not true. While the delay of a bus was the delay of the *worst case* pattern, the energy required for transmission is the *average* of all patterns.

As an example, consider bus shielding versus a simple illustrative code called the "AND code" described below. In bus shielding, wires carrying the  $V_{dd}$  or ground are inserted between data wires. Since there is no signal transition in the shield wires, there are no 4C, 3C, 1C and 0C patterns. The only pattern available is the 2C pattern. The AND code is implemented by replacing the  $V_{dd}$  or ground signal in the shield wires by a logical AND of the two surrounding data wires. This scheme eliminates the 4C and 3C sequences, while keeping 2C, 1C and 0C sequences.

The schemes are implemented on 1 mm long bus in 0.1  $\mu$ m technology, where  $\lambda = 4$  based on a parallel plate model. The delay distributions of both schemes are given in figures 22 and 23 respectively. It is seen that the worst case delay in both cases is 31 ps corresponding to a 2C pattern. The speedup compared to fig 8 is roughly  $\frac{1+4\lambda}{1+2\lambda} = \frac{17}{9} = 1.88$  or  $\frac{57ps}{31ps} = 1.83$ . The small discrepancy is attributed to the inductive effects.

Fig. 22. The signal delay distribution of a 1 mm long "Shielded" bus.

Fig. 23. The signal delay distribution of a 1 mm long bus with "AND" code.

Even though the speedup is equal in both cases, the energy gains are quite different. For 4 bit data, the average energy consumed in an un-coded bus is  $\propto 1 + 1.5\lambda$ , the average energy in the bus with shielding is also  $\propto 1 + 1.5\lambda$ , while the average energy in the AND coded bus is  $\propto 1.5625 + 1.125\lambda$ , meaning a total saving of  $1 - \frac{1.5625 + 1.125\lambda}{1 + 1.5\lambda} = 1 - \frac{6.0625}{7} = 13.4\%$  over both the un-coded bus and the bus with shielding. Note that this saving is despite the fact that a AND coded bus uses 7 wires versus the 4 wires used by an un-coded bus.

# 3. Reliability

The reliability of signals in long buses is affected by the DSM noise, which is also known as the power noise. Power noise is a result of a rapid draining of the power capacitors on a chip when a large number of devices switch simultaneously. As a consequence, the supply voltages deviate from their "rail" values. At times, this deviation results in detection errors at the receiver.

Another factor that leads to errors in detection is the clock speed (delay). Fig. 24 shows the dependence of the received output signal on the clock frequency. It is seen that at faster clocks, there is more chance of an error, while at slower clocks, the signals are more "settled-down". Typically the clock speeds of a system are designed such that signals settle down completely, and the only errors are due to the DSM noise. An ECC can not only correct the errors due to DSM noise, but also the errors due to delay, therefore a two-fold gain in speedup can be had with a "low-delay" ECC.

Fig. 24. The output voltage distribution of an 8 bit wide 1 mm long bus.

## C. Code Construction

Before describing the coding scheme, here is a review list of the traits desired of a practical code.

- High data reliability The codec should not leave any errors in the data-path.

- Low signal propagation delay The signal propagation delay through the encoder, the wires and the decoder combined should be less than un-coded wires.

- Low energy consumption The total energy consumed in the encoder, drivers, wires, sensors and the decoder combined should be less than the energy used in the un-coded system.

- Low coding overhead The overhead of coding, i.e., the extra area used up by the encoding/decoding logic should be minimal. The number of extra wires added for redundancy should be low.

The two codes mentioned before, i.e., shielding and the AND code, are very easy to implement and result in a 1.83x speedup. However, they result in a 100% overhead in terms of the number of wires. This is prohibitive for implementation. A more complex coding scheme that possesses the same properties with a low overhead is desired.

If an n bit information is to be coded using a k bit code (k wires), and if  $S_i$  is a unique set of  $2^n$  k-bit words, out of a total of  $2^k$  words, then there are a total of  $\binom{2^k}{2^n}$  possible sets. Out of these sets, a code (or, a set  $S_i$ ) is chosen by *elimination* as described below.

• First eliminate the codes that have a high worst case delay pattern. Eliminate

the codes  $S_i, \forall 1 < i < {2k \choose 2^n}$  that fail the test,

$$C_c(S_i(x), S_i(y)) \le C_{c,max}, \forall 1 < (x, y) < 2^n$$

(4.5)

where,  $C_{c,max}$  is the maximum coupling capacitance (delay) pattern allowed, and  $C_c(S_i(x), S_i(y))$  is the worst coupling capacitance (delay) when transiting from code word  $S_i(x)$  to  $S_i(y)$ .

• Next eliminate the codes based on their error correction capability. The code correction capability is determined by the minimum hamming distance  $D_{min}$  between any two code words. If e error correction is required, then  $D_{min} \ge 2e + 1$ . Based on this, eliminate the codes that fail the following test.

$$D(S_i(x), S_i(y)) < D_{min}, \forall 1 < (x, y) < 2^n$$

(4.6)

where,  $D(S_i(x), S_i(y))$  is the hamming distance between  $S_i(x)$  and  $S_i(y)$ .

Let **S** be the set of all  $S_i$  that are not eliminated, out of  $\binom{2^k}{2^n}$  initial codes. The choice of the final code C is made based on the average energy consumption.

$$C = \arg\min_{S_i} \sum_{x=1}^{2^n} \sum_{y=1}^{2^n} E(S_i(x), S_i(y))$$

(4.7)

As mentioned before and seen from the algorithm above, this code is constructed using an exhaustive search. A formal technique is difficult to have due to the non-linearity of the low-delay (Crosstalk avoidance) codes. The codes presented are still practical because this search has to be performed only once for a given bus width and a given technology. These codes can be incorporated into the libraries of the design tools and can be transparent to the designer.

Based on the above code search method, table IV presents the values of the number of wires k as a function of the information width n and the code constraint.

The rows of the tables represent the constraint, while the columns represent the information width n. It is seen that for a 4-bits data bus, 5, 5 or 8 wires are required for 3C, 2C or 1C codes respectively. Compared to the Shielding and the AND codes, this is a huge improvement in the overhead requirement.

Table IV. Wire Requirement for Various Codes as a Function of Information Width

|                 | n=2 | n=3 | n=4 | n=5 | n=6 | n=7 |

|-----------------|-----|-----|-----|-----|-----|-----|

| Max. 3C Allowed | 2   | 4   | 5   | 6   | 7   | 8   |

| Max. 2C Allowed | 2   | 4   | 5   | 7   | 8   | 10  |

| Max. 1C Allowed | 3   | 6   | 8   | 11  | 13  | 16  |

| SEC             | 5   | 6   | 7   | 9   | 10  | 11  |

| SEC, Max. 3C    | 5   | 7   | 8   | 10  | 11  | 13  |

| SEC, Max. 2C    | 5   | 7   | 9   | 11  | 12  | 14  |

| SEC, Max. 1C    | 6   | 9   | 11  | 14  | 16  | 19  |

An example code that eliminates 3C patterns in 4-bit wide data is presented in table V. It is named "4B5W" because 4 bits are transmitted over 5 wires. No two codewords exhibit a 4C or 3C pattern. A 1.88x speedup is achieved with just 25% wire overhead and a 2-level gate delay at the encoder. The energy consumption calculated based on equation 4.3 is proportional to  $1.25 + 1.25\lambda$

Another example code that eliminates 2C patterns and correct single errors is presented in table VI. No two codewords exhibit a 4C, 3C or even 2C pattern. Also, each pair of codewords has a hamming distance of at least 3 units. A speedup of  $(1 + 4\lambda)/(1 + \lambda) = 17/5 = 3.4$  is expected, while a speedup of 2.7 is seen in fig. 25. The discrepancy is attributed to the inductive effects which become prominent at speeds around 100 GHz (10ps). The energy consumption based on equation 4.3 is proportional to  $2.6523 + 1.3789\lambda$ .

Table V. An Example 4B5W Code for 3C Elimination

| Data Bits | Code  |

|-----------|-------|

| 0000      | 00000 |

| 0001      | 00001 |

| 0010      | 00110 |

| 0011      | 00011 |

| 0100      | 01100 |

| 0101      | 00111 |

| 0110      | 01110 |

| 0111      | 01111 |

| 1000      | 10000 |

| 1001      | 10001 |

| 1010      | 11000 |

| 1011      | 10011 |

| 1100      | 11100 |

| 1101      | 11001 |

| 1110      | 11110 |

| 1111      | 11111 |

Table VI. An Example 4B11 $\underline{\mathrm{W}}$  Code for 2C Elimination and Single Error Correction

| Data Bits | Code         |  |  |

|-----------|--------------|--|--|

| 0000      | 00000000000  |  |  |

| 0001      | 00000000111  |  |  |

| 0010      | 00000011100  |  |  |

| 0011      | 00001111111  |  |  |

| 0100      | 00111000000  |  |  |

| 0101      | 00111000111  |  |  |

| 0110      | 00111111100  |  |  |

| 0111      | 00111110001  |  |  |

| 1000      | 11100000000  |  |  |

| 1001      | 10000011111  |  |  |

| 1010      | 10001111100  |  |  |

| 1011      | 11100000111  |  |  |

| 1100      | 11100011100  |  |  |

| 1101      | 11111000001  |  |  |

| 1110      | 111111110000 |  |  |

| 1111      | 111111111111 |  |  |

Fig. 25. The signal delay distribution of a 1 mm long bus with 4B11B code.

# 1. Comparison with Existing Codes and Capacity

As mentioned before, a variety of codes were introduced in [15], with a variety of features. These codes are a cascade of CAC, LPC and single error detection/correction (SED/SEC) codes. Table VII compares the codes in [15] to the codes developed here (Shielding, AND, 4B5W, 4B11W) based on delay, energy, overhead and error correction capability. The rate n/k of a code is the number of information bits per transmitted symbol. The energy is calculated based on equation 4.3.

Table VII. Comparison of Speedups and Overheads of Different Codes for a 4-Bit Bus

| Code      | Delay $\propto$ | Code Rate | Energy               | ECC  |

|-----------|-----------------|-----------|----------------------|------|

| Hamming   | $1+4\lambda$    | 0.57      | $1.75 + 3.00\lambda$ | SEC  |

| HammingX  | $1+4\lambda$    | 0.5       | $1.75 + 3.00\lambda$ | SEC  |

| BIH       | $1+4\lambda$    | 0.44      | $1.78 + 3.25\lambda$ | SEC  |

| FTC+HC    | $1+2\lambda$    | 0.28      | $2.09 + 3.20\lambda$ | SEC  |

| BSC       | $1+2\lambda$    | 0.44      | $2.25 + 2.00\lambda$ | None |

| DAP       | $1+2\lambda$    | 0.44      | $2.25 + 2.00\lambda$ | SED  |

| DAPX      | $1+2\lambda$    | 0.4       | $2.50 + 2.00\lambda$ | SED  |

| DAPBI     | $1+2\lambda$    | 0.36      | $1.81 + 1.75\lambda$ | SED  |

| Shielding | $1+2\lambda$    | 0.57      | $1.00 + 1.50\lambda$ | None |

| AND Code  | $1+2\lambda$    | 0.57      | $1.56 + 1.12\lambda$ | None |

| 4B5W      | $1+2\lambda$    | 0.8       | $1.25 + 1.25\lambda$ | None |

| 4B11W     | $1+1\lambda$    | 0.3636    | $2.65 + 1.37\lambda$ | SEC  |

Figure 26 plots the relative speeds of information transfer per wire as a function of  $\lambda = C_c/C_g$  for the various codes. The comparison is done based on the ratio of speedup / number of wires. This is a better metric compared to just speedup because

Fig. 26. The comparison of speedups/overhead of the various codes

Fig. 27. The comparison of energy consumption of the various codes

if overhead cost was not included, then an infinite speedup can be had by placing a large number of independent un-coded 4-bit buses in parallel to each other. Among the SEC codes, the 4B11W code out performs all other codes, while among the non error correcting codes, the 4B5W code is the best.

Figure 27 plots the energy consumption relative to the un-coded system as a function of  $\lambda$  for the various codes. Among the SEC codes, the 4B11W code out performs all other codes for  $\lambda > 2$ , while among the non error correcting codes, the 4B5W code and the AND code are the best depending on the  $\lambda$ .

This section presents a unified coding technique for low energy, low delay, reliable transmission on on-chip buses. The codes developed here speed-up the transmission by avoiding and exploiting the effects of crosstalk, reduce the total energy consumed by minimizing signal switches, and provide reliability using communication-theoretic ECC. The codes presented herein show gain for even small wire-lengths, and therefore can be used in conjunction with the existing buffer insertion techniques to achieve even higher speedups. The codes implemented for a 4-bit wide bus in the  $0.1\mu m$  process show a speedup of 2.7x with a 4 Wire overhead, and 1.83x for a 1 wire overhead. The latter code is called the 4B5W code herein, because it translates 4 bits into 5 wires. If error correction is a requirement then a 2.7x and 1.83 x speedup can be had with 7 and 5 extra wires respectively. The former code is called the 4B11W code. The total energy consumed in the 4B5W code and the 4B11W code are respectively 86% and 120% of the energy consumed in the no-code system. The 20% extra energy consumed in the 4B11W should be seen in light of the fact that it even corrects single errors. Also, as the feature size reduces, i.e., the ratio  $C_c/C_g$  increases, this energy consumption is even better.

Even though the codes presented here are based on exhaustive search of the entire code-space and not a formal closed form technique, they are still practical.

This is because the search does not need to be done at the design time. For every given bus width and technology, there is a unique code. Based on the bus parameters, a library can be constructed and incorporated into the CAD tools, making the bus coding scheme transparent to the designer. For very wide buses, when even a one-time solution is difficult to have, a "divide-and-conquer" technique can be deployed breaking the bus into smaller manageable segments.

## CHAPTER V

#### LDPC CODES

Low density parity check (LDPC) codes, introduced by Gallager [39], are a class of linear block codes that perform very close to the turbo codes [40]. In [41], a use of LDPC codes has been proposed in Core-Network Interfaces (CNI) in the modern NoC architectures. Results claiming energy and latency savings have been provided.