# CMOS RF FRONT-END DESIGN FOR TERRESTRIAL AND MOBILE DIGITAL TELEVISION SYSTEMS

A Dissertation

by

## JIANHONG XIAO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2007

Major Subject: Electrical Engineering

## CMOS RF FRONT-END DESIGN

## FOR TERRESTRIAL AND MOBILE DIGITAL TELEVISION SYSTEMS

## A Dissertation

by

## JIANHONG XIAO

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee, Jose Silva-Martinez Committee Members, Edgar Sanchez-Sinencio

Peng Li

Cesar O. Malave

Head of Department, Costas Georghiades

May 2007

Major Subject: Electrical Engineering

#### **ABSTRACT**

## CMOS RF Front-End Design

for Terrestrial and Mobile Digital Television Systems (May 2007)

Jianhong Xiao, B.S., Peking University

Chair of Advisory Committee: Dr. Jose Silva-Martinez

With the increasing demand for high quality TV service, digital television (DTV) is replacing the conventional analog television. DTV tuner is one of the most critical blocks of the DTV receiver system; it down-converts the desired DTV RF channel to baseband or

a low intermediate frequency with enough quality. This research is mainly focused on the

analysis and realization of low-cost low-power front-ends for ATSC terrestrial DTV and

DVB-H mobile DTV tuner systems.

For the design of the ATSC terrestrial tuner, a novel double quadrature tuner architecture,

which can not only minimize the tuner power consumption but also achieve the fully

integration, has been proposed. A double quadrature down-converter has been designed and

fabricated with TSMC 0.35µm CMOS technology; the measurement results verified the

proposed concepts.

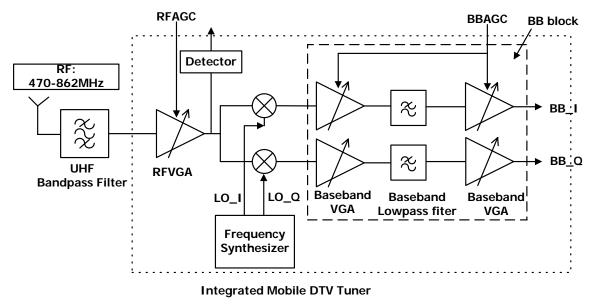

For the mobile DTV tuner, a zero-IF architecture is used and it can achieve the DVB-H

specifications with less than 200mW power consumption. In the implementation of the

mobile DVB-H tuner, a novel RF variable gain amplifier (RFVGA) and a low flicker noise

current-mode passive mixer have been proposed. The proposed RFVGA achieves high dynamic range and robust input impedance matching performance, which is the main design challenge for the traditional implementations. The current-mode passive mixer achieves high-gain, low noise (especially low flicker noise) and high-linearity (over 10dBm IIP3) with low power supplies; it is believed that this is a promising topology for low voltage high dynamic range mixer applications. The RFVGA has been fabricated in TSMC 0.18µm CMOS technology and the measurement results agree well with the theoretical ones.

# DEDICATION

To my parents, my dearest wife Mingya Xu

For all their love and unconditional support

#### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to my advisor, Dr. Jose Silva-Martinez, for his guidance, support and encouragement during my study at Texas A&M University. He showed me the art of analog integrated circuit design through his in-depth knowledge and pioneering expertise. His great personality made my research experience more joyful and encouraging. His guidance during the development of my research has been invaluable. I feel very grateful for his supervision both on the technical and the personal levels during my stay in College Station.

I would like to thank and acknowledge Dr. Edgar Sanchez-Sinencio, the director of the Analog and Mixed-signal center. It was he who gave me the admission into this group. His analog courses have educated me a lot not only in the detailed techniques but also in the spirit of analog design. His kind help, support and encouragement made my study fruitful.

I would like to thank my mentor, Mr. Iuri Mehr, for guidance and discussions during my internship at Analog Devices. From the project definition to chip measurement, he was always accessible and willing to answer my questions. I was deeply affected by his serious attitude and insight explanations. I also would like to thank and acknowledge Sergei Nesterenko, Richard Schreier and Steven Rose for their sincere guide and help during the internship. Specially, I would like to thank my friend, Yunchu Li. He helped me a lot not only in the technical issues but also the personal life. I lived with him and his family in

Andover for around nine months and it is one of the most joyful periods during my graduate study.

I would like to thank Dr. Peng Li, Dr. Henry F. Taylor, and Dr. Cesar O. Malave for serving as my committee members and for their valuable inputs and suggestions. Special thanks go to the secretary of AMSC group, Ms. Ella Gallagher, for her kind help.

Most of my research time was spent on the two research projects, the designs of terrestrial DTV tuner and mobile DTV tuner. The contributions and cooperation of the team members made the learning and research study a great experience of life. Here I would like to thank all of my team members, including Tianwei Li, Guang Zhang, Raghavendra Kulkarni and Dr. Yong Moon.

I'd like to thank my friends, Shanfeng Cheng and Haitao Tong, for their technical discussions and valuable help. I also would like to thank all of professors and students in the Analog and Mixed-signal Center for their kindly help and sharing ideas.

Special thanks go to my parents. Without their love and support, I would not achieve what it is now. Last but not least, I would like to thank my wife, Mingya Xu, who is always there with her constant love, care and support. She gave me the encouragement and motivation to make it through all the hard work during my Ph.D. study.

# TABLE OF CONTENTS

|      |                                                                                                                                                                                                                                           | Page           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABST | TRACT                                                                                                                                                                                                                                     | iii            |

| DEDI | CATION                                                                                                                                                                                                                                    | v              |

| ACKI | NOWLEDGMENTS                                                                                                                                                                                                                              | vi             |

| TABL | LE OF CONTENTS                                                                                                                                                                                                                            | viii           |

| LIST | OF FIGURES                                                                                                                                                                                                                                | X              |

| LIST | OF TABLES                                                                                                                                                                                                                                 | XV             |

| СНА  | PTER                                                                                                                                                                                                                                      |                |

| I    | INTRODUCTION                                                                                                                                                                                                                              | 1              |

|      | <ul><li>1.1. Digital Television Systems</li><li>1.2. Digital Television Tuner</li><li>1.3. Research Focus and Dissertation Overview</li></ul>                                                                                             | 4              |

| II   | LOW POWER FULLY INTEGRATED CMOS DTV TUNER FRONT-END FOR ATSC TERRESTRIAL BROADCASTING                                                                                                                                                     | 10             |

|      | <ul> <li>2.1. ATSC Terrestrial DTV Tuner System</li> <li>2.2. Double Quadrature Down-conversion Architecture</li> <li>2.3. Double Quadrature Down-converter Design</li> <li>2.4. Experimental Results</li> <li>2.5. Conclusion</li> </ul> | 16<br>25<br>39 |

| III  | MOBILE DTV (DVB-H) TUNER SYSTEM DESIGN                                                                                                                                                                                                    | 45             |

|      | 3.1. Introduction 3.2. DVB-H System and Mobile DTV Tuner 3.3. Tuner Architecture 3.4. Block Level Specifications 3.5. Conclusion                                                                                                          | 46<br>59<br>72 |

| IV   | DESIGN OF RF VARIABLE GAIN AMPLIFIER (RFVGA)                                                                                                                                                                                              | 74             |

|      | <ul> <li>4.1. Introduction</li> <li>4.2. RFVGA Architecture Design</li> <li>4.3. Design of Current-steering Transconductance (Gm) Stage</li> <li>4.4. Design of Gain-independent Impedance Matching Block</li> </ul>                      | 77<br>82       |

| CHAPTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 4.5. Design of Gain Control Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93     |

| 4.6. Noise and Linearity Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98     |

| 4.7. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 4.8. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| V HIGH DYNAMIC RANGE DOWN-CONVERSION MIXER DESIGNATION OF THE PROPERTY OF THE | GN 114 |

| 5.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 114    |

| 5.2. Current Mode Passive Mixer Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 123    |

| 5.3. Circuit Implementation and Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 137    |

| 5.4. Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 143    |

| VI CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 145    |

| REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 147    |

| VITA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 153    |

# LIST OF FIGURES

|                                                                                             | Page |

|---------------------------------------------------------------------------------------------|------|

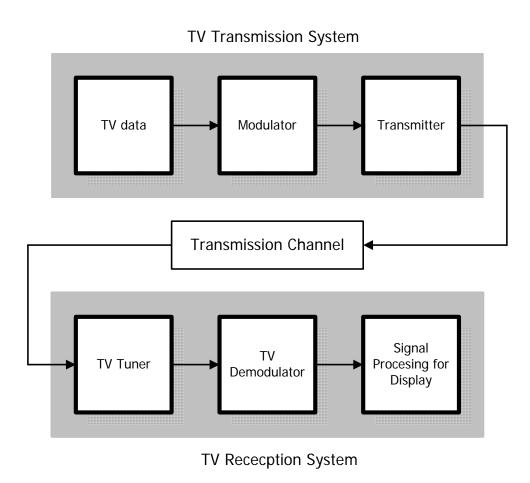

| Fig. 1.1. Block diagram of the television system                                            | 2    |

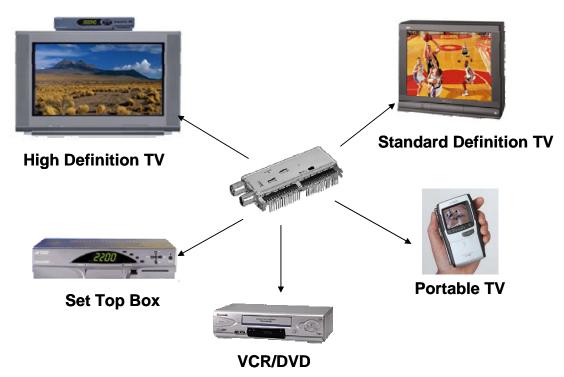

| Fig. 1.2. DTV tuner applications                                                            | 5    |

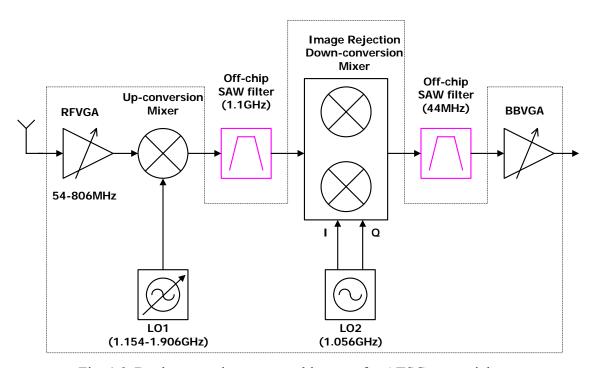

| Fig. 1.3. Dual-conversion tuner architecture for ATSC terrestrial tuner                     | 7    |

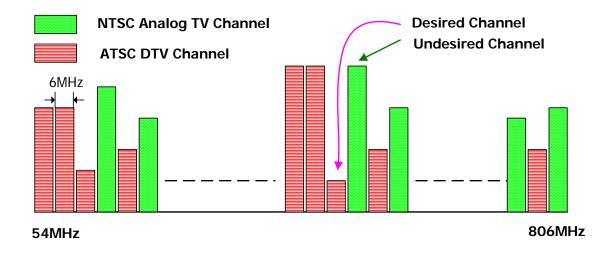

| Fig. 2.1. ATSC DTV tuner input spectrum                                                     | 11   |

| Fig. 2.2. Noise figure calculation plot.                                                    | 11   |

| Fig. 2.3. IIP3 calculation plot.                                                            | 12   |

| Fig. 2.4. Illustration of image problem during down-conversion in low-IF tuner              | 14   |

| Fig. 2.5. Illustration of harmonic mixing in zero-IF tuners                                 | 15   |

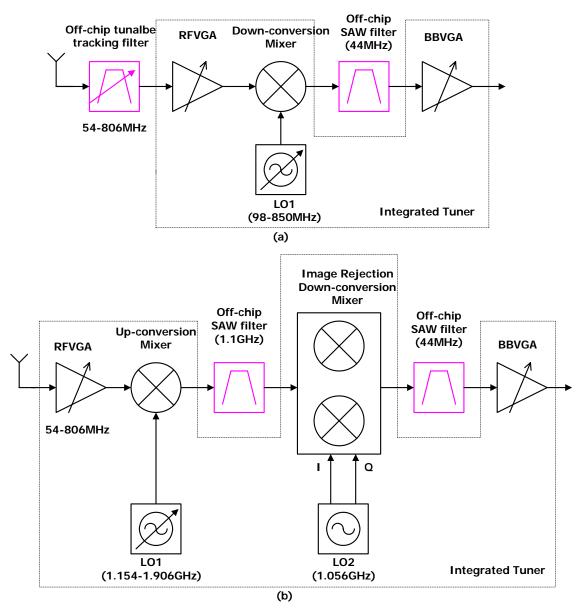

| Fig. 2.6. Typical TV-Tuner architectures (a) single-conversion; (b) dual-conversion         | 17   |

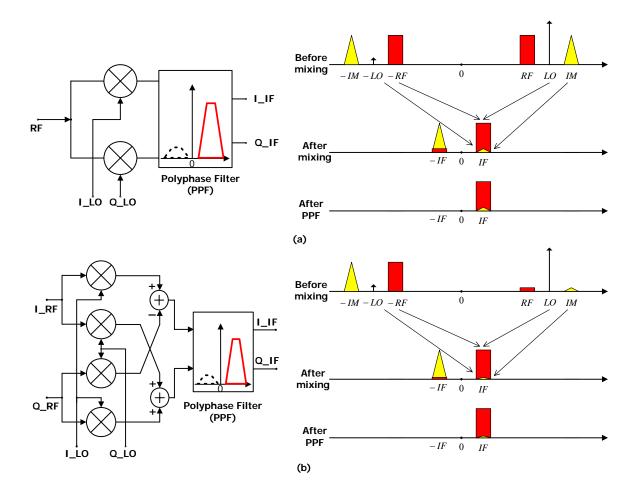

| Fig. 2.7. (a) Single quadrature down-converter; (b) Double quadrature down converter.       | 19   |

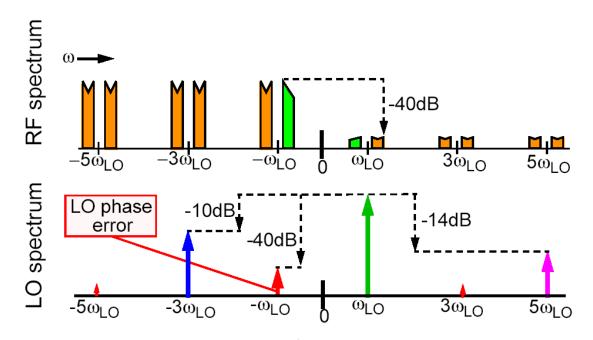

| Fig. 2.8. Harmonic suppression of double quadrature down-converter                          | 23   |

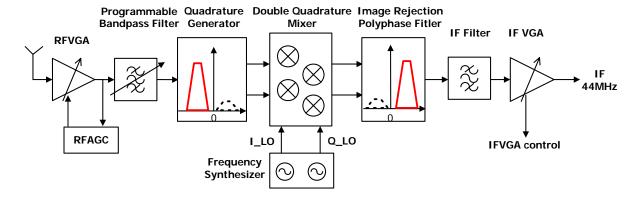

| Fig. 2.9. Double quadrature DTV tuner architecture                                          | 24   |

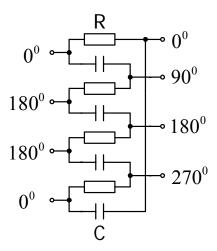

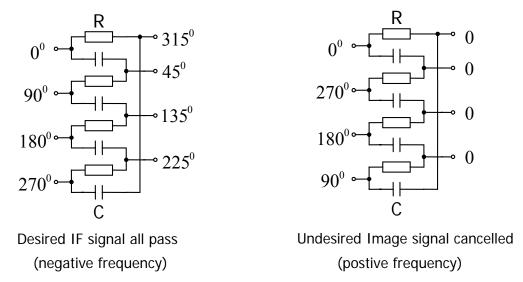

| Fig. 2.10. Single stage passive polyphase filter                                            | 26   |

| Fig. 2.11. Schematic of broadband quadrature generator                                      | 27   |

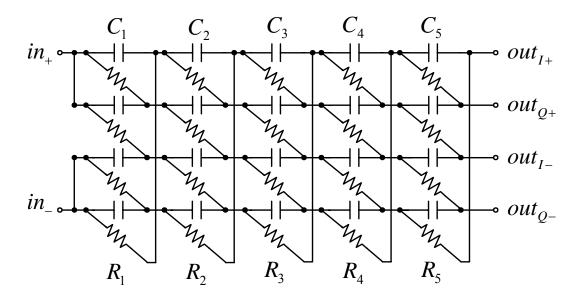

| Fig. 2.12. Frequency response plot of: (a) quadrature generator; (b) image rejection filter | 29   |

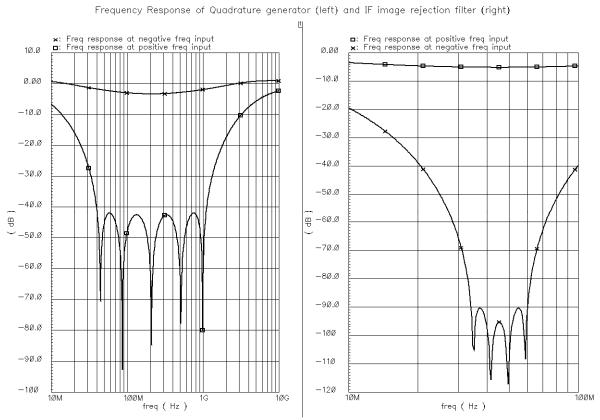

| Fig. 2.13. Quadrature generator Monte Carlo simulation results                              | 30   |

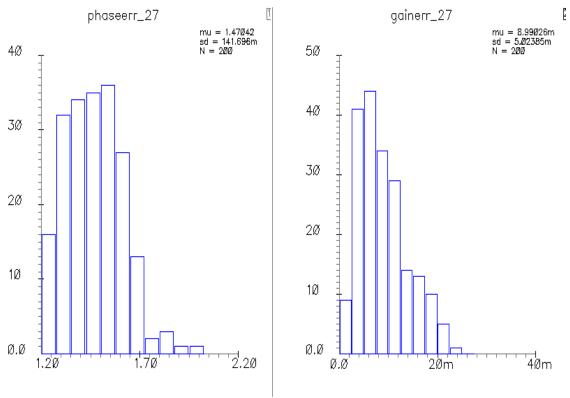

| Fig. 2.14. Image rejection demonstration of single stage passive polyphase filter           | 31   |

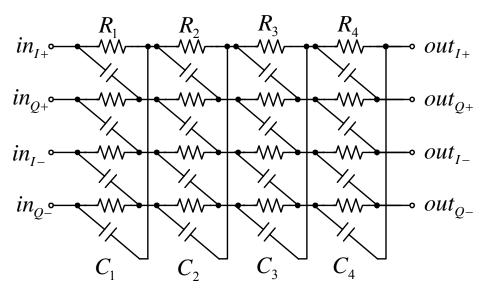

| Fig. 2.15. Image rejection polyphase filter                                                 | 32   |

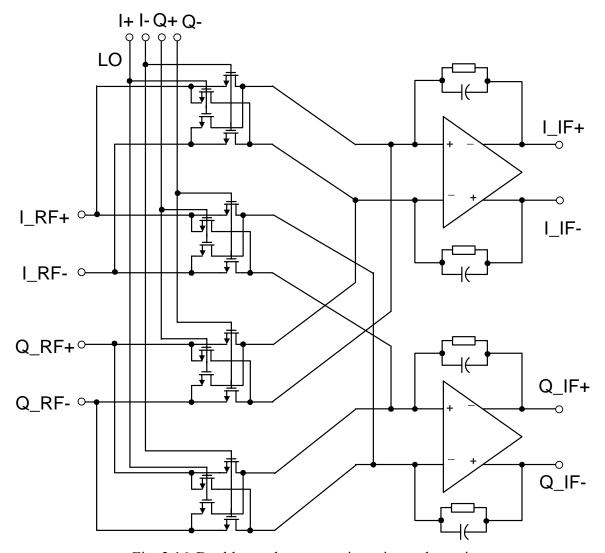

| Fig. 2.16. Double quadrature passive mixer schematic                                        | 33   |

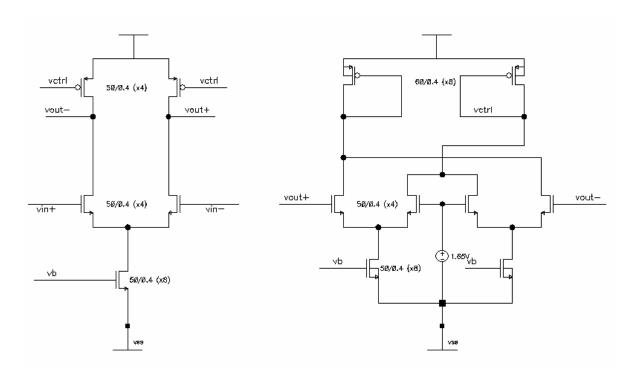

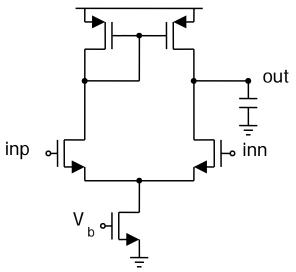

| Fig. 2.17. OTA schematic.                                                                   | 35   |

| I                                                                                                                  | Page |

|--------------------------------------------------------------------------------------------------------------------|------|

| Fig. 2.18. Frequency response of the OTA                                                                           | 36   |

| Fig. 2.19. Inter-stage buffer schematic                                                                            | 38   |

| Fig. 2.20. Overall down-converter noise figure plot.                                                               | 38   |

| Fig. 2.21. Overall down-converter IIP3 plot.                                                                       | 39   |

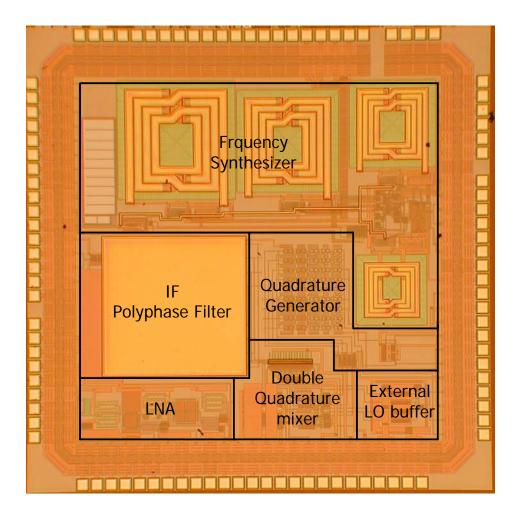

| Fig. 2.22. Photograph of the terrestrial tuner test chip.                                                          | 40   |

| Fig. 2.23. Output spectral plots @ LO 244MHz: (a) -20dBm RF input @ 200MHz; (b) -20dBm RF input @ 288MHz           | 42   |

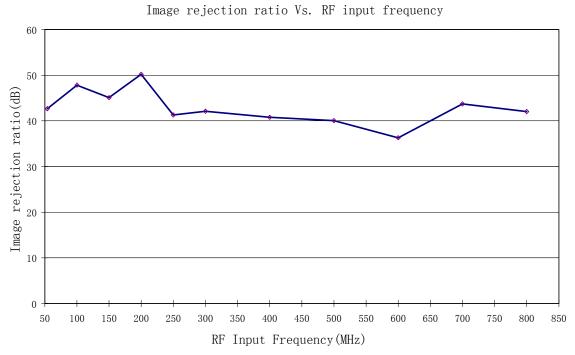

| Fig. 2.24. Measured image rejection ratio vs. frequency                                                            | 43   |

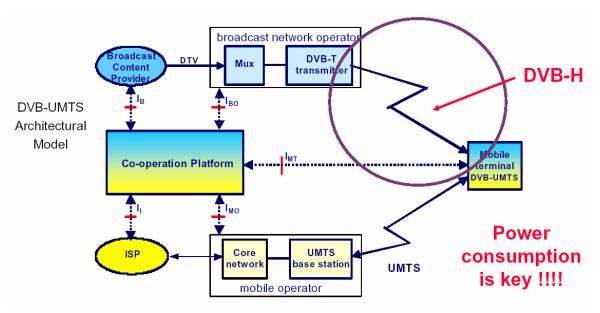

| Fig. 3.1. Mobile DTV applications                                                                                  | 45   |

| Fig. 3.2. DTV for mobile terminal                                                                                  | 47   |

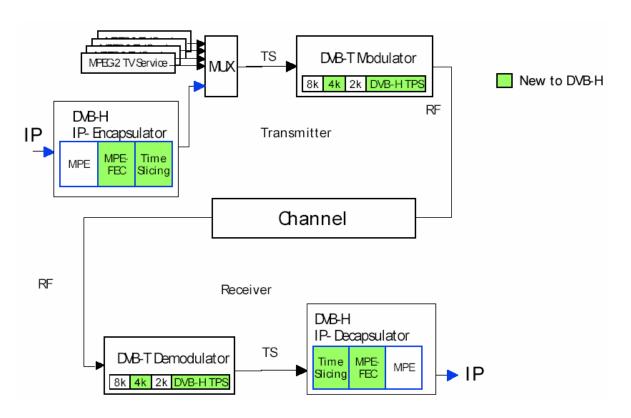

| Fig. 3.3. DVB-H system block diagram                                                                               | 48   |

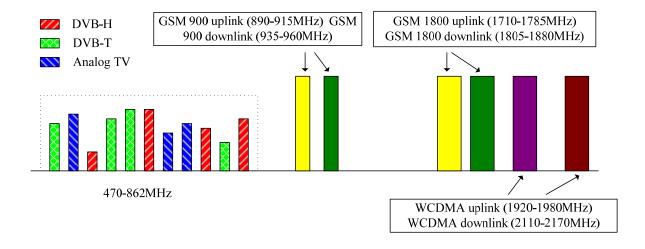

| Fig. 3.4. Spectrum of the DVB-H receiver input                                                                     | 49   |

| Fig. 3.5. Simplified model of DTV receiver.                                                                        | 51   |

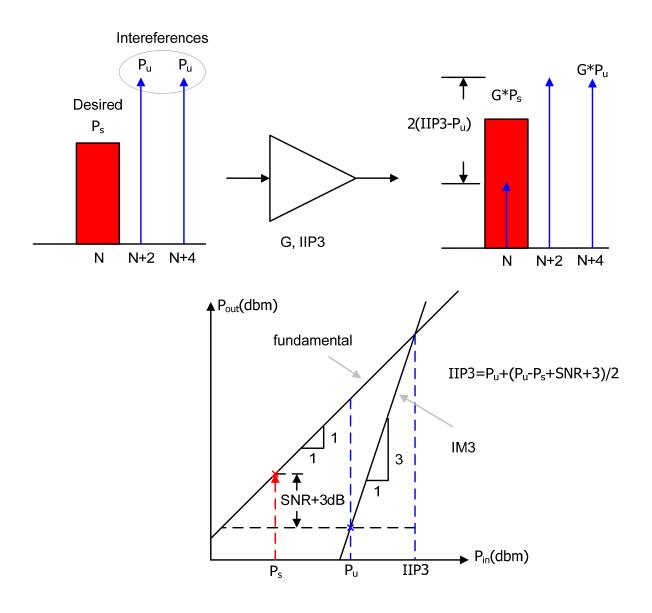

| Fig. 3.6. IIP3 calculation illustration.                                                                           | 54   |

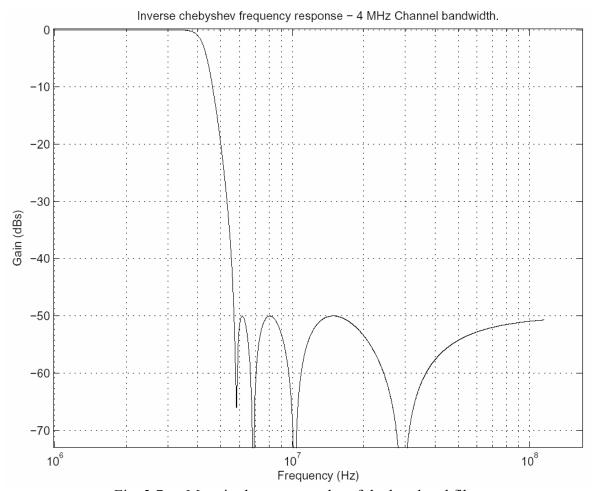

| Fig. 3.7. Magnitude response plot of the baseband filter                                                           | 56   |

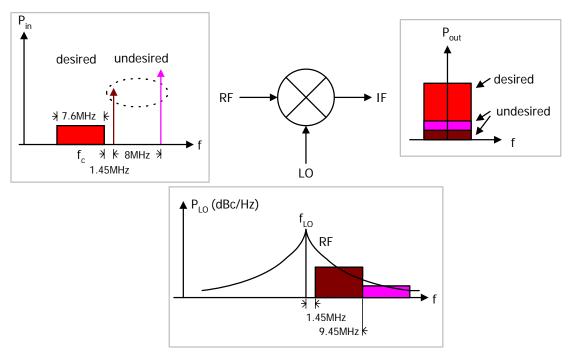

| Fig. 3.8. Phase noise calculation illustration                                                                     | 57   |

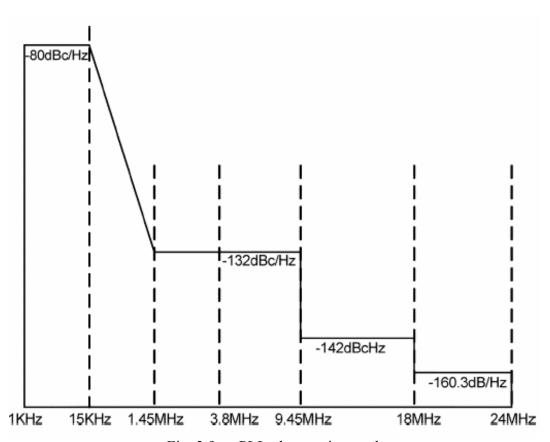

| Fig. 3.9. PLL phase noise mask                                                                                     | 58   |

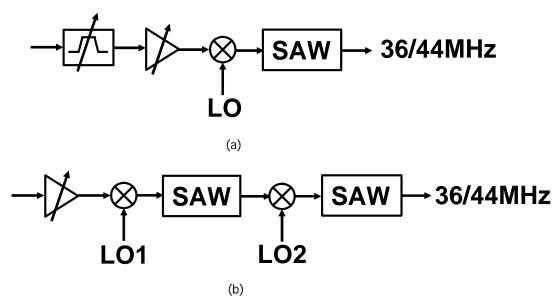

| Fig. 3.10. Conventional TV tuner architectures: (a) single-conversion with RF tracking filter; (b) dual-conversion | 59   |

| Fig. 3.11. Block diagram of direct conversion (zero-IF) DVB-H tuner                                                | 61   |

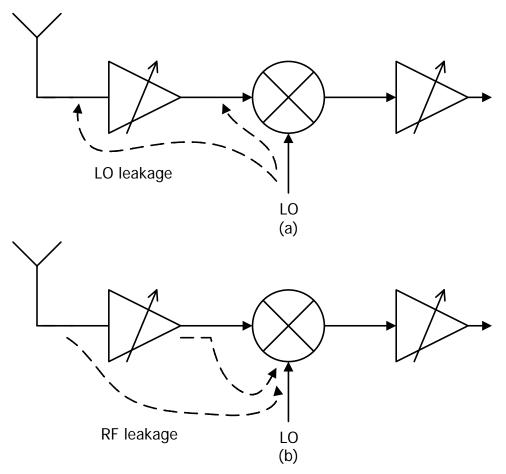

| Fig. 3.12. DC offset introduced due to self mixing                                                                 | 64   |

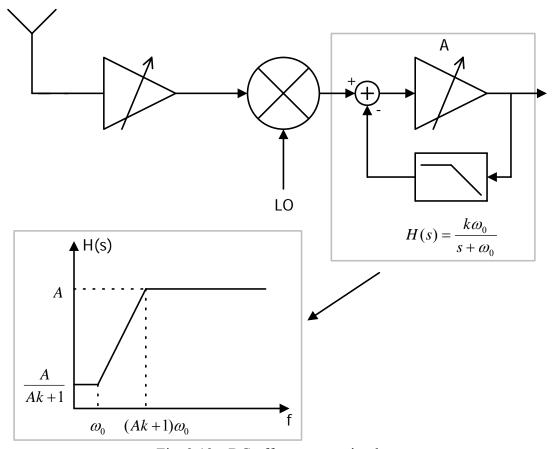

| Fig. 3.13. DC offset suppression loop.                                                                             | 65   |

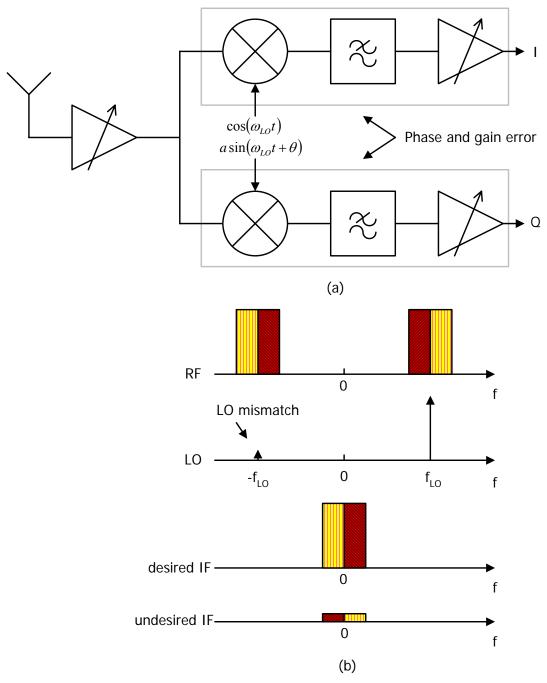

| Fig. 3.14. I/Q mismatch illustration.                                                                              | 67   |

| Page                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

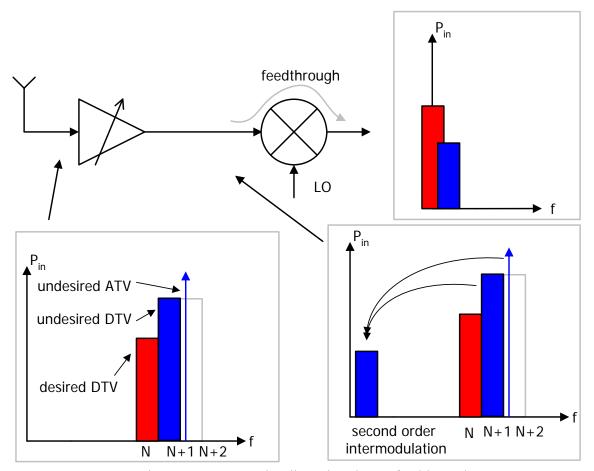

| Fig. 3.15. Even order distortion due to feedthrough                                                                                                                                                                                                                                       |

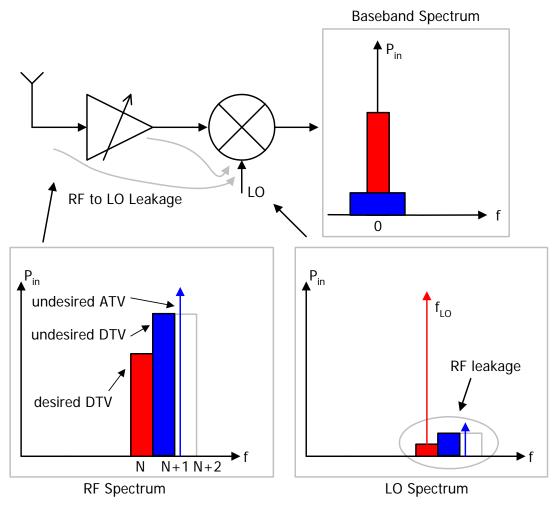

| Fig. 3.16. Even-order distortion due to RF leakage70                                                                                                                                                                                                                                      |

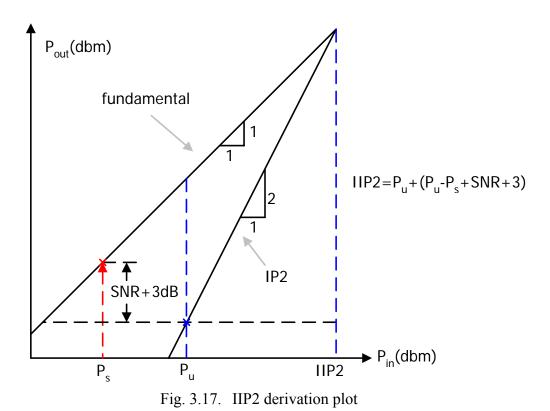

| Fig. 3.17. IIP2 derivation plot                                                                                                                                                                                                                                                           |

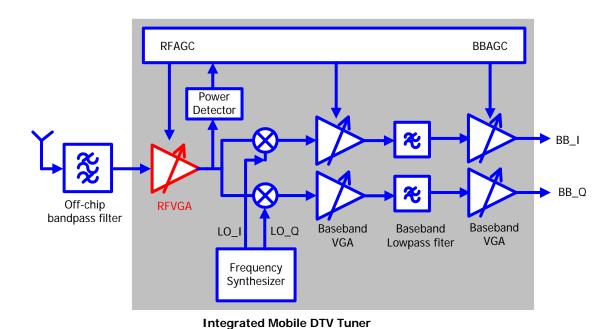

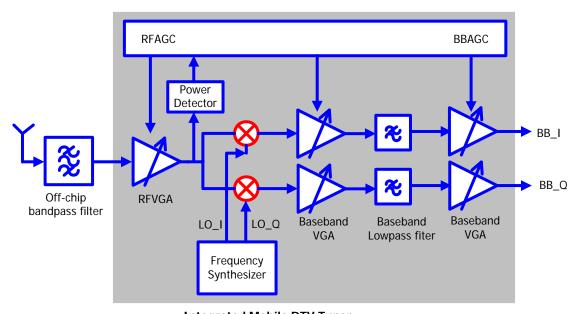

| Fig. 4.1. Mobile DTV tuner architecture                                                                                                                                                                                                                                                   |

| Fig. 4.2. Why the RFVGA is needed                                                                                                                                                                                                                                                         |

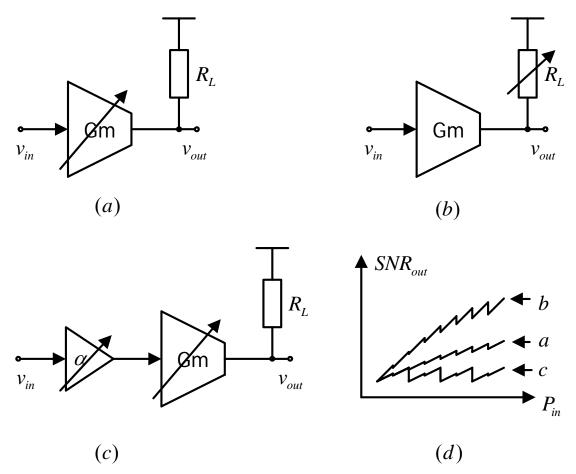

| Fig. 4.3. (a) Variable Gm VGA; (b) Variable load VGA; (c) Pre-attenuation plus variable Gm VGA; (d) Different VGAs' output SNR plots                                                                                                                                                      |

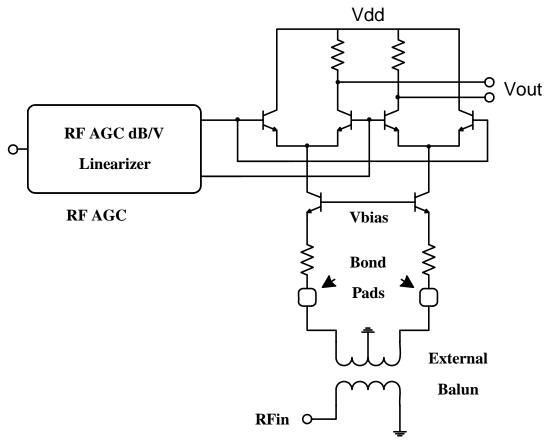

| Fig. 4.4. Schematic of variable-Gm based RFVGA                                                                                                                                                                                                                                            |

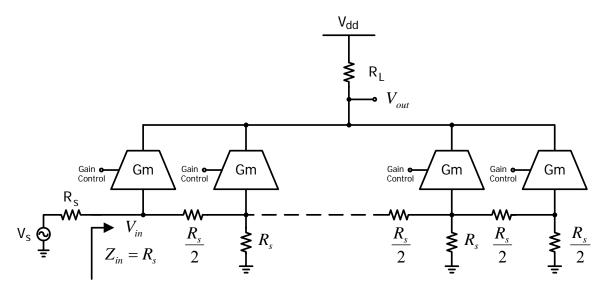

| Fig. 4.5. Block diagram of pre-attenuation type RFVGA (single-ended)                                                                                                                                                                                                                      |

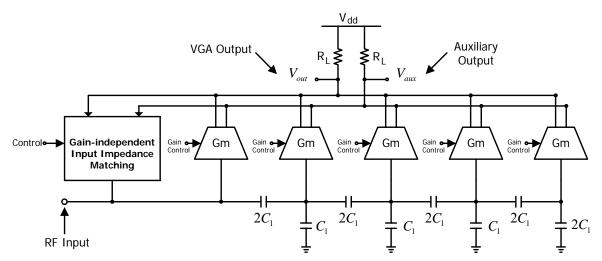

| Fig. 4.6. Block diagram of the proposed RFVGA architecture                                                                                                                                                                                                                                |

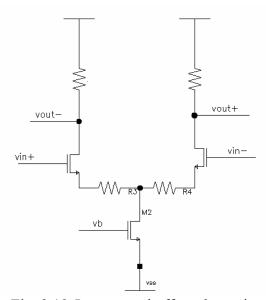

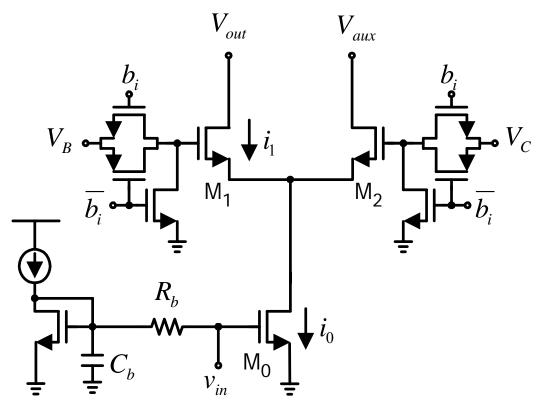

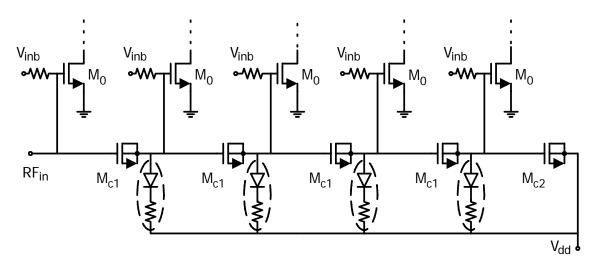

| Fig. 4.7. Simplified schematic of the current-steering Gm stage                                                                                                                                                                                                                           |

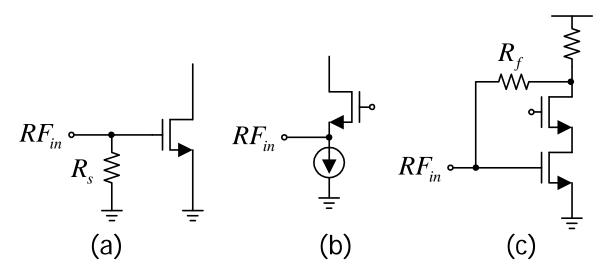

| Fig. 4.8. Broadband impedance matching configurations                                                                                                                                                                                                                                     |

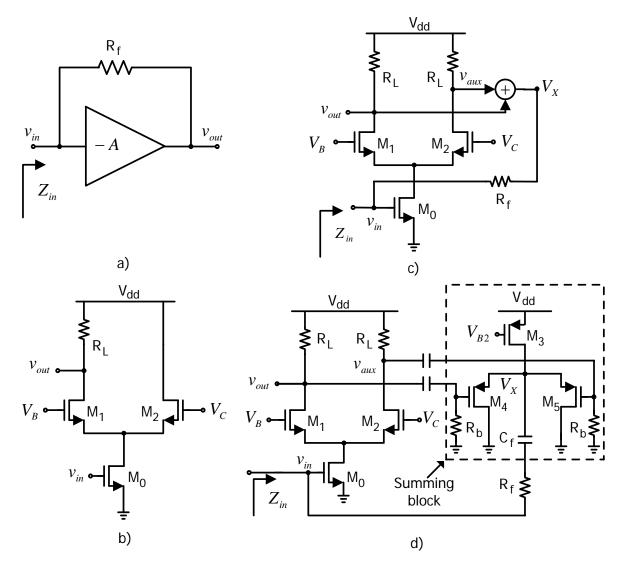

| Fig. 4.9. (a) Block diagram of resistive shunt-feedback input impedance matching; (b) Simplified current-steering VGA schematic; (c) Simplified schematic of the proposed configuration; (d) Circuit implementation of the proposed shunt-feedback input impedance matching configuration |

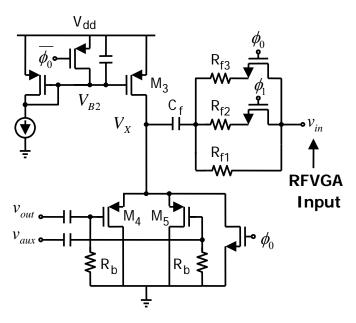

| Fig. 4.10. Schematic of gain-independent input impedance matching block                                                                                                                                                                                                                   |

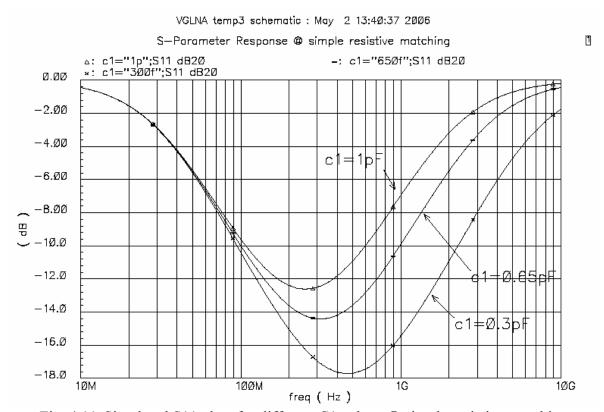

| Fig. 4.11. Simulated S11 plots for different C1 values @ simple resistive matching92                                                                                                                                                                                                      |

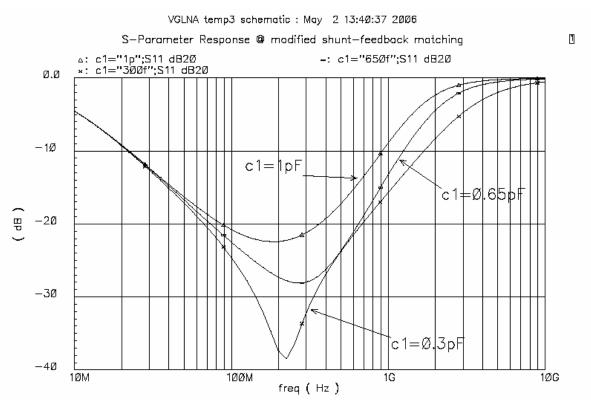

| Fig. 4.12. Simulated S11 plots for different C1 values @ shunt-feedback matching93                                                                                                                                                                                                        |

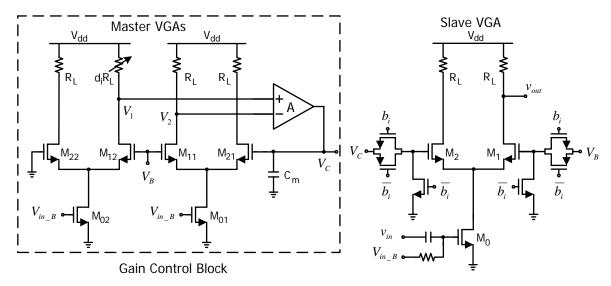

| Fig. 4.13. Schematic of the gain control concept circuit                                                                                                                                                                                                                                  |

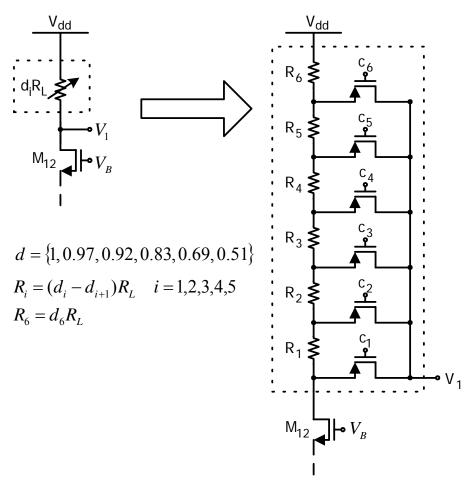

| Fig. 4.14. Schematic of digital control variable resistor implementation                                                                                                                                                                                                                  |

| Fig. 4.15. Schematic of the amplifier used in gain control block                                                                                                                                                                                                                          |

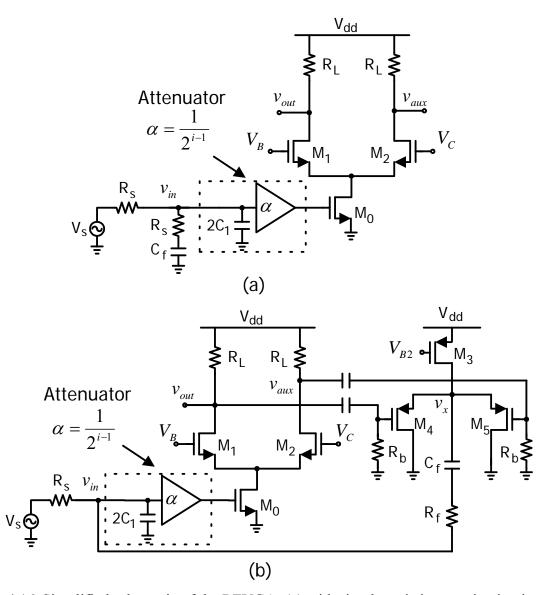

| Fig. 4.16. Simplified schematic of the RFVGA: (a) with simple resistive termination input impedance matching (b) with proposed shunt-feedback input impedance matching                                                                                                                    |

| I                                                                                                                    | Page  |

|----------------------------------------------------------------------------------------------------------------------|-------|

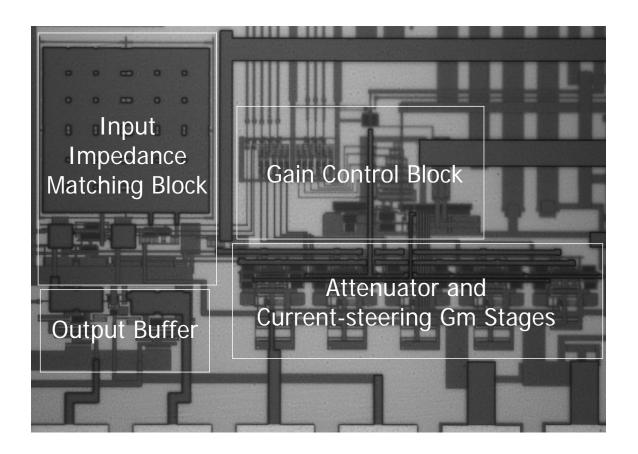

| Fig. 4.17. Photograph of the RFVGA test chip                                                                         | .103  |

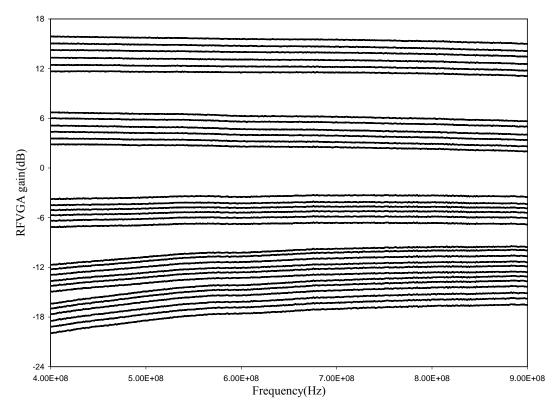

| Fig. 4.18. Measured RFVGA gain vs. frequency                                                                         | . 104 |

| Fig. 4.19. Schematic of the capacitive attenuator with parasitic diodes and resistors                                | .105  |

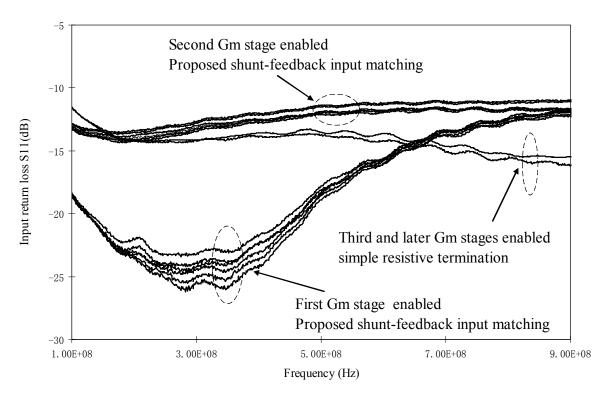

| Fig. 4.20. Measured input return loss (S11) vs. frequency                                                            | .106  |

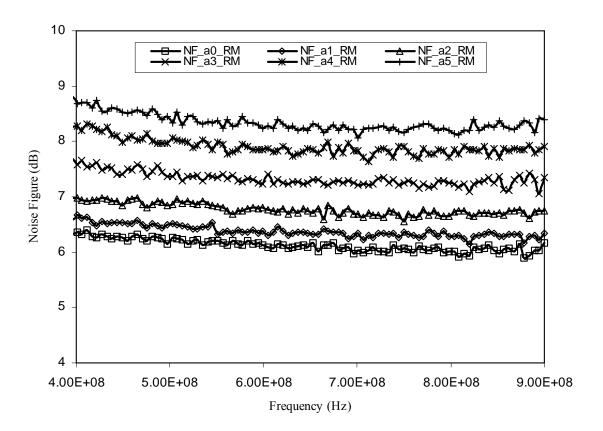

| Fig. 4.21. Measured RFVGA noise figure with simple resistive matching (first six high gain settings)                 | .107  |

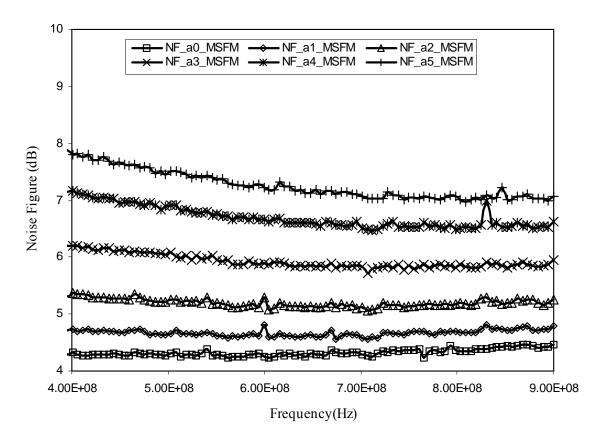

| Fig. 4.22. Measured RFVGA noise figure with modified shunt-feedback matching (first six high gain settings)          | .108  |

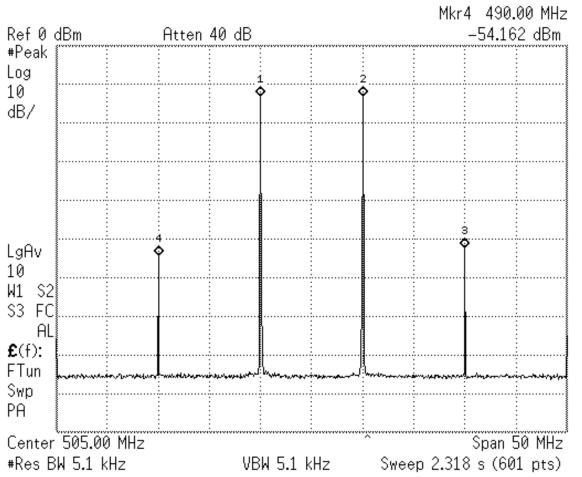

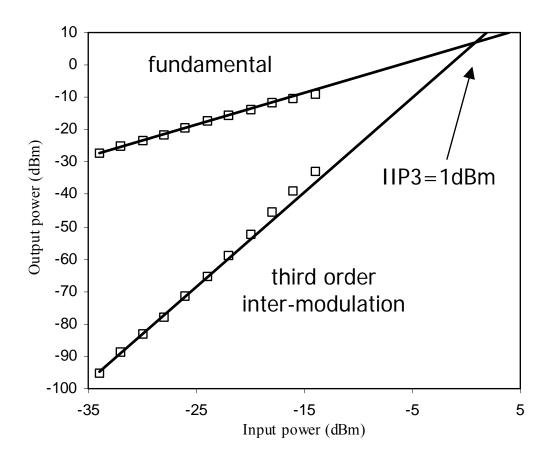

| Fig. 4.23. Output spectral plot for the two tone test @ 500MHz & 510MHz inputs (-20dBm) and the maximum gain setting | .109  |

| Fig. 4.24. IIP3 plot for the two tone test @ 500MHz & 510MHz inputs (-20dBm) and the maximum gain setting            | .110  |

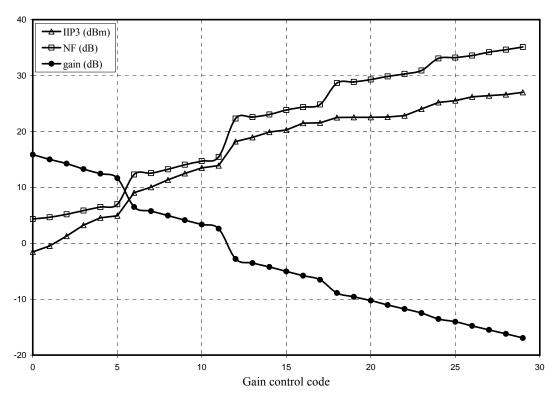

| Fig. 4.25. Measured RFVGA gain, NF and IIP3 vs. gain control setting @ 800MHz                                        | 111   |

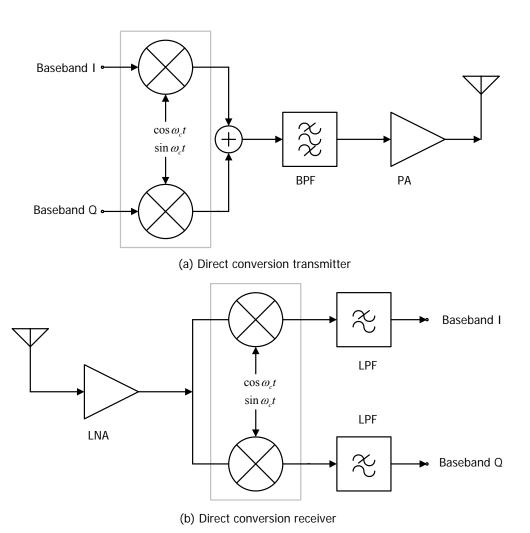

| Fig. 5.1. Block diagram of direct conversion transmitter and receiver                                                | .114  |

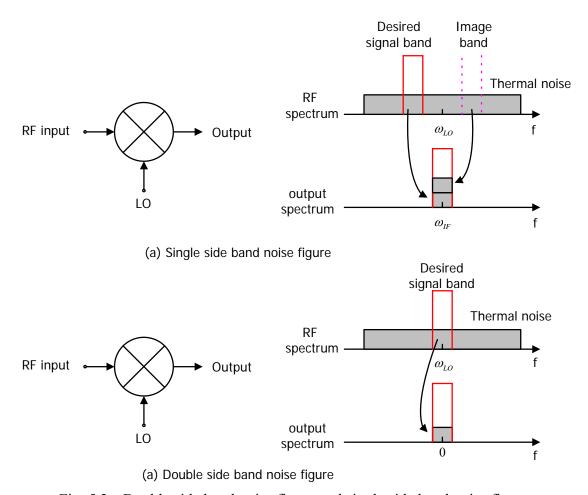

| Fig. 5.2. Double side band noise figure and single side band noise figure                                            | .116  |

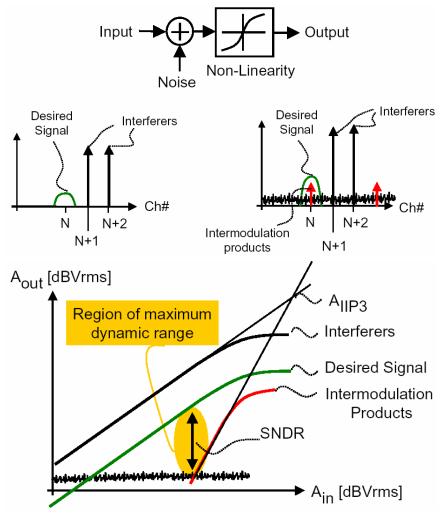

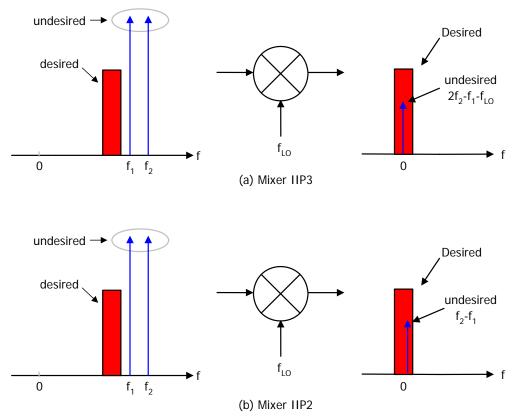

| Fig. 5.3. Illustration of mixer IIP3 and IIP2                                                                        | . 118 |

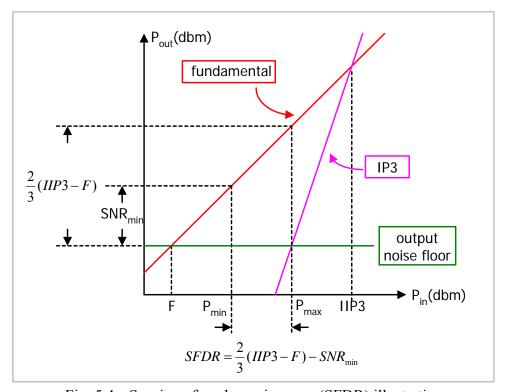

| Fig. 5.4. Spurious-free dynamic range (SFDR) illustration                                                            | .119  |

| Fig. 5.5. DVB-H mobile tuner architecture                                                                            | . 120 |

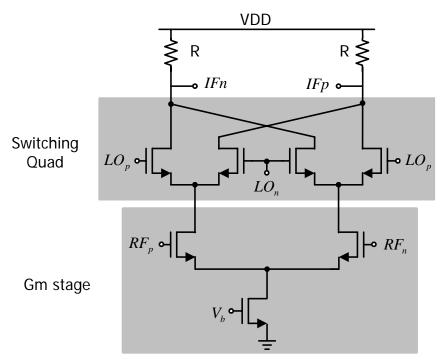

| Fig. 5.6. Gilbert mixer schematic                                                                                    | .124  |

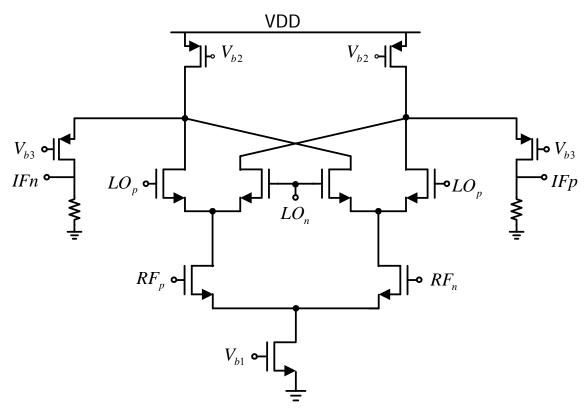

| Fig. 5.7. Schematic of folded-cascode active load Gilbert mixer                                                      | . 125 |

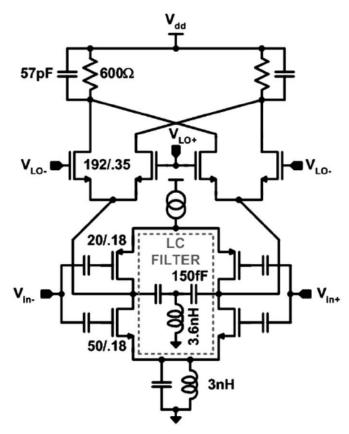

| Fig. 5.8. Schematic of folded-switching mixer                                                                        | .126  |

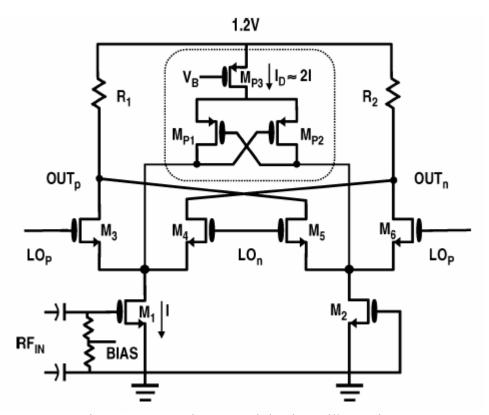

| Fig. 5.9. Dynamic current injection Gilbert mixer                                                                    | 127   |

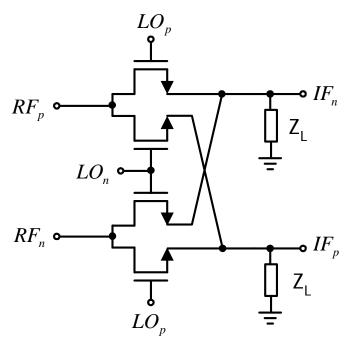

| Fig. 5.10. Double balanced fully differential passive mixer                                                          | .129  |

| Fig. 5.11. Double balanced passive mixer with TIA load                                                               | .130  |

|                                                                     | Page |

|---------------------------------------------------------------------|------|

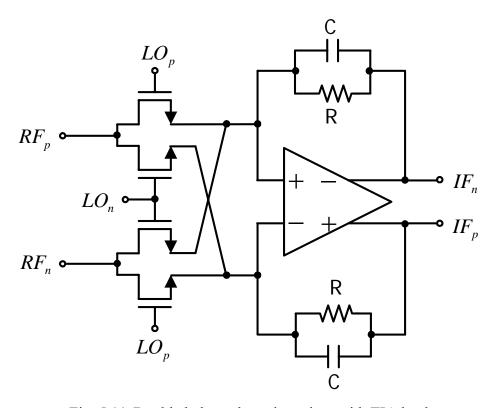

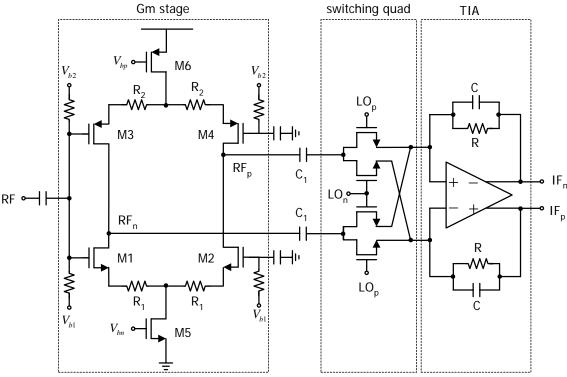

| Fig. 5.12. Current mode passive mixer                               | 132  |

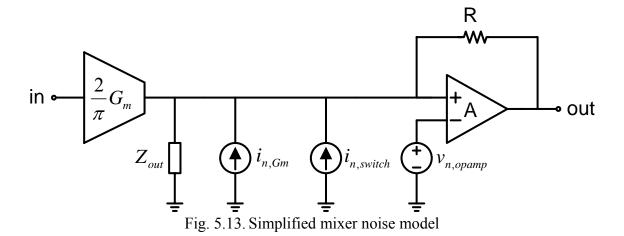

| Fig. 5.13. Simplified mixer noise model                             | 134  |

| Fig. 5.14. Two-stage amplifier schematic                            | 138  |

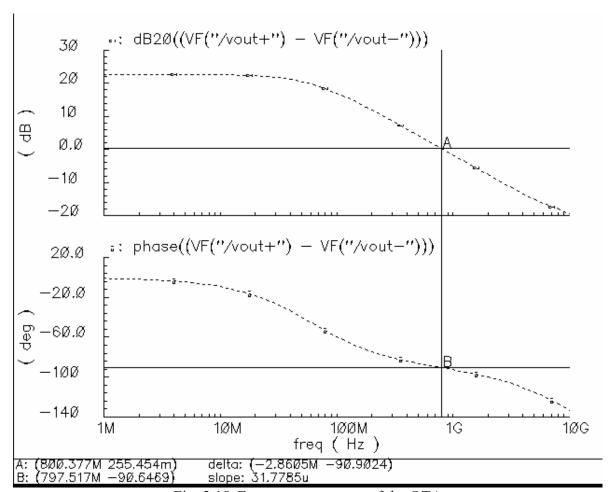

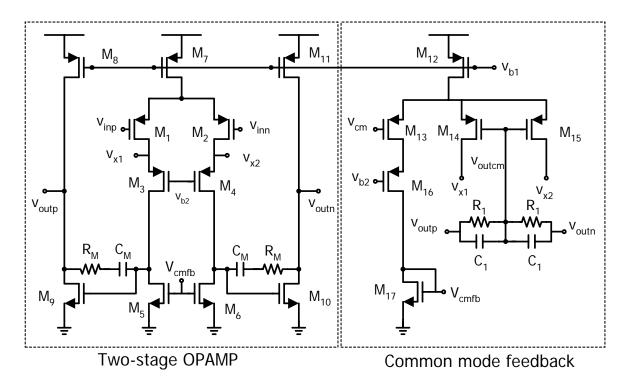

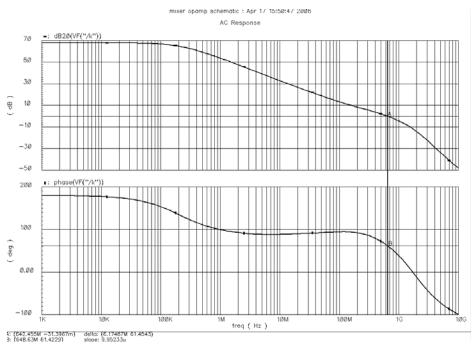

| Fig. 5.15. OPAMP differential-mode open loop frequency response     | 141  |

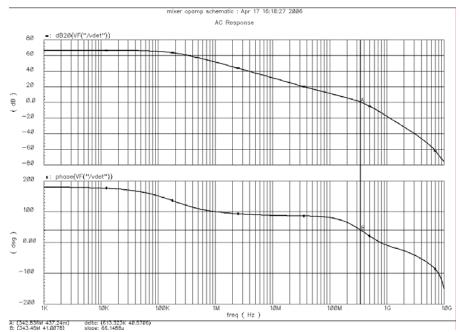

| Fig. 5.16. OPAMP common mode feedback open loop frequency response  | 142  |

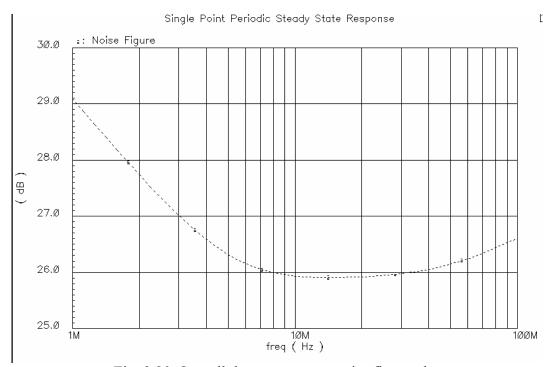

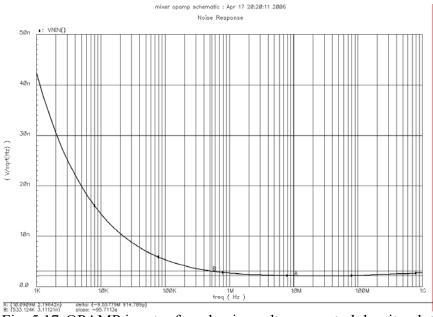

| Fig. 5.17. OPAMP input referred noise voltage spectral density plot | 142  |

# LIST OF TABLES

|                                                                 | Page |

|-----------------------------------------------------------------|------|

| Table 1.1. Summary of terrestrial and mobile DTV standards      | 3    |

| Table 2.1. System specifications for ATSC tuner.                | 16   |

| Table 2.2. Component values of quadrature generator             | 28   |

| Table 2.3. Component values of image rejection polyphase filter | 32   |

| Table 2.4. Prototype measurement summary                        | 43   |

| Table 3.1. Threshold C/N performance                            | 51   |

| Table 3.2. Linearity pattern                                    | 53   |

| Table 3.3. Selectivity patterns                                 | 55   |

| Table 3.4. Block design specifications                          | 72   |

| Table 4.1. Summary of the RFVGA experimental results            | 112  |

| Table 5.1. Mixer design specifications                          | 120  |

| Table 5.2. Gm stage design parameters                           | 137  |

| Table 5.3. OPAMP design parameters                              | 140  |

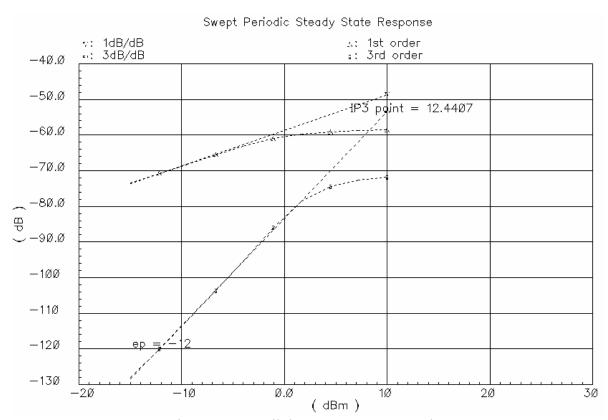

| Table 5.4. Mixer simulation results                             | 143  |

### CHAPTER I

## INTRODUCTION

## 1.1. Digital Television Systems

Television is a very cost-effective system which informs, educates, and entertains all societies around the world. The television system can be simply described by Fig. 1.1. In the transmission side, the TV data including video and audio information is firstly modulated using an efficient modulation scheme and then transmitted. Usually the modulated baseband TV data is up-converted to a predefined radio frequency (RF) band before the transmission. The RF TV signal will be transmitted out from the TV tower station and received by TV receivers. For the broadcasting TV, the transmission channel is air. In the receiver side, the RF TV signal is captured and down-converted to baseband (or low intermediate frequency) by the TV tuner. The demodulator, after the DTV tuner, will complete the data demodulation and feed the signal into the signal processing block (usually digital decoder). Finally, the TV signal will be displayed in the monitor.

In the conventional TV system, the TV data is modulated employing an analog modulation scheme; hence the TV system is called analog television. Analog television broadcasting systems based on NTSC, PAL or SECAM standards have been successfully established in many countries since the middle of the last century. In recent years, due to the development

This dissertation follows the style of IEEE Journal of Solid State Circuits.

of the data compression techniques (like MPEG compression) and digital communication, the digital television system is emerging and will replace analog television system eventually.

Fig. 1.1. Block diagram of the television system

There are multiple advantages for the DTV compared with analog television. DTV not only delivers interference and distortion-free video and audio signals; more importantly it can do so while achieving much higher spectrum efficiency than analog television. DTV can also seamlessly interface with other communication systems, computer networks, digital media,

enabling datacasting and multimedia interactive services; it is a key element of the ongoing digital revolution leading toward the information society [1].

Table 1.1. Summary of terrestrial and mobile DTV standards

|                               | ATSC   | DVB-T  | ISDB-T  | DVB-H   | ISDB-T<br>(Mobile) |

|-------------------------------|--------|--------|---------|---------|--------------------|

| Frequency<br>Range (MHz)      | 54-806 | 47-854 | 470-770 | 470-862 | 470-770            |

| Channel<br>Bandwidth<br>(MHz) | 6      | 8      | 6       | 6/7/8   | 0.43               |

| Modulation<br>Scheme          | 8-VSB  | COFDM  | OFDM    | COFDM   | OFDM               |

| Threshold<br>CNR (dB)         | 15     | 18.7   | 25      | 24.8    | 25                 |

| Sensitivity (dBm)             | -83    | -80    | -75     | -75     | -86                |

Currently multiple DTV standards are used worldwide. In USA, the Advanced Systems Committee (ATSC) developed the 8-VSB standard for the terrestrial DTV [2]; in Europe, the Digital TV Project has finalized the series of DTV standards named as DVB [3]; the ISDB standards were developed by Japan [4]. In addition, China is developing another terrestrial DTV standard, which is expected to be finalized soon [1]. For each series of standards, based on the transmission method, they are classified as terrestrial DTV, cable DTV and satellite DTV. Remarkably, the mobile DTV standards, like DVB-H [5], which is the modified version of the original terrestrial DVB-T standard, have been proposed for the

emerging mobile handset reception and can reduce the average power consumption of the mobile DTV receiver by 90%.

In Table 1.1, the critical transmission parameters of multiple terrestrial and mobile DTV standards are listed. For the DVB-T standard, the threshold carrier to noise ratio (CNR) and sensitivity are defined for 64QAM modulation and 2/3 code rate case. For the ISDB-T standard, the threshold CNR and sensitivity are defined for 64QAM and 7/8 code rate. For the DVB-H mobile standard, the frequency range listed here is only for Europe and the sensitivity is calculated based on 8MHz channel and 64QAM modulation (3/4 code rate). For the ISDB-T mobile standard, only one segment of the 6MHz (totally 13 segments) is used for mobile DTV transmission and the sensitivity is referred to segment power instead of 6MHz channel power.

## 1.2. Digital Television Tuner

Television tuner is the first block of the television receiver, as shown in Fig. 1.1. The functionality of the tuner is to select and down-convert the desired TV channel from RF frequency to DC or a predefined intermediate frequency. Because there are multiple TV transmission methods like terrestrial, cable and satellite, different tuners are required such as terrestrial TV tuner, cable TV tuner and satellite TV tuner. For each kind of tuner, since there are different standards in different regions, it is common to have a tuner specially designed for each region. And since the analog TV will be replaced by digital TV soon, commercially available devices are all DTV tuners. It is important to notice that during the

transition time from analog TV to digital TV, it is mandatory that the tuner has to handle not only digital TV but also analog TV. For example, the market available terrestrial TV tuner for USA has to handle not only ATSC digital TV (ATSC) but also NTSC analog TV.

Fig. 1.2. DTV tuner applications

As discussed before, the tuner is the necessary block for the DTV receiver. More specifically, the tuner can be used in high definition TV (HDTV), standard definition TV (SDTV), set top box (STB), VCR/DVD and even portable TV like PDA or cellphone. These applications are also described in Fig. 1.2. For all of these applications, they have similar design targets, which are low-power and low-cost.

Low-power design can help to reduce the overall power consumption of the DTV receiver. More important, low-power is mandatory for the emerging portable and mobile DTV applications. For example, over 1w power consumption might be acceptable in HDTV or STB but cannot be tolerated in a handset device. Typically, the handset device requires the average power consumption less than 100mW due to limited battery life time, which becomes a design challenge for the tuner industry.

Low-cost means to reduce the bill of material (BOM). It can increase the product profit margin, or alternatively allow more price reduction to strength the market competition. The most efficient way to reduce the cost is to increase the integration level. In the history, bulky can tuners have been used since the invention of the TV. A lot of discrete components including tunable or fixed coils have to be used in the tuner design. Those components usually vary a lot with process and temperature variations, which requires extra labor to tune the parameters. In addition, the bulky area limited its usage in many applications especially the emerging mobile market. On the contrast, the manufactures of highly integrated silicon tuners are much easier and they require much less extra labor, which reduces the overall cost dramatically. In addition, a tiny integrated chip reduces the area a lot compared with the can tuner. Therefore, with the development of silicon technology, there is no doubt that the fully integrated tuner will replace the can tuner eventually just as the transistors replaced the vacuum tube.

For the available integrated DTV tuners, there are still a lot of remaining challenges to achieve low-power low-cost design. For example, most of commercial integrated tuners are

implemented with expensive technologies like SiGe BiCMOS technology instead of standard massive volume CMOS technology. By using CMOS technology, we can reduce the fabrication cost, especially when considering the future receiver system integrated on chip (SOC). Therefore, CMOS DTV tuner design is the main research target for this dissertation, including system level architecture modifications and block level novel circuit implementations to reduce the power consumption and achieve fully integration.

## 1.3. Research Focus and Dissertation Overview

Fig. 1.3. Dual-conversion tuner architecture for ATSC terrestrial tuner

Current commercially available DTV tuners are usually implemented using dualconversion architecture, as shown in Fig. 1.3. In this configuration, the incoming RF signal is first up-converted to a RF frequency (usually more than 1 GHz) and then down-converted to the intermediate frequency (like 44MHz). This approach has multiple drawbacks. First of all, usually two off-chip SAW filters are required in the implementation. This limits the integration level and adds extra cost. Second, due to the up-and-down conversions, it consumes over 1w power consumption and cannot be used for low-power architecturs.

In order to achieve the fully integration and low power, a novel tuner architecture has been employed, which will be addressed in the second chapter. Based on that architecture, the main system and block specifications are derived for the ATSC application. The critical RF front-end blocks are implemented in main stream CMOS technologies. Proper circuit configurations and design trade-offs are discussed and the experimental results are given at the end of the second chapter. With this novel implementation, the SAW filter is avoided and fully integration can be achieved. In addition, the power consumption can be reduced dramatically from over 1 watt to less than 0.5 watt.

Recently, the DTV tuner for mobile application is strongly demanded by the wireless market. Compared with the terrestrial TV tuner, the power consumption and area are more critical due to the feature of handset devices. A direct conversion (zero IF) tuner architecture has been proposed and will be presented in the chapter III. System and block specifications will be derived based on the DVB-H application. In addition, the system level design issues like DC offset, I/Q mismatch, even-order distortion and flicker noise are addressed.

RF variable gain amplifier (RFVGA) is one of the most critical blocks for the tuner application, which adjusts the amplifier gain to achieve maximum system dynamic range. In general, this block requires extremely high dynamic range because this is the first block for the tuner system. To achieve high dynamic range, low noise high linearity and wide gain range are required. In addition, as the RF input block, it requires good input impedance matching, which usually adds extra design constrains and degrades its dynamic range. In order to overcome these issues, a novel RFVGA architecture has been proposed. In the fourth chapter, the RFVGA design including architecture design, block implementation, experimental results are completely presented. The RFVGA is implemented in CMOS technology and suitable for mobile DTV applications.

For the tuner application, high dynamic range mixer is another critical RF block. It requires extremely high linearity, high gain and moderate noise figure, which is difficult to achieve for low voltage CMOS implementations. In chapter V, a novel current-mode passive mixer design will be presented. It can achieve the high dynamic range specifications and contribute very small amount of flicker noise. More importantly, the proposed topology can work properly in low power supply, which is believed to be a promising candidate for the future scaled-down technologies.

In chapter VI, the dissertation is summarized and the main conclusions are given.

#### CHAPTER II

#### LOW POWER FULLY INTEGRATED CMOS DTV TUNER FRONT-END

#### FOR ATSC TERRESTRIAL BROADCASTING

## 2.1. ATSC Terrestrial DTV Tuner System

8-VSB is the modulation scheme for USA digital television broadcasting. According to ATSC digital television standard [2], digital television information including video data and audio data are compressed into MPEG-2 format; the digital data is modulated with 8-VSB and up-converted to the desired RF channel for the transmission. Digital television uses the same frequency plan as conventional analog TV broadcasting, which is from 54MHz to 806MHz. For the receiver design, the major difference between analog TV and digital TV is the threshold SNR requirement for the demodulator. Due to noise-like flat spectrum (digital television) instead of discrete carriers (analog television); the SNR for DTV only needs 15dB, which will potentially make it suitable for wide coverage broadcasting.

Fig. 2.1 shows the input spectrum for the ATSC DTV tuner. During the transition time from analog TV to DTV, both analog TV channel and digital TV channel must be received by the tuner. After the DTV fully replaces analog TV, only DTV channels will be observed at the tuner input. For the desired DTV channel, the signal power (average power) can vary from -81dBm to -20dBm. In the worst case, the maximum power can be much higher than -20dBm. However, for a practical purpose, -20dBm is considered for the design. If the tuner

average output power level is set as 0dBm, the tuner needs provide the power gain from 81dB to 20dB.

Fig. 2.1. ATSC DTV tuner input spectrum

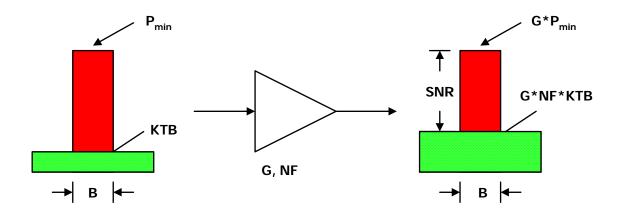

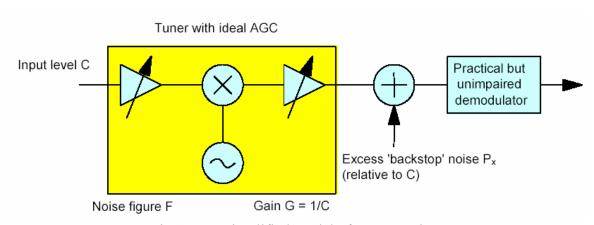

Fig. 2.2. Noise figure calculation plot

One of the critical parameters for the tuner system is noise figure, as shown in Fig. 2.2.  $P_{\min}$  is the minimum input power level (also called sensitivity). kT is the product of Boltzmann

constant and absolute temperature, which is -173.8dBm/Hz in the normal room temperature (300K). *B* is the channel bandwidth, which is 6MHz for ATSC standard. *G* and *NF* are the gain and noise figure of the tuner, respectively. The noise figure is calculated so that the minimum output signal to noise ratio above the threshold (15dB here). Therefore, noise figure can be calculated as below

$$NF(dB) = P_{\min}(dBm) + 173.8(dBm) - 10\log(B) - SNR$$

(1)

The calculated noise figure will be around 10dB.

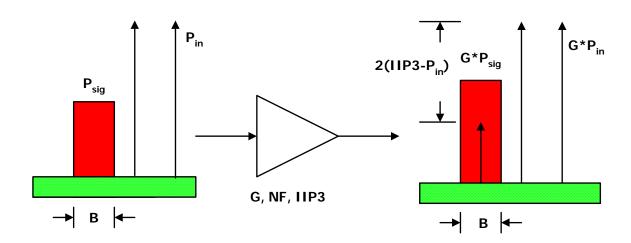

Fig. 2.3. IIP3 calculation plot

Another critical issue for the tuner design is linearity. There are many parameters required to characterize the non-linearity performance. The typical parameters are weak non-linearity specification IIP3 (input referred third order intermodulation intercept point) and strong non-linearity specification  $P_{1dB}$  (input referred 1dB compression point). In addition,

there are other specifications required such as CSO (composite second order distortion) and CTB (composite triple beat distortion) required in practical applications like cable TV. However, there are direct relationships between these specifications and the normal distortion specifications [6]. Therefore, those specifications are neglected for the design point of view. In addition, there is also a relationship between IIP3 and  $P_{1dB}$  [7]. Therefore, only IIP3 specification is required to fully characterize the system non-linearity performances.

Fig. 2.3 shows the IIP3 calculation plot, where the power level of the (N+1) and (N+2) adjacent channels is  $P_{in}$  and the power level of the desired channel is  $P_{sig}$ . The protection ratio is defined as  $P_{in}/P_{sig}$ . The adjacent interference channels will create third order intermodulation product due to the tuner non-linearity and the product falls within the desired channel. To ensure that the output SNR is above the threshold when considering the inter-modulation product, the IIP3 must satisfy the following equation

$$IP3 = \frac{2P_{in} + PR + SNR + 3}{2} \tag{2}$$

where 3 is the 3dB margin used in the derivation. For ATSC application, in the worst case, the protection ratio can be more than 40dB [2]. If considering the maximum interference power level is -20dBm, it results in IIP3=9dBm. Under this condition, the desired signal power level is around -60dBm.

In addition to those gain, noise and linearity specifications, the selectivity is also important. The tuner needs to attenuate the interference channels enough at the output so that the analog to digital converter in the demodulator is not saturated. In the worst case, the tuner needs to provide over 50dB attenuation for the adjacent channel, which defines the baseband filter requirement.

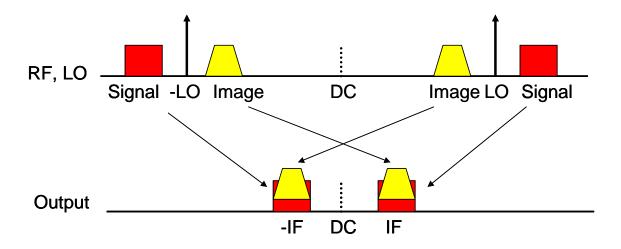

Fig. 2.4. Illustration of image problem during down-conversion in low-IF tuner

Currently, the commercial ATSC tuner needs to provide a 44MHz output, which ensures the tuner compatible with conventional demodulator baseband chip. Although this requirement can be changed in future generations, 44MHz IF is still used for this research. Therefore, there will be image issues to be solved, as shown in Fig. 2.4. For typical low-IF receiver, after the down-conversion, the image channel will be down-converted to the same frequency as signal frequency and degrades the output signal quality. In this specific application, because the final intermediate frequency is 44MHz, the image channel is 88MHz away from the desired channel; the required image rejection ratio is usually over

60dB. This image rejection requirement is the critical factor for the tuner architecture design [8], which will be discussed in the next section.

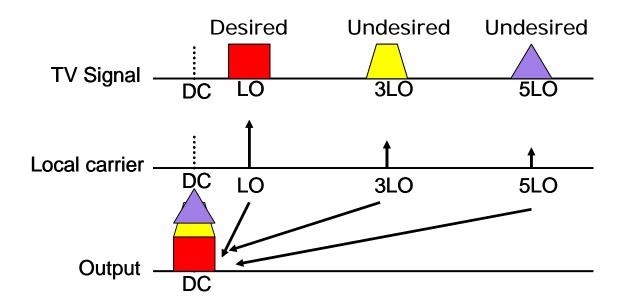

Fig. 2.5. Illustration of harmonic mixing in zero-IF tuners

In addition to image rejection issue, the tuner also has harmonic mixing issue, as illustrated in Fig. 2.5. For the zero-IF tuner, if the LO signal has some harmonic components, those harmonics will mix with the in-band interference channels and generate the undesired product in the baseband, which is called harmonic mixing issue. It is interesting to note that it also matters for low-IF architecture due to the broadband nature of the TV signal. For ATSC application, over 60dB harmonic suppression ratio is required.

From the above discussions, the overall tuner specifications are summarized and listed in Table 2.1.

Table 2.1. System specifications for ATSC tuner

| Parameters              | Value                       |  |

|-------------------------|-----------------------------|--|

| Channel bandwidth       | 6MHz                        |  |

| DTV frequency range     | 54MHz to 806MHz             |  |

| Input power             | -81 dBm to -20 dBm          |  |

| Output range            | $1 V_p @ 500\Omega = 0 dBm$ |  |

| Intermediate Frequency  | 44 MHz                      |  |

| System gain range       | 81 dB to 20 dB              |  |

| NF                      | 10 dB                       |  |

| IIP3                    | 9 dBm                       |  |

| Minimum SNR             | 15 dB                       |  |

| Channel selection ratio | 50 dB                       |  |

| Image rejection Ratio   | 60 dB                       |  |

# 2.2. Double Quadrature Down-conversion Architecture

Nowadays the most popular tuner architectures employ either the single-conversion (with bulky off-chip tracking filter) or the dual-conversion; both tuner architectures are shown in Fig. 2.6. As shown in Fig. 2.6 (a), the center frequency of the tracking filter is set according to the desired channel frequency and the desired channel is pre-selected. After this tracking filter, the image channel is attenuated and single down-conversion architecture can be used without huge image rejection ratio requirement. After the down-conversion, an off-chip SAW filter is used to achieve the desired selectivity. Because of the tracking filter, the tuner architecture is simplified. However, the tracking filter has to be programmable from

50MHz to 800MHz and it is not practical to implement it on-chip; therefore, this architecture is not suitable for integrated tuner solution.

Fig. 2.6. Typical TV-Tuner architectures (a) single-conversion; (b) dual-conversion

In the dual-conversion architecture, as depicted in Fig. 2.6 (b), the desired channel is first up-converted to a high inter-mediate frequency like 1.1GHz, pre-selected by an off-chip high-Q bandpass SAW filter and then down-converted to the standard 44MHz frequency. In the first up-conversion, the frequency of the image channel is out of band and not relevant. In the second down-conversion, the image channel is fixed and 88MHz away from the desired channel. The high-Q off-chip SAW filter can attenuate this image channel by more than 30dB; the second image rejection quadrature mixer also provides more than 30dB image rejection. Therefore, over 60dB image rejection ratio can be achieved without major challenges. Without the need of bulky tracking filter, the tuner has more compact size compared with Fig. 2.6 (a). The dual-conversion architecture is the most popular solution for market available integrated DTV tuners [8]-[10]. The main drawbacks for this architecture are power consumption and requirement of off-chip SAW filter. Due to the high frequency up-conversion, the circuits work at higher frequencies (over 1GHz) and the overall tuner power consumption is usually over 1W. Unfortunately, it is hard to design an on-chip filter to replace the SAW filter and the tuner cannot be fully integrated. These two drawbacks limit this architecture's usage for future low power low cost tuner design.

In both architectures shown in Fig. 2.6, the image rejection is the key consideration. The high image rejection specification is achieved by the filtering, either variable frequency tracking filter or fixed frequency SAW filter. In principle, the image can also be rejected if image cancellation architectures like Hartley and Weaver architectures are used [11].

However, those architectures suffer from I/Q mismatch and it is not possible to achieve 60dB image rejection ratio without the use of sophisticated calibration schemes [12]. The main principle and limitation for the conventional image cancellation architecture are discussed below.

Fig. 2.7. (a) Single quadrature down-converter; (b) Double quadrature down-converter

The typical quadrature down-converter is shown in Fig. 2.7 (a), where the RF input is mixed with two quadrature mixers and the quadrature outputs of the mixer are processed by

the image rejection polyphase filter. For the analysis, the RF input can be expressed as  $A_{RF}\cos(\omega_{RF}t)+A_{IM}\cos(\omega_{IM}t)$ ; the ideal quadrature LO signals can be described as  $A_{LO}\cos(\omega_{LO}t)$  and  $A_{LO}\sin(\omega_{LO}t)$ .  $A_{RF}$ ,  $A_{IM}$  and  $A_{LO}$  are the amplitudes of desired RF signal, image signal and LO signal, respectively. For the simplicity, the quadrature LOs can be combined and viewed as a complex LO signal  $A_{LO}e^{j\omega_{LO}t}$ . Thus the quadrature output of the mixer can also be expressed as  $\left[A_{RF}\cos(\omega_{RF}t)+A_{IM}\cos(\omega_{IM}t)\right]A_{LO}e^{j\omega_{LO}t}$ .

If  $\omega_{IF} = \omega_{LO} - \omega_{RF}$ , and ignoring the high frequency components ( $\omega_{RF} + \omega_{Lo}$  and  $\omega_{IM} + \omega_{LO}$ ), the output can be further simplified as  $\frac{1}{2}A_{RF}A_{LO}e^{j\omega_{IF}t} + \frac{1}{2}A_{IM}A_{LO}e^{-j\omega_{IF}t}$ . Therefore, after the down-conversion the desired RF signal and undesired image signal are separated as positive IF and negative IF. The polyphase filter after the mixer can eliminate the negative frequency components and keep the positive frequency ones only. Usually image rejection ratio is defined as  $\frac{P_{image}}{P_{signal}}$ , where  $P_{image}$  is the image signal power at the final output and  $P_{signal}$  is the desired signal power at the output. Therefore, the overall image rejection ratio

However, practical devices mismatches and process parameter tolerances limit drastically its performance. Fig. 2.7 (a) graphically shows the effect of the LO quadrature mismatch. In the ideal case, the spectrum of the complex LO will be only one tone (positive LO); the mismatch of the LOs generate an undesired negative LO component. This undesired

only depends on the attenuation ratio provided by the polyphase filter.

negative LO mixes with undesired positive image signal and the product falls in desired positive IF frequency, which cannot be filtered away by the polyphase filter. Even if the polyphase filter has infinite attenuation, the achievable image rejection ratio is still limited as

$$IRR \approx \frac{1}{4} \left[ \left( \frac{\Delta A}{A} \right)^2 + \left( \tan(\Delta \Phi) \right)^2 \right]$$

(3)

where  $\Delta A$  is the overall gain mismatch between the I/Q paths and A is the nominal gain,  $\Delta \Phi$  is the overall phase imbalance in radians. Both  $\Delta A$  and  $\Delta \Phi$  are determined by the LO and mixer's mismatches as shown below

$$\frac{\Delta A}{A} \approx \frac{\Delta A_{LO}}{A_{LO}} + \frac{\Delta G_{mixer}}{G_{mixer}}$$

$$\tan(\Delta \Phi) \approx \tan(\Delta \Phi_{LO}) + \tan(\Delta \Phi_{mixer})$$

(4)