# DESIGN AND IMPLEMENTATION OF A FREQUENCY SYNTHESIZER FOR AN IEEE 802.15.4/ZIGBEE TRANSCEIVER

A Thesis

by

### RANGAKRISHNAN SRINIVASAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

May 2006

Major Subject: Electrical Engineering

### DESIGN AND IMPLEMENTATION OF A FREQUENCY SYNTHESIZER

#### FOR AN IEEE 802.15.4/ZIGBEE TRANSCEIVER

A Thesis

by

### RANGAKRISHNAN SRINIVASAN

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved by:

| Co-Chairs of Committee, | Edgar Sánchez-Sinencio   |

|-------------------------|--------------------------|

|                         | José Silva-Martinez      |

| Committee Members,      | Shankar P. Bhattacharyya |

|                         | Charles S. Lessard       |

| Head of Department      | Costas P. Georghiades    |

May 2006

Major Subject: Electrical Engineering

#### ABSTRACT

Design and Implementation of a Frequency Synthesizer for an IEEE 802.15.4/Zigbee Transceiver. (May 2006) Rangakrishnan Srinivasan, B.E. (Hons.), Birla Institute of Technology & Science, Pilani, India Co-Chairs of Advisory Committee: Dr. Edgar Sánchez-Sinencio Dr. José Silva-Martinez

The frequency synthesizer, which performs the main role of carrier generation for the down-conversion/up-conversion operations, is a key building block in radio transceiver front-ends. The design of a synthesizer for a 2.4 GHz IEEE 802.15.4/Zigbee transceiver forms the core of this work. This thesis provides a step-by-step procedure for the design of a frequency synthesizer in a transceiver environment, from the mapping of standard-specifications to its integrated circuit implementation in a CMOS technology.

The results show that careful system level planning leads to high-performance realizations of the synthesizer. A strategy of using different supply voltages to enhance the performance of each building block is discussed. A section is presented on layout and board level issues, especially for radio-frequency systems, and their effect on synthesizer performance. The synthesizer consumes 15.5 mW and meets the specifications of the 2.4 GHz IEEE 802.15.4/Zigbee standard. It is capable of 5 GHz operation with a VCO sensitivity of 135 MHz/V and a tuning range of 700 MHz. It can be seen that the adopted methodology can be used for the design of high-performance frequency synthesizers for any narrow-band wireless standard.

## **DEDICATED TO**

Raga Bhairavi – Mother Goddess Music of Baba Ali Akbar Khan My Gurus

Amma, Appa and Chinna

#### ACKNOWLEDGMENTS

So many people come into our lives to provide valuable lessons, only to proceed in their own ways. I am fortunate and blessed to have had a highly enriching graduate study experience at Texas A&M University. The varied mutual planes of interactions and the deepest of resonance with a select few made my life at Texas A&M all the more special.

Dr. Edgar Sanchez-Sinencio has been a wonderful advisor, mentor, and guide. There have been times when I was straying from the correct path. His timely words of advice helped me a lot. He always made himself available whenever I needed his guidance the most. He helped me decide on what I wanted to do after my MS. He provided support, both financially and emotionally, during my MS. Not only technically, but I also learned a lot about life in general from him.

I am grateful to Dr. Jose Silva-Martinez for being a co-chair of my MS committee and for providing technical guidance when necessary. His words of advice during chaotic times also helped me a lot. I am thankful to Dr. Shankar P. Bhattacharyya and Dr. Charles S. Lessard for being members of my MS committee. Dr. Aydin Karsilayan provided technical support and equipment during the PCB manufacturing phase. Ella Gallagher, with her cheerful presence, made a significant difference too. I thank them all.

I also acknowledge the support of Silicon Laboratories, Austin, TX for the fabrication of the chip. The design review at Silicon Laboratories was a huge learning experience for me. I was fortunate to interact with Dr. Augusto Marques and Dr. Alan Westwick; and the technical discussions with them were extremely invaluable. I am also grateful to Dr. Maher Abuzaid of Texas Instruments, Dallas, and Dr. Mathew B.

Shoemake of Wiquest, Dallas for providing their testing lab facilities during the characterization of the synthesizer. Dr. Bruce McNeill and Mr. John Schuler of Agere Systems provided me with their support during the final stages of the thesis preparation. Further, Bharath provided timely computer support. I thank them all.

Dr. Sung Tae Moon, Dr. Ari Yakov Valero-Lopez and Dr. Alberto Valdes-Garcia provided technical support and guidance. They were also generous in passing on certain "tricks of the trade" that is not available in books. I was a member of the research group working on the Zigbee transceiver and was involved in many technical discussions with Faisal, Didem, Hesam, Sangwook, Dr. Bu, Mobarak, Felix and Fernando. I must acknowledge those numerous technical discussions with Chinmaya. I thank them all.

Didem and Sangwook were closely involved with me during the entire phase of this thesis work. They have seen me at my best and worst. I really valued their presence and acknowledge their support, both technical and emotional. Further, Hesam, Faisal, Radhika and Dr. Bu, were involved with me during the three tape outs at Texas A&M. Dr. Bu was involved with the important frame design. I thank them all.

I was very fortunate to have made an amazing set of friends. I shared different mutual planes of interaction with each one of them. In no particular preference, I acknowledge Didem, Chinmaya, Alberto, Hesam, David, Fernando for their invaluable friendship. They were all there when it used to matter the most. The numerous personal discussions with each one of them have helped mould me into a better person. I thank them all for being my friends.

Outside the research group, I was again, fortunate to be involved with three student organizations of Texas A&M – Association for India's Development, Society for the Promotion of Indian Classical Music and Culture Amongst Youth, and Art of Living.

I deeply appreciate my interactions with all the volunteers of these organizations. I developed certain good friendships too. Of particular mention are Ravi, Aninda, Bharath, Preethi, Prakash, Dipa, Ganesh, Shiva, Kapil, Seeja, Shaija, Puneet, Satish, Sudeshna, Nethra, Pudhuma, Mayuresh, Amnaya, Archana, Amitava, Aditya, Prajakta and Shraddha. I thank them all.

In no particular preference, I am grateful to Aravind, Nitin, Gopi, Siva, Ganesh, Kota, Bharath, Vishnu, Prakash, Dheeraj, Majji, Arun, Amit, Radhika, Sumee, Ramya, Preethi, Divya, Bhavani, Sathya for all the good times. Badminton with Vishnu, Nitin, Gopi and Dheeraj was a pleasure. I thank them all.

I am deeply appreciative of the important friends in my life for their support and confidence in me throughout my MS study. They did their best given that they weren't physically present at Texas A&M. Of particular mention are Arun, Abilin, Anupam, Saurav, Samar, Thatha, Ajay, Prashanth, Rajesh, Hariram, Shankar, Anurup, Barathi and Neelima. I hope to have their invaluable friendships for life. I thank them all.

Again, words fail me when I need to express my gratitude, love and respect for Baba Alauddin Khan, Baba Ali Akbar Khan and Sri. Shankar P. Bhattacharyya. Here's where I acknowledge the role played by my gurus in helping me begin a new lease of life with the sarod. Having come across them all has been one of the biggest blessings in my life. I thank them all.

My *amma*, *apppa* and *chinna* have been my pillars of strength by providing me with their unconditional love and support. Last but not the least; I am deeply indebted to the Divine. I am an insignificant speck in this universe which is a wonderful creation of His/Hers. The beautiful things in the world – arts, music, books, nature, people, philosophy, etc. are a great source of joy, bliss, inspiration and solace. I thank them all.

# TABLE OF CONTENTS

| 1. | INTRODUC  | TION                                     | 1  |

|----|-----------|------------------------------------------|----|

|    | 1.1       | Background and Motivation                | 1  |

|    | 1.2       | Organization                             |    |

|    | 1.3       | Zigbee in Literature                     | 3  |

| 2. | ZIGBEE FR | EQUENCY SYNTHESIZER                      | 4  |

|    | 2.1       | Wireless Standards                       | 4  |

|    | 2.2       | Zigbee Transceiver                       | 6  |

|    | 2.3       | Synthesizer Specifications from Standard | 9  |

|    |           | 2.3.1 Frequency Synthesis                |    |

|    |           | 2.3.2 Phase Noise                        | 10 |

|    |           | 2.3.3 Spur Rejection                     | 14 |

|    |           | 2.3.4 Settling Time                      |    |

|    | 2.4       | Synthesizer Architecture                 |    |

|    | 2.5       | System Level Design                      |    |

|    |           | 2.5.1 Theory                             |    |

|    |           | 2.5.2 Design Procedure                   |    |

|    |           | 2.5.3 System Level Verification          |    |

|    | 2.6       | Literature Survey                        |    |

| 3. | FREQUENC  | CY SYNTHESIZER DESIGN                    | 32 |

|    | 3.1       | Synthesizer Architecture                 | 32 |

|    | 3.2       | Phase/Frequency Detector                 |    |

|    |           | 3.2.1 Topology                           |    |

|    |           | 3.2.2 Dead Zone                          |    |

|    | 3.3       | Charge Pump                              |    |

|    | 3.4       | Loop Filter                              |    |

|    | 3.5       | Loop Filter Buffer                       | 46 |

|    | 3.6       | Voltage Controlled Oscillator            |    |

|    | 3.7       | Frequency Divider                        |    |

|    | 3.8       | Layout Issues                            |    |

|    |           | 3.8.1 Floor Plan                         | 51 |

|    |           | 3.8.2 Supply Biasing Capacitors          | 53 |

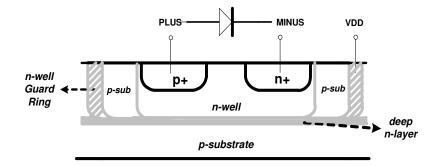

|    |           | 3.8.3 Guard Ring for Substrate Isolation |    |

|    |           | 3.8.4 Pin Placements                     |    |

|    |           | 3.8.5 RF Routing                         |    |

|    | 3.9       | Printed Circuit Board Design             |    |

|    |           | 3.9.1 Chip Fabrication                   |    |

|    |           | 3.9.2 Board Level Issues                 |    |

|    | 3.10      | Testing and Measurement                  |    |

ix

|    |          | 3.10.1        | Testing Setup65                             |

|----|----------|---------------|---------------------------------------------|

|    |          | 3.10.2        | Measurement Results67                       |

|    |          | 3.10.3        | Performance Summary75                       |

|    |          | 3.10.4        | Comparison with Other Zigbee Synthesizers76 |

| 4. | VOLTAGE  | CONTROLL      | ED OSCILLATOR DESIGN77                      |

|    | 4.1      | Architectu    | re77                                        |

|    |          | 4.1.1         | VCO in a Transceiver Environment77          |

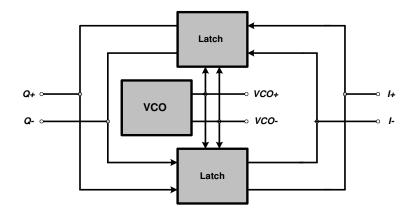

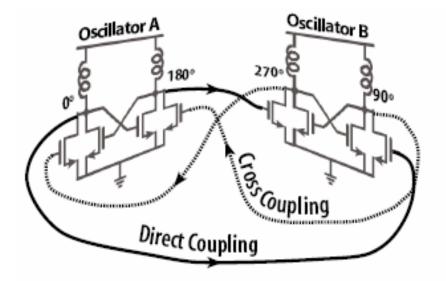

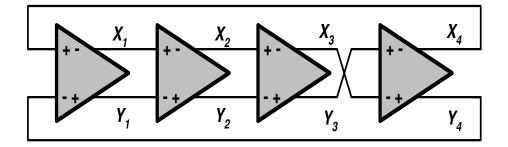

|    |          | 4.1.2         | I-Q Generation79                            |

|    |          | 4.1.3         | 5-GHz L-C VCO82                             |

|    | 4.2      | Passives      |                                             |

|    |          | 4.2.1         | Inductors85                                 |

|    |          | 4.2.2         | Varactors                                   |

|    | 4.3      | Specification | ons                                         |

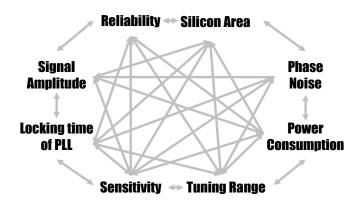

|    |          | 4.3.1         | Tuning Range93                              |

|    |          | 4.3.2         | Phase Noise94                               |

|    |          | 4.3.3         | Sensitivity                                 |

|    |          | 4.3.4         | Output Voltage Swing                        |

|    | 4.4      | Tuning in a   | 96 VCO                                      |

|    | 4.5      | Design Pro    | cedure                                      |

|    |          | 4.5.1         | Bias Current                                |

|    |          | 4.5.2         | Inductor                                    |

|    |          | 4.5.3         | Varactor                                    |

|    |          | 4.5.4         | CMOS Drivers104                             |

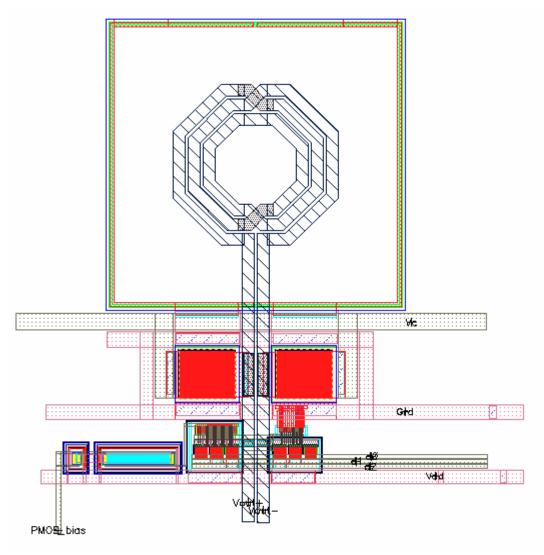

|    | 4.6      | Layout Issu   | 106 nes                                     |

|    | 4.7      | Testing and   | l Measurement111                            |

| 5. | CONCLUSI | ONS           |                                             |

|    | REFERENC | ES            |                                             |

|    | VITA     |               |                                             |

# LIST OF FIGURES

| FIGURE | Page                                                             |

|--------|------------------------------------------------------------------|

| 2.1    | Zigbee Transceiver Architecture7                                 |

| 2.2    | Mapping Standard to Key Synthesizer Specifications               |

| 2.3    | Downconversion in a Transceiver11                                |

| 2.4    | Phase Noise Contribution to SNR at Input of IF Section           |

| 2.5    | Leeson Phase Noise Model                                         |

| 2.7    | Effect of Spurs on SNR at Input of IF Section                    |

| 2.8    | Integer-N PLL Based Synthesizer                                  |

| 2.9    | Charge Pump PLL                                                  |

| 2.10   | Pole-Zero Placement                                              |

| 2.11   | Bode Plots (a) Open Loop (b) Closed Loop for the PLL             |

| 2.12   | SystemView Setup for PLL Design Verification                     |

| 2.13   | Transient Settling Behavior for the PLL Using SystemView         |

| 3.1    | Architecture of the Frequency Synthesizer                        |

| 3.2    | Topology of the Phase/Frequency Detector                         |

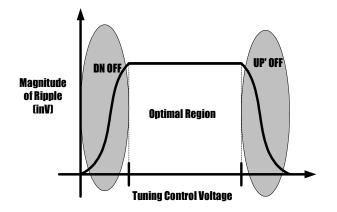

| 3.3    | Ripples in the Control Voltage                                   |

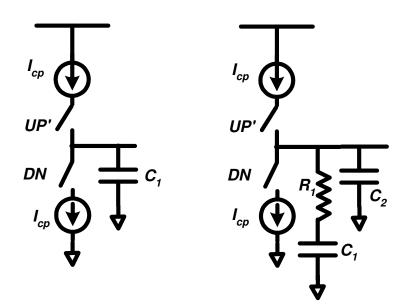

| 3.4    | Charge Pump Model with the Loop Filter (a) Conceptual (b) Actual |

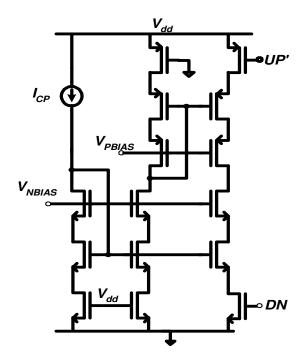

| 3.5    | Charge Pump – Topology                                           |

| 3.6    | Charge Pump Behavior with Varying Output Voltage42               |

| 3.7    | Loop Filter- Conceptual Diagram with Parameters43                |

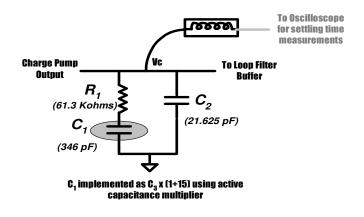

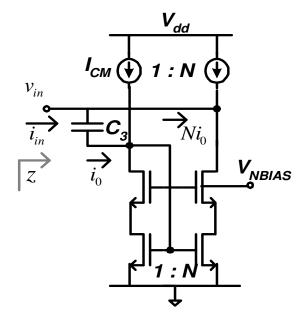

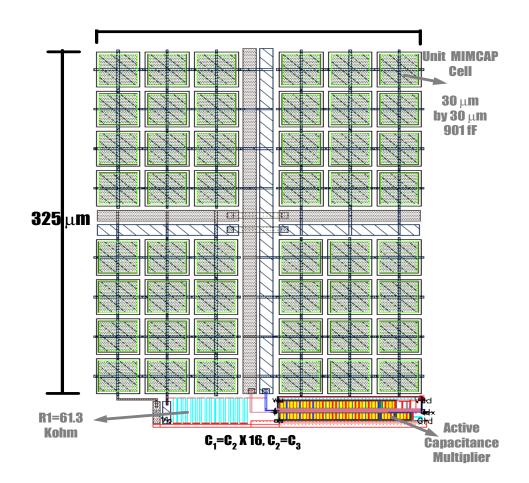

| 3.8    | Capacitance Emulation of C <sub>1</sub> =346 pF44                |

| 3.9    | Layout of the Loop Filter                                        |

# FIGURE

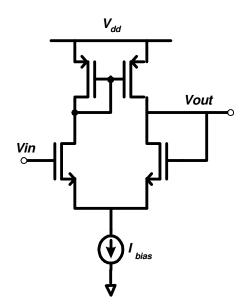

| 3.10 | Loop Filter Buffer                                                                                                                                   | 47 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

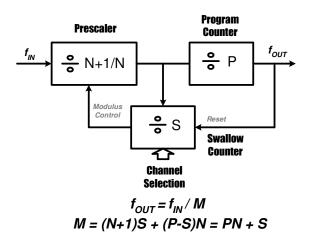

| 3.11 | Frequency Divider – Topology                                                                                                                         | 50 |

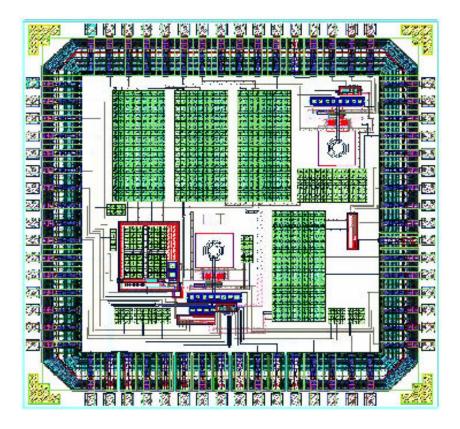

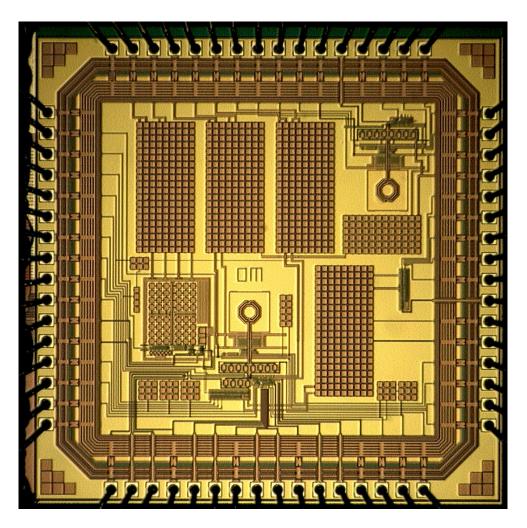

| 3.12 | Frequency Synthesizer Layout with the Frame                                                                                                          | 51 |

| 3.13 | Frequency Synthesizer – Floor Plan                                                                                                                   | 52 |

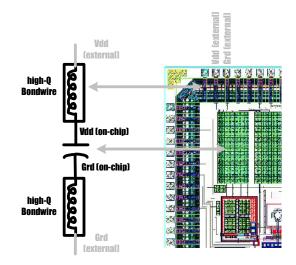

| 3.14 | On-chip Capacitor to Minimize Ground Bouncing                                                                                                        | 53 |

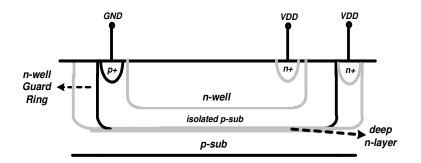

| 3.15 | Conceptual Idea of the Guard Ring                                                                                                                    | 54 |

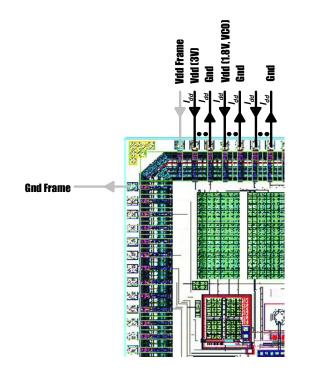

| 3.16 | Power Supply Pin Placement                                                                                                                           | 55 |

| 3.17 | Die Photo of the Frequency Synthesizer                                                                                                               | 57 |

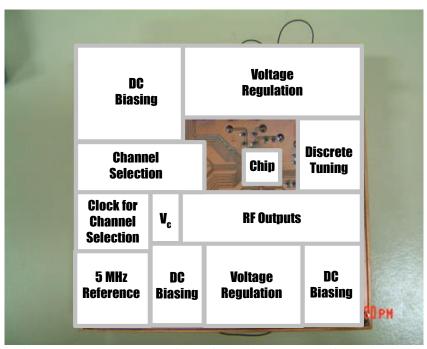

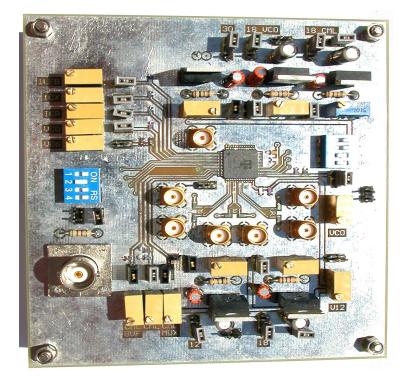

| 3.18 | PCB #4 for Testing the Synthesizer                                                                                                                   | 59 |

| 3.19 | Floor Plan Layout of PCB for Testing the Synthesizer                                                                                                 | 60 |

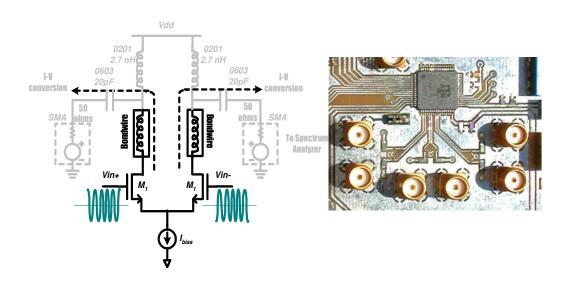

| 3.20 | Tapping Buffered RF Output Using Off-chip Components in the PCB.                                                                                     | 62 |

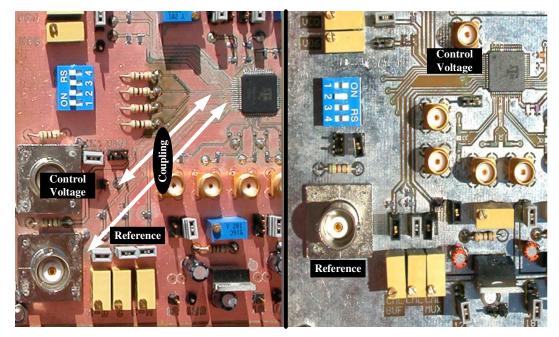

| 3.21 | <ul><li>(a) Coupling in the PCB to the Control Voltage of the VCO</li><li>(b) Refinement in PCB #5</li></ul>                                         | 64 |

| 3.22 | PCB #5 for Testing the Synthesizer                                                                                                                   | 65 |

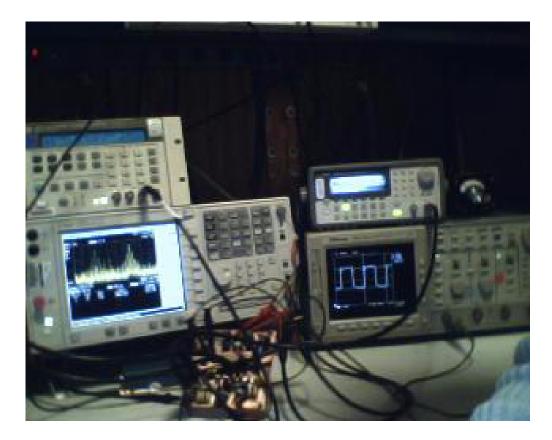

| 3.23 | Testing Bench Setup                                                                                                                                  | 66 |

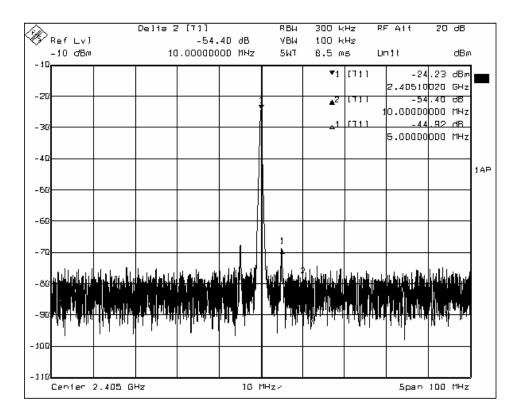

| 3.24 | Frequency Synthesis of Channel 1 for Zigbee Applications                                                                                             | 67 |

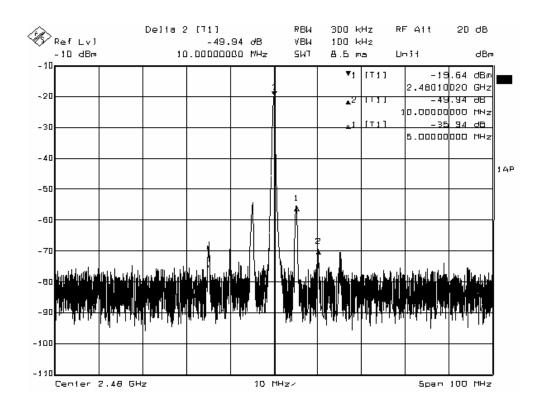

| 3.25 | Frequency Synthesis of Channel 16 for Zigbee Applications                                                                                            | 68 |

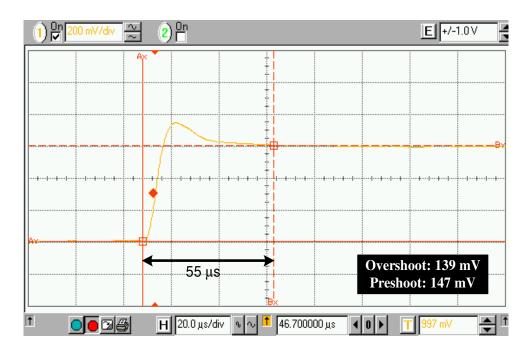

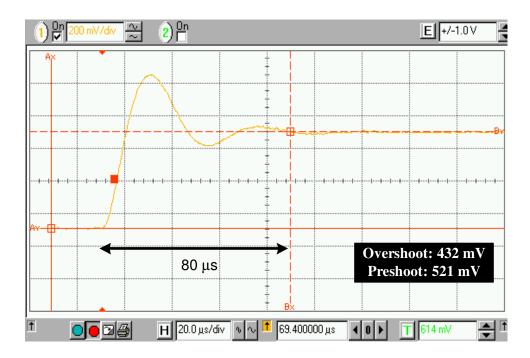

| 3.26 | Settling Time Measurement for the Extreme Switching of the Synthesizer.                                                                              | 69 |

| 3.27 | Settling Time Measurement for the Extreme Switching of the<br>Synthesizer with a 100 pF Capacitor at the Control Voltage Node<br>(Placed Externally) | 70 |

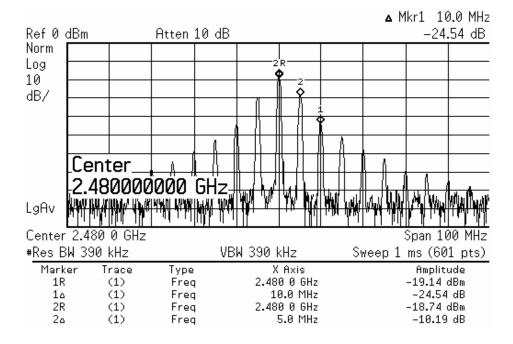

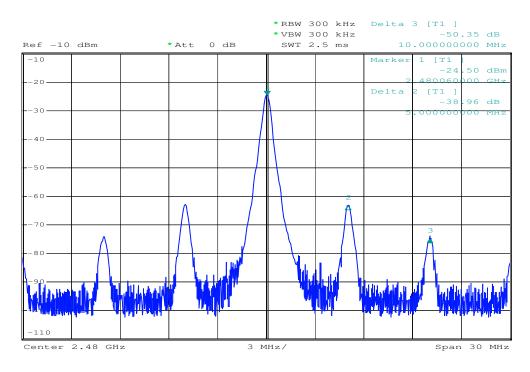

| 3.28 | Spur Suppression for 1.6Vpp, 1.5V, Square, PCB#4 Case                                                                                                | 72 |

| 3.29 | Spur Suppression for 1.7Vpp, 1.5V, Square, 100pF, PCB#5 Case                                                                                         | 72 |

Page

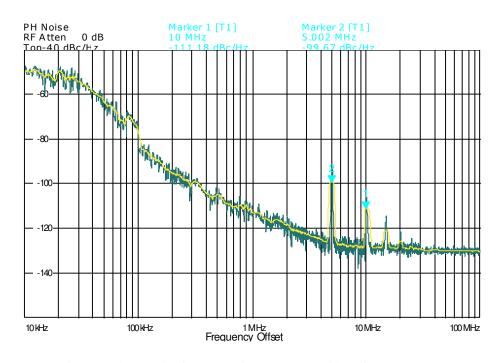

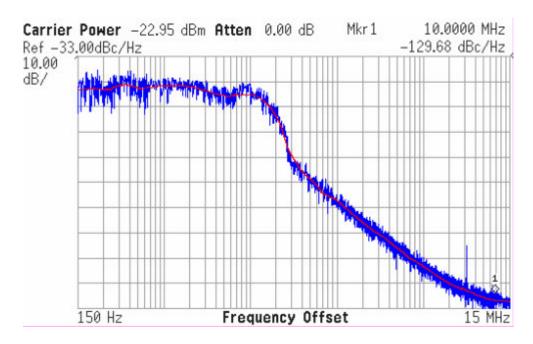

| 3.30 | Phase Noise for Synthesizer Spectrum with Reference Spurs73                |

|------|----------------------------------------------------------------------------|

| 3.31 | Phase Noise Spectrum of the Synthesizer in Open Loop74                     |

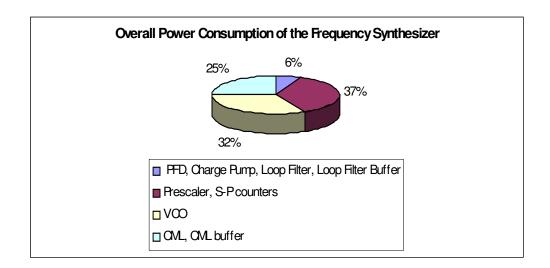

| 3.32 | Power Consumption of the Frequency Synthesizer – Pie Diagram75             |

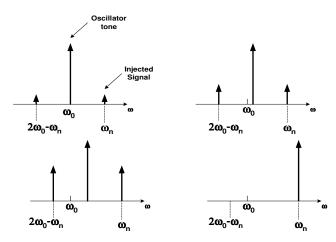

| 4.1  | Injection Pulling of an Oscillator as the Noise Amplitude Increases [11]78 |

| 4.2  | PA Load Pulling in a Transceiver [42]78                                    |

| 4.3  | VCO-Divide by 2 Network for I-Q Generation79                               |

| 4.4  | Quadrature VCO [61]                                                        |

| 4.5  | Ring Oscillator                                                            |

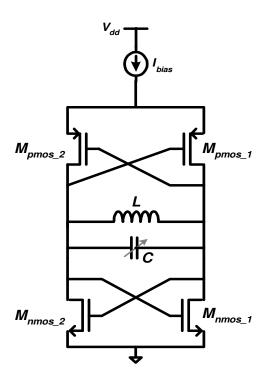

| 4.6  | CMOS VCO – Topology                                                        |

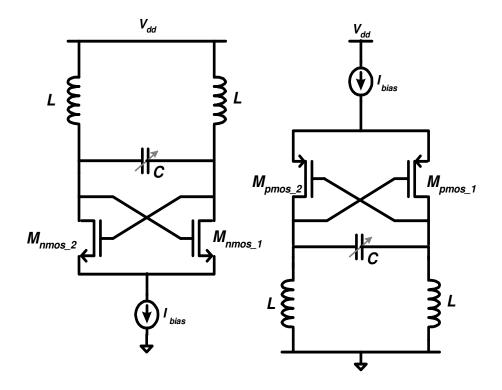

| 4.7  | L-C based VCO Topology (a) NMOS Only (b) PMOS Only 83                      |

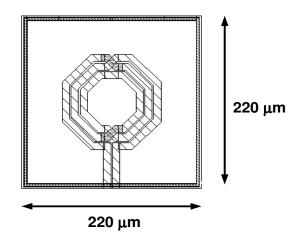

| 4.8  | Layout of the Differential Inductor Used in the VCO Design                 |

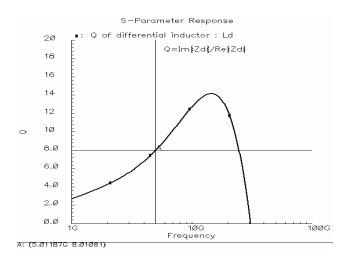

| 4.9  | Q of the Differential Inductor Used in the VCO Design                      |

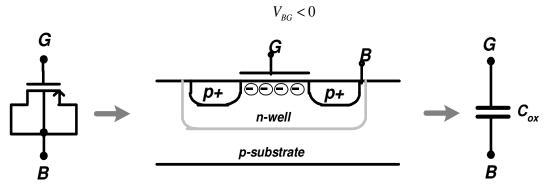

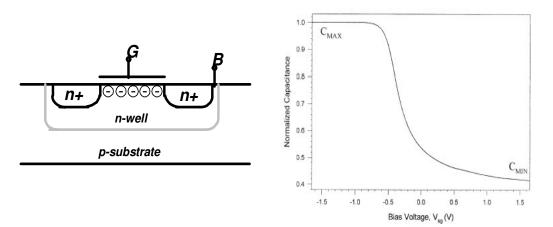

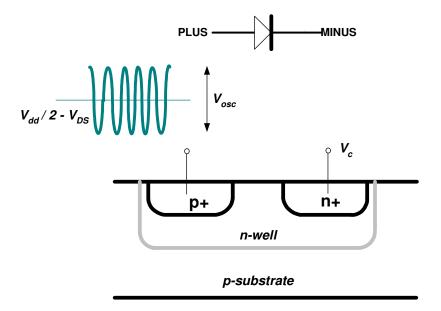

| 4.10 | Accumulation Mode of a PMOS Transistor                                     |

| 4.11 | Depletion Mode of a PMOS Transistor                                        |

| 4.12 | Inversion Mode of a PMOS Transistor90                                      |

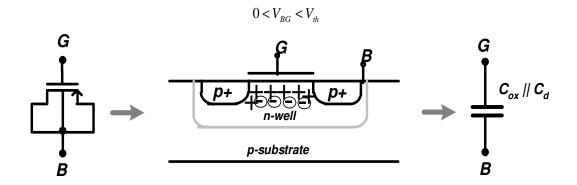

| 4.13 | C-V Characteristic of a PMOS Device (B=S=D) [66]                           |

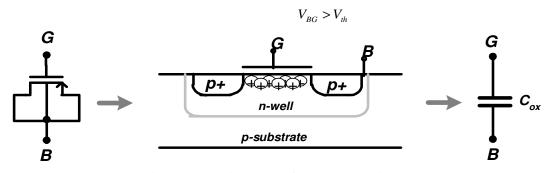

| 4.14 | NMOS Accumulation Mode Varactor and Its Characteristic [66]91              |

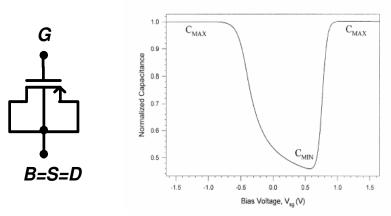

| 4.15 | PMOS Inversion Mode Varactor and Its Characteristic [66]92                 |

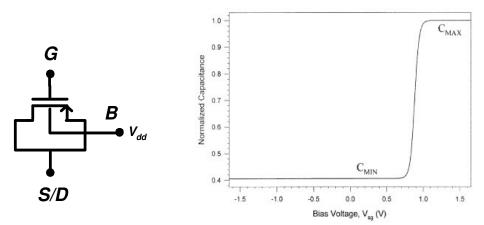

| 4.16 | VCO Design Octagon                                                         |

| 4.17 | Broadband Tuning Range Using Discrete Tuning Mechanism                     |

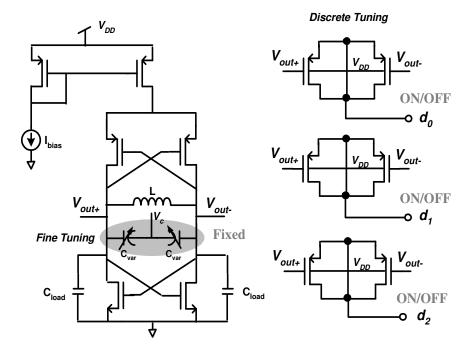

| 4.18 | CMOS VCO with Discrete Tuning – Topology97                                 |

| 4.19 | Issue of Forward Bias in a Junction Varactor103                            |

Page

# FIGURE

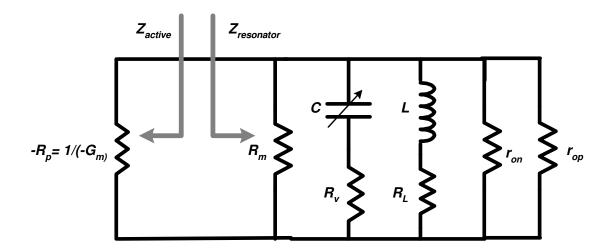

| 4.20 | Elements of Loss in an L-C VCO Using the One-Port Model | . 105 |

|------|---------------------------------------------------------|-------|

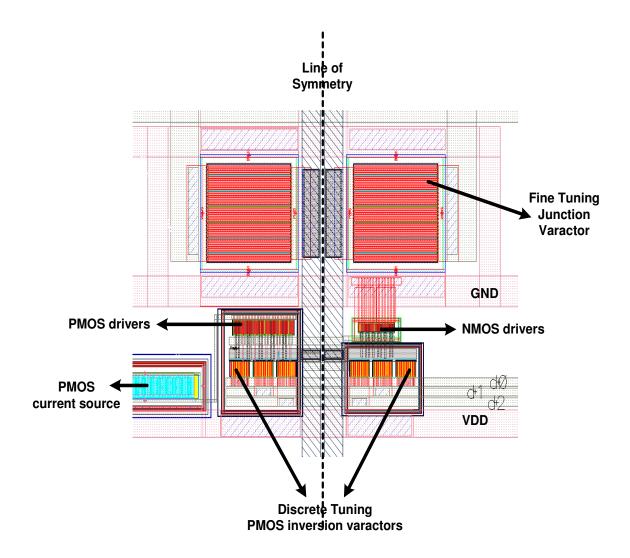

| 4.21 | Layout of the VCO – CMOS Drivers and the Varactors      | . 107 |

| 4.22 | Problem of Guard Ring around the Junction Varactor      | . 108 |

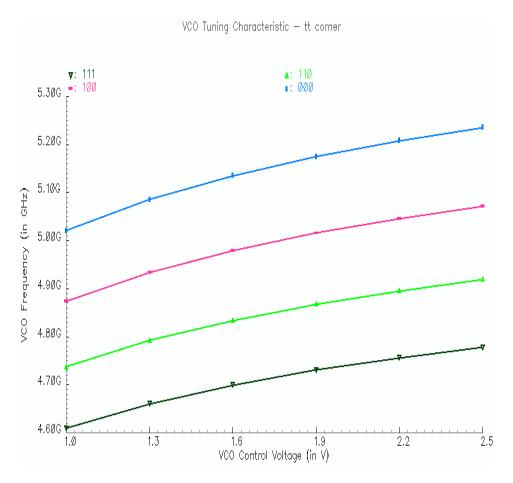

| 4.23 | Post Layout Results of the VCO – "TT" Corner            | 110   |

| 4.24 | Layout of the VCO                                       | .111  |

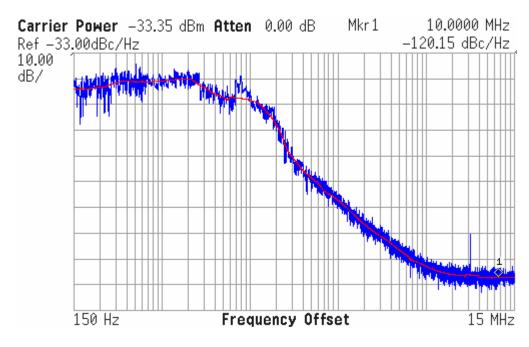

| 4.25 | Phase Noise of the VCO Output                           | . 112 |

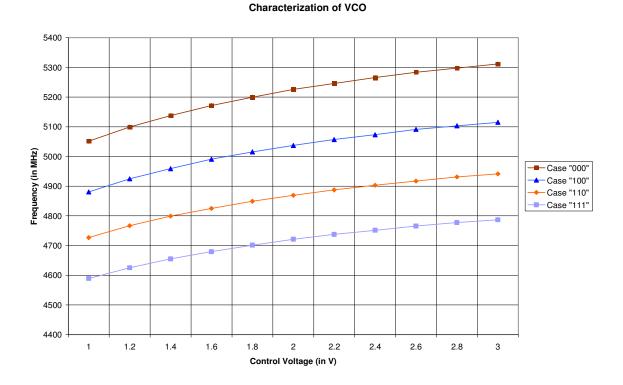

| 4.26 | Measurement Results – VCO with CML Load                 | .113  |

Page

# LIST OF TABLES

| TABLE | Page                                                                                         |

|-------|----------------------------------------------------------------------------------------------|

| Ι     | Wireless Standards                                                                           |

| II    | Specifications of the 2450 MHz IEEE 802.15.4 PHY Layer                                       |

| III   | General Design Methodology for PLL-based Frequency Synthesizer8                              |

| IV    | Specifications for the Synthesizer Derived from the Standard17                               |

| V     | Phase Frequency Detector – Specifications                                                    |

| VI    | Charge Pump – Specifications42                                                               |

| VII   | Loop Filter – Specifications                                                                 |

| VIII  | Loop Filter Buffer – Specifications                                                          |

| IX    | Voltage Controlled Oscillator – Specifications                                               |

| Х     | Frequency Divider – Specifications                                                           |

| XI    | Characteristics of the PCB's Used for Testing                                                |

| XII   | Equipment Used for Testing65                                                                 |

| XIII  | Sources of Reference Spurs and Their Alleviation Methods71                                   |

| XIV   | Spur Suppression for Various Test Scenarios at 2.48 GHz (Reference<br>Amp Bias, Wave Type)71 |

| XV    | Performance Summary of the Frequency Synthesizer75                                           |

| XVI   | Comparison with Other Synthesizers for Zigbee Applications76                                 |

| XVII  | I-Q Generation                                                                               |

| XVIII | L-C VCO Schemes                                                                              |

| XIX   | Parameters of the Differential Inductor                                                      |

| XX    | Specifications for the VCO                                                                   |

| TABLE |                                                              | Page  |

|-------|--------------------------------------------------------------|-------|

| XXI   | Cause-Affect Relation in a CMOS VCO                          | 98    |

| XXII  | Tuning Range with Process Variations                         | . 109 |

| XXIII | Tuning Range with Process Variations and Measurement Results | . 113 |

#### **1. INTRODUCTION**

#### **1.1 Background and Motivation**

The need for ubiquitous mobile computing and networking has lead to the development of various wireless standards by the Institute of Electrical and Electronics Engineers (IEEE) in consortium with the industry over the last decade. The development of such standards has lead to a complete revolution in the wireless segment by spurring on an exponential growth in the semiconductor and communications industry. Examples of such standards include Bluetooth, IEEE 802.11 a/b/g, Ultra wide-band (UWB), etc. It merits mention that each standard caters to a different application and has an altogether different design focus.

The IEEE 802.15.4/Zigbee standard [1] has been recently developed (released in December 2004) to cater to the needs of low cost, low power, low data rate, and short range wireless networks. This new standard is specifically intended for applications pertaining to data monitoring, industrial control and sensor networks. The thesis focuses on the design of a frequency synthesizer for a 2.4 GHz IEEE 802.15.4/Zigbee transceiver.

The design of a monolithic solution of a low power, high-performance frequency synthesizer in CMOS is the main challenge. Implementation of the synthesizer in a transceiver environment leads to additional design considerations and evaluation of nonidealities. It is shown that careful planning at the system level of the synthesizer can lead to high-performance realizations.

This thesis follows the style and format of IEEE Journal of Solid-State Circuits.

The frequency planning of the transceiver also plays a key role in the development of the synthesizer. Further, it can be seen that a similar design approach be followed for the implementation of synthesizers for other wireless transceivers.

#### **1.2 Organization**

Section 2 begins with the need for the IEEE 802.15.4/Zigbee standard and a comparative study with the existing standards of Bluetooth, IEEE 802.11a/b/g and UWB. The architecture of the entire transceiver is given and the important specifications for the synthesizer have been derived from the standard. The architecture chosen for the particular implementation of this synthesizer in a transceiver environment is provided.

Moreover, a detailed system level design procedure with stability and settling time considerations aids in understanding the system level issues of the synthesizer better. A literature survey of synthesizer implementations for transceivers in general (at both 5 GHz and 2.4 GHz) is provided. The section ends with a discussion of the salient features of the synthesizers. The survey helps us in understanding the bottlenecks and performance oriented goals for a successful design better.

Section 3 forms the crux of this thesis and deals with the practical design and implementation of a frequency synthesizer in a plain CMOS technology. It provides a practical solution to the development of the synthesizer after the system level progress in Section 2. Salient considerations affecting the performance of the synthesizer and germane issues specific to the integrated circuit implementation are discussed here.

Further, a section on layout and board level issues highlights their importance and affect on the synthesizer performance. The testing and measurement results of the silicon prototype; both for the synthesizer and the VCO are provided in this section. Moreover,

the key features of the synthesizer are highlighted and a judicious comparative analysis made with existing synthesizers reported in the literature (mentioned in Section 2).

Section 4 is dedicated to the design and implementation of the Voltage Controlled Oscillator (VCO), one of the key radio-frequency (RF) blocks in the synthesizer. Various architectures are considered and the final realization is justified. The passive RF components play a crucial role in a VCO. Hence, a treatment of the varactors and inductors; and their effects on the overall performance is necessary. The design procedure provides a better understanding of the tightly coupled design space.

Finally, Section 5 concludes with a summary of the work done as part of this research. Further the future scope of work and open-ended problems for research treatment are given.

#### **1.3 Zigbee in Literature**

The PHY layer of the standard had been prepared in 2003 by the IEEE and the Zigbee Alliance; and the standard had been officially released in December 2004. Since then, the design of Zigbee related products has been one of the main focuses in the industry, especially among members of the Zigbee Alliance. Publications in the literature related to academic research are limited.

A low-coin sized transceiver for a preliminary IEEE 802.15.4 standard is reported in [2]. Reference [3] reports one of the first 2.4 GHz Zigbee-ready IEEE 802.15.4 compliant radio-transceiver. Recently, a complete system-on-chip solution for a 2.4 GHz transceiver developed in the industry is reported in [4]. References [5] and [6] are standalone frequency synthesizers reported for 2.4 GHz Zigbee applications.

#### 2. ZIGBEE FREQUENCY SYNTHESIZER

In this section, the need for the Zigbee standard is addressed and the specifications for the frequency synthesizer for application in a 2.4 GHz transceiver are derived. The architecture development of the synthesizer and the system level design issues are discussed here. The frequency synthesizer, which performs the main role of career generation for the down-conversion/ up-conversion, is a key building block in radio front-ends. Despite not being directly involved in the signal path, the performance of the synthesizer affects the overall performance of the transceiver. A detailed treatment of the frequency synthesizer is beyond the scope of the thesis and the reader is encouraged to refer to [7-13] for a better understanding of important concepts.

#### **2.1 Wireless Standards**

The 21<sup>st</sup> century has lead to the dawn and revolution of a new information technology era marked by the emergence of various wireless standards. Internetworking technologies have lead to a high connectivity to information, be it data, voice, audio, or video. The need for ubiquitous mobile computing and networking is more so felt now than ever before. Various standards have been developed over the last decade to cater to different needs and applications.

Examples of such standards include Bluetooth, 802.11a/b/g, ultra wideband, 802.15.4/Zigbee, GSM, GPS, DECT-1800, DECT-1900, etc. It merits mention that certain standards like the GPS were mainly developed for military applications, only to be released in the commercial market too. Moreover, the technological advances, especially, in the field of integrated circuits has accelerated this revolution. Complete low-area, low-cost, monolithic integrated transceiver solutions are now in vogue.

The IEEE 802.15.4/ Zigbee standard has been recently developed (officially released for commercial applications in December 2004) to cater to the needs of low cost, low power, low data rate, and short range wireless networks [1]. *The Zigbee Alliance is responsible for the Zigbee wireless technology, which defines network, security and application layers upon the IEEE 802.15.4 PHY and MAC layers [1].* Henceforth, for reasons of brevity, the IEEE 802.15.4/ Zigbee standard will be termed Zigbee.

It has been realized that already existing short-range wireless standards like Bluetooth and 802.11a/b/g have relatively high data rates when compared to the actual data rate required for certain applications. For e.g. the use of a Bluetooth transceiver, with a data rate of 1 Mbps, in applications involving the communication of data in the form of simple text, leads to sheer wastage of resources. Networks involving machine-to-machine (M2M) communication for monitoring and quality control purposes do not need a high data rate.

The standard addresses the need of network applications requiring high density of transceivers with low data-rate. Such transceivers need to have a long battery life and should be highly economical in cost. They are an attractive option for applications pertaining to low-data industrial monitoring and control, sensor based network systems, home automation, gaming, medical and automotive solutions. Further, it can theoretically support upto 65,000 nodes in the network [1].

The important design considerations from the paradigm of a transceiver design are frequency band, the data rate, the required range of wireless transmission, sensitivity at the receiver end, modulation scheme, transmitted output power, settling time for frequency hopping, adjacent and alternate channel interferers etc. These specifications influence the choice of technology, the choice of architecture and the choice of the standard.

Table I gives a comparison between the popular wireless standards - IEEE 802.11.a/b/g [14-16], Bluetooth [17], and ultra wideband [18] with the Zigbee standard [1]. It can be seen that Zigbee is the only standard that is tailored for low data-rate systems. Further, it can be inferred that prior to the Zigbee standard, more importance had been given to the development of high data-rate, multimedia friendly standards.

|                    |             |             | I ADLE I |            |            |          |

|--------------------|-------------|-------------|----------|------------|------------|----------|

| WIRELESS STANDARDS |             |             |          |            |            |          |

|                    | Zigbee      | Bluetooth   | 802.11b  | 802.11g    | 802.11a    | UWB      |

| Data Rate          | 250 Kbps    | 1 Mbps      | 11 Mbps  | 54 Mbs     | 24 Mbps    | 500 Mbps |

| Band               | 2.4 GHz     | 2.4 GHz     | 2.4 GHz  | 2.4 GHz    | 5 GHz UNII | 3.1-10.6 |

|                    | ISM         | ISM         | ISM      | ISM        |            | GHz      |

| Range              | 10m         | 10m         | 100m     | 100m       | 50m        | 10m      |

| Channel            | 5 MHz       | 1 MHz       | 25 MHz   | 25 MHz     | 20 MHz     | 500 MHz- |

| Bandwidth          |             |             |          |            |            | 7.5GHz   |

| Sensitivity        | -85 dBm     | -70 dBm     | -76 dBm  | -76 to -74 | -82 to -65 | -70 dBm  |

|                    |             |             |          | dBm        | dBm        |          |

| Modulation         | O-QPSK      | GFSK        | 11Mbaud  | OFDM 64+   | COFDM      | BPSK/    |

|                    |             |             | QPSK     |            | BPSK       | QPSK     |

| Output Power       | -5 to 3 dBm | 0 to 20 dBm | 30 dBm   | 30 dBm     | 50mW; 250  | -41.3    |

|                    |             |             |          |            | mW         | dBm/MHz  |

| Settling time      | 192 µs      | 259 μs      | 224 µs   | 224 µs     | 224 µs     | 10ns     |

TABLE I

#### **2.2 Zigbee Transceiver**

The design and implementation of the RF front-end of the 2.4 GHz Zigbee transceiver is a collaborative effort of five graduate students (four Ph.D. and one M.S.). The responsibilities of the author included derivation of frequency synthesizer specifications from the standard, architecture development of the frequency synthesizer, phase-locked loop design based on settling time and stability paradigms (Section 2); and the design and implementation of certain building blocks (Sections 3 and 4) of the synthesizer. The main design focus of this transceiver implementation is design for low power consumption and high integrability in a low cost technology.

The TSMC 0.18 µm CMOS technology is used for the design of the transceiver. Two popular radio transceiver architectures exist – the low-IF architecture and Direct Conversion. Both the architectures have their merits and drawbacks. The architecture development of a complete transceiver depends on a multitude of parameters like Noise Figure, Linearity, Power Consumption, SNR-BER, implementation challenges, injection pulling, PA load pulling, Coherent and Non-coherent demodulation, Choice of modulation scheme, Gain Planning and Frequency Planning.

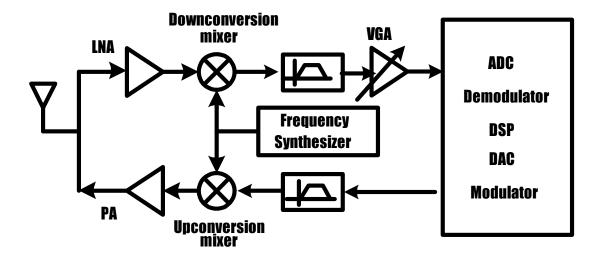

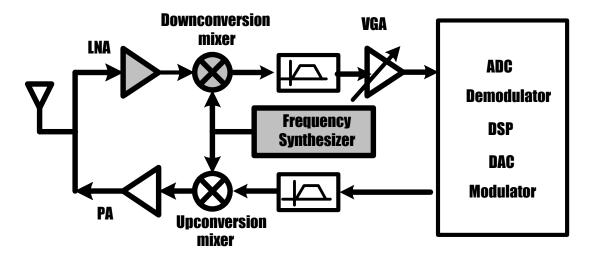

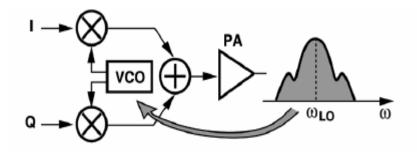

Fig. 2.1 Zigbee Transceiver Architecture

The transceiver architecture is given in Fig. 2.1. The circuit implementation of the important building blocks in the transceiver such as the Low Noise Amplifier, Downconversion mixer, Power Amplifier, Upconversion mixer in the direct signal path and the Frequency Synthesizer introduce non-idealities. A thorough approach to system design is essential and an involved discussion on radio transceivers is beyond the scope of the thesis. The reader is encouraged to read [12] and [13] for a treatment of the issues in a transceiver.

|                             | ABLE II<br>MHz IEEE 802.15.4 PHY Layer |

|-----------------------------|----------------------------------------|

| Performance Metrics         | Specifications                         |

| Carrier                     | 2400 MHz                               |

| Spectrum                    | 2400-2483.5 MHz                        |

| Modulation                  | O-QPSK using DSSS                      |

| Channel Bandwidth           | 3 MHz                                  |

| Channel Spacing             | 5 MHz                                  |

| No. of Channels             | 16 (11-26 of the PHY layer)            |

| Sensitivity                 | - 85 dBm                               |

| FER                         | 5e-5                                   |

| SNR                         | 2 dB                                   |

| Settling Accuracy           | $\pm$ 40 ppm (96 KHz)                  |

| Alternate Channel Rejection | 30 dB at 10 MHz offset                 |

| Adjacent Channel Rejection  | 0 dB at 5 MHz offset                   |

| Output Transmitted Power    | -5 to 3 dBm                            |

The important specifications of the PHY layer from the 2.4 GHz IEEE 802.15.4 standard are given in Table II. The overall transceiver needs to meet these specifications, irrespective of their implementation scheme. The general design methodology for the design of a frequency synthesizer is summarized in Table III. Moreover, the relevant sections in the thesis are given along side for the sake of completeness.

|      | DESIGN METHODOLOGY FOR PLL-BASED FREQUENCY S |                     |

|------|----------------------------------------------|---------------------|

| Step | Procedure                                    | Relevant<br>Section |

| Ι    | Transceiver Considerations                   | 2.2                 |

| II   | Synthesizer Specifications from Standard     | 2.3                 |

| III  | Architecture Development                     | 2.4                 |

| IV   | Phase Locked Loop Design                     | 2.5                 |

| V    | Integrated Circuit Implementation            | 3, 4                |

TADLE III

#### 2.3 Synthesizer Specifications from Standard

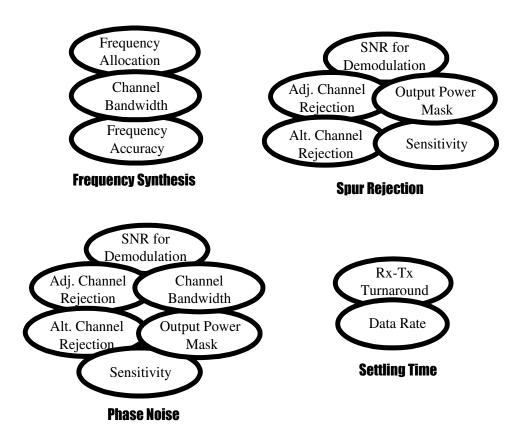

The IEEE 802.15.4 standard gives the communication protocol for the prototype transceiver implementation and the specifications for the transceiver and the synthesizer need to be derived from this standard. The mapping of the specifications from the standard is an important pre-design process. This section highlights the one-to-one correspondence between the standard and the key performance metrics of the synthesizer. The key specifications from the standard that are used for the estimation of the synthesizer performance metrics is explained figuratively using Fig. 2.2.

Fig. 2.2. Mapping Standard to Key Synthesizer Specifications

#### 2.3.1 Frequency Synthesis

The 2.4 GHz Zigbee standard has 16 channels, spaced 5 MHz apart, from 2405 MHz to 2480 MHz. The synthesizer needs to synthesize these 16 channel selection clock frequencies with 40-ppm frequency accuracy. This performance metric is essential for the selection of the architecture and the design of the divide ratio for the divider. Since 16 channels need to be synthesized with a spacing of 5 MHz, it is natural to assume a clock reference of 5 MHz for an integer-N PLL based synthesizer scheme.

#### 2.3.2 Phase Noise

Typical wireless systems employ the concept of time division multiple access or frequency division multiple access to increase the throughput and capacity of the system. Hence, it becomes necessary to switch from one channel to another in time. With this multiple access approach, the signal actually seeps into the other channels and contributes to channel interference. In the Zigbee PHY layer, the maximum contribution to co-channel interference is from the adjacent and alternate channels, spaced 5 MHz and 10 MHz apart from the channel of interest.

Fundamentally, the LO spectrum is not a pure single frequency tone in real-life implementations. The mechanisms of phase noise lead to the "skirt" behavior in the LO spectrum of the VCO or the synthesizer. The time domain manifestation of phase noise is jitter. Jitter can be defined as the variations in the zero crossings of the signal. These variations can be both random and deterministic. The various sources of jitter are reference, charge pump mismatch, spurs in the control line of the VCO, thermal noise of the loop filter, supply noise, phase noise of the VCO, phase mismatch in the dividers, etc. [19-21].

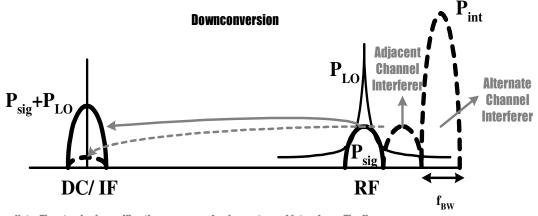

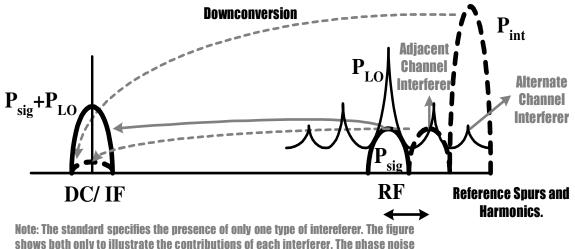

Fig. 2.3 Downconversion in a Transceiver

Thus, the phase noise of the LO for a particular channel, contributes to co-channel interference due to the mechanism of downconversion. In typical wireless systems, signal processing is performed in two steps (as shown in Fig. 2.3) – downconversion of the RF signal following "low-noise" amplification by the LNA to the baseband domain; and subsequent baseband processing. Thus, downconversion is inevitable and most phase noise specifications are derived from adjacent channel rejection requirements of the standard.

The phase noise of the adjacent channel LO frequency tone creates interference for the channel of interest. From Fig. 2.4, it can be seen that the Signal to Noise Ratio required at the input of the IF section (say, following downconversion) is given as

$$SNR = (P_{sig} + P_{LO}) - (PN + P_{int} + P_{BW}) > SNR_{min}$$

(2.1)

where  $P_{sig}$  is the power content of the carrier

$P_{LO}$  is the power content of the LO

PN is the phase noise contribution of the LO

$P_{int}$  is the power content of the interferer

$P_{BW}$  is the power content of the signal across the channel bandwidth

*SNR<sub>min</sub>* is the required SNR at the input of the IF section following downconversion for the given demodulation scheme and tolerable bit error rate.

Note: The standard specifies the presence of only one type of intereferer. The figure shows both only to illustrate the contributions of each interferer. The phase noise must be derived for both the cases.

Fig. 2.4 Phase Noise Contribution to SNR at Input of IF Section

Careful gain planning gives us a minimum SNR requirement at the input of the IF section. To support a minimum SNR requirement of 2 dB at the input of the demodulator in the receiver path, the SNR requirement at the input of the IF section can be calculated as 8 dB. The signal ( $P_{sig}$ ) is downconverted to IF or DC by LO ( $P_{LO}$ ) provided by the synthesizer. The channel spacing is 5 MHz. There would be a guard band on either side of the channel to prevent aliasing and minimize co-channel interference. The actual

bandwidth of the channel would therefore be less than 5 MHz. However, for purposes of hand calculations, we can assume that the bandwidth is 5 MHz. Equation 2.1 can be rearranged to give

$$PN - P_{LO} < (P_{sig} - P_{int}) - P_{BW} - SNR_{min}$$

$$(2.2)$$

From the above equation, the phase noise specifications for the synthesizer can be calculated as

$$(PN - P_{LO})_{5MHz} = (0 - 0) - 10\log(5 \cdot 10^6) - 8 = -75dBc / Hz$$

(2.3)

$$(PN - P_{LO})_{10MHz} = (0 - 30) - 10\log(5 \cdot 10^6) - 8 = -105dBc / Hz$$

(2.4)

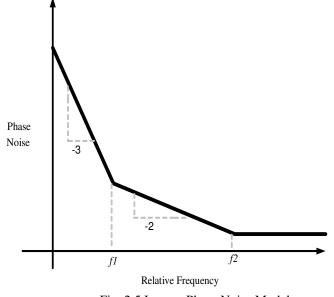

Fig. 2.5 Leeson Phase Noise Model

Assuming a margin of 5 dB in SNR to model the non-idealities of the system, the phase noise specification can be taken as -110 dBc/Hz at an offset of 10 MHz from the carrier. The Leeson model of phase noise provides a good approximation. Typically at

frequency offsets in the range of 1 MHz (beyond the knee frequency  $f_1$ , given by flicker noise upconversion limitations), the "skirt" assumes a -20 dBc/decade roll-off behavior (Refer Fig. 2.5). Thus it can be seen that the 10 MHz specification is tighter to meet. Therefore meeting the phase noise specifications at 10 MHz implies that the specification at 5 MHz is met, but not vice-versa.

Additionally, the power spectral mask requirements for the transmitter require a phase noise of -103 dBc/Hz at an offset frequency of 3.5 MHz.

#### 2.3.3 Spur Rejection

The reference spurs appear at the output of the VCO spectrum in any PLL based system. If the integer-N PLL based synthesizer scheme is implemented, reference spurs appear at an offset of 5 MHz, equal to the channel spacing. The downconverted spur contributes to the interference and worsens the SNR at the input of the IF section. The Zigbee standard specifies the adjacent channel interference of 0 dB at an offset of 5 MHz. Here, the spur is considered as a single tone and not as an integrated noise.

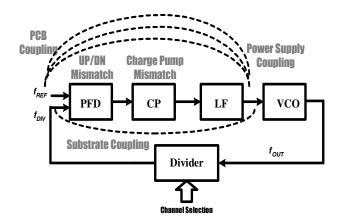

Fig. 2.6 Sources of Reference Spur in an Integer-N PLL based Synthesizer

The various sources of reference spur in a practical implementation of an integer-N synthesizer are discussed in Section 3. Further, the importance of PCB level issues on the spur performance of a synthesizer is highlighted. The modulation of the control voltage of the VCO leads to spurs in the output spectrum of the VCO and the synthesizer. Various sources exist for the modulation of this control line of the VCO. The important sources are the PCB coupling, substrate coupling, charge pump mismatch, and the power supply noise and are given in Fig. 2.6.

From Fig. 2.7, the Signal to Noise Ratio required at the input of the IF section (say, following downconversion) can be obtained as

$$SNR = (P_{sig} + P_{LO}) - (P_{Spurs} + P_{int}) > SNR_{min}$$

(2.5)

$$P_{Spurs} - P_{LO} < (P_{sig} - P_{int}) - SNR_{min}$$

(2.6)

must be derived for both the cases.

Fig. 2.7 Effect of Spurs on SNR at Input of IF Section

Thus the spur suppression requirement for the synthesizer can be calculated as

$$P_{Spurs} - P_{LO} = (0 - 0) - 8 = -8dBc \tag{2.7}$$

Moreover, the fundamental reference spur is at 5 MHz. Harmonics of the reference spur occur at 10 MHz, 15 MHz, etc. The differential mode of operation should ideally give only odd-harmonics. However, realistic environments give finite even-order components. Thus, the spur suppression specification at an offset frequency of 10 MHz, where the alternate channel interferer is present can be calculated as

$$P_{S_{purs}} - P_{LO} = (0 - 30) - 8 = -38 dBc$$

(2.8)

Assuming a margin of 5 dB in SNR to model the non-idealities of the system, the Spur Suppression Specifications can be taken as -13 dBc and -43 dBc at offset frequencies of 5 MHz and 10 MHz respectively.

#### 2.3.4 Settling Time

The standard supports a data rate of 250 Kbps. Each symbol is a word, consisting of 4 bits. Thus, the supported symbol rate is 62.5 Ksymbols/ sec. The maximum RX-TX or TX-RX turnaround time is given as 12 symbol periods, which is equivalent to 192  $\mu$ s. This gives an estimate of the worst case settling time for the synthesizer for extreme switching from Channel 1 to Channel 16.

The settling time for the synthesizer is equivalent to the locking time for the PLL. The loop settles to a new frequency output based on the channel selection configuration. For e.g. the transceiver is operating in the receive mode at 2.405 GHz. In the next scheme of operation, it needs to operate in the transmit mode at 2.48 GHz. The synthesizer now synthesizes 2.48 GHz. The time taken by the synthesizer to settle to the new frequency can be seen as the frequency response time of the loop.

| TABLE IV                                                     |                                 |

|--------------------------------------------------------------|---------------------------------|

| SPECIFICATIONS FOR THE SYNTHESIZER DERIVED FROM THE STANDARD |                                 |

| Performance Metric                                           | Value                           |

| Frequency Synthesis                                          | 2405-2480 MHz in steps of 5 MHz |

| Phase Noise                                                  | -110 dBc at 10 MHz              |

|                                                              | - 102 dBc at 3.5 MHz            |

| Spur Rejection                                               | -13 dBc at 5 MHz                |

|                                                              | -43 dBc at 10 MHz               |

| Settling time                                                | 192 µs                          |

The important frequency synthesizer specifications derived from the standard are given in Table IV. The specifications, derived from first-order hand calculations, are found to be match closely with the ones derived by the system designer for the transceiver.

#### **2.4 Synthesizer Architecture**

The synthesizer needs to synthesize channels in steps of 5 MHz from 2405-2480 MHz. The frequencies to be synthesized are integer multiples of the channel spacing. Hence, integer-N PLL based synthesizer architecture will be best suited for this application. Since the phase noise and spur rejection specifications are relaxed, the integer-N PLL based solution gives the best performance in terms of power consumption and ease of integrability. Other synthesizer architectures exist, namely the Fractional-N synthesizer and Direct Digital Synthesizer [12, 13].

The fractional synthesizer uses a fractional divider scheme with sigma-delta modulator for dithering mechanism and noise shaping in the divider section. This architecture is particularly useful in applications requiring very high frequency resolution. For e.g., in typical read channel applications, the synthesizer works from 1 GHz to 2 GHz with a frequency resolution of 1.5%. The fractional-N synthesizer is not the best scheme for 2.4 GHz Zigbee applications.

The direct digital synthesizer doesn't make use of a feedback mechanism and is known to provide frequency synthesis with fast settling times. However, the frequency of application is limited due to the inherent digital nature of the synthesizer. It makes use of an accumulator, read only memory (ROM), digital-analog converter (DAC) and low pass filter (LPF). It is difficult to obtain ROM's working at 4.8 GHz for 2.4 GHz synthesizers. Thus, this approach is not suitable for 2.4 GHz Zigbee applications.

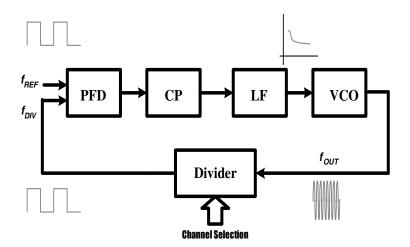

Fig. 2.8 Integer-N PLL Based Synthesizer

$$f_{OUT} = N.f_{REF} \tag{2.9}$$

The integer-N PLL based synthesizer architecture is given in Fig. 2.8. It consists of a phase frequency detector that compares the reference with the feedback signal obtained from the dividers to translate into time-level information. The charge pump along with the loop filter converts the critical time-level information into voltage. This voltage is effectively the control voltage of the VCO. Based on the behavior of the control voltage, the VCO changes its frequency. The PLL finally settles to a new frequency based on the channel select configuration. The dividers provide programmability to the synthesizer.

The synthesizer implementation, given above, is a complex discrete-time system and involves a non-linear control theory approach. However, for purposes of gaining insight into the operation of the PLL control structure, the continuous time approximation can be made, provided the Gardener's Stability limit is taken into consideration [22]. This approximation helps us in understanding the loop stability and dynamics better.

#### 2.5 System Level Design

#### 2.5.1 Theory

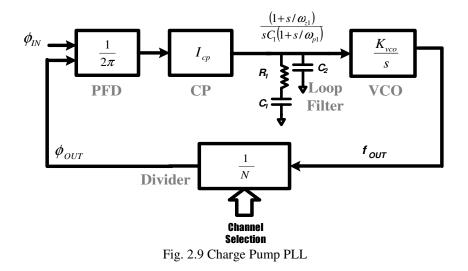

The charge-pump based PLL architecture [22] is given with the respective transfer functions of each block in Fig. 2.9. The oscillator and the charge pump-loop filter contribute to two poles at the origin (Figure on Page 22). For purposes of stability, a zero is placed appropriately to ensure sufficient phase margin. The loop filter introduces a pole and a zero in the system. If  $C_2$  were absent, the control voltage experiences sharp transitions every time charge is injected into the  $R_1$ - $C_1$ .

Eqn. 2.10 gives the overall open loop transfer function as

$$H_{open}(s) = \frac{\phi_{OUT}}{\phi_{IN}} = \frac{K_{vco}I_{cp}}{2\pi NC_1} \cdot \frac{(1 + s/\omega_{z1})}{s^2(1 + s/\omega_{p1})}$$

(2.10)

where

$$\omega_{z1} = \frac{1}{R_1 C_1}$$

and  $\omega_{p1} = \frac{1}{R_1 C_2}$

The closed loop transfer function can be obtained as

$$H_{closed}(s) = \frac{H_{open}(s)}{1 + H_{open}(s)} = \frac{\left(\frac{K_{vco}I_{cp}}{2\pi NC_{1}}\right)(1 + s/\omega_{z1})}{\frac{s^{3}}{\omega_{p1}} + s^{2} + \left(\frac{K_{vco}I_{cp}}{2\pi NC_{1}}\right)\frac{s}{\omega_{z1}} + \left(\frac{K_{vco}I_{cp}}{2\pi NC_{1}}\right)}$$

(2.11)

Normally, the pole  $\omega_{p1}$  is placed beyond the natural frequency  $\omega_n$  of the system. Therefore, Eqn. 2.11 reduces to a second order system given by Eqn. 2.12.

$$H_{closed}(s) = \frac{\left(\frac{K_{vco}I_{cp}}{2\pi NC_{1}}\right)(1 + sR_{1}C_{1})}{s^{2} + \left(\frac{K_{vco}I_{cp}R_{1}}{2\pi N_{1}}\right)s + \left(\frac{K_{vco}I_{cp}}{2\pi NC_{1}}\right)}$$

(2.12)

This can be compared with the classical second order equation given by Eqn. 2.13

$$H_{II}(s) = \frac{\omega_n^2}{s^2 + (2\xi\omega_n)s + \omega_n^2}$$

(2.13)

to obtain the critical design parameters given by Eqns. (2.14-16).

$$\omega_n = \sqrt{\frac{K_{vco}I_{cp}}{2\pi NC_1}}$$

(2.14)

$$\omega_{c} = \left(2\xi\omega_{n}\right) = \frac{K_{vco}I_{cp}R_{1}}{2\pi N}$$

(2.15)

$$\xi = \frac{R_1}{2} \sqrt{\frac{K_{vco} I_{cp} C_1}{2\pi N}}$$

(2.16)

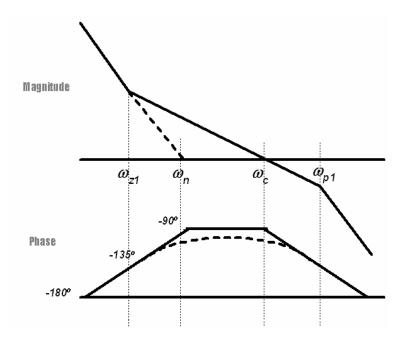

From Fig 2.10, it can be seen that the exact location of the pole  $\omega_{p1}$  and the zero  $\omega_{z1}$  affects the transient dynamics of the entire closed loop. From control theory [23], if

$$\omega_{z1} = \frac{\omega_c}{\alpha^2} \tag{2.17}$$

$$\omega_{p1} = \omega_c \cdot \alpha^2 \tag{2.18}$$

then,  $\alpha = 2$  yields  $\xi = 1$ ; the case for critical damping in a II order system. Critical damping leads to a fair compromise between settling time and overshoot.

Fig. 2.10 Pole-Zero Placement

#### 2.5.2 Design Procedure

The design procedure followed is optimized after several iterations. The initial set of assumptions are  $I_{cp}$ =20 µA and  $K_{vco}$ =150 MHz/V. There is a limit on how low the  $I_{cp}$  can be set. The leakage from the devices into the critical control line needs to be minimized. A lower current in the charge pump helps in increasing the output impedance of the charge pump.

A low sensitivity of the VCO helps in improving the spectral purity of the VCO by providing low gain to the ripples in the control voltage. It merits mention that the tuning range would be affected with the low sensitivity. Section 4 discusses this issue in detail. Moreover, the desired pole-zero placement technique in the loop filter outlined in the previous sub-section requires  $\xi = 1$ .

# 1. Loop Stability

The channel reference frequency is 5 MHz. For the continuous time approximation to be valid, Gardener's stability limit [22] is given by

$$\omega_{n}^{2} < \frac{\omega_{ref}^{2}}{\pi(\pi + \omega_{ref} / \omega_{z1})}$$

(2.19)

For a critically damped system,  $\omega_c \approx \frac{\omega_n^2}{\omega_{z1}}$ . Therefore, the Gardener's stability

limit is now given by

$$\omega_c < \frac{\omega_{ref}}{\pi (1 + \pi \omega_{z1} / \omega_{ref})}$$

(2.20)

A low loop bandwidth improves the spur attenuation and minimizes the noise bandwidth at the expense of a high settling time. It is related to the natural frequency of the PLL system by

$$\omega_n = \frac{\omega_c}{2\xi} \tag{2.21}$$

A natural frequency of 15 KHz is a good starting point in the design. This gives the loop bandwidth to be

$$\omega_c = 2\xi\omega_n = 2\pi \cdot 30Krps \tag{2.22}$$

The pole and zero placement technique for critical damping gives

$$\omega_{z1} = \frac{\omega_c}{2^2} = 2\pi \cdot (7.5) Krps \qquad (2.23)$$

$$\omega_{p1} = \omega_c \cdot 2^2 = 2\pi \cdot 120 Krps \tag{2.24}$$

The phase margin is given as

$$PM = \tan^{-1}\left(\frac{\omega_{c}}{\omega_{z1}}\right) - \tan^{-1}\left(\frac{\omega_{c}}{\omega_{p1}}\right) = \tan^{-1}\left(4\right) - \tan^{-1}\left(\frac{1}{4}\right) = 61.92^{\circ}$$

(2.25)

Using the above values, from Gardener's stability limit, we obtain

$$\omega_{c} < \frac{\omega_{ref}}{\pi (1 + \pi \omega_{z1} / \omega_{ref})} \approx \frac{\omega_{ref}}{\pi}$$

(2.26)

Thus, the minimum value of the loop bandwidth to satisfy the continuous time approximation is  $2\pi \cdot (1.584)Mrps$ . Thus, the actual loop bandwidth is around 52 times lower than the one stipulated by Gardener's stability limit.

## 2. Loop Filter Parameters

The natural frequency is given as

$$\omega_n = \sqrt{\frac{I_{cp}K_{vco}}{2\pi NC_1}} \Longrightarrow C_1 = \frac{I_{cp}K_{vco}}{2\pi N\omega_n^2}$$

(2.27)

$$\therefore C_1 = \frac{(20 \times 10^{-6}) \times (2\pi \times 150 \times 10^6)}{2\pi \times (976) \times (2\pi \times 15 \times 10^3)^2} = 346 \, pF$$

(2.28)

N is taken as an average of 960-992. It will be explained in Section 3 about the need for doubling the divide ratios.

$$\omega_{z1} = \frac{1}{R_1 C_1} \Longrightarrow R_1 = 61.33 K\Omega \tag{2.29}$$

$$\omega_{p1} = \frac{1}{R_1 C_2} \Longrightarrow C_2 = 21.625 \, pF \tag{2.30}$$

It can be seen that  $\frac{C_1}{C_2} = 16$ .

3. Settling time

For critically damped case, the settling time is given by [24-25]

$$t_{lock} = \frac{1}{\xi \omega_n} \ln \left( \frac{\Delta f}{\alpha f_0} \right)$$

(2.31)

where  $\Delta f$  is the maximum frequency switching, here 160 MHz

$\alpha$  is the desired frequency accuracy, here 40 ppm

It is found that  $t_{lock}$  is 71.4 µs, which is 37% of the actual specification. It must be remembered that the settling time equation is only approximate, and over-designing for the settling time is necessary.

# 2.5.3 System Level Verification

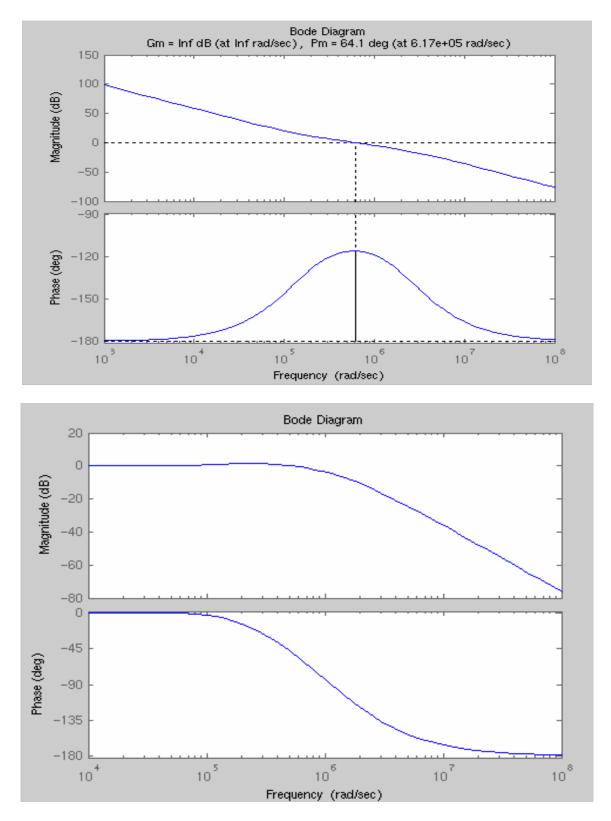

The above design is verified using MATLAB and SystemView. The open loop transfer function is given by

$$A_{OL} = \frac{K_{vco}I_{cp}}{2\pi C_1 N \cdot s^2} \left(\frac{\omega_{p1}}{\omega_{z1}}\right) \left\{\frac{s + \omega_{z1}}{s + \omega_{p1}}\right\} = \frac{1.61 \times 10^{12}}{s^2} \left\{\frac{s + 137 \times 10^6}{s + 2.6 \times 10^6}\right\}$$

(2.32)

Fig. 2.11. Bode Plots (a) Open Loop (b) Closed Loop for the PLL

The MATLAB Bode plots for the open loop and the closed loop of the designed PLL is are given in Fig. 2.11. The phase margin is found to be in agreement with the hand calculations. Further, it can be seen that the Bode plot of the error transfer function of the closed loop is as expected.

Transient response for impulse, step and ramp inputs can be obtained using MATLAB. However, the approximations behind Eqn. (2.32) must be remembered. This analysis gives a good starting point in the design.

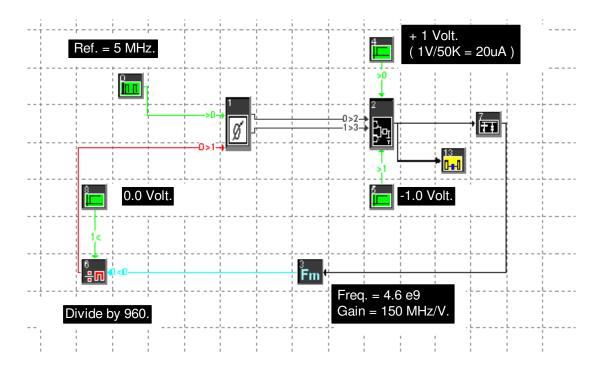

The SystemView setup is given in Fig. 2.12. Based on the loop filter parameters calculated in the previous sub-section and the assumed variables  $I_{cp}$  and  $K_{vco}$ , the given setup is simulated for settling behavior.

Token 0 provides the reference of 5 MHz for the PLL while token 1 is for the Phase/ Frequency detect operation. The charge pump is emulated using tokens 2, 4 and 5. Token 7 accounts for the loop filter in the design. The VCO is modeled using a frequency modulator with the given sensitivity and free running frequency using token 3. The dividers is modeled using token 6 and varies from 962-992 for the Zigbee operation. Token 13 is to tap the control voltage of the VCO to monitor the settling behavior of the PLL.

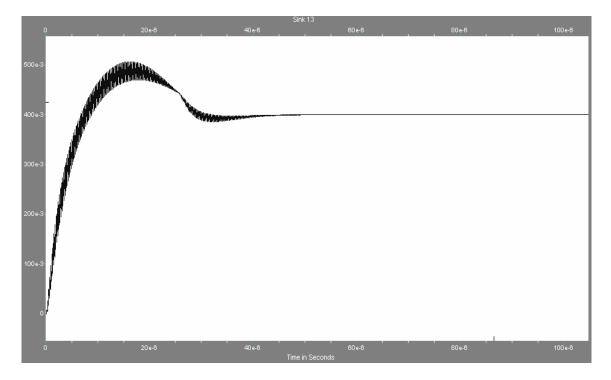

As per the setup given in Fig. 2.12, the VCO is initially operating at 4.6 GHz. The divide ratio is 960 and the reference is 5 MHz. The PLL now needs to lock to 4.8 GHz. Fig. 2.13 provides the transient response of the PLL by showing the control voltage settling behavior.

Fig. 2.12. SystemView Setup for PLL Design Verification

Fig. 2.13 Transient Settling Behavior for the PLL Using SystemView

It merits mention that the system level verification methods used do not account for the discrete nature of the PLL. The actual integrated circuit implementation needs to take into account various parasitic and non-ideal effects and are discussed where relevant in the subsequent sections. At the same time, the importance of the system level design needs to be emphasized.

This section lays the foundation for the actual practical implementation for the PLL based synthesizer. Other methods for system level simulations exist – Cadence based simulations using Verilog and ideal models, and Analog verilog coding. Non-idealities can also be introduced into the existing holistic models used in MATLAB and SystemView.

### **2.6 Literature Survey**

The frequency synthesizer is one of the crucial blocks of the transceiver. The entire translation in frequency is dependent on the LO provided by the synthesizer in the transceiver. It is one of the power-hungry blocks of the transceiver. Most synthesizers are implemented as integer-N or fractional-N PLL applications [24-29]. The locked tone of the PLL is used to synthesize multiple frequencies [30]. Further, injection locking phenomena is used for frequency synthesis [31].

The high-frequency blocks VCO and dividers have received special attention over the recent years [20, 21, 31-34]. Fast settling time [35-36], spur suppression [5, 37], and low jitter [38], spectral purity [39] have been important bottlenecks in the design of synthesizers. Dual-loop architectures for fast settling time are also popular [40-41]. Reference spur optimization techniques heavily depend on superior charge pump performance and excellent power routing and isolation from substrate noise. Spurs and phase noise are crucial in high-performance systems [27, 39].

The requirements for the synthesizer vary from one standard to another. Usually, in wireless systems, power consumption is a very critical issue, as it is always desired to have a long battery life. However, for systems that require high spectral purity, high power consumption in the VCO becomes inevitable to achieve such stringent phase noise specification [27, 39]. It has been shown that injection-locking phenomena can be used to achieve improved phase noise PLL systems [42]. Synthesizers in multi-standard transceiver applications have also been reported [43-44]. Thus, it can be seen that the synthesizer has been a research topic of constant focus and attention.

With the advent of technology scaling, supply voltages have decreased. The effect of scaling is pronounced in the design of high-performance synthesizers in wireless transceivers. On the other hand, technology scaling has increased the  $f_T$  of the devices, benefiting the design of high-performance of 2.4 GHz and 5 GHz systems. A complete integrated solution of a synthesizer with high spectral purity, spur suppression and low power consumption is a challenge in high  $f_T$  technologies.

Moreover, scaling reduces the tuning control voltage range of the VCO; thereby demanding a high VCO sensitivity [11]. On-chip voltage doubler is used to increase the tuning control voltage range in [45]. In charge-pump based PLL systems, the locking range is often limited by the tuning control voltage range [7]. Hence, for broadband synthesizers, it is important to achieve high tuning range [46].

Reference [3] reports a synthesizer for a low-data rate standard, similar to Zigbee. The use of true single phase clocking scheme in the prescaler is explored in [47]. An 802.11a synthesizer based on the principle of transformer coupling achieves a power consumption of 9.7 mW in [48]. Low-voltage design techniques have been incorporated in the design of a 1-V frequency synthesizer in [49]. Recently, a Zigbee frequency synthesizer has been reported with a power consumption of 22 mW in 0.18  $\mu$ m technology (based on simulation results) [5].

This work successfully explores the application of low sensitivity VCOs with a high tuning range using a TSMC 0.18  $\mu$ m CMOS process in a 5 GHz frequency synthesizer. It is also intended for applications in a 2.4 GHz Zigbee transceiver, requiring a low-power, low-cost complete integrated solution.

#### **3. FREQUENCY SYNTHESIZER DESIGN**

This section forms the crux of this thesis and deals with the practical design and implementation of a frequency synthesizer in a plain CMOS technology. It provides a practical solution to the development of the synthesizer after the system level progress made in Section 3. The architecture is given here, for the sake of completeness, and in more detail. The individual building blocks along with the germane implementation issues are discussed in this section. The VCO is discussed in more detail in the next section. The important layout and board-level issues are given along with the measurement results of the silicon prototype.

# **3.1 Synthesizer Architecture**

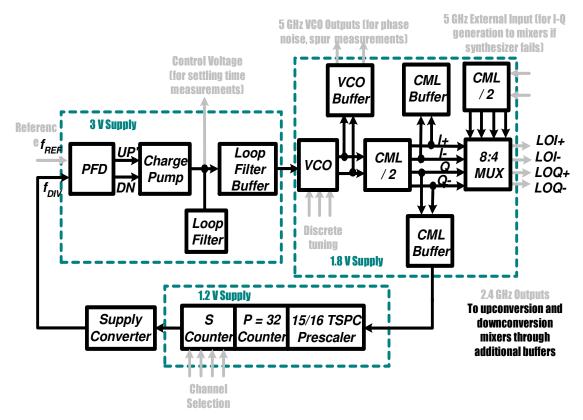

The integer-N PLL based synthesizer circuit implementation with all the building blocks is given in Fig. 3.1. As discussed in Section 2, the synthesizer can be broadly classified into three sub-systems for the purpose of design and efficient simulations. The three systems are (i) core analog system consisting of the phase/ frequency detector, charge pump, loop filter, loop filter buffer (ii) RF system of the voltage controlled oscillator and the CML divide-by-2 (iii) digital system consisting of the prescaler and pulse/ swallow counters. It merits mention that the three sub-systems have different power supplies. It is usually a good practice to isolate the power supplies of the analog and the digital sections to minimize noise interactions through the medium of the substrate.

For purposes of measuring settling time and control voltage during the lock state of the PLL, the output voltage node of the charge pump is tapped. Open-drain buffers are used to "tap" the high frequency outputs of the VCO (4.8 GHz) and the CML divide-by-2 (2.4 GHz). It merits mention that the main purpose of a synthesizer is the generation of I and Q components of the LO for upconversion/ downconversion at the mixer. For the worst case scenario of the synthesizer failing to lock to the required channel frequency, we need to ensure that the mixer still gets the LO input. Therefore, an additional CML divide-by-2 is provided to generate I and Q components from an external source for it is difficult to obtain them directly from the instrument.

Fig. 3.1 Architecture of the Frequency Synthesizer

The output of the CML divide-by-2 used in the synthesizer loop is multiplexed with the output of the CML divide-by-2 for test purposes. Additionally, this test CML

divide-by-2 can be used for the characterization of a stand-alone CML divide-by-2. The power consumption of the frequency synthesizer need not include the test CML divide-by-2, the VCO output buffer for test purposes, the portion of the multiplexer driving the test CML divide-by-2.

### **3.2 Phase/Frequency Detector**

### 3.2.1 Topology

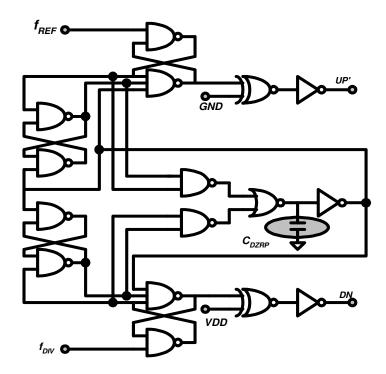

A *nand*-based tri-state Phase/Frequency Detector (PFD) is used to perform the role of phase/ frequency detection in the synthesizer. The PFD compares the divider output with that of the reference clock. It is capable of frequency detection during the coarse acquisition phase and phase detection during the fine acquisition phase. Other topologies exist for phase/ frequency detection.

The implemented scheme is capable of performing both frequency and phase detections. The only drawback of this approach is the frequency limitation determined by the static CMOS implementation (typically 500 MHz). We would be operating at 5 MHz and this architecture is best suited for such synthesizer applications. The selection of the scheme is entirely dependent on the typical application.

This principle of phase/ frequency detection fails in a clock and data recovery (CDR) environment. For high frequency phase detection for random data in CDR circuits, Hogge detectors are used [50-51, 11-12]. Gilbert cell based mixers and XOR gates are used for high frequency phase detectors in synthesizers [10].

The PFD generates two important signals, namely the *UP* and *DN*, which represent the difference in phase/ frequency of the two inputs. The two signals are named figuratively. The *UP* signal is used as an indicator for increasing the VCO frequency

Fig. 3.2 Topology of the Phase/ Frequency Detector

We need a method that converts the critical phase/ frequency difference information in the UP and DN signals to useful voltage related information. The charge pump along with the loop filter performs this operation. It is seen that the final optimization be done with the three blocks in cascade. These three blocks need to be considered together using the tool of transient analysis. Usually,  $\overline{UP}$  and DN are connected to the PMOS and NMOS transistors of the charge pump. The timing mismatch between  $\overline{UP}$  and DN needs to be minimized. This is done by the use of EXOR gates, keeping these Boolean identities in mind:

$$X \oplus 1 = X \text{ and } X \oplus 0 = X \tag{3.1, 3.2}$$

Further, these individual gates must be laid out in a symmetric fashion to minimize the timing delays. Fig. 3.2 gives the gate level schematic of the PFD.

### 3.2.2 Dead zone

Dead zone is one of the crucial aspects of the PFD design and is elaborately discussed in [10]. It can be briefly summarized as that region of operation of the PFD where the PLL loop fails to respond to the phase error at the input. Thus, the critical VCO output is allowed to drift away in open loop. In practical integrated circuit implementations, the dead zone is alleviated by the dead-zone removal pulse (DZRP). When both UP and DN is ON, the reset path becomes active and forces them to the OFF states. The finite gate delays in the reset path are responsible for  $\tau_{DZRP}$ . The DZRP has its own merit and drawback in the overall synthesizer; hence  $\tau_{DZRP}$  must be judiciously set.

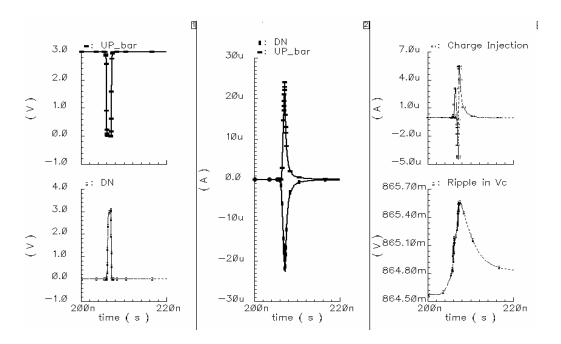

When the PLL is in the locked state, the divider output and the reference phase are identical in frequency with a possible constant phase error between them. In the absence of any DZRP, the system is in open loop. The PFD-Charge Pump fails to track the drift in the VCO. Consider the hypothetical situation where UP is ON and DN is OFF. Then, DN is becoming ON. For a small  $\tau_{DZRP}$ , there is unequal charge injection into the loop filter through the charge pump. This leads to ripples in the control voltage and spurs at the output. If the charge injected is high, the system might be temporarily out of lock. If  $\tau_{DZRP}$  is appropriately sized, the UP and DN conduct equally. Ideally, no charge is injected into the loop filter. However, during this time, the critical control voltage is susceptible to the noise and supply variations from the power rails. Hence, a high  $\tau_{DZRP}$  is not desirable; in direct contradiction to the requirement from a current matching point of view. It merits mention that DZRP forces the system to be in closed loop during the locked state. Thus, the phase comparison during each reference prevents the excessive drifting of the VCO [11].

Fig. 3.3 Ripples in the Control Voltage

Fig. 3.3 gives the post-layout transient simulation results of the core analog system consisting of the PFD, charge pump and loop filter. This design uses  $\tau_{DZRP}$  of 2ns, which translates to 1% of the total reference time. The capacitor  $C_{DZRP}$  (equal to 60fF)

placed on purpose in the delay path helps in sizing the DZRP.  $\tau_{DZRP}$  varies with the process corners and the worst case is during the fast corner, where it is around 1.4 ns.

A small  $\tau_{DZRP}$  requires a high charging time for the UP and DN switches of the charge pump, thereby imposing added performance requirements. Further it can be seen from Fig. 3.3 that current mismatch is inevitable due to realistic charging times for the switches of the charge pump. The unequal charge injection leads to ripples in the control voltage line. These ripples are responsible for the appearance of reference spurs at the VCO spectrum.

| PHASE FREQUENCY DETECTOR           | OR – SPECIFICATIONS |  |  |

|------------------------------------|---------------------|--|--|

| Performance Metric                 | Value               |  |  |

| Gain                               | $1/2\pi$            |  |  |

| Reference Input Frequency          | 5 MHz               |  |  |

| $	au_{\it DZRP}$                   | 2 ns.               |  |  |

| Timing Mismatch between UP' and DN | Minimum             |  |  |

| Supply Voltage                     | 3 V                 |  |  |

TABLE V

Phase Frequency Detector – Specification

In the next section, we will discuss the non-ideal effects of the charge pump, especially during  $\tau_{DZRP}$ . The non-ideal effects further deteriorate the performance of the charge pump during DZRP. Finally, the phase frequency detector specifications are summarized in Table V.

## 3.3 Charge Pump

Functionally, a charge pump transforms the time domain information present in the UP and DN pulses of the PFD to voltage related information by pumping/ extracting charge into/ from the loop filter. The simplest charge pump topology is given in Fig. 3.4(a). It consists of a capacitive load C<sub>1</sub> that contributes to a pole at the origin (Eqn. 3.3). Thus, if one of the signals were to be absent at the input of the PFD, the infinite gain at DC will make the control voltage hit the supply rails. Fig. 3.4(b) gives an accurate charge pump model with a realistic loop filter. As seen from Eqn. 3.4, the premise of a pole at the origin continues to hold true [11].

Fig. 3.4 Charge Pump Model with the Loop Filter (a) Conceptual (b) Actual

$$K_{cp} = \frac{I_{cp}}{2\pi (sC_1)} \tag{3.3}$$

$$K_{cp} = \frac{I_{cp}}{2\pi} \left( \left\{ R_1 + \frac{1}{sC_1} \right\} \left\| \frac{1}{sC_2} \right\} \approx \frac{I_{cp}}{2\pi s} \frac{(1 + s/\omega_{z1})}{(1 + s/\omega_{p1})} \right)$$

(3.4)

The most important characteristic of a charge-pump is its immunity to variations at its output node, which is the control voltage of the synthesizer. Conventional charge pumps suffer from the issues of high sensitivity to the output node voltage and charge sharing. Moreover, for accurate current matching during the UP and DN stages, it is best to use low-voltage cascode current mirrors. As discussed in the previous section, accurate current matching is very critical during  $\tau_{DZRP}$ . It becomes extremely important to have the behavior of the UP and DN current sources immune to the variations in the output node (the control voltage of the VCO). The synthesizer operation makes the variation in the output node of the charge pump essential [11].

For purposes of obtaining a reasonable tuning range at low sensitivity for the VCO, we need to have a high tuning control voltage range. In a charge pump design at 1.8V, it will be impossible to obtain a tuning control voltage range of 1.5V as desired. Thus to achieve a good tuning control voltage range and current matching, the charge pump is implemented in a 3V domain using 3V devices. The choice of 3V supply is justified because of the improved performance at the cost of a minimal increase in the power consumption. From the system level design procedure in Section 2, the charge pump current is taken as  $20 \,\mu$ A.

The charge pump is responsible for the reference spurs seen at the output of the VCO. An accurate well-designed charge pump is essential for minimizing spurs at the output. The spurs appear at the output of the synthesizer at an offset frequency equal to that of the reference. When the PLL is in locked condition, the DZRP appears at a frequency equal to the reference. The two currents related to UP and DN need to be matched very well.

From Fig. 3.3, it can be seen that realistic circuit implementations have a finite mismatch because of difference in charging and discharging of the PMOS and NMOS

devices. This finite mismatch leads to ripples in the control voltage. The ripples modulate the control voltage, which leads to the spurs at the output spectrum. Thus, the presence of reference spurs is an inherent drawback of the PFD-CP based PLL.

Fig. 3.5 gives the circuit implementation of the charge pump [53]. The charge pump operates with a supply voltage of 3V. It is important to note the range of output control voltages allowable for the charge pump. We would like to minimize the dependence of the UP and DN currents on the output node voltage. Low-voltage cascode mirrors are used to minimize the headroom and improve the matching between the UP and DN transistors.

Fig. 3.5 Charge Pump – Topology