## A LOW POWER, HIGH DYNAMIC RANGE, BROADBAND VARIABLE GAIN AMPLIFIER FOR AN ULTRA WIDEBAND RECEIVER

A Thesis

by

LIN CHEN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

May 2006

Major Subject: Electrical Engineering

# A LOW POWER, HIGH DYNAMIC RANGE, BROADBAND VARIABLE GAIN AMPLIFIER FOR AN ULTRA WIDEBAND RECEIVER

A Thesis

by

#### LIN CHEN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

Approved by:

Chair of Committee, Jose Silva-Martinez

Committee Members, Edgar Sanchez-Sinencio

Laszlo Kish

Charles S. Lessard

Head of Department, Costas Georghiades

May 2006

Major Subject: Electrical Engineering

#### **ABSTRACT**

A Low Power, High Dynamic Range, Broadband Variable Gain Amplifier for an Ultra Wideband Receiver.

(May 2006)

Lin Chen, B.E., Tsinghua University; M.E., Cornell University

Chair of Advisory Committee: Dr. Jose Silva-Martinez

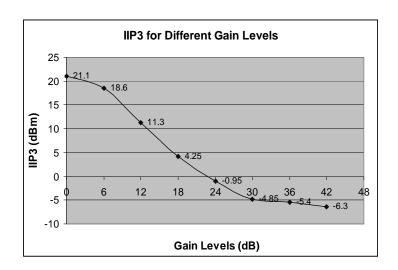

A fully differential Complementary Metal-Oxide Semiconductor (CMOS) Variable Gain Amplifier (VGA) consisting of complementary differential pairs with source degeneration, a current gain stage with programmable current mirror, and resistor loads is designed for high frequency and low power communication applications, such as an Ultra Wideband (UWB) receiver system. The gain can be programmed from 0dB to 42dB in 2dB increments with -3dB bandwidth greater than 425MHz for the entire range of gain. The 3<sup>rd</sup>order intercept point (IIP3) is above -13.6dBm for 1Vpp differential input and output voltages. These low distortion broadband features benefit from the large linear range of the differential pair with source degeneration and the low impedance internal nodes in the current gain stages. In addition, common-mode feedback is not required because of these low impedance nodes. Due to the power efficient complementary differential pairs in the input stage, power consumption is minimized (9.5mW) for all gain steps. The gain control scheme includes fine tuning (2dB/step) by changing the bias voltage of the proposed programmable current mirror, and coarse tuning (14dB/step) by switching on/off the source degeneration resistors in the differential pairs. A capacitive frequency compensation scheme is used to further extend the VGA bandwidth.

## DEDICATION

To my parents and my sister for their unconditional support and love

#### **ACKNOWLEDGEMENTS**

I would like to express many thanks and much appreciation to Dr. Jose Silva-Martinez, for his kindly guidance and attention to details throughout my study. I am also grateful to my thesis committee members, Dr. Edgar Sanchez-Sinencio, Dr. Laszlo Kish and Dr. Charles Lessard, for providing additional insight throughout this process. I would also like to thank Johnny Lee, Jun He, Jason Wardlaw, Xiaohua Fan, and Haitao Tong for their help on proofreading my thesis draft. My gratitude goes to all of the faculty and students of the Analog and Mixed Signal group who have raised my level of, and enthusiasm for, knowledge, and have aided me in reaching my goals. Most of all, I would like to thank my parents and my sister for their unconditional support, trust, encouragement and love through the years.

## TABLE OF CONTENTS

|            |                                                                                                                                                                                                                  | Page           |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABSTRAC    | Γ                                                                                                                                                                                                                | iii            |

| DEDICATION | ON                                                                                                                                                                                                               | v              |

| ACKNOWI    | LEDGEMENTS                                                                                                                                                                                                       | vi             |

| TABLE OF   | CONTENTS                                                                                                                                                                                                         | vii            |

| LIST OF FI | GURES                                                                                                                                                                                                            | ix             |

| LIST OF TA | ABLES                                                                                                                                                                                                            | xiii           |

| CHAPTER    |                                                                                                                                                                                                                  |                |

| Ι          | INTRODUCTION                                                                                                                                                                                                     | 1              |

| II         | BASIC VGA STRUCTURES                                                                                                                                                                                             | 4              |

|            | II.1 VGA structures  II.1.1 Differential pair with diode-connected loads  II.1.2 Analog multiplier  II.1.3 Differential pair with source degeneration  II.1.4 Complementary differential pairs with source       | 4<br>12        |

|            | degeneration II.2 Comparison of the commonly used VGA structures                                                                                                                                                 |                |

| III        | PROGRAMMABLE CURRENT MIRROR                                                                                                                                                                                      | 22             |

|            | III.1 Review of simple current mirror III.2 Proposed programmable current mirror III.2.1 AC response of programmable current mirror III.2.2 Programmability of the programmable current mirror III.3 Conclusions | 24<br>29<br>35 |

| IV         | DESIGN CONSIDERATIONS OF THE PROPOSED VGA                                                                                                                                                                        | 38             |

|            | IV.1 VGA design challenges and motivations                                                                                                                                                                       |                |

| CHAPTER  |                                                                 | Page |

|----------|-----------------------------------------------------------------|------|

|          | IV.3.1 Gain control scheme                                      | 43   |

|          | IV.3.2 Input stage complementary differential pairs with source |      |

|          | degeneration                                                    | 47   |

|          | IV.3.3 Current gain stage—programmable current mirror           | 49   |

|          | IV.3.4 Frequency compensation scheme                            | 51   |

|          | IV.3.5 DC offset cancellation                                   | 57   |

|          | IV.3.6 Digital control circuit                                  | 57   |

|          | IV.3.7 The dimension and bias current for the VGA               | 58   |

|          | IV.4 Conclusion                                                 | 59   |

| V        | SUMMARY OF RESULTS                                              | 60   |

|          | V.1 Design summary                                              | 60   |

|          | V.2 Simulation setup                                            | 60   |

|          | V.3 Simulation results                                          | 63   |

|          | V.3.1 Explanation of simulation terminologies                   | 63   |

|          | V.3.2 Layout                                                    | 67   |

|          | V.3.3 AC response                                               | 68   |

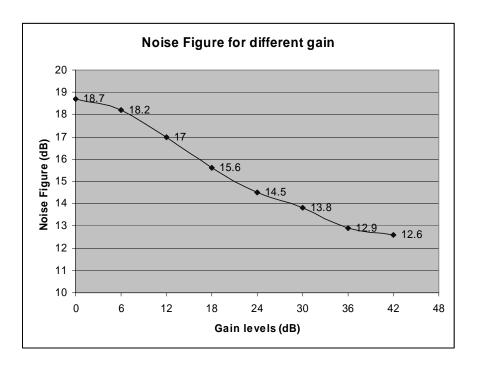

|          | V.3.4 Noise                                                     | 73   |

|          | V.3.5 Linearity                                                 | 75   |

|          | V.3.6 Power consumption                                         | 77   |

|          | V.4 Experimental results                                        | 77   |

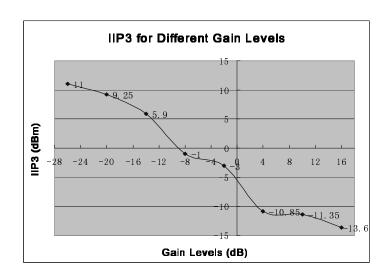

|          | V.4.1 Experimental results for the AC response of the VGA       |      |

|          | V.4.2 Experimental results of the IIP3                          | 86   |

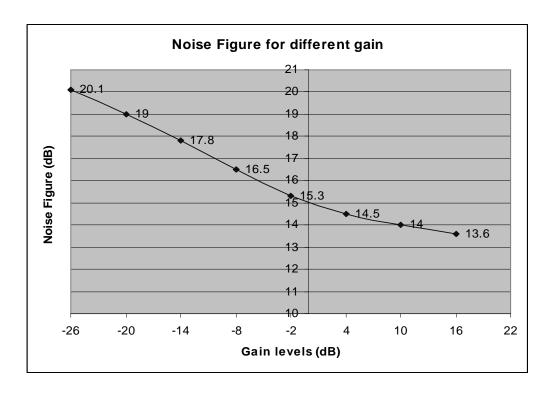

|          | V.4.3 Noise characterization                                    | 88   |

|          | V.5 Summary of results and comparison                           | 92   |

| VI       | CONCLUSION                                                      | 95   |

| REFERENC | CES                                                             | 97   |

| APPENDIX | A                                                               | 99   |

| APPENDIX | B                                                               | 102  |

| VITA     |                                                                 | 107  |

## LIST OF FIGURES

|         |                                                              | Page |

|---------|--------------------------------------------------------------|------|

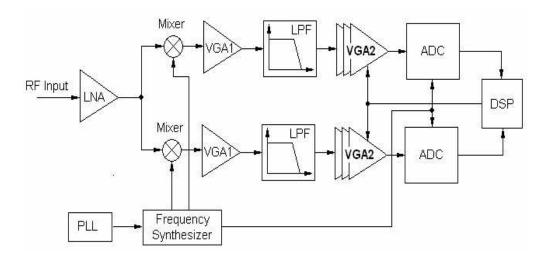

| Fig 1.1 | Proposed UWB receiver architecture                           | 2    |

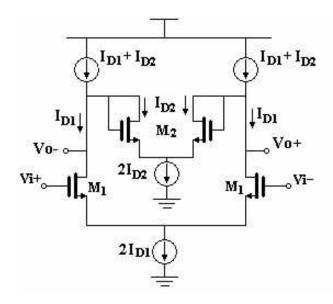

| Fig 2.1 | Differential pair with diode-connected loads                 | 5    |

| Fig 2.2 | Pole location of the differential pair with diode-connected  |      |

|         | loads                                                        | . 7  |

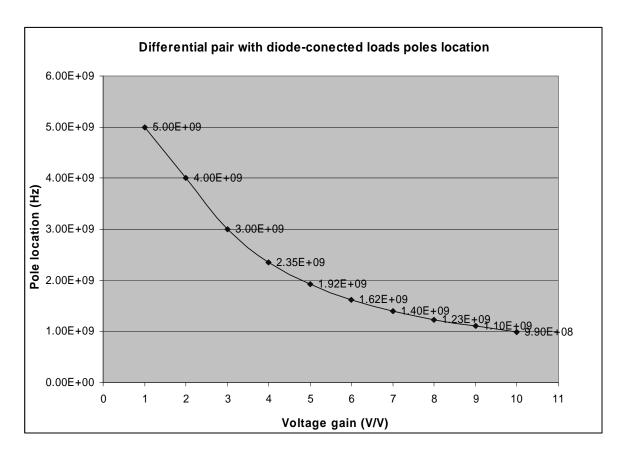

| Fig 2.3 | Differential pair with diode-connected loads pole location   |      |

|         | vs. voltage gain                                             | 9    |

| Fig 2.4 | Linear range of the differential pair with diode-connected   |      |

|         | loads                                                        | 10   |

| Fig 2.5 | Analog multiplier used as VGA                                | 12   |

| Fig 2.6 | Multiplier with current mirror load                          | 13   |

| Fig 2.7 | Block diagram of cross-couple transconductors multiplier     | 15   |

| Fig 2.8 | Differential pair with source degeneration                   | 16   |

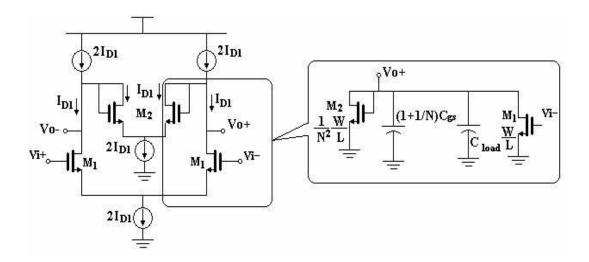

| Fig 2.9 | Complementary differential pair with source degeneration     | 18   |

| Fig 3.1 | Simple current mirror                                        | 22   |

| Fig 3.2 | Programmable current mirror                                  | 24   |

| Fig 3.3 | V <sub>b</sub> generation for programmable current mirror    | 26   |

| Fig 3.4 | Dimensions of the bias circuits bias transistors to generate |      |

|         | seven gain steps for programmable current mirror             | 29   |

| Fig 3.5 | Programmable current mirror low frequency model              | 30   |

|          |                                                                      | Page |

|----------|----------------------------------------------------------------------|------|

| Fig 3.6  | Programmable current mirror high frequency operation                 |      |

|          | model                                                                | 31   |

| Fig 3.7  | Setup for testing f <sub>-3dB</sub> of the current mirror            | 34   |

| Fig 3.8  | $f_{\text{-3dB}}$ of the simple current mirror vs. that of the       |      |

|          | programmable current mirror                                          | 35   |

| Fig 3.9  | Simple current mirror to implement different current gain            | 36   |

| Fig 4.1  | System-level architecture of the proposed VGA                        | 40   |

| Fig 4.2  | Complementary differential pairs with source degeneration            | 40   |

| Fig 4.3  | Programmable current mirror and DC offset cancellation               | 41   |

| Fig 4.4  | Capacitive frequency compensation                                    | 42   |

| Fig 4.5  | Block diagram of the proposed VGA                                    | 43   |

| Fig 4.6  | Source degeneration resistors and controlling switches               |      |

|          | configuration                                                        | 44   |

| Fig 4.7  | Simulation setup for multi-stage programmable current                |      |

|          | mirror                                                               | 50   |

| Fig 4.8  | $f_{\text{-3dB}}$ of the multi-stage programmable current mirror vs. |      |

|          | current gain                                                         | 51   |

| Fig 4.9  | Simplified schematic of the programmable current mirror              | 52   |

| Fig 4.10 | Single-ended version of the compensation circuit and its             |      |

|          | small signal model                                                   | 53   |

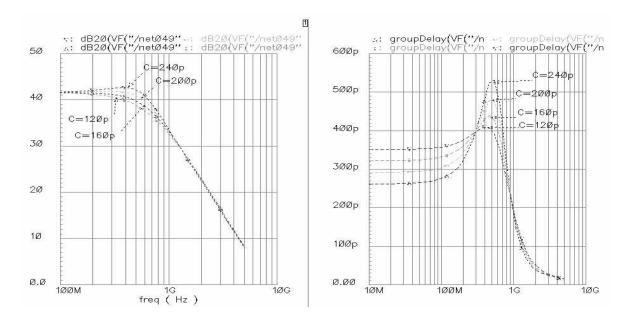

| Fig 4.11 | Compensation effects on the current mirror                           | 54   |

| Fig 4.12 | Capacitance variation effects on frequency response                  | 55   |

|          |                                                          | Page |

|----------|----------------------------------------------------------|------|

| Fig 4.13 | g <sub>mc</sub> variation effects on frequency response  | 55   |

| Fig 4.14 | Implementation of the capacitive frequency compensation  | 56   |

| Fig 4.15 | Digital control circuit.                                 | 58   |

| Fig 5.1  | Simulation setup                                         | 61   |

| Fig 5.2  | Layout view of the I/Q channels of the VGA               | 67   |

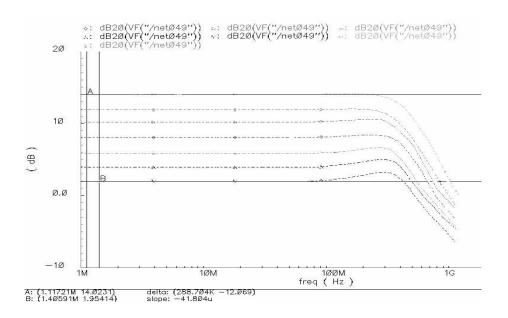

| Fig 5.3  | Gain steps from 30dB to 42dB.                            | 70   |

| Fig 5.4  | Gain steps from 16dB to 28dB                             | 70   |

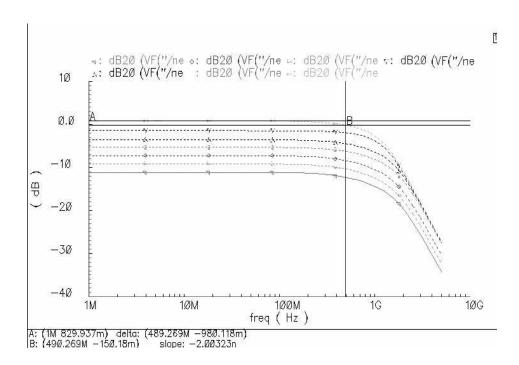

| Fig 5.5  | Gain steps from 0dB to 14dB                              | 71   |

| Fig 5.6  | Gain steps from 2dB to 16dB                              | 71   |

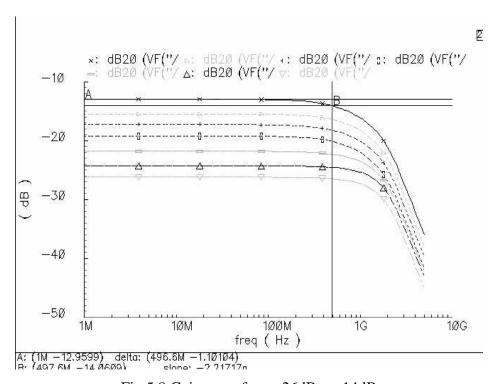

| Fig 5.7  | Gain steps from -12dB to 0dB                             | 72   |

| Fig 5.8  | Gain steps from -26dB to -14dB                           | 72   |

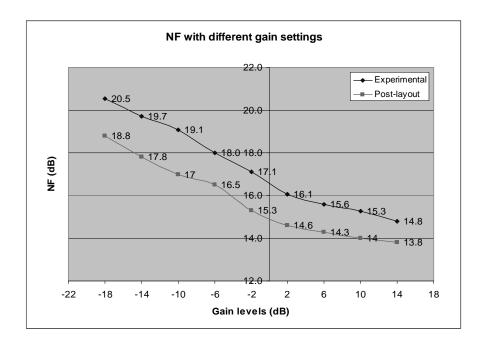

| Fig 5.9  | Noise Figure for different gain levels                   | 74   |

| Fig 5.10 | IIP3 for different gain levels                           | 76   |

| Fig 5.11 | Power consumption                                        | 77   |

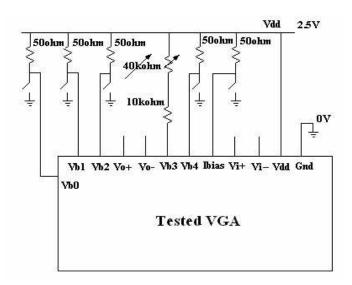

| Fig 5.12 | VGA testing pins arrangement                             | 77   |

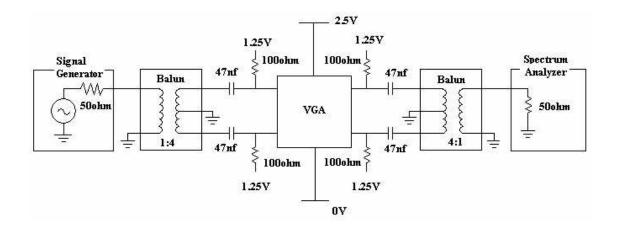

| Fig 5.13 | VGA inputs/outputs testing setup                         | 78   |

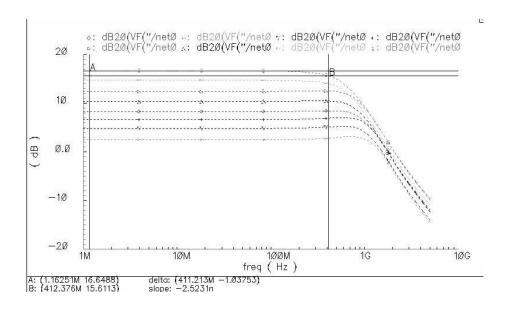

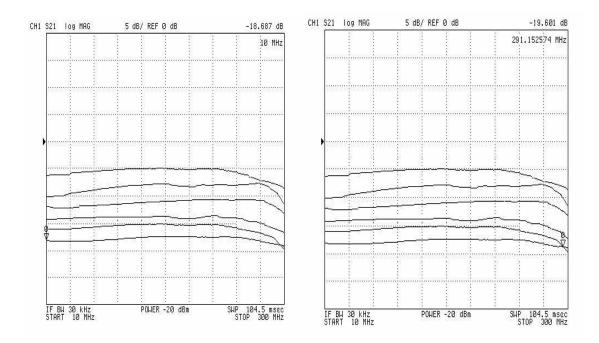

| Fig 5.14 | Frequency response of gain setting of 14, 12, 10, 8, and |      |

|          | 6dB                                                      | 82   |

| Fig 5.15 | Gain setting of 4, 2, 0, -2, -4, and -6dB                | 83   |

| Fig 5.16 | Gain setting of -8, -10, -12, -14, -16, and -18dB        | 84   |

|          |                                                                  | Page |

|----------|------------------------------------------------------------------|------|

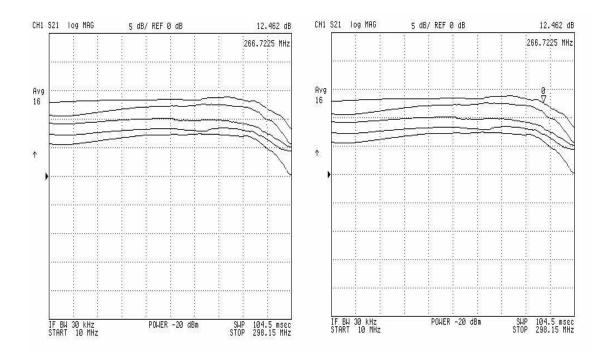

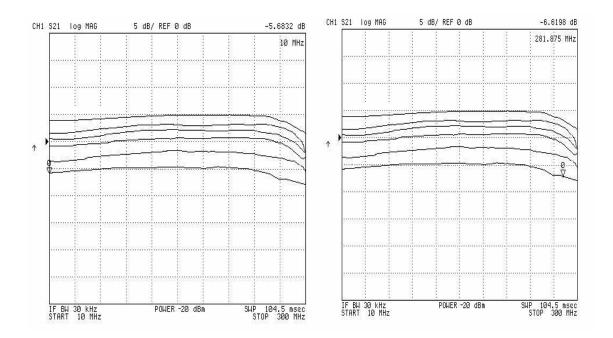

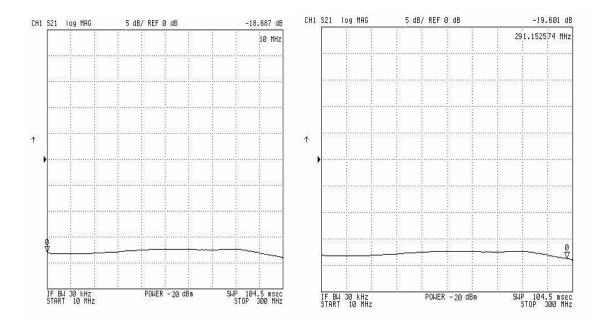

| Fig 5.17 | Gain setting of -18dB: $Av(0) = -18.687dB$ , $f_{-1dB} =$        |      |

|          | 291.15MHz                                                        | 85   |

| Fig 518  | Gain setting of 14dB: $Av(0) = 13.561dB$ , $f_{-1dB} = 266.7MHz$ | 85   |

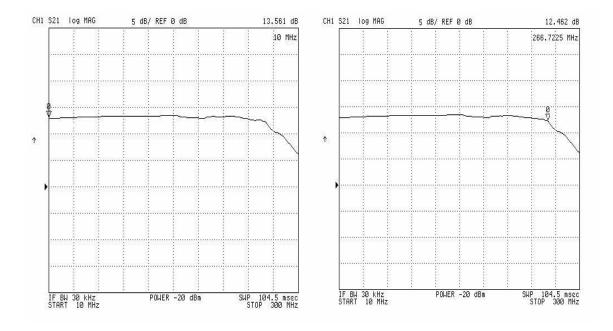

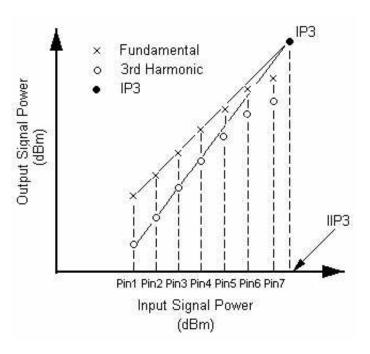

| Fig 5.19 | Measure IIP3 with interpolation                                  | 86   |

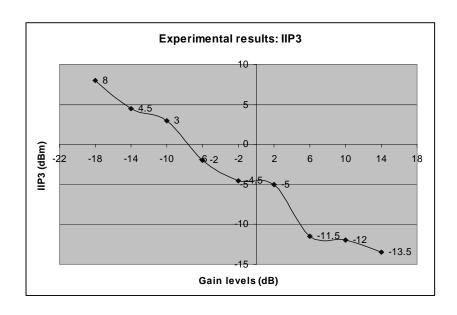

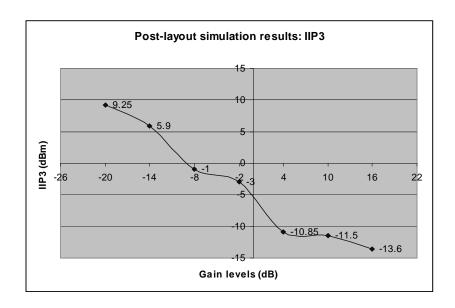

| Fig 5.20 | Testing results of IIP3 vs. gain levels                          | 87   |

| Fig 5.21 | Post-layout results of IIP3 vs. gain levels                      | 88   |

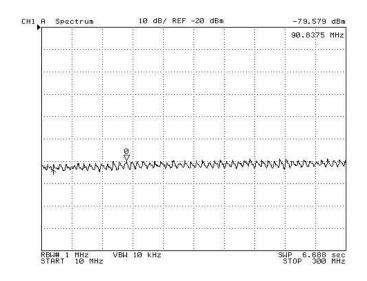

| Fig 5.22 | Av(0) = 14dB, equivalent output noise level = -79.6dBm,          |      |

|          | NF = 14.8dB                                                      | 90   |

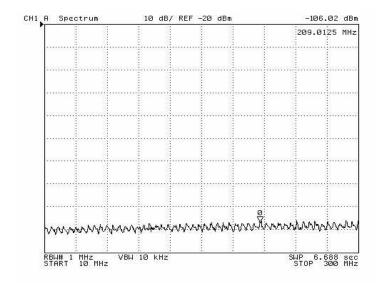

| Fig 5.23 | Av(0) = -18dB, equivalent output noise level = $-106dBm$ ,       |      |

|          | NF = 20.53dB                                                     | 90   |

| Fig 5.24 | Noise Figure (NF): experimental result vs. post-layout           |      |

|          | simulation results                                               | 91   |

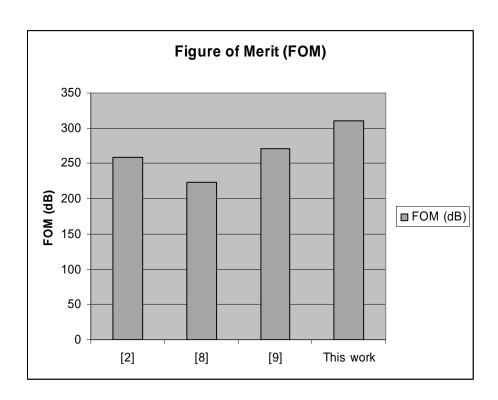

| Fig 5.25 | Figure of Merit (FOM) comparison                                 | 93   |

## LIST OF TABLES

|                                                                      | Page |

|----------------------------------------------------------------------|------|

| Table 1.1 VGA design specifications                                  | 2    |

| Table 3.1 Dimensions of the bias circuits                            | 29   |

| Table 3.2 Dominant poles comparison between programmable and         |      |

| simple current mirror                                                | 32   |

| Table 3.3 Current mirror's f <sub>-3dB</sub> testing setup           | 34   |

| Table 3.4 Current mirror comparison                                  | 37   |

| Table 4.1 VGA specifications                                         | 38   |

| Table 4.2 Coarse tuning steps vs. number of resistors/switches       |      |

| required                                                             | 44   |

| Table 4.3 Coarse/fine tuning combinations                            | 45   |

| Table 4.4 Gain vs. bias transistor mapping                           | 47   |

| Table 4.5 Dimension of the capacitive frequency compensation         | 57   |

| Table 4.6 Dimensions and bias currents of the components of the      |      |

| VGA in the signal path                                               | 58   |

| Table 4.7 Dimensions for the transistors in the bias control circuit | 59   |

| Table 5.1 Design specifications for VGA                              | 60   |

| Table 5.2 Dimensions of the VGAs for different setups                | 62   |

| Table 5.3 Post-layout AC response simulation results vs. system      |      |

| requirements                                                         | 68   |

| Table 5.4 AC response                                                | 69   |

| Table 5.5 Testing results for VGA AC response                        | 81   |

|                                            | Page |

|--------------------------------------------|------|

| Table 5.6 IIP3 testing results             | 87   |

| Table 5.7 Figure of Merit (FOM) comparison | 93   |

#### **CHAPTER I**

#### **INTRODUCTION**

A Variable Gain Amplifier (VGA) is needed in many baseband circuits for communication applications. For example, in a RF receiver, it is required to use a VGA between the filter and the analog to digital converter (ADC), to adjust the output signals from the filter to the required input signal level of the ADC; hence, providing the largest signal-to-noise ratio to the ADC stage and improving the overall dynamic range of the receiver.

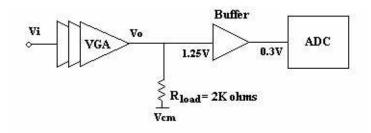

A Multi-Band Orthogonal-Frequency-Division-Multiplexing (MB-OFDM) based Ultra-Wideband (UWB) receiver system is widely adapted in the industry. The analog baseband of the receiver consists of a VGA between the low pass filter and the ADC (VGA2 as shown in Fig 1.1). This VGA must attain a wide bandwidth (250MHz) with minimum noise and power consumption. In addition, due to the characteristics of the OFDM communication system, the receiver's group delay variation within the band of interest should be reduced as much as possible. Since the VGA is used before the ADC, bandwidth and linearity requirements should be comparable with those of the ADC; otherwise, the performance of the ADC will be degraded. The specifications of this VGA are shown in Table 1.1.

Style and format follow IEEE Journal of Solid-State Circuits.

Fig 1.1 Proposed UWB receiver architecture

| Technology | Gain   | Band              | width             | Linearity | Noise  | Group Delay | Power |

|------------|--------|-------------------|-------------------|-----------|--------|-------------|-------|

|            | Range  | (MHz)             |                   | IIP3      | Figure | Variation   | (mW)  |

|            | (dB)   | f <sub>-1dB</sub> | f <sub>-3dB</sub> | (dBm)     | (dB)   | (pS)        |       |

| IBM6HP     | 0 ~ 42 | >264              | >350              | >-15      | <25    | <200        | <20   |

| 0.25um     |        |                   |                   |           |        |             |       |

| CMOS       |        |                   |                   |           |        |             |       |

Table 1.1 VGA design specifications

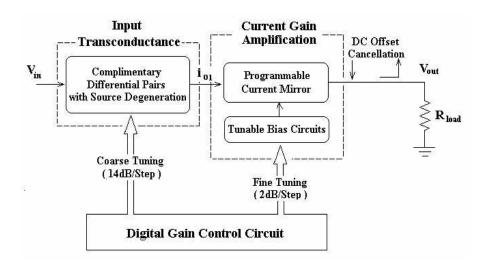

The proposed VGA uses a CMOS fully differential architecture. It includes complementary differential pairs with source degeneration as its input transconductor to convert the input voltage into current, then a programmable current mirror as its current gain stage to further amplify the current, and fixed load resistors to provide the linear current-to-voltage conversion at the output of the VGA. Due to the power efficient complementary differential pairs as the input stage, the power consumption is minimized to a very low level (<10mW) for all gain steps. The gain control scheme consists of fine

tuning (2dB/step) by changing the bias current voltage of the proposed programmable current mirror, and coarse tuning (14dB/step) by connecting/disconnecting the source degeneration resistors in the complementary differential pairs. Capacitive frequency compensation scheme is used to further extend the VGA bandwidth. The DC offset cancellation is implemented to eliminate the offset voltage and fix the DC voltage level at the output of VGA.

This thesis is organized as follows. In Chapter II, several VGA basic architectures are discussed. Since the proposed architecture is based on a programmable current mirror, DC and AC characteristics of the simple current mirror and the programmable current mirror are analyzed in Chapter III. The proposed VGA is presented in Chapter IV, and Chapter V contains the simulation and experimental results of the VGA. Finally, some conclusions are given in the last chapter.

#### CHAPTER II

#### **BASIC VGA STRUCTURES**

This chapter starts with an introduction of the commonly used VGA structures. The gain control schemes, the linearization techniques, and the power consumption of each structure have been discussed and their advantages and drawbacks are compared. The study suggests that a new approach must be introduced because some requirements for the UWB system, such as low power consumption and very wide bandwidth, cannot be achieved with the current structures.

#### II.1 VGA structures

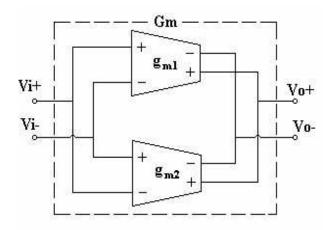

There are several commonly used VGA structures: (1) differential pair with diode-connected loads; (2) analog multiplier; (3) differential pair with source degeneration.

The performance of each structure is studied in the following sessions.

#### II.1.1 Differential pair with diode-connected loads

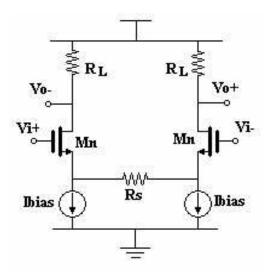

Amplifiers based on differential pair with diode-connected loads have been used for the design of VGAs [1]-[2]. As shown in Fig 2.1, the input voltage signal is converted into current using a non-linear differential pair, and converted back into voltage using a load based on another differential pair with a smaller transconductance.

Fig 2.1 Differential pair with diode-connected loads

The DC voltage gain  $A_v(0)$  of this topology is given by

$$A_{V}(0) = -\frac{g_{m1}}{g_{m2}} = -\frac{\sqrt{\left(\frac{W}{L}\right)_{1} \frac{I_{D1}}{2}} \sqrt{1 - \frac{1}{4} \left(\frac{V_{in}}{V_{DSAT1}}\right)^{2}}}{\sqrt{\left(\frac{W}{L}\right)_{2} \frac{I_{D2}}{2}} \sqrt{1 - \frac{1}{4} \left(\frac{V_{out}}{V_{DSAT2}}\right)^{2}}}$$

(2.1)

where  $V_{DSAT1}$  and  $V_{DSAT2}$  are the saturation voltages ( $V_{DSAT} = V_{GS} - V_{th}$ ) for  $M_1$  and  $M_2$  respectively, and (W/L)<sub>1</sub> and (W/L)<sub>2</sub> are the aspect ratios of  $M_1$  and  $M_2$  respectively.

If

$$\frac{1}{4} \left( \frac{V_{in}}{V_{DSAT1}} \right)^2$$

and  $\frac{1}{4} \left( \frac{V_{out}}{V_{DSAT2}} \right)^2 <<1$ , from equation 2.1, yields

$$A_{V}(0) = -\frac{\sqrt{\left(\frac{W}{L}\right)_{1}}I_{D1}}{\sqrt{\left(\frac{W}{L}\right)_{2}}I_{D2}}$$

(2.2)

Equation 2.2 indicates that the gain can be changed by using different bias currents  $I_{D1}$  and  $I_{D2}$  for  $M_1$  and  $M_2$ . If  $I_{D1}$  exactly matches  $I_{D2}$ , equation 2.2 is reduced to

$$A_{V}(0) = -\frac{\sqrt{W_{1}/L_{1}}}{\sqrt{W_{2}/L_{2}}}$$

(2.3)

Equation 2.3 shows that the voltage gain is linear and independent of the bias currents of the transistors, which also makes it insensitive to the process and the temperature variations. When  $M_1$  and  $M_2$  operate in the saturation region, their drain-source currents are given by

$$I_{D1} = I_{D2} = \frac{1}{2} \mu_n C_{OX} \left(\frac{W}{L}\right)_1 V_{DSAT 1}^2 = \frac{1}{2} \mu_n C_{OX} \left(\frac{W}{L}\right)_2 V_{DSAT 2}^2$$

(2.4)

Combining equation 2.2 with 2.4 yields

$$A_V(0) = -\frac{V_{DSAT2}}{V_{DSAT1}}$$

(2.5)

Equation 2.5 indicates that large gain factors require large  $V_{DSAT2}$ , but the gain is limited by the supply voltage. Next, through the analysis on frequency response and linear range of this structure, its limitations are shown.

#### (1) Frequency response

The parasitic capacitance and the resistance at the output node generate the dominant pole in this structure, which determines its -3dB bandwidth (Fig 2.2).

Fig 2.2 Pole location of the differential pair with diode-connected loads

For a DC voltage gain of N, the small signal gain of this structure is given by

$$A_{V}(s) = \frac{A_{V}(0)}{1 + \frac{s}{\omega_{P}}} = -\frac{N}{1 + \frac{s}{\omega_{P}}}$$

(2.6)

where

$$\omega_P = \frac{\frac{g_{m1}}{N}}{C_{gs1}(1 + \frac{1}{N^2}) + C_{load}} = \frac{g_{m1}}{C_{gs1}(N + \frac{1}{N}) + C_{load}}$$

Assume  $C_{gs1}(N + \frac{1}{N}) >> C_{load}$ , then

$$\omega_{p} \approx \frac{\frac{g_{m1}}{N}}{C_{gs1}(1 + \frac{1}{N^{2}})}$$

$$(2.7)$$

Define "unity gain frequency" as  $\omega = g_{ml}/C_{gsl}$  , then

$$\omega_p = \frac{\omega_t}{N + \frac{1}{N}} \tag{2.8}$$

This structure is a one-pole system, so its -3dB bandwidth (f  $_{-3dB}$ ) is determined by

$$f_{-3dB} = \frac{\omega_P}{2\pi} \approx \frac{\frac{g_{m1}}{N}}{2\pi C_{gs1}(1 + \frac{1}{N^2})}$$

(2.9)

Define the gain-bandwidth-product (GBW) as the product of its DC voltage gain and -3dB frequency:

$$GBW = A_V(0) \times f_{-3dB} \approx N \times \frac{\frac{g_{m1}}{N}}{2\pi C_{gs1}(1 + \frac{1}{N^2})} \approx \frac{g_{m1}}{2\pi C_{gs1}} (\text{If N} >>1)$$

(2.10)

Therefore, we observe that the VGA based on the differential pair with diode-connected loads has a constant gain-bandwidth-product. In other words, there is a trade-off associated with the gain and bandwidth. When gain increases, its bandwidth drops to lower frequency. For example, suppose  $f_t = \frac{\omega_t}{2\pi} = 10 \text{GHz}$  for the above circuit. Then a plot of pole location vs. different voltage gains can be generated as in Fig 2.3, which shows the reduction of the pole frequency with the increasing gain. Compared to bandwidth requirement of this design, an almost constant bandwidth regardless of gain changing is desired. Thus, this structure is not suitable for this design.

Fig 2.3 Differential pair with diode-connected loads pole location vs. voltage gain

#### (2) Linear range limitation

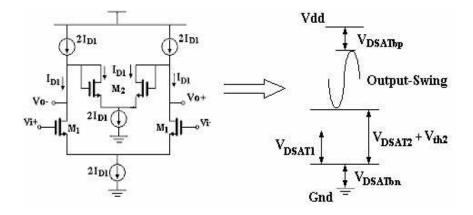

In this VGA design, the output signal is fixed to be  $1V_{pp}$  with 2.5V power supply, to meet the full scale of the ADC. Thus, the suitable VGA topology for this design has to provide at least  $1V_{pp}$  linear range with large variable gain range (42dB). The linear range of the differential pair with diode-connected loads is limited by the voltage headroom occupied by the gate source voltage of  $M_2$ , the saturation voltage of the NMOS transistor to generate the tail current for the differential pair, and the saturation voltage of the PMOS bias transistor to generate  $2I_{D1}$ . (See Fig 2.4)

Fig 2.4 Linear range of differential pair with diode-connected loads

As shown in Fig 2.4, the linear range of differential pair with diode-connected loads is given by

$$V_{linear-range} = \frac{1}{2} \left[ V_{dd} - V_{DSATbp} - (V_{DSAT2} + V_{thn}) - V_{DSATbn} \right]$$

(2.11)

where  $V_{DSATbp}$  is the saturation voltage of the PMOS bias transistor to generate  $2I_{D1}$  current;  $V_{DSAT2}$  is the saturation voltage of  $M_2$ ;  $V_{thn}$  is the threshold voltage of  $M_2$ ;  $V_{DSATbn}$  is the saturation voltage of the NMOS transistor generating the tail current for  $M_2$ . If the DC voltage gain = N, with equation 2.4, we have

$$V_{DSAT2} = N \times V_{DSAT1}$$

Also if  $V_{DSATbp} \sim V_{DSATbn} \sim V_{DSAT1}$ , from equation 2.11, we have

$$V_{linear-range} \approx 0.5 \left( V_{dd} - V_{DSAT1} - N V_{DSAT1} - V_{thn} - V_{DSAT1} \right) = 0.5 \left[ V_{dd} - V_{thn} - (N+2) V_{DSAT1} \right] (2.12)$$

From equation 2.12, it is observed that as the DC gain increases, the linear range drops proportionally.

In this design,  $V_{dd} = 2.5V$ ,  $V_{thn} \sim 0.6V$ . Substitute them into equation 2.12 yields

$$V_{linear-range} \approx 0.95V - 0.5(N+2)V_{DSATn} \tag{2.13}$$

Suppose  $V_{DSATn} = 0.1V$ , to achieve 0.5V amplitude of the linear range required in this design, the gain is limited to be less than 7. Thus, in low voltage applications, the linear range of differential pair with diode-connected loads limits its maximum achievable gain range.

(3) Summary of the VGA based on differential pair with diode-connected loads

The VGA based-on differential pair with diode-connected loads has the following characteristics:

- a) For small signal, its voltage gain is linear and independent of the bias currents of the transistors, which makes it insensitive to the process variations.

- b) The gain-bandwidth-product of this structure is a constant, so the bandwidth trades off with the gain, which is not desired in this design.

- c) Its linear range linearly decreases as gain increases, which prevents it from being used in the low voltage applications

In summary, differential pair with diode-connected loads-based VGA is not suitable for this design, because it cannot simultaneously satisfy the required specifications of large bandwidth, large variable gain range, and large linear range  $(1V_{pp})$ .

#### II.1.2 Analog multiplier

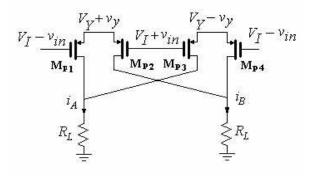

Another commonly used approach to implement a VGA is based on the analog multiplier [3]- [4]. The multiplier can be used as a linearized transconductor if one of the inputs is a DC signal as shown in Fig 2.5.

Fig 2.5 Analog multiplier used as VGA

In Fig 2.5,  $V_I$  and  $V_Y$  are the common-mode levels for the input signal  $v_{in}$  and the DC voltage  $v_y$ , respectively. Assuming that all transistors operate in saturation region, the multiplier transconductance becomes,

$$G_m = 2\mu_p C_{OX} \left(\frac{W}{L}\right) v_y \tag{2.14}$$

Neglecting the second order effects and the transistors mismatches, the transconductance of the multiplier is linear. The DC voltage gain of a multiplier and load resistor is given by

$$A_V(0) = \left(2\mu_n C_{OX}(\frac{W}{L})v_y\right) R_L \tag{2.15}$$

Thus the voltage gain can be varied by changing the control voltage level  $v_y$ . There is flexibility in controlling the gain because the control voltage is an analog signal.

Next the analysis on the linear range and the power consumption of multiplier will be given to show its advantages and drawbacks.

#### (1) Linear range

The linear range of the multiplier-based VGA depends on the control voltage level  $v_y$ . Hence, when the DC voltage gain increases, the linear range of this structure is reduced linearly. It can be justified as follows. The load for the multiplier can be a current mirror (Fig 2.6) [3].

Fig 2.6 Multiplier with current mirror load [3]

The linear range of this multiplier is given by

$$V_{linear-range} = \frac{1}{2} \left( V_{dd} - V_{DSATbp} - V_{DSATp} - V_{DSATn} - V_{thn} \right)$$

(2.16)

where  $V_{DSATbp}$  is the saturation voltage of the PMOS bias transistor;  $V_{DSATp}$  is the saturation voltage of the PMOS drivers  $M_{pi}$ , and  $V_{DSATn}$  is the overdrive voltage of the NMOS transistor  $M_n$ .

Because  $V_{DSATp} = V_Y + v_y - V_I$ , so the output voltage swing is given by

$$V_{linear-range} = \frac{1}{2} \left( V_{dd} - V_{DSATbp} - \left( V_Y + V_y - V_I \right) - V_{DSATn} - V_{thn} \right)$$

$$(2.17)$$

Also, from equation 2.16

$$\Rightarrow v_y = \frac{A_V(0)}{2\mu_n C_{OX} \frac{W}{L} R_L}$$

Substitute the above result into equation 2.16, we have

$$V_{linear-range} = \frac{1}{2} \left( V_{dd} - V_{DSATbp} - V_Y + V_I - V_{DSATn} - V_{thn} - \frac{A_V(0)}{2\mu_n C_{OX} \frac{W}{L} R_L} \right)$$

(2.18)

Equation 2.18 indicates that, as  $A_V(0)$  increases, the linear range drops proportionally. In other words, for large variable gain range, the linear range of the multiplier-based VGA is limited.

#### (2) Power consumption

In this design, low power consumption is a must. However, it will be shown that the multiplier-based VGA is not power efficient. Referring to Fig 2.5, the multiplier is equivalent to the cross-coupled outputs of two differential pairs  $M_{P1}$  and  $M_{P2}$ ,  $M_{P3}$  and  $M_{P4}$  as shown in Fig 2.7.

Fig 2.7 Block diagram of cross-coupled transconductors multiplier

The overall transconductance is given by

$$G_{m,eff} = g_{mp1} - g_{mp2} = 2\mu_p C_{OX} \frac{W}{L} v_y$$

(2.19)

$$g_{mp1} = \mu_p C_{OX}(\frac{W}{L}) (V_Y + V_y - V_I); \quad g_{mp2} = \mu_p C_{OX}(\frac{W}{L}) (V_Y - V_y - V_I)$$

(2.20)

where  $g_{mp1}$  and  $g_{mp2}$  are the transconductance of the differential pair consisting  $M_{P1}$  and  $M_{P2}$ , and the one consisting of  $M_{P3}$  and  $M_{P4}$  respectively.

By varying  $v_y$ ,  $g_{mp1}$  and  $g_{mp2}$  are changed in the opposite directions by the same amount, and the effective transconductance  $G_{m,eff}$  will be doubled by that amount. So, the tuning range of the transconductance is large. However, this scheme is not power-efficient. This is because, in low gain cases,  $v_y$  is small,  $g_{mp1}$  and  $g_{mp2}$  are quite close, and only a small portion of  $g_{mp1}$  is delivered to the output while most of it is cancelled out by  $g_{mp2}$ . Thus a lot of power is wasted in this case. For the high gain cases,  $v_y$  is

large,  $g_{mp1}$  is much larger than  $g_{mp2}$ , but still only part of  $g_{mp1}$  is delivered to the output. As a result, the multiplier-based VGA is not suitable for low power applications.

#### (3) Summary of analog-multiplier-based VGA

In summary, the multiplier-based VGA has good linearity and large gain tuning range, but it is not power efficient because the effective transconductance  $G_{m,eff}$  is generated by the subtraction between  $g_{mp1}$  and  $g_{mp2}$ . And hence, it is not suitable for low-power VGA design.

#### II.1.3 Differential pair with source degeneration

Another commonly used VGA topology is the differential pair with source degeneration [5]- [6], as shown in Fig 2.8. It will be shown that good linearity can be achieved in this structure with large source degeneration factors; but the transconductance is attenuated a lot at the same time.

Fig 2.8 Differential pair with source degeneration

The transconductance of the differential pair with source degeneration is determined by

$$Gm = \frac{g_m}{1 + \frac{g_m R_s}{2}} \tag{2.21}$$

where  $R_s$  is the source degeneration resistor, and  $\frac{g_m R_s}{2}$  is the source degeneration factor.

If the source degeneration factor

$$(\frac{g_m R_s}{2}) >> 1$$

, equation 2.21 yields  $G_m \approx \frac{2}{R_s}$ .

Under this condition, the transconductance of this configuration is simply determined by the source degeneration resistor. By changing the value of  $R_s$ , the amplifier gain can be tuned. Compared to the transconductance of simple differential pair, effective  $G_m$  of differential pairs with source degeneration is only 1/(N+1) times that of the simple differential pair. This motivates us to find an approach to boost effective transconductance of differential pairs with source degeneration.

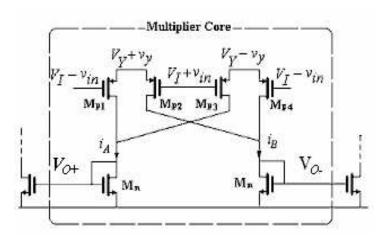

#### II.1.4 Complementary differential pairs with source degeneration

To boost the effective transconductance of differential pairs with source degeneration while still achieving the similar linearity level, the complementary differential pair with source degeneration scheme can be used [7] (see Fig 2.9). In this structure, the drain of a PMOS differential pair and a NMOS differential pair are connected together such that the current converted by each differential pair are delivered

together to the next stage. In each differential pair, source degeneration resistors are used to improve their linearity.

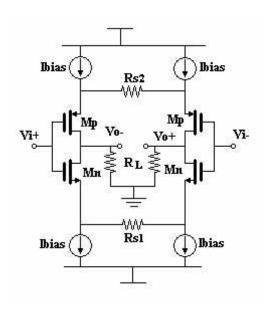

Fig 2.9 Complementary differential pairs with source degeneration

The effective transconductance of this structure is given by

$$G_{m} = \frac{g_{mn}}{1 + \frac{g_{mn}R_{s1}}{2}} + \frac{g_{mp}}{1 + \frac{g_{mp}R_{s2}}{2}}$$

(2.22)

A special case of it is to set  $g_{mn}R_{S1} = g_{mp}R_{S2}$ , then equation 2.21 becomes

$$G_{m} = \frac{g_{mn} + g_{mp}}{1 + \frac{g_{mn}R_{s1}}{2}}$$

(2.23)

Both differential pairs are biased with the same DC current. Compared with the single differential pair case, the power consumption is the same for both topologies. But the complementary configuration has a larger effective transconductance, because the

effective transconductance is the summation of the transconductances of NMOS and PMOS transconductors. It can be shown that with the complementary differential pairs, the effective transconductance can be boosted by 60% compared to that of the single differential pair [7].

#### (1) Linear range

The linear range of complementary differential pairs with source degeneration is limited by the  $V_{dsat}$  of  $M_p$  and  $M_n$ , and those of their bias transistors  $M_{bp}$  and  $M_{bn}$  altogether. So the linear range for it is given by

$$V_{OUTPUT-SWING} = \frac{1}{2} \left( V_{dd} - V_{DSATbp} - V_{DSATp} - V_{DSATn} - V_{DSATbn} \right)$$

$$(2.24)$$

Notice that the DC voltage gain variation is achieved by changing the source degeneration resistor, which will not affect the terms in equation 2.24. Therefore, regardless of the change in the voltage gain, the linear range of complementary differential pairs with source degeneration is fixed. On comparison with the differential pair with diode-connected loads, where the linear range is reduced linearly if gain is increasing, it can be justified that, in low voltage applications, the complementary differential pairs with source degeneration structure can achieve larger variable gain range than that of the differential pair with diode-connected loads structure.

(2) Summary of VGA based on complementary differential pairs with source degeneration

Complementary differential pairs with source degeneration have better power efficiency than that of differential pair with source degeneration. The former boosts the transconductance while consuming the same power and has similar linearity performance as that of the latter. The linear range of the complementary differential pairs with source degeneration is independent of gain variations, which enables it to obtain large variable gain ranges under low supply voltage.

#### II.2 Comparison of the commonly used VGA structures

The design requirements impose challenges on low power consumption, very large bandwidth, large variable gain range, and very small group delay variation.

A differential pair can be linearized with diode-connected loads. But in large gain cases, the linear range and bandwidth are limited.

A multiplier has good linearity and flexible tunablity. However, due to the subtraction of two transconductances in this type of multiplier, the power is wasted when generating total transconductance. So for low power applications, a multiplier may not be a suitable candidate.

The linearity of the differential pair with source degeneration is dependent on the  $g_m R_S$  and  $V_{DSAT}$ . By increasing these values, its linear range becomes comparable with the multiplier's linearity. But at the same time, the effective transconductance is attenuated dramatically.

Currently available VGA structures cannot meet all these requirements. A new approach has to be proposed, in which, the following aspects should be emphasized:

- (1) An approach with better power efficiency while maintaining enough linearity is needed.

- (2) To obtain large bandwidth, current amplification is preferred to voltage amplification due to its low impedance internal nodes.

Starting with differential pairs with source degeneration, a complementary differential pairs with source degeneration configuration is proposed. Its effective transconductance can be boosted up by 60% as compared to a single NMOS differential pairs with source degeneration while maintaining the same power consumption. It also has large variable gain range and large linear range. Therefore it will be a suitable choice for this design.

#### **CHAPTER III**

#### PROGRAMMABLE CURRENT MIRROR

In this chapter, the simple current mirror is briefly reviewed. Its AC response and non-idealities are studied. Based on the design requirements, a programmable current mirror is proposed to improve frequency response and programmability. A performance comparison between the simple current mirror and the proposed programmable current mirror is given.

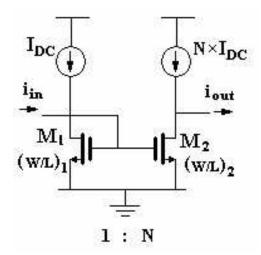

### III.1 Review of simple current mirror

Because of its low-impedance internal node, the current mirror is used in many high-frequency VGA designs [1].

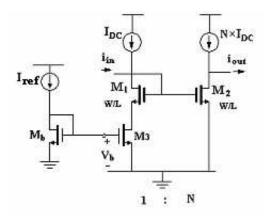

Fig 3.1 Simple current mirror

Neglecting the mismatch and the channel-length modulation effects, the DC current gain for the simple current mirror shown in Fig 3.1 is given by:

$$\frac{i_{out}}{i_{in}} = \frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1} \tag{3.1}$$

In the simple current mirror, the parasitic capacitance and the resistance at the diode-connected node generate an internal pole. It has been shown in [3] that the short circuit transfer function of the simple current mirror in Fig 3.1(a) is given by:

$$\frac{i_{out}}{i_{in}} = -\frac{\frac{g_{m2}}{(N+1)C_{gs}}}{s + \frac{g_{m2}}{(N+1)C_{gs}}} \times N$$

(3.2)

where N is the DC current gain, and  $C_{gs}$  is the gate-source capacitance of the input transistor.

The pole at the diode-connected node is given by

$$\omega_P = \frac{g_{m2}}{(N+1)C_{gs}} \tag{3.3}$$

From equation 3.3, with a DC current gain of N, the gate dimension of the output transistor in simple current mirror is N times larger than its input transistor, so is its parasitic capacitance. This implies that the pole location will drop to a lower frequency. While the current gain still can be changed with an alternate method, if we can find a way with fixed input/output transistor dimensions, the frequency response of the current mirror can be improved.

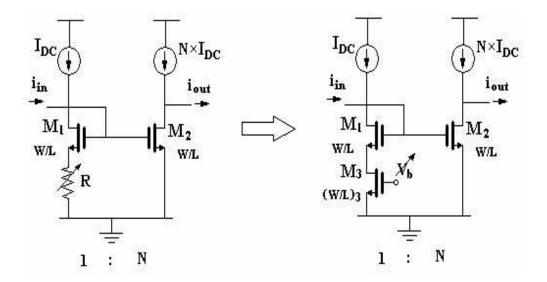

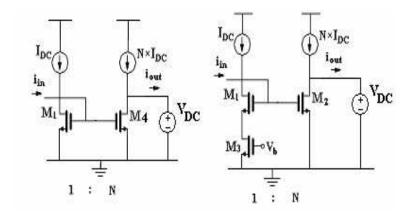

# III.2 Proposed programmable current mirror

As just mentioned, we can try to fix the dimensions of the input/output transistor in the current mirror but change the current gain through alternate means. In the simple current mirror, the DC current gain is given by

$$\frac{i_{out}}{i_{in}} = \frac{\left(\frac{W}{L}\right)_2 (V_{GS2} - V_{th})^2}{\left(\frac{W}{L}\right)_1 (V_{GS1} - V_{th})^2}$$

(3.4)

From equation 3.4, if  $\left(\frac{W}{L}\right)_2$  and  $\left(\frac{W}{L}\right)_1$  are fixed, changing  $V_{GS2}$  or  $V_{GS1}$  can vary

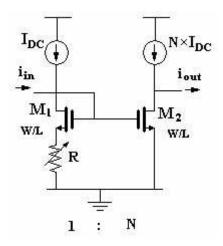

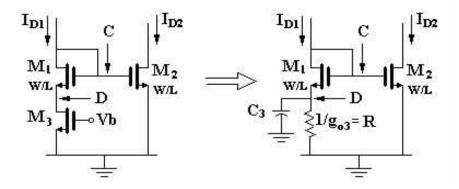

the current gain too. One solution to vary  $V_{GS}$  is to insert a variable resistor between the source and the ground of the input transistor;  $V_{GS1}$  is adjusted by varying the resistor. Fig 3.2 shows the proposed programmable current mirror.

- (a) Simple resistor model

- (b) Linear region transistor replaces resistor

Fig 3.2 Programmable current mirror

As illustrated in Fig 3.2 (a),  $M_1$  and  $M_2$  are identical, and the DC current gain of the programmable current mirror is given by

$$\frac{i_{out}}{i_{in}} = \frac{\left(V_{GS2} - V_{th}\right)^2}{\left(V_{GS2} - R \times I_{DC} - V_{th}\right)^2}$$

(3.5)

For the implementation of a variable resistor, a MOS transistor operating in triode region can be used. Its resistance is then linearly controlled by its gate-source bias voltage. How to generate  $V_b$  to control the current gain of the programmable current mirror accurately will be discussed next.

The proposed bias circuit is shown in Fig 3.3. By rearranging equation 3.5, we obtain

$$\frac{i_{out}}{i_{in}} = \frac{1}{\left(1 - \frac{R \times I_{DC}}{V_{GS2} - V_{th}}\right)^2}$$

(3.6)

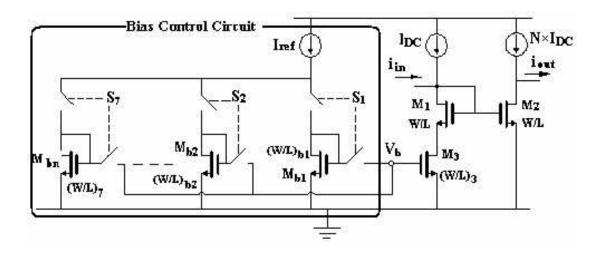

If  $R \times I_{DC} \propto (V_{GS2} - V_{th})$ , then equation 3.6 indicates that the current gain can be accurately controlled. This inspires the circuit shown in Fig 3.3. The diode-connected transistor  $M_b$  is used to convert the DC reference current,  $I_{DC}$ , into a bias voltage,  $V_b$ , to bias  $M_3$ . It will be shown that the current gain is determined by the aspect ratios of  $M_1$  ( $M_2$ ),  $M_3$ ,  $M_b$ , and the ratio between the  $I_{ref}$  and  $I_{DC}$ .

From equation 3.6, we have

$$\Rightarrow \frac{i_{out}}{i_{in}} = \frac{1}{\left(1 - \frac{V_{DS3}}{V_{GS2} - V_{th}}\right)^2}$$

(3.7)

Fig 3.3 V<sub>b</sub> generation for programmable current mirror

If M<sub>3</sub> operates in the linear region, then  $I_{D3} \approx \beta_3 (V_{GS3} - V_{th}) V_{DS3}$ . By rearranging this, we obtain,

$$V_{DS3} \approx \frac{I_{D3}}{\beta_3 (V_{GS3} - V_{th})} \tag{3.8}$$

M<sub>b</sub> operates in the saturation region yields

$$I_{ref} = I_{D3} \approx \frac{1}{2} \beta_b (V_{GS3} - V_{th})^2$$

(3.9)

where

$$\beta_i = \mu_n C_{OX} \left( \frac{W}{L} \right)_i$$

.

If we substitute equations 3.8 and 3.9 into equation 3.7, we have

$$\frac{i_{out}}{i_{in}} = \frac{1}{\left(1 - \frac{\beta_b (V_{GS3} - V_{th})^2}{2\beta_3 (V_{GS3} - V_{th})(V_{GS2} - V_{th})}\right)^2} = \frac{1}{\left(1 - \frac{\beta_b V_{DSAT3}}{2\beta_3 V_{DSAT2}}\right)^2}$$

(3.10)

So, if

$$\beta_b = 2\beta_3$$

, then

$$\frac{i_{Out}}{i_{In}} = \frac{1}{\left(1 - V_{DSAT3} / V_{DSAT2}\right)^2} \tag{3.11}$$

Equation 3.11, based on the special case of  $I_{ref} = I_{D3}$ , indicates that  $V_{DSAT3}$  and  $V_{DSAT2}$  can be related by the dimensions and bias currents of the transistors in the current mirror, and therefore the current gain can be related to them as well. In general cases, we have  $I_{ref} = K \times I_{D3}$  (where K is a constant). The expression of current gain as a function of the aspect ratios of  $M_1$  ( $M_2$ ),  $M_3$ ,  $M_b$ , and the ratio between the  $I_{ref}$  and  $I_{DC}$  is obtained in Appendix A; the result is as follows:

$$\frac{i_{out}}{i_{in}} = \left(\sqrt{NK} + 1 - \sqrt{NK - M}\right)^2 \tag{3.12}$$

where

$$M = \frac{(W/L)_1}{(W/L)_3}$$

$N = \frac{(W/L)_1}{(W/L)_b}$   $K = \frac{I_{ref}}{I_{DC}}$

First, notice that in equation 3.12, the product of NK has to be larger than M. If NK = M, then,  $M_3$  will operate in the saturation region. Even though the drain current equation for  $M_3$  is not valid any more, equation 3.12 is still valid and reduces into equation 3.13,

$$\frac{i_{out}}{i_{in}} = \left(\sqrt{M} + 1\right)^2 = \left(\sqrt{NK} + 1\right)^2 \tag{3.13}$$

However, if  $M_3$  operates in the saturation region, its output resistance is almost constant and only varies subtly due to the channel length modulation effects. Therefore, it is not suitable as a variable resistor.

Equation 3.12 also shows that by increasing M, or decreasing K or N, the current gain can be increased. To minimize the power consumption for the bias control voltage,

we should avoid using large K to keep  $I_{ref}$  at a minimum. Also, according to the real implementation of the programmable current mirror, M cannot be varied, which leaves K and N to be varied. Changing K to obtain different current gain ratios unavoidably requires a large range of K variation, as it is square-root proportional to the current gain, which results in wasting power at large K cases. However, if variable current gain is obtained by varying N, it is only needed to implement a bank of diode-connected transistors with different dimensions and bias with an optimal current ( $I_{ref} = K_{optimal} \times I_{D3}$ ). By connecting or disconnecting them to the gate of  $M_3$ , different gain can be obtained. Thus, restricted by the low power requirement, this approach is adapted to implement the programmable current mirror. Furthermore, as K is fixed, the variables left in equation 3.12 are M and N. As they are both related to the dimensions of  $M_1$ , their ratio, which is the aspect ratio between  $M_b$  and  $M_3$ , can be a variable to determine the current gain.

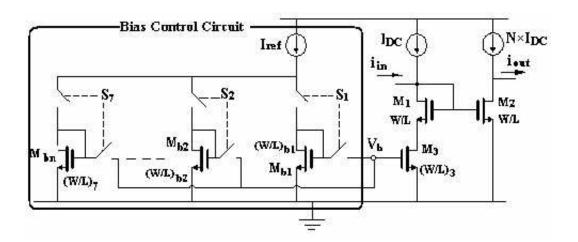

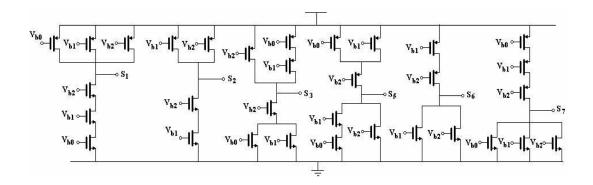

To obtain 14dB of variable gain range, and include the consideration of the trade-off mentioned previously, K = 2 and M = 2 are selected. With this combination, the maximum gain is approximately 14 dB for N = 1. The simulated dimensions of the transistors are listed in Table 3.1.  $W_b$  is the total equivalent transistor width of the bias control circuit,  $W_b = \sum_{i=1}^{N} W_{bi}$ . Therefore, the individual transistor width can be calculated as shown in Table 3.1. The corresponding bias control circuit with programmable current mirror is shown in Fig 3.4.

N 1.01 1.05 1.2 1.4 1.8 3 5.6 Current 14dB 12dB 10dB 8dB 6dB 4dB 2dB Gain 23.6 12 7.2 2.4 0.72  $W_b$ 21.6 16.8  $M_{b1}$  $M_{b2}$  $M_{b3}$  $M_{b4}$  $M_{b5}$  $M_{b6}$  $M_{b7}$ W  $1.68\,\mu m$  $0.72\ \mu m$  $2\mu m$  $4.8 \mu m$ 4.8 µm  $4.8 \mu m$  $4.8 \mu m$

Table 3.1 Dimensions of the bias circuits  $(L=0.24\mu m) \label{eq:L}$

Fig 3.4 Dimensions of the bias circuits bias transistors to generate seven gain steps for programmable current mirror

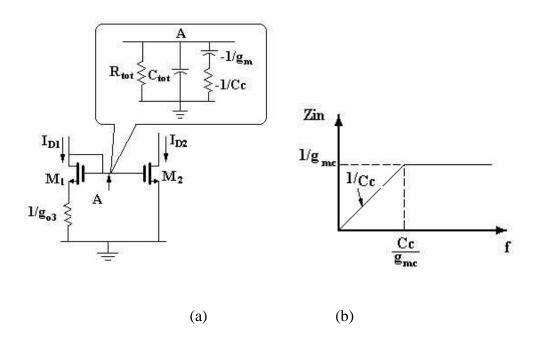

# III.2.1 AC response of programmable current mirror

When the programmable current mirror operates at a low frequency,  $M_3$  is equivalent to a variable resistor R and its parasitic capacitance can be ignored.  $M_1$ , connected to the variable resistor R, converts the input current,  $i_{in}$ , into voltage. This

voltage at node C is then converted back to current ( $i_{out}$ ) through  $M_2$ . As shown in Fig 3.5, the DC current gain is given by

$$\frac{i_{out}}{i_{in}} = g_{m2} \left( R + \frac{1}{g_{m1}} \right) \tag{3.14}$$

Fig 3.5 Programmable current mirror low frequency model

At high frequencies, the parasitic capacitance at node C and D must be taken into account (Fig 3.6). Assuming that the gate-source capacitance of  $M_1$  and  $M_2$  are equal, the current gain computation yields

$$\frac{i_{out}}{i_{in}} \cong \frac{g_{m1} \left(R + \frac{1}{g_{m1}}\right) (C_1 + C_3)}{C_1 (2C_1 + C_3)} \frac{s + \frac{g_{m1} + \frac{1}{R}}{C_1 + C_3}}{\left(s + \frac{g_{m1}}{2C_1}\right) \left(s + \frac{1}{R(C_1 + 0.5C_3)}\right)}$$

When DC current gain = N

$$\Rightarrow$$

R =  $\frac{N-1}{g_{m1}}$

$$\Rightarrow \frac{i_{out}}{i_{in}} \cong \frac{N(C_1 + C_3)}{C_1(2C_1 + C_3)} \frac{s + \frac{\left(1 + \frac{1}{N-1}\right)g_{m1}}{C_1 + C_3}}{\left(s + \frac{g_{m1}}{2C_1}\right)\left(s + \frac{g_{m1}}{(N-1)(C_1 + 0.5C_3)}\right)}$$

$$\Rightarrow \frac{i_{out}}{i_{in}} \approx \frac{N(C_1 + C_3)}{C_1(2C_1 + C_3)} \frac{s + \frac{\left(1 + \frac{1}{N-1}\right)g_{m1}}{C_1 + C_3}}{\left(s + \frac{g_{m1}}{2C_1}\right)\left(s + \frac{g_{m1}}{(N-1)(C_1 + 0.5C_3)}\right)}$$

(3.15)

(a) Nodes C and D

(b) Small signal model

Fig 3.6 Programmable current mirror high frequency operation model

Equation 3.15 indicates that there are two poles and one zero in the programmable current mirror, which are:

$$\omega_{P1} = \frac{g_{m1}}{2C_1}, \quad \omega_{P2} = \frac{g_{m1}}{(N-1)(C_1 + 0.5C_3)}, \quad \omega_Z = \frac{g_{m1}\left(1 + \frac{1}{N-1}\right)}{C_1 + C_3}$$

(3.16)

The dominant pole in the programmable current mirror is

Dominant Pole:

$$\omega_{P2} = \frac{g_{m1}}{(N-1)(C_1 + 0.5C_3)}$$

(3.17)

The dominant pole frequency of the programmable current mirror with that of the simple current mirror is compared as shown in Table 3.3.

Table 3.2 Dominant poles comparison between programmable and simple current mirror

|               | Simple Current Mirror     | Programmable Current Mirror                    |

|---------------|---------------------------|------------------------------------------------|

| Dominant pole | $\frac{g_{m1}}{(N+1)C_1}$ | $\frac{g_{m1}}{(N+1)C_1 + 0.5C_3(N-1) - 2C_1}$ |

From Table 3.3, if  $0.5C_3(N-1)-2C_1 < 0$ , then the dominant pole of the programmable current mirror is at higher frequency than that of the simple current mirror. Further,  $C_1$  (the gate-source parasitic capacitance of  $M_1$ ) and  $C_3$  (the drain-bulk capacitance combined with the drain source parasitic capacitance of  $M_3$ ) are also comparable. Thus, from the expression of the non-dominant pole and zero of the programmable current mirror, when N>>1,

$$\omega_{\rm Z} \approx \frac{g_{m1}}{C_1 + C_3} \approx \frac{g_{m1}}{2C_1} = \omega_{P1}(N >> 1)$$

(3.18)

Therefore, at large gain cases in which N>>1, the zero of the programmable current mirror will cancel out its non-dominant pole and hence its -3dB frequency will be only determined by its dominant pole frequency.

Overall, to achieve an improved frequency response from the programmable current mirror when compared to the simple current mirror, we have to guarantee that at DC current gain of N,

$$0.5C_3(N-1) - 2C_1 < 0 (3.19)$$

The result from equation 3.19 is very critical, since at high gain cases, it can be used to determine whether the programmable current mirror has improved the frequency response when compared to the simple current mirror and determine how much improvement we can get.

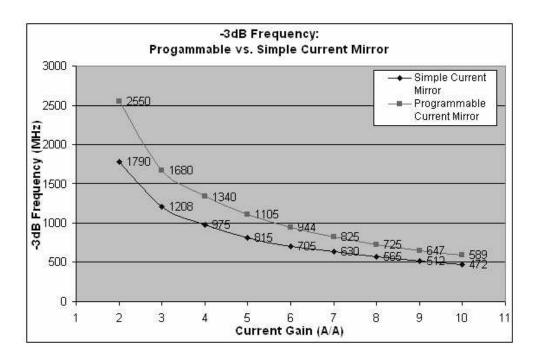

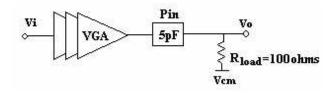

Using the Cadence simulator, a comparison of f<sub>-3dB</sub> of the programmable current mirror vs. that of the simple current mirror under different current gain levels can be obtained. The simulation setup is shown in Fig. 3.7; transistors dimensions are given in Table 3.3.

(a) Simple current mirror (b) programmable current mirror Fig 3.7 Setup for testing  $f_{-3dB}$  of the current mirror

In Fig 3.7, the same DC bias current  $I_{DC}$  is provided for both current mirrors. In the simple current mirror, for different current gain N,  $M_4$  is split into N fingers each with the same dimension as  $M_1$ . Further, a DC voltage is provided at the output to fix the drain-source voltage of  $M_4$  to be the same as that of  $M_1$ . This will avoid the current mismatch caused by the channel-length modulation effects. For the case of the programmable current mirror, the bias voltage  $(V_b)$  is changed to obtain different current gains.

Table 3.3 Current mirror's f.3dB testing setup

|                      | $\mathbf{M}_1$       | $M_2$     | M <sub>3</sub> | $M_4$     |

|----------------------|----------------------|-----------|----------------|-----------|

| W/L (µm)             | 24/0.24              | 24/0.24   | 24/0.24        | 24×N/0.24 |

| I <sub>DC</sub> (µA) | i <sub>in</sub> (μA) | N         |                |           |

| 100                  | 25                   | 2, 3,, 10 |                |           |

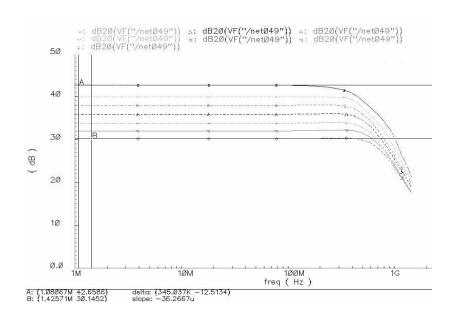

Fig 3.8 f<sub>-3dB</sub> of the simple current mirror vs. that of the programmable current mirror

According to Fig 3.8, with the programmable current mirror, we can improve the  $f_{-3dB}$  in a certain current gain range, but this improvement is reduced as the gain increases, and eventually at very high current gain cases, in which equation 3.19 is not satisfied any more, or say,  $0.5C_3(N-1)-2C_1$  is larger than zero, the programmable current mirror will have even smaller  $f_{-3dB}$  and worse frequency response than those of the simple current mirror.

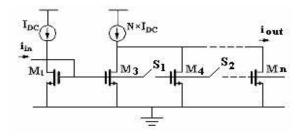

## III.2.2 Programmability of the programmable current mirror

Another advantage of using the programmable current mirror is its good programmability. To change current gain in the simple current mirror, we need several transistors with different dimensions connected to the input transistor with switches.

This circuit is shown in Fig 3.9. There are some effects on the circuit's performance caused by these connections. The on-resistance of the switches combined with the parasitic capacitance at the current mirror internal node (dominated by the gate-source parasitic capacitance of the transistors) generates a RC network. This network is along the signal path of the current mirror, and thus the high-frequency signal will be attenuated and delayed by the RC time constant from this RC network.

Fig 3.9 Simple current mirror to implement different current gain

For the case of the programmable current mirror, the gain control is achieved by the bias control circuit. Even though there are switches in this bias circuit, none of them are in the signal path, implying that there will be no additional time constants, as in the simple current mirror. So, more gain steps with larger overall variable gain ranges can be implemented in the programmable current mirror than that of the simple current mirror.

### III.3 Conclusions

A comparison between the simple current mirror and the proposed programmable current mirror is listed in Table 3.4.

Table 3.4 Current mirror comparison

|                       | simple current                          | programmable current mirror                                                                                                                                                                                                                                                      |

|-----------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | mirror                                  |                                                                                                                                                                                                                                                                                  |

| R <sub>out</sub>      | $r_{ds2}$                               | $r_{ds2}$                                                                                                                                                                                                                                                                        |

| Frequency<br>response | $\omega_p = \frac{g_{m2}}{(N+1)C_{gs}}$ | $\omega_{P1} = \frac{g_{m1}}{2C_1}, \omega_{P2} = \frac{1}{R(C_1 + 0.5C_3)}, \omega_Z = \frac{g_{m_1} + \frac{1}{R}}{C_1 + C_3}$ It is justified in section III.2.1 that It has improved frequency response than simple current mirror if $0.5C_3(N-1) - 2C_1 < 0$ is satisfied. |

| Programmability       | Poor (as explained                      | Good (as explained in section 3.2(2))                                                                                                                                                                                                                                            |

|                       | in section 3.2(2))                      |                                                                                                                                                                                                                                                                                  |

The proposed programmable current mirror avoids changing the output transistor's dimension to change current gain, which improves frequency response and provides larger bandwidth than that of simple current mirror in a certain gain range as long as equation 3.19 is valid. Also, as explained in 3.2(2), it has better programmability than that of the simple current mirror. The current gain variation in the programmable current mirror is obtained by changing the bias voltage, V<sub>b</sub>, for M<sub>3</sub> in Fig 3.6. With the proposed bias control circuit, the current gain of the programmable current mirror becomes a function of the aspect ratios of M<sub>1</sub>, M<sub>3</sub>, M<sub>bi</sub>, and their bias current ratio. By properly selecting these parameters, a large current gain tuning range can be achieved.

#### CHAPTER IV

#### DESIGN CONSIDERATIONS OF THE PROPOSED VGA

In this chapter, VGA design challenges are summarized, and the motivations for the new approach are addressed. Following an overview of the system-level considerations, the individual building blocks of the proposed VGA are introduced. Each building block is explained and analyzed. Finally, detailed calculations for the proposed VGA are given in the Appendix B.

# IV.1 VGA design challenges and motivations

In this design, we want to achieve large bandwidth, large variable gain range with low power consumption and small group delay variation. Also, the VGA should maintain good linearity and low noise performance for all gain steps; its design specifications are given in Table 4.1.

Table 4.1 VGA specifications

| Technology | Gain   | Band              | dwidth     | Linearity  | Noise  | Group delay | Power |

|------------|--------|-------------------|------------|------------|--------|-------------|-------|

|            | range  | (N                | MHz)       | IIP3 (dBm) | figure | variation   | (mW)  |

|            | (dB)   | f <sub>-1dB</sub> | $f_{-3dB}$ |            | (dB)   | (pS)        |       |

| IBM 0.25um | 0 ~ 42 | >264              | >350       | -15        | <25    | <200        | <20   |

| CMOS       |        |                   |            |            |        |             |       |

## IV.2 System-level overview of the proposed VGA

## IV.2.1 System-level design of the proposed VGA

From the system-level point of view, this design can be divided into three categories:

- 1) Gain amplification schemes

- 2) Variable gain control schemes

- 3) Other auxiliary schemes

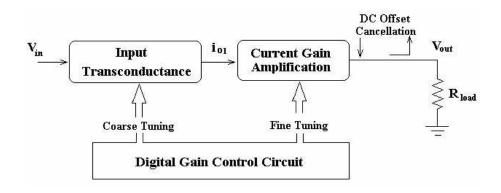

For the first category, the 42dB gain range is distributed into two amplification stages: first with a transconductance stage to convert the input voltage signal into current, and then use a current mirror to further amplify the current. With fixed resistors at the output, the current is converted back into voltage. With the combination of the two gain stages, a large variable gain range is obtained.

For the variable-gain-control scheme, coarse tuning at the transconductance stage and fine tuning at the current mirror stage are implemented respectively.

Besides the previously mentioned two categories in the VGA, frequency compensation and DC offset cancellation are implemented as well. These functions will be explained in the following sections.

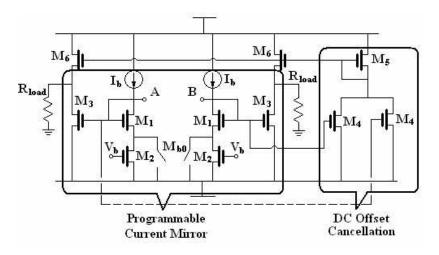

Overall, the system-level architecture of the proposed VGA is shown in Fig 4.1, and an explanation of each block follows.

Fig 4.1 System-level architecture of the proposed VGA

## IV.2.2 Introduction of the building blocks of the proposed VGA

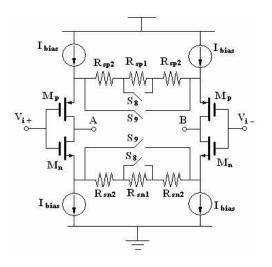

Fig 4.2 Complementary differential pairs with source degeneration

Based on the system-level VGA structure discussed previously, the building blocks can be constructed to meet the system needs. First, a power-efficient transconductor is required as the input stage. From the comparison conducted in Chapter II, the complementary differential pairs with source degeneration boosts

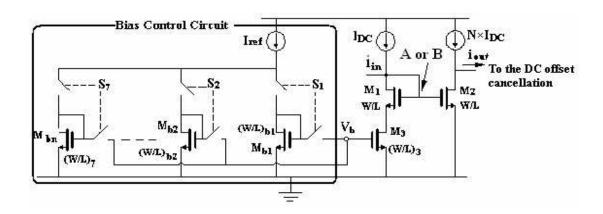

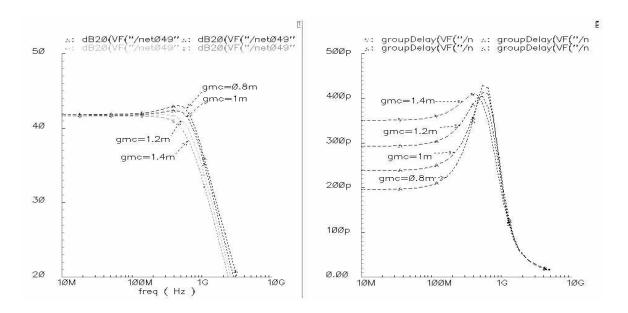

transconductance while consumes the same power as the simple differential pair with source degeneration. Thus, it is used as the input stage (Fig 4.2). As for the current amplification stage, according to the studies in Chapter III, the programmable current mirror shows the good frequency response and gain programmability. Thus, it is used as the current amplification stage (Fig 4.3).

(a) Programmable current mirror

(b) DC offset cancellation

Fig 4.3 Programmable current mirror and DC offset cancellation

Nodes A and B in Fig 4.2and in Fig 4.3 are the same nodes.

Secondly, for the gain-control scheme, the coarse tuning is implemented by changing the source degeneration resistor in the input stage (Fig 4.2). Fine tuning is obtained by changing the dimensions of the transistors in the bias control circuit of the programmable current mirror (Fig 4.3). Both gain varying schemes are then programmed with digital gain control.

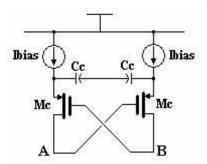

For the auxiliary circuits, a capacitive frequency-compensation scheme is used to further extend the bandwidth of the VGA (Fig 4.4), and a DC offset cancellation output stage is used to fix the DC voltage level, regardless of the offset introduced by mismatch or process variations (Fig 4.3).

Fig 4.4 Capacitive frequency compensation (A and B are the same in Fig 4.3)

Overall, the building blocks in the proposed VGA are shown in Fig 4.5.

Fig 4.5 Block diagram of the proposed VGA

# IV.3 Detailed discussion of the VGA building blocks

### IV.3.1 Gain-control scheme

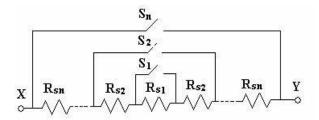

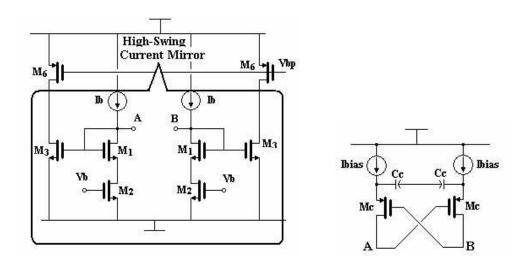

In this VGA, the gain range is from 0 dB to 42dB with 2dB/step and it is divided into coarse tuning (varying the source degeneration resistor) and fine tuning (the varying current gain of the current mirror). There are tradeoffs in allocating the tuning range for coarse and fine tuning. First, consider how many steps can be allocated in the coarse tuning without causing a severe mismatch between the source degeneration resistors. To maintain symmetry and achieve good matching, the resistors and switches should be connected as shown in Fig 4.6.

Fig 4.6 Source degeneration resistors and controlling switches configuration

X and Y are connected between the sources of the driver transistors in differential pairs in Fig 4.2. The relation between the number of coarse tuning steps and the corresponding number of resistors/switches required are demonstrated in Table 4.2.

Table 4.2 Coarse tuning steps vs. number of resistors/switches required

|                       | 2-step | 3-step | 4-step | 5-step | ••• | N-   |

|-----------------------|--------|--------|--------|--------|-----|------|

|                       |        |        |        |        |     | step |

| Number of controlling | 1      | 2      | 3      | 4      |     | N-1  |

| switches              |        |        |        |        |     |      |

| Number of Resistors   | 1      | 3      | 5      | 7      |     | 2N-3 |

|                       |        |        |        |        |     |      |

According to Table 4.2, to realize N steps of coarse tuning, (2N - 3) source degeneration resistors and (N - 1) switches are required. As the number of resistors increases, it is more difficult to match them because of process parameter variations. Also, MOS transistors operating in the linear region are used to implement the switch, which introduces some nonlinearity. The more switches in the circuit, the more nonlinearity. Thus, with the above concerns, 3-step coarse tuning to cover the entire

42dB gain range is more practical. This leads to each coarse tuning step having 14dB gain range.

On the other hand, the fine tuning is achieved by the programmable current mirror. As illustrated in Chapter III, Fig 3.6, the current gain is set to be less than 10 in this design to ensure enough bandwidth. With 3-step coarse tuning, the fine tuning range of the current mirror will be 14dB, which is within the current gain range to ensure enough bandwidth. Gain step size in fine tuning is determined by the UWB receiver system design, which requires 2dB/step. Therefore, 8 steps of fine tuning are needed to cover the 14dB gain range.

As a result, with the nonlinearity concerns of the MOS switches, the mismatch of resistors in the source degeneration, and the limitation of the maximum gain range of the current mirror, 3-step coarse tuning (14dB each) and 8-step fine tuning (2dB each) are chosen as shown in Table 4.3.

Table 4.3 Coarse/fine tuning combinations

| Coarse tuning | Fine tuning (dB) |    |    |    |    |    |    |    |

|---------------|------------------|----|----|----|----|----|----|----|

| (dB)          | 0                | 2  | 4  | 6  | 8  | 10 | 12 | 14 |

| 0             | 0                | 2  | 4  | 6  | 8  | 10 | 12 | 14 |

| 14            | NA               | 16 | 18 | 20 | 22 | 24 | 26 | 28 |

| 28            | NA               | 30 | 32 | 34 | 36 | 38 | 40 | 42 |

### (1) Coarse tuning

Coarse tuning is obtained by switching on/off the resistor  $R_{sni}$  and  $R_{spi}$  in Fig 4.2.

The high gain range (28dB to 42dB) requires the lowest linearity level because the input signal levels are very small ( $10 \sim 20 \text{mV}_{pp}$ ). Thus, source degeneration is not needed for the differential pairs. Hence,  $R_{sn1}$  ( $R_{sp1}$ ) and  $R_{Sn2}$  ( $R_{sp2}$ ) are disconnected by switching on  $S_8$  and  $S_9$ .

In the middle gain range (14dB to 26dB), the input signal is increased compared to the high gain case. To achieve the same linearity level, source degeneration should be included. By switching on  $S_8$  and switching off  $S_9$ ,  $R_{Sn2}$  ( $R_{sp2}$ ) is connected to the circuit to be the source degeneration resistor.

In the low gain range (0dB to 12dB), the VGA experiences the largest input signal. To maintain the similar linearity level, more source degeneration should be used. So, by switching off both  $S_8$  and  $S_9$ ,  $R_{sn1}$  ( $R_{sp1}$ ) and  $R_{Sn2}$  ( $R_{sp2}$ ) are connected in series as source degeneration.

The detailed calculation of source degeneration resistor values is derived in Appendix B.

#### (2) Fine tuning

Fine tuning is obtained by changing the dimensions of the transistors in the bias control circuit of the programmable current mirror. Details about this relation can be found in Chapter III. In our design, 0 ~ 14dB with 2dB/step needed in the fine tuning. So, we implement seven transistors in the bias control circuit to realize 2dB to 14dB.

Also, another switch  $S_8$  is used to short  $M_3$  when 0dB is required as shown in Fig 4.3. Table 4.4 shows the sequence to generate the gain steps.

Table 4.4 Gain vs. bias transistor mapping

| Transistors turn-on          | Gain steps |

|------------------------------|------------|

| $M_{b1}$                     | 2dB        |

| $M_{b1} + M_{b2}$            | 4dB        |

| •••                          | •••        |

| $M_{b1} + M_{b2} + + M_{b7}$ | 14dB       |

## IV.3.2 Input stage complementary differential pairs with source degeneration

Chapter II shows that the VGA based on complementary differential pairs with source degeneration boosts the transconductance while consuming the same power and maintains a similar linearity level as those of the simple differential pair with source degeneration. It is also more power efficient than the multiplier-based VGA and has a larger linear range than the differential pairs with the diode-connected loads-based VGA. Thus, it is used as the input-stage (Fig 4.2).

Also shown in Chapter II, the overall transconductance of this configuration is given by

$$Gm = \frac{g_{mn}}{1 + N_n} + \frac{g_{mp}}{1 + N_n} \tag{4.1}$$

where we define the source degeneration factor N as:  $N_n = g_{mn} \times R_{sn}/2$  and  $N_p = g_{mp} \times R_{sp}/2$

To select the transconductance of differential pairs, two approaches can be followed [8].

I) The saturation voltage  $(V_{DSAT})$  and the source degeneration factors of both differential pairs can be made equal. This approach provides good linearity, since the saturation voltages of both differential pairs can be maximized. Following this approach, it yields

$$V_{DSAT,n} = V_{DSAT,p} \text{ and } I_{bias,n} = I_{bias,p} \Rightarrow \frac{(W/L)_n}{(W/L)_n} = \frac{\mu_p}{\mu_n}$$

(4.2)

In IBM 6HP CMOS technology,  $\mu_n/\mu_p = 4.5$ , then  $(W/L)_p = 4.5$   $(W/L)_n$ . So, the PMOS differential pair will have large dimensions and hence large parasitic capacitance, which will limit the bandwidth of the VGA. This is a major drawback of this approach. The overall transconductance of this approach is given by

$$G_m = \frac{2g_{mp}}{1 + N_n} \tag{4.3}$$

II) Use the same dimensions for both differential pairs and also let  $N_n = N_p$ . Under this condition,  $V_{DSATp} = 2.1 V_{DSATn}$ ; so, the harmonic distortion components are dominated by the nonlinearities of the NMOS differential pair. With this approach, the overall transconductance is

$$G_{m} = \frac{g_{mp} \left( 1 + \sqrt{\mu_{n} / \mu_{p}} \right)}{1 + N_{n}} = \frac{3.13 g_{mp}}{1 + N_{n}}$$

(4.4)

For approach I, the  $V_{DSAT}$  of both differential pairs can be maximized together as they are equal; for approach II,  $V_{DSATp} = 2.1 V_{DSATn}$ , then  $V_{DSATp}$  should be maximized to the desired value, and then  $V_{DSATp}$  can be determined accordingly. Thus,  $V_{DSATp}$  is the same for both approaches.

To avoid the large parasitic due to the large size of PMOS differential pair, we use approach II in this design instead of approach I to design the complementary differential pairs, which use the same dimension for both differential pairs and the same degeneration factor  $N_n = N_p$ .

## IV.3.3 Current gain stage—programmable current mirror

The current amplification stage is implemented with the programmable current mirror, as it improves frequency response and achieves larger bandwidth than those of the simple current mirror.

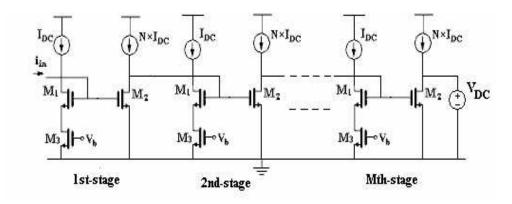

In [2] and [3], multi-stage amplification is used. With one programmable current mirror, its current gain is given by (3.10). Thus, with m identical cascade stages, its overall current gain is given by:

$$\frac{i_{out}}{i_{in}} \cong \left[ \frac{g_{m2}(C_1 + C_3)}{C_1(2C_1 + C_3)} \frac{s + \frac{g_{m1} + \frac{1}{R}}{C_1 + C_3}}{\left(s + \frac{g_{m1}}{2C_1}\right)\left(s + \frac{1}{R(C_1 + 0.5C_3)}\right)} \right]^{m} \tag{4.5}$$

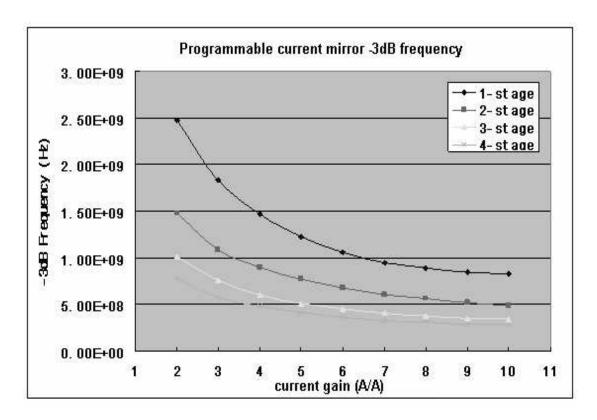

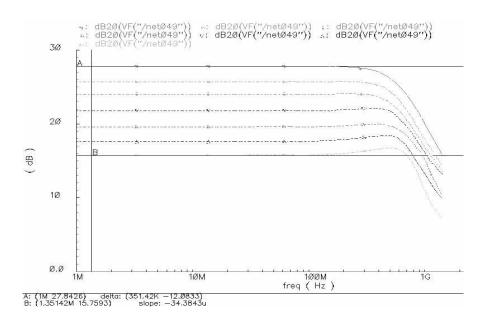

With the Cadence simulation, the  $f_{-3dB}$  of the multi-stage programmable current mirror vs. the current gain can be plotted as shown in Fig 4.8. The simulation setup is shown in Fig 4.7. The dimensions and the bias current values are the same as listed in

Table 3.3. Notice that for an M-stage programmable current mirror to obtain a total current gain of L, each current gain  $N = \sqrt[M]{L}$ .

Fig 4.7 Simulation setup for multi-stage programmable current mirror

Fig 4.8 shows that with two or more programmable current mirror stages, to implement current gain of 5 A/A, their f<sub>-3dB</sub> all drop to less than 700MHz. Including the parasitic capacitance from the input stage which is also connected to the diodeconnected node of the programmable current mirror, the overall f<sub>-3dB</sub> of the VGA may fall below the design requirement (>350MHz). Thus, to ensure enough bandwidth at a large gain variation, only one-stage programmable current mirror is chosen in this design. The details about the programmable current mirror are given in Chapter III.

Fig 4.8  $f_{\text{-3dB}}$  of the multi-stage programmable current mirror vs. current gain

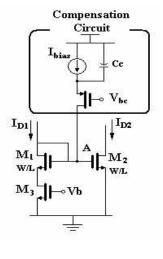

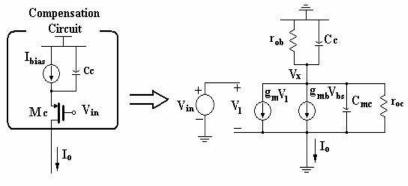

# IV.3.4 Frequency-compensation scheme

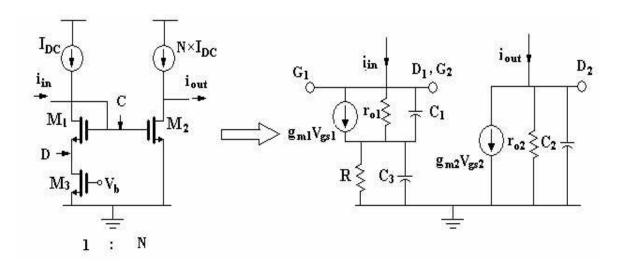

To ensure that even with all parasitic included the overall bandwidth of the VGA is still enough to meet the requirement, the frequency compensation is implemented. To explain the concept of this compensation and its effectiveness, we refer to the programmable current mirror in Fig 4.9.

Fig 4.9 Simplified schematic of the programmable current mirror

From equation 3.15, and there are two poles in the programmable current mirror:

$$\omega_{P1} = \frac{g_{m1}}{2C_1} \text{ (at node } C), \quad \omega_{P2} = \frac{1}{R(C_1 + 0.5C_3)} \text{ (at node } D).$$

where  $2C_1 = C_{GS1} + C_{GD1} + C_{DB1} + C_{GS2} + C_{GD2}$  and  $C_3 = C_{GD3} + C_{DB3} + C_{GS1} + C_{SB1}$

We can cancel some parasitic capacitance at node C. The capacitive frequency compensation is shown in Fig 4.9. At node  $V_{\text{o}}$ , ignoring the output resistance of compensation transistor:

$$I_o + g_m (V_X - V_{in}) + C_m s V_X = 0 \text{ and } I_o = C_C s V_X$$