# ALGORITHMS FOR THE SCALING TOWARD NANOMETER VLSI PHYSICAL SYNTHESIS

A Dissertation

by

CHIN NGAI SZE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2005

Major Subject: Computer Engineering

# ALGORITHMS FOR THE SCALING TOWARD NANOMETER VLSI PHYSICAL SYNTHESIS

## A Dissertation

by

# CHIN NGAI SZE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee,

Jiang Hu Charles J. Alpert Committee Members,

Melvin R. Mercer

Weiping Shi

Sing-Hoi Sze

Head of Department, Chanan Singh

December 2005

Major Subject: Computer Engineering

#### **ABSTRACT**

Algorithms for the Scaling Toward

Nanometer VLSI Physical Synthesis. (December 2005)

Chin Ngai Sze, B.Eng., The Chinese University of Hong Kong;

M.Phil., The Chinese University of Hong Kong

Chair of Advisory Committee: Dr. Jiang Hu

Along the history of Very Large Scale Integration (VLSI), we have successfully scaled down the size of transistors, scaled up the speed of integrated circuits (IC) and the number of transistors in a chip - these are just a few examples of our achievement in **VLSI scaling**. It is projected to enter the nanometer  $(10^{-9}m)$  scale era in the nearest future. At the same time, the scaling has imposed new challenges to physical synthesis. Among all the challenges, this thesis focuses on the following problems:

- Increasingly domination of interconnect delay leads to a need in interconnect-centric design flows;

- Different design stages (e.g. floorplanning, placement and global routing) have unmatched timing estimation, which brings difficulty in timing closure;

- More and more VLSI circuits are designed in architectural styles, which require a new set of algorithms.

The paper consists of two parts, each of which focuses on several specific problems in VLSI physical synthesis when facing the new challenges.

### • Part-1 Place and route aware buffer Steiner tree construction

Efficient techniques are presented for the problem of buffered interconnect tree construction under blockage and routing congestion constraint. This part also contains

timing estimation and buffer planning for global routing and other early stages such as floorplanning. A novel path based buffer insertion scheme is also included, which can overcome the weakness of the net based approaches.

# Part-2 Circuit clustering techniques with the application in Field-Programmable Gate Array (FPGA) technology mapping

The problem of timing driven n-way circuit partitioning with application to FPGA technology mapping is studied and a hierarchical clustering approach is presented for the latest multi-level FPGA architectures. Moreover, a more general delay model is included in order to accurately characterize the delay behavior of the clusters and circuit elements.

To my parent, YIU Wai Wah and SZE Ping Kwong.

#### **ACKNOWLEDGMENTS**

First, I would like to express my deepest gratitude to my advisor, Professor Jiang Hu for his guidance and kindness. He aroused my interest in the research of physical synthesis, piloted me when I was confused and encouraged me when I felt depressed. Besides, I would like to thank Professor Melvin R. Mercer, Professor Weiping Shi, Professor Sing-Hoi Sze and Dr. Charles J. Alpert for their advices.

Special thanks are given to Professor Ting-Chi Wang for his guidance when I first arrived at Texas A&M University.

Last, but not least, the greatest gratefulness is owed to my family. I am just nothing without them.

# TABLE OF CONTENTS

| CHAPTER |                                                                                        | Page |

|---------|----------------------------------------------------------------------------------------|------|

| I       | INTRODUCTION                                                                           | 1    |

|         | A. Motivation and Aims                                                                 | . 1  |

|         | B. Scaling Toward Nanometer VLSI Circuits                                              |      |

|         | 1. Scaling in FPGA                                                                     |      |

|         | C. Contribution                                                                        |      |

|         | 1. Interconnect Tree Synthesis with Buffer Insertion                                   | . 6  |

|         | 2. Circuit Clustering for FPGA Technology Mapping                                      | . 8  |

| II      | PERFORMANCE-DRIVEN INTERCONNECT TREE SYNTHE-<br>SIS AND BUFFER INSERTION               | 9    |

| III     | A PLACE AND ROUTE AWARE BUFFERED STEINER TREE                                          |      |

|         | CONSTRUCTION                                                                           | 12   |

|         | A. Introduction                                                                        | . 12 |

|         | B. Problem Formulation                                                                 | . 15 |

|         | C. The Algorithm                                                                       | . 17 |

|         | 1. Methodology Overview                                                                | . 17 |

|         | 2. Algorithm Motivation                                                                | . 17 |

|         | 3. Steiner Node Adjustment                                                             |      |

|         | 4. Minimum Cost Buffered Path                                                          |      |

|         | 5. Overall Algorithm                                                                   |      |

|         | D. Experimental Results                                                                |      |

|         | 1. Results for Real Multi-Sink Nets                                                    |      |

|         | 2. Results when More Choices for Expanded Node Set                                     |      |

|         | <ul><li>3. Results for Different Adjustment Flexibilities</li><li>4. Summary</li></ul> |      |

|         | E. Conclusion                                                                          |      |

| IV      | ACCURATE ESTIMATION OF GLOBAL BUFFER DELAY                                             | 22   |

|         | WITHIN A FLOORPLAN                                                                     | 33   |

|         | A. Introduction                                                                        |      |

|         | B. Closed Form Formula for Two-Pin Nets                                                |      |

|         | 1. Delay Formula with No Blockages                                                     | . 37 |

| CHAPTER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|         | 2. Delay Formula with Blockages  C. Two-Pin Experiments  D. Linear Time Estimation for Trees  1. Case 1: Unblocked Steiner Points  2. Case 2: Blocked Steiner Points  3. Linear Time Estimation Algorithm  E. Experiments for Multi-Sink Nets  1. Results on Random Nets  2. Results on Large Real Nets  F. Conclusion                                                                                                                                                                                               | 40<br>42<br>43<br>44<br>45<br>48<br>49                               |

| V       | PATH BASED BUFFER INSERTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                   |

|         | A. Introduction B. Problem Formulation C. Net Based Buffer Insertion D. Path Based Buffer Insertion 1. Buffer Aware Static Timing Analysis 2. Path Based Buffer Insertion 3. Off-Path Required Arrival Time Estimation E. Path Based Buffer Insertion and Simultaneous Gate Sizing 1. Gate Sizing at the Sinks F. Experimental Results 1. Path Based Buffer Insertion 2. Simultaneous Gate Sizing and Buffer Insertion 3. PBBI on ISCAS Circuits G. Different Orderings for Net Based Buffer Insertion H. Conclusion | 55<br>58<br>59<br>61<br>62<br>63<br>63<br>66<br>67<br>68<br>72<br>73 |

| VI      | CIRCUIT CLUSTERING FOR FPGA TECHNOLOGY MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                                                   |

| VII     | OPTIMAL CIRCUIT CLUSTERING FOR DELAY MINIMIZATION UNDER A MORE GENERAL DELAY MODEL  A. Introduction  B. Problem Definition  C. Previous Work and Pitfalls in Trivial Extensions  1. Previous Work  2. Pitfalls in Trivial Extensions                                                                                                                                                                                                                                                                                 | 81<br>83<br>83                                                       |

|         | D. Vertey Grouping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86                                                                   |

| CHAPTER  |                                                                                                                | Page                                          |

|----------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|          | <ul><li>E. The Algorithm</li><li>F. Optimality and Complexity of the Algorithm</li><li>G. Conclusion</li></ul> | 93                                            |

|          |                                                                                                                | 90                                            |

| VIII     | MULTI-LEVEL CIRCUIT CLUSTERING FOR DELAY MINIMIZATION                                                          | . 99                                          |

|          | A. Introduction                                                                                                | 102<br>106<br>108<br>110<br>114<br>114<br>115 |

|          | E. Postprocessing Techniques                                                                                   | 126                                           |

| IX       | SUMMARY AND CONCLUSIONS                                                                                        |                                               |

| REFERENC | ES                                                                                                             | . 133                                         |

| APPENDIX | A                                                                                                              | . 140                                         |

| VITA     |                                                                                                                | . 142                                         |

# LIST OF TABLES

| TABLE |                                                                                                                                          | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| I     | Projections of VLSI chips feature size                                                                                                   | 2    |

| II    | Information of all testcases                                                                                                             | 27   |

| III   | Comparison between POROSITY and PRAB under $3\times 3$ tiles adjustment flexibility                                                      | 29   |

| IV    | Comparison between POROSITY and PRAB under $5\times 5$ tiles adjustment flexibility                                                      | 30   |

| V     | Summary of total timing improvement and congestion cost for all 10 nets under different adjustment flexibilities                         | 30   |

| VI    | Comparison of the blockage buffered delay formula with van Ginneken's algorithm for multiple blockages on a 2-pin net with length $12mm$ | 42   |

| VII   | Experiments on randomly generated nets. Each row represents the average of nine different nets                                           | 50   |

| VIII  | Experiments for 13 nets from an industry design                                                                                          | 51   |

| IX    | Summary of testcases                                                                                                                     | 69   |

| X     | Comparison of net based and path based buffer insertion                                                                                  | 71   |

| XI    | Comparison of net based and path based buffer insertion considering buffer blockages                                                     | 71   |

| XII   | Comparison of net based and path based buffer insertion considering gate sizing                                                          | 72   |

| XIII  | Summary of ISCAS placed and routed circuits                                                                                              | 73   |

| XIV   | Comparison of net based and path based buffer insertion                                                                                  | 74   |

| TABLE |                                                              | Page |

|-------|--------------------------------------------------------------|------|

| XV    | Number of buffers inserted for 20 testcases                  | 76   |

| XVI   | Comparison between two TLC implementations and our algorithm | 129  |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                                                                                                        | Page  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1      | Scaling of the gate delay                                                                                                                                                                                                                                                                                                                                                              | 3     |

| 2      | Scaling of the local and global interconnect delay                                                                                                                                                                                                                                                                                                                                     | 4     |

| 3      | Interconnection projections                                                                                                                                                                                                                                                                                                                                                            | 5     |

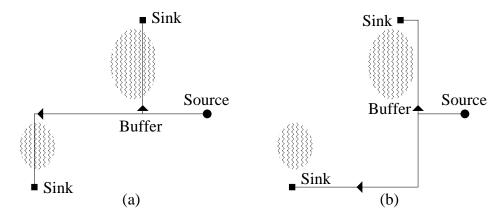

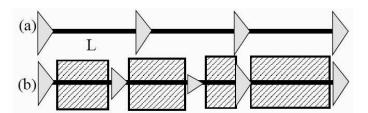

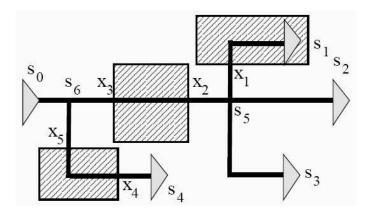

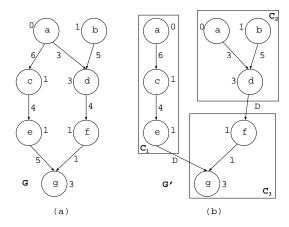

| 4      | A minimum Steiner tree as shown in (a) may force buffers being inserted at dense regions. A placement congestion aware buffered Steiner tree, which is shown in (b), will enable a buffer solution at sparse regions.                                                                                                                                                                  | 13    |

| 5      | A minimum buffered Steiner tree as shown in (a) may force wires going through routing congested regions. A routing congestion aware buffered Steiner tree, which is shown in (b), will enable a buffer solution at less congested regions.                                                                                                                                             | 15    |

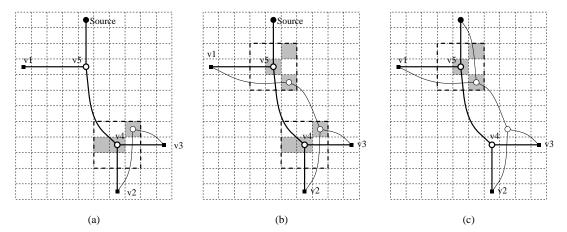

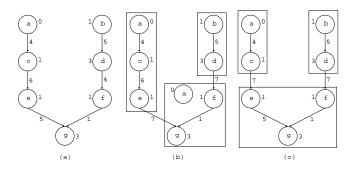

| 6      | (a) Candidate solutions are generated from $v_2$ and $v_3$ and propagated to every shaded tile for $v_4$ . (b) Solutions from $v_1$ and every shaded tile for $v_4$ are propagated to $v_5$ and its alternative nodes. (c) Solutions from $v_5$ and its alternative nodes are propagated to the source and the thin solid lines indicate an alternative tree that may result from this | 20    |

| 7      | process                                                                                                                                                                                                                                                                                                                                                                                | 20    |

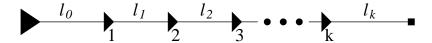

| 7      | Buffer positions along a path                                                                                                                                                                                                                                                                                                                                                          | 22    |

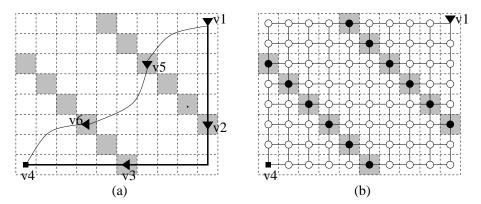

| 8      | Find low congestion path with known buffer positions indicated by the shaded tiles                                                                                                                                                                                                                                                                                                     | 23    |

| 9      | Core algorithm.                                                                                                                                                                                                                                                                                                                                                                        | 24    |

| 10     | Subroutine of propagating candidate solutions from one node set to another                                                                                                                                                                                                                                                                                                             | r. 25 |

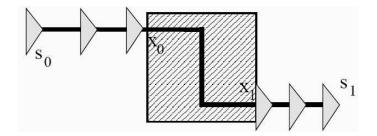

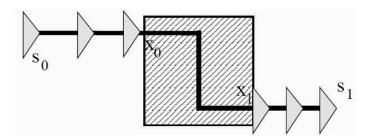

| 11     | Example of (a) an optimally buffered line with equal spaced buffers and (b) an optimal realizable buffering when blockages are present.  Note that unequal buffer sizes may be used here.                                                                                                                                                                                              | 35    |

| FIGURE |                                                                                                                                                       | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

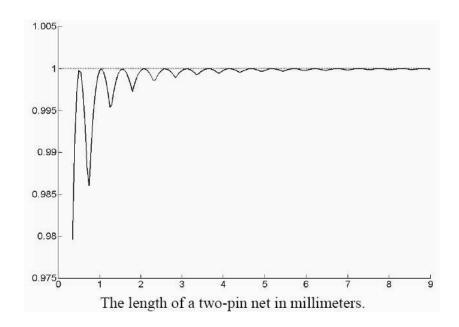

| 12     | Ratio of Equation (1) to (2) as a function of wirelength                                                                                              | 38   |

| 13     | Buffering scheme on a route of length $L=l(s_0,s_1)$ with a single blockage spanning length $w=l(x_0,x_1)$                                            | 40   |

| 14     | Comparison of the blockage buffered delay formula with van Ginneken's algorithm for the case of a single blockage on a 2-pin net with length $10mm$ . | 41   |

| 15     | Multi-sink tree with only unblocked Steiner points                                                                                                    | 43   |

| 16     | Multi-sink tree example with blocked Steiner points                                                                                                   | 45   |

| 17     | Linear time estimation algorithm for trees.                                                                                                           | 47   |

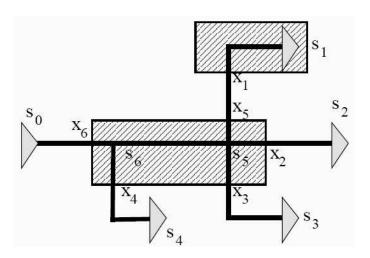

| 18     | Net based buffer insertion solutions depend on net ordering                                                                                           | 54   |

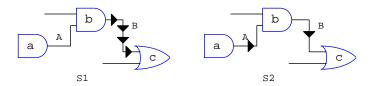

| 19     | Example of combinational circuit models                                                                                                               | 56   |

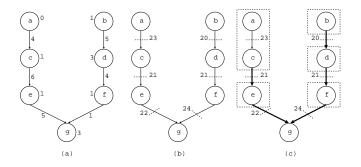

| 20     | Example of algorithm overview                                                                                                                         | 60   |

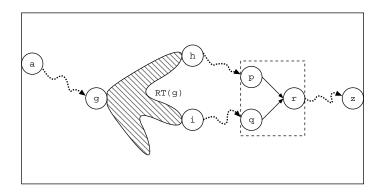

| 21     | A problem of path based buffer insertion algorithm                                                                                                    | 64   |

| 22     | Example of a circuit for Theorem 1                                                                                                                    | 65   |

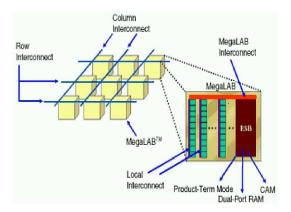

| 23     | The MegaLAB structure in Altera APEX 20K devices                                                                                                      | 79   |

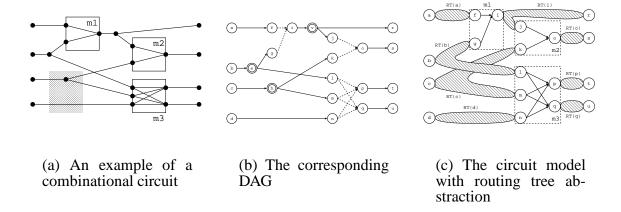

| 24     | A circuit with variable interconnect delay and a clustered circuit                                                                                    | 84   |

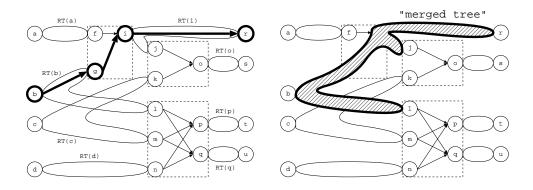

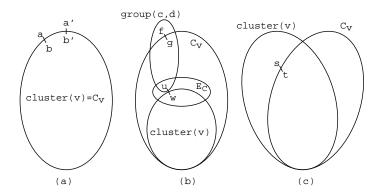

| 25     | Examples of circuit clustering                                                                                                                        | 87   |

| 26     | Illustration of vertex grouping                                                                                                                       | 88   |

| 27     | Illustration of Proof of Lemma 3                                                                                                                      | 97   |

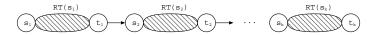

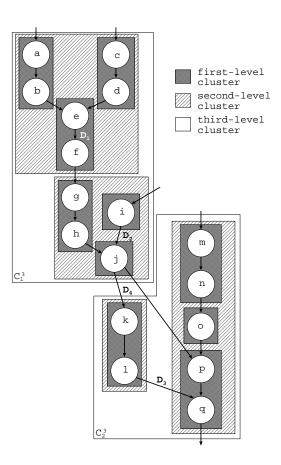

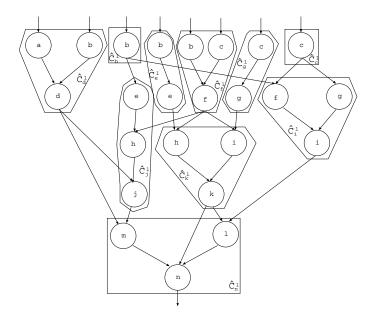

| 28     | An example of circuit clustering with three levels                                                                                                    | 105  |

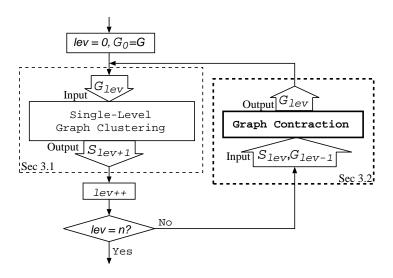

| 29     | The flow of our algorithm                                                                                                                             | 106  |

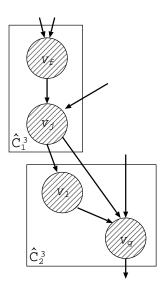

| 30     | The corresponding $\hat{S}_3$ of $S_3$ in Figure 28                                                                                                   | 109  |

| 31     | The pseudo-code of our single-level graph clustering algorithm                                                                                        | 111  |

| FIGURE | 3                                                                                | Page |

|--------|----------------------------------------------------------------------------------|------|

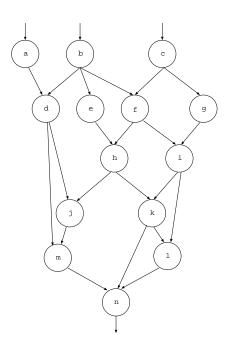

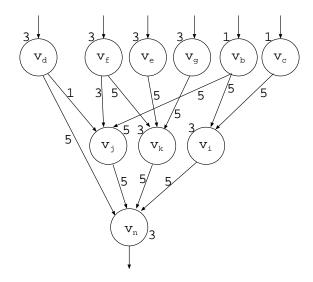

| 32     | A sample circuit $G_0$                                                           | 113  |

| 33     | First-level clustering $\hat{S}_1$ for Figure 32                                 | 114  |

| 34     | The pseudo-code of our graph contraction algorithm                               | 115  |

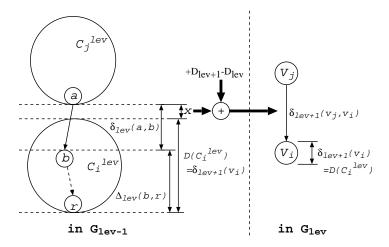

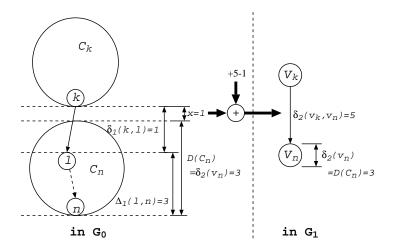

| 35     | Illustration of edge delay calculation in $Graph\_Contraction$                   | 117  |

| 36     | The contracted graph $G_1$ constructed from $\hat{S}_1$ and $G_0$                | 118  |

| 37     | Example of delay calculation of the new edge $(v_k, v_n)$ in $G_1 \ldots \ldots$ | 119  |

| 38     | Second-level clustering $\hat{S}_2$ on $G_1$                                     | 120  |

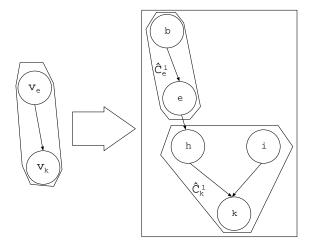

| 39     | A simple example about conversion from $\hat{C}_i^{lev}$ to $C_i^{lev}$          | 121  |

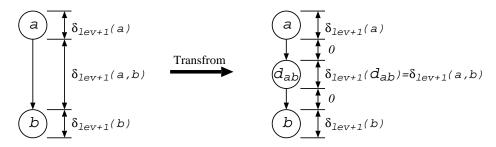

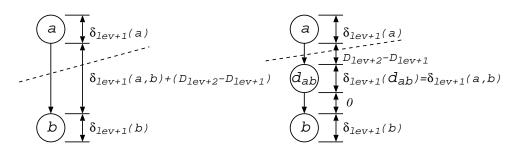

| 40     | Transformation to general delay model                                            | 125  |

| 41     | A simplified VLSI design cycle                                                   | 140  |

#### CHAPTER I

#### INTRODUCTION

### A. Motivation and Aims

Very Large Scale Integration (VLSI) is the process of placing more than  $10^4$  of electronic components on a single chip, namely integrated circuits. It can generally be found in modern memories, computers, signal processors. Due to the very high complexity of VLSI processes, designs of VLSI chips using computer systems are essential in order to reduce the time-to-market (TTM) and cost per transistors, as well as improve total yield. This refers as to the Computer-Aid Design (CAD) or Electronic Design Automation (EDA).

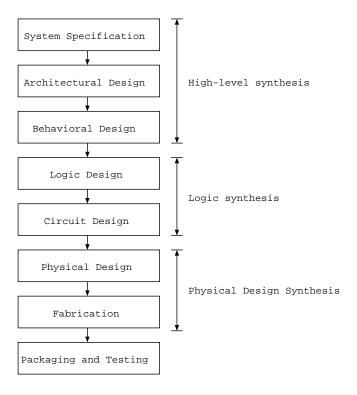

Traditionally, the CAD for VLSI can simply be separated into three steps: high level synthesis (involving Behavioral Synthesis and Sequential Synthesis), logic synthesis (including technology mapping) and physical design synthesis[1, 2]. The detailed design process is shown in Figure 41 in Appendix A. High level synthesis consists of the construction of behavioral and functional specification and the conversion from specification into hardware descriptions such as Finite State Machine (FSM). Logic synthesis refers to the translation of high-level language descriptions into logic designs (a set of technology specific gates and interconnects, or netlist) and the optimization of the chip area, speed (delay) and testability. Physical design synthesis transforms the circuit representation into a geometric representation, the physical layout. It involves the process of circuit partitioning, floorplanning, placement, and routing. The objective of physical design is to minimize the chip area and to maintain chip performance. Since the design processes are very complicated, these steps often operate separately and, there is no interaction between them. However, the de-

This thesis follows the style of *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*..

Table I. Projections of VLSI chips feature size

| Year of 1 <sup>st</sup> Product shipment | 1999 | 2002 | 2005 | 2008 | 2011 | 2014 |

|------------------------------------------|------|------|------|------|------|------|

| Minimum feature size (nm)                | 180  | 130  | 100  | 70   | 50   | 35   |

| (DRAM half-pitch)                        |      |      |      |      |      |      |

sign processes are changing due to the development of sub-micron and deep sub-micron VLSI technology in the last decade. And we are expecting the process continues toward nanometer VLSI technology which will bring us with more new problems.

## B. Scaling Toward Nanometer VLSI Circuits

In 1965, Gordon E. Moore, the co-founder of Intel Corporation, predicted that "The complexity for minimum component costs has increased at a rate of roughly a factor of two per year". After the 70's, this prediction is generally formulated as "the number of transistors on integrated circuits will be doubled every 18 months." The projection is usually referred to as "The Moore's Law".

The Moore's Law is roughly valid throughout the past several decades due to the rapid development of fabrication technology. We can observe that the VLSI feature size, which is usually attributed by DRAM half pitch of the chip, shrinks along with the process generations. The shrinking in chip element size and increase in chip density is generally referred to as the "scaling" of VLSI circuits. According to several reports [3, 4], the feature size will be 70nm and 50nm in 2008 and 2011 respectively. The information is shown in Table I.

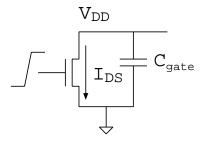

We can use the scaling factor S to describe the scaling effect for consecutive generations (Typically, S=1.5). The gate delay can be characterized by Equation (1.1) as shown

in Figure 1.

$$t_{gate} = \frac{C_{gate}V_{DD}}{I_{DS}} \tag{1.1}$$

When the scaling proceed, we have  $\frac{C_{gate}}{S}$ ,  $\frac{V_{DD}}{S}$  and  $\frac{I_{DS}}{S}$ . Therefore, gate delay is reduced by a factor S for each generation.

Fig. 1. Scaling of the gate delay

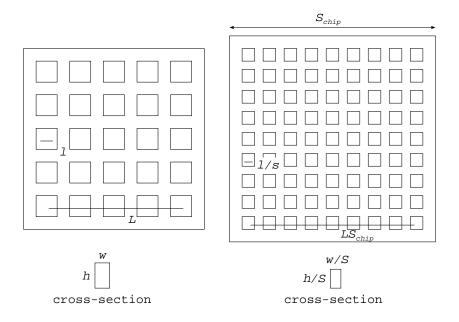

However, scaling has imposed a difference effect on the interconnect delay as shown in Figure 2. The interconnect delay can be formulated by Equation (1.2), where r is the unit length resistance, c is the unit length capacitance,  $k_1$  and  $k_2$  is the resistive and capacitive coefficient,  $w_s$  is the spacing between adjacent interconnects.

$$t_{interconnect} = rcl^2 = \frac{k_1}{wh} \frac{k_2 h}{w_s} l^2 \tag{1.2}$$

If the interconnect dimension and spacing is scaled uniformly, the local interconnect delay will become  $rcS^2(\frac{l}{S})^2$  so that the delay remains unchanged during scaling. However, the length of global interconnect does not scale downward according to the shrink of feature size. On the contrary, it scales upward slightly with the chip size  $S_{chip}$ . As a result, the delay along global interconnect becomes  $rcS^2(lS_{chip})^2$  which is a quadratic relationship to S and becoming much worse when comparing to the gate delay. Hence, as the VLSI

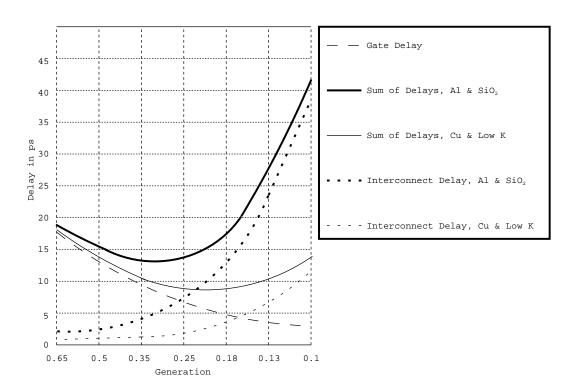

technology scales downward, the interconnect delay has already dominated the total path delay, which includes interconnect and gate delays. (See Figure 3 [3]).

Fig. 2. Scaling of the local and global interconnect delay

The decrease in chip feature size and increase in complexity of chip design also bring the following effects:

- more hierarchical design schemes are needed.

- noise effect is exacerbated.

- power dissipation becomes unmanageable.

As a result, the link between each design stage is loosing. For example, a verified design in logic synthesis steps may violate the rules in physical design steps. Also, a placement with minimum "wirelength" does not produce a final layout with minimum clock cycle.

Fig. 3. Interconnection projections

# 1. Scaling in FPGA

Field-programmable gate array (FPGA) is one of the fastest growing semiconductor sectors. In fact, the growth of FPGA industry is faster than the average of the semiconductor industry. This can be justified by the following examples [5]. In 1988, the Altera MAX 5000 family had only 600 to 3,750 gates, while in 1999, each APEX 20K devices provide 60,000 to 1.5 million usable gates. Similarly, for the Xilinx XC2000 device family introduced in 1985, each device has 1200 to 1800 logic gates, while in 1998, Xilinx Virtex devices provides 58K to 4M gates.

Although the clock speed of FPGAs is comparatively slower than high-end custom-designed devices such as microprocessor, there are many problems related to the increasing complexity of FPGA. For example, there are becoming more hierarchical FPGA architectures to remedy the FPGA design difficulty. In fact, one example of hierarchical FPGA architectures can be found in the APEX20K device family which uses a two-level hierarchy (see Figure 23). Besides, the delay along interconnect is also increasing as the increase in chip size and decrease in size of the logic array blocks.

### C. Contribution

This research project focuses on solving the physical design problems due to the rapid scaling of VLSI systems. The work can be divided into two parts: interconnect tree synthesis with buffer insertion and circuit clustering for FPGA technology mapping.

### 1. Interconnect Tree Synthesis with Buffer Insertion

As mentioned in previous section, interconnect delay is dominating the total delay in the circuit. Buffer insertion is one of the most effective methods to reduce wire delay. Moreover, since buffer insertion improves interconnect timing, the timing estimation in different

stage using different buffering assumption can differ a lot. This actually is one of the reasons why the link between different design stages is getting loose. More importantly, sometimes an inaccurate timing estimation in early stages is vital to the timing closure of the design process.

Due to the high importance of buffer insertion to physical synthesis and timing, I have performed three projects related to buffering and interconnect tree synthesis.

# • Place and route aware buffered Steiner tree construction

A tree adjustment technique is proposed which modifies a given Steiner tree and simultaneously handles the objectives of timing, placement and routing congestion. To the best of my knowledge, this is the first study which simultaneously considers these three objectives for the buffered Steiner tree problem. Experimental results confirm the effectiveness of the algorithm while it achieves up to  $20 \times$  speed-up when comparing with the state-of-the-art algorithm. The project is described in Chapter III.

# • Accurate estimation of global buffer delay within a floorplan

The closed formed delay expressions of a buffered interconnect are extended to show how one can model the blocks into a simple delay estimation technique that applies both to two-pin and to multi-pin nets. Even though the formula uses one buffer type, it shows remarkable accuracy in predicting delay when compared to an optimal realizable buffer insertion solution. Potential applications include wire planning, timing analysis during floorplanning or global routing. Our experiments show that our approach accurately predicts delay when compared to constructing an realizable buffer insertion with multiple buffer types. The project is detailed in Chapter IV.

### • Path based buffer insertion

A novel path based buffer insertion scheme is introduced which can overcome the weakness of the conventional net based approaches. Experimental results show that

our method can efficiently reduce buffer/gate cost significantly (by 71% on average) when compared to traditional net based approaches. In literature, This is the first work on path based buffer insertion and simultaneous gate sizing. The project is explained in Chapter V.

# 2. Circuit Clustering for FPGA Technology Mapping

Owing to the rapid growth of FPGA density, we have more logic blocks in a FPGA chip. The delay in interconnect is becoming more important. In the second part of this thesis, two projects are presented to solve physical design problems related to latest FPGA designs.

# Optimal circuit clustering for delay minimization under a more general delay model

For the problem of area-constrained clustering for delay minimization, I proposed a more general delay model, which practically takes variable interconnect delay into account. The delay model is particularly applicable when allowing the back-annotation of actual delay information to drive the clustering process. An algorithm is presented to the clustering problem and can be proved to solve the problem optimally in polynomial time. This work is presented in Chapter VII.

## • Multi-level circuit clustering for delay minimization

An effective scheme is proposed for multi-level circuit clustering for delay minimization, which is applicable to hierarchical FPGAs. In fact, our algorithm is the first one for the general multi-level circuit clustering problem with more than two levels. The project is included in Chapter VIII.

#### **CHAPTER II**

# PERFORMANCE-DRIVEN INTERCONNECT TREE SYNTHESIS AND BUFFER INSERTION

Due to the development of fabrication technology, the VLSI synthesis processes are entering the deep sub-micron range (feature size < 500 nm). According to the projection in International Technology Roadmap for Semiconductors 2000, the VLSI chips feature size will drop to 100nm and 70nm in 2007 and 2010 respectively. Owing to the tremendous drop in chip feature size, the interconnect delay becomes a dominant part of the total path delay, which includes both the interconnect and gate delays. Since the importance of interconnect delay on VLSI timing optimization increases rapidly, some timing-driven interconnect routing methodologies adopted in current design cycles no longer produce feasible timing solution. Buffering in the interconnect tree is one of the effective techniques to optimize overall system performance and link between different design stages.

However, current buffer insertion techniques are too specific and their applications are very limited within the overall design cycle. As a result, my research is to develop a comprehensive interconnect tree synthesis algorithm which simultaneously handles multiple objectives such as buffer and wiring costs, obstacles, routing congestion, and signal integrity while the algorithm can be applied at different stages in the VLSI Computer-Aided Design cycles.

We focus on the following three objectives of the buffered tree synthesis problem in the next three chapters.

### • Place and route aware buffered Steiner tree construction

In order to achieve timing closure on increasingly complex IC designs, buffer insertion needs to be performed on thousands of nets within an integrated physical synthesis system. In most of previous works, buffers may be inserted at any open space. Even when there may appear to be space for buffers in the alleys between large blocks, these regions are often densely packed or may be useful later to fix critical paths. In addition, a buffer solution may inadvertently force wires to go through routing congested regions. Therefore, within physical synthesis, a buffer insertion scheme needs to be aware of both placement congestion and routing congestion of the existing layout and so it has to be able to decide when to insert buffers in dense regions to achieve critical performance improvement and when to utilize the sparser regions of the chip. With the proposed Steiner tree adjustment technique, this work aims at finding congestion-aware buffered Steiner trees. Our tree adjustment technique takes a Steiner tree as input, modifies the tree and simultaneously handles the objectives of timing, placement and routing congestion. To our knowledge, this is the first study which simultaneously considers these three objectives for the buffered Steiner tree problem. Experimental results confirm the effectiveness of our algorithm while it achieves up to  $20 \times$  speed-up when comparing with the state-of-the-art algorithm [6].

### Accurate estimation of global buffer delay within a floorplan

Closed formed expressions for buffered interconnect delay approximation have been around for some time. However, previous approaches assume that buffers are free to be placed anywhere. In practice, designs frequently have large blocks that make the ideal buffer insertion solution unrealizable. The theory of [7] is extended to show how one can model the blocks into a simple delay estimation technique that applies both to two-pin and to multi-pin nets. Even though the formula uses one buffer type, it shows remarkable accuracy in predicting delay when compared to an optimal realizable buffer insertion solution. Potential applications include wire planning, timing analysis during floorplanning or global routing. Our experiments

show that our approach accurately predicts delay when compared to constructing an realizable buffer insertion with multiple buffer types.

### • Path based buffer insertion

Along with the progress of VLSI technology, buffer insertion plays an increasingly critical role on affecting circuit design and performance. Traditional buffer insertion algorithms are mostly net based and therefore often result in sub-optimal delay or unnecessary buffer expense due to the lack of global view. In this paper, we propose a novel path based buffer insertion scheme which can overcome the weakness of the net based approaches. We also discuss some potential difficulties of the path based buffer insertion approach and propose solutions to them. A fast estimation on buffered delay is employed to improve the solution quality. Gate sizing is also considered at the same time. Experimental results show that our method can efficiently reduce buffer/gate cost significantly (by 71% on average) when compared to traditional net based approaches. To the best of our knowledge, this is the first work on path based buffer insertion and simultaneous gate sizing.

#### **CHAPTER III**

## A PLACE AND ROUTE AWARE BUFFERED STEINER TREE CONSTRUCTION

#### A. Introduction

It has been widely recognized that interconnect becomes a dominating factor for modern VLSI circuit designs. A key technology to improve interconnect performance is buffer insertion. A recent study by Intel [8] speculates that for 35nm technology, 70% of the cells on a chip will be buffers.

Early works on buffer insertion are mostly focused on improving interconnect timing performance. The most influential pioneer work is van Ginneken's dynamic programming algorithm [9] that achieves polynomial time optimal solution on a given Steiner tree under Elmore delay model [10]. In [11], Lillis *et al.* extended van Ginneken's algorithm by using a buffer library with inverting and non-inverting buffers, while also considering power consumptions.

The major weakness of the van Ginneken approach is that it requires a fixed Steiner tree topology which makes the final buffer solution quality dependent on the input Steiner tree. Even though it is optimal for a given topology, the van Ginneken algorithm will yield poor solutions when it is fed with a poor topology. To overcome this problem, several works have proposed to simultaneously construct a Steiner tree while performing buffer insertion [12, 13, 14]. Although the simultaneous algorithms generally yield high quality solution, their time complexities are very high. A different approach to solve the weakness of van Ginneken's algorithm is proposed by Alpert *et al.* [15]. They construct a "bufferaware" Steiner tree, called C-Tree for van Ginneken's algorithm. Despite being a two-stage sequential method, it yields solutions comparable in quality to simultaneous methods, while consuming significantly less CPU time.

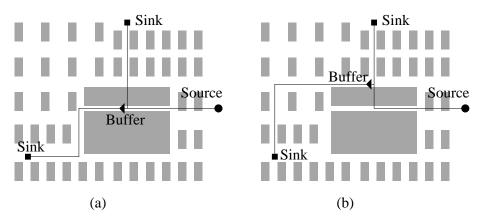

Fig. 4. A minimum Steiner tree as shown in (a) may force buffers being inserted at dense regions. A placement congestion aware buffered Steiner tree, which is shown in (b), will enable a buffer solution at sparse regions.

Recent trends towards hierarchical (or semi-hierarchical) chip design and system-on-chip design force certain regions of a chip to be occupied by large building blocks or IP cores so that buffer insertion is not permitted. These constraints on buffer locations can severely hamper solution quality, and these effects have to be considered in the buffered path [16, 17, 18] class of algorithms. Though optimal, they are only applicable to two pin nets. Works that handle restrictions on buffer locations while performing simultaneous Steiner tree construction and buffer insertion are proposed in [19, 20], which can provide high quality solutions though the runtimes are too exorbitant to be used in a physical synthesis system. In [21], a Steiner tree is rerouted to avoid buffer blockages before conducting buffer insertion. This sequential approach is fast, but sometimes unnecessary wiring detours may result in poor solutions. An adaptive tree adjustment technique is proposed in [22] to obtain good solution results efficiently.

The huge number of nets that require buffering means that resources have to be allocated intelligently. For example, large blocks closely placed together create narrow alleys that are magnets for buffers since they are the only locations that buffers can be inserted for those routes that cross over these blocks. But competition for resources for these routes

is very fierce. Inserting buffers for less critical nets can eliminate space that is needed for more critical nets which require gate sizing or other logic transforms. Further, though no blockages lie in the alleys, these region could already be packed with logic and feasible space may not exist for the buffers. If the buffer insertion algorithm cannot recognize this scenario, after a buffer is inserted into this congested space, placement legalization may shift it out too far from its original location due to cell overlap. Hence, whenever possible one should avoid denser regions unless it is absolutely critical. For example, Figure 4(a) shows a multi-pin net which is routed through a dense region or "hot spot", and (b) shows that the Steiner point is moved outside of the dense region in order to obtain an improved buffer insertion result.

Similarly, a buffer solution may inadvertently force wires to go through routing congested regions such as in Figure 5(a). Such solution causes wire detours in routing stage. Generally speaking, an L-shaped wire has flexibilities on avoiding congestions without increasing wirelength. These flexibilities may be ripped off when inserted buffers make the L-shaped wire into a set of straight connections. If we let the buffering algorithm be aware of the routing congestions, these flexibilities can be kept for congestion avoidance in later routing stage.

To the best of our knowledge, the only published work about placement congestion aware buffer insertion is the porosity aware buffered Steiner tree problem addressed in [6]. This work integrates the length-based buffer insertion [23] with a plate-based tree adjustment to obtain a Steiner tree at regions with greater porosity. However, the routing congestion is not considered and the runtime overhead is too large.

This work adopts the sequential method in constructing a Steiner tree and the tree is then fed into a van Ginneken style buffer insertion algorithm. However, before buffer insertion, a timing-driven plate-based tree adjustment algorithm is applied so that both the placement and routing congestion are considered. Buffered paths between nodes are

Fig. 5. A minimum buffered Steiner tree as shown in (a) may force wires going through routing congested regions. A routing congestion aware buffered Steiner tree, which is shown in (b), will enable a buffer solution at less congested regions.

found through utilizing the analytical form buffered path solution and a congestion cost driven maze routing. In [6], each solution during path search is characterized by its cost and downstream capacitance, thus, the solution set is a two-dimensional array while at the same time, the tree adjustment is not driven by timing optimization. In the maze routing of this work, only the congestion cost is considered for each candidate solution. Therefore, the candidate solution set is a one-dimensional array and this smaller-sized solution set enables a faster computational speed. In fact, our experiment shows that, when comparing with [6], our algorithm achieves 7% better timing, 9% lower total placement and routing congestion but runs up to 20 times faster.

#### B. Problem Formulation

In this paper, we use a tile graph to capture the placement and routing congestion information and at the same time reduce the complexity of our problem. A tile graph is represented as  $G = (V_G, E_G)$  such that  $V_G = \{g_1, g_2, ...\}$  is a set of tile and  $E_G$  is a set of boundaries each  $(g_i, g_j)$  of which is between two adjacent tile  $g_i$  and  $g_j$ .

If a tile  $g_i \in V_G$  has an area of  $A(g_i)$  and its area occupied by placed cells are  $a(g_i)$ , the

placement density is defined as the area usage density  $d(g_i) = \frac{a(g_i)}{A(g_i)}$ . Let  $W(g_i, g_j)$  be the maximum number of wires that can be routed across the tile boundary  $(g_i, g_j)$  and  $w(g_i, g_j)$  be the number of wires crossing  $(g_i, g_j)$ . Similarly, the boundary density is  $d(g_i, g_j) = \frac{w(g_i, g_j)}{W(g_i, g_j)}$ .

A net is represented as a set of sinks  $V_{sink} = \{v_1, v_2, ..., v_n\}$  and a source node  $v_0$ . Each sink  $v_i \in V_{sink}$  at location  $(x_i, y_i)$  is associated with a load capacitance  $c(v_i)$  and a required arrival time  $q(v_i)$ . The source node is at  $(x_0, y_0)$  and is associated with a driver with driver resistance  $R_d$ . For simplification, a buffer type with input capacitance  $C_b$ , intrinsic delay  $t_b$  and output resistance  $R_b$  is used. The unit wire resistance is r and the unit wire capacitance is r. We use Elmore model [10] for interconnect delay and RC switch model for driver and buffer delay.

**Problem Definition:**(Buffered Steiner Tree for Placement and Routing Congestion Mitigation) Given a net  $N = \{v_0, v_1, \ldots, v_n\}$  with source  $v_0$  and sinks  $\{v_1, \ldots, v_n\}$ , load capacitance  $c(v_i)$  and required arrival time  $q(v_i)$  for  $1 \le i \le n$ , tile graph  $G(V_G, E_G)$ , and a buffer type b, construct a Steiner tree T(V, E), in which  $V = N \cup V_{Steiner}$  and edges in E span every node in V, such that a buffer insertion solution that satisfies  $q(v_i)$  is obtained with a minimum congestion cost S.

The congestion cost can be formulated based on the application but the algorithm should have the flexibility to take any kind of congestion cost formulation. In this paper, we adopt the following definition. The placement cost  $p(g_i)$  of placing a buffer in a tile  $g_i$  is the square of the density  $d(g_i)$ ; while the routing cost  $p(g_i, g_j)$  crossing a tile boundary  $(g_i, g_j)$  is the square of the boundary density  $d(g_i, g_j)$ . With this cost definition, we do not use an infinite cost for overflow. In reality, if the placement or routing on a dense region really helps improving slack or other design objectives, moving the previously placed and routed elements in the next design cycle would be more beneficial.

# C. The Algorithm

# 1. Methodology Overview

Since simultaneous Steiner tree construction and buffer insertion is computationally expensive for practical circuit designs, we propose to solve the congestion aware buffered Steiner tree problem through the following three stages: 1)Initial timing-driven Steiner tree construction<sup>1</sup>; 2)Tree adjustment for congestion improvement; 3)Van Ginneken style buffer insertion.

Stage 1 can be accomplished by any heuristics while we apply "buffer aware" C-Tree algorithm[15]. Stage 2 contains the key ideas behind the algorithm. The tree adjustment phase modifies the existing timing-driven Steiner tree in an effort to reduce congestion cost while maintaining the tree's high performance. It allows Steiner points to migrate outside of congested tiles into lower-congestion tiles while maintaining (if not improving) performance. Finally, in Stage 3 the resulting tree topology is fixed for van Ginneken style buffer insertion. Since we use known algorithms for Stages 1 and 3, the rest of the discussion focuses on stage 2, which is the main contribution of this work.

## 2. Algorithm Motivation

The basic idea for the tree adjustment is to perform a simplified simultaneous buffer insertion<sup>2</sup> and local tree topology modification so that the Steiner nodes and wiring paths can be moved to less congested regions without significant disturbance on the timing performance obtained in Stage 1. Also for the sake of simplification, we assume a single "typical" buffer

<sup>&</sup>lt;sup>1</sup>We choose a timing-driven Steiner tree algorithm here since it is fast and easy to implement with our proposed tree adjustment technique. However, any Steiner tree (e.g., congestion-aware Steiner tree) can also be fed into stage 2 of our overall algorithm.

<sup>&</sup>lt;sup>2</sup>Note that the "buffer insertion" in tree adjustment is for timing estimation. Actual buffer insertion is performed in stage 3 of our algorithm.

type, the Elmore delay model for interconnect and a switch level RC gate delay model for this tree adjustment. The tree adjustment traverses the given Steiner topology in a bottom-up fashion similar to van Ginneken's algorithm. During this process, candidate buffering and routing solutions are propagated from leaf nodes towards the source. At a Steiner node, candidate solutions from its two child branches are merged. Therefore, we can consider the propagation and merging process separately.

The buffered Steiner tree problem is inherently very difficult to solve and including congestions into account makes the complexity even more formidable. In this problem, three major factors (1) timing (2) load capacitance and (3) congestion cost have to be considered simultaneously on a two-dimensional Manhattan plane. Note that load capacitance needs to be evaluated and maintained for delay calculation even though it is not a part of objectives. In order to make the computation time practical, solution quality has to be sacrificed to a certain degree. Of course, the sacrifice on solution quality need to be as small as possible while the computation cost reduction has to be substantial. In [6], a length-based buffer insertion [23] scheme is employed to reduce complexity. Instead of maintaining all the timing and load capacitance information, only the maximum driving load for each buffer/driver is enforced as a rule of thumb. Therefore, the number of factors is reduced from three to two and the computation speed is acceptable. However, the experimental results in [6] show that runtime is almost doubled just because of considering congestions. The runtime bottleneck is due to the fact that buffering solution has to be searched along with node-to-node<sup>3</sup> paths in a two-dimensional plane since low congestion paths have to be found at where the buffers are needed.

If we can predict where buffers are needed in advance, then we can merely focus on searching low congestion paths and the number of factors to be considered can be further re-

<sup>&</sup>lt;sup>3</sup>The node may be the source node, a sink node or a Steiner node of degree greater than two. Thus, degree-2 Steiner nodes are not included here.

duced to one. If we diagnose the mechanism on how buffer insertion improves interconnect timing performance, it can be broken down into two parts: (1) regenerating signal level to increase driving capability for long wires and (2) shielding capacitive load at non-critical branches from the timing critical path. In a Steiner tree, buffers that play the first role are along a node-to-node path while buffers for the second purpose are normally close to a branching Steiner node. The majority of buffer insertion algorithms such as van Ginneken's method are dynamic programming based and have been proved to be very effective for both purposes. However, optimal buffer solutions along a node-to-node path can be found analytically if the driving resistance for this path is known [24, 25]. This fact suggests that we may have a hybrid approach in which buffers along paths are placed according to the closed form solutions while the buffers at branching nodes are still solved by dynamic programming, i.e., analytical buffered path solutions replace both the wire segmenting [24] and candidate solution generations at segmenting points in the bottom-up dynamic programming framework. The only problem of this approach is that the driving resistance of a path to be processed is not known in this bottom-up procedure. This can be solved by sampling a set of anticipated upstream resistance values and generating candidate buffering solutions for each anticipated value. Different sampling rate may result in different solution quality and runtime tradeoffs. Computing candidate buffered paths analytically is faster than dynamic programming, because the complexity of a dynamic programming approach has a quadratic dependence on the segmenting size while analytical approach has only linear dependence on the upstream resistance sampling size.

# 3. Steiner Node Adjustment

For a Steiner node, we find a few nearby tiles with the least congestion. In each of these tiles, we consider an alternative Steiner node there. Therefore, the candidate solutions from child branches are propagated to not only the original Steiner node but also these

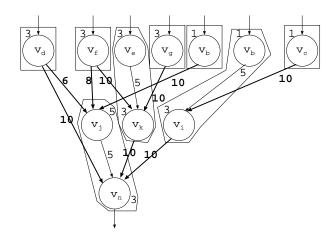

Fig. 6. (a) Candidate solutions are generated from  $v_2$  and  $v_3$  and propagated to every shaded tile for  $v_4$ . (b) Solutions from  $v_1$  and every shaded tile for  $v_4$  are propagated to  $v_5$  and its alternative nodes. (c) Solutions from  $v_5$  and its alternative nodes are propagated to the source and the thin solid lines indicate an alternative tree that may result from this process.

alternative Steiner nodes. For a node v, we define expanded node set as its alternative nodes as well as the node itself and denote this set as P(v). The selection of alternative nodes in P(v) can be controlled by the placement cost and wiring cost of the tiles<sup>4</sup> or for different objectives of Steiner node adjustment, other selection schemes may be applied. After candidate solutions from child branches are merged at the original Steiner node and each of the alternative Steiner nodes, the merged solutions are propagated further towards the source. This process is illustrated in Figure 6 where the tiles for the expanded node set are shaded. The alternative Steiner nodes enable alternative tree topologies and only the topology that is part of the best solution at the root will be finally selected. Therefore, this tree adjustment is a dynamic selection.

Usually, we restrain the alternative Steiner nodes to be close to the original Steiner node so that the perturbation to the original timing driven Steiner tree is limited. We define

<sup>&</sup>lt;sup>4</sup>See Section D for the P(v) selection details adopted in our experiment.

the adjustment flexibility which represent what the maximum distance of the alternative Steiner nodes can be away from the original Steiner node. For example, in Figure 6, all alternative nodes are enclosed in  $3 \times 3$  tiles and so we refer it as the  $3 \times 3$  tiles adjustment flexibility. By this definition, we can have a larger flexibility for the selection of expanded node set if, for instance, we adopt the  $5 \times 5$  tiles adjustment flexibility in our program. A larger adjustment flexibility would lead to a higher possibility for the original Steiner node to migrate outside of the congested area.

The main difference between our proposed technique and the work of [6] is that a regular array of tiles are considered for alternative Steiner node in [6] while our selection on alternative Steiner nodes is according to the congestion for nearby tiles. This is based on our observation that only the nearby tiles with relatively low buffer placement or routing congestion cost worth considering to be the alternative Steiner node. Moreover, due to the irregularity and flexibility of expanded node set in our algorithm, we have more choices and can pick alternative Steiner nodes other than the immediate neighbor nodes for better congestion reduction and higher efficiency. On the contrary, since [6] features a regular array of tiles, a larger flexibility for alternative Steiner nodes is desired, the runtime would become unbearable. This can be shown by our experiments in Section D.

## 4. Minimum Cost Buffered Path

Our work distinguishes from [6] significantly on the candidate solution propagation between two nodes. In [6], a length based buffer insertion is integrated with the minimum congestion cost path search, so the process is not timing-driven. However, our algorithm has the required arrival time information in an intermediate solution during the bottom-up propagation and pruning process, and hence our work is capable of handling not only the congestion reduction but also the timing optimization. In order to achieve these two objectives, we separate the buffer insertion for timing from the minimum congestion cost path

Fig. 7. Buffer positions along a path.

search. For a path of length l with driver resistance  $R_d$  at one end and a load capacitance  $C_L$  on the other end, the number of buffers k that minimizes the path delay is obtained in [24] as:

$$k = \left| -\frac{1}{2} + \frac{1}{2} \sqrt{1 + \frac{2(rcl - r(C_b - C_L) - c(R_b - R_d))^2}{rc(R_b C_b + t_b)}} \right|$$

The k buffers separate the path into k + 1 segments of length  $l_0$ ,  $l_1$ , ... $l_k$  as illustrated in Figure 7. According to [24], The length of each segment can be obtained through:

$$l_{0} = \frac{1}{k+1} \left( l + \frac{k(R_{b} - R_{d})}{r} + \frac{C_{L} - C_{b}}{c} \right)$$

$$l_{1} = \dots = l_{k-1} = \frac{1}{k+1} \left( l - \frac{R_{b} - R_{d}}{r} + \frac{C_{L} - C_{b}}{c} \right)$$

$$l_{k} = \frac{1}{k+1} \left( l - \frac{R_{b} - R_{d}}{r} - \frac{k(C_{L} - C_{b})}{c} \right)$$

(3.1)

Then, we explain our buffered path routing technique by an example. For the thickened path in Figure 8(a), if we know the driving resistance at  $v_1$  and load capacitance at  $v_4$ , we may obtain the optimal buffer positions at  $v_2$  and  $v_3$ . However, if we connect  $v_1$  and  $v_4$  in a two-dimensional plane, there are many alternative paths between them and the optimal buffer locations form rows along diagonal directions. The tiles for the optimal buffer locations are shaded in Figure 8(a). Therefore, if we connect  $v_1$  and  $v_4$  with any monotone path and insert a buffer whenever this path passes through a shaded tile, the resulting buffered path should have the same minimum delay. The thin solid curve in Figure 8(a) is an example of an alternative minimum delay buffered path. Certainly, different buffer paths may have different congestion cost. Then the minimum congestion cost buffered path can be found by running the Dijkstra's algorithm on the tile graph which is demonstrated

Fig. 8. Find low congestion path with known buffer positions indicated by the shaded tiles.

in Figure 8(b). In Figure 8(b), each solid edge corresponds to a tile boundary and its edge cost is the corresponding wiring congestion cost (=square of its boundary density). There are two types of nodes, the empty circle nodes that have zero cost and filled circle nodes that have cost equal to the placement congestion cost in corresponding tile. In conclusion, the shortest path obtained in this way produces a buffered path with both good timing and low congestion cost.

An issue need to be handled by this approach is that the upstream resistance  $R_d$  is unknown in the bottom-up solution propagation process. However, we are aware that the lower bound on the upstream resistance is  $\underline{R} = \min(R_d, R_b)$  and the upper bound  $\overline{R}$  is  $\max(R_d, R_b)$  plus the upstream wire resistance<sup>5</sup>. Then, we can sample a few values between  $\underline{R}$  and  $\overline{R}$ , and find the minimum cost buffered path for each value. Since the timing result is not sensitive to the upstream resistance, normally the sampling size is very limited.

# 5. Overall Algorithm

In our algorithm, each intermediate buffer solution is characterized by a 4-tuple s(v, c, q, w) in which v is the root of the subtree, c is the downstream load capacitance seen from v, q

<sup>&</sup>lt;sup>5</sup>The maximum upstream wire resistance can be derived from the length of maximum buffer-to-buffer interval. This is also mentioned in [23].

```

Procedure: FindCandidates(v)

Input: Current node v to be processed

Output: Candidate solution set S(P(v))

Global: Steiner tree T(V, E)

Tile graph G(V_G, E_G)

1. If v is a sink

S(v) \leftarrow \{(v, c(v), q(v), 0)\}

S(P(v)) \leftarrow \{S(v)\}

Return S(P(v))

2. v_l \leftarrow \text{left child of } v

S(P(v_l)) \leftarrow FindCandidates(v_l)

3. S_l(P(v)) \leftarrow Propagate(S(P(v_l)), P(v))

4. If v has only one child

Return S_l(P(v))

5. v_r \leftarrow \text{right child of } v

S(P(v_r)) \leftarrow FindCandidates(v_r)

6. S_r(P(v)) \leftarrow Propagate(S(P(v_r)), P(v))

7. S(P(v)) \leftarrow Merge(S_l(P(v)), S_r(P(v)))

8. Prune(S(P(v)))

9. Return S(P(v))

```

Fig. 9. Core algorithm.

is the required arrival time at v and w is the accumulated congestion cost. A solution  $s_i(v, c_i, q_i, w_i)$  is said to be dominated by another solution  $s_j(v, c_j, q_j, w_j)$ , if  $c_i \geq c_j, q_i \leq q_j$  and  $w_i \geq w_j$ . A set of buffer solutions S(v) at node v is a non-dominating set when there is no solution in S(v) dominated by another solution in S(v).

The complete algorithm descriptions are given in Figures 9 and 10 where the basic operations are defined as follows.

•  $Merge(S_l(v), S_r(v))$ : merge solution set from left child of v to the solution set from the right child of v to obtain a merged solution set S(v). For a solution  $s_{i,l}(v, c_{i,l}, q_{i,l}, w_{i,l})$  from the left child and a solution  $s_{j,r}(v, c_{j,r}, q_{j,r}, w_{j,r})$ , they are merged to  $s_k(v, c_k = c_{i,l} + c_{j,r}, q_k = \min(q_{i,l}, q_{j,r}), w_k = w_{i,l} + w_{j,r})$ .

```

Procedure: Propagate(S(P(v_i)), P(v_i))

Input: Candidate solutions at P(v_i)

Expanded node set P(v_j)

Output: Candidate solution set S(P(v_i))

Global: Tile graph G(V_G, E_G)

1. S(P(v_i)) \leftarrow \emptyset

2. For each node v_l \in P(v_j)

S(v_l) \leftarrow \emptyset

For each node v_k \in P(v_i)

For each anticipated upstream resistance R_u at v_l

(\mathcal{L}, c, q) \leftarrow FindBufferPositions(R_u, v_l, v_k)

w \leftarrow FindMinCostPath(v_l, v_k, G, \mathcal{L})

S(v_l) \leftarrow S(v_l) \cup \{s(v_l, c, q, w)\}

Prune(S(v_l))

S(P(v_i)) \leftarrow S(P(v_i)) \cup S(v_l)

8. Return S(P(v_i))

```

Fig. 10. Subroutine of propagating candidate solutions from one node set to another.

- Prune(S(v)): remove any solution  $s_i \in S(v)$  that is dominated by another solution  $s_i \in S(v)$ .

- $FindBufferPositions(R_u, v_u, v_d)$ : apply equations of (3.1) to find the set of buffer positions  $\mathcal{L}$  for the minimum delay from node  $v_u$  to  $v_d$  assuming driving resistance  $R_u$  at  $v_u$ . The required arrival time q and downstream capacitance c at  $v_u$  are also returned.

- $FindMinCostPath(v_u, v_d, G, \mathcal{L})$ : apply Dijkstra's algorithm to find the minimum cost path connecting  $v_u$  and  $v_d$  on tile graph  $G(V_G, E_G)$ . On tile graph G, the cost of each node  $g \in V_G$  is  $d^2(g)$  if  $g \in \mathcal{L}$ ; otherwise zero. The cost of an edge in G corresponding to boundary between tiles  $g_i$  and  $g_j$  is  $d^2(g_i, g_j)$ . Return the path cost finally. (An example is shown in Section III.D.)

FindCandidates(v) (Figure 9) is a recursive procedure which is similar to van Gin-

neken's algorithm such that at each node, we propagate the solutions from its children, merge and prune the solutions. However, the procedure  $Propagate(S(P(v_i)), P(v_j))$  (Figure 10) for solution propagation adopts our analytical equations and shortest path algorithm described in Section III.D, which accelerates our algorithm when compare with the van Ginneken's dynamic programming approaches. When our algorithm terminates, we obtain a set of solutions with different timing and congestion cost tradeoffs at the root.

## D. Experimental Results

All experiments are performed on a Sun Ultra Sparc 450 machine running in 400 MHz. Our experiments adopt the following parameters:  $r=0.184\Omega/\mu m$ ,  $c=0.124fF/\mu m$ ,  $R_b=246.3\Omega$ ,  $C_b=7.2fF$  and  $t_b=27.46ps$ . The sampling size of upstream resistance is set to 3.

We implement our algorithm "Place and Route Aware Buffered Steiner Tree Construction" (PRAB) and the algorithm "Porosity Aware Buffered Steiner Tree Construction" in [6]<sup>6</sup> (namely POROSITY in this paper) with C++ and compare them based on a set of industrial nets which is also used in [15] and [22]. In the benchmark nets, the driver resistance ranges from  $271.8\Omega$  to  $2557.5\Omega$  while the loading capacitance ranges from 2.9fF to 55.6fF.

For each net, after we construct a tile graph, we randomly produce a set of buffer blockages and then calculate the placement density for each tile which range from 0 to 1. The boundary density for each tile boundary is also generated randomly ranging from 0 to 0.25 so that the importance of buffer placement cost and wiring congestion cost balance each other in the buffered Steiner trees.

<sup>&</sup>lt;sup>6</sup>We compare our work to the algorithm in [6] since it is the latest published work with almost the same problem formulation and similar objectives.

In order to ensure a fair comparison, the buffered Steiner tree generation for both implementations follows the three-stage scheme mentioned in Section C-1 and therefore we can focus on the comparison between the congestion-aware tree adjustment step for both algorithms. After the tree adjustment in stage 2, our PRAB algorithm generates a set of solutions with different timing and congestion cost tradeoff but POROSITY produces a single solution which only considers the minimization of estimated congestion cost. Therefore, before running the van Ginneken style buffer insertion, we only pick the one with least estimated cost in our solution set for the comparison with POROSITY.

## 1. Results for Real Multi-Sink Nets

| Table  | H | Inform    | nation  | of all | testcases |

|--------|---|-----------|---------|--------|-----------|

| 141715 |   | 1111(7111 | iautoni | OI all | residases |

|          |      | graph size         | Stage 1  |

|----------|------|--------------------|----------|

| net      | sink | $(row \times col)$ | req/ps   |

| mcu0s5   | 18   | $32 \times 34$     | 5949.31  |

| mcu1s9   | 19   | $38 \times 29$     | 5936.46  |

| n1071    | 17   | $23 \times 37$     | 1723.04  |

| n18905   | 29   | $67 \times 53$     | -1062.66 |

| n313     | 19   | $36 \times 45$     | 646.43   |

| n7866    | 32   | $112 \times 45$    | -635.27  |

| n8692    | 21   | $79 \times 27$     | 284.87   |

| n8702    | 43   | $106 \times 68$    | -2031.09 |

| n8730    | 20   | $55 \times 33$     | -538.76  |

| pointer3 | 20   | $64 \times 53$     | -613.75  |

In the first experiment, we pick the expanded node set from the  $3 \times 3$  neighbor tiles of each Steiner node  $-3 \times 3$  tiles adjustment flexibility. Each expanded node set consists of three tiles: the tile  $g_1$  containing the original Steiner node, the tile  $g_2$  with the smallest buffer placement cost  $p(g_2)$ , and the tile  $g_3$  with the smallest wiring cost average, which is defined as  $\frac{\sum_{g' \in N(g_3)} p(g_3,g')}{|N(g_3)|}$  where  $N(g) = \{g' | (g,g') \in E_G\}$ . To achieve the same Steiner

node adjustment flexibility, we implement POROSITY with the "plate size" to be  $3 \times 3$ . Table II shows the information of all testcases. For each net, the second column shows the number of sinks. "graph size" displays the number of columns and rows in the tile graph which encloses the routing region of the net. "Stage 1 req" represents the required arrival time at source node which is propagated from all sinks along the initial timing driven Steiner tree without buffer insertion (just after Stage 1). Table III shows the comparison between the POROSITY algorithm and our PRAB algorithm. Columns 2-7 represents the results of POROSITY [6] while columns 8-13 shows our results. "req" represents the required arrival time at source node for the buffered Steiner tree generated by all three stages for both algorithms. Then, "imp" means the timing improvement by each three-stage implementation when comparing to the first-stage Steiner tree. (Note that both algorithms generate a negative improvement for the net mcu0s5 since in the process of congestion mitigation, the total wire-length increases and in turn decreases the required arrival time at source node.) "cost" shows the total congestion cost that is a sum of wiring cost "w.cost" and buffer placement cost "b.cost", which are induced by the final buffered Steiner tree on the tile graph. Although we perform all three stages for both implementations, only the CPU time for second stage is shown for proper comparisons.

From Table III, we observe the following:

- Our algorithm for tree adjustment outperforms POROSITY [6] in the sense of both timing improvement (7%) and congestion cost evaluation(7%). Particularly, we are better than POROSITY by 15% in buffer placement cost. This justifies our claim that our tree adjustment algorithm not only operates in a timing-driven manner but also simultaneously handles the wiring and placement congestion while [6] does not.

- PRAB runs with about 15 times speed-up. The main reason for the efficiency is that

we selectively pick the expanded node set according to the congestion nearby the

Table III. Comparison between POROSITY and PRAB under  $3 \times 3$  tiles adjustment flexibility.

|          |         |         | Our algorithm PRAB |        |        |        |         |         |       |        |        |       |

|----------|---------|---------|--------------------|--------|--------|--------|---------|---------|-------|--------|--------|-------|

| net      | req/ps  | imp/ps  | cost               | w.cost | b.cost | CPU/s  | req/ps  | imp/ps  | cost  | w.cost | b.cost | CPU/s |

| mcu0s5   | 5919.85 | -29.46  | 3.71               | 1.99   | 1.72   | 6.23   | 5922.10 | -27.21  | 4.07  | 1.99   | 2.08   | 1.88  |

| mcu1s9   | 6047.52 | 111.06  | 4.13               | 1.50   | 2.63   | 9.89   | 6082.39 | 145.93  | 2.67  | 1.10   | 1.57   | 0.65  |

| n1071    | 1787.23 | 64.19   | 3.58               | 1.08   | 2.50   | 7.64   | 1792.37 | 69.33   | 3.08  | 1.45   | 1.63   | 1.93  |

| n18905   | -869.89 | 192.77  | 5.06               | 2.88   | 2.19   | 23.83  | -791.84 | 270.82  | 4.69  | 3.07   | 1.63   | 4.69  |

| n313     | 870.89  | 224.46  | 2.78               | 1.90   | 0.88   | 6.02   | 869.68  | 223.25  | 2.66  | 1.77   | 0.90   | 0.65  |

| n7866    | -20.83  | 614.44  | 3.19               | 2.24   | 0.95   | 141.67 | 32.30   | 667.56  | 2.69  | 2.02   | 0.68   | 8.06  |

| n8692    | 639.72  | 354.85  | 3.39               | 1.81   | 1.59   | 18.27  | 660.48  | 375.61  | 4.36  | 1.74   | 2.62   | 1.00  |

| n8702    | 347.54  | 2378.63 | 7.10               | 2.45   | 4.65   | 261.26 | 386.53  | 2417.62 | 5.64  | 2.63   | 3.01   | 11.89 |

| n8730    | 99.45   | 638.21  | 8.29               | 1.61   | 6.68   | 11.42  | 169.78  | 708.54  | 8.02  | 1.53   | 6.49   | 1.12  |

| pointer3 | -328.44 | 285.30  | 3.56               | 1.99   | 1.57   | 41.36  | -289.58 | 324.16  | 2.77  | 1.77   | 1.00   | 3.46  |

| sum      |         | 4834.45 | 44.80              | 19.46  | 25.34  | 527.59 |         | 5175.61 | 40.65 | 19.06  | 21.59  | 35.33 |

| ratio    |         | 1       | 1                  | 1      | 1      | 1      |         | 1.07    | 0.91  | 0.98   | 0.85   | 0.067 |

node containing the original Steiner node; And, buffer location is determined by an analytical formula so that node-to-node routing becomes very fast.

# 2. Results when More Choices for Expanded Node Set

The second experiment is intended to show that our algorithm is capable in handling the situation when a greater flexibility is needed for the Steiner node adjustment. As stated in Section C-3, the set of alternative Steiner nodes is defined by the expanded node set. In Table IV, we have a  $5 \times 5$  tiles adjustment flexibility while keeping the size of expanded node set to be 3, which is the same as the first experiment. Similarly, POROSITY is implemented with each plate consisting of  $5 \times 5$  tiles.