## A METHODOLOGY FOR MEMORY CHIP STRESS LEVELS PREDICTION

A Thesis

by

### KARTIK SHARMA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

August 2005

Major Subject: Mechanical Engineering

### A METHODOLOGY FOR MEMORY CHIP STRESS LEVELS PREDICTION

A Thesis

by

### KARTIK SHARMA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved by:

Chair of Committee, Sheng Jen (Tony) Hsieh Committee Members, Steve Suh Andrew K. Chan Head of Department, Dennis L. O'Neal

August 2005

Major Subject: Mechanical Engineering

#### ABSTRACT

A Methodology for Memory Chip Stress Levels Prediction. (August 2005) Kartik Sharma, B.Tech, B.I.E.T. Institute, Jhansi, India Chair of Advisory Committee: Dr. Sheng-Jen (Tony) Hsieh

The reliability of an electronic component plays an important role in proper functioning of the electronic devices. The manufacturer tests electronic components before they are used by end users. Still at times electronic devices fail due to undue stresses existing inside the microelectronic components such as memory chips, microcontrollers, resistors etc. The stresses can be caused by variation in the operating voltage, variation in the usage frequency of the particular chip and other factors. This variation leads to variation in chip temperature, which can be made evident from thermal profiles of these chips.

In this thesis, effort was made to study two different kind of stress existing in the electronic board, namely signal stress based on variation in duty cycle/frequency of chip usage and the voltage stress. Memory chips were tested using these stresses causing change in heating rates, which were captured by infrared camera. This data was then extracted and plotted to obtain different curves for the heating rate. The same experiment was done time and again for a large number of chips to get heating rate data.

This data consisting of average heating rate for large number of chips was used to build Neural Network model (NN). Back Propagation algorithm was used for modeling because of its advantage of converging to solution faster compared to other algorithms. To develop a prediction model, data sets were divided into two-third and one-third parts. This two-thirds of the data was used to build the prediction model and the remaining one third was used to evaluate the model. The designed model would predict the stress levels existing in the chips based on the heating rates of the chips. Results obtained suggested

- 1. There is difference in heating rate for chips stressed at different stress levels.

- 2. Accuracy of the model to predict the stress is high (greater than 90 %).

- 3. Model is robust enough that is it can yield efficient results even if there is presence of noise in the data.

- 4. Generic methodology can be proposed based on the experiments.

This work is progress in the direction of making a predictive model for a complete electronic device, which can predict the stress level existing on any component in the device and will provide an opportunity to either protect the data or removal of the defected components timely before it even fails.

#### ACKNOWLEDGEMENTS

I would like to express my sincere thanks and appreciation to my adviser Dr. Sheng-Jen (Tony) Hsieh, for his guidance, patience and all kind of help through out the completion of my thesis and for showing confidence in me. I would like to take this opportunity to thank Dr. Steve Suh from the Mechanical Engineering Department and Dr. Andrew. K. Chan from the Electrical Engineering Department for serving on my thesis committee.

At this point I would also like to thank Dr. Ali Beskok of the Mechanical Engineering Department, without whom it would have been impossible to start this work. To Anthony Li and Daniel Moyer, I can simply say Thank You; because words cannot explain the efforts that you both made in order to help me finish my work.

Regards to my family and the folks back home who enlighten me with their support every time I need it.

## TABLE OF CONTENTS

| ABSTRACT.            |                                                                                                                                                                                                  | . iii                |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| ACKNOWLEDGEMENTS v   |                                                                                                                                                                                                  |                      |  |

| TABLE OF C           | DNTENTS                                                                                                                                                                                          | vi                   |  |

| LIST OF FIG          | IRES                                                                                                                                                                                             | ix                   |  |

| LIST OF TAE          | LES                                                                                                                                                                                              | x                    |  |

| NOMENCLATURE x       |                                                                                                                                                                                                  |                      |  |

| CODES                |                                                                                                                                                                                                  | xiii                 |  |

| CHAPTER              |                                                                                                                                                                                                  |                      |  |

| I INTRODUCTION       |                                                                                                                                                                                                  |                      |  |

|                      | <ul> <li>1.1 Motive</li> <li>1.2 Nature of Problem</li> <li>1.3 Problem Statement</li> <li>1.4 Scope and Objective of Research</li> <li>1.5 Format of Research Work</li> </ul>                   | 2<br>2<br>3          |  |

| II LITERATURE REVIEW |                                                                                                                                                                                                  | 5                    |  |

|                      | <ul> <li>2.1 Introduction</li> <li>2.2 Electronic Reliability</li> <li>2.3 Current Approaches in Testing Memory Chips</li> <li>2.4 Prediction of Stress Failure in Electronics and in</li> </ul> | 5<br>7               |  |

|                      | 2.5 Memory chips<br>2.5 Stresses on Memory Chips                                                                                                                                                 |                      |  |

| III                  | DESIGN OF EXPERIMENTS                                                                                                                                                                            | 17                   |  |

|                      | <ul> <li>3.1 Introduction</li></ul>                                                                                                                                                              | 17                   |  |

| IV                   | EXPERIMENTS                                                                                                                                                                                      | 24                   |  |

|                      | <ul> <li>4.1 Introduction</li></ul>                                                                                                                                                              | 24<br>27<br>28<br>30 |  |

| V    | RESU   | JLTS                                           | 35  |

|------|--------|------------------------------------------------|-----|

|      | 5.1    | Introduction                                   | 35  |

|      | 5.2    | Results from Signal Stress-I                   | 36  |

|      | 5.3    | Model Development Approach for Signal Stress-I | 38  |

|      | 5.4    | Matlab results for Signal Stress-I             |     |

|      | 5.5    | Inferences for Signal Stress-I                 |     |

|      | 5.6    | Results from Signal Stress-II                  | 44  |

|      | 5.7    | Matlab Results for Signal Stress-II            | 46  |

|      | 5.8    | Inferences for Signal Stress-II                | 47  |

|      | 5.9    | Results from Voltage Stress                    | 50  |

|      | 5.10   | Model Development Approach for Voltage Stress  | 52  |

|      | 5.11   | Matlab Results for Voltage Stress              | 52  |

|      | 5.12   | Inferences for Voltage Stress                  | 54  |

| VI   | MOD    | EL TOLERANCE                                   | 56  |

|      | 6.1    | Introduction                                   | 56  |

|      | 6.2    | Generating Data for Signal Stress-I            | 56  |

|      | 6.3    | Increase in Standard Deviation and Calculation |     |

|      |        | of Overlap Area                                | 58  |

|      | 6.4    | Noise Tolerance Results for Signal Stress-I    |     |

|      | 6.5    | Inferences for Signal Stress –I                | 65  |

|      | 6.6    | Generating Data for Signal Stress-II           | 66  |

|      | 6.7    | Noise Tolerance Results for Signal Stress-II   |     |

|      | 6.8    | Inferences for Signal Stress-II                |     |

|      | 6.9    | Generating Data for Voltage Stress             | 68  |

|      | 6.10   | Noise Tolerance Results for Voltage Stress     | 69  |

|      | 6.11   | Inferences for Voltage Stress                  | 71  |

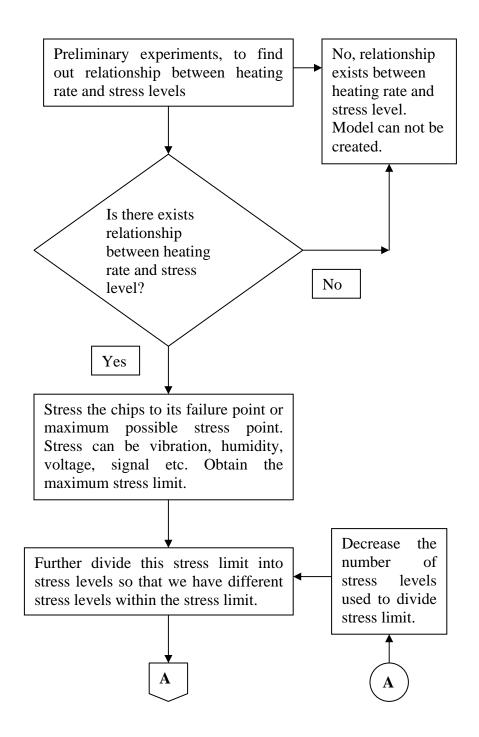

| VII  | GENI   | ERIC METHODOLOGY FOR STRESSING                 | 72  |

|      | 7.1 In | troduction                                     | 72  |

|      | 7.7 G  | eneric Methodology for Stressing               | 72  |

| VIII | CON    | CLUSION AND FUTURE WORK                        | 75  |

|      | 8.1    | Introduction                                   | 75  |

|      | 8.2    | Conclusion from Signal Stressing               | 75  |

|      | 8.3    | Conclusion from Voltage Stressing              | 77  |

|      | 8.4    | Future Work                                    | 78  |

|      | 0.1    |                                                | , 0 |

| REFERENCES | 79 |

|------------|----|

| APPENDIX A | 85 |

| APPENDIX B | 91 |

| VITA       | 96 |

## LIST OF FIGURES

## FIGURE

| 3.1 | Layout of the board and SRAM used for experiments                         | 18 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Functional block diagram for SRAM                                         | 19 |

| 3.3 | Timing waveform for the read cycle                                        | 20 |

| 3.4 | Timing waveform for write cycle                                           | 21 |

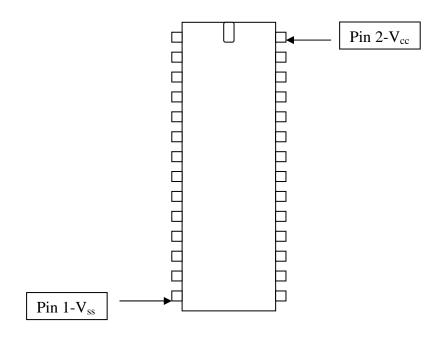

| 4.1 | Pins that were stressed $V_{cc}\left(+\right)$ and $V_{ss}\left(-\right)$ | 26 |

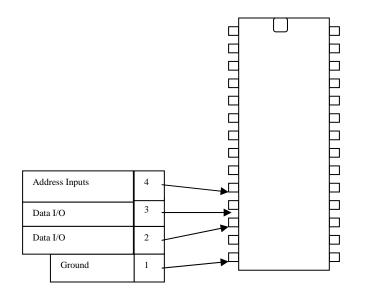

| 4.2 | SRAM and the pins stressed                                                | 32 |

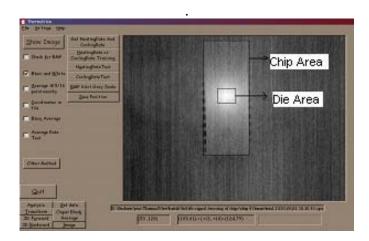

| 5.1 | Chip area and the die area using Thermal View                             | 36 |

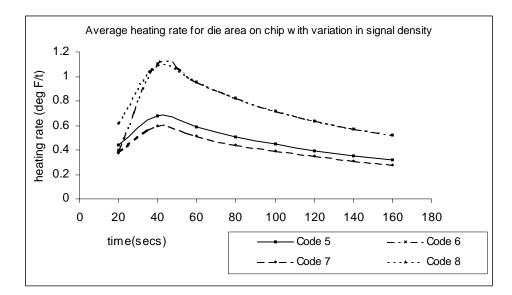

| 5.2 | Variation in heating rate for die area on chips for signal stress-I       | 37 |

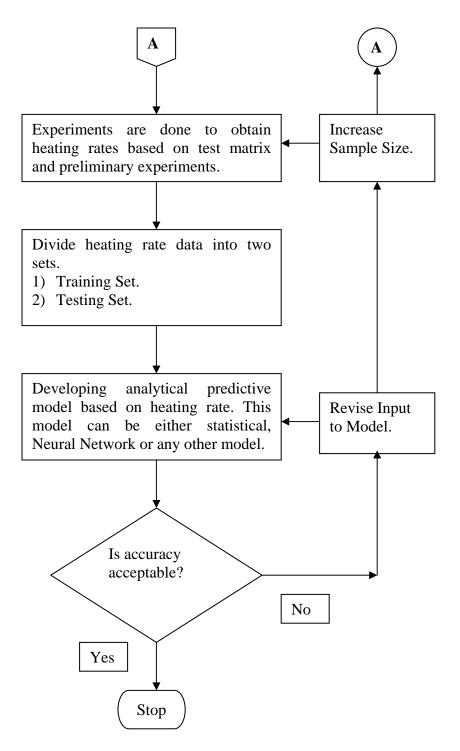

| 5.3 | 3-2-1 topology of Neural Network prediction model                         | 38 |

| 5.4 | Variation in heating rate for die area on chips for signal stress-II      | 45 |

| 5.5 | Die area and chip area while imaging                                      | 51 |

| 5.6 | Average heating rate trend for different chips for same stress level      | 51 |

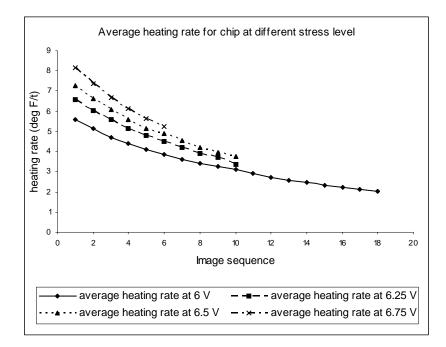

| 5.7 | Average heating rate trend for different stresses                         | 52 |

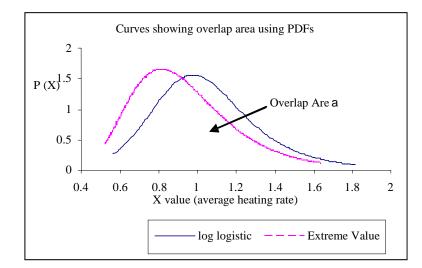

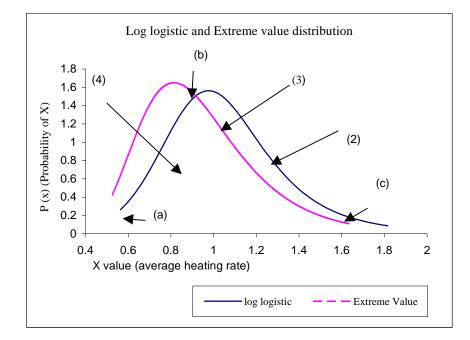

| 6.1 | Overlap area of two distributions                                         | 58 |

| 6.2 | Probability density distributions with 95% confidence interval            | 59 |

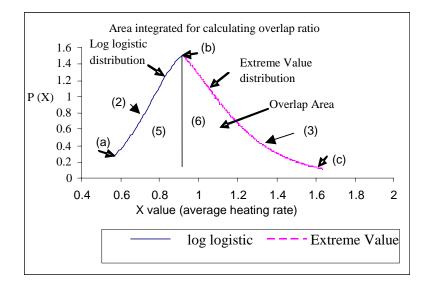

| 6.3 | Area needed to be integrated for overlap ratio                            | 62 |

| 7.1 | Generic methodology for building a stress prediction model                | 73 |

#### LIST OF TABLES

**TABLE**

#### 4.1 Test matrix for the experiment based on the different tests 4.2 4.3 Test matrix for the experiment based on the different stress 5.1 5.2 Various learning functions for back propagation method ...... 41 5.3 Matlab results obtained using different training functions for die area on chip and using signal stress –I..... 42 5.4 Matlab results obtained using different training functions for chip area and using signal stress –I ...... 43 5.5 5.6 Matlab results obtained using network 3-2-1 and two different methods of training the data ...... 47 5.7 5.8 5.9 5.10 6.1

# TABLE

| 6.2 | Average error rate for SD-I die area                      | 64 |

|-----|-----------------------------------------------------------|----|

| 6.3 | Number of iterations needed for SD-I die area             | 65 |

| 6.4 | Overlap percentage between classes (input-I and input-II) | 66 |

| 6.5 | Average error rate for signal density-II die area         | 67 |

| 6.6 | Iterations needed for signal density-II die area          | 67 |

| 6.7 | Overlap percentage between classes (input-I and input-II) | 69 |

| 6.8 | Deviation results from voltage stress chip area           | 70 |

| 6.9 | Number of iterations for voltage stress chip area         | 71 |

## NOMENCLATURE

### SYMBOLS DEFINITION

| amb               | Ambient                                  |

|-------------------|------------------------------------------|

| AH <sub>i</sub>   | Average heating rate                     |

| V <sub>ss</sub>   | Ground pin on SRAM                       |

| $H_1, H_{2,,H_N}$ | Heating rate                             |

| MSE               | Mean square error                        |

| a, b              | Parameter for extreme value distribution |

| γ, β, α           | Parameter for log logistic distribution  |

| RMS error         | Root mean square error                   |

| Т                 | Time (seconds)                           |

| V                 | Voltage                                  |

| V <sub>cc</sub>   | Voltage input pin on SRAM                |

# CODES

| 1 | 1206.asm                |

|---|-------------------------|

| 2 | 1206ram2.asm            |

| 3 | 1206ram 3.asm           |

| 4 | 1.asm                   |

| 5 | IncrementsRAM.asm       |

| 6 | IncrementsRAMwdelay.asm |

| 7 | Zerosnfswesc.asm        |

| 8 | Zerosnfswescndelay.asm. |

|   |                         |

| SET CODE | PROGRAM NAME          |

|----------|-----------------------|

| 9        | SRAM more -FLASH same |

| 10       | SRAM 200k -FLASH same |

| 11       | SRAM same -FLASH same |

| 12       | SRAM same -FLASH 150k |

# CHAPTER I INTRODUCTION

#### 1.1 Motive

Chips are widely used in all kind of electronic components, but they are highly prone to failure. Chip in an electronic device may fail due to voltage overstress or signal overstress existing in the chip. Voltage stress may cause gate oxide breakdown [1], electro migration or breaking of bonds at high temperature. Electrostatic discharge and electrical overstress (EOS) caused due to voltage overshoot are blamed for up to 60% of field failures [2]. Due to the unavailability of accurate circuit level simulation tool lots of work had been done on simulation models [3]. Other detection technologies include Wunsch- Bell Paradigm [4], non-destructive solutions using percolation and FEA tools.

Similarly, signal stress caused due to variation in duty cycle and chip usage may lead to unnecessary heating in the chip, which can lead to the failure of processor chip and other high frequency electronic devices. Jung et al. [5] mentioned duty cycle correction scheme. Okuda et al. [6] gave the different method for duty cycle error correction, while Chen et al. [7] described the effect of dynamic stress testing on memory application.

Currently most of the methodologies for chip testing study the defective chip and try to narrow down on possible causes, which must be avoided or try to analyze the defects using simulation models, rather then collecting real time data, while the chip is in operation. Nowadays demand is for methodology based on the concurrent technology that can give real time analysis of the chip condition and can predict the failure before time based on the stress level existing in the chip.

This thesis follows the style and format of IEEE Journal of Solid-State Circuits.

#### **1.2** Nature of the Problem

When the end user uses the electronic components, at times they are subjected to extreme conditions, which might make them to work outside their design limits. In this research two of those extreme conditions were studied: signal stress and voltage stress. Here in this thesis work, we define signal stress due to variation in signals sent in/ out of the particular chip.

In addition, voltage stress refers to the increase in the voltage at address and data pins on chips. Device components at times have to work at maximum capacity, resulting in increased heating rate of the device. The most familiar example is the cooling fan use to cool off over the microcontroller in a PC. The stress resulting on the chip due to the variation in the signals is what we call as the signal stress and can lead to component failure either due to excessive heating or due to internal stuck in faults in the registers.

The voltage stress is caused when the component has to work at some higher voltage than the usual. This result in various kinds of failures in the chip most common is the gate failure at the pins on the chip. Failure can be slow or avalanche depending on the stress level. Voltage stress results in the increase of the temperature of the chip or heating rate and chip may fail due to the breakdown at very high temperature.

For both of these stresses we saw that the heating rate plays a crucial role and increases with increase in both signal stress and voltage stress. As a result heating rate was taken one of the parameters which if kept under control or if there are some methods to detect the variation in the heating rate and then we can avoid chip failure.

#### **1.3 Problem Statement**

In this research work, the failure of the chip was identified due to the increase in signal stress caused by the variation in duty cycle and/or frequency of memory chip usage and voltage stress caused due to voltage overstressing on pins. It is assumed that heat will be generated over time as chips are subjected to stresses.

In this research work, heating rate was considered as a primary parameter for developing an analytical model using this parameter to predict the stress level existing in the chips. Neural Network is proposed as a modeling technique for this research work.

#### **1.4** Scope and Objective of Research

The scope of research work is to build a predictive model and methodology which can avoid the failure of the chips under actual conditions by predicting the stress levels existing in the electronic components or board as a whole.

The research objectives can be summarized as follows:

- To understand the relationship between heating rate and stress levels.

- To build a Neural Network model for failure prediction based on the voltage stress existing in the component using the relationship between stress and heat rates of the electronic components while in operation.

- To build similar kind of Neural Network model for failure prediction based on signal stress existing in the component using the relationship between heating rates given by chips and corresponding stress level existing in the chips.

- To test the noise tolerance of the model developed using statistical tools.

- To proposed a generic methodology for electronic stress level prediction.

### **1.5** Format of Research Work

The progress of research work, starting from the idea of studying the thermal profile and then carrying out experiments and modeling to build the prediction model is mentioned in the following chapters.

Chapter II in the research work consists of the literature review on the possible stresses existing in the chip, failure caused due to stresses, current methodologies and prediction techniques.

Chapter III talks about the various aspects of board and the chip and design of experiment.

Chapter IV describes the way experiments were conducted for all the stresses to gather the heating rate information.

Chapter V gives the results obtained from experiments and inferences obtained on the basis of results.

In chapter VI the model was tested for its robustness by comparing the deviation in data to its effect on the model results.

Chapter VII consists of the generic methodology that can be for creating a prediction model based on the stress existing in chips.

Finally last chapter VIII consists of the conclusion drawn and the future work that can be done on similar lines of research.

The entire procedure of using thermal profiles and using Neural Network modeling technique is innovative and can be successful in predicting the chip failures. The conclusion is drawn in the end based on the results from the neural model and its noise tolerance efficiency.

## CHAPTER II LITERATURE REVIEW

#### 2.1 Introduction

The research work is related to stress level prediction which is a part of field of reliability and testing. This chapter starts with brief history on chip reliability and testing. First few page deals with the reliability theory, followed by sections which talk about current techniques and prediction methodologies. The last section in literature review talks about stresses specifically those that were our main concern in this research work.

Chip reliability and testing is vast field of research in electronics industry today. Every year millions of dollars are spent to find out the answers to various reliability issues and for the analysis of chip failure. Two main reasons for many research efforts in the field of chip reliability and failure analysis are given below:

- First, the use of memory in electronic devices is indispensable and thus their failure during operation is not only irritating to end-users, but may result in the loss of life and valuable information.

- Secondly, historically speaking the number of bits per chip has quadrupled roughly every  $3.1(\pi)$  years; and as memory chips have become more complex, so have their faults and sensitivity to faults. On the other hand, due to economic reasons, the test cost per chip (which is directly related to the test time) cannot be allowed to increase significantly. As a direct consequence, economical memory testing has been the subject of a large research effort.

#### 2.2 Electronic Reliability

As the first reliability studies have been made in the USA, at the beginning the American definition has been adopted: "The reliability is the probability that a certain product does not fail for a given period of time, and for certain operational and environmental conditions" [8].

The evolution of reliability field can be traced between the milestones of the semiconductor manufacturing history as given by Birolini, Kuehn, Knight and Bazu. The first studies concerning the electronic equipment and its reliability have been made for the purpose to improve the military avionics technique and the radar systems of the army. The mathematical formulation of the reliability and its utilization for material tests originate in ideas born in WWII when Werner Von Braun and his colleagues worked on V1 missiles. They started from an idea that a chain can't be more resistant than its weakest link. But repeated failure and multiple errors make them realize that all the constructive elements must play a role in reliability evaluation [8].

As of today reliability has been defined as the probability that an item will perform a required function under stated conditions for a stated period of time. Factors affecting the reliability of a product cover a large range of variables including design, manufacturing, application and the human involvement factor at each stage of production.

For a product to have high reliability it should have a low failure rate; and in order to achieve a low failure rate, careful failure analysis is needed. The origin of device failure analysis began with the invention and fabrication of the transistor. Initially single transistor, such as point contact structures and micro alloy germanium devices, could be analyzed by adopting previously developed metallurgical cross- sectioning procedure [8].

The entire semiconductor industry was revolutionized by silicon planar technology. Optical microscopy was extensively used at that time.

With the introduction of multiple devices fabricated within the same chip (ICs), electrical diagnostics became more complicated. Failure analysis technology continued to grow in parallel with IC fabrication in devising ways for selective passivation removal and methods for isolating individual transistor [8].

Reliability studies are performed to find out the reasons for chip failure and methods to avoid the failure. During its lifetime, a memory chip goes through various phases from wafer to final wear out period where it is highly susceptible for failure. Failure classification of the memory device can occur, depending on the cause, depending on the speed of failure or depending on the technical complexity. For simplicity, all failures can be broadly characterized into two categories [9].

- Failure Due to Manufacturing Defects at Chip Level and PCB Board Level: These failures arises due to the defects during manufacturing processes such as Epitaxy, Oxidation, Patterning, Diffusion, Thermal treatment, Cleaning, Etching, Bonding etc. [10]. PCB board defects may be caused due to improper wiring, missing chips and defect on board etc.

- *Failure Due to User Environment:* This type of failure arises unexpectedly when the user is in control of the device. These may be catastrophic failures causing interruption of the normal operation, or drift failures, producing defective operation by varying electrical characteristics. These defects are primarily caused due to electrical overstress, thermal overstress, and environmental stresses.

Most failures arising during the manufacturing and the user environment stage are due to the stresses that are inherent during the whole life cycle of the device. From the wafer stage until final packaging a device has to go through lots of mechanical and thermal stresses and in practice, lots of these stresses still remain inside the memory and affect functioning at the later stage. The next section describes current techniques for memory chip testing that are widely used in industries to detect these failures.

### 2.3 Current Approaches in Testing Memory Chips

Lots of research has already been devoted to the techniques being used in order to test the memory chips. These tests are done to find out the reliability of the chip while in operation. Here some of those important techniques are summarized.

Testing for inbuilt manufacturing defect can be done through electrical tests using flying probe testers, using manufacturing defect analyzers, using automated optical inspection, infrared thermography, acoustic micro imaging, and laser systems [11]. For environmental stress screening *s*tress may be applied in combination or in sequence on an accelerated basis within the product design capabilities. Stressing can be thermal cycling, vibration or both. Temperature range used is -65 to 230 deg F [11].

For finding the faults existing during functional or operating conditions electrical characterization is performed. It is a parametric, experimental analysis of the electrical properties of a given integrated circuit; its purpose is to investigate the influence of different operating conditions on the IC's behavior. Electrical characterization is thorough and exhaustive and can be carried out on an automatic test equipment (ATE) and resulting in all practical combinations; device supply voltages, logic input/output voltages, temperatures, timing conditions, parametric variations, various test patterns, operating frequency responses, modes of operation and power consumption [9].

Screening tests and test strategies includes Burn in (statically or dynamically), constant acceleration, ESD tests, glassivation, high temperature storage, hot carriers, humidity or damp test, latch up test which simulate voltage overstress on signal and power supply line as well as power on/ power off sequences, seal test, soft errors, solderability, thermal cycles and time dependent dielectric breakdown [11].

Test programs for the RAM memory consist of three items: DC parametric test, AC parametric test and functional test (although they often are applied simultaneously). A memory test program comprises various tests such as continuity check, leakage tests, a variety of functional tests, dynamic or timing tests, and parametric tests. Functional tests by far are the most important test where in DUT (device under test) is in dynamic test mode, which uses fast changing input stimuli to check the DUT's internal logic, i.e. check the storage and retrieval of standard patterns at rated cycle times. Various test patterns and truth tables are use for the functional test. Some of these test patterns include GALPAT, DIAPAT, MARCH, CHECKERBOARD [9].

Other tests that can be performed and play the most important role during the life cycle of the memory device are termed under *life testing*. The purpose of life test is to obtain information about the lifetime properties of the components. The term reliability testing is often used synonymously with lifetesting. As actual test for the memory device

life cycle is not feasible, several kinds of accelerated tests are performed and inferences about the reliability of the components under different set of loading conditions can be made based on a proven acceleration model [12].

Accelerated tests [13] (ATS) are used widely in manufacturing industries, particularly to obtain timely information on the reliability of product components and materials. Generally, information from tests at high levels of stress (e.g. use rate, temperature, voltage, or pressure) is extrapolated, through a physically reasonable statistical model, to obtain estimates of life or long-term performance at lower, normal levels of stress.

There are fundamentally two different methods of accelerating a reliability test:

- Increase the use rate of the product

- Increase the aging rate of the product by changing the conditions in which it is ought to work i.e. its loading conditions, thus decreasing the safety margin.

There are two important prerequisites that must be fulfilled, if useful information is to be derived from an accelerated life test:

- The failure mechanisms generated in the accelerated test must be the same as those observed under normal operating conditions.

- Its must be possible to extrapolate the lifetest results from the accelerated conditions to normal operating conditions.

Most accelerated tests data analyses include a combination of graphical methods (scatter and probability analysis) and analytical methods (regression analysis) based on the maximum likelihood (ML) estimation. These methods use the statistical models such as Arrehenius model, Monte Carlo simulation etc. Though most of the literature is devoted to using statistical methods for accelerated testing but there are other methods as well to analyze the data obtained from the accelerated tests. Few examples of new techniques that have evolved after different combinations of these traditional methods and using new devices are:

- Methodology for finding the *metallization and the gate defects* are photoemission microscopy, liquid crystal analysis [14], Voltage contrast [15] or internal probe [16, 17].

- Methodologies for SRAM defect due to the gate oxide short [18] based on the surveillance of the circuit current consumption (IDDQ) are more efficient than logic testing.

- Methodology for *Defect in chips due to metallization* shorts and the technique to single out the defect [19] can be external electrical functional test or internal contact less beam testing.

- Methodologies for SRAM bit failure due to the high frequency operations [20] uses nanoprobes and a minute manipulator is use to find out these defects.

- Methodology for *SRAM cell cold failure* [21] is based on using the electrical signatures of the transistors of SRAM cell after isolating the cell.

All the methods that are described above are those, which can either find the defect and errors in the memory at the time of inspection or at the user level. But what about predicting the reliability of the chip in future or say lifetime of the memory chip? Most of the research work that is being presented is based on the handbooks that were developed by the reliability engineers based on the experience and the statistical data. Most of those handbooks still serve as the guide to predict the lifetime estimation of the memory device [22]. But as already mentioned in earlier text, today need is for concurrent methodologies which can help in either protecting the component or provide opportunity for safe transfer of the important information before failure can occur.

### 2.4 Prediction of Stress Failure in Electronics and in Memory Chips

In 1860, A.Wohler presented some of the earlier fatigue failure information; the S-N curve that he showed identifies the stress below, which no failure will occur. Reliability engineering for electronics started with the establishment of the Ad Hoc Group on reliability of electronic component in 1950s. The first formal handbook was

publication of RCA called TR- 1100. In the following years RCA proposed a new prediction model for microcircuits, based on work of Boeing Aircraft Company. One was steady state temperature and other was mechanical related failure rate. The advent of complex microelectronics devices pushed the application of MIL-HDBK beyond reasons and they are used in comprehensive number around the world these days [23, 24].

Given the system architecture and parts, reliability prediction models are used to assess the influence of the magnitude and duration of the stresses on the reliability of the parts and systems, so that stress, environment controlling techniques and derating techniques can be implemented. For electronics derating parameters include current, voltage, power frequency and temperature [25].

The traditional approach to predict the long-term reliability of devices in field use involves implementing statistical models, using the exponential or constant failure rate model [26, 27, and 28]. Modified traditional approach is doubly conservative. After a time of 10<sup>4</sup> hr or say 1year it fixes the failure rate to be constant [29]. Other prediction techniques involve using the MIL-HDBK, Bellcore TR-NWT standard handbook, for the failure rate prediction. The new approach: Physics of failure modeling [12] arises due to lot of dissatisfaction in traditional technique. New approach is based on developing number of models for physics of failure lifetime evaluation. These models address the long-term wear out phase primarily. Modeling of electromigration failure and corrosion had already been mentioned in the modeling literatures.

Many of these approaches are used for the stress failure analysis of the memory chips. One such model based on the physics of failure approach was given by [9] called as *SYRP- for predicting failure rate* in a lot- based on the physics of failure lifetime evaluation.

Though most of the prediction methods that are being used in the memory chips are based on the RPP (reliability prediction procedures) as given in MIL-HDBK-217. Dynamic life testing methodology is used for purpose of quantifying the performance degradation during IC operation. Infact dynamic life testing is done for two major types of degradation mechanisms: electrical ones (such as latchup, ESD, hot carrier effect, dielectric break down and electromigration) and environmental ones (produced by thermal stress, humidity) [12].

The accelerated tests stand-alone as the best-suited method for predicting the life time performance of the memory device. These tests are based on the fact that the life of a memory device can be compressed to few days or even to few hours. Thus faults that would occur in the memory in the near future occur during the test and estimation and prediction about the lifetime of the memory device can be made.

#### 2.4.1 Traditional Accelerated Test, Statistical Models and Methods

For predicting the failure of the components using accelerated techniques, two statistical methods are widely used. One of them is Arrehenius model, which is used to predict the failure based on temperature-accelerating factor. The other one is the Eyring model based on the voltage-accelerating factor.

There are few other models that don't use statistical methods or mathematical modeling but use other advanced methods such as Neural Networks or Computer Aided Design for doing accelerated tests. Though these tests are not done on the memory devices but they have been done for residual life prediction from vibration based signals using Neural Network approach where in the input data is fed in to the feed forward back propagation Neural Network [30]. The device produces a signal of different frequencies or when device starts malfunctioning is known. As a result the signals at which the failure or the malfunctioning occurs are noted and then used for the input in Neural Networks [31, 32].

Next section talks about stresses, which can cause chip failure and are studied in this research work.

#### 2.5 Stresses on Memory Chips

Till now we already reviewed reliability, current techniques for detection and also failure prediction techniques. In this section stresses that are existing within the chips, which leads to its failure at manufacturing stage or after a lifetime are discussed. We also talked about the current work that's been done in voltage stress and signal stress specifically, which is main concern of this research work as well.

### 2.5.1 Mechanical Stresses

Both tensile and compressive stresses exist inside the memory device. If we look at the wafer grain surface due to ion implantation and bonding there are different stresses at the grain boundaries. These stresses can cause the failure of the memory devices if they are present in excess.

#### 2.5.2 Electrical Stresses

SRAM when under operating conditions is subjected to different kind of stresses. These stresses can be voltage stress, current stress, or current density.

#### 2.5.3 Environmental Stresses

Stresses arise due to the internal and external conditions such as vibration, shock, radiation, humidity, temperature, and contaminants. The failure mechanisms involved in all these process are generally corrosion, distortion, fatigue, fracture and wear. These defects may cause electro migration, change in electrical parameters, deformation, cracking, change in resistance, degradation, acid formation, material fatigue, shorting of electrical parts, and permanent stress etc [11].

The stresses that are being studied in this research work are voltage stress and signal stresses. This section describes the current study and research being done in either detecting these stresses in chips or predicting failure due to them.

#### 2.5.4 Voltage Stress

The chip may fail due to various different reasons when subjected to higher than normal voltage. Generally if voltage overload is slowly applied then bond wires fail and if it is applied relatively fast then silicon junctions fail. But the location of the failure depends on the current path and melting temperature of the materials. Various methods are used to either predict overstress directly, or find a model that simulate the conditions and that data can be used to find out when the chip is going to fail [2].

One of the major reasons for failure due to chip overstress is ESD (electrostatic discharge). ESD failures are usually due to a brief, high intensity static charge, often caused when an improperly grounded human or machine handles the chip. Similarly EOS (electrical overstress) failures typically involve long term low intensity stress such as might arise if a part consistently ran at a higher voltage or clock speed than intended [2].

Some of the novel techniques used for detecting of stress is using thermal simulators. In [33] algorithm for thermal simulations is given for electothermal simulation. This algorithm helps in studying the transient thermal effect caused due to existence of electrical overstressing. The algorithm is based on the region wise exponential approximation technique and a recursive convolution scheme. Like wise lots of other electrothermal circuit models are defined to simulate the conditions resulting from the thermal degradation setting in the chips due to overstressing [34].

In another approach electrical overstress is considered to be the effect of plasma instabilities and Wunsch-Bell thermal paradigm was used for practical failure modeling [35]. Also an engineering method based on the failure threshold of diodes and transistors due to reverse biasing pulses that are generated due to electrical overstressing is mentioned in [36].

Along with research for predicting electrical stress there is an ongoing effort to predict the defects that are produced due to overstressing. iTEM which is a reliability diagnosis tool for electromigration [37] and iCET a chip level electrothermal simulator which gives the CMOS on chip steady state temperature profile and circuit performance

for given input conditions [38] are used. Substrate resistance extraction method that accurately calculates, the distribution of injection current into the substrate during ESD or latch up resulting from overstressing is mentioned in [39].

Most of these methods create the simulation of the component failure but today demand is for the concurrent technologies, which can predict the failure before time and avoid the unnecessary failure of the chips. One of the current technologies based on the concurrent engineering was developed at Hughes Aircraft Company, radar system group. They developed software called HAC RPP, which concurrently does the computation of derated and stressed part failure rate/ unit and identifies overstressed part problem [40].

#### 2.5.5 Signal Stress

Signal stress can be caused due to variation in signal frequency, clock frequency, duty cycle or if the signal voltage is kept higher than the normal.

Signal stress we used for the research was the stress induced, when continuous signals are send to chip and chip processes that information as compared to when its working intermittently. This kind of stress can be understood as the variation in the duty cycle as well as the variation in the frequency because it depends upon, how frequently code is running on the chip and the duration for which the code was running each time.

Most of the work done for signal stress is based on finding out the defects during the duty cycle variation and defects due to variation in frequency.

Research has been done on variation in the frequency to outline various defects and detection techniques. Nowadays chips are being made which can work in access of 200 MHz. Dobberpuhl [41] mentioned the technique for self stress test for the systems working at very high frequency. It investigates the reliability concerns due to hot carrier injection, electromigration under realistic circuit conditions. Snyder et al. [42] did work to analyze the reasons of failure while the chip is working at very high frequency. Ikeda, Yoshida et al. [43, 44] described various different techniques such as nanoprobes, selective etching and TEM observations to analyze the bit failure that occurs at low voltage and high frequency operating speeds. Research has been done to understand and detect the defects caused by the variation in frequency. The most prominent defect that may arise is the hot carrier injection as mentioned in [45].

The work on frequency variation in most of the researches deals with the variation induced due to variation in clock frequency of sending the signals but here in the research the term frequency means as to how frequent we are using particular component. This way we can avoid its overuse or prevent it from failure due to overuse by comparing the heating rate for the chip when it is working continuously and when its working intermittently.

There were several codes, which were run on the chip for reduced duty cycle. The heating rate difference was calculated to give us the fair good results from which we can show that there is fairly good reason between the heating rate when chip is working continuously and when its working intermittently.

As memory chip was used in the research so there was no significant increase in the chip-heating rate, which can cause the failure. But if the similar work is done for the microcontroller then we can build a heating rate model for variation in signal stress that is duty cycle and the frequency of the signals and avoid over heating which can lead to the failure of the chip.

From the literature review it is clear, though lot of work is done for chip failure and controlling the parameter which might lead to its failure but lesser work is done in predicting the chip failure if it might occur while chip is being used. This research work is thus novel in finding out the possibility of predicting the chip failure due to two most important parameters namely voltage overstress and signal stress.

All this can prove to be a step towards building a predictive model for complete electronic device based on the similar lines of conclusion.

## CHAPTER III DESIGN OF EXPERIMENTS

#### 3.1 Introduction

This chapter details the features of the 8051 board used for the research. Description of static random access memory and its functional diagram, material used, detailed test set-up along with the data acquisition techniques and finally the hypothesis used for testing are given. This design of experiments gives the overall view of the various components, which were used for the research and also the test setup that was used to do the experiments.

### 3.2 Experimental Setup

This subsection consists of the details about the micro controller board that was used for the research work. It discusses the basic features of 8051 board, description of SRAM used manufactured by Samsung, function of the SRAM, test set-up, material used and finally data acquisition and imaging procedure.

#### 3.2.1 Features of 8051 Board

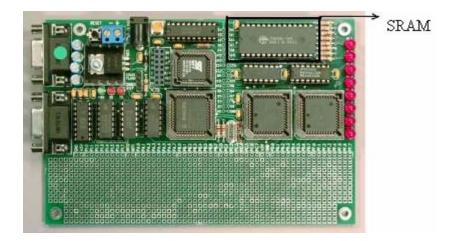

Some of the features of the 8051 board used were standard 87C52 CPU clocked at 22.1184 MHz, with on board 32k SRAM (2000-7FFF) and 30k FLASH ROM (8000-F7FF). It can also work at high-speed baud rates: 115200, 75600, 38400, etc. It had eight LED's controlled by 8 dedicated I/O lines. Figure 3.1 shows the layout of the board and the SRAM used.

Requirement for the board were DC Voltage (8 - 15 volts), AS-31 Assembler or Compiler, Terminal Emulation Program, e.g. HyperTerminal (windows) or VB code. The internal layout allows the data transfer between micro controller-FLASH, micro controller-SRAM.

#### 3.2.2 General Description of SRAM

The SRAM used belonged to K6X0808C1D family of CMOS chips [46]. It supported low data retention voltage and current. The normal operating voltage range for

SRAM was (Vcc Range: 4.5 V- 5.5V). Voltage on any pin relative to  $V_{ss}$  was (-0.5 to +0.5 V on  $V_{cc}$ ) and maximum was 7.0 V. Voltage on  $V_{cc}$  supply relative to  $V_{ss}$  was (-0.3 to 7.0 V).

Figure 3.1 Layout of the board and SRAM used for experiments.

#### 3.2.3 Function of SRAM Diagram

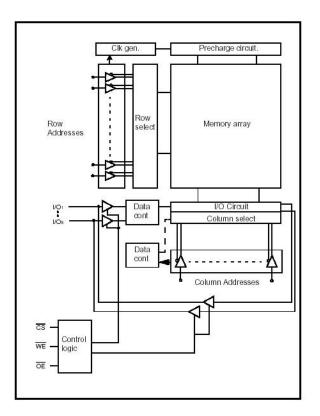

Since the goal of the experiment was to excite the SRAM it is important to understand the functioning of the component to excite it the most. The SRAM functions in a series of steps as is shown quite well in the timing diagrams. To explain its function it is important to know the overall function of the SRAM in tandem with the 8051 microcontroller. The microcontroller is able to send and retrieve data from the SRAM by sending two important pieces of information: the address of data to be read/written and the data to be written if that is the command to be used. The SRAM is tied to the microcontroller by several lines as shown in Figure 3.2.

Figure 3.2 Functional block diagram for SRAM.

The first lines are the write enable, and output enable lines, or WE and OE, which are used in reading and writing data to the SRAM. The other single wire connected is the chip select wire. This wire is used in indicating that this particular chip is to be used to store the incoming data, and will thus be used in writing data to the chip. This is incase there are multiple RAM chips for one particular board, it may be necessary to send data to a different RAM chip. The last individual line on the SRAM is the line tied to the system clock of the microcontroller. This is to allow the chip to sync up with the controller so that all data is captured properly and not at in between values. It is also used so that the SRAM will know when exactly eight bits have been entered and are ready to be read into and placed in memory. Also going from the controller to

the SRAM are a series of address and data lines. There are 15 address lines, and 8 data lines used to transmit data.

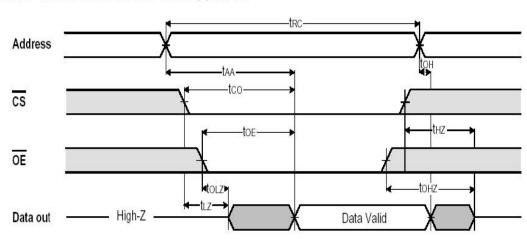

The read cycle shown in Figure 3.3 is a simple process that essentially requires two steps out of the microcontroller. It first will begin sending the address bits to the RAM chip(s). The RAM chip(s) will receive the bits and one will be pulsed low on its CS line. At this point it will also have its OE line pulsed low as well, enabling it to send the data specified by the address it is receiving.

TIMING WAVEFORM OF READ CYCLE(2) (WE=VIH)

Figure 3.3 Timing waveform for the read cycle.

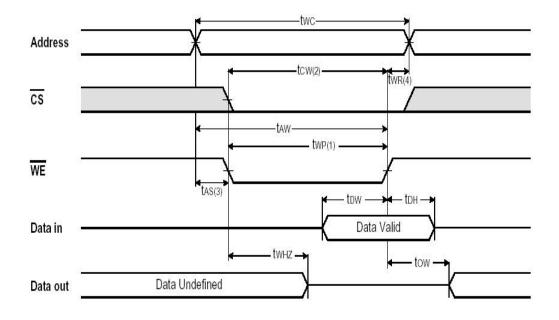

The write cycle shown of the SRAM in Figure 3.4 is quite similar to the read cycle with the exception that the microcontroller sends data to the SRAM which is one more step in the process. To write to the SRAM, the first step is for the microcontroller to send an address to the SRAM followed by pulsing the chip select line and write enable line low. This will allow the address lines to bring in the memory location to be written to and will divide the information into row and column addresses. At this point the data will be coming in and placed into the address specified on the address lines.

#### TIMING WAVEFORM OF WRITE CYCLE(1) (WE Controlled)

Figure 3.4 Timing waveform for write cycle.

#### 3.2.4 Materials

Electronic equipment used for the experiments include 8051 development board communicating with computer through COM port, a enclosure with infrared camera inside it, special arrangement for experiments, bread board, connectors to stress the chips, power supplies. Also two thermocouples one for measuring temperature of the room and other inside the box, O-scope and digital multimeters were used. Various software tools were used for evaluating, collecting and analysis of data such as MATLAB's Neural Network tool box, Statistical software tools like Statmost, Best Fit.

#### 3.2.5 Test Set-Up

A connector was mounted on a board. Chips were placed over this connector while the board was kept on a fixture inside a black box that also has an infrared camera mounted inside it. This infrared camera was used for imaging the chip on the board, while chips were stressed. The other end of connector was soldered to another connector via ribbon cable. This second connector was inserted in the slot for SRAM on the micro controller board. The purpose of this kind of arrangement was to keep SRAM separated from all the components on the micro controller board. As imaging was done for heating rate from SRAM so there was no use keeping the micro controller board having all the other components beside SRAM under infrared camera. That is why micro controller board was kept outside the box and only the ribbon cable connects the SRAM on the board, inside the box, with micro controller board outside the box.

Beside experimental setup few softwares were also used. VB code APPENDIX B was used to synchronize the time between turning the power on, on the micro controller board, sending the code on the board and start imaging through infrared camera. This VB code mimics the HyperTerminal in windows but saves all kind of manual operations involving opening and sending the data file to micro controller. Besides that all the process of opening the files and sending the code and running it can be done by single command thus its easy to turn the power on and enter the command to send the code simultaneously. This way synchronization between turning the power on and sending the code was achieved. Power was turned on and at the same time code was sent on micro controller board as soon as first scan gets over. This way all three are synchronized.

Two more softwares were used. WinTes to take the images using IR camera and Thermal View to get the heating rate data from the images obtained from IR camera. With this setup completed, we were ready for experiments.

#### 3.2.6 Image and Data Acquisition Procedure

- 1. Once the codes were stored on SRAM, board was kept over a fixture inside an enclosed chamber.

- 2. Infrared camera that was permanently fixed inside the chamber was positioned to take images of chip over board.

- Once chip was properly placed and chamber was closed, VB code was used to start the codes already stored. VB code was used to synchronize the time between turning the power on and running the code.

- 4. Each code was run on the chip for specific time duration during which infrared camera takes images every 20 secs or 7 secs depending on the experiments.

- 5. At the end of the trial we had several images from which data regarding the variation in the heating rate was obtained using Thermal View software. The heating rate was plotted on excel charts.

#### 3.3 Hypothesis

In general terms hypothesis can be understood as the basis of doing any experiment. For every experiment we need to test certain hypothesis. Components of hypothesis are [47]:

3.3.1 Null Hypothesis: According to the null hypothesis

$$H_0 = \operatorname{All} \mu_i$$

are same

where  $\mu_i$  is the performance variable which is the heating rate in our case.

Performance Variable =  $\tilde{\mu}_i$  = "Average Heating Rate"

3.3.2 Alternative Hypothesis: According to the alternative hypothesis

$H_a$  = At least two of the  $\tilde{\mu}_i$  's are different

Model can only be created if Alternative Hypothesis proved to be true.

# CHAPTER IV EXPERIMENTS

#### 4.1 Introduction

Our main aim was to build a predictive model based on the heating rate emitted from the chip under voltage stress and signal (frequency/ duty cycle) stresses. For reaching on to that point we needed to follow certain steps.

These steps included finding out the heating rate for chips, which were stressed, extracting data using thermal view and finally building a model.

But before starting on the actual experiments from which model was created, few preliminary experiments were done to explore the parameter settings needed. This information would help us to reduce the errors in the later stage of the experiments.

Sections in this chapter discuss about results from preliminary experiments, methods to avoid errors and details of all the experiments done, while stressing.

The experiments can be categorized into two parts.

- *Preliminary Experiments:* These experiments served as a platform and mean to standardize the second set of experiments. This set of experiments included experiments for ascertaining parameters such as "how long the chip should be stressed, what should be the cooling time, what should be the stress levels on the chip, what codes needed to be used etc.?"

- *Full Experiments:* The second set of experiments referred to experiments that were needed for obtaining data for developing Neural Network. This set included experiments for voltage stress and signal frequency/duty cycle stress.

#### 4.2 **Preliminary Experiments**

Following are the results that were obtained from preliminary experiments. At the end of these experiments we had all the necessary information that was needed to do the experiments that would finally give us the heating rate data to build the model.

- Heating rate from chips became constant in approximately 2 minutes, thus scanning time was reduced to less than 5 minutes.

- Cooling time for the chip was same irrespective of whether it was a stressed chip or unstressed chip.

- There was little effect due to random noise by infrared camera.

- While doing voltage stressing, with positive voltage overstressing on  $V_{cc}$  and ground on  $V_{ss}$  pins on chip as shown in Figure 4.1, no difference in heating rate between various stress levels was obtained. This was also proved by considering results from both F-test and excels graphs. Neither there was any difference in memory map between stressed and unstressed chips. The reason might be  $V_{cc}$  pins are better protected against voltage surge than data or address pins or  $V_{cc}$  pin connections do not directly interacts with the die area.

- Heating rate difference was obtained when stressing was done on data pins and address pins simultaneously. The detail of the test are as follows:

- Pins to be stressed: Two data pins and an address pin were selected because it was

possible to clearly differentiate between heating rates while stressing these pins.

Although earlier V<sub>cc</sub> pin was stressed but heating rate failed to give any significant

difference for unstressed and stressed chips.

- 2. **Stress Levels:** For the experiment 10 chips were stressed for five minutes each starting at 5.5V and going till 6.75 V. Chips were tested after every five minutes of stress to see if they were still working or not. Based on the finding it was concluded that out of 10 chips 7 of them failed when 6.75 V was supplied for five minutes. Thus the highest stress voltage was kept at 6.75 V.

- 3. Time for Stressing: Experiment results suggest that chip failure occur while temperature exceeds 350 °F and chips attain that temperature within first two minutes for the least voltage stress used. So the time for least stress level was around 2 minutes and it decreased correspondingly with increase in the stress level depending on how fast upper limit of temperature (>= 350 °F) was reached.

Figure 4.1 Pins that were stressed  $V_{cc}$  (+) and  $V_{ss}$  (-).

• From the graphs between the heating rate and average heating rate, we observed that variation in heating rate was much smoother for graphs based on average of heating rates thus it was decided to build model based on average of heating rates for chip and die area.

Average Heating rate for a cell (particular row and column) at  $N^{th}$  time interval is defined by taking the average of heating rate of cell, at that time interval and at all previous time intervals.

Consider that initial heating rate is given as  $H_o$  and subsequent heating rates for every interval are defined as  $H_1$ ,  $H_2$ ,..., $H_N$ , then average heating rate at  $N^{th}$  time interval is

$$AH_N = \sum_{i=1}^N \boldsymbol{H}_i$$

4.1

$AH_i$  = Average heating rate at i<sup>th</sup> time interval

$H_i$  = Heating rate at i<sup>th</sup> time interval

- Increase in the temperature of the chips was exponential. At higher voltage which was around 7V the increase in the temperature from ambient to the failure temperature (>300 °F) was within couple of seconds.

- The failure rate of the chips was thus exponential as well; i.e. the time for failure decreases exponentially with increase in the stress level.

- There exists heating rate difference between unstressed chip and stressed one if stressed chip was made to run just after it was stressed but if its allowed to cool down for a day or two, no difference in heating rate exists between the two chips. The reason may be the tendency of the chip internal architecture to snap back to it normal conditions once it cools down.

- For the particular memory chip that was suppose to work within the range of 4.5V to 5.5V the failure rate was significantly higher at 6.75 V and above.

- When chip temperature is above 350 °F, the failure rate is around 40%.

# 4.3 Avoiding Errors

Few house keeping things to be aware of while doing the experiments are as follows.

- Do not touch the chips with bare hands or blow air near the chips.

- Try maintaining the ambient environment constant inside the chamber.

- Try maintaining the same chip position and Infrared camera position.

- Check for possibility of shorts on the board.

- Check for any inconsistency in data due to environmental factors or due to human errors such as time lag between turning power on and sending code to the micro controller board.

#### 4.4 Experiments with Signal Stress-I

Signal stress experiment was done in two parts based on different ways of applying signal (frequency/duty cycle) stress.

First experiment was done to find out the effect of signal density variation for the data transfer across the SRAM and the micro controller. This kind of signal stress imitates the stress existing due to the variation in frequency of usage of particular component, SRAM in our case.

For the experiment, two codes each with two modifications were used. In the next paragraph, basic differences in the codes are explained. More detailed explanation is provided in APPENDIX A.

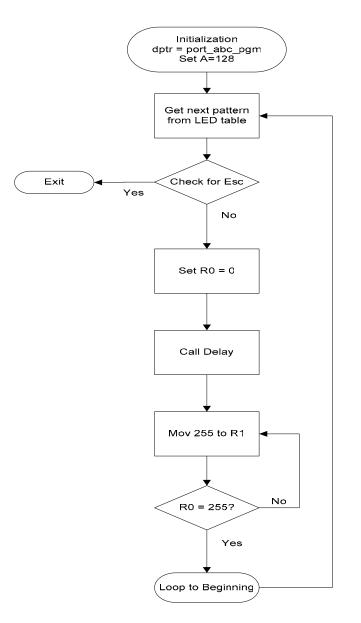

Two codes were used along with two modified codes, from each one of them, consisting of series of NOPs (No operation loop) in the codes. Code 5 "IncrementsRAM.asm" incremented the value by 1 moving across the SRAM memory and increased the value till it reaches to the end of the address and then repeats the loop back again. Code 6 was the modification in the code 5 with finite number of NOP loops in the code, which caused the delay in execution of commands in the code. Code 7 "Zerosnfswesc" filled the address with zeros till it reaches to memory address 7FFF and then it looped back and filled the addresses with F's, this procedure was done repeatedly till "ESC" key was pressed. Code 8 was the variation in the code 7 with NOPs loop in the code, which does the same operation as explained for code 6 above.

For each one of them, time for execution of the commands was different on SRAM therefore they stressed the chips to different extent, depending on the usage of SRAM. For codes with NOPs the commands NOPs were executed faster than the instructions in the codes without NOPs. As a result the code with NOP heated the chip far more than those without NOPs.

Also between the two codes there was slight heating rate difference because of variation in data stored at different memory addresses as these values corresponds to variation in voltage level stored in the chip capacitors. Table 4.1 shows the test matrix based on the above description.

| Number of chips | Codes Used                       |  |

|-----------------|----------------------------------|--|

| 40              | Code 5 – IncrementsRAM.asm       |  |

|                 | Code 6 – IncrementsRAMwdelay.asm |  |

|                 | Code 7- Zerosnfswesc.asm         |  |

|                 | Code 8- Zerosnfswescndelay.asm   |  |

Table 4.1 Test matrix for the experiment based on the different tests on unstressed chips.

In these experiments two trials were done on each chip. Testing was done on 40 chips; out of which two-third were used to develop Neural Network model and one-third test the model. The amount of time between each subsequent trial was reduced to 7-8 minutes, which includes 2-3 minutes of blowing air in the chamber, 2 minutes of leaving the box open and lastly 2 minutes of leaving the box closed. In total of 4 codes were made to run for 3 minutes on each chip and adding repeated trials to it, we did 8 trials on each chip, which took around hour and half for each chip. Again specific care was taken to keep the chip position to be same for every trial and for every test and to avoid or reduce the error due to human intervention.

#### 4.4.1 Procedure

The design for the experiment and test set-up was already mentioned in detail in chapter-II. Following steps describe the procedure for performing signal stress experiment.

- 1. Once the codes were stored on SRAM (for Signal Density stress-I), board was kept over a fixture inside an enclosed chamber.

- 2. Infrared camera which was permanently fixed inside the chamber was positioned to take images of chip (SRAM) on the board.

- 3. Once chip was properly placed and chamber was closed, visual basic (VB) code automate the testing procedures by synchronizing the time between turning the power on, running the code and start imaging the chip for its heating rate.

- 4. Each code was run on the chip for a minute and a half for which infrared camera takes images every 20secs.

- 5. At the end of the trial we have 7 images from which data regarding the variation in the heating rate was obtained using an in-house written software called thermal view. The heating rate was plotted on excel charts.

#### 4.5 Experiments with Signal Stress-II

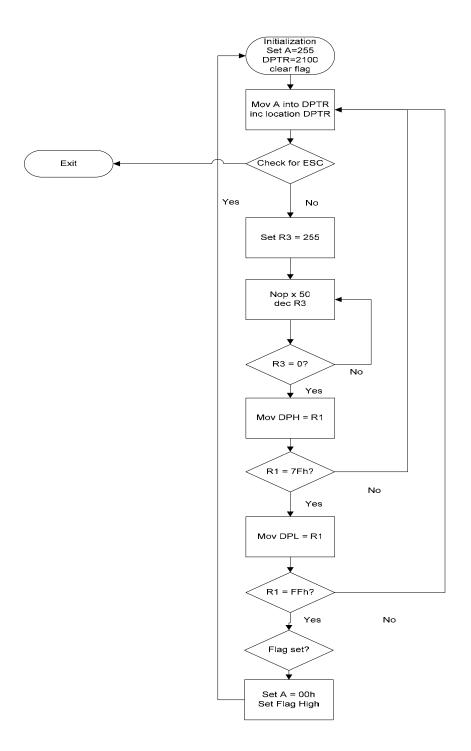

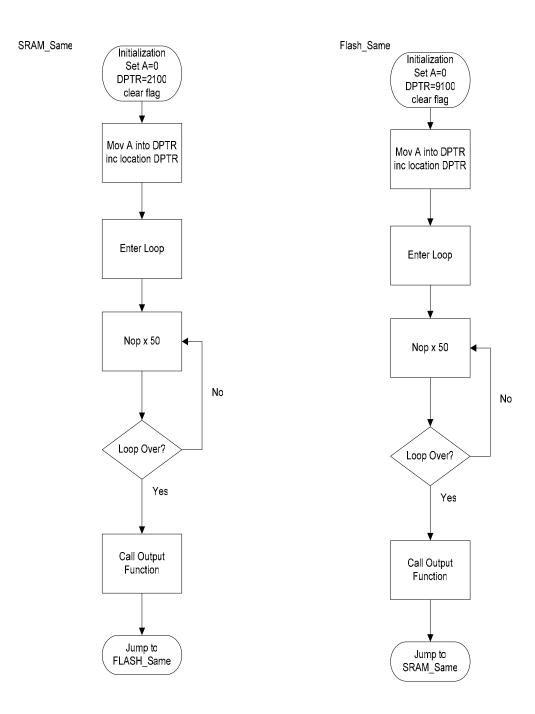

This section talks about experiments consisting of signal stress caused due to the change in the duty cycle and also due to change in the frequency of chip usage. Codes were stored both on flash memory and SRAM so that when delay was caused SRAM should not be used instead code should run on flash for the time we want to cause the delay. Four different sets of codes were used to change the frequency of data in and out of the SRAM. Each set of code consisted of one code on SRAM and one code on flash.

The code on SRAM runs for different duration for each set of code and thus gives the change in duty cycle of SRAM. Similarly code spent different time on flash before jumping on to SRAM which gave the variation in frequency of chip usage.

The time spent on either of the chip was mentioned in ratio of SRAM: flash which means the ratio of time, spent on SRAM in comparison to that on flash. For the first code this ratio was 20:1 that means code was running 20 times more on SRAM than on flash. For the second code these ratios was 3:1 and still code was running on SRAM for longer duration than on flash. For the third code the ratio was 1:1 that is equal time spent on SRAM and on flash. For the last and the fourth code this ratio is 1:3 that is code on the flash was running 3 times more in comparison to the one on SRAM. The function of each code is separately mentioned in APPENDIX A. Table 4.2 shows the test matrix based on the above description.

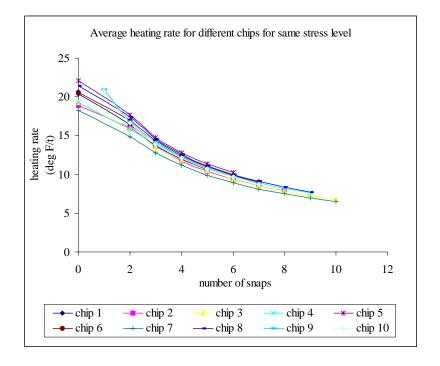

It can be noticed that time spent on SRAM was decreasing as we moved from code 1 to code 4 and thus its heating rate as well.

Testing was done on 40 chips, out of which two-third were used to develop Neural Net model and one- third for evaluating accuracy of the model. Number of trials was reduced from 5 to 2 for every chip while running each set of code. The time spent between the trials was also reduced as the external conditions in the room were stable. Again specific care was taken to keep the chip at the same position for every trial to avoid human intervention error.

The design, test set-up and procedure followed for the experiments were similar to that of Signal Stress-I.

| Number of | Code used on SRAM and Flash       | Ratio of time |

|-----------|-----------------------------------|---------------|

| Chips     |                                   | spent         |

| 40        | Code set 9: SRAM more-Flash same  | 20:1          |

|           | Code set 10: SRAM 200k-Flash same | 3:1           |

|           | Code set 11: SRAM same-Flash same | 1:1           |

|           | Code set 12: SRAM same-Flash 150k | 1:3           |

Table 4.2 Test matrix based on the different sets of codes

### 4.6 Experiments with Voltage Stress

In this experiment we stressed two data pins simultaneously at varying voltages. Several sets of chips were stressed for before finally arriving at the conclusion as to how many chips needed to be stressed and how? During the course of the experiments several things were noted. Few of them are summarized below.

.

#### 4.6.1 Procedure for Stressing

- 1. 10 chips were placed on the breadboard. Data pins 2, 3 and address pin 4 were stressed simultaneously as shown in Figure 4.2.

- 2. Each chip was stressed with the voltage starting from 5.5V and stressed for 5 minutes. Once stressed this chip was tested if it was still working or not. If it was working then voltage was increased by 0.25 to 5.75 V and the chip was stressed for 5 minutes again. The whole procedure was repeated till the chip failed.

Figure 4.2 SRAM and the pins stressed.

- 3. From the experiments highest voltage at which chip can be stressed was considered to be 6.75 V with high probability of chip failure if it was stressed for 5 minutes.

- 4. The stress level was divided into four different categories 6V, 6.25V, 6.5V and 6.75V and each category consisted of 10 chips each. In total, we had 40 chips that were tested for 4 stress levels as shown in Table 4.3.

| Number of chips               | Stress level Used |

|-------------------------------|-------------------|

| 1st set- 10 chips             | 6 V               |

| 2nd set- 10 chips             | 6.25 V            |

| 3 <sup>rd</sup> set- 10 chips | 6.5 V             |

| 4 <sup>th</sup> set- 10 chips | 6.75 V            |

Table 4.3 Test matrix for the experiment based on the different stress levels used.

# 4.6.2 Procedure for Imaging

- For starting the experiment chip was placed on a connector (1) on the board and the board was kept under the IR camera inside the box. The other end of the connector was soldered to second connector (2), which was outside the box on the breadboard. The reason for this arrangement was that when we stressed the pins of the connector outside the box it sends the same voltage to the corresponding pins on the chips. So we can stress the chip while scanning it under IR camera by applying voltage on corresponding pins of the connector (2) outside the chamber.

- 2. Once setup was ready the connector outside the enclosure was stressed with 6V in such a way that it will stress the corresponding pins 2, 3 and 4. 2 and 3 were data pins whereas 4 was the address pin. Figure 4.2 shows the stressed pins on SRAM. The chip was stressed till its temperature starts increasing drastically. At the same time IR camera was turned on to take the scans every 7 seconds. The temperature determined the scanning time and the scanning was usually stopped whenever temperature reached around 350°F.

- 3. Usually heating starts around 20 minutes or so for 6V whereas it took just 8 mins or so for temperature to increase when stressed at 6.25V, 6.5V and 6.75V. Once all the chips were scanned, thermal view software was used to obtain the data from the images. This data was plotted in the excel sheets to see the difference in the heating

rate of the stressed chips. The heating rate data obtained from the first four images in a scan were used as an input to the Back Propagation algorithm in Neural Networks.

4. We had 40 scans in total, 10 scans each for individual stress level equal to the number of chips for each stress level. Out of these 40 scans 28 scans or two-third was used to train the neural net and 12 scans or one-third were used for the testing purposes. MSE (mean square error) value was the factor defining the accuracy and the efficiency of the Neural Network method.

# CHAPTER V RESULTS

#### 5.1 Introduction

This chapter describes all the experiment results obtained from infrared imaging over the chip, while it was stressed. The heating rate data was plotted in the Excel sheet and the graphs are shown for various set of experiments. This heating rate data was then used to train Neural Network to build a model based on the training set and the testing set used. MSE (Mean Square Error) was considered as the parameter to define efficiency of particular model. Thus MSE is shown for various topologies and using various training functions based on Back propagation algorithm.

The chapter consists of three sections. First section consists of the results from the signal stress-I, second from section-II. Finally third section consists of the results from voltage stress.

Heating rate data obtained using infrared camera was extracted using thermal view software. Excel charts were then used to plot the heating rate graphs. These graphs gave the visual representation of the heating rate curves for different stress levels. On these heating rate data statistical analysis was done to find out if the heating rate belong to different classes because then only it was possible to build efficient Neural Network model. Using heating rate data Neural Network model was build. As previously said out of the heating rate from all 40 chips two third was used to train the model and remaining one third was used to test the model. Details of the procedure are given in the subsequent sections.

# 5.2 Results from Signal Stress-I

## 5.2.1 Thermal Profiles

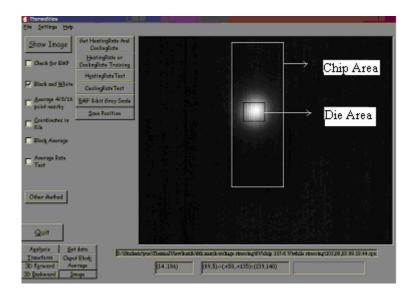

For every chip, average heating rate was obtained for both the chip and die area on chip using four different stress levels. Figure 5.1 shows the chip area and die area on a chip while imaging.

Figure 5.1 Chip area and the die area using Thermal View.

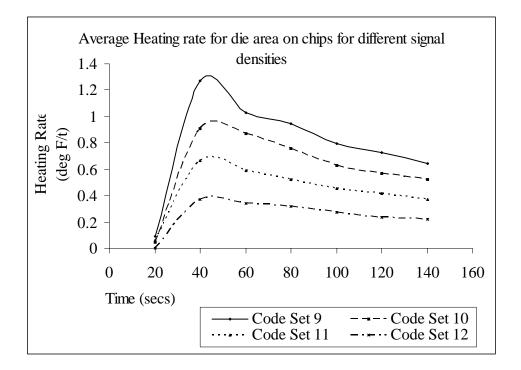

Figure 5.2 shows the average heating rate trend for the chips using heating rate for the die area. Average heating rate for the codes with NOPs was pretty similar and was significantly higher than the heating rate for the codes with NOPs. Among the codes with NOPs heating rate was higher for the code in which each memory address was increased by 1.

Figure 5.2 Variation in heating rate for die area on chips for signal stress-I.

#### 5.2.2 Statistical Analysis Results

Heating rate graphs in Excel showed that average heating rate differs for each code mimicking various stress levels. But to prove it definitely, statistical *f-test* using STATMOST software was done. If the critical *f-value* is higher than the *f-value* from the data then it's difficult to differentiate between the data into different classes. But if *f-value* from the data is higher than critical *f-value*, it means that it is possible to differentiate data into different classes.

*F-test* results from the analysis showed that the critical *f-value* was much smaller than the *f-value* from data thus it was possible to clearly differentiate between the heating rate data from various stress levels. Table 5.1 shows the *F-test* results obtained.

| F- Test results for SD – I for die area    |        |                    |  |  |

|--------------------------------------------|--------|--------------------|--|--|

| Column Name Mean                           |        | Standard Deviation |  |  |

| Code 5                                     | 3.0165 | 0.6756             |  |  |

| Code 6                                     | 4.5626 | 0.4825             |  |  |

| Code 7                                     | 2.6622 | 0.3570             |  |  |

| Code 8                                     | 4.8448 | 0.4887             |  |  |

| <i>f-value</i> for confidence interval 95% |        | 153.6855           |  |  |

| Critical <i>f-value</i> (0.05,3)           |        | 2.6732             |  |  |

Table 5.1 F-test results for SD-I die area.

# 5.3 Model Development Approach for Signal Stress-I

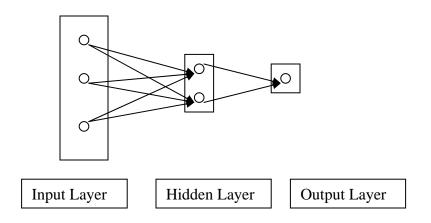

In this section complete methodology regarding neural net is described. Basic 3-2-1 network is shown in Figure 5.3 consisting of 3 input nodes, 2 hidden nodes and one output node. Neural net model is more or less like brain having millions of neurons and hence the name.

Figure 5.3 3-2-1 topology of Neural Network prediction model.

The underlying premise behind neural net methodology was the training of the network using input data based on some primary assumptions regarding the choice of network, number of nodes, layers, and training functions used. Repeated tests can be performed in order to obtain the best network. Neural Net is capable of complex modeling using large number of parameters while adjusting the values of the weights associate between elements (nodes) in order to reduce the error.