## LAYOUT OPTIMIZATION IN ULTRA DEEP SUBMICRON VLSI DESIGN

A Dissertation

by

DI WU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2006

Major Subject: Computer Science

# LAYOUT OPTIMIZATION IN ULTRA DEEP SUBMICRON VLSI DESIGN

A Dissertation

by

DI WU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

Co-Chairs of Committee, Rabi N. Mahapatra

Jiang Hu

Committee Members, Duncan M. Walker

Jianer Chen

Head of Department, Valerie E. Taylor

May 2006

Major Subject: Computer Science

#### **ABSTRACT**

Layout Optimization in Ultra Deep Submicron VLSI Design. (May 2006)

Di Wu, B.E., Beijing University of Posts and Telecommunications;

M.S., East Carolina University

Co-Chairs of Advisory Committee: Dr. Rabi N. Mahapatra

Dr. Jiang Hu

As fabrication technology keeps advancing, many deep submicron (DSM) effects have become increasingly evident and can no longer be ignored in Very Large Scale Integration (VLSI) design. In this dissertation, we study several deep submicron problems (eg. coupling capacitance, antenna effect and delay variation) and propose optimization techniques to mitigate these DSM effects in the place-and-route stage of VLSI physical design.

The place-and-route stage of physical design can be further divided into several steps: (1) Placement, (2) Global routing, (3) Layer assignment, (4) Track assignment, and (5) Detailed routing. Among them, layer/track assignment assigns major trunks of wire segments to specific layers/tracks in order to guide the underlying detailed router. In this dissertation, we have proposed techniques to handle coupling capacitance at the layer/track assignment stage, antenna effect at the layer assignment, and delay variation at the ECO (Engineering Change Order) placement stage, respectively. More specifically, at layer assignment, we have proposed an improved probabilistic model to quickly estimate the amount of coupling capacitance for timing optimization. Antenna effects are also handled at layer assignment through a linear-time tree partitioning algorithm. At the track assignment stage, timing is further optimized using a graph based technique. In addition, we have proposed a novel gate splitting methodology to reduce delay variation in the ECO placement considering spatial correlations. Experimental results on benchmark circuits showed the effectiveness of our approaches.

To my parents

#### ACKNOWLEDGMENTS

First, I would like to thank my advisors Professor Rabi Mahapatra and Professor Jiang Hu for their continuous support, guidance and encouragement. They have led me into this exciting field of VLSI physical design and their insights on research directions and active mentoring have made this dissertation possible. I believe that what I have learned in my research will definitely benefit my career upon graduation.

I am also grateful to members of my advisory committee, Dr. Hank Walker and Dr. Jianer Chen for their valuable comments and precious time. My deep gratitude also goes to Dr. Ricardo Gutierrez-Osuna for helping with my dissertation proposal.

I would like to thank my colleagues and co-authors for sharing research ideas and for helping me on various research projects. Cliff Sze has helped me wrote a dual-driver timing analyzer and taught me how to use the C-tree program in the latest research project. Lu Xiang has provided me his ISCAS85 testcases and standard cell libraries and taught me how to extract timing information using HSPICE. Qiuyang Li helped me write a gate-sizing program for the lastest project. I would also like to thank Ke Cao, Ganesh Venkataraman and Dr Min Zhao for their help and discussions. It is my pleasure to work with them.

Finally, I dedicate this dissertation to my parents for their long-term encouragement, support and patience. They have given me so much inspiration and love throughout my graduate study at Texas A&M.

# TABLE OF CONTENTS

| CHAPTER |                                                                                                                                                                                                                                                                                                                            | Page                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| I       | INTRODUCTION                                                                                                                                                                                                                                                                                                               | 1                                            |

|         | <ul> <li>A. Coupling Capacitance Mitigation and Timing Optimization at Layer and Track Assignment</li></ul>                                                                                                                                                                                                                | 3                                            |

| II      | LAYER ASSIGNMENT FOR CROSSTALK RISK MINIMIZATION                                                                                                                                                                                                                                                                           | 5                                            |

|         | A. Introduction                                                                                                                                                                                                                                                                                                            | 7<br>10<br>13<br>14<br>16<br>19<br>21        |

| III     | TIMING-DRIVEN TRACK ROUTING CONSIDERING COUPLING CAPACITANCE                                                                                                                                                                                                                                                               | 24                                           |

|         | A. Introduction B. Preliminaries 1. Coupling Capacitance and Its Impact on Delay 2. Problem Formulation C. Algorithm 1. Constraint Graph 2. Wire Detour Induced Delay and Bipartite Graph Model 3. Sequential Ordering Problem Based Track Routing Algorithm 4. Post SOP Improvement D. Experimental Results E. Conclusion | 27<br>28<br>30<br>30<br>32<br>33<br>37<br>39 |

| IV      | COUPLING AWARE TIMING OPTIMIZATION AND ANTENNA AVOIDANCE IN LAYER ASSIGNMENT                                                                                                                                                                                                                                               | 43                                           |

| CHAPTER   | Pa                                                                                                                                                                                                                                                                                         | ıge                                                            |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|           | B. Problem Formulation                                                                                                                                                                                                                                                                     | 43<br>47<br>48<br>53<br>53<br>55<br>60<br>61<br>64<br>66       |

| V         | DICER: DISTRIBUTED AND COST-EFFECTIVE REDUNDANCY FOR VARIATION TOLERANCE                                                                                                                                                                                                                   | 70                                                             |

|           | B. Motivation Examples  1. Elmore Delay Based Analysis  2. SPICE Based Monte Carlo Simulations  C. Gate Splitting Methodology  D. Handling Dual-driver Nets  1. Short Circuit Avoidance  2. Dual-driver Delay Estimation  E. Spin-off Gate Placement  1. Problem Formulation  2. Algorithm | 70<br>73<br>76<br>79<br>81<br>81<br>82<br>85<br>85<br>85<br>91 |

| VI        | CONCLUSION AND FUTURE WORK                                                                                                                                                                                                                                                                 | 95                                                             |

| REFERENC! | ES                                                                                                                                                                                                                                                                                         | 97                                                             |

| VITA      | 10                                                                                                                                                                                                                                                                                         | 07                                                             |

# LIST OF TABLES

| TABLE |                                                                                                                         | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------|------|

| I     | Circuit specification                                                                                                   | 21   |

| II    | Experimental result: a comparison of $min\_slack$ between three different approaches as via height constraints increase | 22   |

| III   | Experimental result: CPU time (sec)                                                                                     | 22   |

| IV    | Circuit specification                                                                                                   | 41   |

| V     | Experimental results.                                                                                                   | 41   |

| VI    | CPU time                                                                                                                | 42   |

| VII   | Benchmark circuit specification                                                                                         | 69   |

| VIII  | Experimental results on coupling aware timing validated through track assignment.                                       | 69   |

| IX    | Experimental results on antenna violations and via violations                                                           | 69   |

| X     | Benchmark circuit specification                                                                                         | 92   |

| XI    | Experimental results.                                                                                                   | 92   |

| XII   | CPU time (sec)                                                                                                          | 94   |

# LIST OF FIGURES

| FIGURE |                                                                                                                           | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Example: a net passes through a four-layer routing area                                                                   | 8    |

| 2      | A top view of the cell processing order of a panel                                                                        | 13   |

| 3      | (a) net $N_i$ experiences minimum crosstalk noise. (b) net $N_i$ experiences maximum crosstalk noise                      | 17   |

| 4      | Multi-candidate approach                                                                                                  | 20   |

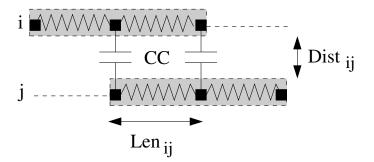

| 5      | Coupling capacitance between two wire segments $i$ and $j$                                                                | 28   |

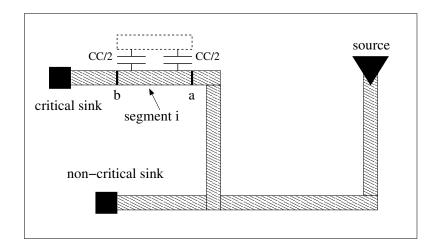

| 6      | Coupling capacitance between two wire segments                                                                            | 29   |

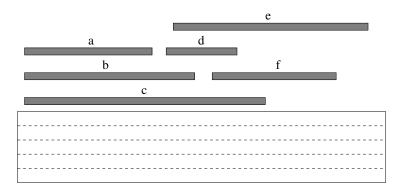

| 7      | An example of the track routing problem                                                                                   | 30   |

| 8      | A constraint graph.                                                                                                       | 31   |

| 9      | An example of detour                                                                                                      | 32   |

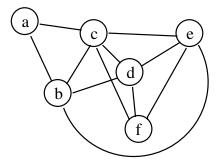

| 10     | The integration of a constraint and a bipartite graph                                                                     | 33   |

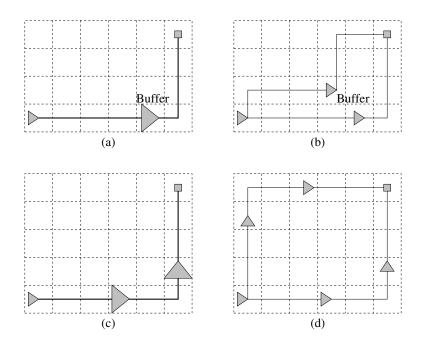

| 11     | (a) a type $\cup$ segment. (b) a type $\cap$ segment. (c) a type H segment. (d) a "don't care" segment                    | 35   |

| 12     | An example SOP tour                                                                                                       | 36   |

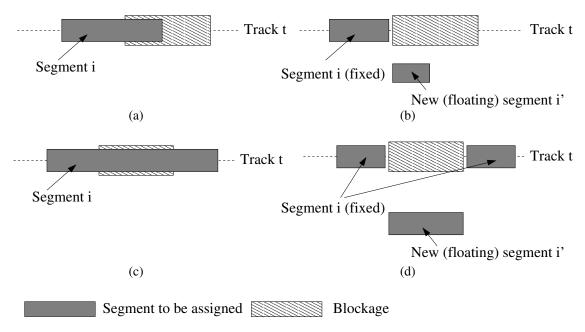

| 13     | Failed track assignment for a segment.                                                                                    | 37   |

| 14     | Segments overlapping with blockages in (a) and (c) are split to fixed and floating segments in (b) and (d), respectively. | 38   |

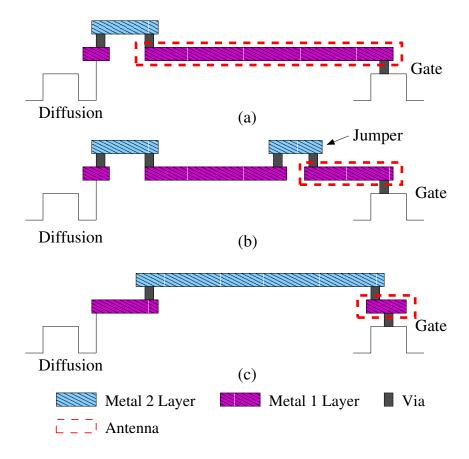

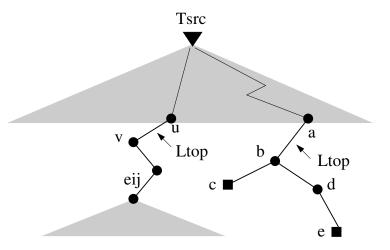

| 15     | (a)An antenna. (b) Reduce antenna length by inserting a jumper. (c) Reduce antenna length by layer assignment             | 45   |

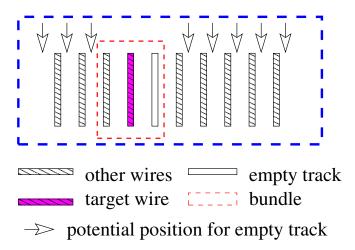

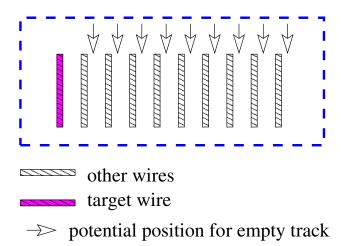

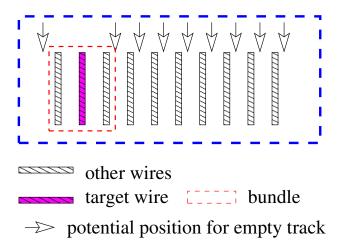

| 16     | $\pi_{k,n,1}$ case 1: the target wire has an adjacent wire on one side and an adjacent empty track on the other side      | 50   |

| FIGURE |                                                                                                                                                                                  | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 17     | $\pi_{k,n,1}$ case 2: the target wire is on a boundary track                                                                                                                     | 51   |

| 18     | $\pi_{k,n,2}$ : the target wire has two adjacent wires                                                                                                                           | 52   |

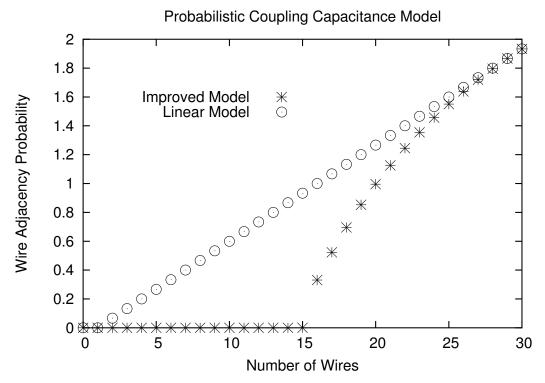

| 19     | Comparison of the improved probabilistic model with the linear model [26] when $k = 0$ to 30 and $n = 30$                                                                        | 53   |

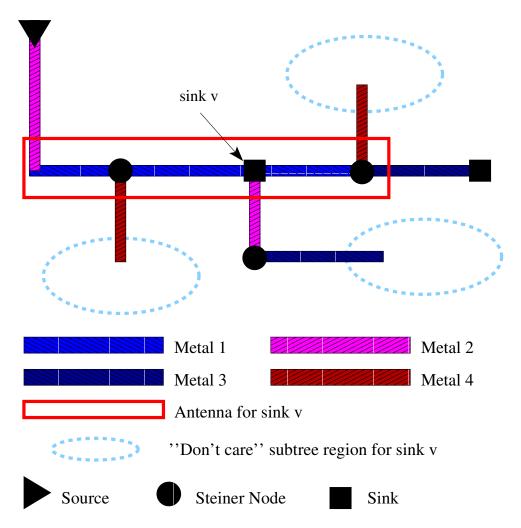

| 20     | Example: antenna for a sink $v$                                                                                                                                                  | 54   |

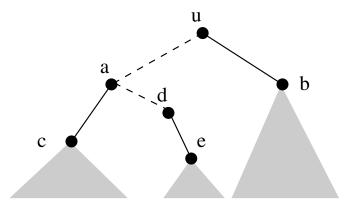

| 21     | Dashed edges cannot be assigned to $L_{top}$ and there are 3 maximal feasible branches $(a,c)+T_c$ , $(d,e)+T_e$ and $(u,b)+T_b$                                                 | 59   |

| 22     | Example for checking antenna-critical segments                                                                                                                                   | 62   |

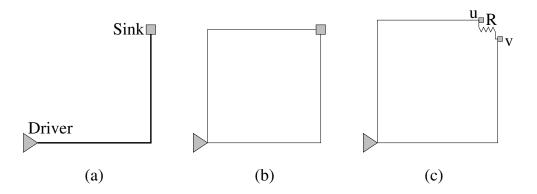

| 23     | A simple example of redundancy                                                                                                                                                   | 74   |

| 24     | Layout configurations for Monte Carlo simulations                                                                                                                                | 77   |

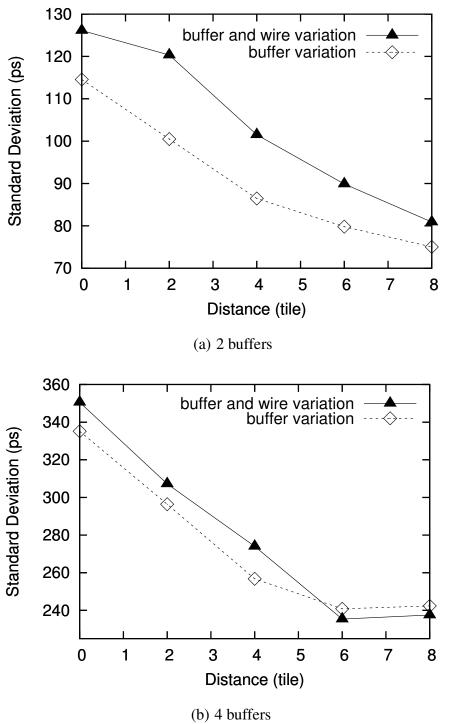

| 25     | Standard deviations of delay vs. distance between split buffers                                                                                                                  | 78   |

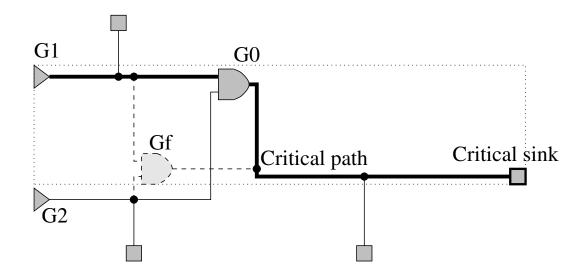

| 26     | An example of gate splitting. $G_f$ is the spin-off gate and the dotted rectangle is the feasible region                                                                         | 79   |

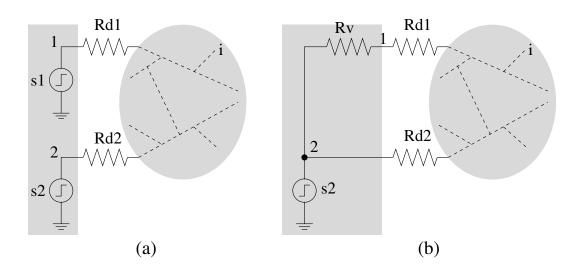

| 27     | The dual driver net in (a) can be converted to the single driver net in (b) when signal departure time $t_1$ at node 1 is no less than the signal departure time $t_2$ at node 2 | 83   |

| 28     | Main algorithm of spin-off gate placement                                                                                                                                        |      |

#### CHAPTER I

#### INTRODUCTION

A. Coupling Capacitance Mitigation and Timing Optimization at Layer and Track Assignment

Coupling capacitance (crosstalk, capacitive coupling or cross coupling) has become one of the most vital problems in DSM physical design because of (1) interconnect dominated circuit delay and (2) strong coupling effects between interconnect wires. According to ITRS roadmap [1], coupling capacitance starts to surpass wire self capacitance (including substrate capacitance and fringing capacitance) at  $0.18\mu m$  technology.

Coupling capacitance can induce two unfavored problems: (1) glitches, which introduce unnecessary signal switching and power consumption. Glitches can also cause circuit malfunction, particularly for dynamic domino circuits; (2) delays, caused by the extra capacitive load, especially when two neighboring signal nets make transitions at the same time but at different direction. In this dissertation, we propose techniques to mitigate the crosstalk-induced-delays. These techniques can be used for high-performance microprocessor and ASIC design.

Most of the previous crosstalk-related research targets at the detailed routing stage which is, however, limited by its routing flexibility. Meanwhile, crosstalk avoidance at the global routing still remains as a challenging problem [2] since the capacitive coupling relies on the neighboring wires, which are difficult to determine at an early routing stage. Between the global routing and detailed routing is the layer and track assignment - an appealing stage to tackle crosstalk problem as neighboring information between long segments of wires can be decided at this stage. There are a number of existing works [3, 4]

The journal model is IEEE Transactions on Computer-Aided Design.

on layer/track assignment, however, they are mainly routability-driven and cannot directly address the delay problem caused by coupling capacitance.

Our strategy to handle crosstalk and its induced delay can be described as two steps: (1) At layer assignment, we propose a probabilistic model to quickly calculate the estimated capacitance coupling given number of tracks and segments in a routing region. The estimated coupling is then utilized to calculate delay cost. Layer assignment is performed such that minimum timing slack among all nets is maximized. (Antenna effect, which will be discussed later, is handled simultaneously at this stage). The entire problem can be formulated as a Mixed Integer Linear Programming (MILP) problem and we provide fast heuristic to solve it effectively. (2) Track assignment assigns wire segments to routing tracks once the layer assignment is done. Similar to the layer assignment, the objective of the track assignment is to maximize the minimum slack considering both coupling capacitance and wire detours. This difficult track-routing task can be converted to a well-defined Sequential Ordering Problem (SOP). Our SOP formulation can handle detour-induced-delay and coupling-induced-delay simultaneously. Empty tracks are utilized automatically in the SOP formulation to separate highly coupled signal nets.

Experiments on benchmark circuits showed the effectiveness of both the probabilistic coupling model and our layer/track routing approach. One of the major observations from the experiments is *coupling-induced-delay* must be optimized directly during layer/track assignment, instead of merely minimizing the total amount of coupling capacitance.

#### B. Antenna Avoidance at Layer Assignment

Antenna effect occurs during the manufacturing process when conductors are fabricated from the lowest layer to the highest layer. In the manufacturing process, conductors (such as gate poly and metal), which have not been covered by a shielding layer of oxide, act like antenna that collect charges when exposed directly to the plasma [5]. If the conductors (antenna) are connected only to the transistor gates, the accumulated charge in manufacturing can damage the gate oxide through the Fowler-Nordheim (F-N) tunneling current. On the other hand, if the charges can be released through a low impedance path connected to a diffusion, gate damages can be avoided. The risk of the antenna damage to the gate oxide is proportional to the area and perimeter length of the antenna and inversely proportional to the area and perimeter length of the gate oxide.

Existing methods handling antenna effect include diode insertion [6] and jumper insertion [7]. However, both diode and jumper insertion degrade circuit performance. In particular, diodes introduces capacitive load and consumes routing resources. Jumper insertion adds vias and occupies extra space on the top metal layer.

We propose to solve the antenna effects at layer assignment, which are directly related to each other. A linear time optimal tree partitioning algorithm is adapted to solve the antenna problem during layer assignment. Compare to jumper insertion, our method results in significant via reductions. This linear time algorithm can also be applied to existing jumper insertion methods for better CAD tool performance.

#### C. Delay Variability Reduction at ECO Placement

The variability of circuit delay due to device and interconnect variations (eg. gate length, oxide thickness, threshold voltage and interconnect width variations) has become a great concern. Process variations can be further classified as inter-die and intra-die variations, where intra-die variation often exhibit spatial correlations - device variations have similar trends if placed in close proximity. A statistical timing analyzer is commonly used to find delay variations.

Our focus is to develop techniques to reduce delay variations. In recent literatures,

a number of approaches have been reported to reduce circuit delay variability through *redundancy*. In [8], cross links are inserted to a clock tree to reduce delay variations (clock skews). The work of [9] proposed a re-synthesis technique to trade extra circuitry for delay variation reduction. The use of redundancy can be also found in other works [10] for delay reduction.

Inspired by all these remarkable works, we have proposed a novel *gate splitting* methodology to reduce delay variation in the ECO placement considering spatial correlations. Our approach is integrated into the flow of an industrial place-and-route tool and tested on the ISCAS85 circuits. The experiemental results confirmed the effectiveness of our approach.

# D. Organization of the Dissertation

The rest of the dissertation is organized as follows. In Chapter II, we introduce our work on mitigating the risk of crosstalk at layer assignment. Chapter III presents our work on timing-driven track routing considering coupling capacitance. Chapter IV discusses our layer assignment heuristic considering both antenna effects and coupling capacitance. In Chapter V, we present our gate splitting work for variation tolerance. Chapter VI concludes this dissertation and discusses future work.

#### CHAPTER II

#### LAYER ASSIGNMENT FOR CROSSTALK RISK MINIMIZATION

Under modern VLSI technology, crosstalk noise is so severe that effort merely in detailed routing stage is not adequate for solving the problem and it has to be considered in earlier design stages. In this work, we propose two heuristic algorithms for crosstalk mitigation in layer assignment, which is a stage between global routing and detailed routing, so that subsequent crosstalk avoidance in detailed routing can be more attainable. The predetailed-routing crosstalk is estimated through a probabilistic model. Constraint on the amount of vias is also considered. Experimental results on benchmark circuits confirm the effectiveness of the proposed heuristics.

#### A. Introduction

When VLSI technology feature size keeps shrinking, interconnect wire width scales faster than height and consequently wires look progressively thin and tall. Moreover, higher degree of integration makes wires to be placed much closer to each other. This technology trend leads to greater and greater coupling capacitance between neighboring wires. As a result, signal switching at one net may greatly affect its neighboring wires. Such crosstalk noise [11] may cause logical malfunction or at least extra signal propagation delay.

Since 1990s, crosstalk avoidance has been a focal point of research. Early works mostly solve the crosstalk problem through detailed routing [12–16] or wire spacing [17, 18], since crosstalk is directly determined by wire adjacency and spacing. Even though the contributions of these works are indispensable, the freedom and effect of change in detailed routing and wire spacing are limited. When the crosstalk problem is severely strong, a localized optimization is not adequate any more.

A much greater flexibility on crosstalk avoidance can be obtained at the global routing

stage. However, without wire adjacency information, it is very hard to estimate crosstalk with decent accuracy at this level. Perhaps the only crosstalk driven global routing work is reported by Zhou and Wong [2]. In this work, a simplified trial layer/track assignment is employed to estimate crosstalk and guide a Lagrangian relaxation based optimization. Post global routing adjustment techniques are proposed in [19, 20]. In [19], a graph-based technique is presented to check if certain crosstalk tolerance is satisfied. The work of [20] estimated crosstalk based on expected spacing in a gridless routing. As a compromise between difficulty and flexibility, crosstalk issue is considered in crosspoint assignment [21, 22] which is a stage between global routing and detailed routing.

Layer assignment is another stage between global routing and detailed routing which is suitable for solving crosstalk problem. There are greater flexibilities on changing wire route and thereby greater capability on mitigating crosstalk in the layer assignment stage. Furthermore, the problem size of layer assignment is usually smaller than that of global routing so that it is relatively easier to be handled. An optimal minimum crosstalk layer assignment algorithm is provided in [23]. It considered only VHV channel routing and assumed the horizontal tracks had been assigned. A combined crosstalk driven layer/track assignment technique is proposed in [24]. However, this work did not evaluate crosstalk quantitatively and only attempted to enforce the rule that wires of simultaneous switching nets should not be adjacent to each other. Such formulation neglects the difference between a short adjacency and a long adjacency. Moreover, it did not consider the option to break a long wire into segments and assign them to different layers [25].

We propose layer assignment heuristics that can reduce crosstalk *risk* so that crosstalk can be handled more effectively in subsequent detailed routing. The input to the layer assignment algorithms includes a global routing result and crosstalk tolerance for each net. The objective of this work is to maximize the minimum crosstalk slack among all nets. The crosstalk slack of a net is its crosstalk tolerance minus the estimated crosstalk of this net

in the resulting layer assignment solution. The estimated crosstalk is obtained by using a probability based model. We allow a long wire to be segmented in term of global routing cells, and these segments can be assigned to different layers so that more flexibilities can be exploited for crosstalk risk reduction. Since layer switching for wires of a same net implies vias, the constraint on the number of vias is also enforced in the proposed algorithms. The major contributions of this work are:

- This is the first work that optimizes crosstalk probability in layer assignment, to the best of our knowledge. Compared with previous works that optimize crosstalk according to trial track assignment, probability based approach is better at capturing overall crosstalk risk. Further, probability based crosstalk estimation is significantly faster than trial track assignment method.

- A crosstalk bound analysis is performed in this work and the analysis result reveals that many nets can be treated as "don't cares" in the process of layer assignment.

- A *soft net prefixing* technique is introduced to exploit the "don't cares" in the context of considering via constraints. This technique can improve solution quality significantly without increasing computation cost.

The proposed algorithms are tested on benchmark circuits with different levels of crosstalk tolerances and via constraints. The experiments show encouraging results, and particularly the soft net prefixing technique yields about 20% improvement on crosstalk slacks.

#### B. Preliminaries

In previous works, crosstalk estimation at the global routing level is usually conducted with a simplified trail track/layer assignment, of which the following limitations can be observed:

(1) a simplified track/layer assignment may not reflect the actual track/layer assignment

later in the detailed routing; (2) even with a simplified track/layer assignment, it is still too time consuming in the inner loop of the optimization. In addition, the goal of the global level optimization is to reduce the risk of crosstalk by making the crosstalk-driven detailed routing easier, not to completely eliminate the crosstalk. Therefore, in this work, we employ a fast probabilistic model to estimate crosstalk noise based on the grid graph in global routing. Similar model has been reported in [26].

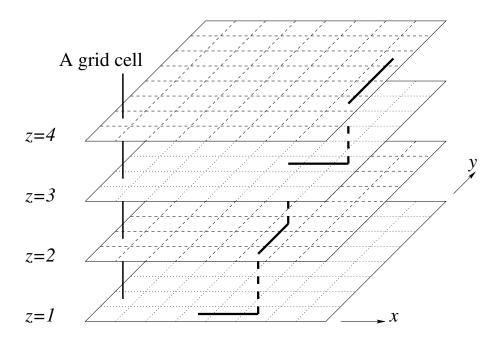

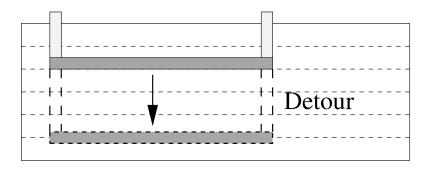

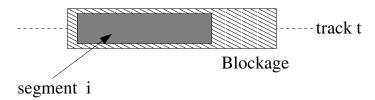

Fig. 1. Example: a net passes through a four-layer routing area.

Since our layer assignment heuristics take a global routing solution as input, we tessalate the whole routing region in a grid graph which is an array of grid cells  $\{g_1, g_2, ...\}$ . A routing solution for a net is expressed in terms of the grid cells its wiring route passes through, the detailed route within each grid cell will be specified in the detailed routing stage. When we consider multi-layer routing, each grid cell includes several layers. An example of a four layer routing is illustrated in Figure 1 where we use z as layer index. Please

note that each layer has a preferred direction for routing, either horizontally or vertically. A layer switching implies a via. Each grid cell  $g_j$  on layer z has a size  $\lambda_{jz}$  which is the cell width(height) if layer z is for horizontal(vertical) wires. A grid cell  $g_j$  can be divided into two *sub-grid-cells*. Each sub-grid-cell consists of layers with the same routing direction, i.e.,  $g_j, z = 1, 3, \ldots$  and  $g_j, z = 2, 4, \ldots$

Crosstalk or coupling capacitance between two nets is generally proportional to their adjacency length and inversely proportional to their spacing. We consider a gridded routing design where the routing track pitch is fixed. If there is at least one empty track between two wires, the crosstalk between them can be neglected for two reasons: (1) the spacing between them is relatively large and (2) a shield may be inserted in the empty track between them. If two wires occupy two adjacent tracks, then the crosstalk can be evaluated according to their adjacency length.

For a grid cell  $g_j$  on a routing layer z, the number of routing tracks and wires passing through are denoted as  $K_{jz}$  and  $u_{jz}$ , respectively. If we assume every wire segment has equal chance to occupy any of the routing track, then the probability that a wire has one other wire in its neighboring track is

$$P_{1,jz} = \frac{2(K_{jz} - u_{jz} + 1)(u_{jz} - 1)}{K_{jz}(K_{jz} - 1)}$$

(2.1)

then the probability that a wire has two other wires in its neighboring track is

$$P_{2,jz} = \frac{(u_{jz} - 1)(u_{jz} - 2)}{K_{iz}(K_{iz} - 1)}$$

(2.2)

Similar conclusion is reached in [26], thus we skip the derivation here. The expected crosstalk is

$$\chi_{jz} = (P_{1,jz} + 2P_{2,jz})\lambda_{jz} = 2\lambda_{jz}(u_{jz} - 1)/K_{jz}$$

(2.3)

Under this probabilistic model, we assume that a horizontal/vertical wire segment always

occupies an entire track of a grid cell in full length. If a horizontal/vertical wire segment is shorter than the grid cell width/height, the above crosstalk estimation introduces pessimism. However, this pessimism compensates well for the optimism due to the neglection of jogs that may be brought to a straight wire segment in detailed routing. Even though we consider gridded routing, our work can be extended to gridless routing easily.

#### C. Problem Formulation

For each net  $N_i$ , we assume there is a crosstalk tolerance  $\tau_i$  given. Normally, a timing critical net has a low crosstalk tolerance and a non-critical net has a high tolerance. A crosstalk slack is  $\phi_i = \tau_i - \chi_i$  where  $\chi_i = \sum_{j:N_i \in g_j} \sum_{z:N_i \in z} \chi_{jz}$  is the total crosstalk for net  $N_i$ . For a long wire spanning multiple grid cells, we allow it to be broken into several segments in terms of grid cells. Each segment may be assigned to a different layer. If two segments in two neighboring cells are assigned to different layers, a via is incurred. The height of the via depends on the number of layer switching, i.e., if a net switches from layer  $z_1$  to  $z_2$ , then the via height is proportional to  $|z_1 - z_2|$ . Sometimes we need such layer switching to reduce crosstalk risk, but we need to restrain such layer switching because of the vias. We define total via height  $via_{jk}$  as the summation of via heights of all nets between two neighboring grid cells  $g_j$  and  $g_k$ .  $via_{jk}$  is bounded by a user defined total via height constraint  $\psi_{jk}$ .

Besides their wire adjacency length, the crosstalk between two nets also depends on their switching activities. Two nets with simultaneous opposite signal switching need to be separated. A timing critical net should be placed away from a net that switches frequently. These switching activity related issues are not directly included in the formulation here for two reasons: (1) considering switching activities requires a great number of variables to specify constraint between every pair of nets in the same grid cell; (2) the primary goal in

layer assignment is to reduce the crosstalk risk, not to solve everything completely. Timing critical net will be placed into less congested layer so that there will be greater chance it is separated by a shield. The problem formulation is described as follows.

Layer Assignment for Minimum Crosstalk Risk(LA-MinCR): Given a grid graph composed by a set of grid cells  $\{g_1, g_2, ...\}$ , number of routing tracks  $K_{jz}$  for each grid cell  $g_j$  on layer z, total via height  $\psi_{jk}$  between two neighboring grid cells  $g_j$  and  $g_k$ , a set of nets  $\{N_1, N_2, ...\}$  routed in terms of grid cells, and crosstalk tolerance  $\tau_i$  for each net  $N_i$ , assign each net in each grid cell to a specific layer such that the minimum expected crosstalk slack among all nets is maximized while the number of wires in each grid cell on each layer does not exceed its corresponding number of tracks and total via heights between two grid cells is no greater than the given bound.

The crosstalk estimation in this stage is based on probability estimation and the actual crosstalk after detailed routing may deviate from this estimation. Thus, we attempt to maximize the slack instead of just satisfying the tolerance so that there could be a maximum safety margin to cushion any deviations from the detailed routing solutions. Throughout this chapter, we use the term  $min\_slack$  to represent the minimal slack among all nets in a circuit and our goal is to maximize  $min\_slack$ .

If we let  $x_{ijz}$  be a decision variable to tell if net  $N_i$  in grid cell  $g_j$  is assigned to layer z, then the complete LA-MinCR problem can be formulated as a mixed 0-1 and non-linear programming problem as follows.

Maximize:  $\phi$

Subject to:

$$\phi + \sum_{j:N_i \in g_i} \sum_{\forall z} \frac{2\lambda_{jz} \left(\sum_{l:N_l \in g_j} x_{ljz} - 1\right)}{K_{jz}} x_{ijz} \le \tau_i, \forall N_i$$

(2.4)

$$\sum_{i:N_i \in g_j} x_{ijz} \le K_{jz}, \forall g_{j,z}$$

(2.5)

$$\sum_{i:N_i \in g_j, N_i \in g_k} |\sum_{\forall z} z x_{ijz} - \sum_{\forall z} z x_{ikz}| \le \psi_{jk}$$

$$j, k: g_j \text{ adjacent to } g_k$$

$$(2.6)$$

$$\sum_{\forall z} x_{ijz} = 1, \forall N_i; g_j : N_i \in g_j$$

(2.7)

$$x_{ijz} \in \{0, 1\}, \forall N_i, g_j, z$$

(2.8)

the sum of total estimated crosstalk and the slack variable  $\phi$  should never exceed the crosstalk tolerance for each net. The next inequality (2.5) states that the number of wires on each layer of each grid cell is no greater than the number of tracks or wiring capacity. In constraint of (2.6),  $\sum_{\forall z} zx_{ijz}$  tells the layer index number of net  $N_i$  in grid cell  $g_j$  in terms of decision variables. Inequality (2.7) is the exclusivity constraint ensuring that a wire is assigned only to one layer. The last constraint implies that this is an integer programming problem which is generally NP-hard. The computation cost for directly solving this non-linear integer programming problem is prohibitive since it would require tremendous CPU time and memory.

In this chapter, we propose two efficient heuristic algorithms to solve the LA-minCR problem. The first approach (LA-MinCR-Solve) is a greedy heuristic, i.e., layer assignment is performed on each of the sub-grid-cells one after another. Once a sub-grid-cell is processed, its layer asssignment is fixed. The second heuristic (LA-MinCR-Solve<sup>+</sup>) extends LA-MinCR-Solve by using a multi-candidate approach to better exploit the solution space. At the same time, a simple yet effective pruning technique is applied to make the multi-candidate approach more efficient. In this work, our heuristic algorithms are focused on a four-layer model, but they can be extended to handle models with more than four

layers.

# D. Algorithm

In both of our LA-MinCR-Solve and LA-MinCR-Solve<sup>+</sup> heuristics, we perform layer assignment on a panel-by-panel and cell-by-cell basis. We define a panel as an entire row/column on the routing area. A row panel consists of horizontal layers and a column panel consists of vertical layers. Within a panel, sub-grid-cells are processed cell by cell. All sub-grid-cells in an entire panel need to be processed before we proceed to the next panel following the order of the panel/cell criticality we defined as follows.

**Definition 1:** The criticality  $\alpha_{g_i}$  of a sub-grid-cell  $g_i$  is defined as the number of horizontal/vertical wire segments in  $g_i$ .

**Definition 2:** The criticality  $\alpha_{s_i}$  of a horizontal/vertical panel  $s_i$  is equal to the value of the maximal  $\alpha_{g_i}$  among all sub-grid-cells  $\{g_1, g_2, ..., g_i, ...\}$  in panel  $s_i$ .

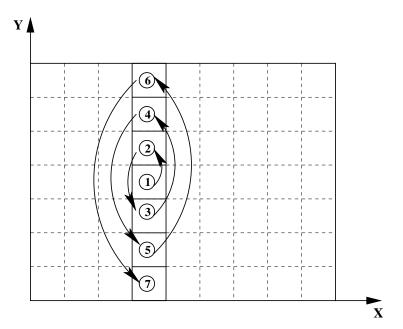

Fig. 2. A top view of the cell processing order of a panel.

For each panel, we first process the most critical sub-grid-cell in it. Then, we use this particular sub-grid-cell as a starting point and continue to process the remaining cells in an alternate direction towards both ends of the panel. For instance, in Figure 2, cell 1 is the most critical sub-grid-cell in this panel and the cell processing order is represented by the increasing number on each of the sub-grid-cells in this panel. This continuous cell-by-cell processing order prevents via height constraint deadlocks and facilitates our multicandidate approach as described in section 3. Using congestion condition as the processing order alllows us to reach as many nets as possible in the early stage to reduce the chance of being trapped in local optima.

## 1. Greedy Heuristic (LA-MinCR-Solve)

Before we proceed to perform layer assignment on a single sub-grid-cell  $g_j$ , we need to the know the following information about  $g_j$ : track capacity K at each layer, nets in  $g_j$  and their current crosstalk slack  $\phi_i$ . It is important to note that we use  $\phi_i$ ,  $\forall N_i$  here to represent a gradually reduced slack value during the progress of the layer assignment.

In order to maximize the minimum crosstalk slack for a sub-grid-cell  $g_j$ , nets with greater crosstalk slack need to be placed on a more congested layer and nets with less crosstalk slack can be placed on a less congested layer. For each sub-grid-cell  $g_j$ , we sort the nets into a sequence  $\{N^1,N^2,...,N^q\}$  in non-increasing order of their crosstalk slack. Then the layer assignment for this sub-grid-cell becomes to find an index p such that this net sequence is partitioned into two subsequence  $S_{g_j}^1 = \{N^1,N^2,...,N^p\}$  and  $S_{g_j}^2 = \{N^{p+1},N^{p+2},...,N^q\}$  with each subsequence corresponding to a layer. We select an index p such that the minimal slack among all nets in  $g_j$  is maximized. Furthermore, p must be selected in the range of  $[max(1,q-K),min(K,q)](q \leq 2K)$ . Otherwise, track capacity constraint K will be violated. After such a partitioner p is selected, we need to verify if this net partitioning solution satisfies the via height constraint between  $g_j$  and its

neighbore  $g_k$ , where a layer assignment is fixed previously. We represent the fixed layer assignment for  $g_k$  in a similar way by using subsequences  $S_{g_k}^1$  and  $S_{g_k}^2$ . A via occurs only if a net passing through both  $g_j$  and  $g_k$  is placed on different layers. Given  $S_{g_j}^1$  and  $S_{g_j}^2$  obtained from the initial net partitioning, we first check if the current total via height  $via_{jk}$  between  $g_j$  and  $g_k$  is greater than the user defined total via height constraint  $\psi_{jk}$ . If yes, we feed  $S_{g_j}^1$  and  $S_{g_j}^2$  to the via enforcement procedure (as shown in Algorithm 1). Otherwise, we skip this procedure.

# Algorithm 1: Via constraint enforcement

```

1: while via_{jk} > \psi_{jk} do

choose a net N_i \in S^1_{g_j} and S^2_{g_k}, if such net doesn't exist, N_i = null; choose a net N_j \in S^2_{g_j} and S^1_{g_k}, if such net doesn't exist, N_j = null; if (N_i \neq null \text{ and } |S^2_{g_j}| + 1 \leq \text{track capacity } K) \text{ OR } (N_j \neq null \text{ and } |S^1_{g_j}| + 1 \leq \text{track capacity } K)

3:

4:

track capacity K) then S_{g_j}^2 \leftarrow N_i or S_{g_j}^1 \leftarrow N_i depends on feasibility and which switching produces greater minimal slack;

5:

6:

via_{ik} \leftarrow via_{ik} - 2;

7:

(only swapping nets between S_{g_j}^1 and S_{g_j}^2 simultaneously can reduce vias) if (N_i \neq null \text{ AND } N_j \neq null) then S_{g_j}^2 \leftarrow N_i and S_{g_j}^1 \leftarrow N_j; via_{jk} \leftarrow via_{jk} - 4; else if (N_i \neq null \text{ AND } N_j = null) then

8:

9:

10:

11:

12:

eise if (N_i \neq nutt \text{ AND } N_j = nutl) then find a net N_l \in S_{g_j}^2 and N_l \notin g_k; S_{g_j}^2 \leftarrow N_i and S_{g_j}^1 \leftarrow N_l; via_{jk} \leftarrow via_{jk} - 2; else if (N_i = nutl \text{ AND } N_j \neq nutl) then find a net N_l \in S_{g_j}^1 and N_l \notin g_k; S_{g_j}^1 \leftarrow N_j and S_{g_j}^2 \leftarrow N_l; via_{jk} \leftarrow via_{jk} - 2; end if

13:

14:

15:

16:

17:

18:

19:

20:

end if

21:

end if

22: end while

```

In Algorithm 1, whenever we have multiple candidate nets to choose from for a layer switching, we select one that can produce greater minimum slack. The via enforcement procedure ends whenever the via height constraint is satisfied. Then we fix the layer as-

signment for  $g_i$  and update the crosstalk slack  $\phi_i$  for each net  $N_i$  in  $g_j$ . The same net partitioning and via enforcement procedure is repetitively utilized for layer assignment on the remaining sub-grid-cells. The via enforcement procedure only takes O(K) time. The net partitioning at each sub-grid-cell takes O(KlogK) time because its time complexity is bounded by the sorting procedure. The overall time complexity of LA-MinCR-Solve is bounded by O(GKlogK), where G is the total number of sub-grid-cells.

## 2. Crosstalk Bound Analysis and Net Pre-fixing

Since large number of nets are involved in a circuit, we would like to see if certain wire segments can be pre-fixed without affecting or even producing better  $min\_slack$  solution. By carefully examing the problem, we have the following observations.

For an individual net  $N_i$ , its maximum and minimum estimated crosstalk can be represented by  $\chi_i^-$  and the  $\chi_i^+$ , respectively. If we define  $G_i = \{g_{i1}, g_{i2}, ..., g_{ij}, ...\}$  as the set of sub-grid-cells on the route of net  $N_i$ ,  $\chi_i^-$  can be obtained by summing up the worse-case crosstalk that net  $N_i$  can experience at each  $g_{ij}$ . This is done by moving as many wires as possible to the same layer where  $N_i$  is placed under the limit of the track constraint. Similarly,  $\chi_i^+$  is obtained by summing up the best-case crosstalk that net  $N_i$  can experience at each  $g_{ij}$  and this is done by moving away as many wires as possible from the layer where  $N_i$  is placed. Therefore, we can see that  $\phi_i$  is bounded by  $[\Gamma_i^-, \Gamma_i^+]$ , where  $\Gamma_i^+ = \tau_i - \chi_i^+$  and  $\Gamma_i^- = \tau_i - \chi_i^-$  Please note that we always put the most congested layer close to the bottom. For horizontal wires, the most congested layer is layer 1. For veritcal wires, it is layer 2.

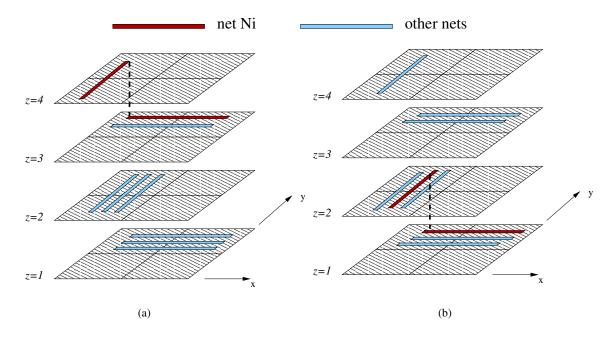

Now let us look at a simple example, as shown in Figure 3. A net  $N_i$  with  $\tau_i=400$  routes through a  $2\times 2$  routing areas with each grid cell has 4 layers. Each of the grid cell has a size of  $100\times 100$  and each layer includes 3 tracks. We first calculate  $\Gamma_i^+$  by placing all wire segments of  $N_i$  to the higher layer for each grid cell it passes through and push

Fig. 3. (a) net  $N_i$  experiences minimum crosstalk noise. (b) net  $N_i$  experiences maximum crosstalk noise.

as many other wires as possible to lower layer, as illustrated in Figure 3(a). Based on our probability model (Equation 2.3), the estimated crosstalk noise  $\chi_i^+$  for  $N_i$  is  $100\times 2(1-1)/3+100\times 2(1-1)/3+100\times 2(2-1)/3+100\times 2(2-1)/3=132$ . Therefore,  $\Gamma_i^+=400-132=268$ . Similarly, the estimated crosstalk noise  $\chi_i^-$  for net  $N_i$  in Figure 3(b) is  $100\times 2(3-1)/3+100\times 2(3-1)/3+100\times 2(3-1)/3+100\times 2(3-1)/3=533$  and  $\Gamma_i^-=400-533=-133$ . As a result,  $\phi_i$  will always be in [-133,268] under any layer assignment solutions.

If we denote  $\Gamma_{min}^+$  as the minimal of  $\Gamma_i^+, \forall N_i$ . We can reach following conclusion:

**Lemma 1:** Maximal min\_slack is no greater than  $\Gamma_{min}^+$  and a net  $N_i$  can be considered as a non-critical net if  $\Gamma_i^- \geq \Gamma_{min}^+$ .

It is important to note that when calculating  $\Gamma_i^-$  and  $\Gamma_i^+$ , we focus our attention to an individual net  $N_i$  while treating other nets only as track occupiers. Therefore,  $\Gamma_{min}^+$  only provides a upper bound for  $min\_slack$ . We can claim that an optimal solution is achieved

if the maximal  $min\_slack$  we find is equal to  $\Gamma_{min}^+$ . But it is not true vice versa.

It is our intention to pre-fix all non-critical nets to the lower layer so that crosstalk noise can be mitigated at the higher layer for critical nets. However, non-critical nets can account for a large portion of total nets in a circuit (As shown in TABLE VII), hence not all of them can be pre-fixed to the lower layer because of the track capacity constraint at each sub-grid-cell. Also, directly(hard) pre-fixing non-critical nets to certain layers can cause via constraint deadlocks if we use a cell-by-cell based layer assignment. To overcome these difficulties, we propose a technique called soft pre-fixing by taking advantage of our net partitioning technique. The basic idea of the soft pre-fixing is to increase the initial crosstalk slack  $\tau_i$  for non-critical nets to  $\tau_i = \Phi + \Gamma_i^-$ , where  $\Phi$  is an extremely large value. With our net partitioning technique, this modification allows a non-critical net to be assigned towards the lower layer at each sub-grid-cell it passes through. We call this method a soft net pre-fixing since we don't directly provide which layer a non-critical net is assigned to. Adding  $\Gamma_i^-$  as an offset to  $\Phi$  provides two advantages: (1) it increases the minimal slack among non-critical nets. (2) it allows a non-critical net to keep the same relative ordering among other non-critical nets so that they have the tendency to remain in the same layer at neighboring sub-grid-cells. As a result, layer switchings between neighboring sub-grid-cells for non-critical nets are reduced and thereby vias can be utilized by critical nets to achieve greater min\_slack.

Soft pre-fixing plays an important role when used in conjunction with our net parititioning technique. It incorporates global behavior of nets in terms of their crosstalk slack into the localized optimization, as a result, soft pre-fixing is guaranteed to achieve better global solution.

# 3. A Multi-candidate Approach (LA-MinCR- $Solve^+$ )

To furthur reduce the chance of local optima, we extend our LA-MinCR-Solve by perturbating extra candidate solutions at each sub-grid-cell. We call it a multi-candidate approach. Together with the original LA-MinCR-Solve solution, the perturbated solutions are kept for each sub-grid-cell during the layer assignment process. This additional perturbation makes the solution space better exploited, in contrary to LA-MinCR-Solve where only a single solution is retained for each sub-grid-cell. A solution tree is generated and expanded during the progress of this muti-candidate approach, with the first sub-grid-cell being processed as its root. A thread on the solution tree corresponds to a complete layer assignment solution for all sub-grid-cells having been processed so far. Upon completion of tree construction (that's when all sub-grid-cells are processed), the best thread with the maximal min\_slack is picked and a backward traversal is utilized to perform the actual layer assignment.

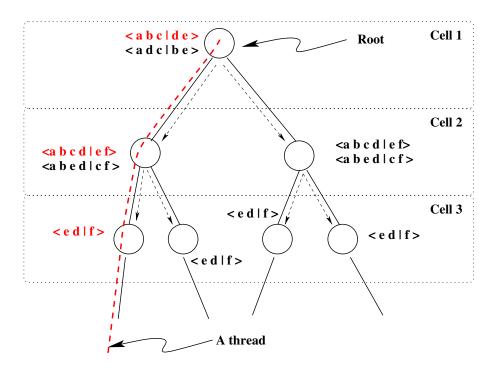

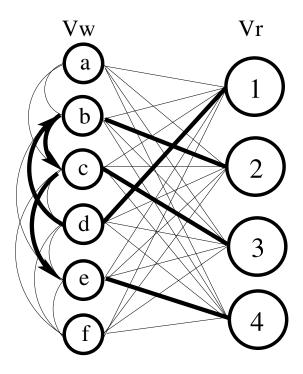

Figure 4 shows an example of the multi-candidate approach. Each tuple in the graph corresponds to a layer assignment solution for a sub-grid-cell with each letter representing a net. The first subsequence in the tuple represents nets that are assigned to the lower layer and the second subsequence represents nets that are assigned to the higher layer. Arrows in the graph indicate the growing direction of the solution tree. At each sub-grid-cell, the perturbation process is accomplished by swapping nets between different layers based on the initial net partitioning result. Each of the perturbated tuples should perform no worse than the original tuple with respect to  $min\_slack$ , and they are also subject to the via height constraint enforcement as described in Algorithm 1. At each sub-grid-cell, we allow a maximum of v candidate solutions.

Since explicit multi-candidate perturbation is involved, a pruning technique is needed to remove non-promising threads during the perturbation process to avoid number of tuples

Fig. 4. Multi-candidate approach.

being exponentially increased. We define a upper limit  $\gamma$  as the maximal number of total threads we can retain during the expansion of the solution tree. If more than  $\gamma$  threads are encoutered, we must eliminate the exceeding threads by using the following pruning procedure.

- 1: sort the tuples with non-decreasing order according to its  $min(\phi_i), \forall N_i$

- 2: remove tuples with lower crosstalk slack  $\phi_i$  until the maximum thread number  $\gamma$  is satisfied.

- 3: if there are ties among tuples with the same  $min(\phi_i), \forall N_i$ , remove those that have lower  $secondary\ min(\phi_i), \forall N_i$ .

The perturbation process at each sub-grid-cell takes O(v) time. The overall time complexity of the LA-MinCR- $Solve^+$  is bounded by  $O(Gv(KlogK)(\gamma log\gamma))$ .

## E. Experimental Results

We have implemented both LA-MinCR-Solve and LA-MinCR- $Solve^+$  in GNU C on a Linux platform with a 2.4GHz Pentinum IV processor and 640MB memory. We use the following benchmark circuits to test our heurisites: apte, a9c3, ac3, playout and xc5. Both benchmarks and their global routing solutions are obtained from authors of [27]. Crosstalk tolerances are generated randomly but we have verified our heuristics with different levels of crosstalk tolerances. Table I lists the specifications, slack upper bound  $\Gamma_{min}^+$  and the percentage of non-critical nets for each benchmark circuit based on Lemma 1.

$\Gamma_{min}^+$ no. of circuit no. of no. of non-critical grid cells non-critical net name nets net percentage  $\overline{35} \times 33$ 508 a9c3 1148 955 83% 5905 ac3  $27 \times 28$ 200 33% 65  $23 \times 22$ 77 35 45% 5801 apte playout  $\overline{42} \times 36$ 1294 832 64% 777  $42 \times 39$ 975 69% 2611 xc5 674

Table I. Circuit specification.

Since no previous work is close to our formulation, we tested our heuristics with the following three different approaches, as shown in Table II. (1) LA-MinCR-Solve with no soft pre-fixing. (2) LA-MinCR-Solve with soft pre-fixing. (3) LA-MinCR- $Solve^+$  with soft pre-fixing and maximum threads  $\gamma=100$  and v=3. We use a uniform via height constraint for each boundary between two neighboring sub-grid-cells and we vary the total via height constraint by 2,4,6 and infinity (no via constraint). As we expected, when via height constraint is relaxed,  $min\_slack$  increases with approach (3) outperforming both (1) and (2). On the average, approach (2) increases  $min\_slack$  by 20% compare to approach (1), and approach (3) increases  $min\_slack$  by 6% compare to approach (2). Table III lists the CPU time averaged over different via height constraints for each benchmark circuit.

Table II. Experimental result: a comparison of  $min\_slack$  between three different approaches as via height constraints increase.

|                             |             | a9c3  | ac3  | apte | playout | xc5  |

|-----------------------------|-------------|-------|------|------|---------|------|

| (1)                         | via ht.=2   | -2337 | 4817 | 5291 | -175    | 1738 |

| LA-MinCR-Solve              | via ht.=4   | -1473 | 4789 | 5511 | 49      | 2031 |

| w/o prefix                  | via ht.=6   | -1185 | 4993 | 5731 | 385     | 2423 |

|                             | via ht.=Inf | -1041 | 4993 | 5801 | 385     | 2611 |

| (2)                         | via ht.=2   | -500  | 4874 | 5291 | 329     | 2074 |

| LA-MinCR-Solve              | via ht.=4   | -68   | 5189 | 5511 | 329     | 2367 |

| w/ soft prefix              | via ht.=6   | 220   | 5189 | 5731 | 385     | 2535 |

|                             | via ht.=Inf | 508   | 5189 | 5801 | 777     | 2611 |

| (3)                         | via ht.=2   | -212  | 4874 | 5511 | 385     | 2311 |

| LA-MinCR-Solve <sup>+</sup> | via ht.=4   | 76    | 5189 | 5731 | 385     | 2367 |

| w/ soft prefix              | via ht.=6   | 364   | 5189 | 5801 | 441     | 2535 |

| (max. 100 threads)          | via ht.=Inf | 508   | 5189 | 5801 | 777     | 2611 |

Table III. Experimental result: CPU time (sec).

| circuit | avg. LA-MinCR-Solve | avg. LA-MinCR-Solve <sup>+</sup> |

|---------|---------------------|----------------------------------|

| name    |                     | (max. 100 threads)               |

| a9c3    | 1.14                | 53.15                            |

| ac3     | 0.07                | 7.89                             |

| apte    | 0.02                | 1.68                             |

| playout | 1.77                | 69.00                            |

| xc5     | 1.75                | 53.19                            |

In particular, CPU time for LA-MinCR-Solve is averaged over both approach (1) and (2) since little timing difference is observed between these two approaches.

#### F. Conclusion

In this chapter, we have proposed a new approach for crosstalk mitigation at the layer assignment stage between global routing and detailed routing in VLSI physical design. This approach aims to discover and reduce crosstalk risk at the pre-detailed-routing level

and the crosstalk noise is estimated based on a probabilistic model. We formulate our problem as an integer convex programming problem and provide two heurisites to solve it efficiently. Experimental results confirmed the effectiveness of our heuristics on benchmark circuits.

#### **CHAPTER III**

TIMING-DRIVEN TRACK ROUTING CONSIDERING COUPLING CAPACITANCE

Track routing is a step between layer assignment and detailed routing. In this chapter, we

propose a coupling aware timing driven track routing heuristic. Given a global routing

solution and timing constraint for each net, major trunks of wire segments are assigned

to routing tracks such that the minimum timing slack among all nets is maximized. Delay penalties from both coupling capacitance and wire detour are considered in a unified

graph model. The core problem is formulated and solved as a Sequential Ordering Problem

(SOP). Routing blockages are handled in a post processing procedure. The experimental

results on benchmark circuits show that the effect of coupling capacitance on timing is

significant and the proposed heuristic results in greater improvement on coupling aware

timing compared with other approaches.

#### A. Introduction

The sustained VLSI technology scaling leads to two trends: (1) interconnect dominated circuit delay and (2) strong coupling effects between interconnect wires. A tremendous amount of work has been reported on either timing driven interconnect routing [28–32] or coupling noise avoidance [2,4,13,15–20,22,24,33,34]. However, very few works address the closely related timing and coupling issue at the same time. In most of the timing driven routing works, the coupling capacitance induced delay is neglected. In the coupling noise avoidance works, efforts are made to minimize either total coupling capacitance or violations on coupling constraints, but the impact on timing is not considered.

In ultra-deep submicron technology, the coupling capacitance starts to dominate self capacitance which includes substrate capacitance and fringing capacitance. Therefore, coupling capacitance greatly affects wire delay and can no longer be ignored in a timing driven

routing. Merely minimizing the total coupling capacitance is not adequate either, since the same amount of coupling capacitance may cause a different value of delay depending on its location. Therefore, the impact of coupling capacitance on delay needs to be handled directly in a timing driven routing. Considering coupling capacitance in timing driven routing presents a great challenge, since the delay estimation has to consider wire adjacencies in addition to individual wire routes. The simplest version of routing problem, which handles only routability and only 2-pin nets, is an NP-complete problem. Even when coupling capacitance is neglected and the delay of each net can be estimated independently, optimizing timing in routing is a notoriously difficult problem [30–32]. Including the coupling effect brings complex inter-wire dependencies to the complicated routing procedure.

Because of the high complexity, a routing problem is usually solved in two stages: global routing and detailed routing. In global routing, the entire routing area is tessellated into an array of rectangle global cells and each net is routed in term of the global cells. The detailed route within each cell is determined in subsequent detailed routing. In detailed routing [13,16], the freedom to make route change is restricted to a small region and therefore the improvement on timing or coupling is limited. In contrast, global routing allows much greater freedom and flexibility on optimizing timing and coupling. However, the absence of wire adjacency information makes the coupling capacitance estimation hard to be obtained. A methodology level approach on coupling aware timing driven global routing is suggested in [35].

Recently, another routing stage - track routing - is proposed [3,24,34] to be performed between global routing and detailed routing. Taking a global routing result, a track router assigns major trunks of wire segments to routing tracks in a row(column) of global cells. Please note that the track assignment in a track routing is different from the track assignment in a detailed routing which only handles nets within one global cell. Track routing is an appealing stage for handling the coupling issue, as both the wire adjacency information

and decent freedom of route change are available. In addition, a track routing does not need to deal with complicated design rules as in detailed routing so that it can be focused on the timing and routability issue. In [3], Batterywala *et al.* modeled the track routing as a weighted bipartite matching problem, however their work is mainly routability driven and does not handle coupling and timing. In [4,24,34], coupling noise is avoided without considering timing. A similar stage between global routing and detailed routing is crosspoint assignment [21,22]. When a wire route goes from one global cell across a boundary to another global cell, a crosspoint assignment determines the crossing location on the boundary. In [21], a coupling aware timing driven crosspoint assignment heuristic is proposed. This is a greedy approach that assigns wire segments sequentially in an order of timing criticality. After initial assignment, wire spacings are tuned to further reduce coupling capacitance for timing critical nets.

In this chapter, we propose a new heuristic on timing driven track routing considering coupling capacitance. The objective is to find a feasible track assignment such that the minimum timing slack among all nets is maximized. In timing estimation, delay penalties due to both coupling capacitance and wire detour are counted. The heuristic proceeds in a panel (a row or a column of global cells) by panel manner. The track assignment problem within each panel is modeled by graphs. The problem of minimizing coupling induced timing penalty is equivalent to finding the minimum weight Hamiltonian path in a clique. Minimizing timing penalty due to wire detour can be solved via the minimum weight matching in a bipartite graph. The hard problem of minimizing both timing penalties simultaneously is formulated and solved as a Sequential Ordering Problem(SOP) [36]. A post processing step is performed to further improve timing and routability. Our heuristic is designed primarily for global wires and is more effective on upper layers where less pre-fixed local wires exist, even though it is capable of handling routing blockages. A major contribution of this work is that timing is optimized directly with consideration of both detour and

coupling induced delay. Experimental results on benchmark circuits demonstrate that our heuristic can remarkably improve coupling aware timing performance than other coupling aware approaches.

#### B. Preliminaries

## 1. Coupling Capacitance and Its Impact on Delay

Given two wire segments i and j, as shown in Figure 5, the coupling capacitance between them can be expressed as follows [2, 21]:

$$CC(i,j) = \alpha \cdot f_{ij} \cdot \frac{Len_{ij}}{Dist_{ij}^{\beta}}$$

(3.1)

where  $Len_{ij}$  is the coupling length,  $Dist_{ij}$  is the wire spacing between i and j,  $\alpha$  and  $\beta$  are technology dependent constants and  $f_{ij}$  is the *switching factor* for i and j. A switching factor is a real number between 0 and 1 according to [2] that indicates switching activity relations between two nets. The worst case coupling occurs when two adjacent signal nets make transitions at the same time but at opposite direction. For this worst case coupling, the switching factor between the two wires is 1. On the other hand, if two adjacent wire segments switch at the same time and at the same direction, the switching factor is 0. Any other switching activity relations should fall into the range between these two cases. Other definitions for the switching factor can be adopted easily to the works in this dissertation. As the spacing between two adjacent wire segments increases, the coupling capacitance between them decreases rapidly since emperical experiments in [20] showed  $\beta$  is approximately the constant of 2. Therefore, for track/detailed routing with fixed pitch, it is reasonable to assume that coupling capacitance occurs only between segments in adjacent tracks. This model is used to estimate the coupling capacitance throughout this dissertation.

Once the amount of coupling capacitance is calculated, the coupling induced delay

Fig. 5. Coupling capacitance between two wire segments i and j.

to each sink of a net can be found easily. Same as many other timing driven routing works [21, 31], the Elmore delay model [37] is employed for estimating wire delay in this dissertation. Even though the Elmore model is sometimes inaccurate, it has high fidelity [38] that can provide proper guidance for a combinatorial optimization. Moreover, layer/track assignment is a relatively early stage of wire timing optimization which allows and needs simple models. A more accurate model can be employed at later wire timing optimization stages to fine tune the coupling aware timing.

In Figure 6, we use a simple example to illustrate the coupling induced delay. Consider a net N and a wire segment  $i \in N$ . If segment i has an estimated coupling capacitance of CC, the extra delay due to CC for the critical sink of N is  $R_{sa} \cdot CC + R_{ab} \cdot \frac{CC}{2}$  where  $R_{sa}$  is the path resistance from the source to point a and  $R_{ab}$  is the resistance between a and b. Please note that the same amount of coupling capacitance may cause different amount of delay depending on the coupling location.

## 2. Problem Formulation

Since our track routing takes a global routing solution as input, the whole routing region is tessellated into a grid of global cells (GCs) { $g_{11}, g_{12}, ...g_{21}, g_{22}, ...$ }. A global routing solution for a net  $N_i$  is expressed in terms of the GCs that the wiring route of the net passes through. A complete row (column) of GCs is called a *panel*. In track routing, only wire

Fig. 6. Coupling capacitance between two wire segments.

segments whose lengths are at least one GC are considered. All the other small segments are handled in detailed routing. In gridded routings, each horizontal(vertical) panel consists of a set of  $K_p$  uniformly spaced horizontal(vertical) routing tracks. Some part of a track may be pre-occupied by certain blockages and cannot accommodate additional wire segments.

Given a net  $N_i$  with source node i, the timing slack  $s_{ik}$  for a sink k of the net is  $s_{ik} = \tau_k - \chi_{ik}$  where  $\tau_k$  is a timing constraint or required arrival time at sink k and  $\chi_{ik}$  is the delay from source i to k. The sink with the minimal  $s_{ik}$  is called the critical sink of  $N_i$  and we use  $S^i_{min} = min(s_{ik}), \forall k \in sinks \ of \ N_i$  to represent the minimum timing slack of net  $N_i$ . Throughout this chapter, we will use  $min\_slack$  as an alternative to represent minimum timing slack. The problem formulation is described as follows.

Coupling Aware Timing-Driven Track Routing Problem: Given an array of panels  $\{p_1, p_2, ...\}$  each of which is composed of  $K_p$  routing tracks with certain blockages, a set of nets  $\{N_1, N_2, ..., N_i, ...\}$  each of which is composed of segments  $\{N_{i1}, N_{i2}, ..., N_{ij}, ...\}$ , and timing constraints for each net, assign each segment  $N_{ij}$  to a track of its corresponding panel p in a non-overlapping manner such that the minimal slack among all nets is

maximized.

## C. Algorithm

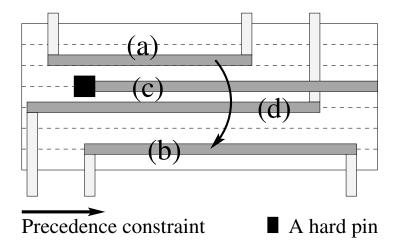

In general, the number of wire segments in a routing procedure is huge and even a routability driven track routing problem is NP-complete [3], therefore a "divide and conquer" strategy is employed in this work. Since each panel consists of only horizontal/vertical wire segments, we solve the track routing problem panel by panel. Figure 7 shows an example of assigning wire segments a, b, c, d, e and f to the tracks of a horizontal panel of capacity  $K_p = 4$ .

Fig. 7. An example of the track routing problem.

## 1. Constraint Graph

For each horizontal (vertical) panel p, we construct an undirected constraint graph CG(V, E) with each vertex  $v_i \in V$  corresponding to a segment i in panel p. There is an edge  $e(v_i, v_j)$  between vertices  $v_i$  and  $v_j$  if there exists a span overlap between i and j. Figure 8 shows the constraint graph for the track routing example used in Figure 7. If segment i belongs to net  $N_m$  and segment j is a part of net  $N_n$ , the edge weight  $wt(v_i, v_j)$  is defined as follows.

$$wt(v_i, v_j) = \frac{d_{ji}}{S_{min}^{N_m}} + \frac{d_{ij}}{S_{min}^{N_n}}$$

(3.2)

where  $d_{ji}$  and  $d_{ij}$  are delay costs defined in Section II-A. Note here  $d_{ji}$  and  $d_{ij}$  could be quite different depending on the coupling location of segment i, j of net  $N_m$ ,  $N_n$ , respectively. The minimum timing slack  $S_{min}^{N_n}$  and  $S_{min}^{N_m}$  are used as weighting factors. In case of negative timing slacks, a large positive offset is temporarily added to the  $min\_slack$  of every net in the constraint graph, only for calculating  $wt(v_i, v_j)$ . It is easy to observe that the edge weight between critical nets with strong coupling will be significantly higher. Our graph based algorithm, which will be discussed later, is able to avoid the adjacency of such pair of nets if their edge weight is large. Therefore, this edge weight definition enables us to optimize timing slacks and coupling-induced-delay simultaneously. Previous works [3, 4], however, are primarily focused on minimizing the total amount of coupling capacitance.

Fig. 8. A constraint graph.

Since the size of a constraint graph is generally very large, we consider it in a clique-by-clique manner [3,4,24]. A clique is a complete subgraph of the constraint graph. Each vertex (segment) in a clique has span overlap with every other vertex (segment) in the same clique. The size of a clique tells the minimal number of routing tracks needed to route all the segments in the clique. In the constraint graph, the largest clique in the graph is processed first. If there exist more than one largest cliques with the same size, we choose a clique with the maximal span. After performing track assignment for the largest clique, we remove this clique from the constraint graph and start to process the next largest clique.

Finding the largest clique can be done in polynomial time since our constraint graph is also an interval graph [3],

For each clique, a track assignment solution corresponds to a Hamiltonian path. If only coupling capacitance induced delays are considered, our objective becomes to find a Hamiltonian path that can provide a maximal  $min\_slack$  among all the segments in the clique. Based on the edge weight definition that considers both coupling induced delay and timing criticality, our problem becomes a minimum weight Hamiltonian path problem.

## 2. Wire Detour Induced Delay and Bipartite Graph Model

Fig. 9. An example of detour.

track b, respectively. The edge weight for  $(v_i, v_b)$  can be defined as  $\frac{e_{i,b}}{S_{min}^i}$  where  $e_{i,b}$  is the slack change when the segment i is moved from the minimum detour location to track b. If we only consider the detour induced delay, our problem can be formulated as a minimum weight matching problem for the bipartite graph. The edge weight can be defined to include other design concerns besides the detour induced delay penalty.

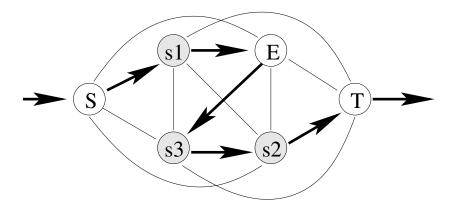

## 3. Sequential Ordering Problem Based Track Routing Algorithm

Fig. 10. The integration of a constraint and a bipartite graph.

When both the coupling capacitance induced delay and the detour induced delay are considered simultaneously, the clique model and the bipartite graph described in the previous subsection can be integrated into a hybrid graph as shown in Figure 10. In Figure 10, the highlighted edges on the constraint graph represent a Hamiltonian path for clique

(d,b,c,e) and the highlighted edges on the bipartite graph part indicate a matching solution. In this solution, wire segments b,c,d and e are assigned to track 2,3,1 and 4, respectively. The integrated problem becomes to find a minimum weight Hamiltonian path on the clique part and a minimum weight matching on the bipartite part simultaneously. In addition, the min-path solution and the min-matching solution should be compatible with each other. The minimum weight Hamiltonian path problem alone is notoriously hard and the integrated problem is obviously more difficult.

The special difficulty of this problem is the partial correlation between two different kinds of cost (coupling induced delay cost and detour induced delay cost) in the objective. We solve this difficulty by transforming the detour induced delay cost into precedence constraints to the Hamiltonian path problem. A precedence constraint (i, j) tells that vertex i is required to precede j in the tour of a Hamiltonian path.

The cost-constraint transformation is carried out according to segment types defined as follows. (1) Type  $\cup$  segments are those horizontal segments with two ends connected upward with vertical segments  $^1$ . (2) Type  $\cap$  segments are the horizontal segments with two ends connected downward with vertical segments. (3) Type H segments are those connected to hard pins in the panel. (4) "don't care" segments are the other horizontal segments in the panel. These segment types are illustrated in Figure 11.

Then, we add the following precedence constraints to the Hamiltonian path problem: for any segment  $i \in type \cup set$ , there is a precedence constraint (i, j),  $\forall j \in type \cap group$ . This set of precedence constraints can limit the vertical wire lengths for both type  $\cup$  and  $\cap$  wire segments. As a result, delays induced by redundant vertical wire lengths are alleviated. Other constraints can be added in a similar way to tighten the flexibility of a Hamiltonian path. For example, we can enforce a  $\cup$  type segment to precede a H type segment in the

<sup>&</sup>lt;sup>1</sup>Here we categorize these types in the scenario of a horizontal panel as in Figure 11. Segments in vertical panels can be categorized in the same way.

Fig. 11. (a) a type  $\cup$  segment. (b) a type  $\cap$  segment. (c) a type H segment. (d) a "don't care" segment.

lower half of the panel. The additional constraints may further reduce detour induced delay cost. However, they may degrade coupling induced delay cost as the solution space for the Hamiltonian path problem is reduced. Therefore, we believe our precedence constraint definition is generally sufficient to minimize detours while leaving enough solution space for the Hamiltonian path problem.

Finding a minimum weight Hamiltonian path with precedence constraints is known as a Sequential Ordering Problem (SOP) [36], which is an extension to the asymmetric traveling salesman problem (ATSP) with additional precedence constraints: given a complete graph G with directed weighted edges, a precedence constraint set R and designated start and terminal vertices, SOP finds a minimum weight Hamiltonian path from the start vertex to the terminal vertex which observes the precedence constraints. The precedence constraint set R can be represented by pairs of vertices (i,j) ( $i \neq j$ ). For each precedence constraint  $(i,j) \in R$ , vertex i is required to precede vertex j in the tour of Hamiltonian path. The SOP is also known to be an NP-complete problem. In our constraint graph, each undirected edge can be converted to two directed edges with the same edge weight.