#### A modular approach to next generation Qucs

### Felix Salfelder Qucs Development Team and Mike Brinson Centre for Communications Technology, London Metropolitan University, UK

1st Asia/South Pacific MOS-AK Workshop (virtual/online) FEB. 25-26, 2021

# A modular approach to next generation Qucs: presentation topics

- Background and timeline

- Next generation Qucs

Qucs - a modular approach But why plug-ins? Comparison and plans (exemplified) Library design Development Example slides

• Qucs-S (Qucs for SPICE)

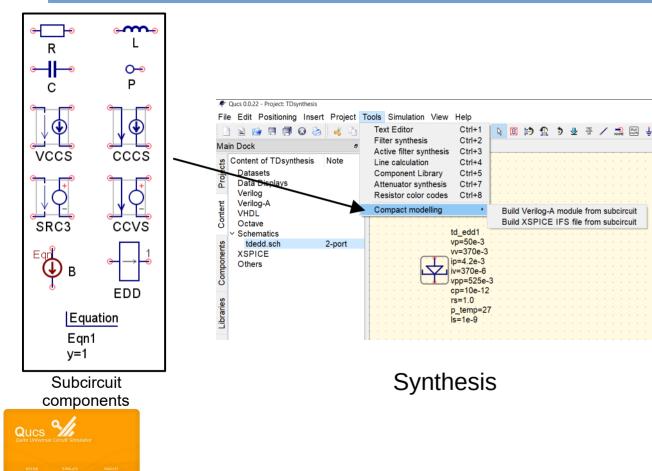

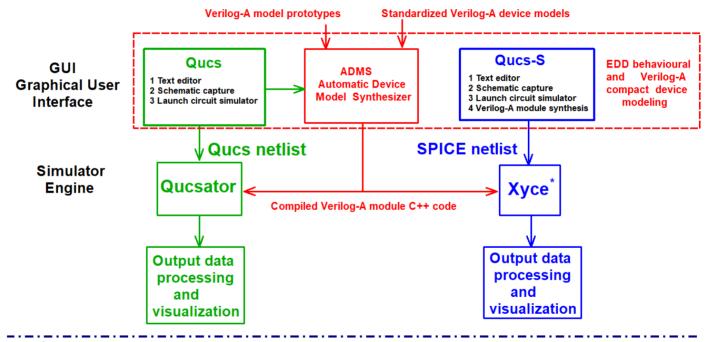

Qucs-S: a FOSS circuit simulator formed from the Qucs GUI plus Xyce simulation engine Compact device modeling: Equation Defined Device model and Verilog-A module development

#### • Merging Qucs(Qt5) GUI and Qucs-S Qucs(Qt5)/Xyce schematic symbols and models Evolving Qucs(Qt5)/Xyce modeling and simulation capabilities

- Summary

- References

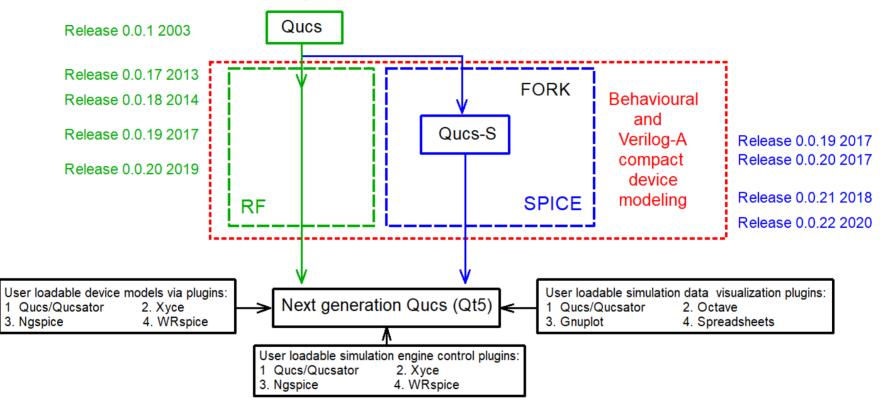

## A modular approach to next generation Qucs: background and timeline

### A modular approach to next generation Qucs: Qucs – a modular approach

- Evident challenges

- Over 100.000 lines of code

- A zoo of features

- Moving targets (dependencies and applications)

- Approach: Small library and extensions

- Separate data from UI and interactions

- Establish internal and external interfaces

- Opt-in extensions (including default features)

- User extensions (no approval required)

- Goals

- Growth without forking

- Encourage alternatives and improvement

- Avoid review and integration overhead

- Keep/support the legacy ("0.0.20") but move forward

#### A modular approach to next generation Qucs: But why plug-ins?

- A Plug-in extends a program

- Loaded at run time

- Provides nontrivial features

- Allows customisation

- Does anything (aka. Turing completeness)

Known software with plug-in support

- linux> modprobe pcspkr # I can play sound

- python> import numpy # fancy arrays and maths

- gnucap> attach bsimXYZ.so # use transistor model

- Firefox, Gimp, Inkscape, Emacs(endless)

#### A modular approach to next generation Qucs: Comparison and plans - exemplified

|                      | Gnucap | Qucs | Хусе | future Qucs |

|----------------------|--------|------|------|-------------|

| plugins              | yes    | no   | no   | yes         |

| interactions         | yes    | yes  | no   | yes         |

| devices              |        | many | many | plugin      |

| GUI                  | no     | yes  | no   | plugins     |

| <b>HB</b> simulation | n/a    | no   | yes  | plugin      |

| Verilog-AMS          | n/a    | no   | ?    | plugin      |

| Python library       | YOU    | GET  | THE  | IDEA        |

#### A modular approach to next generation Qucs: Intended plug-ins

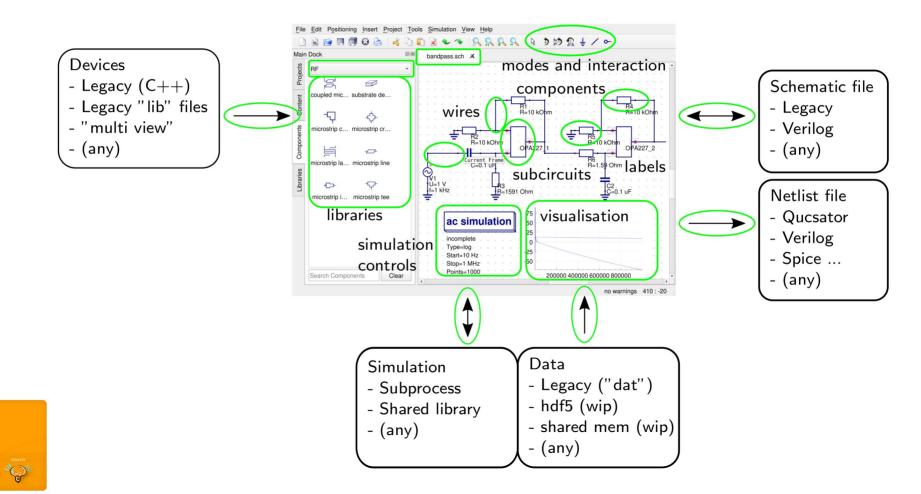

#### A modular approach to next generation Qucs: Library design

- Few base classes, broad inheritance

- Clear distinction between data and UI

- Circuit representation

- UI (cli) + GUI (Qt)

- Explicit objective circuit model

- Symbols with ports and parameters

- Nodes, Nets & Hierarchy

- Interfaces for

- Parsers, netlisters, subprocesses

- Data sets and manipulation

- Elaborate symbols ("multiview", wire, equation...)

- GUI (Dialog widgets, menus, drawings ...)

- (Non-C++ plugins intended, need wrapper.)

#### A modular approach to next generation Qucs: Qt5 benefits

- Broadly available across platforms (Qt3/4 has reached EOL years ago)

- Fast & scalable graphics scene

- Support for high resolution displays

- Built-in manipulation routines

- 2D/3D data visualisation options

- Standardised undo/redo stack etc.

- (expecting easy transition to Qt6)

#### A modular approach to next generation Qucs: Development

Process

- 1. Identify relevant library, infrastructure

- 2. Move everything else to plugins

Status/Summary

- Library is converging (minor changes expected)

- new:Simulator interface

- new:Symbol plug-ins

- new:Pluggable Data

- new:Nets are explicit

- new:(Circuit & Schematic) language support

- Schematic editor (rewrite) usable, needs work.

- Diagrams, need work, QtWidget rewrite intended

- Legacy schematics: Lacks some fancy stuff (labels...)

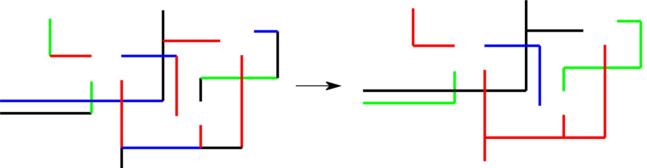

#### A modular approach to next generation Qucs: Feature preview: Explicit nets

- "Which net does this wire belong to?"

- ... introduce (persistent) nets and keep track

- i .e. follow circuit alterations

- Simpler API and possible UI improvements

- Traditional "netlisting" is now trivial

- Labels, feedback, DRC ...

#### A modular approach to next generation Qucs: Finally - Qucs-S

| File       | Edit Positioning | g <u>I</u> nsert <u>P</u> rojec | t <u>T</u> oo | Is Simulation View Help                             |

|------------|------------------|---------------------------------|---------------|-----------------------------------------------------|

| 1          | 🖹 📄 🗏            | 0 👌 🤞                           |               | 🛍 🗟 🗢 🤏 🕵 🕵 🔖 🦻 🚔 🛓 🖍 👓                             |

| Main       | Dock             |                                 | 0 X           | test_td_edd_dc.sch X                                |

| Projects   | QucsXyceLib1     |                                 | •             | ***************************************             |

| Proj       | -k-              | , <b></b> ,                     | -             | · · · · · · · · · · · · · · · · · · ·               |

| ent        | HICUML0_n        | ammeter                         |               | XYCE SCRIPT Qucs-S plugins                          |

| Content    | Ŧ                | Ŧ                               |               | incomplete<br>Script=                               |

| nents      | c_lin            | c_q                             |               | .global_param dcsweep=0.0                           |

| Components | 1                |                                 | A series      | .print dc format=std file=dc.txt dcsweep e ammeter1 |

|            | i_dc             | I_lin                           |               | + v(xvoltmeter1;pton)                               |

| Libraries  |                  |                                 |               |                                                     |

| Libr       | Ø                | 19                              |               |                                                     |

|            | port_device      | probe_v                         |               | Work in progress                                    |

|            | ň                | 2                               | •             |                                                     |

|            | Search Compone   | ents Clea                       | ar            |                                                     |

|            | ·                |                                 |               | E F                                                 |

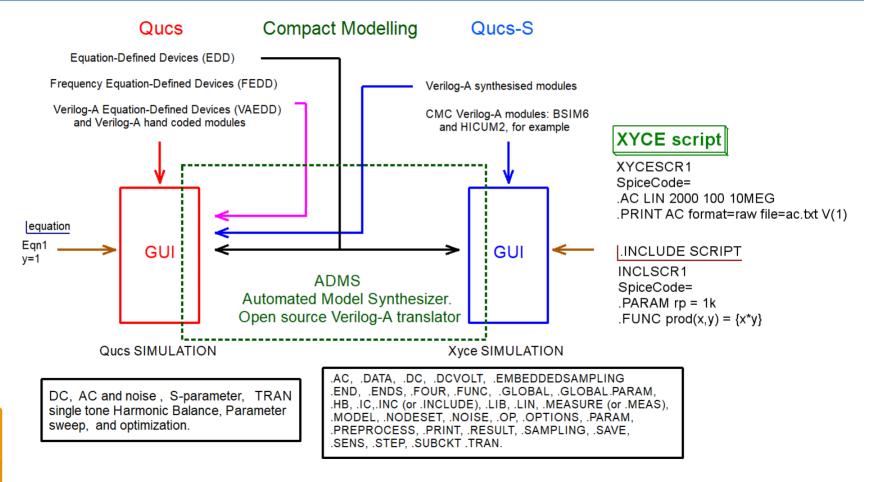

#### • A modular approach to next generation Qucs: Qucs-S = Qucs GUI plus Xyce

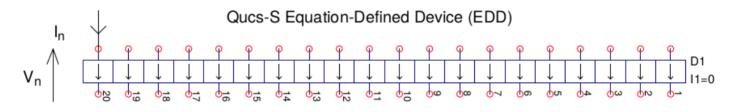

#### A modular approach to next generation Qucs: Equation Defined Device (EDD) models 1

I = I(V), g = dI/dV Q = Q(V,I), C = dQ/dV =  $\partial Q(V)/\partial V + \partial Q(I)/\partial I \cdot g$ , where the current flowing in branch n is I<sub>n</sub> = I(V<sub>n</sub>) + d/dt(Q<sub>n</sub>), and 1 <= n <= 20.

- EDD is a multiterminal nonlinear component with branch currents that can be functions of EDD branch voltage, and stored charge that can be a function of both EDD branch voltages and currents

- EDD is similar, but more advanced to the SPICE 3f5 B type I or V controlled sources

- EDD can be combined with conventional circuit components and Qucs-S equation blocks when constructing compact device models and subcircuit macromodels

- EDD is an advanced component, allowing users to construct prototype experimental models from a set of equations derived from physical device properties

- EDD operator d/dt is undertaken internally by Qucs-S

- Qucs-S EDD can have a maximum of 20 two terminal branches

#### A modular approach to next generation Qucs: Equation Defined Device (EDD) models 2

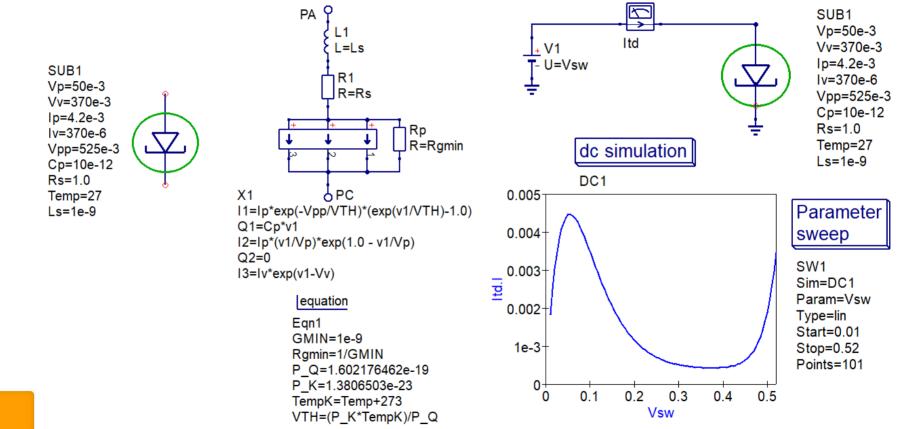

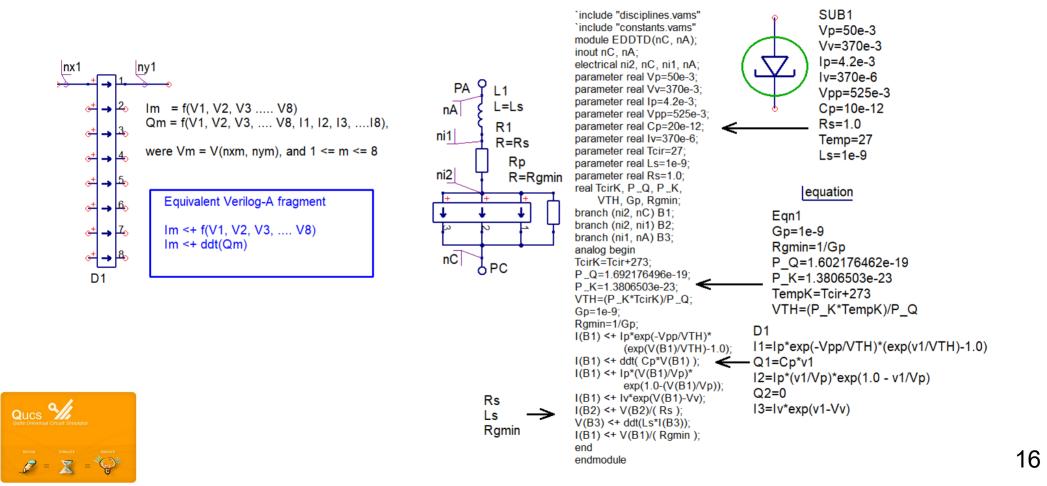

#### A modular approach to next generation Qucs: EDD models translated to Verilog-A modules

#### A modular approach to next generation Qucs: Synthesis of Qucs-S schematics to Verilog-A modules

`include "disciplines.vams" 'include "constants.vams" module EDDTD(nC, nA): inout nC. nA: eleIctrical ni2. nC. ni1. nA. net0L1: parameter real Vp=50e-3: parameter real Vv=370e-3: parameter real lp=4.2e-3: parameter real Vpp=525e-3; parameter real Cp=20e-12: parameter real lv=370e-6: parameter real Tcir=27: parameter real Ls=1e-9: parameter real Rs=1.0; real TcirK, P.,Q, P.,K, VTH, Gp, Rgmin; analog begin @(initial model) begin TcirK=Tcir+273: P Q=1.692176496e-19: P K=1.3806503e-23: VTH=(P\_K\*TcirK)/P\_Q; Gp=1e-9: Ramin=1/Gp: end  $I(ni2,nC) \le Ip^{exp}(-Vpp/VTH)^{exp}(V(ni2,nC)/VTH)^{-1.0};$ I(ni2.nC) <+ ddt(Cp\*V(ni2.nC)):I(ni2,nC) <+ lp\*(V(ni2,nC)/Vp)\*exp(1.0-(V(ni2,nC)/Vp)); I(ni2,nC) <+ Iv\*exp(V(ni2,nC)-Vv);I(ni2.ni1) <+ V(ni2.ni1)/( Rs ): I(ni2,ni1) <+ white \_\_noise( 4.0\*`P \_\_K\*( 26.85 + 273.15) / (Rs), "thermal");  $I(\_net0L1) <+ ddt(V(\_net0L1));$ I(\_net0L1) <+ V(ni1,nA); I(ni1.nA) <+ V( net0L1)/(Ls+1e-20)1: I(nC,ni2) <+ V(nC,ni2)/(Rgmin);I(nC,ni2) <+ white \_noise( 4.0\*`P\_K\*( 26.85 + 273.15) / (Ramin), "thermal"): end endmodule

### A modular approach to next generation Qucs: Qucs/Qucs-S/Xyce Verilog-A compact device modeling

- 1. DIODE.CMC , 2. BJT VBIC 1.3, FBH HBT.X, HICUML0/L2, MEXTRAM.

- 3. MOSFET BSIM3, BSIM4, BSIM6, BSIM.SOI, BSIM.CMG, MVS, PSP

- 4. Memristor-TEAM, -Yakopcic, -PEM

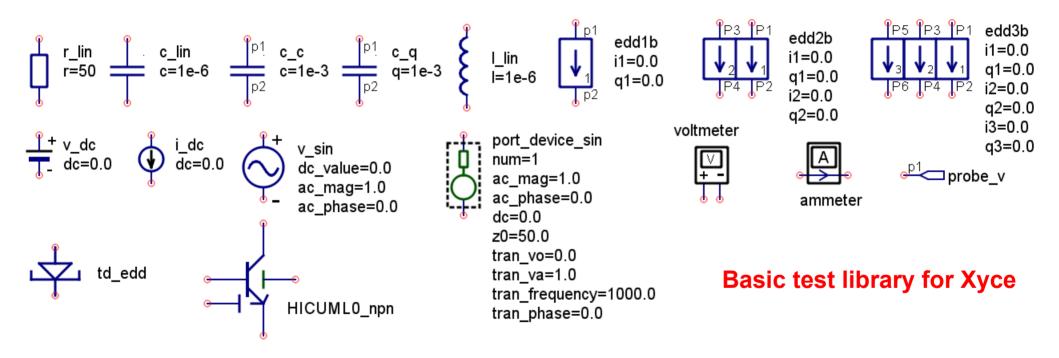

### A modular approach to next generation Qucs: Qucs(Qt5)/Xyce schematic symbols and models 1

Points to note: 1. Component and device models are no longer hard wired into Qucs.

- 2. Xyce SPICE dialect becomes the Qucs(Qt5)/Xyce netlist format.

- 3. The body of each schematic symbol holds defining Xyce SPICE code

### A modular approach to next generation Qucs: Qucs(Qt5)/Xyce schematic symbols and models 2

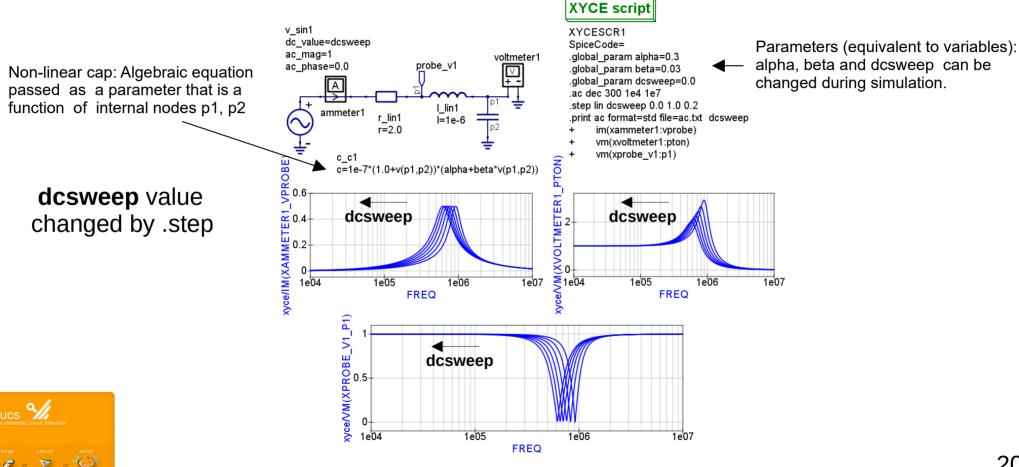

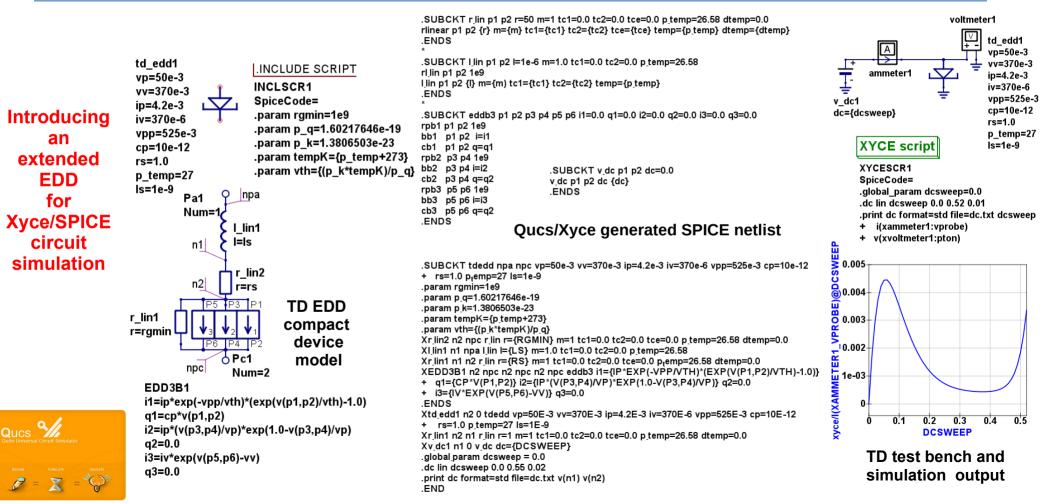

#### A modular approach to next generation Qucs: Qucs(Qt5)/Xyce tunnel diode EDD compact model

### A modular approach to next generation Qucs: Simulation with CMC Verilog-A standardised device models

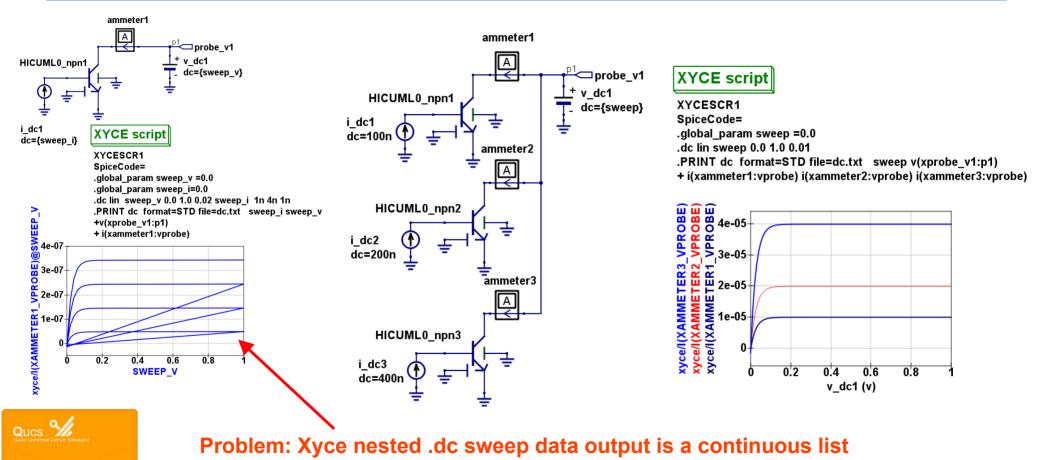

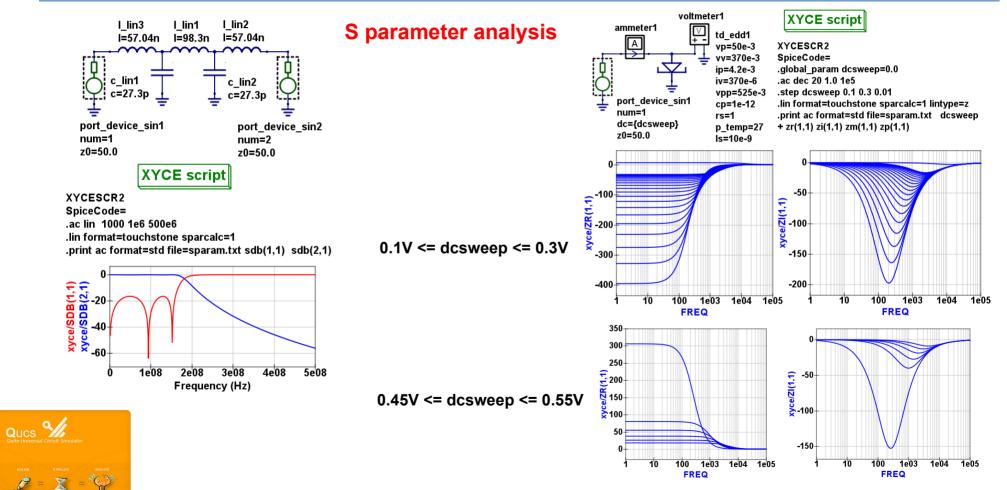

#### A modular approach to next generation Qucs: Evolving Qucs(Qt5)/Xyce simulation capabilities 1

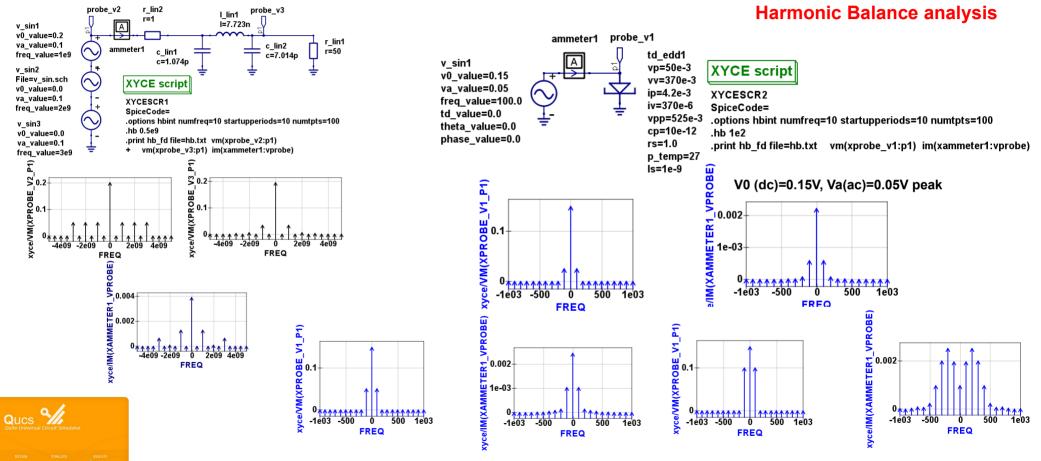

#### A modular approach to next generation Qucs: Evolving Qucs(Qt5)/Xyce simulation capabilities 2

V0 (dc)=0.15V, Va(ac)=0.1V peak

### QucsStudio and Qucs-S Verilog-A compact device modeling Summary

This presentation introduced the background, concepts and current progress in developing a modular Qt5 version of Qucs, which is

- easy to maintain

- makes extensive use of plugins

- and is driven by discipline and user needs

The package is in it's early stages of development and it is envisaged that the first general release will not before the end of 2021.

### QucsStudio and Qucs-S Verilog-A compact device modeling -References

Qucs (0.0.19/20): https://github.com/Qucs/qucs/ Download - version (Linux, Windows or Mac) as required from home page.

Qucs-S (0.0.22): Qucs with SPICE - https://ra3xdh.github.io/; Download – version (Linux or Windows) as required from home page.

Xyce: https://xyce.sandia.gov/; Download - version (Linux, Windows or Mac) as required from home page.