# INVESTIGATION OF ANTI-ISLANDING SCHEMES FOR UTILITY

## INTERCONNECTION OF DISTRIBUTED FUEL CELL

## **POWERED GENERATIONS**

A Dissertation

by

## CHUTTCHAVAL JERAPUTRA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2004

Major Subject: Electrical Engineering

## INVESTIGATION OF ANTI-ISLANDING SCHEMES FOR UTILITY

## INTERCONNECTION OF DISTRIBUTED FUEL CELL

## **POWERED GENERATIONS**

A Dissertation

by

CHUTTCHAVAL JERAPUTRA

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved as to style and content by:

Prasad N. Enjeti (Chair of Committee)

> Chanan Singh (Member)

Emil J. Straube (Member)

Aniruddha Datta (Member) Chanan Singh (Head of Department)

December 2004

Major Subject: Electrical Engineering

#### ABSTRACT

Investigation of Anti-Islanding Schemes for Utility Interconnection of Distributed Fuel Cell Powered Generations.

(December 2004)

Chuttchaval Jeraputra,

B.S., King Mongkut's Institute of Technology (Ladkrabang), Bangkok, Thailand;

M.S., The Pennsylvania State University

Chair of Advisory Committee: Dr. Prasad N. Enjeti

The rapid emergence of distributed fuel cell powered generations (DFPGs) operating in parallel with utility has brought a number of technical concerns as more DFPGs are connected to utility grid. One of the most challenging problems is known as islanding phenomenon. This situation occurs when a network is disconnected from utility grid and is energized by local DFPGs. It can possibly result in injury to utility personnel arriving to service isolated feeders, equipment damage, and system malfunction.

In response to the concern, this dissertation aims to develop a robust antiislanding algorithm for utility interconnection of DFPGs. In the first part, digital signal processor (DSP) controlled power electronic converters for utility interconnection of DFPGs are developed. Current control in a direct-quadrature (dq) synchronous frame is proposed. The real and reactive power is controlled by regulating inverter currents. The proposed digital current control in a synchronous frame significantly enhances the performance of DFPGs.

In the second part, the robust anti-islanding algorithm for utility interconnection of a DFPG is developed. The power control algorithm is proposed based on analysis of a real and reactive power mismatch. It continuously perturbs  $(\pm 5\%)$  the reactive power supplied by the DFPG while monitoring the voltage and frequency. If islanding were to occur, a measurable frequency deviation would take place, upon which the real power of the DFPG is further reduced to 80%; a drop in voltage positively confirms islanding. This method is shown to be robust and reliable.

In the third part, an improved anti-islanding algorithm for utility interconnection of multiple DFPGs is presented. The cross correlation method is proposed and implemented in conjunction with the power control algorithm. It calculates the cross correlation index of a rate of change of the frequency deviation and ( $\pm 5\%$ ) the reactive power. If this index increases above 50%, the chance of islanding is high. The algorithm initiates ( $\pm 10\%$ ) the reactive power and continues to calculate the correlation index. If the index exceeds 80%, islanding is now confirmed. The proposed method is robust and capable of detecting islanding in the presence of several DFPGs independently operating.

Analysis, simulation and experimental results are presented and discussed.

To My Family

#### ACKNOWLEDGMENTS

I would like to express my gratitude to Dr. Prasad Enjeti. His professionalism in academic and research activities has broadened my knowledge in the field of power electronics. I am so thankful for his support and encouragement throughout my study. I express my sincere appreciation to the other committee members for their valuable comments and time.

To Somnida Ratanapachote, Hanju Cha, Maja, Sangsun Kim, Leonado Palma and other colleagues in power electronics and clean power research lab, I thank you for all of your advice and assistance.

Special thanks to my wonderful parents and family for their love, support and encouragement. I also thank Salilla Lertbannaphong who is always by my side through ups and downs and makes me feel so special. To all of my friends, I thank you all for being great companions and thank you for encouraging me.

# TABLE OF CONTENTS

| CHAPTE | R   |                                                         | Page |

|--------|-----|---------------------------------------------------------|------|

| Ι      | INT | RODUCTION                                               | 1    |

|        | 1.1 | Introduction                                            | 1    |

|        | 1.2 | Review of Islanding Detection                           | 3    |

|        |     | 1.2.1 Passive Method                                    |      |

|        |     | 1.2.1.1 Over/Under Voltage and Frequency Detection.     |      |

|        |     | 1.2.1.2 Phase Jump Detection                            |      |

|        |     | 1.2.1.3 Voltage Harmonic Detection                      |      |

|        |     | 1.2.2 Active Method                                     |      |

|        |     | 1.2.2.1 Output Power Variation                          |      |

|        |     | 1.2.2.2 Impedance Measurement                           |      |

|        |     | 1.2.2.3 Sliding Mode Frequency Shift                    |      |

|        |     | 1.2.2.4 Active Frequency Drift                          |      |

|        |     | 1.2.2.5 Main Monitoring Units with Allocated All-Pol    |      |

|        |     | Switching Devices Connected in Series (MSD)             |      |

|        |     | 1.2.3 Other Method                                      |      |

|        |     | 1.2.3.1 Reactance Insertion                             |      |

|        |     | 1.2.3.2 Power Line Carrier Communication                |      |

|        |     | 1.2.3.3 Supervisory Control and Data Acquisition        |      |

|        | 1.3 | IEEE Standard 1547                                      |      |

|        | 1.4 | Research Objective                                      |      |

|        | 1.5 | Dissertation Outline                                    | 26   |

| II     | DSP | CONTROLLED POWER ELECTRONIC CONVERTERS FOR              | ł    |

|        |     | LITY INTERCONNECTION OF DISTRIBUTED FUEL CELL           |      |

|        | POW | VERED GENERATIONS                                       | 28   |

|        | 2.1 | Introduction                                            | 28   |

|        | 2.1 | DSP Based Control                                       |      |

|        | 2.2 | Control Topology                                        |      |

|        | 2.4 | Proposed Digital Current Control in a Synchronous Frame |      |

|        | 2.1 | 2.4.1 Modeling of PWM Inverters                         |      |

|        |     | 2.4.1.1 A Single Phase PWM Inverter                     |      |

|        |     | 2.4.1.2 A Three-Phase PWM Inverter                      |      |

|        |     | 2.4.2 Synchronous Frame Current Control                 |      |

|        | 2.5 | Current Reference Calculation                           |      |

|        | 2.6 | Space Vector PWM                                        |      |

|        |     | 2.6.1 Single Phase Space Vector PWM                     |      |

|        |     | 2.6.2 Three-Phase Space Vector PWM                      |      |

|        | 2.7 | Implementation of DSP Based Control                     |      |

|         |                                                              | 2.7.1 Sampling                                                                                                                                                                                                          | 62                                                               |

|---------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

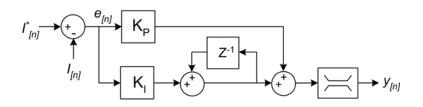

|         |                                                              | 2.7.2 PI Controller                                                                                                                                                                                                     | 62                                                               |

|         |                                                              | 2.7.3 Phase Lock                                                                                                                                                                                                        | 63                                                               |

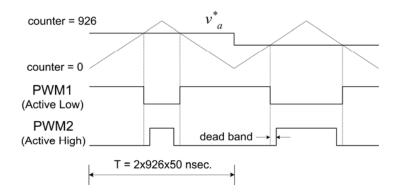

|         |                                                              | 2.7.4 Generation of PWM Output                                                                                                                                                                                          | 64                                                               |

|         | 2.8                                                          | Simulation Results                                                                                                                                                                                                      |                                                                  |

|         | 2.9                                                          | Experimental Results                                                                                                                                                                                                    |                                                                  |

|         |                                                              | Summary                                                                                                                                                                                                                 |                                                                  |

| III     | DEVI                                                         | ELOPMENT OF A ROBUST ANTI-ISLANDING                                                                                                                                                                                     |                                                                  |

|         |                                                              | ORITHM FOR UTILITY INTERCONNECTION OF A                                                                                                                                                                                 |                                                                  |

|         |                                                              | RIBUTED FUEL CELL POWERED GENERATION                                                                                                                                                                                    | 77                                                               |

|         | 3.1                                                          | Introduction                                                                                                                                                                                                            | 77                                                               |

|         | 3.2                                                          | Analysis of Real and Reactive Power Mismatch                                                                                                                                                                            |                                                                  |

|         | 3.3                                                          | A Robust Anti-Islanding Algorithm Development                                                                                                                                                                           |                                                                  |

|         |                                                              | Proposed Power Control Algorithm                                                                                                                                                                                        |                                                                  |

|         | 3.4<br>3.5                                                   | Simulation Results                                                                                                                                                                                                      |                                                                  |

|         | 3.5<br>3.6                                                   | Experimental Results                                                                                                                                                                                                    |                                                                  |

|         | 3.0<br>3.7                                                   | Summary                                                                                                                                                                                                                 |                                                                  |

|         |                                                              | -                                                                                                                                                                                                                       |                                                                  |

| IV      |                                                              | MPROVED ANTI-ISLANDING ALGORITHM FOR UTIL                                                                                                                                                                               | ITY                                                              |

|         |                                                              | RCONNECTION OF MULTIPLE DISTRIBUTED FUEL                                                                                                                                                                                | 07                                                               |

|         |                                                              | POWERED GENERATIONS                                                                                                                                                                                                     |                                                                  |

|         | CLLL                                                         |                                                                                                                                                                                                                         |                                                                  |

|         |                                                              | Introduction                                                                                                                                                                                                            |                                                                  |

|         |                                                              | Introduction                                                                                                                                                                                                            | 97                                                               |

|         | 4.1                                                          |                                                                                                                                                                                                                         | 97<br>99                                                         |

|         | 4.1<br>4.2                                                   | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function                                                                                                                             | 97<br>99<br>106                                                  |

|         | 4.1<br>4.2<br>4.3                                            | Introduction<br>Analysis of Islanding Voltage and Frequency                                                                                                                                                             | 97<br>99<br>106<br>107                                           |

|         | 4.1<br>4.2<br>4.3<br>4.4                                     | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function<br>Proposed Cross Correlation Method                                                                                        | 97<br>99<br>106<br>107<br>110                                    |

| V       | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                       | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function<br>Proposed Cross Correlation Method<br>Simulation Results                                                                  | 97<br>99<br>106<br>107<br>110<br>114                             |

| V       | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                       | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function<br>Proposed Cross Correlation Method<br>Simulation Results<br>Summary                                                       | 97<br>                                                           |

| V       | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>CONO               | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function<br>Proposed Cross Correlation Method<br>Simulation Results<br>Summary<br>CLUSION                                            | 97<br>                                                           |

|         | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>CONO<br>5.1<br>5.2 | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function<br>Proposed Cross Correlation Method<br>Simulation Results<br>Summary<br>CLUSION<br>Conclusion<br>Suggestion of Future Work | 97<br>99<br>106<br>107<br>110<br>114<br>115<br>115<br>116        |

| REFEREN | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>CON<br>5.1<br>5.2  | Introduction<br>Analysis of Islanding Voltage and Frequency<br>A Cross Correlation Function<br>Proposed Cross Correlation Method<br>Simulation Results<br>Summary<br>CLUSION                                            | 97<br>99<br>106<br>107<br>110<br>114<br>115<br>115<br>115<br>116 |

# LIST OF FIGURES

| FIGUI | RE                                                                                                | Page |

|-------|---------------------------------------------------------------------------------------------------|------|

| 1.1   | Fuel cell power conditioner control system for supplying power to the utility (utility interface) | 2    |

| 1.2   | Real and reactive power mismatches at the instant utility disconnected.                           | 4    |

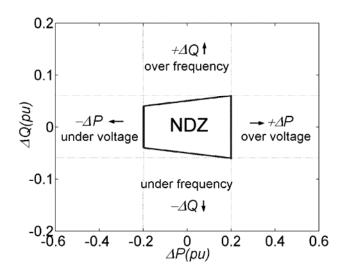

| 1.3   | A non-detection zone (NDZ) of over/under voltage and frequency detection method                   | 6    |

| 1.4   | Voltage phase jump after utility is disconnected                                                  | 7    |

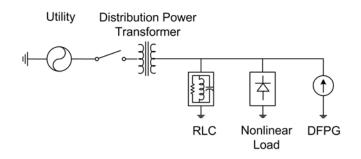

| 1.5   | Islanding contains RLC load, nonlinear load, and distribution power transformer                   | 8    |

| 1.6   | Output power variation method                                                                     | 11   |

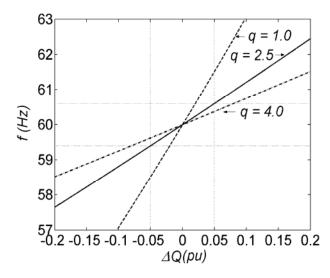

| 1.7   | A sinusoidal function of phase angle and load lines                                               | 13   |

| 1.8   | Output current waveform implementing upward active frequency drift.                               | 14   |

| 1.9   | Design of automatic disconnection switch in accordance to VDE 126                                 | 17   |

| 1.10  | System configuration of reactance insertion method                                                | 18   |

| 1.11  | System configuration of power line carrier communication method                                   | 20   |

| 1.12  | Series of Interconnection Standard IEEE 1547                                                      | 22   |

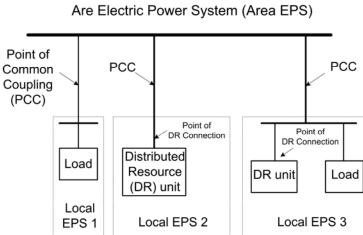

| 1.13  | Interconnection configuration and definition                                                      | 23   |

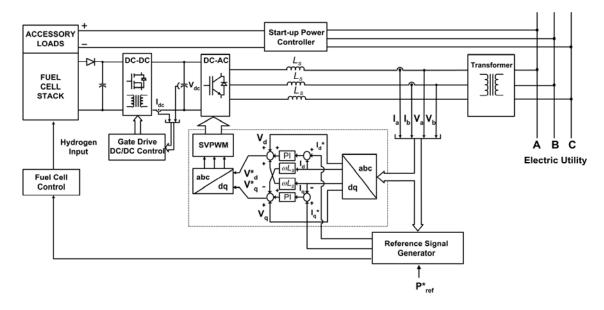

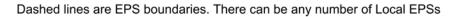

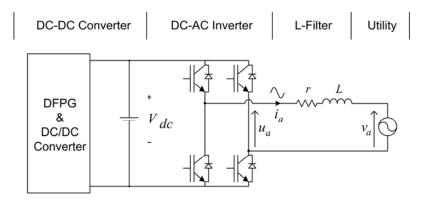

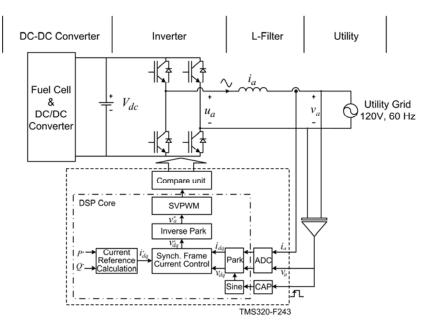

| 2.1   | System integration of fuel cell power conditioning systems                                        | 29   |

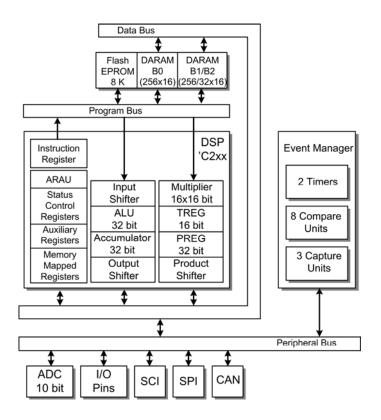

| 2.2   | A simplified block diagram of a digital signal processor TMS320-<br>F243                          | 32   |

| 2.3   | Control topology                                                                                  | 34   |

| 2.4   | Per-phase equivalent circuits of DC-AC PWM inverters                                              | 35   |

| 2.5   | A transformation diagram using two-phase Park's transformation                                    | 37   |

| 2.6   | A transfer function block diagram of a single phase PWM inverter in a synchronous frame           | 39   |

| 2.7   | A transformation diagram between a stationary frame and a synchronous frame                       | 41   |

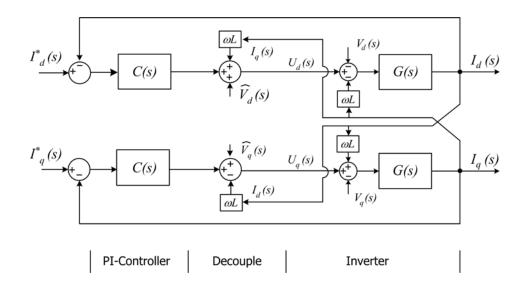

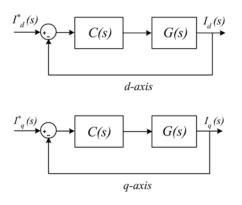

| 2.8   | Synchronous frame current control in frequency domain                                             | 43   |

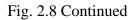

| 2.9   | Synchronous frame current control in discrete-time domain                                         | 44   |

# FIGURE

| 2.10 | Opened loop poles (x), zero (o), and desirable closed loop pole $(z^*)$                                                   | 46 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | Root locus of closed loop current control                                                                                 | 49 |

| 2.12 | Step response of closed loop current control                                                                              | 49 |

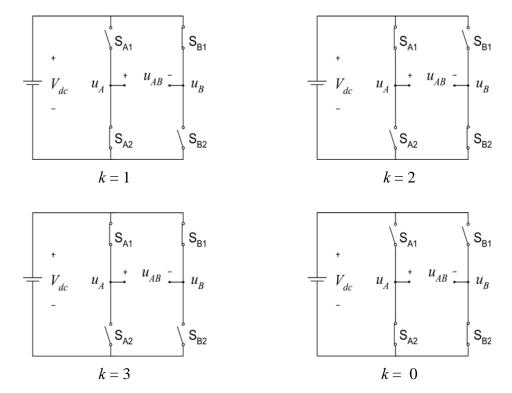

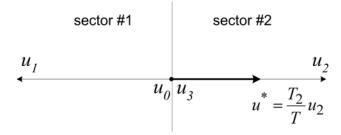

| 2.13 | Single phase space vector PWM                                                                                             | 52 |

| 2.14 | Switching pattern of symmetrical space vector PWM for a single phase PWM inverter                                         | 53 |

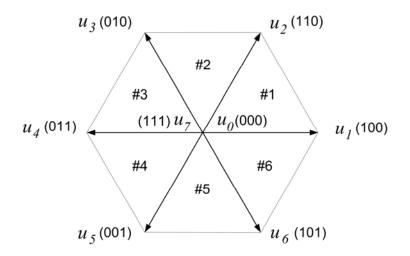

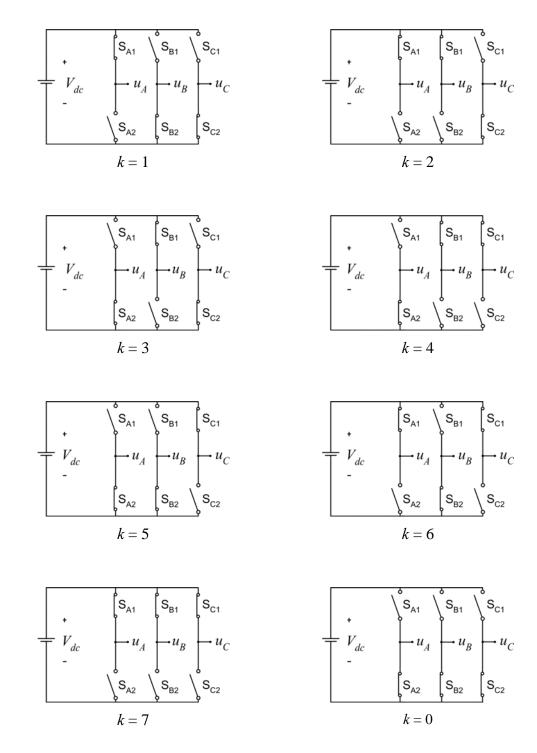

| 2.15 | Eight possible switching states form 6 active vectors and two zero vectors                                                | 54 |

| 2.16 | Eight switching states of a three-phase PWM inverter                                                                      | 55 |

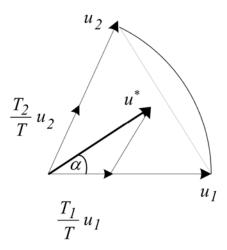

| 2.17 | Reference vector and its adjacent vectors                                                                                 | 56 |

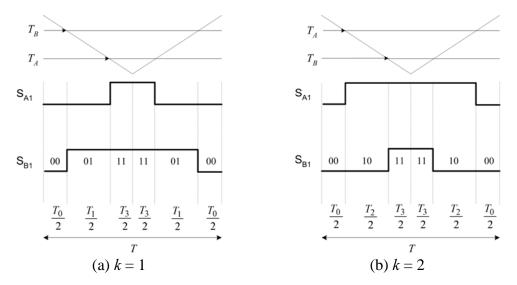

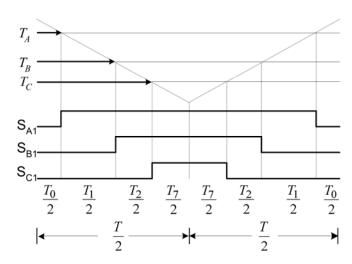

| 2.18 | Switching pattern of symmetrical space vector PWM ( $k = 1$ )                                                             | 58 |

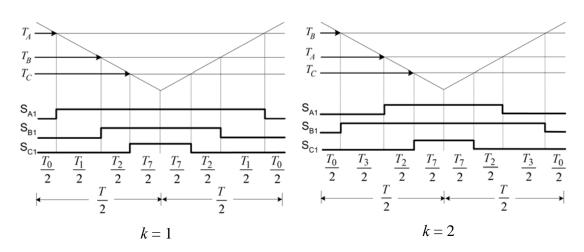

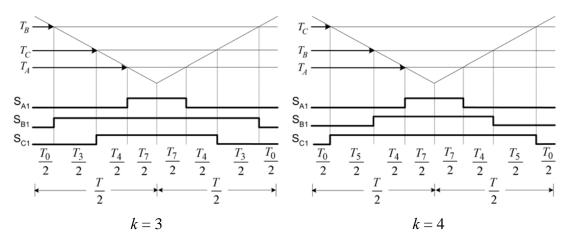

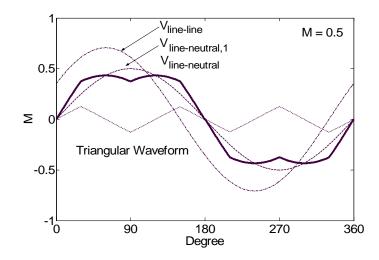

| 2.19 | Switching patterns of symmetrical space vector PWM                                                                        | 59 |

| 2.20 | Line to load-neutral and line to line voltage                                                                             | 60 |

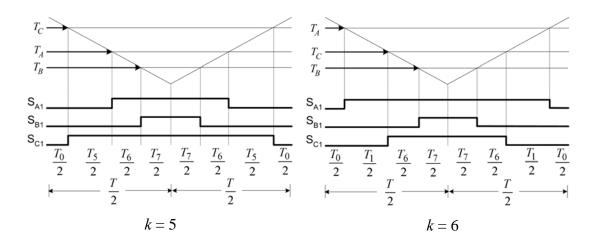

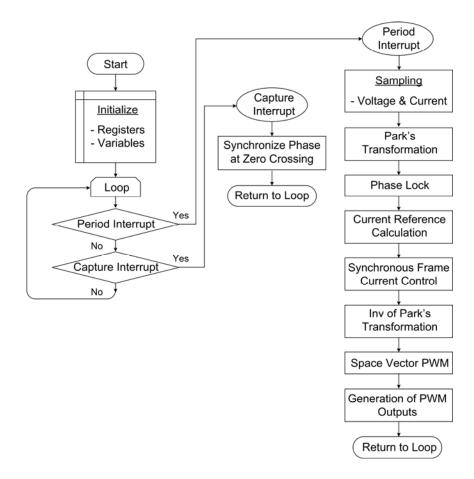

| 2.21 | Flow control of the program implemented by software                                                                       | 61 |

| 2.22 | Discrete time realization of the PI controller                                                                            | 62 |

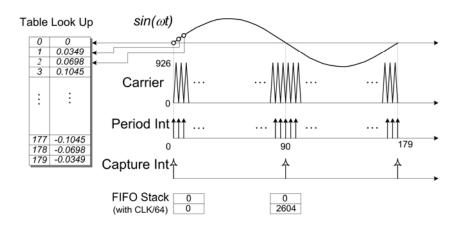

| 2.23 | Generation of a fundamental sinusoidal waveform                                                                           | 64 |

| 2.24 | Generation of PWM outputs                                                                                                 | 64 |

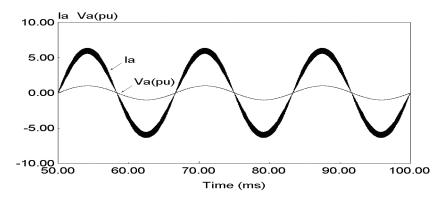

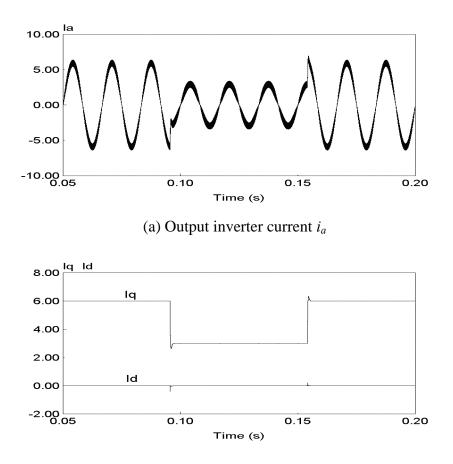

| 2.25 | Simulation result of the single phase PWM inverter supplying 0.5 kW, the inverter current $i_a$ and utility voltage $v_a$ | 67 |

| 2.26 | Step response of the single phase PWM inverter current under 50% real power reduction                                     | 68 |

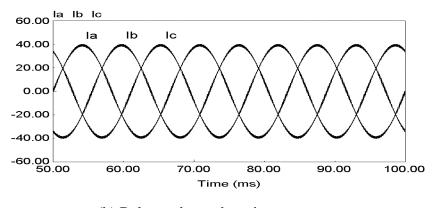

| 2.27 | Simulation result of the output current of the three-phase PWM inverter supplying 10 kW                                   | 69 |

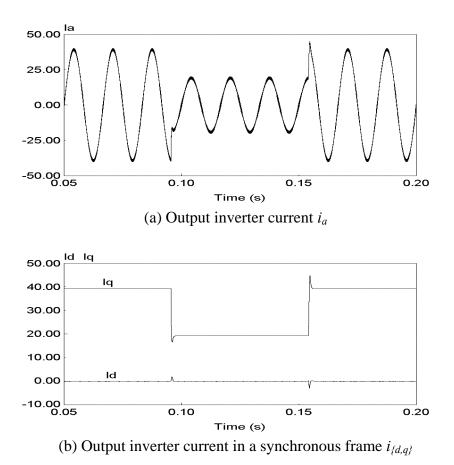

| 2.28 | Step response of the three-phase inverter current under 50% real power reduction                                          | 70 |

| 2.29 | DSP control implementation of the single phase fuel cell based inverter                                                   | 71 |

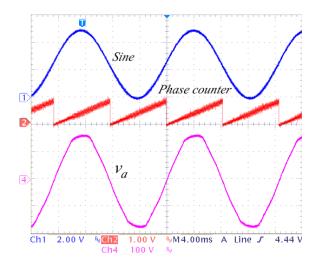

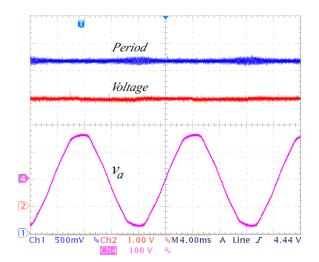

| 2.30 | Phase lock and sinusoidal waveform generation                                                                             | 72 |

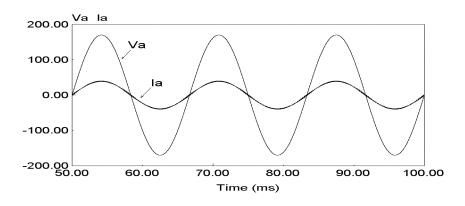

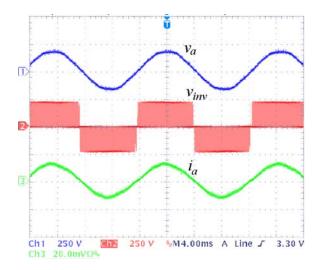

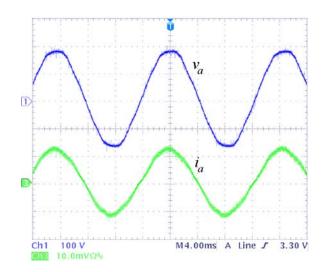

| 2.31 | Steady state operation of the single phase PWM inverter supplying 0.5 kW                                                  | 73 |

|      |                                                                                                                           |    |

# FIGURE

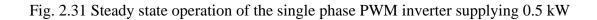

| 2.32 | Transformed inverter output currents in a synchronoud frame $i_d$ and $i_q$ while the single pase PWM inverter supplies 0.5 kW      | 74  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

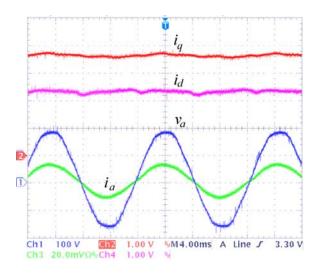

| 2.33 | Control voltage references in a synchronous frame $v_d$ and $v_q$ , transformed voltage reference $v_a^*$ and utility voltage $v_a$ | 75  |

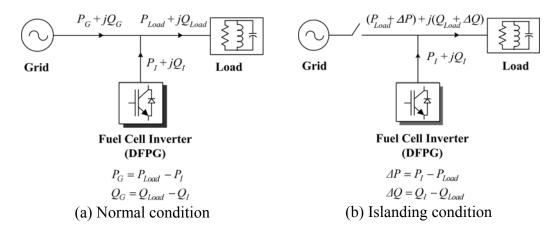

| 3.1  | Interconnection of a DFPG to utility and a load                                                                                     | 78  |

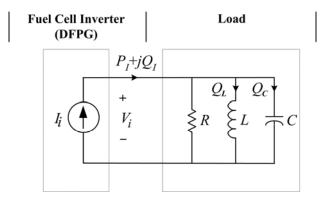

| 3.2  | Equivalent circuit of a DFPG and an RLC load at the instant the utility disconnected                                                | 79  |

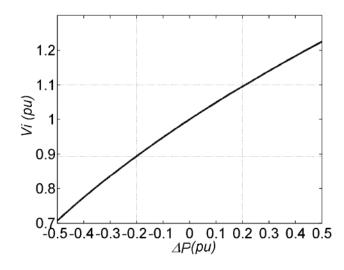

| 3.3  | Variation of islanding voltage $V_i$ (in Fig. 3.2) versus $\Delta P$                                                                | 82  |

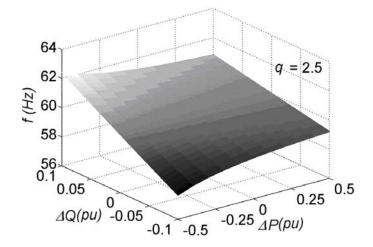

| 3.4  | Islanding frequency                                                                                                                 | 83  |

| 3.5  | Exist of a non-detection zone (NDZ) of over/under voltage and frequency method                                                      | 85  |

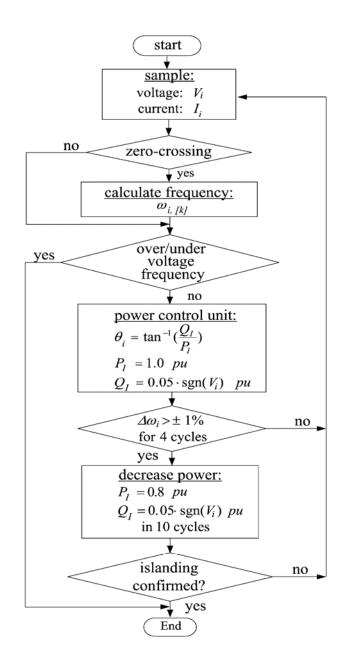

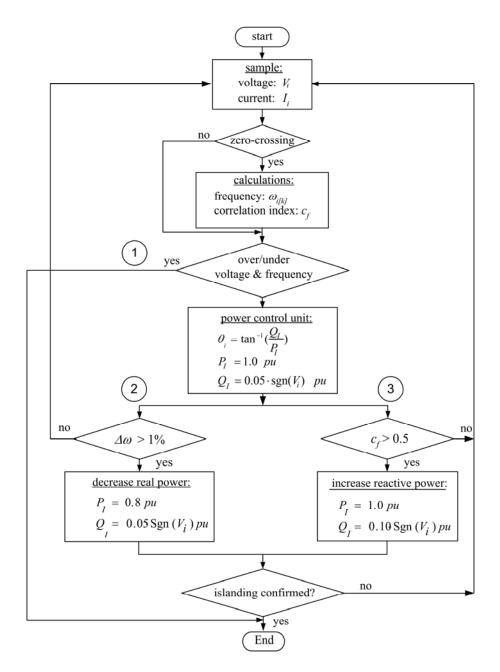

| 3.6  | Flow chart of the robust anti-islanding detection algorithm                                                                         | 87  |

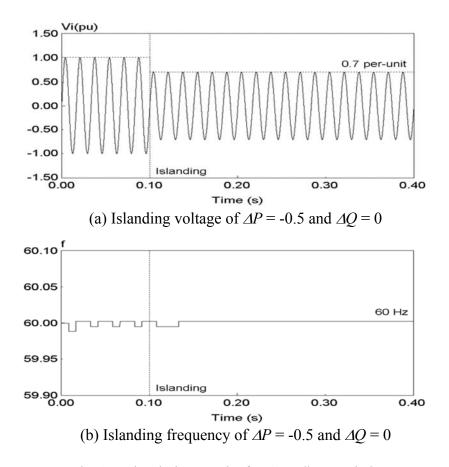

| 3.7  | Simulation results for Case # 1: $\Delta P$ is large                                                                                | 89  |

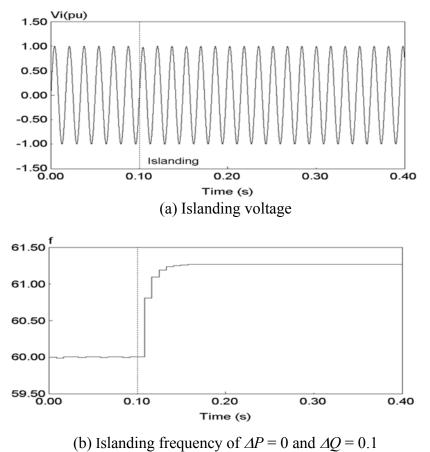

| 3.8  | Simulation results for case #2: $\Delta P$ is small and $\Delta Q$ is larger                                                        | 90  |

| 3.9  | Simulation results for case #3: $\Delta P$ and $\Delta Q$ are small and the proposed power control algorithm is applied             | 91  |

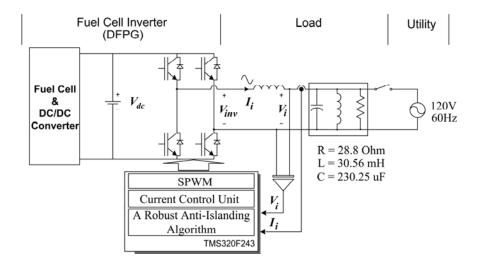

| 3.10 | Experimental set up                                                                                                                 | 92  |

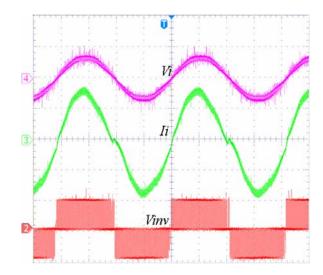

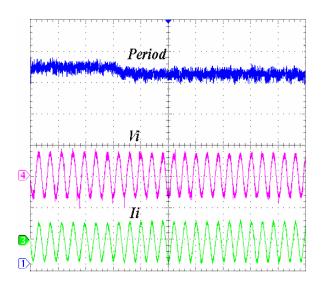

| 3.11 | Experimental result of normal operation of the DFPG connected to utility                                                            | 93  |

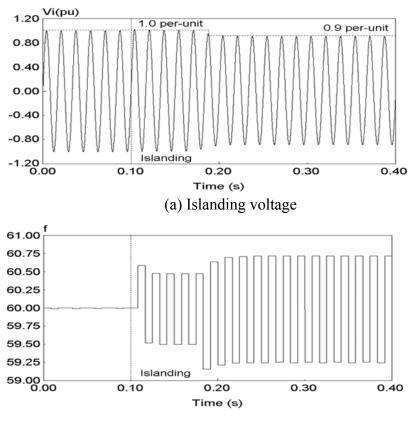

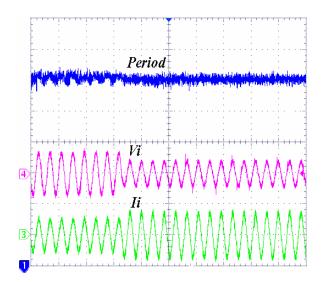

| 3.12 | Experimental result of islanding case #1                                                                                            |     |

| 3.13 | Experimental result of islanding case#2                                                                                             | 94  |

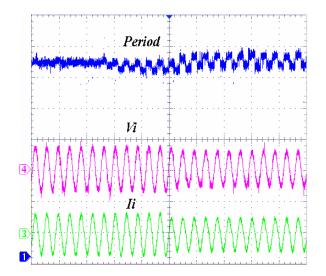

| 3.14 | Experimental result of islanding detection by the developed robust anti-islanding algorithm                                         | 95  |

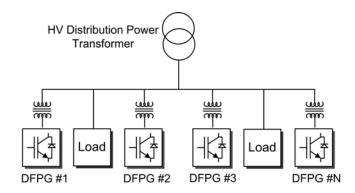

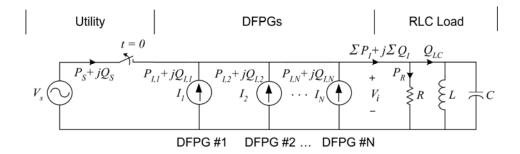

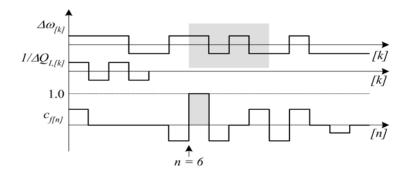

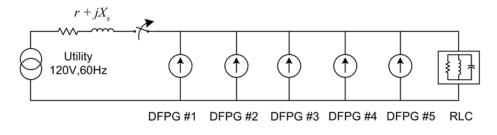

| 4.1  | Mulitple DFPGs independently operating in parallel to utility                                                                       | 98  |

| 4.2  | Equivalent circuit of islanding load                                                                                                | 99  |

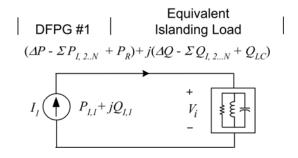

| 4.3  | Non-detection zones (NDZ) of the DFPG #1 under the worst case islanding condition                                                   | 105 |

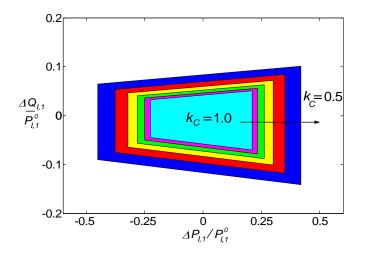

| 4.4  | Illustration of cross correlation index calculation                                                                                 | 107 |

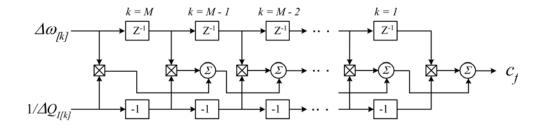

| 4.5  | Discrete-time realization of a cross correlation function                                                                           | 107 |

| 4.6  | Flow chart of the proposed cross correlation method                                                                                 | 109 |

|      |                                                                                                                                     |     |

Page

| FIGUR | RE                                                                            | Page |

|-------|-------------------------------------------------------------------------------|------|

| 4.7   | A circuit diagram of simulation                                               | 110  |

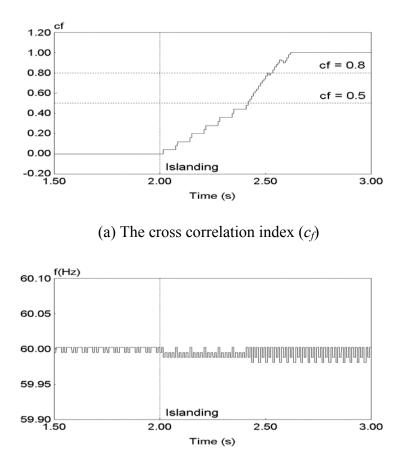

| 4.8   | Simulation results of the proposed cross correlation method ( $k_c = 0.2$ )   | 112  |

| 4.9   | Simulation results of the proposed cross correlation method ( $k_c = 0.01$ ). | 113  |

# LIST OF TABLES

| TABLE | Pag                                                                  |

|-------|----------------------------------------------------------------------|

| 1.1   | Technical specifications of IEEE Std. 1547                           |

| 1.2   | Maximum harmonic current distortion2                                 |

| 2.1   | System parameters and selected gains4                                |

| 2.2   | Phase/sector compare value settings (single phase space vector PWM)5 |

| 2.3   | Phase/sector compare value settings (three-phase space vector PWM)5  |

| 2.4   | System parameters and gain selection of a single phase PWM inverter6 |

| 2.5   | System parameters and selected gains of a three-phase PWM inverter6  |

| 3.1   | Simulation parameters                                                |

| 3.2   | Summary of calculation, simulation and experimental results9         |

| 4.1   | Simulation parameters11                                              |

| 4.2   | Specifications of DFPGs11                                            |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Introduction

Recent developments in fuel technology have contributed to lower cost and better performance of fuel cell stacks [1]. With these positive gains and deregulation as a driving force, the result has been a rapidly increasing number of non utility owned distributed fuel cell powered generations (DFPGs) operating in parallel with utility. Fig. 1.1 shows the typical configuration of a DFPG connected to utility grid [2]. Fuel cells typically generate low output voltage (current). They can be interfaced to utility grid by means of power electronic converters. Use of DFPGs integrated to utility can provide numerous benefits to both utilities as well as customers [3-5]. In utility perspectives, some of the apparent advantages include distribution and transmission capacity relief, load peak shaving, deferral of high cost transmission and distribution (T&D) system upgrades, etc. Utility customers also gain benefits from efficient use of energy from combined heat and power (CHP), enhanced power quality and reliability, tax incentives, etc.

Despite the benefits gained as described, synchronization of DFPGs with utility can cause many serious technical issues that are currently discussed and addressed in the IEEE Std 929-2000 [6] and the IEEE Std. 1547 [7-8]. One of the most serious issues

The journal model for this dissertation is IEEE Transactions on Power Electronics.

Fig. 1.1 Fuel cell power conditioner control system for supplying power to the utility (utility interface)

is islanding phenomenon. Islanding phenomenon is a situation in which a portion of the distribution system is intentionally or accidentally isolated from the utility grid. It is energized by local power generations without control and/or supervision of utility. This phenomenon can result in a number of potential hazards [9-11].

- Maintenance personnel may be harmed when arriving to service the energized isolated feeder.

- Utility customer equipment may be damaged due to uncontrolled voltage and frequency excursion.

- Switching and measuring devices may be damaged due to unsynchronized reclosure.

- Automatic reclosing devices may malfunction.

As a result, this dissertation proposes a robust anti-islanding algorithm for utility interconnection of DFPGs. The proposed algorithm is highly effective in detecting islanding in the presence of a number of DFPGs which are independently operating. Furthermore, it is capable of eliminating a so called "non-detection zone" (NDZ) without causing significant implications to utility.

#### **1.2 Review of Islanding Detection**

Several islanding detection methods have been developed [9-21]. They can be organized into three major categories such as passive, active, and other methods. Their principles, strengths and weaknesses are detailed in the following sections.

#### **1.2.1** Passive Method

The principle of the passive method is to monitor selected system variables such as the voltage at inverter (DFPG) terminal, the frequency of inverter (DFPG) terminal voltage, and other characteristics. The Passive method does not have influences upon utility grid. If observed parameters are out of set limits, an occurrence of islanding can be confirmed.

#### 1.2.1.1 Over/Under Voltage and Frequency Detection

The principle of the over/under voltage and frequency detection is to monitor the voltage at the inverter (DFPG) terminal and the frequency of the inverter (DFPG) terminal voltage [9-13]. A DFPG must be disconnected to prevent equipment damage when the voltage or the frequency are out of recommended thresholds ( $0.88 \le V \le 1.10$  per-unit and  $59.3 \le f \le 60.5$  Hz) specified by the IEEE Std. 929-2000 [6] or the IEEE Std. 1547-2003 [7].

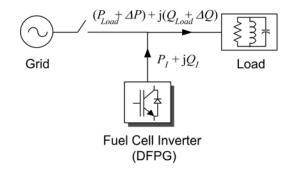

As the basic over/under voltage and frequency protection described, an occurrence of islanding can be detected concurrently. Fig. 1.2 shows real and reactive power mismatch at the instant utility disconnected. Real and reactive power mismatch is the difference between real and reactive power supplied by the inverter (DFPG) and consumed by the load before utility disconnection expressed as,

$$\Delta P = P_I - P_{Load} \tag{1.1}$$

$$\Delta Q = Q_I - Q_{Load} \tag{1.2}$$

Real and reactive power supplied by the inverter (DFPG) can be expressed as,

$$P_I = V_i I_i \cos(\phi) \tag{1.3}$$

$$Q_I = V_i I_i \sin(\phi) \tag{1.4}$$

where  $V_i$  and  $I_i$  are root mean square (RMS) values of the voltage at inverter (DFPG) terminal and the inverter (DFPG) current and  $cos(\phi)$  denotes displacement power factor.

Fig. 1.2 Real and reactive power mismatch at the instant utility disconnected

The load is modeled as parallel RLC components. It is assumed that real power is absorbed by the resistor R and reactive power is consumed by the parallel LC. Real and reactive power of the load can be expressed in a function of voltage and frequency as,

$$P_{Load} = \frac{V_i^2}{R} \tag{1.5}$$

$$Q_{Load} = V_i^2 \left( \frac{1}{\omega \cdot L} - \omega \cdot C \right)$$

(1.6)

In the absence of utility, the voltage and the frequency are uncontrolled. Their new operating points must satisfy balances of real and reactive power between the inverter (DFPG) and the load. From (1.1)-(1.6), the following can be concluded.

- If real power mismatch ΔP is positive (ΔP > 0), the inverter (DFPG) terminal voltage will be higher than the system voltage. But, if real power mismatch ΔP is negative (ΔP < 0), the inverter (DFPG) terminal voltage will be lower than the system voltage for vice versa.</li>

- If reactive power mismatch is positive (△Q > 0), the frequency will be increased until reactive power supplied by the capacitor C balances with that consumed by the inductor L. However, if reactive power mismatch is negative (△Q < 0), the frequency will be decreased for vice versa.</li>

In most cases, real and reactive power mismatch is relatively large ( $\Delta P > \pm 20\%$ or  $\Delta Q > \pm 5\%$ ). After utility disconnected, the voltage and the frequency are immediately out of the thresholds confirming islanding.

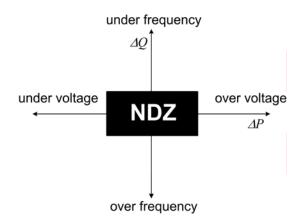

Fig. 1.3 A non-detection zone (NDZ) of over/under voltage and frequency detection method

This method of detection is shown to be simple. However, its principle relies on real and reactive power mismatch at the instant utility disconnected. If both real and reactive power mismatch ( $\Delta P$  and  $\Delta Q$ ) is small, the voltage and the frequency remain in the thresholds and escape the detection. It is commonly known as a non-detection zone (NDZ) shown in Fig. 1.3. Thus, it is concluded that the over/under voltage and frequency detection method is insufficient for islanding detection.

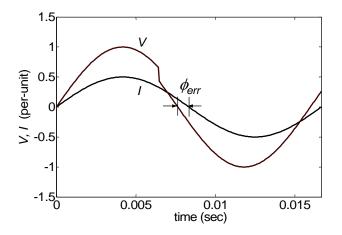

## **1.2.1.2** Phase Jump Detection

The principle of the phase jump detection is to monitor the phase difference (sudden phase jump) between phase of the utility voltage and the inverter (DFPG) current [9-13]. In the presence of utility, utility can be assumed as a stiff voltage source providing sinusoidal voltage at system voltage and frequency. While operating as power conditioning, an inverter (DFPG) regulates sinusoidal waveform current

impressed into utility grid. Phase of the inverter (DFPG) current is synchronized with phase of the utility voltage via phase lock loop circuitry (PLL). However, at the instant the utility disconnected, if real and reactive power mismatch is large, phase of the voltage at inverter (DFPG) terminal is instantaneously shifted so as to balance real and reactive power between the inverter (DFPG) and the load. Fig. 1.4 shows lagging phase error  $\phi_{err}$  occurred due to the presence of an inductive load after utility disconnected. If this phase error exceeds the phase threshold ( $\phi_{err} > \phi_{th}$ ), islanding is now confirmed.

This method of detection is shown to be simple. Phase lock loop (PLL) can be implemented by analog circuitry or software using a digital signal processor (DSP). Size of a non-detection zone (NDZ) can be reduced by setting small phase threshold  $\phi_{th}$ . However, too small phase threshold  $\phi_{th}$  can result in nuisance tripping during startup of large induction motors or switching of power factor correction capacitors. The method also fails when power factor of the load is near unity.

Fig. 1.4 Voltage phase jump after utility is disconnected

#### **1.2.1.3** Voltage Harmonic Detection

The principle of the voltage harmonic distortion detection is to detect total harmonic distortion (THD) of the voltage at inverter (DFPG) terminal [9-13]. In the presence of utility, utility can be considered as a stiff voltage source providing essentially sinusoidal waveform voltage. However, after utility disconnected, voltage harmonic distortion at the point of common coupling (PCC) becomes significant due to interaction between high impedance of islanding loads and harmonic currents from various sources such as inverter (DFPG) itself, nonlinear power electronic load, and nonlinear excitation current of distribution power transformer etc as shown in Fig. 1.5. If the total harmonic distortion (THD) is higher than the threshold, an occurrence of islanding can be confirmed.

Fig. 1.5 Islanding contains RLC load, nonlinear load, and distribution power transformer

This method of detection is effective to detect islanding because it does not rely on real or reactive power mismatch at the instant utility disconnected. However, the method is more computational involved than other methods. In addition, if a formed islanding load has a high quality load factor ( $q = R\sqrt{C/L}$ ), it could serve as a low pass filter having very low impedance for a wide range of frequency. Thus, it results in low total harmonic distortion (THD < 5%) to appear and it possibly leads to failure of the detection. Furthermore, appropriate harmonic threshold is hard to find, hence rendering this method as impractical [14].

#### 1.2.2 Active Method

The principle of active method is to slightly perturb system variables such as the voltage at inverter (DFPG) terminal and/or the frequency of inverter (DFPG) terminal voltage and simultaneously observing their impacts. Islanding is detected if observed variables are forced out of thresholds.

#### **1.2.2.1** Output Power Variation

The principle of the output power variation method is to periodically vary real power output supplied by an inverter (DFPG) to utility [9, 11, 15]. Islanding is detected, if a change in the voltage at inverter (DFPG) terminal escapes the threshold (0.88 < V < 1.10 (per-unit)). Let real power output be expressed in average real power  $P^{0}$  and real power variation  $\Delta P$  as,

$$P = P^0 + \Delta P \tag{1.7}$$

Voltage variation  $\Delta V$  is expressed in a function of real power variation  $\Delta P$  and load real power  $P_{Load}$  (see (1.5)) as,

$$\Delta V = \sqrt{\frac{\Delta P}{P_{Load}} + 1} - 1 \tag{1.8}$$

From (1.8), the real power variation  $\Delta P$  must be set at least ±0.20 (per-unit) so that a change in the voltage at inverter (DFPG) terminal is out of the threshold (0.88 < V < 1.10 (per-unit)) after disconnection of utility, hence confirming an occurrence of islanding.

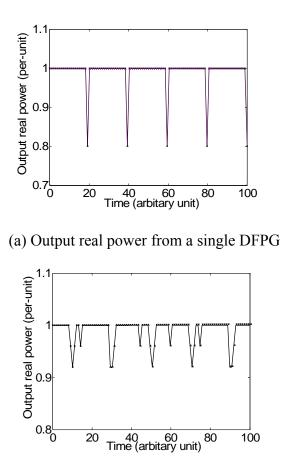

This method of detection is shown to be robust and capable of reducing size of a non-detection zone (NDZ) to zero when a single inverter (DFPG) is connected to utility. Fig. 1.6 (a) shows the real power output of the inverter (DFPG) while supplying the load. The real power variation  $\Delta P = -0.20$  (per-unit) is periodically changed. After utility disconnected, the voltage at inverter (DFPG) terminal is dropped below 0.88 per-unit and islanding is confirmed. But it possibly fails to detect the occurrence of islanding, if multiple inverters (DFPGs) connected to utility are operating independently due to unsynchronized output power variations [9, 11, 15]. Fig. 1.6 (b) shows the real power output from multiple inverters (DFPGs) which are independently operating. It results in inadequate real power mismatch ( $\Delta P < \pm 0.20$  per-unit) and the voltage at inverter (DFPG) terminals remains within the threshold. This method therefore fails to detect islanding. In addition, large real power variation  $\Delta P$  by this method causes poor power quality such as voltage flicker and grid instability.

(b) Net real power output from multiple DFPGs while operating independently Fig. 1.6 Output power variation method

#### **1.2.2.2** Impedance Measurement

The principle of the impedance measurement method is similar to the output power variation method. Real power output is periodically varied while simultaneously determining grid impedance by calculating a rate of change of the voltage at inverter (DFPG) terminal with respect to the inverter (DFPG) current given by (1.9) [9, 11]. Islanding is confirmed, if a significant increase in grid impedance above the threshold is observed.

$$Z = \frac{\Delta V}{\Delta I} \tag{1.9}$$

This method has advantages and disadvantages similar to the output power variation method. However, it requires a precise value of grid impedance which may not be known and available, hence causing this method as impractical.

#### 1.2.2.3 Sliding Mode Frequency Shift

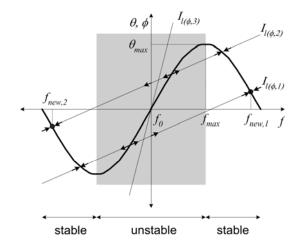

The principle of the sliding mode frequency shift method is to force the frequency of inverter (DFPG) output up/down by controlling the starting phase angle of the inverter (DFPG) current [16-18]. Islanding can be confirmed, if the frequency is out of the threshold (59.3  $\leq f \leq$  60.5 Hz). It is suggested that a sinusoidal function should be used to provide phase information for the current which is expressed as,

$$\theta = \theta_{max} \sin\left(\frac{\pi(f - f_0)}{2(f_{max} - f_0)}\right)$$

(1.10)

where  $\theta_{max}$  is the maximum phase shift corresponding to the maximum frequency  $f_{max}$ .

The system frequency is represented by  $f_0$ . The function of phase angle (1.10) is plotted associated with various load lines shown in Fig. 1.7. In the presence of utility, it is assumed that the inverter (DFPG) supplies constant real power output and zero reactive power output. After utility disconnected, for an inductive load (load line #1,  $I_{l(\phi, I)}$ ), the frequency is immediately increasing while simultaneously phase of the inverter (DFPG) current is controlled in advanced with respect to the load phase angle. It results to further accelerate the frequency moving out of the unstable region (see Fig. 1.7). When the frequency is higher than the maximum frequency  $f_{max}$ , the starting phase angle is controlled in the opposite direction. It is gradually decreased while the frequency is increasing to seek a new operating frequency. The new operating frequency is found where the starting phase angle equals the load phase angle. At this equilibrium point, the reactive power supplied by the inverter (DFPG) is evenly absorbed by the load. This process occurs in the opposite manner with a capacitive load (load line #2,  $I_{l(\phi,2)}$ ). That is, the frequency and the starting phase angle are decreasing until the starting phase angle matches with the load phase angle.

This method is shown to be highly effective to detect islanding and capable of reducing size of a non-detection zone (NDZ) near to zero. It provides good compromise between effectiveness and output power quality. However, it possibly fails to detect islanding, if the starting phase angle matches with the load phase angle at frequency located within the threshold. It also fails, if a rate of change of the starting phase angle with respect to the frequency is less than that of the load line as shown by  $I_{l(\phi,3)}$ .

Fig. 1.7 A sinusoidal function of phase angle and load lines

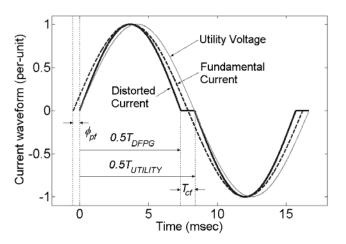

#### **1.2.2.4** Active Frequency Drift

The principle of the active frequency drift method is to force the frequency of inverter (DFPG) output up/down by using positive feedback to accelerate the frequency of the inverter (DFPG) current [9, 11, 19]. Islanding can be confirmed, if the frequency is out of the frequency threshold (59.3  $\leq f \leq 60.5$  Hz). Fig. 1.8 shows the current waveform that implements upward active frequency drift along with its fundamental waveform and utility voltage. With upward active frequency drift, the current waveform is sinusoidal with frequency slightly higher that of a previous positive half cycle. When the inverter (DFPG) current reaches zero, it is held at zero for a chopping fraction  $T_{cf}$  until the next zero crossing of utility voltage occurs. Similarly, during a negative half cycle, the current waveform has a negative half of a sinusoidal waveform with frequency higher than that of a previous cycle. When the current waveform has a negative half of a sinusoidal waveform approaches zero, it is again held constant at zero for a chopping fraction  $T_{cf}$  until the next zero crossing of utility cycle.

Fig. 1.8 Output current waveform implementing upward active frequency drift

While utility is connected, reactive power output is constantly supplied to utility expressed as,

$$Q_I = V_i I_i \sin(\phi_{pf}) \tag{1.11}$$

where  $V_i$  and  $I_i$  are RMS values of the voltage at inverter (DFPG) terminal and the inverter (DFPG) current respectively and  $\phi_{pf}$  represents the phase offset due to perturbing the frequency. It is assumed that the load is represented by parallel RLC elements. Reactive power of the load  $Q_{Load}$  and reactive power mismatch  $\Delta Q$  at instant the utility disconnected (see Fig. 1.1) can be expressed as,

$$Q_{Load} = V_i^2 \left( \frac{1}{\omega \cdot L} - \omega \cdot C \right)$$

(1.12)

$$\Delta Q = Q_I - Q_{Load} \tag{1.13}$$

From (1.11-1.13), it can be concluded in the following.

- If reactive power mismatch is positive ( $\Delta Q > 0$ ), the frequency will be increasing so that the load can supply more reactive power and eventually the reactive power supplied by the inverter (DFPG) balances with reactive power of the load ( $\Delta Q = 0$ ).

- If reactive power mismatch is negative ( $\Delta Q < 0$ ), the frequency will be decreasing so that the load produces less reactive power and eventually the reactive power supplied by the inverter (DFPG) balances with reactive power of the load ( $\Delta Q = 0$ ).

As a result, if the frequency is drifted up/down out of the frequency threshold (59.3 < f < 60.5 Hz), the occurrence of islanding is confirmed. This method of detection

is shown to be highly effective to detect islanding and it can eliminate a non-detection zone (NDZ) near to zero. However, the method fails to detect islanding, if the phase offset generated by perturbing the frequency matches with the load phase angle at frequency within the threshold. In addition, if its use is to be widespread, interventions among them lead to detection failure, unless all inverters (DFPGs) must adopt the same drifting direction.

# 1.2.2.5 Main Monitoring Units with Allocated All-Pole Switching Devices Connected in Series (MSD)

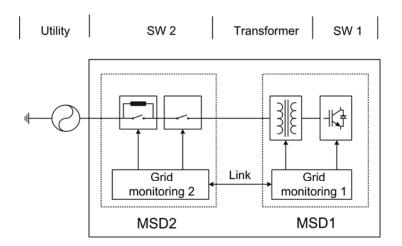

The principle of the main monitoring units with allocated all-pole switching devices is to employ two separate MSD (<u>Mains Monitoring with Allocated Switching Devices</u>) in cascade to perform self test to ensure reliability of both islanding detection devices [10]. Fig. 1.9 shows a block diagram of design of automatic disconnection devices according to VDE 126 [11]. Allocated all pole switches (SW2) in Fig. 1.9 must be electromechanical devices with load break rating such as relays or magnetic contactors.

Multiple islanding detection methods can be used in both of MSD1 and MSD2 such as the over/under voltage and frequency detection method and the grid impedance measurement method. For the grid impedance measurement method, islanding is confirmed, if there is a sudden change in grid impedance larger than 0.5 ohm ( $\Delta Z \ge 0.5$  $\Omega$ ) or grid impedance is higher than 1.25 ohm ( $Z > 1.25\Omega$ ).

Fig. 1.9 Design of automatic disconnection switch in accordance to VDE 126

This method basically has advantages and disadvantage similar to impedance measurement method. Moreover, with the redundant design and automatic self test capability, reliability of the detection is improved and periodic approval of inverters (DFPGs) requested by DNO (Distributed Network Operator) is not required. But dispensable switches (SW2) in the redundant design add additional cost to inverters (DFPGs).

#### **1.2.3** Other Method

Other method employs different detection techniques than passive or active method as described. They are often implemented at utility level. These detection methods include reactance insertion, power line carrier communication (PLCC) and supervisory control and data acquisition (SCADA).

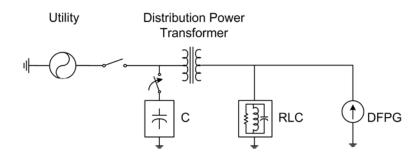

#### **1.2.3.1** Reactance Insertion

The principle of the reactance insertion is to connect a low-value impedance such as a capacitor bank to a distribution feeder within a short delay time after utility is disconnected as shown in Fig. 1.10 [9, 11]. The capacitor bank supplies additional reactive power to the load and unbalances reactive power between the inverter (DFPG) and the load. If the frequency is below the frequency threshold (59.3  $\leq f \leq 60.5$  Hz), an occurrence of islanding is confirmed.

Other types of impedances such as a low-value resistance can be used to unbalance real power between the inverter (DFPG) and the load during the occurrence of islanding. If a drop in the voltage occurred is below the voltage threshold (0.88 < V <1.10 per-unit), islanding is positively confirmed.

This method is highly effective to prevent islanding. A non-detection zone (NDZ) can be eliminated, if a capacitor bank is properly installed and coordinated (with additional time delay). But it has a slow response compared to active method. Furthermore, cost of implementation is expensive because every disconnection switch must be equipped with a switchable capacitor bank.

Fig. 1.10 System configuration of reactance insertion method

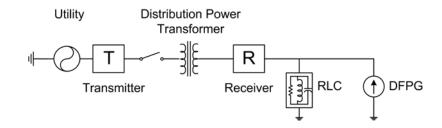

#### **1.2.3.2** Power Line Carrier Communication

The principle of the power line carrier communication (PLCC) is to use a low energy communication signal sent by a transmitter at utility side throughout power distribution network shown in Fig. 1.11 [9, 21]. Line discontinuity is acknowledged and an occurrence of islanding can be confirmed, if a signal cannot be received by a receiver installed at the inverter (DFPG).

A continuous communication signal is preferred since it is more reliable and simpler than an intermittent signal (discrete or digital signal) for continuity test. With an intermittent signal, loss of the signal due to discontinuity or cessation of the transmission cannot be distinguished without encoding and decoding a signal. In addition, the signal should be low frequency signal (i.e., less than 500 Hz) so that it can propagate well in power line without having troubles with line inductance. A sub-harmonic signal is also preferable because it is not mistakenly produced by customer loads.

Use of power line carrier communication has several advantages. It does not degrade power quality. A non-detection zone (NDZ) can be eliminated. It is unaffected by a number of inverters (DFPGs) connected to utility (high penetration level). Furthermore, with existing automatic meter reading (AMR) system, it is possible to use its signal for this purpose in conjunction with an inexpensive receiver. However, such transmitter is uncommon and expensive. It is economical only in high-density distributed generation areas.

Fig. 1.11 System configuration of power line carrier communication method

#### 1.2.3.3 Supervisory Control and Data Acquisition

The principle of the supervisory control and data acquisition (SCADA) is to monitor states of entire distribution system such as voltage, frequency and other characteristics and enable rapid response to eliminate islanding [9, 11]. When an inverter (DFPG) is installed, a voltage-sensing device must be installed in the local part of utility. Voltage information is sent through communication links to a central station. After utility disconnected, if the voltage can be detected from the disconnected area, the occurrence of islanding is confirmed. Corrective measures must be done to eliminate islanding so that utility personnel are not injured while servicing isolated feeders and out of phase reclosure can be avoided.

This method is highly effective to detect islanding and a non-detection zone (NDZ) is eliminated, if the system is properly instrumented and controlled. However, cost of implementation is highly expensive because each inverter (DFPG) installed needs separate instrumentation and communication to send necessary information to a central station.

#### 1.3 IEEE Standard 1547

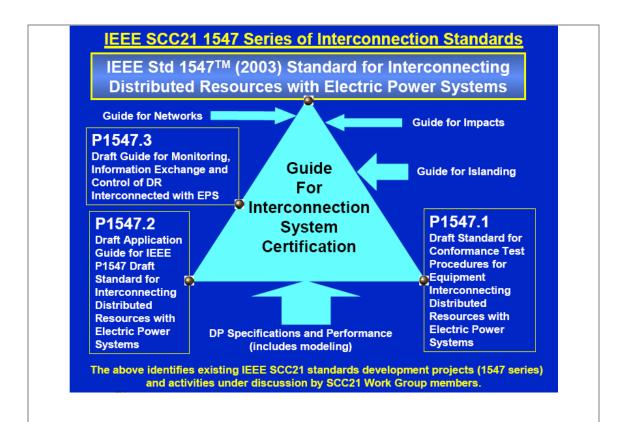

As the interest of use of distributed resources (DR) such as fuel cell (DFPGs) photovoltaic cells, microturbines, energy storages etc operating in parallel to utility is rapidly escalated. It has raised the concerns of having a uniform technical standard for the following reasons – prevent hazards possibly occurred to utility personnel, minimize their impacts on power quality, and avoid conforming to numerous local practices and guidelines.

In response to these concerns, Standard for Interconnecting Distributed Resources (DR) with Electric Power Systems (EPS), IEEE Std. 1547-2003 has been developed by IEEE Standards Coordinating Committee 21 (SCC21). It is the primary interconnection standard that provides system-level technical requirements and specifications needed to interconnect DR with EPS. Other ancillary standards for testing, applications, and communications are now being developed by IEEE work groups as shown in series of interconnection standard in Fig. 1.12.

IEEE Std. 1547-2003 is a uniform standard for interconnection of distributed resources (with aggregate capacity of 10 MVA or less at point of common coupling (PCC)) with EPS as shown in interconnection configuration and definition in Fig. 1.13. It provides requirements relevant to performance, operation, safety consideration, testing, and maintenance of interconnection. Summary of essential interconnection technical specifications and requirements is given in Table 1.1.

**IEEE 1547<sup>™</sup> (2003)** – This standard establishes criteria and requirements for utility interconnection of distributed resources (DR) with electric power systems (EPS)

**P1547.1** – This standard specifies the type, production, and commissioning tests that shall be performed to demonstrate that interconnection functions and equipment of a DR conform to IEEE 1547.

**P1547.2** – This guide provides technical background and application details to support the understanding of IEEE 1547 Standard for Interconnecting DR with EPS.

**P1547.3** – This document provides guidelines for monitoring, information exchange, and control for DR interconnected with EPS

Fig. 1.12 Series of Interconnection Standard IEEE 1547 [20]

Fig. 1.13 Interconnection configuration and definition

| Specifications                                        | Descriptions                                                                                  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Voltage                                               | 0.88 – 1.10 per-unit                                                                          |

| Frequency                                             | 59.3 – 60.5 Hz                                                                                |

| Voltage Flicker                                       | Imperceptible, IEEE 519 – 1992 [B5]                                                           |

| DC Injection                                          | Less than 0.5%                                                                                |

| Harmonics                                             | TDD < 5% (see Table 1.2)                                                                      |

| Islanding                                             | Must be detected within 2 sec.                                                                |

| Synchronization                                       | Must cause voltage fluctuation < 5%                                                           |

| Isolation Device<br>Parallel Device<br>Voltage Rating | Upon request of the area EPS<br>Capable of withstanding up to 220% of<br>system rated voltage |

Table 1.1 Technical specifications of IEEE Std. 1547

| Individual<br>harmonic<br>order h (odd<br>harmonics) | h <11 | 11≤ h <17 | 17≤ h <23 | 23≤ h <35 | h > 35 | Total<br>demand<br>distortion<br>(TDD) |

|------------------------------------------------------|-------|-----------|-----------|-----------|--------|----------------------------------------|

| Percent (%)                                          | 4.0   | 2.0       | 1.5       | 0.6       | 0.3    | 5.0                                    |

Table 1.2 Maximum harmonic current distortion

#### **1.4** Research Objective

As discussed in the introduction, safety of utility personnel and equipment is one of the most serious issues associated with islanding phenomenon. Thus, a robust and reliable anti-islanding algorithm is necessary when more and more DFPGs are connected to utility. In response to this concern, this research is focused on investigation and development of a robust anti-islanding algorithm for utility interconnection of DFPGs.

In the first study, DSP controlled power electronic converters for utility interconnection of distributed fuel cell powered generations (DFPGs) are developed. Current control in a synchronous reference frame (dq-frame) utilizing proportionalintegral (PI) controllers is proposed. The pulse width modulation (PWM) inverters are fully digitally controlled employing a commercially available digital signal processor (DSP). With a high speed DSP, real time control of digital current control in a synchronous frame, phase lock (PLL), and space vector PWM is realizable by implementing via software. Advantages of the proposed current control are capable of achieving zero steady state error, fast dynamic, and supplying high quality output power to utility. Simulation and experimental results of the three-phase PWM inverter rated at 10 kW, 208V/60Hz and the single-phase PWM inverter prototype rated at 0.5 kW, 120V/60Hz show excellent performance.

In the second study, the development of the robust anti-islanding algorithm is explored. The power control algorithm is proposed following the analysis of real and reactive power mismatch. The proposed algorithm continuously perturbs  $\pm 5\%$  the reactive power supplied by the DFPG while monitoring the utility voltage and frequency. If islanding were to occur, noticeable frequency deviation ( $>\pm 1\%$ ) is observed. To further confirm islanding, the output real power is reduced to 80%. Now, if a drop in voltage is below 0.9 per-unit, islanding is positively confirmed and the DFPG is safely disconnected. This method of detection is shown to be robust, fast acting (operable in one cycle) and significantly reduces the non-detection zone (NDZ) compared to all other detection methods. Several possible islanding conditions are simulated and verified with analysis. Experimental results confirm effectiveness of the proposed algorithm.

In the third study, an improved anti-islanding algorithm for utility interconnection of multiple DFPGs is presented. As shown via analysis, multiple DFPGs independently operating in parallel to utility possibly result the power control algorithm failed to detect islanding due to ( $\pm$ 5%) the reactive power average out. Thus, the cross correlation method is proposed and implemented in conjunction with the power control algorithm. While the power control algorithm continuously perturbs ( $\pm$ 5%) the reactive power supplied by the DFPG, the cross correlation index of a rate of change of the frequency deviation  $\Delta \omega$  with respect to the ( $\pm$ 5%) reactive power is calculated to confirm an occurrence of islanding. If islanding were to occur, the crosscorrelation index is higher than 50%, the proposed algorithm further initiates  $(\pm 10\%)$ reactive power increase and continues to calculate the correlation index. If the cross correlation index exceeds 80%, the occurrence of islanding is positively confirmed. The proposed method is shown to be robust and capable of detecting the occurrence of islanding in the presence of several DFPGs independently operating in parallel to the same utility grid. The viability of the cross-correlation method is demonstrated by the simulation of multiple inverters (DFPGs) under the worst case islanding condition and the results confirm effectiveness of the proposed method.

## **1.5** Dissertation Outline

The content of this dissertation is organized in five chapters in the following manner. Chapter I, islanding phenomenon and its associated potential hazards are introduced and presented. Review of islanding detection methods is discussed and provided as a background. Standard related to interconnection of distributed resources (DR) with area of electric power system (EPS) is also presented along with some important specifications and requirements related to this research. Finally, research objectives are presented and discussed.

Chapter II, DSP controlled power electronic converters are developed for utility interconnection of DFPGs. Current control in a synchronous frame (dq-frame) utilizing proportional-integral (PI) controllers is proposed. Analysis and design of the synchronous frame current controller are detailed. DSP implementation combines space vector pulse width modulation (PWM), phase lock, synchronous frame current control etc. Simulation and experimental results are presented and discussed.

Chapter III, the development of a robust anti islanding algorithm is explored. Analysis of islanding voltage and frequency is shown. The power control anti-islanding algorithm is proposed following the analysis. Several possible islanding conditions are simulated and verified with analysis and experimental results are presented and discussed.

Chapter IV, an improved anti-islanding algorithm for utility interconnection of multiple DFPGs is presented. Analysis of islanding voltage and frequency is shown. The cross correlation method is proposed and used in conjunction with the power control algorithm. Simulation results of multiple DFPGs independently operating in parallel with utility under the worst case islanding condition are presented and discussed.

Chapter V, the contributions of this research in the area of islanding detection is concluded. Finally, some suggestions are also provided for future work.

## **CHAPTER II**

# DSP CONTROLLED POWER ELECTRONIC CONVERTERS FOR UTILITY INTERCONNECTION OF DISTRIBUTED FUEL CELL POWERED GENERATIONS

### 2.1 Introduction

Due to the present high electricity demand, utility deregulation, and market uncertainty, distributed fuel cell powered generations (DFPGs) are considered as a technology of choice providing electricity economically, efficiently and environmentally safely. With their clean performance, high power density and modularity, they are allowed to be sited near to electricity users and supply electricity through existing public utility grid. DFPGs operating in parallel with utility can provide numerous potential benefits such as augmenting capacities of distribution systems, deferring capital investments on distribution and transmission (T&D) systems, and improving power quality and system reliability.

Fuel cells are electrochemical energy conversion devices similar to batteries. They generate variable and low output voltage (current). Thus, they are unable to connect to utility directly. However, they can be interfaced and supply power to utility by means of power electronic converters [22]. Fig. 2.1 show system integration of fuel cell power conditioning system which comprising of a fuel cell stack associated with a dc-dc converter and a widely used DC-AC pulse width modulation (PWM) inverter connected to utility grid. A single phase fuel cell power conditioning system is often selected for low power applications (< 3 kW) i.e., residential applications. For higher power applications i.e., commercial or industrial applications, a three-phase fuel cell power condition system is preferable.

(a) System integration of single phase fuel cell power conditioning system

(b) System integration of three-phase fuel cell power conditioning system

Fig. 2.1 System integration of fuel cell power conditioning systems

While cost of digital signal processor (DSP) has been drastically decreased since its introduction in 1980's, use of DSP based control of power electronic converters has been gaining popularity [23]. With commercially available high speed DSP core processors, real time control of power electronic converters formerly processed by analog circuitry is now realizable by implementing in software. The advantages of successfully performing these functions are in the followings.

- Performance of power electronic converters is significantly enhanced and less dependent on device technology and environmental variations.

- Cost of power electronic converters is less expensive by mass-production of switching devices embedded with DSP controllers.

- Flexibility and ability to implement advance control algorithms are realizable via programmability.

- High power quality and system reliability can be obtained.

In this chapter, DSP controlled power electronic converters for utility interconnection of DFPGs using commercial DSP are developed. The PWM inverters are controlled in current mode and able to supply high quality output real and reactive power to utility. Current control in a synchronous frame (dq-frame) utilizing proportional-integral (PI) controllers is proposed to ensure sinusoidal waveform current impressed to utility grid. Analysis and design of the PI-controller are discussed. DSP implementation combines space vector pulse width modulation (PWM), phase lock (PLL), closed loop current control etc. Advantages of the proposed current control are capable to achieve zero steady state error, fast dynamic response, and high quality output power with low current distortion. Simulation and experimental results of the fuel cell based single-phase and three-phase power conditioning systems, employing commercial Texas Instrument DSP TMS320-F243 shows excellent performance.

## 2.2 DSP Based Control

Implementation of power electronic converters traditionally employs analog control. Lower cost compared to DSP based control is seen as a major advantage in the past. Despite the cost competitiveness, analog control has many drawbacks such as a number of component counts and connections, long-term component instability (aging) and thermal drift. These adverse effects directly degrade performance of converters and cost expensive routine maintenance. In addition, analog control typically is designed specifically for a single converter model. As a result, converter upgrade and scalability are impossible without replacing new hardware.

Currently, price of a single DSP chip is drastically dropped to a few dollars but its performance and capability of executing millions of instructions (MIPS) is significantly increased. Fig. 2.2 shows a block diagram of a DSP controller TMS320-F243 from Texas Instrument. It has a 16 bit fixed-point DSP core which is integrated with several specific peripherals on-chip including – 2 general purpose timers and 8 PWM generators, 3 capture units, 16 channels 10 bit ADC, CAN Interface, SPI, SCI etc. Integration of a high speed DSP core with specific peripherals does not only simplify design process but also offers flexibility via programmability. Thus, advance control algorithms can be implemented and upgraded by a short period of development time.

With all advantages mentioned above, the DSP based control now becomes preferable to analog counterpart so that higher-performance and lower cost of power electronic converters for utility interconnection application could be realized.

Fig. 2.2 A simplified block diagram of a digital signal processor TMS320-F243

## 2.3 Control Topology

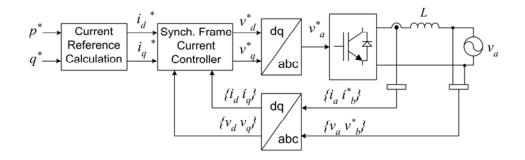

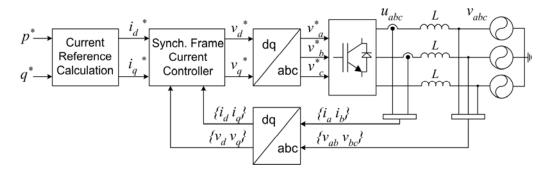

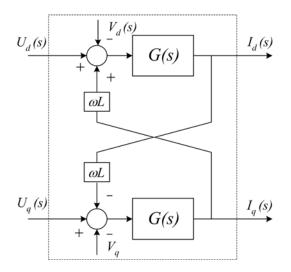

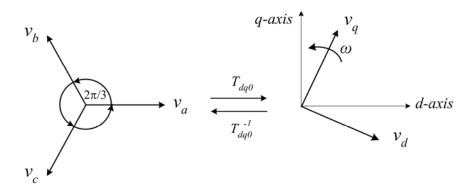

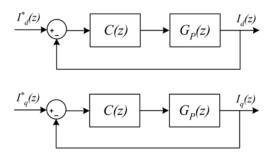

The objective of power electronic converters for utility interconnection of DFPGs is to supply high quality power output to utility grid. In compliance with the IEEE Std. 929-2000 [6] and the IEEE Std. 1547-2003 [7], the real power output is maintained constant to minimize current and/or voltage harmonic distortion at the point of interconnection and the reactive power output is regulated to zero to achieve power factor near unity. Fig. 2.3 shows the control topology employing synchronous frame current control. DC-AC PWM inverters are operated in current mode. The inverter currents are transformed into a synchronous frame by Park's transformation and regulated in dc-quantity corresponding to the current references  $i^*_{(d,q)}$ . In the following stage, the voltage references in dc-quantities  $v^*_{(d,q)}$  which being processed by PI controllers are transformed into a stationary frame by the inverse of Park's transformation and utilized as command voltages for generating high frequency pulse width modulated (PWM) voltage ensuring high quality power with low current harmonic distortion supplied to utility.

With the control topology described, fuel cell power conditioning system is capable of supplying sinusoidal waveform current into utility grid. Zero steady state error of inverter current can be achieved [24]. In addition, real and reactive output power can be independently controlled [25], hence resulting power conditioning system furthering capable of providing other ancillary services such as reactive power compensation (voltage support).

(a) Control topology of a single phase PWM inverter

(b) Control topology of a three-phase PWM inverter

Fig. 2.3 Control topology

## 2.4 Proposed Digital Current Control in a Synchronous Frame

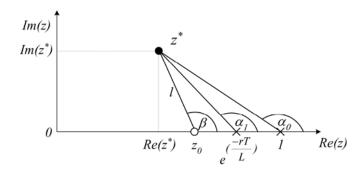

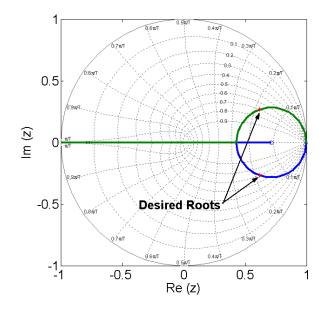

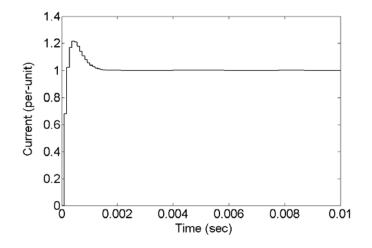

In this section, modeling of a single phase and a three-phase PWM inverter and design of synchronous frame current control in discrete time domain based on Root Locus method are detailed.

## 2.4.1 Modeling of PWM Inverters

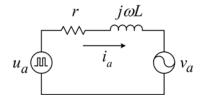

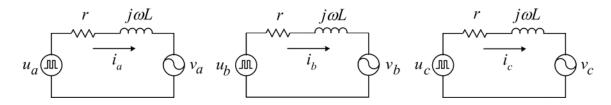

Fig. 2.4 shows per-phase equivalent circuits of a single-phase and a threephase PWM inverter. By neglecting high switching frequency components, a DC-AC PWM inverter can be represented as a sinusoidal voltage source which connects to utility through a L filter [26]. With this configuration, the PWM inverter can be modeled as the first-order system in frequency domain. An input-output transfer function of the PWM inverter in a synchronous frame can be derived by choosing inductor current as a state variable and voltage generated by the PWM inverter as a control input.

(a) Equivalent circuit of a single phase PWM inverter

(b) Equivalent circuit of a three-phase PWM inverter

Fig. 2.4 Per-phase equivalent circuits of DC-AC PWM inverters

## 2.4.1.1 A Single Phase PWM Inverter

From Fig. 2.4 (a), let the utility voltage  $v_a$  and the inverter current  $i_a$  be expressed as,

$$v_a = \sqrt{2} \cdot V_{rms} \cdot \sin(\omega \cdot t) \tag{2.1}$$

$$i_a = \sqrt{2} \cdot I^*_{rms} \cdot \sin(\omega \cdot t + \phi) \tag{2.2}$$

where  $V_{rms}$  is a root-mean-square (RMS) value of the utility voltage and  $I_{rms}^*$  is a RMS value of the current reference.

The inverter voltage  $u_a$  is derived in a function of the inverter current  $i_a$  and the utility voltage  $v_a$  expressed as,

$$u_a = r \cdot i_a + L \frac{di_a}{dt} + v_a \tag{2.3}$$

In addition to an actual circuit (phase A) of the inverter, a virtual circuit (phase B) operating 90° out of phase with respect to the actual circuit (phase A) is introduced and expressed as,

$$u_b^* = r \cdot i_b^* + L \frac{di_b^*}{dt} + v_b^*$$

(2.4)

where

$$v_b^* = \sqrt{2} \cdot V_{rms} \cdot \sin(\omega \cdot t + \frac{\pi}{2})$$

(2.5)

$$i_b^* = \sqrt{2} \cdot I^*_{rms} \cdot \sin(\omega \cdot t + \frac{\pi}{2} + \phi)$$

(2.6)

From (2.1) and (2.2), they are formed into two-phase system and expressed as,

$$\begin{bmatrix} u_a \\ u_b^* \end{bmatrix} = r \cdot \begin{bmatrix} i_a \\ i_b^* \end{bmatrix} + L \frac{d}{dt} \begin{bmatrix} i_a \\ i_b^* \end{bmatrix} + \begin{bmatrix} v_a \\ v_b^* \end{bmatrix}$$

(2.7)

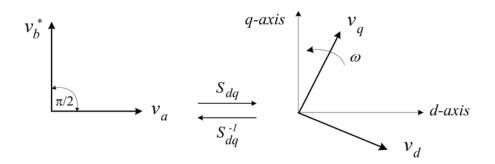

To find an input-output transfer function (2.7) in a synchronous frame, the system equation (2.7) must be transformed by two-phase Park's transformation  $S_{dq}$  expressed as,

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{bmatrix} \cos(\omega \cdot t) & -\sin(\omega \cdot t) \\ \sin(\omega \cdot t) & \cos(\omega \cdot t) \end{bmatrix} \cdot \begin{bmatrix} v_a \\ v_b \end{bmatrix}$$

(2.8)

or

$$\mathbf{v}_{dq} = \mathbf{S}_{dq} \cdot \mathbf{v}_{ab} \tag{2.9}$$

and its inverse also holds

$$\boldsymbol{v}_{ab} = \boldsymbol{S}_{dq}^{-1} \cdot \boldsymbol{v}_{dq} \tag{2.10}$$

Fig. 2.5 A transformation diagram using two-phase Park's transformation

Fig. 2.5 shows a transformation diagram between a stationary frame and a synchronous frame using two-phase Park's transformation. In a synchronous frame, a direct axis (d-axis) is lagged a quadrature axis (q-axis) by 90°. Since the dq-axis rotates in counter clockwise at the system frequency, voltage and current variables transformed into a synchronous frame become dc-quantity.

Let the system equation (2.7) be transformed to a synchronous frame by twophase Park's transformation (2.8) expressed as,

$$S_{dq}\begin{bmatrix}u_a\\u_b\end{bmatrix} = r \cdot S_{dq}\begin{bmatrix}i_a\\i_b\end{bmatrix} + L\frac{d}{dt}\left(S_{dq}\begin{bmatrix}i_a\\i_b\end{bmatrix}\right) + S_{dq}\begin{bmatrix}v_a\\v_b\end{bmatrix}$$

(2.11)

Differentiation of the product of Park's transformation and the inverter currents  $i_{\{a,b\}}$  is derived by calculus rules as,

$$S_{dq}\begin{bmatrix}u_{a}\\u_{b}\end{bmatrix} = r \cdot S_{dq}\begin{bmatrix}i_{a}\\i_{b}\end{bmatrix} + L \cdot \left(\frac{dS_{dq}}{dt}\begin{bmatrix}i_{a}\\i_{b}\end{bmatrix} + S_{dq}\frac{d}{dt}\begin{bmatrix}i_{a}\\i_{b}\end{bmatrix}\right) + S_{dq}\begin{bmatrix}v_{a}\\v_{b}\end{bmatrix}$$

(2.12)