# RELIABILITY-YIELD ALLOCATION FOR SEMICONDUCTOR INTEGRATED CIRCUITS: MODELING AND OPTIMIZATION

A Dissertation

by

### CHUNGHUN HA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

August 2004

Major Subject: Industrial Engineering

### **RELIABILITY-YIELD ALLOCATION FOR SEMICONDUCTOR**

### **INTEGRATED CIRCUITS:**

### MODELING AND OPTIMIZATION

A Dissertation

by

### CHUNGHUN HA

### Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved as to style and content by:

Way Kuo (Chair of Committee)

Bryan L. Deuermeyer (Member) Daniel W. Apley (Member)

Jianer Chen (Member) Mark L. Spearman (Head of Department)

August 2004

Major Subject: Industrial Engineering

#### ABSTRACT

Reliability-Yield Allocation for Semiconductor Integrated Circuits: Modeling and Optimization. (August 2004) Chunghun Ha, B.A., Yonsei University; M.S., Texas A&M University

Chair of Advisory Committee: Dr. Way Kuo

This research develops yield and reliability models for fault-tolerant semiconductor integrated circuits and develops optimization algorithms that can be directly applied to these models. Since defects cause failures in microelectronics systems, accurate yield and reliability models considering these defects as well as optimization techniques determining efficient defect-tolerant schemes are essential in semiconductor manufacturing and nanomanufacturing to ensure manufacturability and productivity. The defect-based yield model considers various types of failures, fault-tolerant schemes such as hierarchical redundancy and error correcting code, and burn-in effects, simultaneously. The reliability model counts on carry-over single-cell failures accompanied by the failure rate of the semiconductor integrated circuits under the assumption of an error correcting code policy. The redundancy allocation problem, which seeks to find an optimal allocation of redundancy that maximizes system reliability, is one of the representative problems in reliability optimization. The problem is typically formulated as a nonconvex integer nonlinear programming problem that is nonseparable and coherent. Two iterative heuristics, tree and scanning heuristics, and variants are studied to obtain local optima and a branch-and-bound algorithm is proposed to find the global optimum for redundancy allocation problems. The proposed algorithms engage a multiple-search paths strategy to accelerate efficiency. Experimental results of these algorithms indicate that they are superior to the existing algorithms in terms of computation time and solution quality. An example of memory semiconductor integrated circuits is presented to show the applicability of both the yield and reliability models and the optimization algorithms to fault-tolerant semiconductor integrated circuits.

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Professor Way Kuo, who provided guidance, encouragement in my research, and continuous financial support during this study. Special thanks go to my advisory committee Professor Bryan L. Deuermeyer, Professor Daniel A. Apley, and Professor Jianer Chen for their continuous attention. I have learned much from those individuals which was of value in completing this dissertation as well as of help in cultivating my career.

My fellow graduate students, Wen Luo, Jung Yoon Hwang, Linda Maria, Dini Sunardi, and Hsiang Lee deserve my thanks for their valuable comments and technical discussions on this research.

This dissertation is devoted to my parents, Jeong Kwang Ha and Jeong Ja Jeon. I could not have finished this research without their endless love, encouragement, and support. I am also indebted to my wife, Seong Hee Kim, for her sacrifice and support, and my daughter, Yeo Heun Ha, for the happiness and joy she brings to my life. I also want to thank to my parents-in-law for their continuous help to my family.

### NOMENCLATURE

#### YIELDS

- $Y_{MFT}$  manufacturing yield of a semiconductor integrated circuit

- $Y_{WP}$  yield at wafer production stage

- $Y_{FAB}$  yield at wafer fabrication stage

- $Y_{AP}$  yield at assembly and packaging stage

- $Y_{BI}$  yield at burn-in and final test stage

- $Y_{POI}$  the Poisson yield model

- $Y_{NB}$  the negative binomial yield model

- $Y_{YD}$  yield related to yield defects

- $Y_{BD}$  yield related to burn-in defects

- $Y_{IC}$  yield of a semiconductor integrated circuit

- $Y_{PC}$  yield of peripheral circuits

- $Y_{MB}$  yield of a memory block

- $Y_{BF}$  yield related to block failures

- $Y_{SC}$  yield related to single cell failures

- $Y_{BI}$  burin-in yield

- $Y_{DC}$  yield of supporting circuits in a memory block

- $Y_{MA}$  yield of memory segments in a memory block

- $Y_{LF}$  yield related to line failures in a memory block

| $Y_{SCN}$ | yield | of a | single | $\operatorname{cell}$ | without | an | ECC |

|-----------|-------|------|--------|-----------------------|---------|----|-----|

|           |       |      |        |                       |         |    |     |

$Y_{BDC}$  yield of supporting circuits at a block redundancy

$Y_{BLF}$  yield related to line failures in a block redundancy

- $Y_{BM}$  yield of a block module

- $Y_{BR}$  yield of a block redundancy

$Y_{ICN}$  yield of a integrated circuit without fault-tolerance

### RELIABILITIES

- $R_{IC}$  reliability of a integrated circuit in an useful life period

- $R_{NC}$  reliability of non-memory components in a chip

$R_{SC}$  reliability of memory segments in a chip

### AREAS

| $A_{chip}$ total are | ea of a chip |

|----------------------|--------------|

|----------------------|--------------|

- $A_{IC}$  total area of IC

- $A_{PC}$  area of peripheral circuits per HALF

- $A_{MB}$  area of a memory block

- $A_{MB0}$  area of a memory block without fault-tolerance

- $A_{BR}$  area of a block redundancy

- $A_{BR0}$  area of a block redundancy without fault-tolerance

- $A_{WL}$  area of a word line

- $A_{BL}$  area of a bit line

- $A_{BWL}$  area of a word line at a block redundancy

$A_{BBL}$  area of a bit line at a block redundancy

- $A_c$  average critical area of all sizes of defects

- $A^c_{\Phi}$  critical area for area  $\Phi$

### FUNCTIONS

- R(t) reliability function at time t

- $\mu(t)$  failure rate at time t

- h(t) hazard rate or instantaneous failure rate at time t

- D(x) defect density for defect size x

- $A_c(x)$  critical area for defect size x

- $f_s(x)$  probability density function for defect size x

- pof(x) probability of failure for defect size x

### PARAMETERS

| x           | defect size, diameter of a defect                               |

|-------------|-----------------------------------------------------------------|

| $x_0$       | the size of a defect with the highest probability of occurrence |

| $s_0$       | the size of a critical defect                                   |

| $D_0$       | average defect density for all sizes of defects                 |

| $\lambda$   | the average number of defects (faults)                          |

| $\lambda_i$ | the average number of $i$ type defects (faults)                 |

| $\alpha$    | clustering factor for the negative binomial yield model         |

| $lpha_i$    | clustering factor of $i$ type failures                          |

| $\gamma$    | a ratio constant for a burn-in yield model                      |

| $\mu_{NC}$ | failure rate of non-memory components in a chip                    |

|------------|--------------------------------------------------------------------|

| $\mu_{SC}$ | failure rate of memory segments in a chip                          |

| $t_0$      | mission time of an integrated circuit                              |

| $N_{mb}$   | the number of memory blocks                                        |

| $N_{wlc}$  | the total number of memory words at a chip                         |

| $N_{bm}$   | the number of block modules with the same size of block redundancy |

| $N_{wl}$   | the number of word lines at a memory block                         |

| $N_{bl}$   | the number of bit lines at a memory block                          |

| $N_{tbw}$  | the total number of bits in in a memory word                       |

| $N_{cbw}$  | the number of correctable bits in a memory word                    |

| $N_{par}$  | the number of parity bits in a memory word                         |

| $N_{bwl}$  | the number of word lines at a block redundancy                     |

| $N_{bbl}$  | the number of bit lines at a block redundancy                      |

### VARIABLES

| $n_{br}$  | the number of block redundancies                        |

|-----------|---------------------------------------------------------|

| $n_{wl}$  | the number of row redundancies                          |

| $n_{bl}$  | the number of column redundancies                       |

| $n_{bwl}$ | the number of row redundancies at a block redundancy    |

| $n_{bbl}$ | the number of column redundancies at a block redundancy |

| $n_{ecc}$ | existence of ECC                                        |

### TABLE OF CONTENTS

### CHAPTER

| Ι   | INTRODUCTION                                                                                                                                                                                          | 1                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| II  | DEFECTS AND DEFECT MANAGEMENT                                                                                                                                                                         | 8                          |

|     |                                                                                                                                                                                                       | 8                          |

| III | YIELD AND RELIABILITY MODELS                                                                                                                                                                          | 7                          |

|     | III.2.Reliability of Semiconductor Integrated Circuits1III.3.Defect Size, Defect Density, and Critical Area2III.4.Poisson and Negative Binomial Yield Models2III.5.Defect-based Burn-in Yield Models2 | 8<br>9<br>2<br>5<br>9<br>3 |

| IV  | MODELING OF FAULT-TOLERANT MEMORY INTEGRATEDCIRCUITS3                                                                                                                                                 | 6                          |

|     | IV.2.Yield Model with Redundancy3IV.3.Yield Model with Various Types of Failures4IV.4.Yield Model with ECC4                                                                                           | 6<br>9<br>0<br>1           |

| V   | OPTIMIZATION OF YIELD AND RELIABILITY 5                                                                                                                                                               | 2                          |

|     | V.2. Formulation of Optimization Problems                                                                                                                                                             | $\frac{2}{3}$              |

| VI  | EXACT ALGORITHM FOR REDUNDANCY ALLOCATION 5                                                                                                                                                           | 9                          |

|     | VI.2.Multi-path Branch-and-Bound Method6VI.3.Numerical Examples6                                                                                                                                      | 3<br>6<br>9<br>5           |

| VII | HEURISTIC FOR REDUNDANCY ALLOCATION 8                                                                                                                                                                 | 0                          |

|        | VII.1.   | Definitions and Notation               | 84  |

|--------|----------|----------------------------------------|-----|

|        | VII.2.   | Steepest Ascent Rate Heuristic Method  | 85  |

|        | VII.3.   | Tree Heuristic Method                  | 86  |

|        | VII.4.   | Scanning Heuristic Method              | 91  |

|        | VII.5.   | Combinations of Heuristic Methods      | 94  |

|        | VII.6.   | Computational Complexity of Heuristics | 96  |

|        | VII.7.   | Numerical Experimentation              | 98  |

| VIII   | CASE STU | JDY: REDUNDANCY ALLOCATION OPTIMIZA-   |     |

|        | TION FOR | R MEMORY INTEGRATED CIRCUITS           | 108 |

|        | VIII.1.  | Optimization Problems                  | 108 |

|        | VIII.2.  | Numerical Experimentation              | 111 |

| IX     | CONCLUI  | DING REMARKS                           | 120 |

| REFERE | NCES     |                                        | 123 |

| VITA . |          |                                        | 130 |

## Page

### LIST OF TABLES

| TABLE |                                                                                             | Page |

|-------|---------------------------------------------------------------------------------------------|------|

| 1     | Formulas for Yield and Reliability Calculation                                              | 51   |

| 2     | Parameters Used in Example II                                                               | 73   |

| 3     | Comparison of Computation Time for Three Algorithms                                         | 78   |

| 4     | History of Iteration Heuristics for Redundancy Allocation                                   | 82   |

| 5     | Iterative Heuristic Classification by Advantage                                             | 95   |

| 6     | Experimental Results of OR for Various Heuristics                                           | 104  |

| 7     | Experimental Results of AAE for Various Heuristics                                          | 104  |

| 8     | Experimental Results of MAE for Various Heuristics                                          | 105  |

| 9     | Experimental Results of the Average Computation Time for Var-<br>ious Heuristics (Absolute) | 105  |

| 10    | Experimental Results of SR for Various Heuristics                                           | 106  |

| 11    | Experimental Results of ARE for Various Heuristics                                          | 106  |

| 12    | Experimental Results of MRE for Various Heuristics                                          | 107  |

| 13    | Experimental Results of the Average Computation Time for Var-<br>ious Heuristics (Relative) | 107  |

| 14    | Basic Parameters for Calculating Yield and Reliability                                      | 111  |

| 15    | Optimal Allocations for the Various Conditions                                              | 119  |

### LIST OF FIGURES

| FIGURI | ${\mathfrak E}$                                                                     | Page |

|--------|-------------------------------------------------------------------------------------|------|

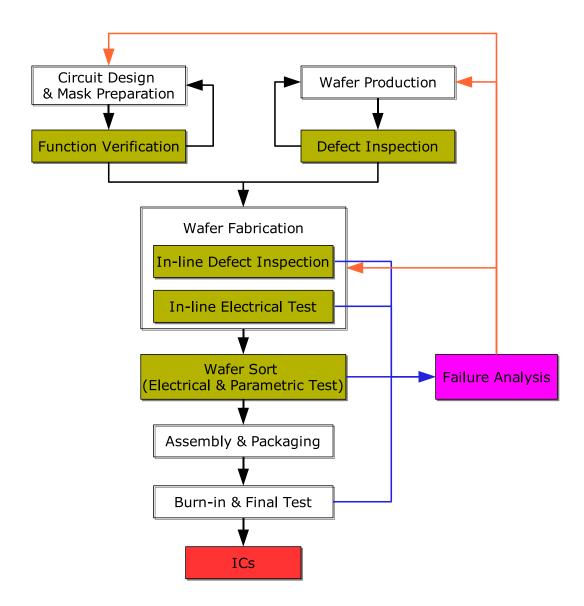

| 1      | Manufacturing and Inspection Processes of Semiconductor Inte-<br>grated Circuits    | 9    |

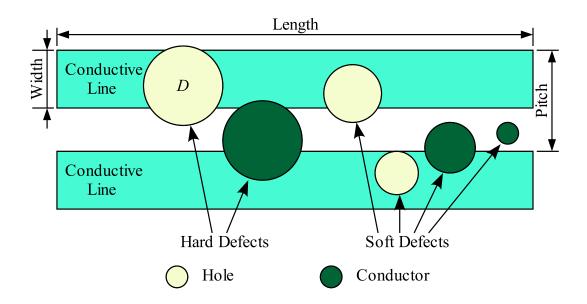

| 2      | Hard and Soft Defects at an Intra-Layer                                             | 11   |

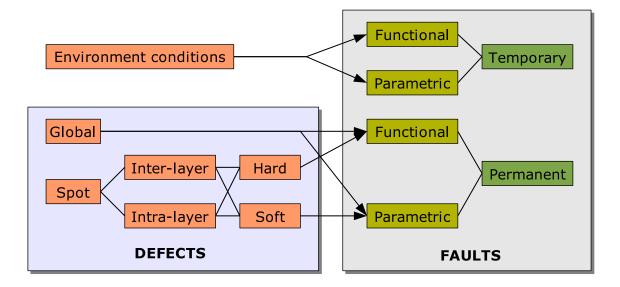

| 3      | Possible Combinations of Defects and Faults                                         | 13   |

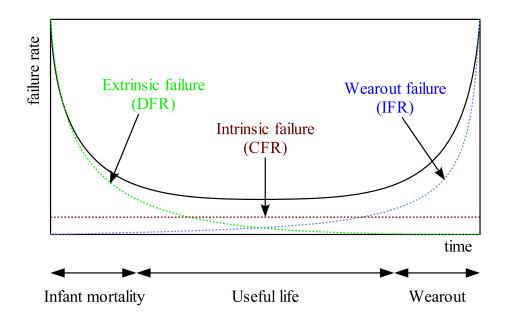

| 4      | Bathtub Shape Failure Rate                                                          | 22   |

| 5      | Distribution and Classification According to Defect Size                            | 23   |

| 6      | Schematic Diagram of a Typical Memory Integrated Circuit                            | 37   |

| 7      | Relationship of Yield, Reliability, Failure Type, and Fault-Tolerant<br>Scheme      | 38   |

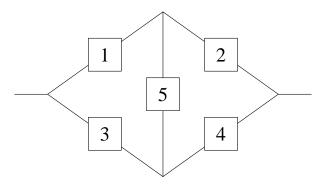

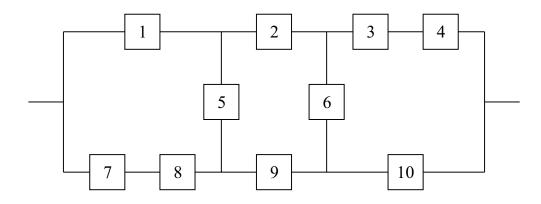

| 8      | A Bridge System                                                                     | 70   |

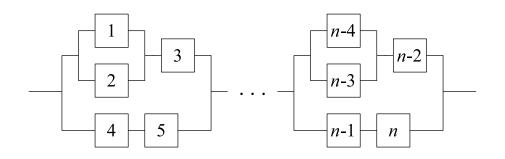

| 9      | A HSP System                                                                        | 73   |

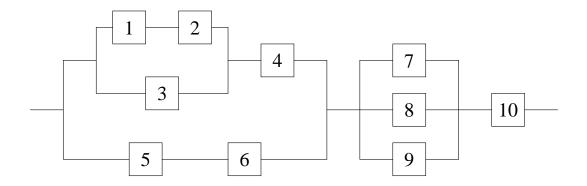

| 10     | A Series of HSP Systems                                                             | 76   |

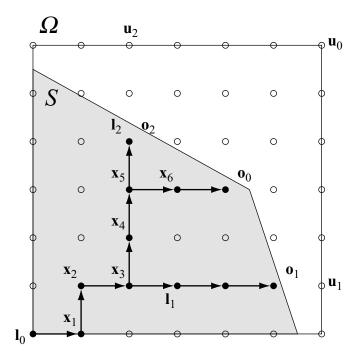

| 11     | Graphical Example of a Tree Heuristic                                               | 88   |

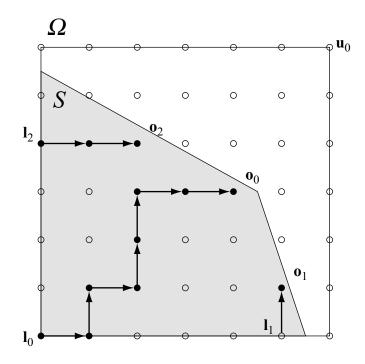

| 12     | Graphical Example of a Scanning Heuristic                                           | 93   |

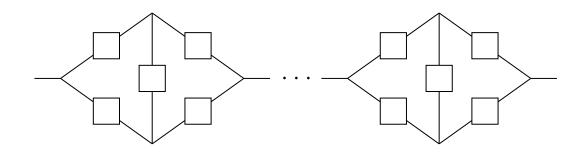

| 13     | A Series of Bridge Systems                                                          | 99   |

| 14     | A Complex System                                                                    | 101  |

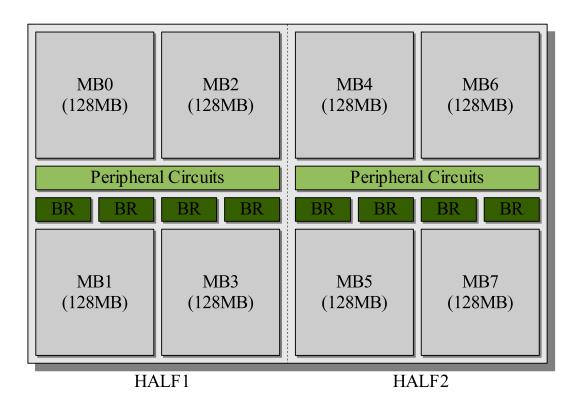

| 15     | A Block Diagram of a 1Gb DRAM                                                       | 109  |

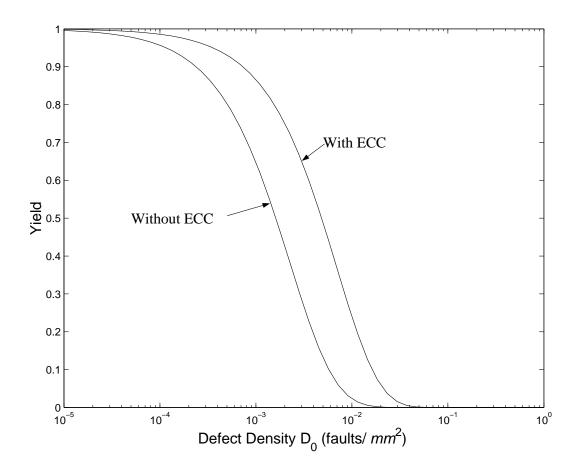

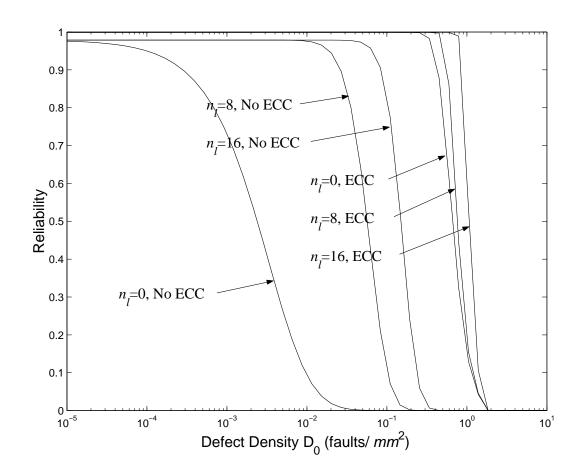

| 16     | Comparison of IC Yield Related to the Existence of ECC                              | 113  |

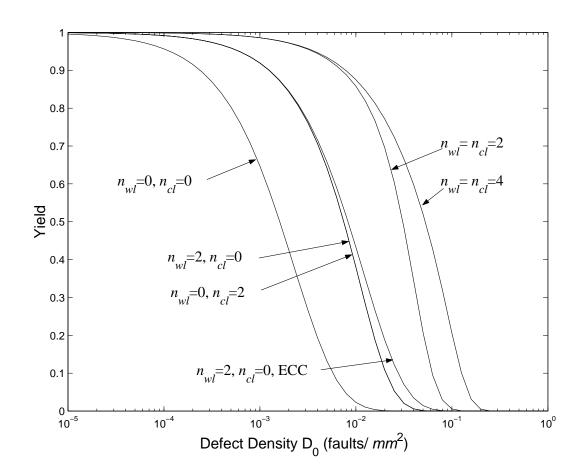

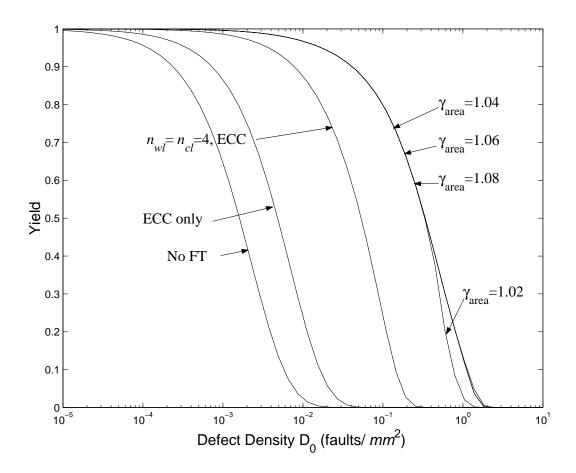

| 17     | Comparison of IC Yield Related to the Various Row and Column<br>Redundancy Policies | 114  |

Page

| 18 | Comparison of IC Reliability Related to the Various Row and   |     |

|----|---------------------------------------------------------------|-----|

|    | Column Redundancy Policies                                    | 115 |

| 19 | Comparison of Optimal Yield Related to the Various Conditions | 118 |

#### CHAPTER I

#### INTRODUCTION

Nanotechnology is considered one of the promising technologies for 21st century. The prefix "nano-" indicates one billionth  $(10^{-9})$ , i.e., one nanometer (nm) is equal to  $10^{-9}m$  or  $0.001\mu m$ . In a narrow sense, *nanotechnology* means the design, fabrication, and manipulation of atoms and molecules. Therefore, it is sometimes referred to as *molecular technology*. In a broad sense, nanotechnology can be defined as any science and technology that manipulates matter and systems whose size or tolerance is less than 100nm. It is widely known that classical Newtonian physics describes the interaction of matter with sizes of more than 100nm and that quantum physics handles matter less than 10nm. Nanotechnology acts as a link between those two fields of physics.

Nanotechnology today is pervasive due to its broad applications. Anticipated applications include electronics, telecommunications, materials, pharmaceutical and medical fields, bioengineering, the environment, energy, space, and so on. It is generally accepted that human life will change dramatically when nanotechnology is successfully implemented in the real-world. Nanotechnology should also result in breakthroughs in other leading technologies. For example, evolution of information technology is required to manipulate large amounts of information in biotechnology, and the success of information technology will critically rely on nanotechnology in the form of nanocomputer and quantum computing.

Since the invention of Scanning Tunneling Microscopy (STM) in 1983 and

This dissertation follows the style of the IEEE Transactions on Reliability.

the discovery of the molecular structure, Fullerenes ( $C_{60}$ ), in 1985, numerous research results have been announced by various institutes and academia related to nanotechnology over the last two decades. However, most of the results have not guaranteed feasibility in industry, but have been limited to the laboratory. To elevate nanotechnology from the science to the engineering, the assurance of manufacturability and productivity is indispensable. *Nanomanufacturing* is defined as a series of processes for building nano-systems whose scale is less than 100*nm*. This includes various multidisciplinary areas such as materials, devices, design, architecture, fabrication, analysis and estimation, modeling and control, optimization, simulation, testing and inspection, various facilities for manufacturing, and so on.

The heart of nanomanufacturing is nanofabrication which is achieved by two fundamentally distinct approaches, *top-down* and *bottom-up*. The top-down approach follows a technology similar to current semiconductor manufacturing, such as photolithography, thin film diffusion, polymer molding, cutting, wrapping, polishing. Electron-beam lithography, molecular beam epitaxy, microcontact print, nanoimprint lithography, etc. are included in this approach. The main advantage of this approach is its repeatability which makes volume production possible. On the other hand, the bottom-up approach employs self-assembly methods using a molecular array and the stiction property of atoms through Scanning Probe Microscopes (SPM). Self-assembly, robotic nano-assembly, template develop, etc. are included in this class. Although the bottom-up approach is very difficult to develop, it is expected that bottom-up will be the dominate form of nanofabrication in the end because of the resolution limitations of the top-down approach.

During nanomanufacturing, large numbers of defects inevitably occur because of the tiny scale of the devices, complex manufacturing processes, contamination, insufficient resolution of the lithography facilities, uncertainty of the connectivity between devices, and so on [1]. These defects reduce the yield and reliability of manufactured nano-systems, as a result, decrease manufacturability and productivity. It is impossible to detect all occurring defects, and is very expensive, exhaustive, and sometimes impossible to eliminate them. Nano-systems may also have severe reliability problems because they are very sensitive to external environmental factors such as temperature, humidity, and the electric field.

The ITRS Semiconductor Roadmap [2], assessed by several semiconductor associations at all over the world is the most reliable source for obtaining current and future physical and technical trends in semiconductor integrated circuits. According to the roadmap, the half pitch of manufactured semiconductor integrated circuits at 2002 is about 130nm, and it will become 65nm by 2007 and 22nm by 2016 for dynamic random access memory (DRAM). In addition to the nano-scale, manufacturing technology of semiconductor integrated circuits is similar to the top-down approach of nanomanufacturing. Therefore, it is reasonable to include semiconductor manufacturing into the nanomanufacturing in a broad sense.

The assurance of manufacturing yield and system reliability is also very important in semiconductor manufacturing. The ITRS 2002 update [2] suggests several grand challenges related to yield and reliability. In the near future (through 2007), new reliability screen methods for burn-in, inspection techniques for non-visual defect sources with high aspect ratio inspection, and design methods considering manufacturing and test are considered the critical technologies. In the distant future (2008 through 2016), error-tolerant design techniques, yield models for new materials and devices, and integration of them will take an important role in semiconductor manufacturing. In summary, key technologies related to yield and reliability in nanomanufacturing as well as in future semiconductor manufacturing are defect detection and analysis, accurate yield modeling, and defect-tolerant design.

Critical defects cause failures in semiconductors. Since the manufacturing yield and reliability of manufactured systems rely on these failures, it is necessary to efficiently manage the defects. There are two approaches for enhancing yield and reliability on the basis of defects. The first approach is to decrease the number of defects, and the second approach is to develop defect-robust design. Decreasing the defects can be accomplished by tightly controlling the contamination level, by increasing the quality of the cleaning processes, and by precisely controlling the manufacturing processes using statistical process control methods. Defect-robust design can be achieved by designing physically reliable devices such as high-k dielectric gate materials and by employing fault-tolerant schemes. Since it is technically impossible to fabricate perfect devices and to eliminate all defects, defect-tolerance has been considered a worthy method for dealing with defects. Heath et al. [1] have defined defect-tolerance as the capability of a circuit to operate as desired without physical repair or the removal of random mistakes incorporated in the system during the manufacturing process. The most cost-efficient defect-tolerant method for improving yield and reliability is to assign and manage additional replaceable components in vulnerable components. These redundancies may have self testing and repairing ability, so called BIST (built-in self test) and BISR (built-in self repair) [3].

With any defect management methods, accurate yield and reliability models are essential. Accurate models are very useful for evaluating the feasibility of new devices, identifying and monitoring the sources of defects, providing accurate simulations for the improvement of physical and logical device designs, and so on. For the past four decades, various forms of yield and reliability models have been proposed [4, 5]. Yield models are primarily based on statistical inference for defect size distribution, defect density, critical area, and failure types. On the other hand, reliability models are primarily based on the physical behavior of the electronic devices. There are many factors that affecting yield and reliability, such as the failure types, the system architecture, defect density, critical area, defect clustering, burn-in effects, fault-tolerant schemes such as redundancies and error correcting code, and so on. However, most of the models developed so far, only partially consider these factors due to the complex structure of, and the complicated correlation relationships of, these factors.

Since the late 1950's, redundancy techniques have been successfully employed and their effectiveness has been verified by diverse applications. Yield and reliability can be enhanced by adding redundancies on failed or unreliable components or by increasing the robustness of the components physically. Looking at the manner in which manufacturing and design technologies have developed, improving component reliability appears to have been generally preferred over adding redundancies in industry, because, in many cases, redundancy is difficult to add to real systems due to technical limitations and the relatively large quantities of resources, such as weight, volume, and cost, that are required. However, recently developed advanced technologies, such as semiconductor integrated circuits and nanotechnology, have revived the importance of the redundancy strategy [1, 6]. The current down-scaling trend in semiconductor manufacturing places certain limitations on enhancing reliability or yield by developing relevant physical technologies [7, 8]. Hence, various fault-tolerant and self-repairable techniques are generally recommended [6]. In fact, most advanced memory integrated circuits and VLSI, which include internal memory blocks, currently use a hierarchical redundancy scheme and an error correcting code.

The objectives of this dissertation are to develop accurate yield and reliability models for defect-tolerant semiconductor integrated circuits and to develop optimization algorithms that can be applied to various complex systems including the developed models; thus, the models and the optimization algorithms can be applied to current semiconductor-systems and to future nano-systems with minor modifications. The defect-based yield and reliability models consider as many critical factors as possible for yield and reliability, which include various types of failures, burn-in effects, and fault-tolerant architecture with a hierarchical redundancy structure and an error correcting code, while the computational efficiency endures. Defect-tolerant architecture using redundancy increases yield and reliability, but consumes other resources such as area, volume, weight, cost, test and repair algorithm, and repair architecture. To efficiently achieve fault-tolerant systems, the number of redundancies should be optimized to maximize yield and reliability with the available resources, the so-called the redundancy allocation problem. Typical yield and reliability models are nonconvex, nonlinear, nonseparable, and coherent, and optimization problems have the same properties. Coherent systems have component-wise increasing property, that is, adding redundancies increases the yield and reliability. In this study, I propose an efficient branch-and-bound approach for obtaining the global optimum and two iterative heuristics, a scanning heuristic and a tree heuristic, and their variants for achieving the local optimum of yield or reliability redundancy allocation problems. The global optimization method is based primarily on a search space elimination of disjoint sets in a solution space that does not require any relaxation of branched subproblems. The scanning heuristic finds a better local optimum by solving the problem from several systematically generated initial points, and the tree heuristic obtains several local optima by branching off solution paths from the main solution path, which is a set of points with a maximum sensitivity factor. The main advantage of these methods is flexibility (i.e., it does not rely on any assumptions of linearity, separability, single constraint, or convexity) which make the method adaptive to various applications.

This dissertation is organized into three major parts: modeling, optimization, and a case study. In Chapter II, the terms defect, fault, error, and failure, are defined and classified. Then, the methods for managing defects are briefly reviewed. Chapter III begins with a description of yield and reliability. Basic defect-based yield models, the Poisson model and the negative binomial model, are reviewed considering defect size, defect density, and critical area. At the end, the defect-based burn-in yield models and the reliability model in an useful life period are introduced. In Chapter IV, an integrated yield model and a reliability model considering carry-over failures for memory integrated circuits are proposed based on the models in Chapter III.

Chapter V introduces coherent systems, and redundancy allocation problems are defined under mathematical programming techniques. In Chapter VI and VII, new algorithms for solving reliability optimization problems are proposed. Chapter VI offers a branch-and-bound algorithm employed for redundancy allocation problems. Chapter VII proposes two efficient iterative heuristics, the tree heuristic and the scanning heuristic, for redundancy allocation problems. Numerical experimentation in Chapter VI and VII shows that the proposed global and local optimization algorithms are superior to other existing algorithms for redundancy allocation problems in terms of computation time and/or solution quality.

In Chapter VIII, the optimization algorithms in Chapter VI and VII are applied to the integrated yield model and the reliability model in Chapter IV to obtain an optimal number of redundancies in an example problem. Finally, Chapter IX summarizes the work in the modeling and the optimization of semiconductor integrated circuits. The directions for future research in nanomanufacturing are described.

#### CHAPTER II

#### DEFECTS AND DEFECT MANAGEMENT

Semiconductor manufacturing consists of several stages of circuit design and mask preparation, wafer production, wafer fabrication, assembly and packaging, and burnin and testing [9]. Each stage also includes a series of processes. For instance, wafer fabrication consists of oxidation, photoresist coating and etching, polysilicon masking and etching, ion implantation, metal deposition and etching, and so on. Figure 1 presents a diagram of the complex semiconductor manufacturing process. For modern complex semiconductor products, more than 400 steps of individual processes are required, and it often takes more than two months to complete the manufacturing process. The complexity of the semiconductor manufacturing process presents many opportunities defects to occur. Defects cause faults, errors, and failures in manufactured integrated circuits, and they result in yield loss and reliability degradation. In this chapter, defects and related terms are defined and classified, and defect management methods for enhancing yield and reliability are discussed.

### II.1. Defect, Fault, Error, and Failure

Defect, fault, error, and failure are frequently used terms in semiconductor engineering as are yield and reliability engineering. In semiconductor engineering, a defect is defined as any physical imperfection which does not satisfy specified requirements. A fault is a critical defect which affects the performance or functional behavior of the integrated circuit. An error, which is a manifestation of a fault, is a discrepancy between the theoretical value of a correctly designed function and real observed value of the function in the semiconductor system. A failure is an event, or inoperable state,

Figure 1: Manufacturing and Inspection Processes of Semiconductor Integrated Circuits

in which any item, or part of an item, does not, or would not, perform as previously specified [10]; in other words, failure is a status which does not function correctly without repair. In many cases, fault, error, and failure are used interchangeably to indicate a malfunction. However, strictly speaking, they have different definitions: a fault is physical and local; error is logical and functional; failure is physical and global. Not all defects result in faults, and not all errors are failures. For example, a memory bit can be temporarily changed by an  $\alpha$ -particle in a memory integrated circuit and it can be fixed by an error correcting code immediately. In this case, the changed bit is not a failure, but an error.

To efficiently enhance yield and reliability, classification, diagnosis, and analysis of the defects and faults are very important. Since they are sources of failure, further investigation of them is required. Defects can be classified into several types according to their size, sources, location, and types as follows:

#### Global and point defects

Global defects, or gross area defects, are defects which occur on relatively large areas of a wafer surface. The main sources of global defects are wafer dislocations, wafer mishandling, mask misalignment, over etching or under etching, variation of implantation levels, and so on. Global defects can be gradually decreased during volume production by precisely controlling corresponding manufacturing processes. Point defects, or spot defects, are random local defects which mainly come from undesirable airborne particles, metallic impurities, and electrostatic discharge (ESD). They are mainly caused by cleanroom contamination, imperfect manufacturing processes, wafer mishandling, and so on. Since it is very difficult to control for spot defects, spot defects are a major concern of semiconductor manufacturers and, thus, a major focus of this research.

Figure 2: Hard and Soft Defects at an Intra-Layer

### Hard and soft defects

Spot defects can be further classified into hard and soft defects. A hard defect is a spot defect which results in an open, or short, circuit; that is, failure of the integrated circuit. On the contrary, a soft defect does not affect the functionality of circuits, but it decreases or increases the physical dimensions of a device which may change the characteristics of the device. Soft defects can lead to system failure during manufacturing, the burn-in process, or operation. A graphical description of hard and soft defects appears in Figure 2. A defect is considered as a hard or soft defect based on size, location, and type. For example, the hard defect D in Figure 2 could be a soft defect if the defect was not a hole but a conductor.

#### Inter-layer and intra-layer defects

Based on their locations, spot defects are classified into inter- and intra-layer defects. Current complex integrated circuits have more than 8 layers built to avoid interconnections of the conductive lines which electronically connect devices [2]. Intra-layer defects, or photolithographic defects, are located on the same layer. Inter-layer defects occur between two adjacent layers. Missing or extra material at the intra-layer or inter-layer may result in an open, or short, circuit, respectively.

Faults can be also classified into several types. The major types of faults are summarized below:

#### Functional and parametric faults

Functional faults, or logical faults, cause catastrophic behavior in a circuit device, which prevent it from performing its intended function correctly. Stuck-at-0 and stuck-at-1 faults, bridging, stuck-open or -short, and so on, are included in this category of faults. Parametric faults do not change any functional values, but they generate time delays of the signal or magnitude variations in some electrical parameters, such as voltage, current, and resistance, and capacitance.

#### Permanent and temporary faults

Permanent faults, or hard faults, are continuous and stable faults which endure regardless of time. Design faults, broken wire, and missing or extra material are permanent faults. On the other hand, temporary faults occur randomly (transient faults) or regularly with unknown intervals (intermittent faults). The transient faults are mainly caused by environmental conditions such as  $\alpha$ -particle hits, cosmic rays, temperature variations, and electromagnetic interference. Intermittent faults are caused by non-environmental conditions such as variations of resistance and capacitance, noise, and wear-out.

Some types of defects and faults are correlated. They can be comprehend as a mixed form; for example, a soft spot defect at an intra-layer can be a parametric permanent fault. The possible combinations of the defects and faults are depicted as a block diagram in Figure 3.

Figure 3: Possible Combinations of Defects and Faults

### II.2. Defect Management

Various types of defects and faults can be detected by several different inspection processes. Defect inspection, or defect monitoring, can be performed during wafer fabrication (on-line inspections) using manual detection with an optical microscope and automatic detection with light scattering (or laser scattering) facilities. Global defects can be detected by a parameter monitoring approach, and local defects can be investigated by in-line monitors, gate-oxide monitors, and interconnect monitors. However, some defects may not be detected during any visual inspection process. At the end of wafer fabrication, a pattered wafer contains several hundred dies (or chips) which is a unit of the actual integrated circuits. The wafer sort process, probe testing or wafer probing, is performed to test parametric and electrical operation on each die by contacting bonding pads. Failed dies on the wafer sort process are marked, and discarded from further manufacturing stages. The various inspection processes and their flows during semiconductor manufacturing are depicted in Figure 1. To enhance yield and reliability, manufacturing defects and faults should be managed effectively. One approach for defect management is to minimize the number of occurring defects and faults by controlling contamination levels and manufacturing processes with a low tolerance. The keys to this approach are how to retrieve main defect sources as correctly as possible to control the related processes, and how to perform the control process as precisely and fast as possible to increase yield as much, and as soon, as possible. Defect and fault classification, fault diagnosis, failure analysis, and statistical process control (SPC) are the main methods used to in this approach. However, there are certain limitations to this approach. Not all defects and faults can be detected by inspection processes because they may be located inside the physical layers or their size may be smaller than the resolution of the inspection facilities. Even when all of the defects and faults can be detected, it is still may not be possible to eliminate them entirely because of complex manufacturing processes, the resolution limit of the photolithography, or extremely high facilities costs.

Optical lithography is the key technology for future semiconductor manufacturing. Current extremely high density semiconductor integrated circuits are expected to meet its physical limitations in a few years [7, 8]. The most used light sources for lithography, at present, are the KrF laser (wavelength 248*nm*) and the ArF laser (wavelength 193*nm*). However, their resolution is not accurate enough for future use. The resolution of lithography is proportional to the wavelength of the light source and the processing techniques, and inversely proportional to the numerical aperture of the lens [9]. Due to technical difficulties, the resolution is generally similar to, or a little less than, the wavelength. Several alternative technologies, such as the  $F_2$ excimer laser (wavelength 157*nm*), extreme ultraviolet (wavelength 10 – 14*nm*), and electron projection lithography, have been investigated by many research institutions for use in the near future [11]. However, as device dimensions decrease, the initial facility cost and the mask cost for lithography with the same or less resolution increase exponentially; and, as a consequence, so does the cost of fabrication of semiconductor integrated circuits.

Another approach to managing defects and faults is to design circuits and architecture that are more robust, the so-called defect-tolerant or fault-tolerant technique. This approach can be classified into two methods. The first method is to design devices on integrated circuits that are more tolerant to defects and other environmental variations. Most current semiconductor integrated circuits use CMOS (Complementary Metal Oxide Semiconductor) as a device. In current CMOS technology, the thickness of the gate dielectric (SiO<sub>2</sub>) is less than 40Å [12] and the physical gate length is about 50nm [2]. Sizes continue to decrease to a few Å to meet the electrical requirements, such as capacity and resistance, of the new down-scaled devices. However, ultra-thin gate dielectric film invokes many manufacturing problems which affect yield and reliability. These problems include dielectric thickness variations, penetration of impurities from the gate into the gate dielectric, leakage current of the gate, and gate breakdown [12]. To overcome these problems, various high-kmaterials are being investigated as a substitute for the currently used SiO<sub>2</sub>. With high-k materials, we can preserve the thickness of the gate dielectric, and, as a result, further down-scaling can be achieved without loss of yield and reliability. In addition to robust device design, yield can be also enhanced by decreasing the critical area of a chip. The critical area is the area where a certain size defect causes failure. The critical area can be decreased by optimizing the conducting lines, by optimizing the layout of devices, and by changing the floor plan of integrated circuits [6].

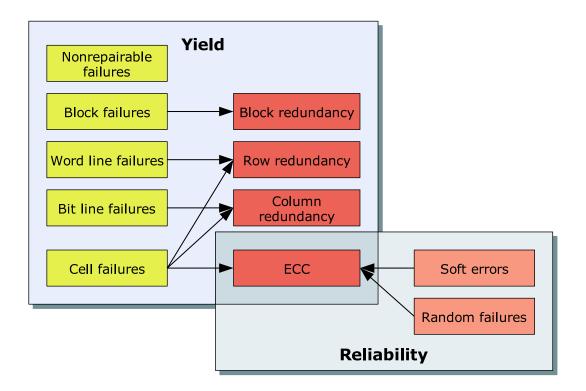

The second type of fault-tolerant techniques involves replacing failed devices with other working devices. Redundancy and error correcting codes (ECC) are the most used techniques in this category. From the late 1970's, these techniques have been popular on memory integrated circuits; in fact, most advanced memory integrated circuits such as DRAM, SRAM, flash memories and microprocessors, which include an internal memory section, employ a hierarchical redundancy structure and ECC to increase yield and reliability [13]. There are several types of failures in the memory array related to the size and the location of defects. When a redundancy technique is employed on memory integrated circuits, word line failures, bit lines failures, cell failures, and block failures should be compensated for by the proper type of redundancies. At the end of wafer probing, this reconfiguration is typically performed by blowing and connecting built-in fuses/antifuses using laser equipments. However, the reconfiguration method using fuses has several disadvantages: 1) it requires additional processes which increase manufacturing cost; 2) it can not repair failures that occurred during operation due to its physical limitations; 3) it is unable to detect and test defects and faults; and 4) it is expensive due to the extremely high testing facility cost. Thus, the various automatic reconfiguration techniques such as BIST (built-in self test), BISD (built-in self diagnosis), and BISR (built-in self repair) have been proposed [3]. To perform the function correctly and efficiently, these built-in techniques require additional hierarchical cell array architecture and algorithms for finding the proper redundancies for detected failures.

#### CHAPTER III

#### YIELD AND RELIABILITY MODELS

Yield and reliability models can be classified into two types: physical models and statistical models. Physical models explain the electrical and parametric behavior of semiconductor devices. The famous Arrhenius equation for thermal behavior and the classic anode hole injection (1/E) model and the thermochemical (E) model for gate oxide are included in this class. This type of model is mainly used to improve reliability by changing the device characteristics. Statistical models are primarily based on statistical inference and the estimation of defect and failure data that are obtained in field. Most models, such as the Poisson and the negative binomial models for yield and the exponential and the Weibull models for reliability, belong to this category.

An accurate yield model is very useful for the following activities:

- verifying the productivity of current or new products by yield projection

- improving yield during volume production by diagnosing the defect types which cause most of the yield loss and monitoring relative manufacturing processes

- improving device design by providing accurate yields to simulation tools

- determining production control parameters by providing accurate estimations.

Similar to the yield model, reliability model is also very useful for the following activities [14]:

- evaluating the feasibility of new products

- comparing competing designs in terms of reliability

- identifying potential reliability problems

- planning maintenance and logistic support strategies

- providing input to other studies such as life-cycle cost analysis or product selection.

#### III.1. Manufacturing Yield

Manufacturing yield is defined as the ratio of the number of working units at the end of production to the total number of possible units at the beginning of production. Since semiconductor manufacturing consists of a series of stages, manufacturing yield can be calculated from the following equation:

$$Y_{MFT} = Y_{WP} \cdot Y_{FAB} \cdot Y_{AP} \cdot Y_{BI}, \qquad (3.1)$$

where  $Y_{WP}$ ,  $Y_{FAB}$ ,  $Y_{AP}$ , and  $Y_{BI}$  denote the yields of wafer production, fabrication, assembly & packaging, and burn-in stages of Figure 1, respectively. Since this study does not deal with the wafer production and assembly & packaging stages, for simplicity, we can assume that  $Y_{WP} = 1$  and  $Y_{AP} = 1$ .

Many semiconductor engineers regard manufacturing yield as fabrication yield because the wafer fabrication stage is the most important stage, and the wafer production and the assembly & packaging stage are sometimes performed at different companies that are not fabrication companies. However, from the reliability point of view, this perspective is not appropriate. Yield can be interpreted as reliability at time zero. Since reliability considers the lifetime of a device during operation, the lifetime should be calculated from the customer's viewpoint, i.e., operation. However, if we assume yield to be the fabrication yield, there is a time gap between yield and reliability because of the assembly & packaging and burn-in stages. For this reason, I will distinguish fabrication yield from manufacturing yield. Therefore, fabrication yield and manufacturing yield can be calculated as follows (with field data in percentage unit):

$$Y_{FAB} = \frac{\text{Average number of good chips per wafer}}{\text{Total number of possible chips per wafer}} \times 100\%,$$

where a chip or a die denotes a piece of a silicon wafer that contains the complete device.

$$Y_{MFT} = \frac{\text{Average number of working ICs per wafer}}{\text{Total number of possible chips per wafer}} \times 100\%$$

where IC indicates the final products that are ready to ship to the customer.

#### III.2. Reliability of Semiconductor Integrated Circuits

Reliability is one of the important factors determining the productivity of semiconductor integrated circuits. Reliability is defined as the probability that a device operates properly for a given period of time (a mission time) under designated operating conditions. Each device has a lifetime which is the length of time that the device works properly. Let T be a random variable for the lifetime of a integrated circuit. If the mission time of the integrated circuit is unspecified, the reliability of the integrated circuit becomes a real-value function for the mission time, i.e., the so-called reliability function. Note that the mission time is not a random variable. The reliability function, R(t), which is the probability that lifetime T is greater than mission time t, can be formulated as follows:

$$R(t) = \Pr(T > t) = \int_{t}^{\infty} f(\theta) d\theta, \qquad (3.2)$$

where  $f(\theta)$  is the probability density function (pdf) of lifetime T with respect to operating time  $\theta$ . An unreliability function which implies the probability of failure at time t is also defined as follows:

$$F(t) = \Pr(T \le t) = \int_0^t f(\theta) d\theta = 1 - R(t).$$

(3.3)

The failure rate is the ratio of failures during a particular interval given that the product works properly by time t. Let the interval be  $(t, t + \Delta t]$ . Then, the failure rate is:

$$\mu(t) = \frac{\Pr(t < T \le t + \Delta t)}{\Delta t \Pr(t < T)} = \frac{F(t + \Delta t) - F(t)}{\Delta t R(t)} = \frac{R(t) - R(t + \Delta t)}{\Delta t R(t)}$$

(3.4)

The instantaneous failure rate, or hazard rate h(t), is the limit of the failure rate as  $\Delta t$  approaches zero, and it is expressed as:

$$h(t) = \lim_{\Delta t \to 0} \mu(t) = \lim_{\Delta t \to 0} \frac{F(t + \Delta t) - F(t)}{\Delta t R(t)} = \frac{dF(t)/dt}{R(t)} = \frac{f(t)}{R(t)}$$

(3.5)

Now, take the integral on both sides of Equation (3.5). Then, the following mathematical relationship between h(t) and R(t) holds:

$$\int_0^t h(\theta) d\theta = \int_0^t \frac{1}{R(\theta)} \frac{dF(\theta)}{d\theta} d\theta = \int_0^t \frac{-1}{R(\theta)} dR(\theta) = -\ln R(\theta)|_0^t = -\ln R(t) + \ln R(0).$$

We can assume that R(0) = 1, i.e., no failure at time zero, because any product is totally reliable at the beginning of its life. Then, the reliability function at mission time t can be computed with a hazard rate as follows:

$$R(t) = \exp\left(-\int_0^t h(\theta)d\theta\right).$$

(3.6)

Assuming that the instantaneous failure rate h(t) is a constant  $\mu$  w.r.t. at time t, the

reliability function becomes:

$$R(t) = e^{-\mu t} \tag{3.7}$$

and it is a exponential distribution.

Failures are counted in calculating yield and reliability. In semiconductor engineering, failures can be classified into three types according to the failure source: extrinsic, intrinsic, and wear-out. If a failure is caused by unrevealed manufacturing defects, it is called an extrinsic failure. Defects which do not materialize into yield losses can be grown to failures during operation depending on the quantity of external and internal stresses. The extrinsic failures usually observed during the infant mortality period have a decreasing failure rate (DFR). These failures can be effectively screened by accelerated life testing and burn-in. Intrinsic failures, sometimes called defect-free failures, occur randomly during operation. These failures have a constant failure rate (CFR) and can be observed during the useful life period. The most important reliability measure in semiconductor integrated circuits, time-dependent dielectric breakdown (TDDB), is related to both extrinsic and intrinsic failures. Wear-out failures, which have an increasing failure rate (IFR), are the result of device aging such as electromigration and transistor degradation. In general, wear-out failures should be avoided in the design stage of semiconductor devices [15]. Thus, wear-out failures will be ignored in this study. Since actual semiconductor integrated circuits include all of the types of failure, the failure rate function of an integrated circuit can be represented by the famous bathtub curve by summing the three failure rate functions. Figure 4 describes all of the failure rate functions and their corresponding periods.

Figure 4: Bathtub Shape Failure Rate

### III.3. Defect Size, Defect Density, and Critical Area

Defect-oriented yield models are significantly related to defect sizes, defect density, and critical area. Commonly, a spot defect, which is our major concern, is assumed to be a circle with a specific diameter, which is called the defect size. It has been verified empirically that the density of the number of defects has a peak at a specified defect size. The density linearly increases if the size of defect is less than the specific size and inverse polynomially decreases if the size of the defect is lager than the specific size. The defect size at the peak of the pdf depends on the contamination level and the resolution of the processes during manufacturing. Let the defect size be x and the specific size be  $x_0$ . The pdf of the defect size,  $f_s(x)$ , is generally described as follows [16]:

$$f_s(x) = \begin{cases} \frac{2(p-1)}{p+1} \frac{x}{(x_0)^2}, & 0 \le x \le x_0, \\ \frac{2(p-1)}{p+1} \frac{(x_0)^{p-1}}{x^p}, & x_0 \le x \le \infty. \end{cases}$$

(3.8)

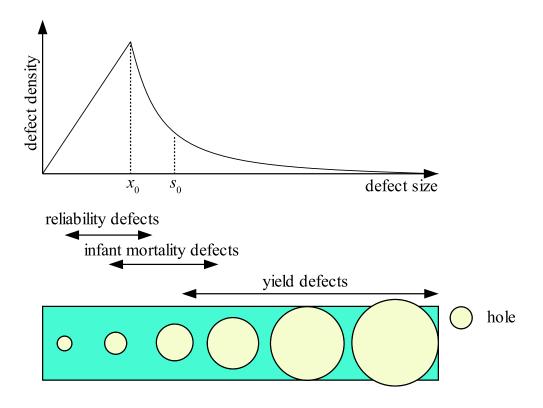

Figure 5: Distribution and Classification According to Defect Size

Many empirical data show that a reasonable value of p is in the interval [2.5, 3.7] [16]. The pdf for the defect size is described in Figure 5. In the figure,  $s_0$  is the critical size of the defects which affect the yield, and a typical value of  $s_0$  is a half of the minimum device feature size. Generally,  $x_0$  is smaller than  $s_0$ .

Defect density, D(x), is the number of defects of size x in a unit area  $(cm^2$  or  $m^2)$ . The average defect density for all defect sizes,  $D_0$ , can be computed by:

$$D_0 = \int_0^\infty D(x) dx.$$

Since  $f_s(x)$  is a pdf of the defect size, the following relationship between the defect density and the pdf of the defect sizes holds:

$$D(x) = D_0 f_s(x).$$

The critical area is a set of locations where a defect with a certain size results in a failure of the integrated circuit. In other words, if a defect, which size is greater than, or equal to, x, falls in a critical area,  $A_c(x)$ , the integrated circuit fails. The probability of failure (pof) is the failure probability when a defect falls on a chip. Thus, the pof can be interpreted by a ratio of the critical area to the total area of the chip as follows:

$$pof(x) = \frac{A_c(x)}{A_{chip}},$$

(3.9)

where  $A_{chip}$  is a total area of the chip. For all defect sizes, the average critical area can be computed by following:

$$A_c = \int_0^\infty A_c(x) f_s(x) dx,$$

In a yield model, the most important parameter is the average number of defects which is denoted by  $\lambda$ .  $\lambda$  can be computed with the following equation:

$$\lambda = \int_0^\infty A_c(x)D(x)dx$$

=  $D_0 \int_0^\infty A_c(x)f_s(x)dx$

=  $A_c D_0.$  (3.10)

To calculate the  $\lambda$ , we must know the critical area,  $A_c(x)$  (or pof(x) by Equation (3.9)), since  $D_0$  can be obtained from the field data and  $f_s(x)$  can be computed by Equation (3.8). There are various methods for achieving  $A_c(x)$  and pof(x). Geometrical methods applying a Boolean polygon operation can calculate  $A_c(x)$  and Monte-Carlo methods can compute pof(x). For a good summary and references on calculating the critical area, refer to [5]. These methods for calculating  $A_c(x)$  or pof(x) can be repeatedly performed at the design stage in order to decrease the critical area of a chip.

#### III.4. Poisson and Negative Binomial Yield Models

The Poisson distribution is the most widely used discrete distribution for a statistical model with random occurrences in a specified interval or area. Since the number of defects varies from wafer to wafer and chip to chip, the Poisson model is appropriate for our purpose. To employ the Poisson distribution to a yield model, the following assumptions must be satisfied:

- all defects are chip-kill defects which induce failure of the integrated circuit

- all defects are mutually independent, i.e., the occurrence of a defect at any location does not affect the occurrence of any other defects.

Let a random variable X denote the number of defects in a chip. X follows the Poisson distribution with an intensity parameter of  $\lambda$ . The probability that a chip contains k defects is:

$$\Pr(X = k | \lambda) = \frac{e^{-\lambda} \lambda^k}{k!}, k = 0, 1, \dots$$

(3.11)

Since the mean of X is  $\lambda$ ,  $\lambda$  can be interpreted as the average number of defects occurring on a chip - this coincides with the definition of  $\lambda$  in Section III.3. Since yield is the probability of a no chip-kill defect, the yield of the Poisson model can be formulated by Equation (3.10) and (3.11):

$$Y_{POI} = \Pr(X = 0|\lambda) = e^{-\lambda} = e^{-A_c D_0}.$$

(3.12)

Although the Poisson yield model is a reasonable yield model for the random occurrences of defects, the projected yield of the Poisson model is often pessimistic

because of the clustering effect of the defects. If defects are not evenly distributed on a wafer, some chips contain more defects than the average and some chips contain none. The failure of an integrated circuit does not depend on the number of defects but only on the existence of defects. Note that we are not yet employing defecttolerant techniques. The clustering effect generally cause real yield to be larger than the projected yield using the Poisson model. To reflect the clustering effect of defects, many researchers have studied compound Poisson models [17, 18, 19].

The compound Poisson model assumes that the average number of defects,  $\lambda$ , (or the average defect density  $D_0$ ) has a type of distribution. Murphy [17] compounded the Simpson distribution (triangular distribution) and the rectangular distribution, and Seed [18] applied an exponential distribution as a compounder. However, the most widely accepted compounder is the Gamma distribution [19]. Let L be a random variable which indicates the average number of defects. If L has a constant value  $A_c D_0$ , the pdf of L is a sifted Dirac  $\delta$  function as follows:

$$f_L(\lambda) = \delta(\lambda - A_c D_0),$$

the yield can be computed by:

$$Y = \int_0^\infty e^{-\lambda} f_L(\lambda) d\lambda = e^{-A_c D_0}.$$

(3.13)

This coincides with the Poisson yield model of Equation (3.12).

Now, let the pdf of the random variable L be the Gamma distribution as follows:

$$f_L(\lambda|\alpha,\beta) = \frac{1}{\Gamma(\alpha)\beta^{\alpha}} \lambda^{\alpha-1} e^{-\lambda/\beta}, \ 0 < \lambda < \infty, \ \alpha > 0, \ \beta > 0,$$

where  $EL = A_c D_0 = \lambda = \alpha \beta$  and  $var(D) = \alpha \beta^2$ . Since the number of defects on a chip, X, depends on the average number of defects, L, the random variable X has a mixture distribution. It is well known that if X has a hierarchical mixture distribution of  $X|L \sim \text{Poisson}(L)$  and  $L \sim \text{Gamma}(\alpha, \beta)$  with integer  $\alpha$ , the marginal distribution of X follows a negative binomial distribution. Thus, the probability that a chip contains k defects is:

$$\Pr(X = k | \alpha, \beta) = \int_{0}^{\infty} \frac{e^{-\lambda} \lambda^{k}}{k!} f_{L}(\lambda | \alpha, \beta) d\lambda$$

$$= \frac{1}{k! \Gamma(\alpha) \beta^{\alpha}} \int_{0}^{\infty} \lambda^{\alpha + k - 1} e^{-\lambda(1 + 1/\beta)} d\lambda$$

$$= \frac{\Gamma(\alpha + k) \left(1 + \frac{1}{\beta}\right)^{-(\alpha + k)}}{k! \Gamma(\alpha) \beta^{\alpha}} \int_{0}^{\infty} f_{L}(\lambda | \alpha + k, (1 + 1/\beta)^{-1}) d\lambda$$

$$= \frac{\Gamma(\alpha + k) (\beta)^{k}}{k! \Gamma(\alpha) (1 + \beta)^{\alpha + k}} \sim \text{negative binomial} \left(\alpha, \frac{1}{1 + \beta}\right)$$

$$= \frac{\Gamma(\alpha + k) \left(\frac{\lambda}{\alpha}\right)^{k}}{k! \Gamma(\alpha) \left(1 + \frac{\lambda}{\alpha}\right)^{\alpha + k}}$$

(3.14)

Since yield is the probability of a zero chip-kill defect, the yield can be computed by the following:

$$Y_{NB} = \Pr(X = 0 | \alpha, \beta)$$

$$= \left(1 + \frac{\lambda}{\alpha}\right)^{-\alpha} = \left(1 + \frac{A_c D_0}{\alpha}\right)^{-\alpha}.$$

(3.15)

This yield model is normally called a generalized negative binomial yield model or a Stapper model [19]. In this model, the clustering factor,  $\alpha$ , is used to adjust the clustering level compared to the observed field data.

Poisson and negative binomial yield models assume that the  $\lambda$  and the  $\alpha$  are constants in the whole chip. However, in real applications, the chip area is often divided into several independent areas which have distinct values of the  $\lambda$  and the  $\alpha$ . For example, a memory integrated circuits consists of several sections, including peripheral circuits and memory arrays. The critical area of the peripheral circuit area is normally designed to be much smaller than that of the memory array area because any fault on the area cause chip failure. Thus, the  $\lambda$  of the peripheral circuit area is much less than the  $\lambda$  of the memory array area even though the defect density is the same. Consider a chip which consists of n statistically independent partitions. Let a random variable  $X_i$  be the number of defects for the *i*th section for  $i = 1, \ldots, n$  and the total number of defects on the chip  $X = \sum_{i=1}^{n} X_i$ . Then, the probability that kdefects occur at a chip is:

$$P(X=k) = \sum_{\mathbf{k}\in K} \prod_{i=0}^{n} P(X_i = k_i),$$

where  $k_i$  denotes the number of defects in the *i*th section,  $\mathbf{k} = (k_1, \ldots, k_n)$ , and  $K = \{\mathbf{k} | \sum_{i=1}^n k_i = k\}$ . Since yield is the probability of no defects on a chip, yield can be computed by:

$$Y = P(X = 0) = \prod_{i=0}^{n} P(X_i = 0) = \prod_{i=0}^{n} Y_i,$$

(3.16)

where  $Y_i$  is the yield of the *i*th section. If  $X_i$  follows the Poison distribution with parameter  $\lambda_i$  for i = 1, ..., n, the yield becomes:

$$Y = \prod_{i=0}^{n} P(X_i = 0 | \lambda_i) = \prod_{i=0}^{n} e^{-\lambda_i} = e^{-\overline{\lambda}},$$

(3.17)

where  $\overline{\lambda} = \sum_{i=1}^{n} \lambda_i$ . If  $X_i$  follows the negative binomial distribution with parameters  $\lambda_i$  and  $\alpha_i$  for i = 1, ..., n, the yield can be computed by:

$$Y = \prod_{i=0}^{n} P(X_i = 0 | \lambda_i, \alpha_i) = \prod_{i=0}^{n} \left( 1 + \frac{\lambda_i}{\alpha_i} \right)^{-\alpha_i}.$$

(3.18)

## III.5. Defect-based Burn-in Yield Models

Yield and reliability are two important factors for productivity and manufacturability, but they are different from each other. A simple way to divide them is to define yield as reliability at time zero. Time zero, however, is sometimes vague because of the burn-in process. Burn-in imposes excess electrical and thermic stresses to manufactured semiconductor products, which causes unreliable ones to fail early in the process. The failed products are discarded from the population. Since the remaining products have passed the infant mortality period, the reliability of the final products increase. Depending on the time zero, burn-in is included in the yield or the reliability calculation. Many semiconductor engineers include the burn-in process in the reliability area. However, as I mentioned before in Section III.1, I will include the burn-in process in yield area.

According to whether defects affect yield, burn-in, and reliability, they can be categorized into yield defects, burn-in defects, and reliability defects. Yield defects, or chip-kill defects, which have a relatively large size, cause failures at the wafer fabrication stage, so the defects are considered in calculating fabrication yield. Burnin defects, or infant mortality defects, which typically are of medium size, do not cause failures at the fabrication stage, but result in failures in burn-in stage. Reliability defects, which have a relatively small size, do not cause failures during manufacturing, but they result in failures during operation. From now on, I will use the subscripts YD for yield defects and BD for burn-in defects to distinguish burn-in defects from yield defects. The types of failures are determined by the size and location of the defects; in other words, there are some interactions between the defects. Figure 5 describes the relationship between defect size and the classification of defects.

Since a defect can be the yield or the burn-in defects, many researchers have

attempted to find an unified model for both yield and burn-in defects, the so-called yield-reliability model [15, 20, 21, 22, 23]. The first model was introduced by Huston and Clarke [15]. Their model employs both a average critical area for yield defects,  $A_{YD}$ , and a average critical area for burn-in defects,  $A_{BD}$ , in the unified form. Similar to  $A_{YD}$ ,  $A_{BD}$  is defined as a average critical area where the defects result in failures during the burn-in process.  $A_{BD}$  can be also obtained by a Monte-Carlo simulation. Assume that the number of defects follows the Poisson distribution. Then, yield can be computed by the following equation using Equation (3.12):

$$Y_{YD} = Y_{YD0} e^{-D_{YD}A_{YD}}, (3.19)$$

where  $Y_{YD0}$  is the yield of the non-random yield defects and  $D_{YD}$  is the average defect density for the yield defects. Similar to the yield for yield defects in Equation (3.19), the yield for burn-in defects can be formulated with  $A_{BD}$ :

$$Y_{BD} = Y_{BD0} e^{-D_{BD} A_{BD}}, (3.20)$$

where  $Y_{BD0}$  is the burn-in yield of the non-random burn-in defects, and  $D_{BD}$  is the average defect density for the burn-in defects. The  $D_{BD}$  is assumed to be the same as the  $D_{YD}$ . Thus, if we ignore the non-random terms  $Y_{YD0}$  and  $Y_{BI0}$ , the relationship between the yields for yield defects and burn-in defects can be formulated as following the equation by the simple manipulation of Equations (3.19) and (4.17):

$$Y_{BD} = (Y_{YD})^{A_{BD}/A_{YD}}.$$

(3.21)

Kuper and van der Pol [22, 23] proposed another yield-reliability model. They assumed that there is no difference between yield defects and burn-in defects but that only some of the yield defects become burn-in defects. This assumption implies that the average defect density for burn-in defects is a fraction of the average defect density for yield defects, i.e,  $D_{BD} = \alpha D_{YD}$ , where  $\alpha$  is a constant much less than 1. They employed the Poisson yield model as follows:

$$Y_{YD} = M e^{-D_{YD}A}, (3.22)$$

where A is the total area, or the average critical area, of a chip and M is the maximum possible yield fraction which reflects the clustering effects. Similarly, the burn-in yield can be formulated by the Poisson model as follows:

$$Y_{BD} = e^{-D_{BD}A}.$$

(3.23)

Combining Equations (3.22) and (3.23), the following relationship holds:

$$Y_{BD} = \left(\frac{Y_{YD}}{M}\right)^{\alpha}.$$

(3.24)

The Kim and Kuo model [21] considered time-dependent dielectric breakdown which is one of the major failures in integrated circuits. Let  $Z_{OX}$  be the thickness of the gate oxide and  $Z_{EOX}$  is the effective oxide thickness, which is the remaining thickness of the gate oxide due to defects. Then, the following relationship holds for  $Z_{OX}$ ,  $Z_{EOX}$ , and s:

$$Z_{EOX} = sZ_{OX},\tag{3.25}$$

where s is the severity of the defect growth at time t during operation temperature  $T_0$ . The severity factor is calculated by the following equation[21]:

$$s = \frac{t}{\tau_0(T_0)} \exp\left[-\frac{G(T_0)Z_{OX}}{V_{OX}}\right],$$

where  $\tau_0(T_0)$  and  $G(T_0)$  are constants depending on temperature and  $V_{OX}$  is the

voltage across the gate oxide. Now, consider a single gate oxide where the critical area for yield defects is  $A_{YDOX}$  and critical area for burn-in defects is  $A_{BDOX}$ . Then, the ratio of critical area can be computed by following equation:

$$\frac{A_{BDOX}}{A_{YDOX}} = \frac{Z_{OX}^2}{(Z_{OX} - Z_{EOX})^2} - 1 = \frac{1}{(1-s)^2} - 1.$$

(3.26)

By incorporating Equation (3.26) into Equation (3.21), the burn-in yield at burn-in time t can be computed by:

$$Y_{BD}(t) = (Y_{YD})^{A_{BDOX}/A_{YDOX}} = (Y_{YD})^{1/(1-s)^2 - 1}.$$

(3.27)

Barnett [24] assumed that the average number of yield defects  $\lambda_{YD}$  and the average number of burn-in defects  $\lambda_{BD}$  have the following relationship:

$$\lambda_{YD} = \gamma \lambda_{BD}, \tag{3.28}$$

where  $\gamma$  is a constant of less than one. Let YD(m) and BD(n) denote the events of exactly m yield defects and exactly n burn-in defects, respectively. If we employ a negative binomial yield model and assume the defects are statistically independent, the total yield, i.e., the probability of no yield or burn-in defects is:

$$Y = \Pr\{YD(0), BD(0)\} = \left(1 + \frac{\lambda_{YD} + \lambda_{BD}}{\alpha}\right)^{-\alpha}$$

and the probability of no yield defects is:

$$Y_{YD} = \Pr\{YD(0)\} = \left(1 + \frac{\lambda_{YD}}{\alpha}\right)^{-\alpha}, \qquad (3.29)$$

and the probability of no burn-in defects given no yield defects is:

$$Y_{BD} = \Pr\{BD(0)|YD(0)\} = \left(1 + \frac{\lambda_{BD}}{\alpha + \lambda_{YD}}\right)^{-\alpha}, \qquad (3.30)$$

By merging Equations from (3.28) to (3.30), the burn-in yield can be formulated by:

$$Y_{BD} = \left[1 + \gamma \left(1 - (Y_{YD})^{1/\alpha}\right)\right]^{-\alpha}.$$

(3.31)

## III.6. Reliability Model in an Useful Life Period

In the useful life period, it is very difficult to develop a generalized reliability model because of the complex failure mechanisms of integrated circuits. Since the failure rate in this period is generally assumed to be a constant, a simple exponential reliability model of Equation (3.7) is extensively used:

$$R(t) = e^{-\mu t}$$

where t is the mission time and  $\mu$  is the failure rate of an integrated circuit. General measurement unit of the failure rate is failures per 10<sup>9</sup> operation hours (FIT). In typical,  $\lambda$  stands for the failure rate, but, in this dissertation, I will use  $\mu$  for the failure rate to distinguish it from the average number of defects in the yield model. For this exponential reliability model, both mean time to failure (MTTF) and mean time between failures (MTBF) are  $1/\mu$ .

Assuming the exponential reliability model, the only remaining problem is to find the appropriate value of  $\mu$  because the mission time t is determined by the customer's needs and the manufacturer's strategy. There are two approaches to estimate  $\mu$ . The first approach is to use accelerated life testing (ALT) [4, 25]. Most microelectronics products have a very long lifetime with a very low failure rate. ALT imposes excessive electrical and environmental stresses, which are greater than the normal operating conditions, for a reasonable amount of time. The lifetime and failure rate of a product, therefore, can be estimated by extrapolating the ALT results into normal operating conditions. A temperature test for chemical reactions, a voltage test for time-dependant dielectric breakdown (TDDB), a humidity test for moisture resistance, and a current density test for electromigration are the widely used ALT methods in semiconductor manufacturing [25].

For example, let us consider ALT for temperature stress and voltage stress. It is generally agreed that the famous Arrhenius equation explains well the relationship between a chemical reaction and temperature as follows:

$$R_r = k_0 \exp\left(-\frac{E_a}{kT}\right),\tag{3.32}$$

where  $R_r$  is the chemical reaction rate;  $k_0$  is a constant;  $E_a$  is the activation energy in the eV unit; k is the Boltzmann's constant (8.617e-5 eV/K); and T is the temperature in the K unit. Let  $T_1$  be the temperature of the ALT and  $T_2$  be the temperature at the normal operating condition. Then, the lifetime of the system can be estimated by modifying Equation (3.32) as follows:

$$L_{T2} = L_{T1} \exp\left[-\frac{E_a}{k} \left(\frac{1}{T_1} - \frac{1}{T_2}\right)\right],$$

(3.33)

where  $L_{T1}$  and  $L_{T2}$  are measured or estimated lifetimes related to temperature  $T_1$ and  $T_2$ , respectively. For voltage stress, the following relationship is typically used:

$$L_{V2} = L_{V1} \exp\left[-B(V_2 - V_1)\right], \qquad (3.34)$$

where  $L_{V1}$  and  $L_{V2}$  are lifetimes related to applied voltage  $V_1$  and  $V_2$ , respectively, and B is the voltage acceleration constant which depends on the oxide film. The lifetime of the integrated circuit can be computed by projecting the accelerated conditions,  $T_1$  and  $V_1$ , into the normal condition,  $T_2$  and  $V_2$ , respectively. If we consider both of the tests, the failure rate  $\mu$  can be estimated with a confidence level as follows:

$$\mu = \frac{\chi_{1-\alpha}^2(2n+2)}{2 \cdot A_f \cdot t_0} \cdot 10^9 (\text{FITS}), \qquad (3.35)$$

where r is the number of failures;  $\alpha$  is the confidence level for the  $\mathcal{X}^2$  distribution; n is the number of samples;  $t_0$  is the test time; and  $A_f$  is the acceleration coefficient, i.e.,  $(L_{T2}/L_{T1}) \cdot (L_{V2}/L_{V1})$ .

A second approach is to use industry or military standards such as MIL-STD-217, Bellcore, JAP, etc. With these standards, many factors are involved in the estimation of  $\mu$ : temperature, quality, voltage stress, environmental factors, etc. The only difference in these standards is that they consider different factors and formulae to calculate  $\mu$ . To see detailed explanations of and references to the various standards for microelectronic devices, refer to a good summary paper [14]. In fact, some formulae in the standards include the ALT feature. However, the estimated  $\mu$  using the standards is often different from the actual field data for recently developed semiconductor devices because they do not reflect emerging devices and manufacturing technology.

#### CHAPTER IV

# MODELING OF FAULT-TOLERANT MEMORY INTEGRATED CIRCUITS

Memory integrated circuits such as DRAM (dynamic random access memory), SRAM (static random access memory), and flash memories have often employed fault-tolerant techniques to enhance manufacturing yield at a low additional cost. The importance of fault-tolerant techniques will increase even more as microprocessors and system-on-a-chips (SoC) demand more memory capability on their chips. Since the 1980's, various yield and reliability models for fault-tolerant memory integrated circuits have been developed [5, 6, 26, 27, 28, 29]. However, most of these models gave only partial consideration to failure types, redundancies, error correcting codes, and burn-in effects. In this section, these yield and reliability models are integrated into the defect-based yield model and the reliability model that consider both hierarchical redundancies and error correcting codes.

## IV.1. System Architecture of a Typical Memory IC

A modern memory integrated circuit consists largely of peripheral circuits for the controller and the interface circuits and memory arrays for information data storage. Figure 6 shows the design architecture of a typical memory integrated circuit. We define a memory block as a memory array which includes column and row redundancies. Each memory block consists of a sey of memory segments, row and column redundancies, and supporting circuits such as a row decoder and stitching region, a column decoder and sense amplifier, buses, selection switches, and a fuse box for replacing failed memories as redundancies. Block redundancy (BR in Figure 6) may

| Peripheral<br>Circuits | Memory<br>Block | Memory<br>Block | Memory<br>Block | Memory<br>Block |

|------------------------|-----------------|-----------------|-----------------|-----------------|

|                        | BR              | BR              | BR              | BR              |

|                        | Memory<br>Block | Memory<br>Block | Memory<br>Block | Memory<br>Block |

Figure 6: Schematic Diagram of a Typical Memory Integrated Circuit