# DESIGN OF LARGE TIME-CONSTANT SWITCHED-CAPACITOR FILTERS FOR BIOMEDICAL APPLICATIONS

A Thesis

by

SANJAY TUMATI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2004

Major Subject: Electrical Engineering

### DESIGN OF LARGE TIME-CONSTANT SWITCHED-CAPACITOR

## FILTERS FOR BIOMEDICAL APPLICATIONS

A Thesis

by

### SANJAY TUMATI

### Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved as to style and content by:

Jose Silva-Martinez (Chair of Committee)

> Prasad Enjeti (Member)

Ugur Cilingiroglu (Member)

> Jay R. Porter (Member)

Chanan Singh (Head of Department)

December 2004

Major Subject: Electrical Engineering

### ABSTRACT

Design of Large Time-Constant Switched-Capacitor Filters for Biomedical Applications.

(December 2004)

Sanjay Tumati, B.Tech., Indian Institute of Technology, Mumbai, India Chair of Advisory Committee: Dr. Jose Silva-Martinez

This thesis investigates the various techniques to achieve large time constants and the ultimate limitations therein. A novel circuit technique for the realization of large time constants for high pass corners in switched-capacitor filters is also proposed and compared with existing techniques. The switched-capacitor technique is insensitive to parasitic capacitances and is area efficient and it requires only two clock phases. The circuit is used to build a typical switched-capacitor front end with a gain of 10. The low pass corner is fixed at 200 Hz. The high pass corner is varied from 0.159Hz to 4 Hz and various performance parameters, such as power consumption, silicon area etc., are compared with conventional techniques and the advantages and disadvantages of each technique are demonstrated. The front-ends are fully differential and are chopper stabilized to protect against DC offsets and 1/f noise. The front-end is implemented in AMI0.6um technology with a supply voltage of 1.6V and all transistors operate in weak inversion with currents in the range of tens of nano-amperes.

# DEDICATION

To my Late Grandmother

#### ACKNOWLEDGEMENTS

I gratefully acknowledge my advisor Dr. Jose Silva-Martinez for giving me great freedom in choosing a thesis topic and then patiently answering my queries and keeping me on the right track. Dr. Silva has this amazing ability to quickly penetrate the core of any circuit which would elude me for weeks. This ability of his used to be a great source of embarrassment to me (and as I later found out, to almost everyone who had technical discussions with him). However, it was possibly the best training I could get in analyzing circuits in an intuitive non-mathematical way. I am also thankful to Dr. Jay R. Porter who has been my employer, an excellent one at that, for almost my entire stay at A&M. I would like to thank David Genzer, Dr. Ashok Nedungadi and Dr. Lee Hudson of Biotronik GmBh for giving me an opportunity to intern with them. They effectively suggested my thesis topic and addressed many practical issues and concerns that I have had. I would like to thank Dr. Cilingiroglu for his excellent course on device physics. Thanks to him, I am no longer afraid of device physics. His friendly manner and his humility in spite of his apparent genius for device physics have made a deep impression on me. Finally, I would like to thank my father for keeping me calm when things threatened to overwhelm me and my mother for constantly calling me and asking me if I was done with my thesis already. Without this kind of outside support, this thesis would never have been completed.

# TABLE OF CONTENTS

|            |         |                                  | Page |

|------------|---------|----------------------------------|------|

| ABSTRACT   | Γ       |                                  | iii  |

| DEDICATI   | ON      |                                  | iv   |

| ACKNOWL    | EDGEN   | MENTS                            | V    |

| TABLE OF   | CONTE   | ENTS                             | vi   |

| LIST OF FI | GURES   |                                  | ix   |

| LIST OF TA | ABLES . |                                  | xiii |

| CHAPTER    |         |                                  |      |

| Ι          | INTR    | RODUCTION                        | 1    |

|            | 1.1     | Motivation                       | 1    |

|            | 1.2     | On-chip Implementation           | 4    |

|            | 1.3     | The Switched-Capacitor Circuitry | 6    |

| II         | OTA     | DESIGN                           | 9    |

|            | 2.1     | Operation in Weak Inversion      | 9    |

|            | 2.2     | The Folded-Cascode OTA           | 11   |

|            | 2.3     | The Single-Stage OTA             |      |

|            | 2.4     | Mismatches in OTA Transistors    | 16   |

|            | 2.5     | Conclusions                      | 19   |

| III        | LAR     | GE TIME CONSTANTS IN SC CIRCUITS | 20   |

IV

| TER |      |                                                     | Page |

|-----|------|-----------------------------------------------------|------|

|     | 3.1  | Conventional Integrator                             | 20   |

|     | 3.2  | Fleischer-Laker (FL) Biquad                         | 22   |

|     | 3.3  | The T-Cell Method                                   |      |

|     | 3.4  | The Split-Integrating Capacitor Technique           |      |

|     | 3.5  | The Nagaraj Technique                               |      |

|     | 3.6  | Combining the FL Biquad with the Nagaraj Integrator | 46   |

|     | 3.7  | Conclusions                                         | 51   |

| V   | LAR  | GE TIME CONSTANTS IN SC HIGH PASS FILTERS           | 52   |

|     | 4.1  | Realizing a Differentiator                          | 53   |

|     | 4.2  | Basic High Pass Filter                              | 54   |

|     | 4.3  | Partial Positive Feedback                           | 57   |

|     | 4.4  | Attenuated Feedback HPF                             | 61   |

|     | 4.5  | Differentiators                                     | 71   |

|     | 4.6  | Noise Analysis                                      | 73   |

|     | 4.7  | Comparisons                                         | 79   |

|     | 4.8  | Conclusions                                         | 84   |

| V   | PRE- | AMP DESIGN                                          | 85   |

|     | 5.1  | Introduction and Specifications                     | 85   |

|     | 5.2  | Pre-amp Using the Proposed HPF                      |      |

|     | 5.3  | Pre-amp Using the FL-Nagaraj Biquad                 | 93   |

| CHAPTER    |                              | Page |

|------------|------------------------------|------|

| 5.4        | The Nagaraj Low Pass Filter  |      |

| 5.5        | Charge Injection and Leakage |      |

| 5.6        | Clock Feed-Through           |      |

| 5.7        | Comparisons                  |      |

| 5.8        | Layout                       |      |

| 5.9        | Simulation Results           |      |

| VI CON     | CLUSIONS                     | 121  |

| REFERENCES |                              |      |

| VITA       |                              |      |

# LIST OF FIGURES

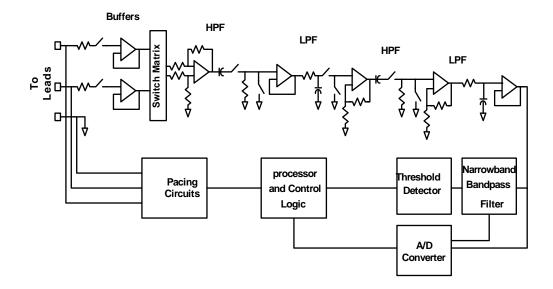

| Fig. 1-1.  | Experimental pacemaker                                              | 2  |

|------------|---------------------------------------------------------------------|----|

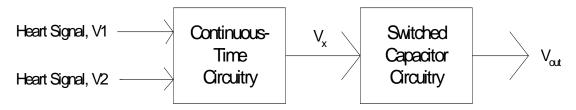

| Fig. 1-2.  | High level block diagram of pacemaker pre-amp                       | 5  |

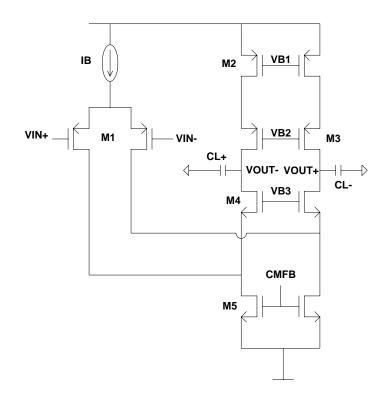

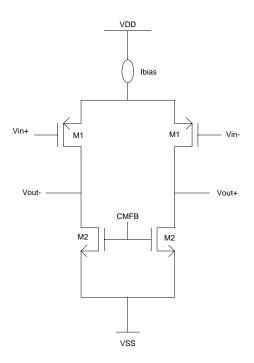

| Fig. 2-1.  | Conventional fully differential folded-cascode OTA                  | 12 |

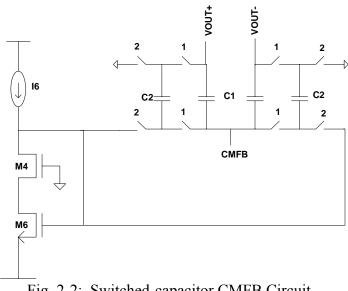

| Fig. 2-2.  | Switched-capacitor CMFB circuit                                     | 13 |

| Fig. 2-3.  | Conventional fully differential single-stage OTA                    | 15 |

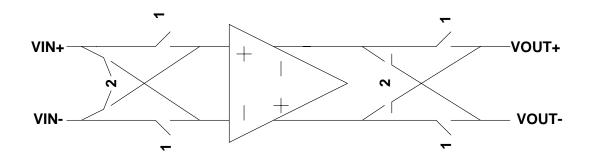

| Fig. 2-4.  | Chopper stabilization to chop the OTA offsets to higher frequencies | 17 |

| Fig. 2-5.  | The effect of chopper stabilization on an ideally stationary output | 18 |

| Fig. 3-1.  | Conventional SC lossless integrator                                 | 20 |

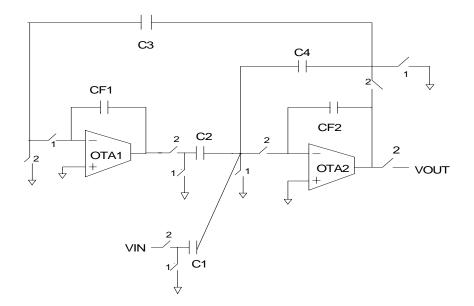

| Fig. 3-2.  | Conventional Fleischer-Laker biquad for low Q applications          | 22 |

| Fig. 3-3a. | Loading configuration for OTA 2 of Fig. 3-2 during phase 2          | 28 |

| Fig. 3-3b. | Circuit of Fig. 3-3a with feedback loop opened                      | 28 |

| Fig. 3-4.  | Conceptual implementation of large integrator time constants        | 30 |

| Fig. 3-5.  | Large TC integrator using the T-Cell technique                      | 31 |

| Fig. 3-6.  | Conceptual diagram of the split-integrating capacitor technique     | 32 |

| Fig. 3-7.  | SC implementation of the concept shown in Fig. 3-6                  | 34 |

| Fig. 3-8.  | Conceptual implementation of large TC LPF                           | 35 |

| Fig. 3-9.  | A large time constant integrator in the FL biquad                   | 36 |

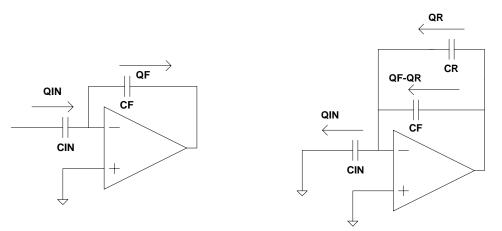

| Fig. 3-10. | The Nagaraj integrator                                              | 39 |

| Fig. 3-11. | Illustrating the integrating principle in the Nagaraj integrator    | 40 |

Page

# Page

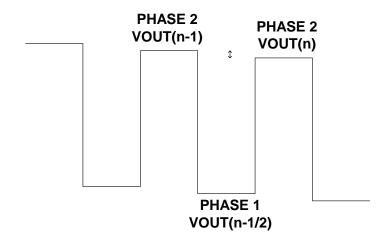

| Fig. 3-12.         | Illustrating the voltage waveforms in the Nagaraj integrator   | 41 |

|--------------------|----------------------------------------------------------------|----|

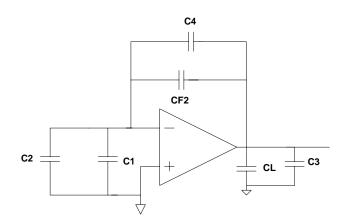

| Fig. 3-13.         | The Nagaraj low pass filter                                    | 42 |

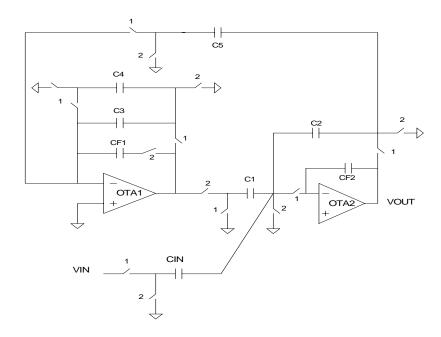

| Fig. 3-14.         | FL biquad using the Nagaraj integrator                         | 47 |

| Fig. 4 <b>-</b> 1. | Conventional SC differentiator                                 | 53 |

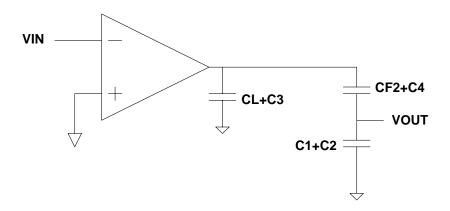

| Fig. 4 <b>-</b> 2. | Conventional continuous time high pass filter                  | 54 |

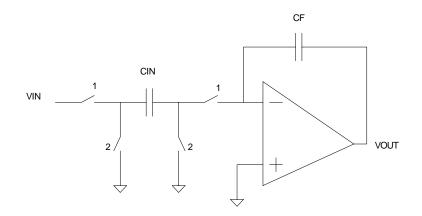

| Fig. 4-3.          | Conventional SC high pass filter                               | 55 |

| Fig. 4-4.          | Illustrating loading by breaking the feedback loop in Fig. 4-3 | 56 |

| Fig. 4-5.          | Conceptual partial positive feedback                           | 57 |

| Fig. 4-6.          | Simple SC implementation of partial positive feedback          | 58 |

| Fig. 4-7.          | A sophisticated implementation of partial positive feedback    | 59 |

| Fig. 4-8.          | Conceptual attenuated feedback                                 | 61 |

| Fig. 4-9.          | Conceptual SC implementation of attenuated feedback            | 62 |

| Fig. 4-10.         | The T-Cell technique adapted to high pass filters              | 63 |

| Fig. 4-11.         | Attenuated feedback in SC HPFs using two OTAs                  | 64 |

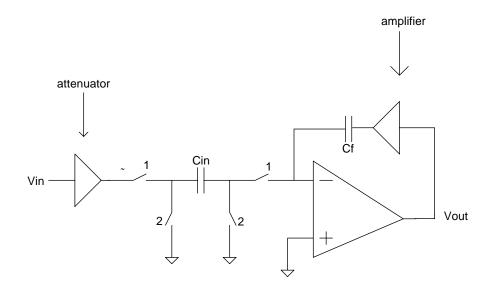

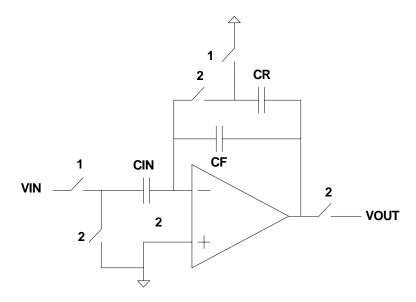

| Fig. 4-12.         | Fully differential LTC SC HPF using only one OTA               | 65 |

| Fig. 4-13a         | HPF of Fig. 4-12 in phase 2 performing attenuation             | 66 |

| Fig. 4-13b         | HPF of Fig. 4-12 in phase 1 performing high pass filtering     | 66 |

| Fig. 4-14.         | Loading on OTA of Fig. 4-12 during phase 1                     | 69 |

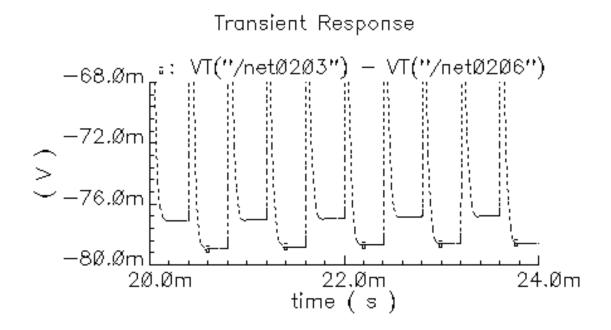

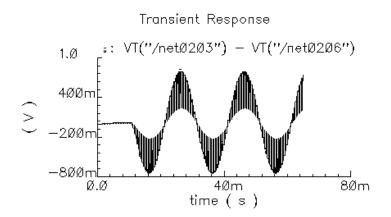

| Fig. 4-15.         | Transient waveforms for the structure of Fig. 4-12             | 70 |

| Fig. 4-16.         | Large time constant SC differentiator                          | 72 |

| Fig. 4-17a.        | The CT HPF                                                     | 73 |

xi

| Fig. 4-17b. | The CT LPF                                                               | 75 |

|-------------|--------------------------------------------------------------------------|----|

| Fig. 4-17c. | HPF implementation using buffers and an LPF                              | 76 |

| Fig. 4-17d. | CT FL biquad                                                             | 77 |

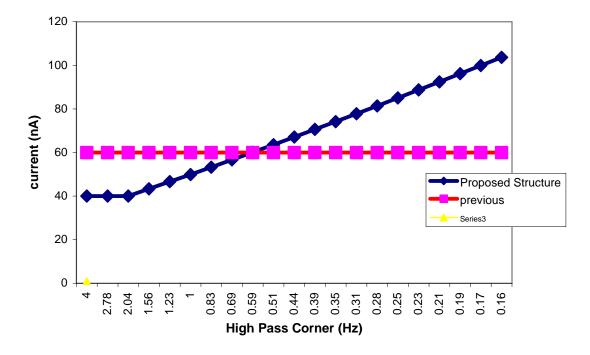

| Fig. 4-18.  | Power comparison plots                                                   | 81 |

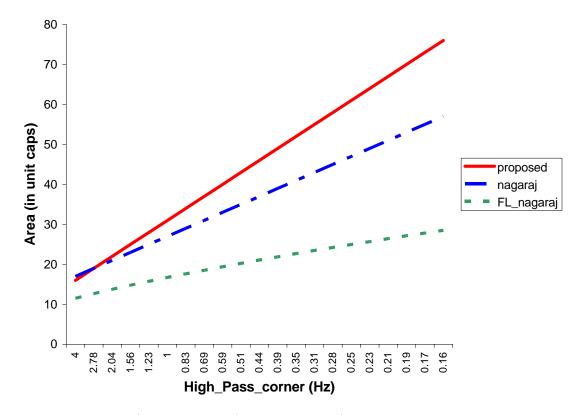

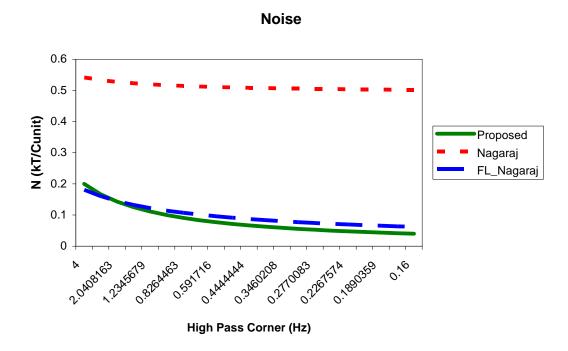

| Fig. 4-19.  | Capacitor area comparisons                                               | 82 |

| Fig. 4-20.  | Noise comparison plots                                                   | 83 |

| Fig. 5-1.   | Block diagram of pacemaker pre-amp                                       | 86 |

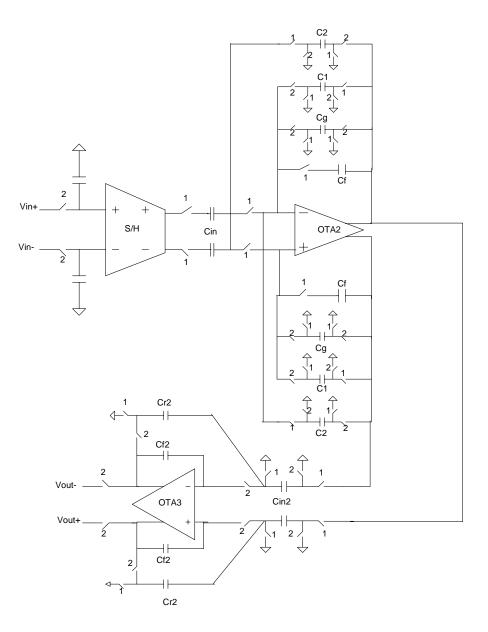

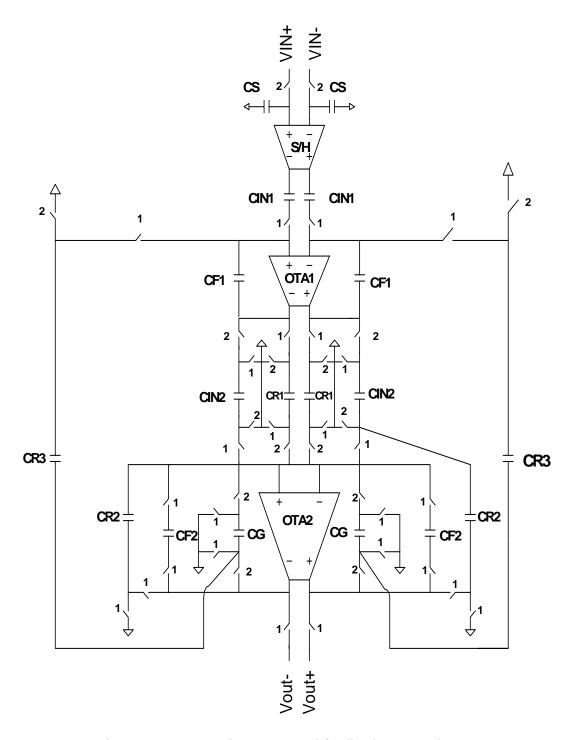

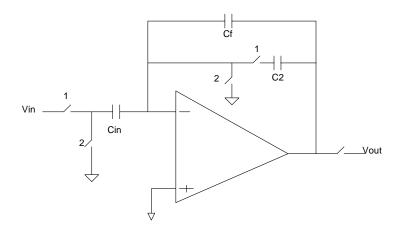

| Fig. 5-2.   | Pre-amp using proposed fully differential HPF                            | 87 |

| Fig. 5-3.   | Pre-amp using attenuated feedback HPF and OTA reuse                      | 88 |

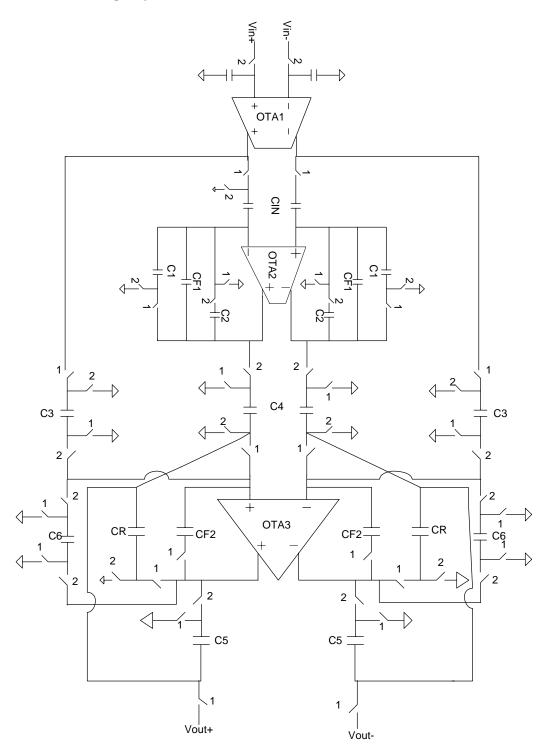

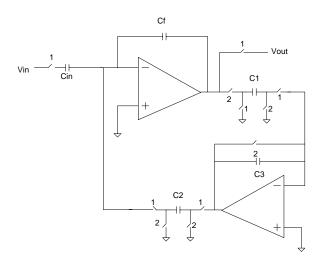

| Fig. 5-4.   | Pre-amp using FL biquad and Nagaraj integrator                           | 94 |

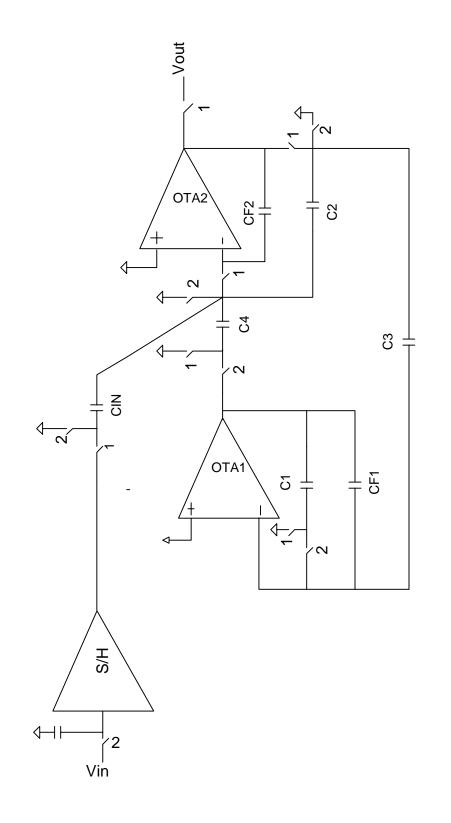

| Fig. 5-5.   | Pre-amp implementation using Nagaraj LPF and OTA reuse                   | 98 |

| Fig. 5-6a.  | The Nagaraj LPF10                                                        | 04 |

| Fig. 5-6b.  | Nagaraj integrator10                                                     | )5 |

| Fig. 5-6c.  | Proposed HPF10                                                           | )5 |

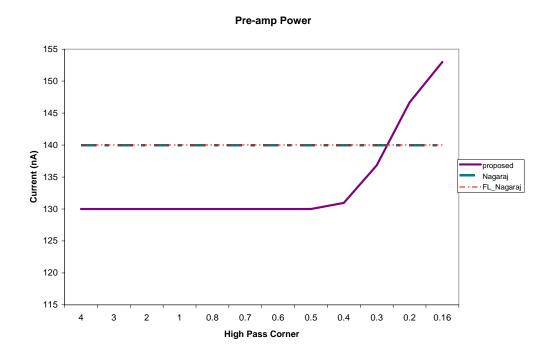

| Fig. 5-7.   | Power consumption of the three pre-amps, $I_{NAGARAJ}=I_{FL-NAGARAJ}$ 10 | )6 |

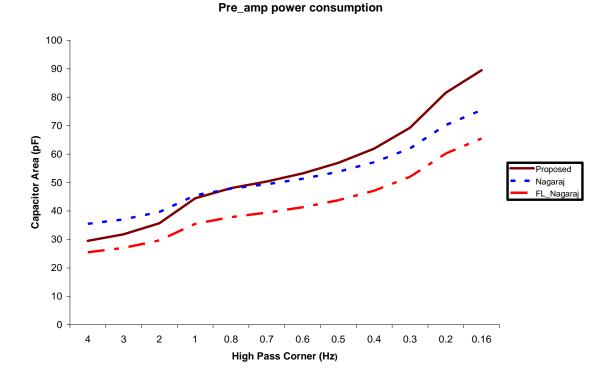

| Fig. 5-8.   | Capacitor area of the three pre-amps10                                   | )7 |

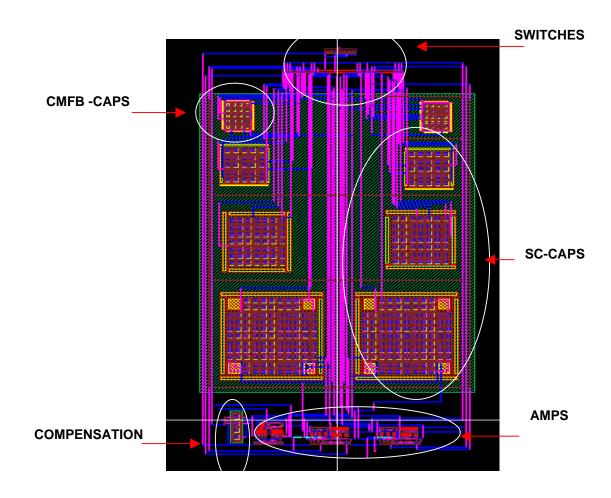

| Fig. 5-9.   | HPF based pre-amp layout1                                                | 08 |

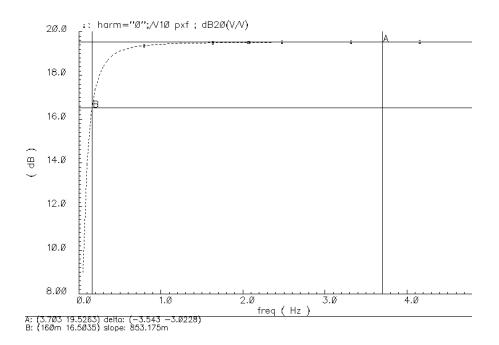

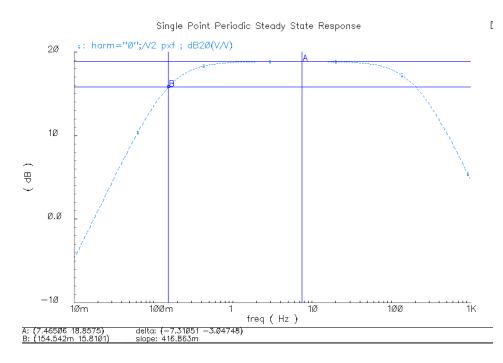

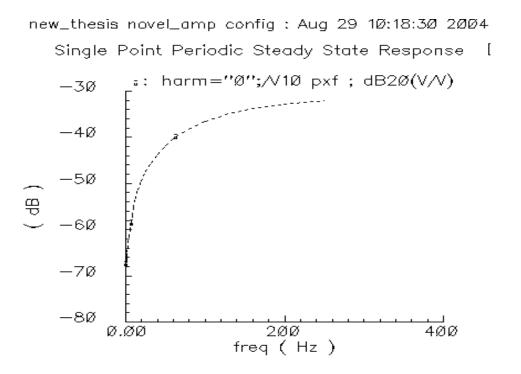

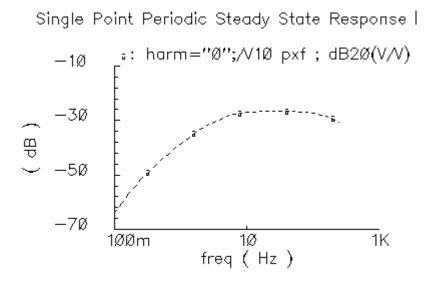

| Fig. 5-10a. | PSS response showing high pass corner1                                   | 10 |

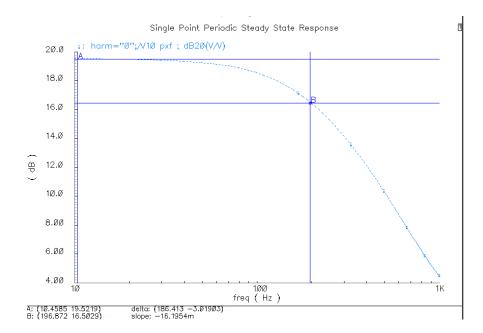

| Fig. 5-10b. | PSS response showing low pass corner                                     | 10 |

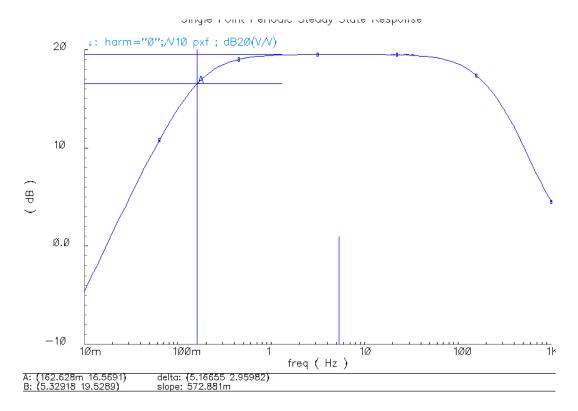

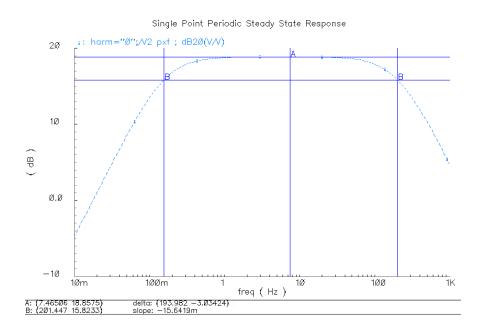

| Fig. 5-10c. | Complete PSS response for the proposed pre-amp1                          | 11 |

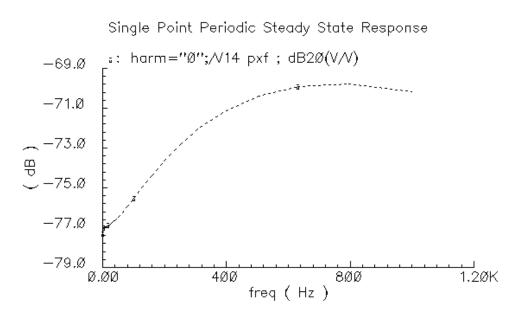

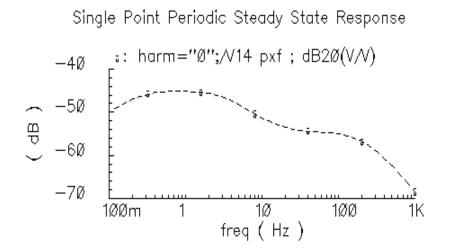

| Fig. 5-11a. | Complete PSS response for FL biquad showing the high pass corner1        | 12 |

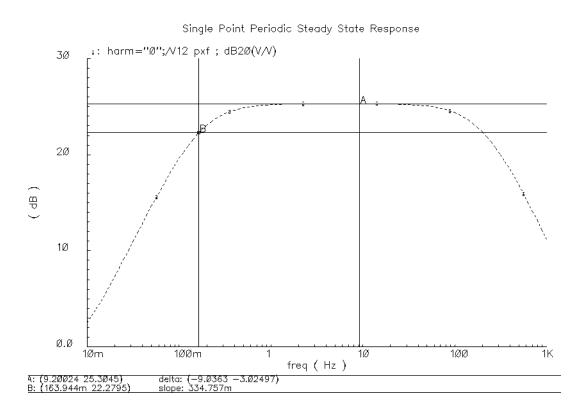

# Page

| Fig. 5-11b. | Complete PSS response of FL biquad showing the low pass corner112 |

|-------------|-------------------------------------------------------------------|

| Fig. 5-12a. | PSS response showing high pass corner113                          |

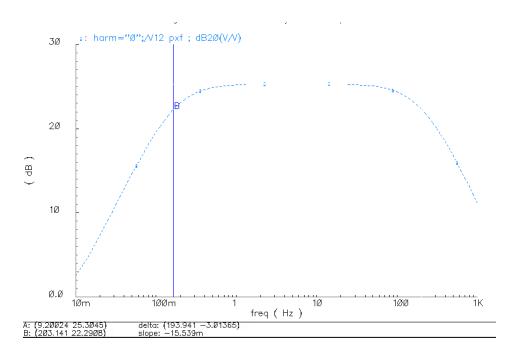

| Fig. 5-12b. | PSS response showing low pass corner114                           |

| Fig. 5-13a. | CMRR in presence of 5% path loading mismatch116                   |

| Fig. 5-13b. | CMRR in presence of 1% ratio mismatch116                          |

| Fig. 5-13c. | PSRR in presence of 5% ratio mismatch117                          |

| Fig. 5-13d. | PSRR in presence of 1% ratio mismatch117                          |

| Fig. 5-14a. | Demonstrating output swing in the OTA118                          |

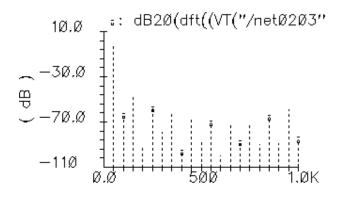

| Fig. 5-14b. | Demonstrating linearity via FFT. THD > 40dB119                    |

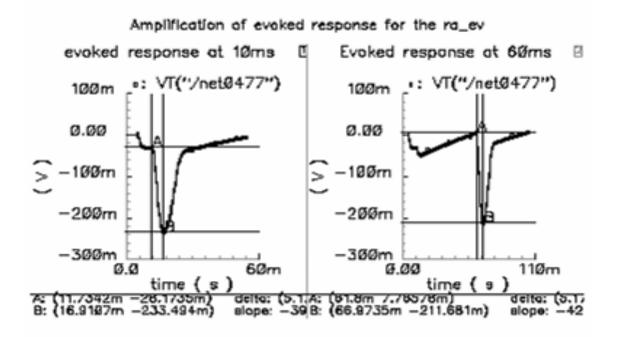

| Fig. 5-15.  | Output to the evoked response                                     |

# LIST OF TABLES

| Table 3-1. | Capacitor values for FL biquad of Fig. 3-2                          | 25 |

|------------|---------------------------------------------------------------------|----|

| Table 3-2. | Capacitor values for Fig. 3-9, DNM stands for does not matter       | 37 |

| Table 3-3. | Capacitor values for Fig. 3-13 optimizing spread                    | 13 |

| Table 3-4. | Capacitor values for Fig. 3-13 optimizing area                      | 14 |

| Table 3-5. | Capacitor values for Fig. 3-14 optimizing spread                    | 19 |

| Table 3-6. | Capacitor values for Fig. 3-14 optimizing loading on opa-2          | 19 |

| Table 4-1. | Capacitor values for Fig. 4-12                                      | 57 |

| Table 4-2. | Table of comparisons for various structures for a 4Hz 3-dB corner7  | 79 |

| Table 4-3. | Comparison table for various structures for a 0.159 Hz 3 dB corner8 | 30 |

| Table 5-1. | Capacitor values for Fig. 5-3 for a 4 Hz high pass corner9          | 0  |

| Table 5-2. | Capacitor values for Fig. 5-3 for a 0.159 Hz high pass corner9      | 1  |

| Table 5-3. | Capacitor values for Fig. 5-4 for a 4 Hz high pass corner9          | 6  |

| Table 5-4. | Capacitor values for Fig. 5-4 for a 0.159 Hz high pass corner9      | 7  |

| Table 5-5. | Capacitor values for Fig. 5-5 for a 4 Hz high pass corner10         | 0  |

| Table 5-6. | Capacitor values for Fig. 5-5 for a 0.159 Hz high pass corner10     | 1  |

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Motivation

The realization of large time constants on-chip is of considerable interest in biomedical and electrochemical applications, which require real time processing of analog voltages [1]. One example is a pre-amp used in a pacemaker circuit. Other examples include some biomedical applications in which stand alone differentiators and high pass filters are required [2,3]. In this thesis, we explore the problem of large time constants and present some novel differentiators and high pass structures, which realize large time constants. The novel structures will be used in a biomedical switched-capacitor pre-amplifier, which is used in pacemaker circuits.

In pacemaker circuits, whenever the heart is given a pacing pulse, the heart responds through a set of signals. The response of the heart to a pacing pulse is referred to as the *evoked response*. This response is first captured by the analog front-end, amplified, filtered and fed to the DSP core. The DSP core performs signal processing on this amplified and filtered version of the response and the decision circuit uses the results of this processing. A block level schematic of a pacemaker [4] is given in Fig. 1-1. To make an intelligent decision, the pacemaker front end needs to capture as much information as possible in the *evoked response*.

This thesis follows the style and format of IEEE Journal of Solid State Circuits.

Fig. 1-1: Experimental pacemaker

The front end is basically a filter, which provides amplification to the evoked response. The input to the front end comes from the leads that are connected to the various chambers of the heart (left/right atrium/ventricle). The wideband analog front-End consists of all circuits up to the Narrow-Band Band-pass filter and the ADC.

The front end includes the following:

- 1. High input impedance buffers so as not to load the heart chambers.

- 2. A switch matrix to multiplex the inputs from the leads. There are a total of 8 input leads. Only two have been shown in Fig. 1.1.

- 3. The first HPF, which consists of a differential amplifier providing a gain of 10 and passive RC components.

- 4. The first LPF, which consists of a buffer and passive RC components.

- 5. A second HPF incorporating a gain of 5.

- 6. A second LPF incorporating a gain of 2.

- 7. A buffer at the end to interface with the narrow band filter and the rest of the digital circuitry.

- 8. One must have also observed a large number of switches in what appears to be continuous time circuitry. The reason for the switches is that the Front end must be switched on gradually. First the high pass switches on and is given some time to settle down to its steady state. Once the high pass settles, the low pass filter switches ON and so on and so forth. The reason for switching on the front-end gradually is that if a large device with such high open loop gain is switched on all at once, there will be a considerable amount of ringing. And this ringing might bury the evoked response.

It must be mentioned here that Fig. 1-1 is only a conceptual discrete implementation. The actual on-chip implementation will be considerably different as will be discussed later in this chapter.

The *evoked response* contains useful information in frequencies less than 1Hz. The information can be processed by the DSP in the pacemaker to decide on whether a pacing pulse must be given to the heart. More sophisticated pacemakers are expected to decide on even the amplitude and duration of the pacing pulse. Since the pulse generator in the pacing circuit consumes so much power, it is not desirable to give the heart a pacing pulse when it is not needed. Thus the front-end needs to capture the *evoked response* with a fair amount of accuracy, i.e. low distortion, high SNR and accurate filter corners. Currently the biomedical industry uses front-ends with a high pass corner of 4

Hz and a low pass corner of 200 Hz with a clock frequency of 2.5KHz. The main aim is to push the high pass corner to sub-hertz frequencies.

#### **1.2 On-chip Implementation**

The block diagram in Fig. 1-1 shows the discrete realization of the pacemaker front-end. However, an on-chip realization is required. The problem with on-chip implementations is that precise resistors and capacitors are not available on-chip in most CMOS processes. Typically the RC time-constant varies by 20%. Thus, either Laser trimming is required for on-chip passive components or else they have to go off-chip. Both options are expensive.

Switched-capacitor implementations can offer very accurate time constants and are thus ideal for low frequency applications such as pacemaker circuitry. Another advantage is that switched-capacitor circuits are very linear. Continuous time circuits based on transconductances inherit their non-linearity from the MOS transistor. Switched-capacitor circuits are much less dependent on the non-linearity of the MOS transistor.

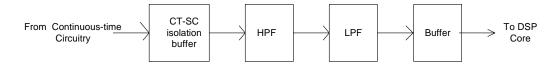

However, we cannot completely eliminate the continuous time circuitry. The reason is that switched-capacitor circuits cause aliasing (down-conversion) of high frequency noise to low frequencies and degrade the SNR. Thus a continuous time antialiasing low pass filter will always be required to attenuate the high frequency noise before it is aliased by the switched-capacitor circuitry. Fig. 1-2 shows a high level block diagram of an on-chip pacemaker pre-amp.

Fig. 1-2: High level block diagram of pacemaker pre-amp

The continuous time circuitry consists of:

- A low noise gain stage of 10. This ensures that the noise of succeeding stages is less important. This is similar to the use of Low Noise amplifiers in RF frontends.

- 2. A high pass filter to remove the offsets, which are residues from the pacing pulse.

- 3. A low pass anti-aliasing filter.

The switched-capacitor circuitry consists of a high pass filter, a low pass filter and an amplifier with a gain of 10. Thus the complete front end has a second order roll off for both the high pass and low pass corners and a combined gain of 100.

#### **1.3** The Switched-Capacitor Circuitry

Our focus here is the switched-capacitor circuitry and the problem of realizing large time constants therein. The switched-capacitor circuitry has a gain of 10, a low pass corner of 4Hz and a high pass corner of 200 Hz. In addition, the continuous time circuitry is followed immediately by a switched-capacitor S/H hold stage to isolate the continuous

time circuitry from the switched-capacitor circuitry. A S/H stage is used as a buffer between the blocks to prevent loading on the continuous circuitry and the switched-capacitor circuitry.

The realization of large time constants is the main bottleneck in the design of the front-end. The clock frequency is 3-4 orders of magnitude larger than the high pass corner. Two factors are involved in the selection of 2.5 KHz as the clock frequency. One is the low pass corner (quite high at 200 Hz) and the other is the need to maintain compatibility with the rest of the system. If conventional switched-capacitor structures are used in the above applications, the capacitor ratios tend to be large enough to discourage their implementation in integrated circuits.

Many techniques have been proposed to implement large time constants [5-9]. These techniques will be discussed in subsequent chapters. All of the techniques are for use in integrators or in first order low pass sections. To the author's knowledge, there is no technique yet to achieve large time constants in first order high pass sections or differentiators. Switched-capacitor differentiators are used in audio codecs and in some biomedical applications [2,3]. It is quite intuitive that the best way to achieve a high pass sections and amplifiers. We will see that this intuition holds in some cases, but not in others.

Conventionally, there are two methods to achieve a high pass corner in switchedcapacitor circuits.

1. Band-pass biquads: Biquads are usually used in narrow band filtering applications where complex poles are required. In pacemaker applications, the front-end is a wideband filter and hence it is hard to justify using a biquad. One reason is that wideband transfer functions realized using Bi-quads have a greater passband ripple than by using first order sections. The other reason is that in wideband applications, biquads introduce greater errors than first order sections. Biquads, in general, also have lower dynamic range than first order sections. Further, in any implementations of band pass functions using ideal biquads, the zero of the transfer function is at DC. However, in real biquads, due to finite DC gain of the op-amps, the zero of the transfer function is not at DC. Rather, it is at a low frequency. This low frequency zero introduces an error in the 3-dB high pass corner, especially if that 3-dB corner is at a very low frequency. This statement will be proved further in Chapter II when we discuss biquad implementations of large time constants. Thus the error (in the corner) would be greater in a bi-quad. Nevertheless, the Fleischer-Laker biquad can achieve wide band operation. Indeed, the Fleischer-Laker biquad is widely used in single ended applications where DC offset is a problem. In differential ended applications, these offsets are largely eliminated by the common mode feedback circuitry.

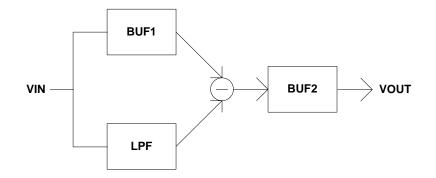

2. *First order sections*: A high pass corner can be achieved, by designing a low pass filter with the same low pass corner as the desired high pass corner and then subtracting from a buffer or a gain stage as illustrated in the equations below

$$H_{LPF}(s) = \frac{1}{1 + \frac{s}{\rho}}$$

$$H_{HPF}(s) = 1 - H_{LPF}(s) = \frac{s}{s + \rho}.$$

(1.1)

If by some way, we could build a first order high pass section, we could eliminate the buffer or the gain stage and thus save power. This provides our motivation for coming up with a new scheme to realize large time constants in high pass sections.

#### CHAPTER II

#### OTA DESIGN

#### 2.1 Operation in Weak Inversion

Biomedical applications are very low frequency applications. Thus the operational transconductor amplifiers (OTAs) used in switched-capacitor circuits for such applications have a much greater amount of time for settling. For this reason, the transistors in biomedical applications operate in weak inversion and carry currents in the nano-ampere range. Usually, the OTA power requirements in switched-capacitor applications are set by the required DC gain as well as the unity gain frequency. However, for biomedical applications, one further consideration comes into play. Transistors operating in weak inversion for biomedical applications must carry a minimum current regardless of the DC gain or settling time requirements. The reason for this is mentioned below.

Transistor currents are quite hard to control as they get smaller and smaller. The reason for this is that a large biasing resistor is required to set the biasing currents. Large resistors inject greater noise and also have lower tolerances. Thus, the biasing resistor cannot be allowed to get arbitrarily large.

The other consideration comes from the digital circuitry. Most pacemakers have analog and digital circuitry on the same chip (true mixed signal product). This makes the analog circuitry quite susceptible to substrate coupling from the digital circuitry. This coupling could momentarily cause spikes in the current flowing in the transistors in the OTA. If the current is small enough, it could even momentarily disappear and heavily impact settling of the OTAs. Thus, a large enough bias current provides a good degree of protection from such coupling.

Finally, the matching between transistors also deteriorates with decreasing current flowing through them.

For all these reasons, the biomedical industry requires that at least 10nA of bias current flows through all transistors. More current might be required depending on settling requirements, or DC gain or noise. But 10nA is the *minimum* bias current that must flow in any transistor for such applications.

In weak inversion operation, the I-V characteristics of the MOS transistor are given by equation (2.1) [1].

$$I_{D} = I_{D0} \frac{W}{L} (e^{(V_{G} - V_{TH})/\eta V_{T}}) [e^{-V_{S}/V_{T}} - e^{-V_{D}/V_{T}}]$$

$$V_{GS} < V_{TH} + 2\eta V_{T}$$

$$V_{DS} > 3V_{T}.$$

(2.1)

Assuming  $V_s=0$  and  $V_D >> \eta V_T$ , the equation above can be simplified as

$$I_{D} = I_{D0} \left(\frac{W}{L}\right) e^{(V_{GS} - V_{TH})/\eta V_{T}}$$

$$V_{DS} > 3V_{T}$$

$$V_{GS} < V_{TH} + 2\eta V_{T}.$$

$$(2.2)$$

From the equation above the trans conductance can be derived as

$$g_m = \frac{I_D}{\eta V_T}.$$

(2.3)

Characterization of long channel as well as short channel transistors gives us a value of around 25-45 mV for  $\eta V_T$ . The equations (2.1)-(2.3) above do not model the output resistance of the transistor. The output resistance due to channel length modulation by the drain-source voltage may be expressed in terms of an extrapolated voltage by

$$r_o = \frac{V_A}{I_D}.$$

(2.4)

V<sub>A</sub> can be referred to as the early voltage.

While the above equations are highly simplified, they greatly aid in design analysis. One can also expect a 20% variation in  $g_m$  and a greater variation in the output resistance from the above equations.

#### 2.2. The Folded-Cascode OTA

Folded-cascode OTAs [11] are popular in switched-capacitor circuits because of their large DC gain and the fast settling time. One such structure is shown in Fig. 2-1. The large DC gain comes from the output stage that is a stack of a common source transistor (M5) and a common gate transistor (M4). Folded-cascode OTAs have a dominant pole at the output and have very good phase margin that allow them to be analyzed as single-pole systems. The good phase margin and absence of any pole-zero pair means that its transient step response has remarkably low ringing. The OTA has a p-channel input pair, which is preferred to an n-channel input pair because of the lower flicker noise of p-channel devices and also the absence of the bulk-effect.

Fig. 2-1: Conventional fully differential folded-cascode OTA

The various parameters of the Folded-cascode OTA are given by equation (2.5).

$$A = g_{m1} (g_{m4} r_{o4} r_{o5} || g_{m3} r_{o3} r_{o2})$$

$$GBW = \frac{g_{m1}}{C_L}$$

$$v_{n,in\_thermal}^2 = \frac{2kT\gamma}{g_{m1}} \left( 1 + \frac{g_{m5}}{g_{m1}} + \frac{g_{m2}}{g_{m1}} \right)$$

$$swing \le V_{DD} - V_{SS} - 4V_{DS,SAT}$$

$$slew = \frac{I_B}{C_L}.$$

(2.5)

The OTA may consume a minimum of 40nA of current (not counting the biasing circuitry). For this minimum power, and a supply of 1.6V, a  $g_m$  of 0.25uA/V and a DC gain of 74 dB are obtained quite easily. As will be seen later, these parameters are enough for almost all of our applications. For instance, a DC gain of 74dB results in less than 1% steady state error for capacitor ratios up to 50. A  $g_m$  of 0.25uA/V can tolerate capacitor loads of up to 10pF for less than 1% settling error for the given clock frequency.

Fig. 2-2: Switched-capacitor CMFB Circuit

The structure in Fig. 2-1 is fully differential. Therefore a common mode feedback circuit is required. The switched-capacitor common-mode feedback circuit used is shown in Fig. 2-2 [10].

The output of the circuit is the node labeled CMFB. This voltage is applied to the gates to transistors M5 in Fig. 2-1. M6 (of Fig. 2-2) is similar in geometry to M5 (of Fig. 2-1) by matching. M6 generates the nominal CMFB voltage. The relation between M5 and M6 is given by

$$\frac{\binom{W}{L}_{5}}{\binom{W}{L}_{6}} = \frac{I_{5,nom}}{I_{6}}.$$

(2.6)

Finally, note that the CMFB circuit is a discrete time circuit. Its z-domain transfer function is given by equation (2.7) below

$$\frac{V_{CMFB}(z)}{V_{O,CM}(z)} = \frac{C_2}{C_1} \frac{1}{1 - z^{-1} + \frac{C_2}{C_1}}$$

$$V_{O,CM} = \frac{V_{OUT}^+ + V_{OUT}^-}{2}.$$

(2.7)

$V_{O,CM}$  is the output common mode voltage of the OTA. To analyze the complete CMFB loop, we need to convert the z-domain representation to an s-domain representation. Note that such an approximation will always be crude owing to the fact the CMFB circuit is expected to settle at a speed that is comparable to the clock frequency. However, such an approximation provides us with some insight into the issues involved in designing the CMFB network. The approximate s-domain representation is given by equation (2.8)

$$\frac{V_{CMFB}(s)}{V_{O,CM}(s)} = \frac{1}{1 + \frac{s}{f_{clk}} \frac{C_1}{C_2}}.$$

(2.8)

The CMFB loop gain is given by

$$loop\_gain = \frac{g_{m5}}{s(C_L + C_1 + C_2) + \left(\frac{g_{o4}g_{o5}}{g_{m4}} + \frac{g_{o3}g_{o2}}{g_{m3}}\right)} \times \frac{1}{1 + \frac{sC_1}{f_{clk}C_2}}.$$

(2.9)

To improve stability, one could increase  $C_L$ , or  $C_2$ . Increasing  $C_L$  will push the dominant pole to a lower frequency, while increasing  $C_2$  would push the dominant pole to a lower frequency and the non-dominant pole to a higher frequency. To increase speed, one could increase  $g_{m5}$ .

### 2.3 The Single-Stage OTA

Fig. 2-3: Conventional fully differential single-stage OTA

Folded cascode OTAs provide very high gain, but for some applications like buffering, such high gains are not required. In such cases, a single stage OTA is good enough. The schematic such an OTA is shown in Fig. 2-3.

The minimum power consumption of such an OTA may be as low as 20nA following the rule that each transistor must carry at least 10nA of current. The various parameters of this OTA are:

$$A = \frac{g_{m1}}{g_{o1} + g_{o2}}$$

$$GBW = \frac{g_{m1}}{C_L}$$

$$slew = \frac{I_{BIAS}}{C_L}$$

$$v_{n,in}^2 = 2 \times \frac{4kT\gamma}{g_{m1}} \left(1 + \frac{g_{m2}}{g_{m1}}\right)$$

$$V_{OUT,SWING} = |V_{DD}| + V_{TH1} - |V_{DS,sat2}|.$$

(2.10)

For a 40nA current and at the supply of 1.6V, this OTA gives us 40 dB of DC gain and  $g_m$  of 0.25uA/V. This OTA has lower power than a folded-cascode OTA and since buffering does not require a very high DC gain, this OTA is most suitable for buffering.

#### 2.4 Mismatches in OTA Transistors

In differential ended structures like in Fig. 2-1 to Fig. 2-3, we do not need to worry about systematic offsets (biasing). However, random offsets could be a problem. We assume that each pair of transistors labeled M1 –M5 are perfectly matched. Under such conditions, there are no differential offsets. However, in real OTAs, offsets are always a

problem. All random offsets are a result of such mismatches between transistors or capacitors that are ideally perfectly matched. Such mismatches lead to differential offsets that could become very critical, as the time constants get larger. This will be demonstrated in succeeding chapters. The offset can be solved by a technique known as chopper stabilization [10] that basically just swaps the asymmetrical signal paths. Chopper stabilization is illustrated in Fig. 2-4 below.

Fig. 2-4: Chopper stabilization to chop the OTA offsets to higher frequencies

The switches are controlled by a chopper clock, whose frequency (chopping frequency) is typically an even multiple of the switched-capacitor clock frequency. The chopping action is very much like the action of a mixer in RF circuits. The offsets as well as 1/f noise is up converted to the chopping frequency. Assume that we have 1/f noise in the bandwidth from 1 Hz to 10Hz. If the chopping clock runs at 1KHz, then the noise is up converted to a frequency bandwidth between 1001 Hz and 1010 Hz. Thus offsets can be taken care of by a chopper clock.

However, chopper stabilization leads to increased swing at both the output nodes of the OTA. This leads to greater settling time and hence greater power consumption. Fig. 2-5 illustrates chopping action for a DC output.

Fig. 2-5: The effect of chopper stabilization on an ideally stationary output

There is another non-ideality introduced by mismatches in the CMFB circuit. Refer back to Fig. 2-2. Lets consider what happens if the capacitors labeled C1 are not equal. Let us also assume that the capacitors labeled C2 are also not equal. Let us further assume that the ratio  $C_2/C_1$  is matched. In this case the total load capacitance at the two differential outputs of the OTA is mismatched causing a mismatch in the dominant pole frequency. This causes a pole-zero doublet, which could introduce common mode ringing. This effect can be minimized by careful matching and cannot be removed by chopper stabilization.

#### 2.5 Conclusions

The minimum power consumption in the OTA is set by requirements such as controllability of bias currents, substrate coupling and matching. Thus, a minimum of 10nA of bias current must flow through each transistor. Thus, a folded-cascode OTA may have power consumption not lower than 40nA. This current, though small provides an OTA with enough  $g_m$  and DC gain so that up to certain values of the capacitor size, the power consumption of the OTA is independent of the loading effect on the OTA. Therefore, even though high pass filters load the OTA more than low pass filters, they do not increase the power consumption up to a certain value of time constants.

#### CHAPTER III

### LARGE TIME CONSTANTS IN SC CIRCUITS

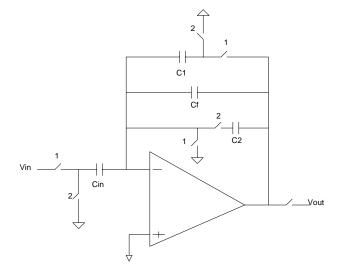

#### **3.1** Conventional Integrator

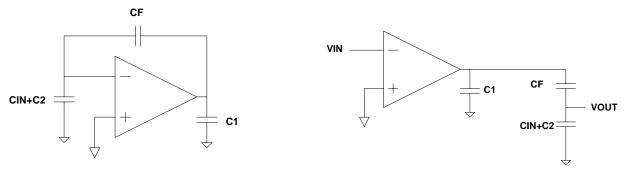

If conventional switched-capacitor (SC) structures are used to implement large time constants, the required capacitor ratios tend to be huge enough to occupy a large area thus preventing on-chip implementation. To illustrate this consider the conventional lossless integrator shown in Fig. 3-1 below [9].

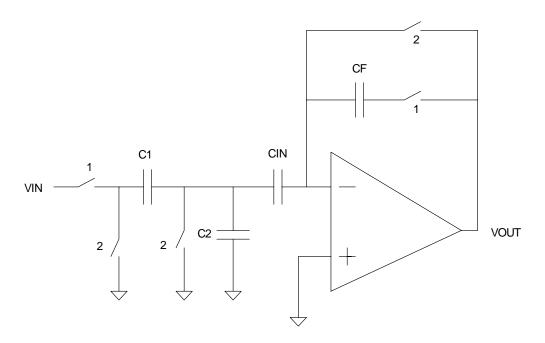

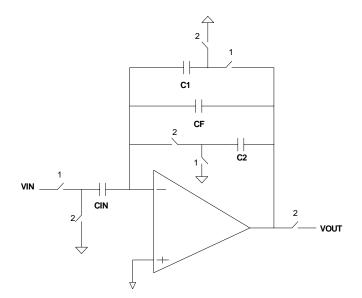

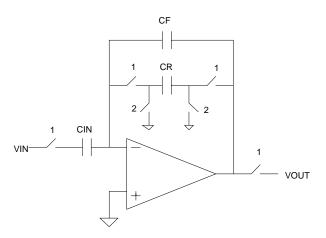

Fig. 3-1: Conventional SC lossless integrator

When the output of the integrator is taken in phase 1, the z-domain transfer function is given by

$$\frac{V_{OUT}(z)}{V_{IN}(z)} = -\frac{C_{IN}}{C_F} \frac{1}{1 - z^{-1}}.$$

(3.1)

The relationship between the time constant and clock frequency for such an integrator can be approximately given by equation (3.2).

$$\tau = \frac{C_f}{f_{CLK}C_{in}}.$$

(3.2)

If large time constants are desired, two options are available, decreasing the clock frequency or increasing the  $C_F/C_{IN}$  ratio. Decreasing the clock frequency is not really an option because we want to realize a wideband band pass function with a low pass corner at 200Hz. To prevent pre-warping errors, the clock frequency should be at least one order of magnitude larger than the low pass corner. Thus, the clock frequency is limited by the low pass corner we want to achieve. This leaves us with the option of increasing the  $C_F/C_{IN}$  ratio. The required capacitor spread can easily run into a several hundreds or even a few thousands in practice. For instance, a 1Hz high pass corner working from a 2.5 KHz clock would require a capacitor spread of around 400.

Several approaches have been investigated for realizing very large time constants in an area efficient manner. Most of these approaches achieve the required capacitor ratio as a product of two smaller capacitor ratios. For instance, if a capacitor spread of 400 can be realized as a product of two capacitor ratios of 20 each. Thus the total area has been reduced by a factor of 10 in the above case. In subsequent sections, we will discuss the various techniques by which this is achieved. For each of the techniques, we will demonstrate capacitor spread, capacitor area, the effects of op-amp DC gain and GBW, the sensitivity to capacitor mismatch, sensitivity to op-amp mismatches (differential mode offsets). We will do this for the extremes of the corner frequency, viz. 4Hz and 0.159 Hz.

#### 3.2 Fleischer-Laker (FL) Biquad

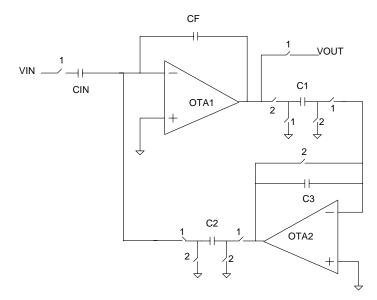

The Fleischer-Laker biquad [8] is a wideband low-Q biquad. It consists of a two integrator loop, one lossy and one lossless. The switched-capacitor implementation is shown in Fig. 3-2 below.

Fig. 3-2: Conventional Fleischer-Laker biquad for low Q applications

The output of OTA 1 is a low pass function and the output of OTA 2 is the required wideband band pass function. The z-domain transfer function is given by

$$\frac{V_{OUT}(z)}{V_{IN}(z)} = -\frac{C_1}{C_{F2}} \frac{1 - z^{-1}}{(1 - z^{-1})^2 + \frac{C_4}{C_{F2}}(1 - z^{-1}) + \frac{C_2C_3}{C_{F1}C_{F2}}z^{-1}}.$$

(3.3)

To analyze approximately for the corners, the z-domain representation must be converted to an s-domain representation. This is not necessary, but since we are more used to dealing in the continuous-time, it is more convenient. The universal transformation is given by

$$z^{-1} \leftrightarrow e^{-sT_{clk}} \,. \tag{3.4}$$

$T_{CLK}$  is the sampling clock frequency. This is a nonlinear transformation and can lead to cumbersome expressions sometimes. If the clock frequency is sufficiently higher than the operating frequency of the SC filter, then a bi-linear transformation can be used. The transformation can be approximated by

$$z^{-1} = \frac{1 - 0.5sT_{CLK}}{1 + 0.5sT_{CLK}}$$

$$z^{-1/2} = \frac{\sqrt{1 - s^2 T_{CLK}^2}}{1 + 0.5sT_{CLK}} \approx \frac{1}{1 + 0.5sT_{CLK}}.$$

(3.5)

A few more approximations are in order to derive a less cluttered expression and develop insight.

$$\frac{C_2 C_3}{C_{F1} C_{F2}} << \frac{C_4}{C_{F2}}.$$

(3.6)

This transformation will give us an accurate result for the high pass corner, which is low frequency, but it will give some error for the low pass corner (a large value). Using the above transformation, we obtain

$$\frac{V_{OUT}(s)}{V_{IN}(s)} = -\frac{C_1}{C_{F2}} \frac{sT_{CLK}(1+0.5sT_{CLK})}{s^2 T_{CLK}^2 (1+\frac{C_4}{2C_{F2}}) + s\frac{C_4}{C_{F2}} T_{CLK} + \frac{C_2 C_3}{C_{F1} C_{F2}} (1+0.5sT_{CLK})}.$$

(3.7)

For obtaining the high pass corner, which is at low frequency, we can make one further approximation, i.e.  $1 + 0.5sT_{CLK} \approx 1$ . This will give us

$$\frac{V_{out}(s)}{V_{in}(s)} = -\frac{s\frac{2C_1}{2C_{F2} + C_4}f_{clk}}{s^2 + s\frac{2C_4}{C_4 + 2C_{F2}}f_{clk} + \frac{2C_2C_3}{C_{F1}(C_4 + 2C_{F2})}f_{clk}^2}.$$

(3.8)

In the above transfer function, the roots of the denominator (or the poles of the transfer function) will give us the approximate high pass and low pass corners. The corners can be derived as

$$\rho_{HPF} = f_{clk} \frac{C_2 C_3}{C_4 C_{F1}} \Rightarrow \tau_{HPF} = \frac{C_4 C_{F1}}{C_2 C_3 f_{clk}}

\rho_{LPF} = f_{clk} \frac{2C_4}{(C_4 + 2C_{F2})} \Rightarrow \tau_{LPF} = \frac{2C_{F2} + C_4}{2f_{clk} C_4}

G(passband) = \frac{C_1}{C_4}.$$

(3.9)

The derived high pass corner is much more accurate than the derived low pass corner. For greater accuracy in deriving the low pass corner, we need to pre warp the low pass corner. We can thus obtain the more accurate low pass corner as in [8]

$$\rho_{LPF} = \frac{f_{clk} \frac{2C_4}{2C_{F2} + C_4} Sin\left(\frac{2C_4}{2C_{F2} + C_4}\right)}{\frac{2C_4}{2C_{F2} + C_4}} = f_{clk} Sin\left(\frac{2C_4}{2C_{F2} + C_4}\right).$$

(3.10)

Thus, the problem of realizing the large time constant has been solved by now involving four capacitors rather than just two in conventional switched-capacitor structures. From the above equations a few facts are clear:

- 1.  $C_4 < C_{F2}$  because the clock is one order higher than the low pass corner

- 2.  $C_4$  and  $C_{F1}$  are much larger than  $C_2$ ,  $C_3$  for large time constants

3.  $C_1$  is as large as  $C_4$  if a gain of 1 is desired and larger for larger gains

#### 3.2.1 Capacitors, matching and sensitivity

$C_4$ ,  $C_2$ ,  $C_1$  and  $C_{F2}$  must be mutually matched, as must  $C_3$  and  $C_{F1}$ . Since  $C_2$  and  $C_3$  are the only small capacitors in their respective cluster, both can be unit capacitors for common centroid matching to be possible. The capacitor values are given in Table 3-1. The low pass corner is always fixed at 200Hz. The values have been optimized for spread. They can also be optimized for GBW as will become clear in the discussion in section 3.2.3.

$C_1$  $C_2$  $f_{HPF}$  $C_3$  $C_4$  $C_{F1}$  $C_{F2}$ 0.159 Hz 36 1 1 36 70 70 4 Hz 8 1 1 8 14 14

Table 3-1: Capacitor values for FL biquad of Fig. 3-2

The capacitor spreads depend on both the high pass and the low pass corner. While having a small high pass corner causes a large capacitor spread, the presence of a low pass corner pushes the spreads to even higher values. This is one disadvantage of this biquad. The sensitivities with respect to all capacitor mismatches have a magnitude of 1. As an example for calculation, let us calculate the sensitivity of the high pass corner with respect of  $C_{F1}$ .

$$S_{C_{F1}}^{\rho_{HPF}} = \left(\frac{\partial \rho_{HPF}}{\partial C_{F1}}\right) \div \frac{\rho_{HPF}}{C_{F1}} = -1.$$

(3.11)

Similarly it can be shown that the sensitivity with respect to  $C_2$  and  $C_3$  is 1 while the sensitivity of the high pass corner with respect to  $C_4$  is -1. Thus the absolute value of sensitivity with respect to all capacitors is 1. The absolute sensitivity is given by

$$S = \left| S_{C_{F1!}}^{\rho_{HPF}} \right| + \left| S_{C2}^{\rho_{hpf}} \right| + \left| S_{C3}^{\rho_{HPF}} \right| + \left| S_{C4}^{\rho_{HPF}} \right| = 4.$$

(3.12)

### 3.2.2 Effects of finite DC gain

The ideal transfer function in a Fleischer-Laker biquad has a zero at the origin and two left half poles in the s-plane for a continuous time implementation. For a discrete time implementation, the zero ideally lies on the unit circle and the poles lie within the unit circle of the z-plane. This is true if the op-amps are ideal. However, if the op-amp is not ideal, then the transfer function contains a zero inside the unit circle (analogous to a left half zero). This causes not only a phase error, but also an error in the 3-dB high pass corner. The main reason for this zero is that a lossless integrator if implemented by a non-ideal op-amp is actually lossy. The larger the gain of the op-amp, the smaller the loss. The transfer function considering finite DC gain is given by

$$H(z) = -\frac{C_1}{C_{F2}(1+A_2^{-1})} + \frac{1-z^{-1} + \frac{C_3}{(1+A_1)C_{F1}}}{(1-z^{-1})^2 + G_1(1-z^{-1}) + G_2 z^{-1/2}}$$

$$G_1 = \frac{C_4}{C_{F2}} + \frac{C_1}{C_{F2}(A_2+1)} + \frac{C_3}{C_{F1}(A_1+1)}$$

$$G_2 = \frac{C_2 C_3}{C_{F1}C_{F2}(1+A_1^{-1})(1+A_2^{-1})}.$$

(3.13)

The frequency of the zero is given by

$$\rho_Z = \frac{f_{clk}C_3}{A_1 C_{F1}}.$$

(3.14)

For small DC gains, this zero can be uncomfortably close to the required high pass corner. For instance, in the biquad above, if OTA 1 has a DC gain of 40 dB (normal for a current mirror OTA), then the zero frequency is only three times lower than the frequency of the required pole. By increasing the spread, the zero can be pushed to lower frequencies, but the spreads are already too high. Thus, OTA 1 must have a large DC gain. A typical folded-cascode (gain = 74 dB) can push the zero to reasonably lower frequencies, so that it does not affect the response too much.

Another error is due to the apparent change in the values of  $C_{F1}$ ,  $C_{F2}$  and  $C_4$ . This change is entirely due to the DC gain. The apparent values become

$$C_{F1} \to C_{F1}(1 + A_1^{-1})$$

$$C_{F2} \to C_{F2}(1 + A_2^{-1})$$

$$C_4 \to C_4(1 + A_2^{-1}).$$

(3.15)

These errors are quite obvious from inspection. These errors are quite small however. The point that we are trying to make here is that one has to use large DC gain to realize the required transfer function with a reasonable accuracy. These conclusions can be verified via simulations.

#### 3.2.3 Op-amp GBW

OTA 1 is effectively loaded by capacitor  $C_3$  during phase 1 and  $C_2$  during phase 2. Both of these are small capacitors and hence OTA 1 has minimal GBW requirements. OTA 2 however is loaded by a parallel combination of  $C_1$ ,  $C_2$  and  $C_3$  during phase 2. The loading diagrams for OTA 2 are shown below in Fig. 3-3a and Fig. 3-3b.

Fig. 3-3a: Loading configuration for OTA 2 of Fig. 3-2 during phase 2

Fig. 3-3b: Circuit of Fig. 3-3a with feedback loop opened

The loop GBW is given by

$$loop\_GBW = \frac{g_m}{C_1 + C_2 + (C_L + C_3) \left(1 + \frac{C_1 + C_2}{C_{F2} + C_4}\right)}.$$

(3.16)

$C_1$  is a big capacitor and loads the OTA, impacting settling time. Thus, as the time constants increase and push up the spread,  $C_1$  increases and thus OTA 2 requires greater power consumption ( $g_m$ ) for proper settling.

#### 3.2.4 Op-amp offsets

One advantage of the Fleischer-Laker biquad is that it is robust with respect to op-amp offsets. This is why, in single ended implementations of large time constants, the FL biquad is preferred over other methods. For differential ended structures, this advantage vanishes because of the very nature of differential ended circuitry. In differential ended circuits, the biasing offsets (systematic offsets) appear as a common mode voltage, which is eliminated by the common mode feedback circuitry. Mismatch offsets (random offsets) can be eliminated by chopper stabilization. The output offset of the FL biquad is approximately equal to (but of opposite sign) the input referred offset of the OTA 1. This can be intuitively seen by understanding that in steady state, no charge flows through either integrating capacitor  $C_{F1}$  or  $C_{F2}$ . Thus,

$$V_{out,off} = -V_{in,off,OTA1}.$$

(3.17)

#### **3.3** The T-Cell Method [4]

To understand the T-Cell method, consider the discrete time integrator in Fig. 3-4. To achieve a large time constant  $C_{IN}$  needs to be as small as possible and  $C_F$  should be as large as possible. Conceptually, this can be achieved by placing an attenuator between the input and  $C_{IN}$  and/or an amplifier between the output and  $C_F$ . The conceptual schematic is shown below in Fig. 3-4.

Fig. 3-4: Conceptual implementation of large integrator time constants

Thus the input signal is reduced by an attenuating factor (>1) and the feedback signal is increased by the amplification factor (>1). Thus, the time constant of the integrator increases by the product of the attenuation and amplification factors. The effect is equivalent to reducing the input capacitor,  $C_{in}$  (increasing the resistor) and increasing the feedback capacitor  $C_F$  (the integrating capacitor). Amplification can be implemented only by adding an extra OTA. This increases power consumption. Attenuation does not need active elements. Passive voltage division can implement it. This is the theory behind the T-Cell implementation. The T-Cell method implements a small input capacitor by means of capacitive (switched capacitive) voltage division. The switched-capacitor implementation of the T-Cell integrator is shown in Fig. 3-5.

Fig. 3-5: Large TC integrator using the T-Cell technique

$C_1$  and  $C_2$  make sure that only a small fraction of the input charge is actually integrated by passage through  $C_F$ . The z-domain transfer function, when the output is sampled in phase 1 is given by

$$\frac{V_o(z)}{V_{in}(z)} = -\frac{C_1}{C_1 + C_2 + C_{IN}} \frac{C_{IN}}{C_F} \frac{1}{1 - z^{-1}}.$$

(3.18)

To implement a lossy integrator using the T-Cell, one will have to use it in the Fleischer-Laker biquad. This structure is not parasitic-insensitive. When using poly

capacitors, the bottom plate parasitic capacitor could be as large as 20% of the main capacitor. Metal-Metal capacitors have smaller parasitic effects, but they occupy a huge amount of chip area compared to poly capacitors. Therefore, we will not be using this structure or discussing it further.

### **3.4** The Split-Integrating Capacitor Technique [3]

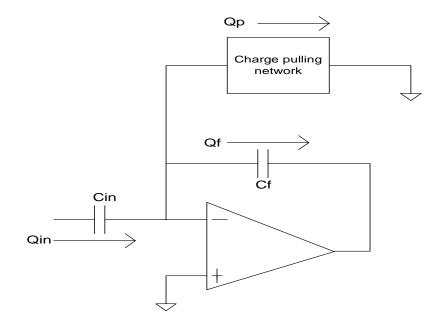

Consider the lossless integrator again. The T-Cell technique was concerned with making the input capacitor look small. The split-integrator technique uses the same principle, but the implementation is parasitic-insensitive. The way it does this is by throwing away a big fraction of the input charge and only passing a small fraction of it through the feedback integrating capacitor. The conceptual diagram is shown in Fig. 3-6.

Fig. 3-6: Conceptual diagram of the split-integrating capacitor technique

In the conventional integrator, the whole of the input charge passes through the integrating feedback capacitor. In the split-integrating technique, a considerable fraction of the input charge is sucked in by the charge pulling network and only a small fraction of the input charge passes through the integrating feedback capacitor. This operation makes the feedback capacitor look much larger than it actually is or conversely, we can say that it makes the input capacitor look small.

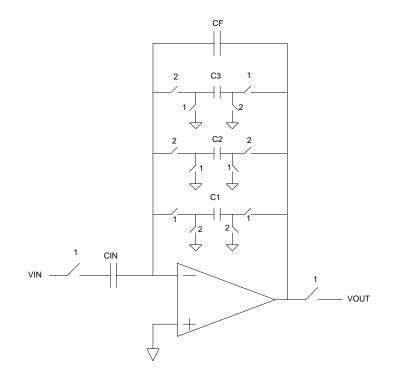

Fig. 3-7 demonstrates the discrete time implementation of the technique. The feedback capacitor  $C_F$  is split into three capacitors,  $C_{F1}$ ,  $C_{F2}$  and  $C_{F3}$ . The circuit exploits an extra op-amp phase. In the conventional integrator, the integration and sampling are performed only in phase 1. In phase 2, the op-amp is idle and the output is a don't care. In the split-integrator technique, both phases are used. In phase 1, the input charge ( $Q_{in} = C_{in}V_{in}$ ) is divided between  $C_{F1}$  and  $C_{F2}$ . In phase 2, the bigger capacitor,  $C_{F1}$  discharges to ground, and a significant portion of the input charge is lost. The smaller capacitor,  $C_{F2}$ , which holds only a small portion of the input charge, discharges through the integrating capacitor. Thus only a small portion of the input charge is integrated, making the integrating capacitor look really very big.

Fig. 3-7: SC implementation of the concept shown in Fig. 3-6

The z-domain transfer function can be written as

$$\frac{V_{out}(z)}{V_{in}(z)} = -\frac{C_{F2}}{C_{F3}} \frac{C_{IN}}{C_{F2} + C_{CF1}} \frac{z^{-1/2}}{1 - z^{-1}}.$$

(3.19)

The relationship between the time constant and the clock frequency is given by

$$\tau = \frac{C_{F3}}{C_{IN}} \frac{C_{F2} + C_{F1}}{C_{F2}} \frac{1}{f_{clk}}.$$

(3.20)

Thus for a large time constant,  $C_{F3}$  and  $C_{F1}$  must be large while  $C_{IN}$  and  $C_{F2}$  must be small. Also  $C_{IN}$ ,  $C_{F2}$ ,  $C_{F1}$ ,  $C_{F3}$  must all be mutually matched.

Now, we must, at this point, begin to wonder whether a lossy integrator can be synthesized using this technique. It may be impossible to do this using only one op-amp. To implement a lossy integrator, let us go back to the conceptual diagram as given below.

Fig. 3-8: Conceptual implementation of large TC LPF

The technique makes the input capacitor  $C_{IN}$  look small (using the attenuator). To maintain gain and also a large time constant, it must also make  $C_R$  look small. To do this, it must attenuate the output  $V_{OUT}(n)$ . Both clock phases are already utilized (one is utilized in attenuating the input signal and the other in the integration). So we would need an extra clock to make  $C_R$  look small. Thus, we cannot implement a lossy integrator, using just this one op-amp and only two clock phases. To implement a lossy integrator using this technique and only two clock phases, we will need to use this integrator in an FL biquad. The discrete-time implementation is shown in Fig. 3-9. The loop implements a high pass function. Technically, we don't need  $C_{F2}$ . I have just included it for completeness. We can allow the value of  $C_{F2}$  to be any value of our choosing, i.e. any arbitrarily small value.

Fig. 3-9: A large time constant integrator in the FL biquad

The transfer function is given by

$$H(z) = -\frac{C_{IN}}{C_{F2}} \frac{1 - z^{-1}}{\left(1 - z^{-1}\right)^2 + \left(1 - z^{-1}\right)\frac{C_2}{C_{F2}} + \frac{C_1 C_3 C_5}{C_{F1} C_{F2} (C_3 + C_4)} z^{-1}}.$$

(3.21)

The high pass corner is then given by

$$\rho_{HPF} = f_{clk} \frac{C_1 C_3 C_5}{C_{F1} C_2 (C_3 + C_4)}.$$

(3.22)

If  $C_1=C_3=C_5 = C$ , and  $C_{F1} = C_2 = C\beta$ , and  $C_4 = (\beta-1) C$ , then the corner is given by equation (3.23).

$$\rho_{HPF} = \frac{f_{clk}}{\beta^3}.$$

(3.23)

#### 3.4.2 Capacitors, matching and sensitivity

$C_5$ ,  $C_3$ ,  $C_4$ ,  $C_{F1}$  form one cluster.  $C_1$ ,  $C_{in}$ ,  $C_{f2}$  and  $C_2$  form another cluster. The various capacitor sizes are given in Table 3-2.

| Corner | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>5</sub> | C <sub>IN</sub> | C <sub>F1</sub> | C <sub>F2</sub> |

|--------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|

| 4 Hz   | 1              | 4              | 2              | 8              | 2              | 4               | 5               | DNM             |

| 0.159  | 1              | 14             | 2              | 26             | 2              | 14              | 26              | DNM             |

Table 3-2: Capacitor values for Fig. 3-9, DNM stands for does not matter

The magnitude of sensitivity of the high pass corner with respect to all capacitor ratios is 1. Sensitivity is defined the same way as in section 3.2.1. However, the structure is more sensitive that first order sections or even the conventional FL biquad, because there are more ratios (3 rather than 2) involved in determining the time constant. The value of total sensitivity (as defined in B1) is 6.

### 3.4.3 Op-amp DC gain

If the finite DC gain of the op-amp is considered, the transfer function is given by equation 3.24 below.

$$H(z) = -\frac{C_{IN}}{C_{F2}} \frac{1 - z^{-1} + \frac{C_3}{C_{F1}(A_1 + 1)}}{\left(1 - z^{-1}\right)^2 + \left(1 - z^{-1}\right)\left(\frac{C_3}{C_{F1}(A_1 + 1)} + \frac{C_2}{C_{F2}} + \frac{C_{IN}}{A_2C_{F2}}\right) + Gz^{-1}}$$

(3.24)

$$G = \frac{C_1C_3C_5}{C_{F1}C_{F2}(C_3 + C_4)}.$$

Just like in the conventional FL biquad, the finite DC gain of OTA moves a zero within the unit circle. The frequency of this zero is given by

$$\rho_z = \frac{C_3}{C_{F1}(A+1)}.$$

(3.25)

For small gains of OTA 1, the zero is too close to the high pass corner.

### 3.4.4 Op-amp GBW

OTA 1 is loaded by the parallel combination of  $C_5$  and  $C_1$  while OTA 2 is loaded by the parallel combination of  $C_{in}$ ,  $C_1$  and  $C_3$ . All of these are small capacitors and hence there will not be much of a problem with respect to settling even for minimum power consumption.

#### 3.4.5 Op-amp offsets

The output offset of this biquad can be shown to be equal in magnitude to the input referred offset of OTA 1. So offsets are not a problem in this biquad.

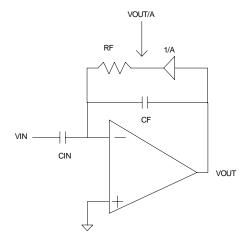

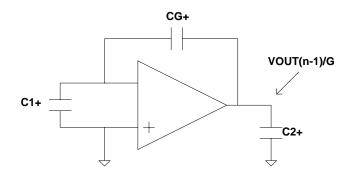

### **3.5** The Nagaraj Technique [5]

The Nagaraj technique is by far the most area efficient method of implementing large time constants yet. A circuit schematic of the Nagaraj integrator is shown in Fig. 3-10.

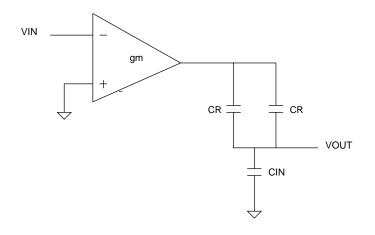

Fig. 3-10: The Nagaraj integrator

In each of the schemes discussed earlier, the basic trick has been the same. The charge passing through the integrating capacitor must be limited to as small a fraction of the input charge as possible. The Nagaraj technique is no different in this respect. However, in the techniques discussed above, attenuation and integration were performed by different capacitors. In the Nagaraj technique, the same capacitor is used to perform the integration as well as the attenuation function resulting an almost 50% saving in total capacitance. In the above circuit schematic, capacitor  $C_2$  is used for attenuation as well as for integration. This is illustrated by Fig. 3-11.

The circuit on the left illustrates the charge transfer in phase 1 while that on the right illustrates the charge transfer in phase 2. In phase 1, the entire input charge ( $Q_{IN} = Q_F$ ) flows through  $C_F$ , which is the big integrating capacitor. In phase 2, almost the entire

Fig. 3-11: Illustrating the integrating principle in the Nagaraj integrator

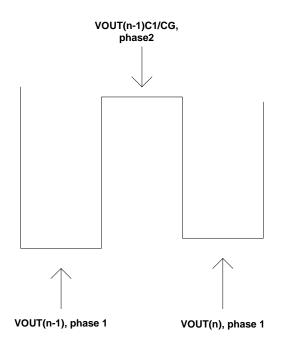

input charge  $(Q_{IN}-Q_R)$  flows through the integrating capacitor, but in the reverse direction. Thus, in effect, only a small portion of the input charge  $(Q_R)$  is integrated by the large capacitor  $C_F$ . Voltage waveforms are shown in Fig. 3-12.

During phase 1, the output voltage takes a step of a certain size in the negative direction. This is when the input charge flows through  $C_F$ . During phase 2, when a large fraction of the input charge is returned by  $C_F$ , the voltage waveform takes a step in the positive direction. The step in the positive direction is a little less than the one in the negative direction.

Fig. 3-12: Illustrating the voltage waveforms in the Nagaraj integrator

The z-domain transfer function of the integrator is

$$H(z) = -\frac{1}{1 + \frac{C_2}{C_F}} \frac{C_2}{C_F} \frac{C_{IN}}{C_F} \frac{z^{-1/2}}{1 - z^{-1}}.$$

(3.25)

The time constant of the integrator is given by

$$\tau = \left[1 + \frac{C_2}{C_F}\right] \frac{C_F}{C_{IN}} \frac{C_F}{C_2} \frac{1}{f_{clk}}.$$

(3.26)

Thus  $C_F$  is a large capacitor and  $C_{IN}$ ,  $C_2$  are small capacitors. Rather large time constants can be implemented with reasonable capacitor ratios.

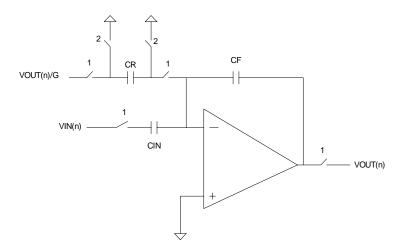

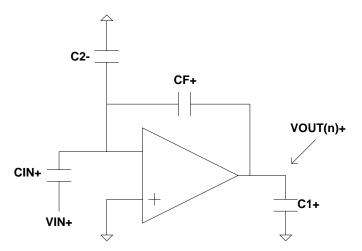

The idea above can be extended to realize lossy integrators as shown in Fig. 3-13. The transfer function of the integrator can be shown to be

$$H(z) = -\frac{1}{\left(1 + \frac{C_2}{C_F}\right)\left(1 + \frac{C_1}{C_F}\right)} \frac{C_{IN}}{C_F} \frac{C_2}{C_F} \left[\frac{z^{-1/2}}{1 - z^{-1}} + \frac{1}{\left(1 + \frac{C_1}{C_F}\right)\left(1 + \frac{C_2}{C_F}\right)} \frac{C_1 C_2}{C_F^2} z^{-1}}\right].$$

(3.27)

The DC gain of this lossy integrator (LPF) is equal to  $C_{IN}/C_1$ .

Fig. 3-13: The Nagaraj low pass filter

The corner frequency is given by

$$\rho = \frac{C_1 C_2}{C_F^2} f_{clk} \frac{1}{\left(1 + \frac{C_1}{C_F}\right) \left(1 + \frac{C_2}{C_F}\right)}.$$

(3.28)

Large time constants are obtained by keeping  $C_F$  large and  $C_1$ ,  $C_2$ ,  $C_{IN}$  small. Let us now analyze the Nagaraj low pass filter for various parameters.

### 3.5.2 Capacitors, matching and sensitivity

Capacitors  $C_1$ ,  $C_2$ ,  $C_{in}$  and  $C_F$  belong to the same cluster and hence must be mutually matched. Since  $C_{1,2,in}$  are all small capacitors, all three of them cannot be mutually matched and be unit capacitors at the same time. Here, we come across a tradeoff between capacitor spread and capacitor area. Given in Table 3-3 is the list of capacitor values optimizing spread. Table 3-4 optimizes area.

Table 3-3: Capacitor values for Fig. 3-13 optimizing spread

| Corner | C <sub>IN</sub> | C <sub>1</sub> | C <sub>2</sub> | C <sub>F</sub> |

|--------|-----------------|----------------|----------------|----------------|

| 0.159  | 2               | 2              | 2              | 98             |

| 4      | 2               | 2              | 2              | 18             |

| Corner | C <sub>IN</sub> | C <sub>1</sub> | C <sub>2</sub> | C <sub>F</sub> |

|--------|-----------------|----------------|----------------|----------------|

| 0.159  | 2               | 2              | 1              | 70             |

| 4      | 2               | 2              | 1              | 13             |

Table 3-4: Capacitor values for Fig. 3-13 optimizing area

The sensitivities are given by

$$S_{C_F}^{\rho_{HPF}} = -2$$

$$S_{C1}^{\rho_{HPF}} = 1$$

$$S_{C2}^{\rho_{HPF}} = 1$$

$$S = 4.$$

$$(3.29)$$

The Nagaraj structure is about as sensitive as the conventional Fleischer-Laker biquad.

# 3.5.3 Op-amp DC gain

If op-amp DC gain is taken into account, the transfer function for the low-pass filter can be derived to equal the expression in equation (3.30).

$$H(z) = -\frac{C_2 C_{IN}}{C_F^2} \frac{1}{\left(1 + \frac{C_2}{C_F}\right) \left(1 + \frac{C_1}{C_F}\right)} \left( \frac{1}{\left(1 - \left(\frac{C_1 C_2}{C_F^2} \frac{1}{\left(1 + \frac{C_2}{C_F}\right) \left(1 + \frac{C_1}{C_F}\right)} + \frac{C_1}{A C_F}\right)}\right) - z^{-1}}\right).$$

(3.30)

The new corner frequency is given by

$$\rho = f_{clk} \left( \frac{C_1 C_2}{C_F^2} \frac{1}{\left(1 + \frac{C_1}{C_F}\right) \left(1 + \frac{C_2}{C_F}\right)} + \frac{C_1}{A C_F} \right).$$

(3.31)

The error in the time constant is thus given by

$$\varepsilon = \frac{C_1}{C_1 C_2} \frac{C_F}{A}.$$

(3.32)

If  $C_{IN} = C_1 = C_2 = C$  and  $C_F = \beta C$ , then the error is given by

$$\varepsilon = \frac{\beta}{A}.$$

(3.33)

Thus for a time constant of 1s (cutoff of 0.159 Hz) and a clock of 2.5 KHz, the Spread required is 50 and the DC gain required for 1% error would be 5000 or 74dB.

#### 3.5.4 Op-amp GBW

There is not much stress on the GBW of the OTA because the AC loading capacitor in both phases is  $C_{IN}$ , which is a small capacitor. The GBW requirement can be met easily by the minimum power OTA (40nA).

#### 3.5.5 Op-amp offsets

The effects of the op-amp offsets can be derived in straightforward manner. The way to do this, is to set the input to zero, assume infinite DC gain and assign an input referred offset of  $V_{IN,off,OTA}$  to the OTA. The output offset can be derived to be

$$V_{out,off} = 2\beta V_{in,off,OTA}.$$

(3.34)

Since we are using fully differential configurations, we do not worry about biasing offsets. Mismatch offsets can be removed by chopper stabilization [10].

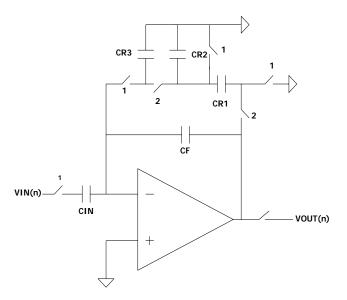

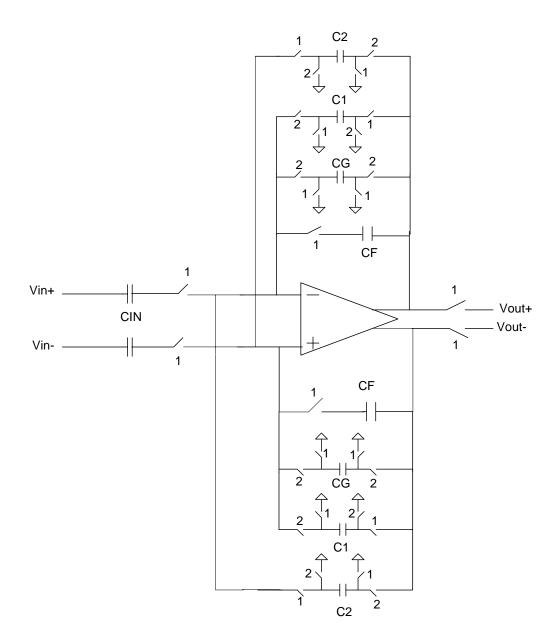

#### **3.6.** Combining the FL Biquad with the Nagaraj Integrator

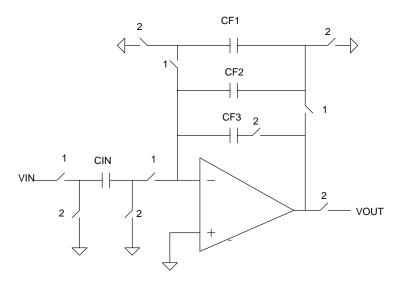

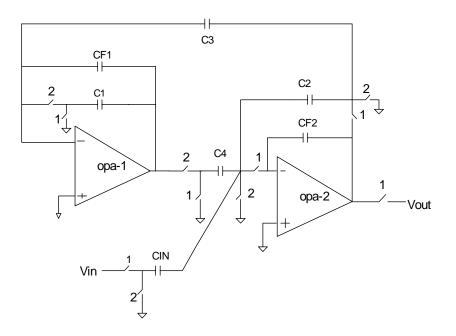

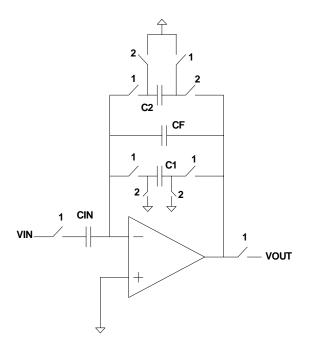

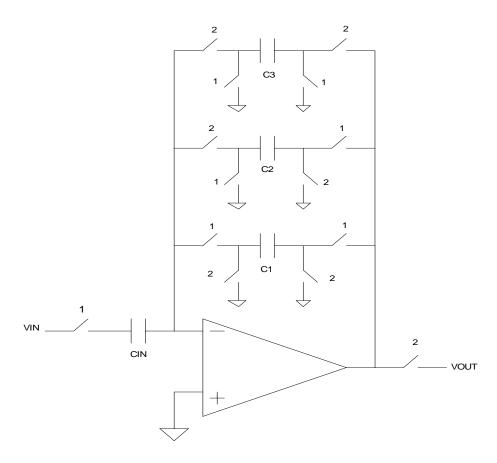

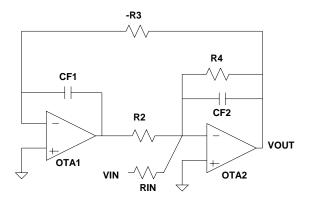

We might recall that the FL biquad contained a two integrator loop of which one integrator was lossy and the other, lossless. Two of the problems, viz. large capacitor spread and area, and loading effect can be greatly alleviated, by replacing the conventional integrator with the Nagaraj integrator. Doing so reduces the area as well as the spread as compared with the first order Nagaraj lossy integrator. The switched-capacitor implementation of the improved FL biquad is shown in Fig. 3-14.

Fig. 3-14: FL biquad using the Nagaraj integrator

Opa-1 implements the lossless Nagaraj integrator while opa-2 implements the conventional lossy integrator. Recall that in the conventional FL biquad,  $C_{IN}$ ,  $C_{f2}$  and  $C_2$  would be large capacitors increasing the area as well as the loading on opa-2. In this improved biquad, the sizes of  $C_{IN}$ ,  $C_2$  and  $C_{f2}$  can be drastically reduced because the large time constant is chiefly being realized by the capacitors  $C_1$ ,  $C_3$  and  $C_{f1}$ . This is well illustrated by the transfer function that is written below as

$$H(z) = -\frac{C_{IN}}{C_{F2}} \frac{1 - z^{-1}}{(1 - z^{-1})^2 + (1 - z^{-1})\frac{C_2}{C_{F2}}} + \frac{C_1 C_3 C_4}{C_{F1}^2 C_{F2} \left(1 + \frac{C_1}{C_{F1}}\right)} z^{-1}.$$

(3.35)

The above z-domain transfer function can be converted to s-domain quite trivially as

$$H(s) = -\frac{s\left(\frac{f_{clk}C_{in}}{C_{F2}}\right)}{s^{2} + s\frac{f_{clk}C_{2}}{C_{F2}} + \frac{f_{clk}^{2}C_{1}C_{3}C_{4}}{C_{F2}C_{F1}^{2}\left(1 + \frac{C_{1}}{C_{F}}\right)}}.$$

(3.36)

The roots of the denominator will give us the respective corner. Our concern is with the high pass corner. The high pass corner is given by

$$\rho_{HPF} = f_{clk} \frac{C_1 C_3 C_4}{C_2 C_{F1}^2 \left(1 + \frac{C_1}{C_{F1}}\right)}.$$

(3.37)

And the corresponding time constant is given by

$$\tau = \frac{C_2 C_{F1}^2}{C_1 C_3 C_4} \left( 1 + \frac{C_1}{C_{F1}} \right). \tag{3.38}$$

Thus the time constant here is a ratio of three transistors. Thus the loading effect on OTA 2 can be reduced in comparison with the conventional Fleischer-Laker structure. Further, lower spreads can be achieved because now three ratios are involved. The low pass corner is given by

$$\rho_{LPF} = f_{clk} \frac{C_2}{C_{F2}}.$$

(3.39)

Both C<sub>2</sub> and C<sub>F2</sub> can be small capacitors.

### 3.6.2 Capacitors, matching and sensitivity

If we optimize for spread, Table 3-5 gives the values of the capacitors in numbers of unit capacitors.

| Corner  | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>IN</sub> | $C_{F1}$ | C <sub>F2</sub> |

|---------|----------------|----------------|----------------|----------------|-----------------|----------|-----------------|

| .159 Hz | 2              | 12             | 2              | 1              | 12              | 28       | 18              |

| 4 Hz    | 2              | 4              | 2              | 1              | 4               | 10       | 6               |

Table 3-5: Capacitor values for Fig. 3-14 optimizing spread

Thus, this structure does a better job of reducing spread and area than the Nagaraj integrators. However, for large time constants, OTA 2 might be loaded by  $C_{IN}$ . Thus, we can optimize loading for 0.159 Hz using the values of capacitors as given in Table 3-6.

Table 3-6: Capacitor values for Fig. 3-14 optimizing loading on opa-2

| Corner   | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> | C <sub>IN</sub> | $C_{F1}$ | C <sub>F2</sub> |

|----------|----------------|----------------|----------------|----------------|-----------------|----------|-----------------|

| 0.159 Hz | 2              | 2              | 2              | 2              | 2               | 100      | 3               |

Note that if we eliminate  $C_{f2}$ , we get a one-integrator loop with two OTAs. The structure will be a pure high pass. This is not a problem if a stand-alone high pass is required or if the succeeding stage is available to implement a low pass. Thus, we may be able to reduce the area by eliminating  $C_{F2}$ . If we eliminate  $C_{F2}$ , the low pass corner is not defined. It is set by the OTA bandwidth. However, to define the low pass corner, we can have another low pass block following this stage.

The FL biquad using the Nagaraj integrator is more sensitive to capacitor mismatch than the other structures because of the number of capacitor ratios (3) involved in implementing the time constant. The sensitivities are given by

$$S_{C1}^{HPF} = S_{C3}^{HPF} = S_{C4}^{HPF} = -1$$

$$S_{C2}^{HPF} = 1$$

$$S_{CF1}^{HPF} = 2$$

$$S = 6.$$

(3.40)

#### 3.6.3 Op-amp DC gain

If the finite DC gain of the OTA is considered, then again we end up with a zero in the unit circle just as was the case with the conventional Fleisher-Laker biquad. The transfer function is given by

$$H(z) = -\frac{C_{IN}}{C_{F2}(1+A_2^{-1})} \frac{1-z^{-1}+\frac{C_1}{A_1C_{F1}}}{\left(1-z^{-1}\right)^2 + \left(1-z^{-1}\right)\left(\frac{C_2}{C_{F2}}+\frac{C_1}{A_1C_{F1}}\right) + z^{-1}\frac{C_1C_3C_4}{C_{F1}^2C_{F2}\left(1+\frac{C_1}{C_{F1}}\right)}.$$

(3.41)

Thus the frequency of the zero is given by

$$\rho_Z = \frac{f_{clk}C_1}{A_1 C_{F1}}.$$

(3.42)

Thus, the DC gain of OTA 1 must be large. Otherwise the zero will be too close to the pole. This is exactly the same as for the conventional Fleischer-Laker biquad.

#### 3.6.4 Op-amp GBW

The settling time of OTA 2 is dictated by its  $g_m$  and the parallel combination of  $C_4$ ,  $C_{in}$  and  $C_3$ . The settling of OTA 1 is dictated by its  $g_m$  and  $C_3$  during phase 1 and by  $C_4$  during phase 2. If the large time constant is dictated mainly by the Nagaraj integrator, then settling of the OTA will not be a problem because the  $g_m$  corresponding to minimum power consumption (10nA per transistor) should be enough for all purposes.

#### 3.6.5 Op-amp offsets

The output voltage in the presence of op-amp offsets is given by

$$V_{OUT,off} = -\left(1 + \frac{C_{F1}}{C_3}\right) V_{in,off,1}.$$

(3.43)

Thus the output offset of the entire biquad is scaled up by the input referred offset of OTA 1, which implements the Nagaraj integrator.

### 3.7 Conclusions

Of the various schemes discussed here, it appears that from the point of view of capacitor area or capacitor spread, the best technique is the one by Nagaraj. All the techniques require identical DC gains and  $g_m$  from the OTA for implementing the same time constant. Thus, it is the Nagaraj technique, which will be compared with the high pass structures that we will present in the next chapter.

### CHAPTER IV

## LARGE TIME CONSTANTS IN SC HIGH PASS FILTERS

This chapter includes the main contributions of this thesis. To the author's knowledge, no work on achieving large time constants in switched-capacitor high pass filters or differentiators has ever been reported in literature. All the structures in this chapter are thus the contributions of this thesis. As was pointed out in the first chapter, the main motivation for focusing on SC HPFs is that they are the most natural way to implement low frequency high pass corners in wideband applications. Another advantage is that they conserve power. A conventional method of implementing a high pass function is by subtracting a low pass function from a unity gain buffer, i.e. HPF = 1 - LPF. Thus, if we could realize a high pass structure as is, we could eliminate the buffer. We begin with a discussion on differentiators and then move on to high-pass filters.

# 4.1 Realizing a Differentiator

A conventional switched-capacitor differentiator is shown in Fig. 4-1.

Fig. 4-1: Conventional SC differentiator

The ideal z-domain transfer function is given by

$$H(z) = -\frac{C_{IN}}{C_F} (1 - z^{-1}).$$

(4.1)

For slowly carrying input signals, large time constants are required. The time constant is given by

$$\tau = T_{CLK} \frac{C_{IN}}{C_F}.$$

(4.2)

$T_{CLK}$  is the clock frequency. For very large time constants,  $C_{IN}$  could occupy a very large on-chip area.

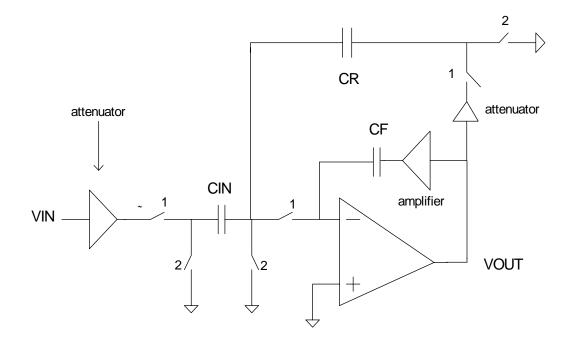

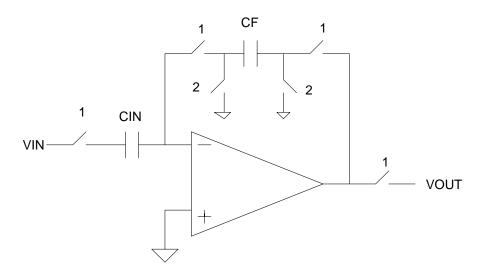

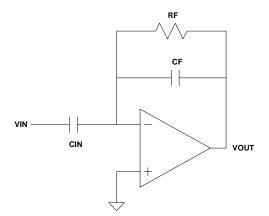

### 4.2 Basic High Pass Filter

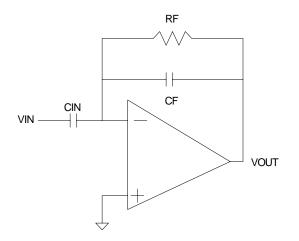

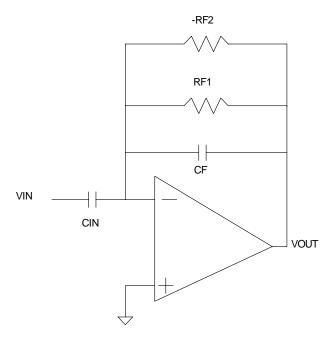

The basic continuous-time HPF is given below in Fig. 4.2.

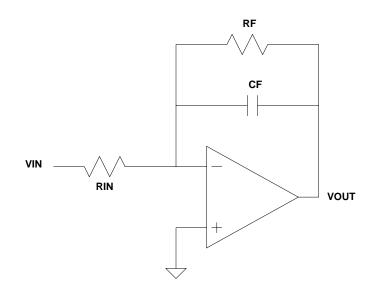

Fig. 4-2: Conventional continuous time high pass filter

To have a large time constant  $C_F$  and  $R_F$  must both be made as large as possible. However, to maintain the passband gain  $C_{IN}$  must also be scaled up along with  $C_F$ . Thus for large time constants all the components must be increased. The discrete-time version of the SC HPF is shown in Fig. 4-3.

Fig. 4-3: Conventional SC high pass filter

The z-domain transfer function is given by

$$H(z) = -\frac{C_{IN}}{C_F} \frac{1 - z^{-1}}{1 - z^{-1}} + \frac{C_R}{C_F}.$$

(4.4)

The time constant is given by

$$\tau = \frac{1}{f_{clk}} \frac{C_F}{C_R}.$$

(4.5)

And the gain is given by  $C_{IN}/C_2$ . Thus, for large time constants  $C_R$  must be made small while  $C_F$  must be made large. To maintain gain,  $C_{IN}$  must also be scaled up with  $C_F$ . However, scaling up  $C_{IN}$  and  $C_F$  requires amplification circuitry, which cannot be implemented using passive components. Besides, scaling up  $C_{IN}$  will place a severe stress on the settling time of the OTA during phase 1, which is the high-pass filtering phase (phase 2 is the reset phase for  $C_R$  and the idle phase for the OTA). This is readily apparent by breaking the OTA feedback loop at the inverting terminal during phase 1 as shown in Fig. 4-4.

Fig. 4-4: Illustrating loading by breaking the feedback loop in Fig. 4-3

The loop gain of the overloaded circuit is given by

$$\frac{V_{out}}{V_{in}} = \frac{g_m}{sC_{IN}}.$$

(4.5)

And the GBW of the loop gain is given by

$$f_{GBW} = \frac{g_m}{2\pi C_{IN}}.$$

(4.6)

Thus we need a larger  $g_m$  as the  $C_{IN}$  increases. And a larger  $g_m$  is obtained only by increasing the power consumption of the OTA.

A second solution to large time constants involves the reduction of  $C_R$ . Thus we will concentrate on techniques to reduce the effective size of  $C_R$ .

### 4.3 Partial Positive Feedback

The basic idea of partial positive feedback is given for a continuous time high pass filter below in Fig. 4-5.

Fig. 4-5: Conceptual partial positive feedback (conductance subtraction)

A positive resistance is placed in parallel with a negative resistance. The positive resistance is slightly less than the negative resistance (positive conductance is slightly greater than the negative conductance). Thus the parallel combination would yield a positive resistance that is quite large (or a positive conductance that is quite small). The switched-capacitor implementation of just such an idea is shown below in Fig. 4-6.

Fig. 4-6: Simple SC implementation of partial positive feedback

The z-domain transfer function is given by

$$\frac{V_{OUT}(z)}{V_{IN}(z)} = -\frac{C_{IN}}{C_F + C_2} \frac{1 - z^{-1}}{1 - z^{-1} + \frac{C_1 - C_2}{C_F + C_2}}.$$

(4.7)

And the time constant being implemented is given by

$$\tau = \frac{1}{f_{clk}} \frac{C_F + C_2}{C_1 - C_2}.$$

(4.8)

Thus, for a large time constant  $C_1$  should be slightly greater than  $C_2$ . However, *as in any scheme involving partial positive feedback, the sensitivity of the time constant increases as the difference between*  $C_1$  *and*  $C_2$  *is lowered.*  $C_1$  and  $C_2$  cannot be made arbitrarily close to each other. The circuit depends on the closeness of  $C_1$  and  $C_2$  and not on the ratio. Thus it is not possible to match  $C_1$  and  $C_2$  to arbitrarily close values using *unit capacitors*.

A more sophisticated structure using partial positive feedback, but allowing the use of unit capacitors for better matching is given below in Fig. 4-7.

Fig. 4-7: A sophisticated SC implementation of partial positive feedback

The z-domain transfer function of this structure is given by

$$H(z) = \frac{C_{IN}}{C_F + C_1} \frac{1 - z^{-1}}{1 - z^{-1} + z^{-1}} \frac{C_1 C_3 + C_F (C_1 + C_3 - C_2)}{(C_F + C_1)(C_F + C_3)}.$$

(4.9)

And the time constant is given by