# BLUETOOTH/WLAN RECEIVER DESIGN METHODOLOGY AND IC IMPLEMENTATIONS

A Dissertation

by

### AHMED AHMED ELADAWY EMIRA

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2003

Major Subject: Electrical Engineering

## **BLUETOOTH/WLAN RECEIVER DESIGN METHODOLOGY AND**

## **IC IMPLEMENTATIONS**

A Dissertation

by

### AHMED AHMED ELADAWY EMIRA

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Approved as to style and content by:

Edgar Sánchez-Sinencio (Chair of Committee)

> Aydin Karsilayan (Member)

Scott Miller (Member)

Duncan Walker (Member) Chanan Singh (Head of Department)

December 2003

Major Subject: Electrical Engineering

José Silva-Martínez (Member)

#### ABSTRACT

Bluetooth/WLAN Receiver Design Methodology and IC Implementations. (December 2003) Ahmed Ahmed Eladawy Emira, B.Eng., Cairo University, Egypt; M.Eng., Cairo University, Egypt Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

Emerging technologies such as Bluetooth and 802.11b (Wi-Fi) have fuelled the growth of the short-range communication industry. Bluetooth, the leading WPAN (wireless personal area network) technology, was designed primarily for cable replacement applications. The first generation Bluetooth products are focused on providing low-cost radio connections among personal electronic devices. In the WLAN (wireless local area network) arena, Wi-Fi appears to be the superior product. Wi-Fi is designed for high speed internet access, with higher radio power and longer distances. Both technologies use the same 2.4GHz ISM band. The differences between Bluetooth and Wi-Fi standard features lead to a natural partitioning of applications. Nowadays, many electronics devices such as laptops and PDAs, support both Bluetooth and Wi-Fi standards to cover a wider range of applications. The cost of supporting both standards, however, is a major concern. Therefore, a dual-mode transceiver is essential to keep the size and cost of such system transceivers at a minimum.

A fully integrated low-IF Bluetooth receiver is designed and implemented in a low cost, main stream 0.35µm CMOS technology. The system includes the RF front end, frequency synthesizer and baseband blocks. It has -82dBm sensitivity and draws 65mA current. This project involved six Ph.D. students and I was in charge of the design of the channel selection complex filter.

In the Bluetooth transmitter, a frequency modulator with fine frequency steps is needed to generate the GFSK signal that has  $\pm 160$ kHz frequency deviation. A low power ROM-less direct digital frequency synthesizer (DDFS) is designed to implement the frequency modulation. The DDFS can be used for any frequency or phase modulation communication systems that require fast frequency switching with fine frequency steps.

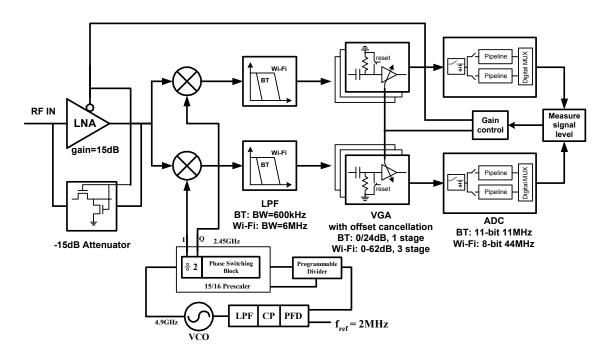

Another contribution is the implementation of a dual-mode 802.11b/Bluetooth receiver in IBM 0.25µm BiCMOS process. Direct-conversion architecture was used for both standards to achieve maximum level of integration and block sharing. I was honored to lead the efforts of seven Ph.D. students in this project. I was responsible for system level design as well as the design of the variable gain amplifier. The receiver chip consumes 45.6/41.3mA and the sensitivity is -86/-91dBm.

# **DEDICATION**

To my Parents, To my Brother, and Sister, And to my fiancée Eman For their love and support

#### ACKNOWLEDGEMENTS

A journey is easier when you travel together. Interdependence is certainly more valuable than independence. This dissertation is the result of four years of work whereby I have been accompanied and supported by many people. It is a pleasant aspect to now have the opportunity to express my gratitude for all of them.

With a deep sense of gratitude, I wish to express my sincere thanks to my supervisor, Dr. Edgar Sánchez-Sinencio, for his immense help in planning and executing the work in a timely manner. The confidence and dynamism with which Dr. Sánchez guided the work requires no elaboration. His company and assurance at the time of crisis will always be remembered. His technical and editorial advice was essential to the completion of this dissertation and taught me innumerable lessons and insights on the workings of academic research in general.

I am also grateful to Dr. Sherif Embabi and his group at Texas Instruments for sharing much of their valuable time to review the design of the Bluetooth and Chameleon receiver projects. Their comments and suggestions were very useful in avoiding potential design problems and improving the performance of the receiver. I would also like to express my gratitude to Dr. José Silva-Martínez and Dr. Aydin Karsilayan who were always there to answer my technical questions throughout my entire Ph.D. program. Thanks also go to my committee members: Dr. Scott Miller and Dr. Duncan Walker for their time and valuable comments on my research.

I am fortunate to have had the opportunity to work with a group of energetic people in the Analog and Mixed Signal Center (AMSC). Special thanks and words of appreciation are due to my friend, research partner, and ex roommate Ahmed Nader Mohieldin. I was his roommate during the first two years of my Ph.D. He made my arrival to College Station a lot smoother than I thought it would be. He was like my family away from home. On the technical side, Ahmed and I worked together on three fruitful projects, which constituted a major part of my Ph.D. I learned much from our numerous technical discussions. I also enjoyed the company of many students with whom I had very interesting technical discussions. I had the most wonderful learning experience working with a team of very active and bright Ph.D. students in the Bluetooth and the Chameleon projects, which included Alberto Valdes-Garcia, Ari Valero-Lopez, Wenjun Sheng, Bo Xia, Sung Tung Moon, Chunyu Xin, and Ahmed Nader Mohieldin. Their talent and determination was behind the success of the two projects. I am also grateful to my friend and colleague, Faisal Abdellatif Elseddeek, for good times we spent together as roommates. He provided me the emotional support I much needed at the last stage of my Ph.D.

Finally, I will never find words enough to express the gratitude that I owe to my late father, my mother, my sister Sahar, my brother Mohamed, and my fiancée Eman. Their tender love and support have always been the cementing force for building the blocks of my career. The all round support rendered by them provided the much needed stimulant to sail through the phases of stress and strain.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                  | iii   |

|-----------------------------------------------------------------------------------------------------------|-------|

| DEDICATION                                                                                                | v     |

| ACKNOWLEDGEMENTS                                                                                          | vi    |

| TABLE OF CONTENTS                                                                                         | viii  |

| LIST OF FIGURES                                                                                           | xi    |

| LIST OF TABLES                                                                                            | xviii |

| CHAPTER                                                                                                   |       |

| I INTRODUCTION                                                                                            | 1     |

| <ul><li>1.1. Background and Motivation</li><li>1.2. Dissertation Overview</li></ul>                       | 1     |

| II SHORT-RANGE COMMUNICATION STANDARDS                                                                    | 4     |

| <ul> <li>2.1. Short-Range Wired Communications</li></ul>                                                  | 5<br> |

| <ul><li>2.3.4. Blocking Requirements</li></ul>                                                            |       |

| 2.4.1. Wi-Fi Operation<br>2.4.2. Modulation Format                                                        |       |

| <ul> <li>2.4.3. Operating Frequency Range</li></ul>                                                       |       |

| <ul><li>2.4.6. Sensitivity</li><li>2.5. Comparing Bluetooth and Wi-Fi</li><li>2.6. What is UWB?</li></ul> |       |

| III BLUETOOTH RECEIVER ARCHITECTURE AND CHANNEL<br>SELECTION FILTER                           | 31  |

|-----------------------------------------------------------------------------------------------|-----|

|                                                                                               | 22  |

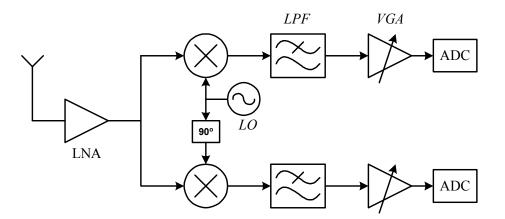

| 3.1. Direct-Conversion Receiver Architecture                                                  |     |

| 3.1.1. DC Offsets                                                                             |     |

| 3.1.2. 1/f Noise                                                                              |     |

| 3.1.3. Even Order Distortion                                                                  |     |

| 3.1.4. I/Q Mismatch<br>3.2. Low-IF Receiver Architecture                                      |     |

| 3.3. Bluetooth Receiver Architecture                                                          |     |

| 3.4. Channel Select Complex Filter Design                                                     |     |

|                                                                                               |     |

| 3.4.1. Complex Filter Theory                                                                  |     |

| <ul><li>3.4.2. Complex Filter Implementation</li><li>3.4.3. Frequency Tuning Scheme</li></ul> |     |

| 3.4.4. Experimental Results                                                                   |     |

| 3.5. Conclusions                                                                              |     |

| <i>5.5.</i> Conclusions                                                                       | 00  |

| IV DIRECT DIGITAL FREQUENCY SYNTHESIZER (DDFS)                                                | 69  |

| 4.1. Conventional DDFS Architecture                                                           | 70  |

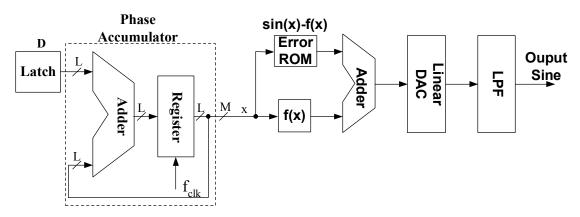

| 4.2. Proposed DDFS Architecture                                                               | 74  |

| 4.3. Linear DAC                                                                               | 79  |

| 4.4. Switched Weighted-Sum Block                                                              |     |

| 4.5. Experimental Results                                                                     |     |

| 4.6. Particular Case                                                                          | 96  |

| 4.7. Conclusions                                                                              | 97  |

| V CHAMELEON: A MULTI-STANDARD RECEIVER DESIGN                                                 | 99  |

| 5.1. Possible Receiver Architectures                                                          | 99  |

| 5.2. Proposed Direct-Conversion Receiver Architecture                                         | 102 |

| 5.3. System Design Issues                                                                     | 104 |

| 5.3.1. BER versus SNR                                                                         | 105 |

| 5.3.2. DC Offset Problem                                                                      | 108 |

| 5.3.3. Filter Frequency Response                                                              |     |

| 5.3.4. ADC Resolution and Sampling Rate                                                       |     |

| 5.3.5. VGA Dynamic Range                                                                      | 123 |

| 5.3.6. I/Q Mismatches                                                                         | 124 |

| 5.3.7. Even-order Distortion                                                                  |     |

| 5.3.8. VCO Frequency Pulling                                                                  |     |

| 5.3.9. Combined Effects                                                                       |     |

| 5.4. From Standard to Block Specifications                                                    |     |

| 5.4.1. From Standard to Receiver Specifications                                               |     |

| 5.4.2. Determination of Receiver Building Blocks Specifications                               |     |

| 5.4.3. System Design Verification                                                             | 148 |

| VI CHAMELEON: CIRCUIT IMPLEMENTATIONS          |     |

|------------------------------------------------|-----|

| 6.1. LNA and Mixer                             | 158 |

| 6.2. VCO and PLL                               |     |

| 6.3. Channel Select Filter                     |     |

| 6.4. Variable Gain Amplifier                   |     |

| 6.4.1. DC Offset Problem, Revisited            |     |

| 6.4.2. Proposed Solution for HPF Slow Response |     |

| 6.4.3. OpAmp and Buffer Designs                |     |

| 6.4.4. VGA Gain Lineup                         |     |

| 6.4.5. Testing Results                         |     |

| 6.5. Analog to Digital Converter               |     |

| VII CHAMELEON: EXPERIMENTAL RESULTS            |     |

| 7.1. System Chip                               |     |

| 7.2. Experimental Results                      |     |

| 7.2.1. BER vs. Input Power (Sensitivity)       |     |

| 7.2.2. IIP3                                    |     |

| 7.2.3. IIP2                                    |     |

| VIII CONCLUSIONS                               |     |

| REFERENCES                                     |     |

| APPENDIX A                                     |     |

| APPENDIX B                                     |     |

| APPENDIX C                                     |     |

| APPENDIX D                                     |     |

| APPENDIX E                                     |     |

| VITA                                           |     |

# **LIST OF FIGURES**

|      |      | Pa                                                                                                                                                     | age  |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. | 2.1  | Short range communication standards                                                                                                                    | 4    |

| Fig. | 2.2  | Point-to-point and point-to-multipoint and scatternet topology in Bluetooth                                                                            | .13  |

| Fig. | 2.3  | Gaussian LPF impulse response                                                                                                                          | . 14 |

| Fig. | 2.4  | Gaussian LPF frequency response                                                                                                                        | . 14 |

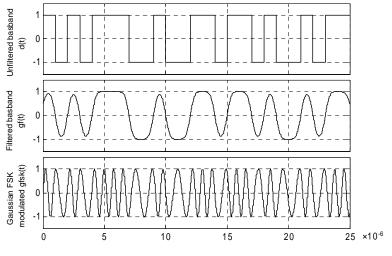

| Fig. | 2.5  | GFSK modulation steps                                                                                                                                  | . 16 |

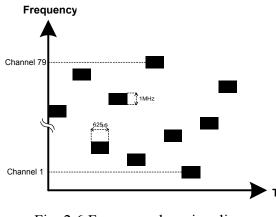

| Fig. | 2.6  | Frequency hopping diagram                                                                                                                              | . 17 |

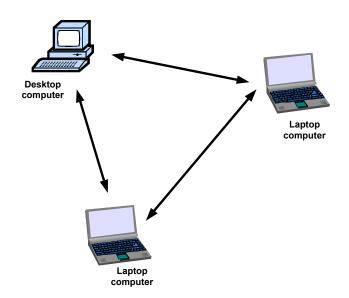

| Fig. | 2.7  | An ad hoc wireless network with three stations using Wi-Fi                                                                                             | .21  |

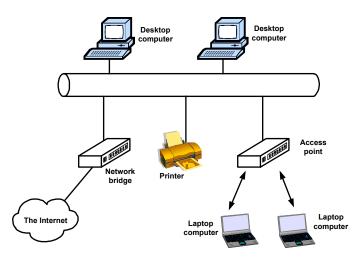

| Fig. | 2.8  | A simple infrastructure network using Wi-Fi                                                                                                            | 21   |

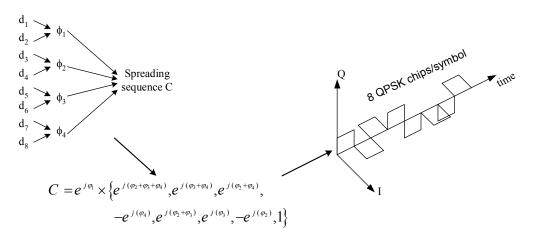

| Fig. | 2.9  | Construction of the CCK modulated signal                                                                                                               | . 22 |

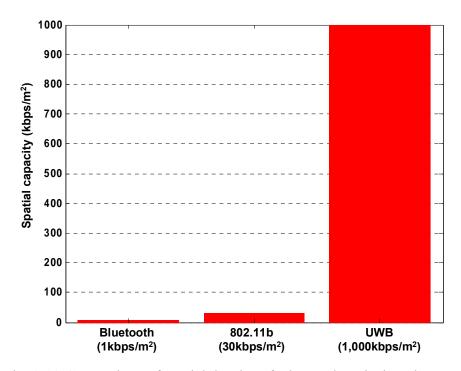

| Fig. | 2.10 | Comparison of spatial density of Bluetooth, Wi-Fi, and UWB                                                                                             | . 30 |

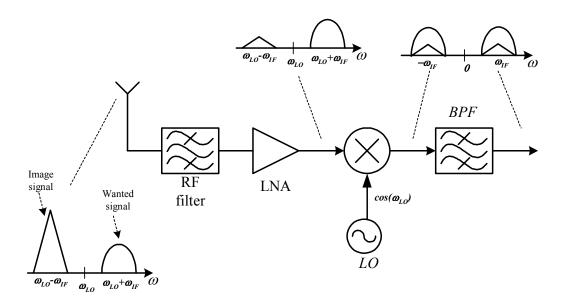

| Fig. | 3.1  | Direct-conversion receiver architecture.                                                                                                               | . 32 |

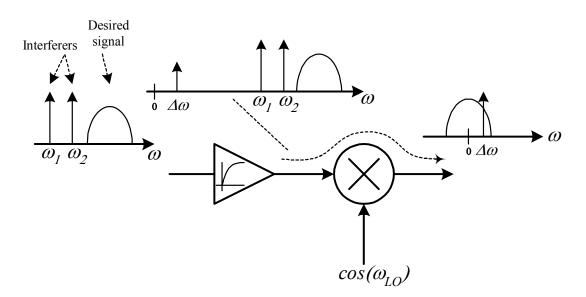

| Fig. | 3.2  | Effect of even order distortion                                                                                                                        | .35  |

| Fig. | 3.3  | IF receiver architecture.                                                                                                                              | .37  |

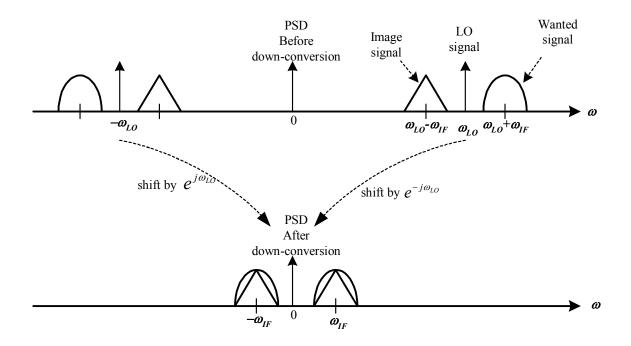

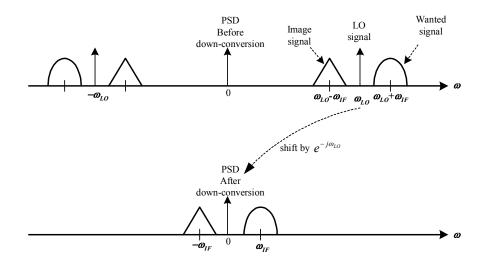

| Fig. | 3.4  | Down-conversion with a single sinusoidal signal.                                                                                                       | .37  |

| Fig. | 3.5  | Down-conversion with a single exponential.                                                                                                             | .38  |

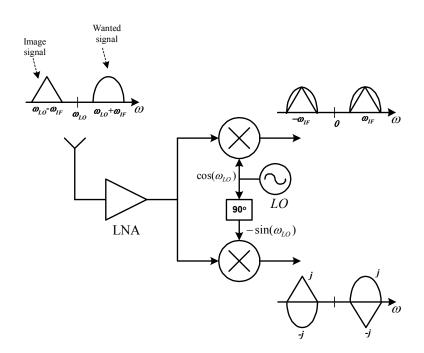

| Fig. | 3.6  | Basic low-IF receiver architecture.                                                                                                                    | .39  |

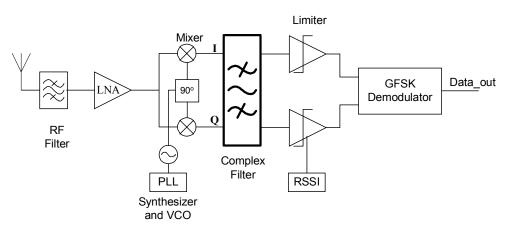

| Fig. | 3.7  | A Low-IF Bluetooth receiver architecture [15]                                                                                                          | .41  |

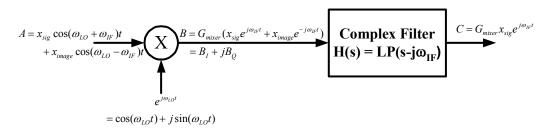

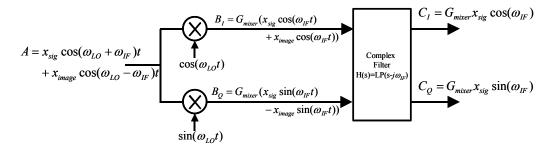

| Fig. | 3.8  | Receiver image rejection architecture in the complex domain                                                                                            | .43  |

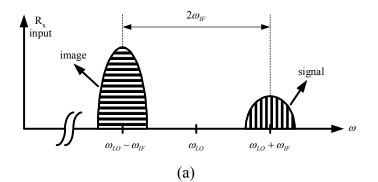

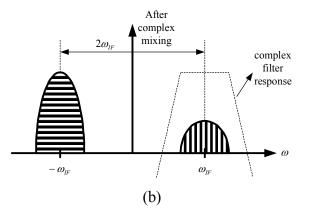

| Fig. | 3.9  | Frequency translation of a complex (quadrature) mixer (a) before complex mixing (signal A in Fig. 3.8) (b) after complex mixing (signal B in Fig. 3.8) | .45  |

| Fig. | 3.10 | Practical implementation of the receiver image rejection                                                                                               | .46  |

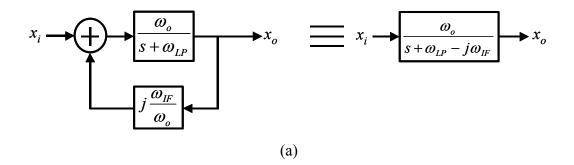

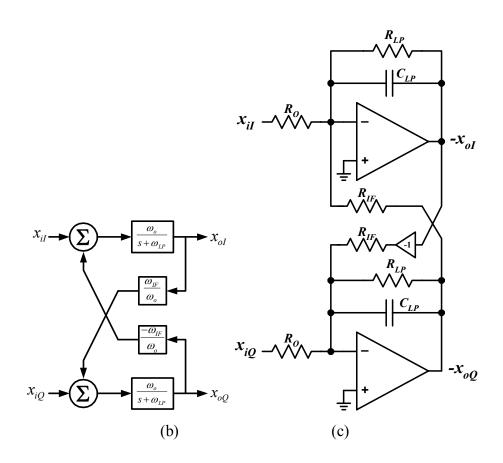

| Fig. | 3.11 | LPF shifted to $\omega_{IF}$ (a) conceptual complex representation (b) actual building block implementation (c) Active-RC implementation               | . 48 |

|                                                                                            | Page |

|--------------------------------------------------------------------------------------------|------|

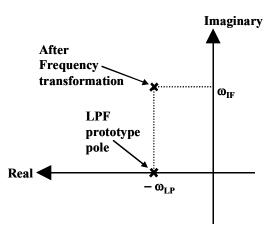

| Fig. 3.12 Pole locus of the LPF prototype and the complex BPF                              | 49   |

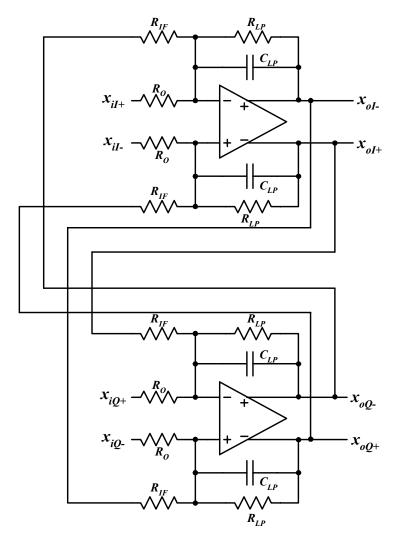

| Fig. 3.13 Fully differential active-RC complex first-order LPF                             | 49   |

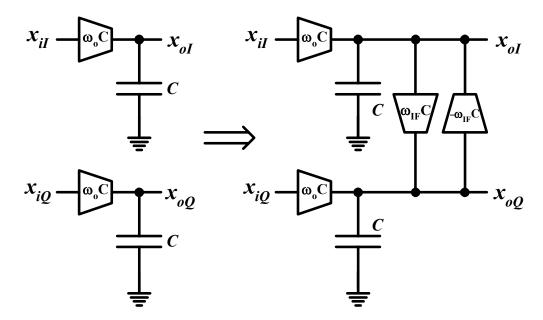

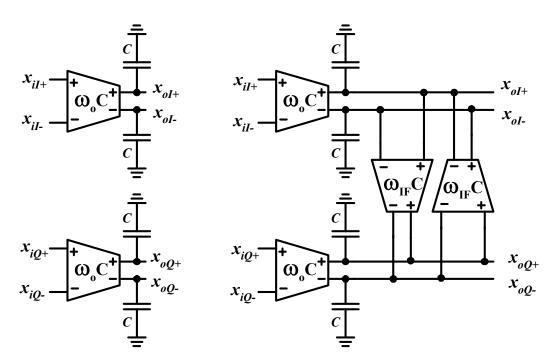

| Fig. 3.14 Linear frequency translation to convert LPF to complex BPF                       | 50   |

| Fig. 3.15 Differential OTA-C implementation of linear frequency translation                | 50   |

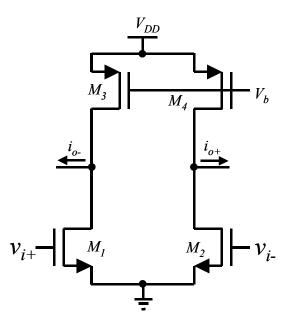

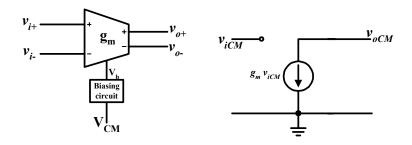

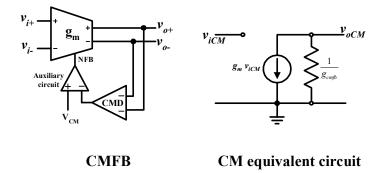

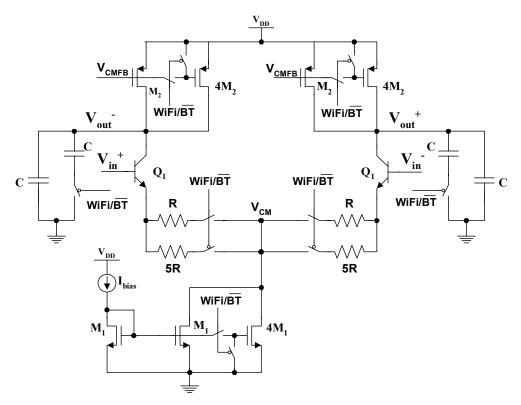

| Fig. 3.16 Pseudo differential OTA                                                          | 51   |

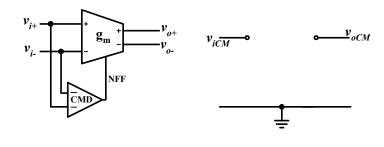

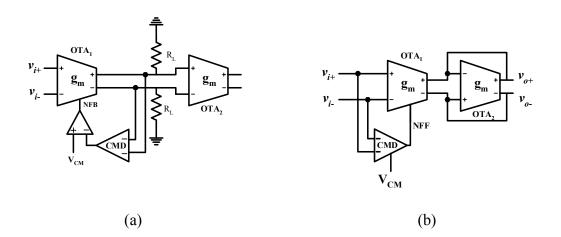

| Fig. 3.17 (a) No CM control (b) CMFB circuit (c) CMFF circuit                              | 52   |

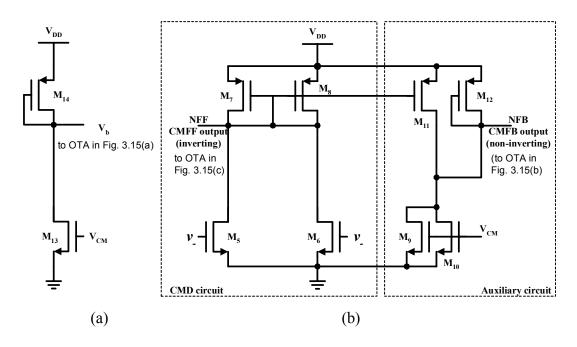

| Fig. 3.18 (a) Biasing circuit (b) The CMD and auxiliary circuit required for CMFF and CMFB | 53   |

|                                                                                            |      |

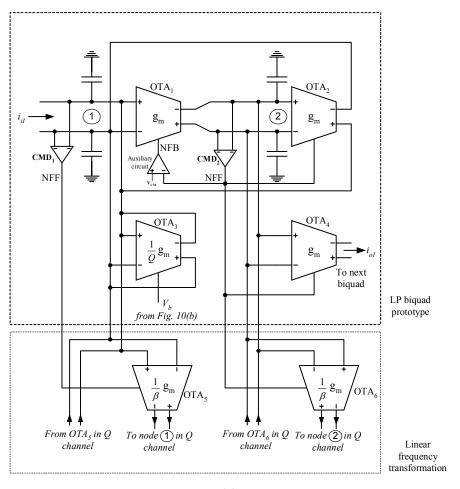

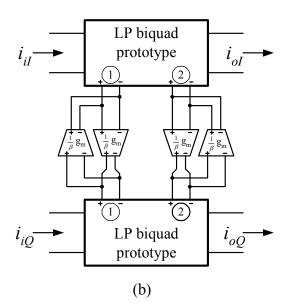

| Fig. 3.19 (a) I branch of the complex biquadratic section (b) Conceptual complex biquad. | 54 |

|------------------------------------------------------------------------------------------|----|

| Fig. 3.20 (a) Circuit setup for HD3 analysis (b) Another scenario for HD3 analysis       | 57 |

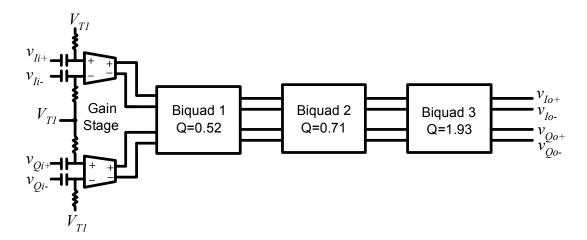

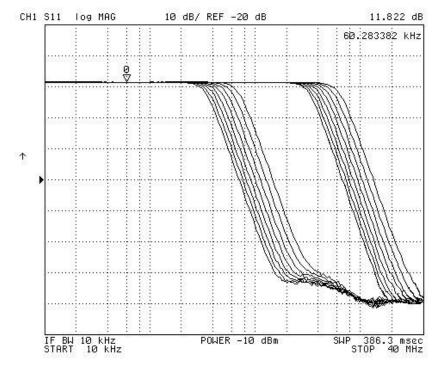

| Fig. 3.21 The complete 12 <sup>th</sup> order complex filter                             | 59 |

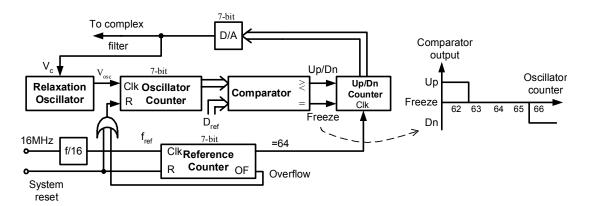

| Fig. 3.22 Frequency tuning circuit for complex filter                                                                            | 61 |

|----------------------------------------------------------------------------------------------------------------------------------|----|

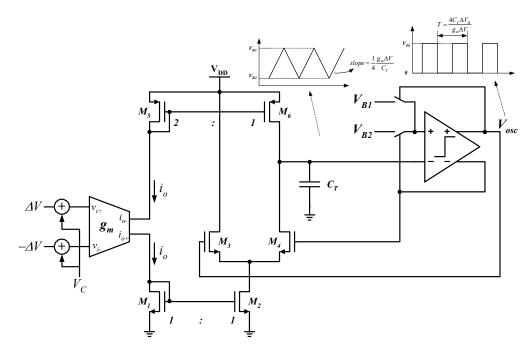

| Fig. 3.23 The relaxation oscillator                                                                                              | 63 |

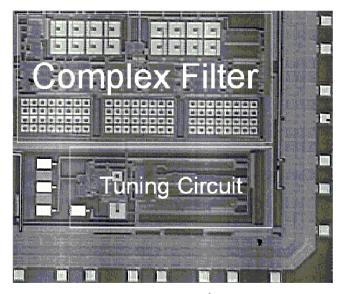

| Fig. 3.24 The die photo (filter area= $1.6 \times 0.8$ mm <sup>2</sup> and tuning circuit area= $1 \times 0.4$ mm <sup>2</sup> ) | 65 |

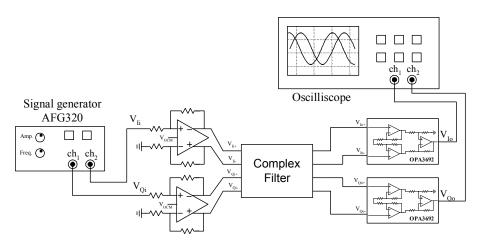

| Fig. 3.25 Test setup for the complex filter                                                                                      | 65 |

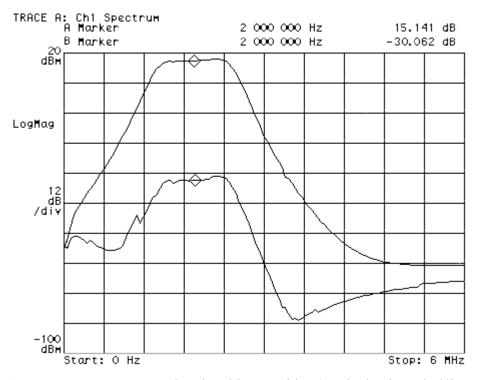

| Fig. 3.26 Frequency response at signal and image sides (vertical axis 12dB/div, ideal, — actual)                                 | 66 |

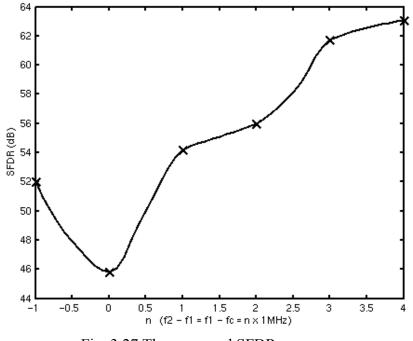

| Fig. 3.27 The measured SFDR versus n                                                                                             | 66 |

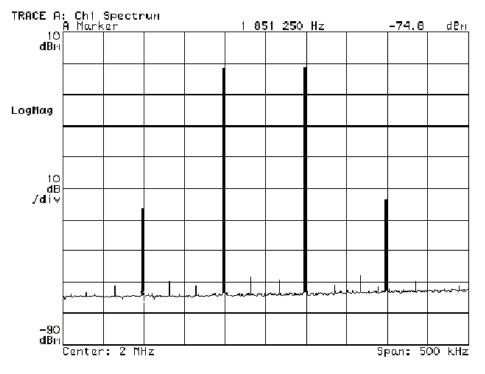

| Fig. 3.28 IM3 test for $f_1 = 1.95$ MHz and $f_2 = 2.05$ MHz                                                                     | 67 |

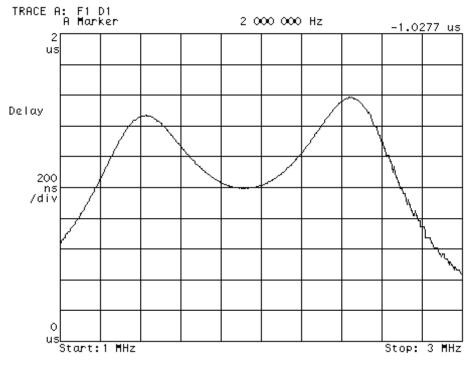

| Fig. 3.29 Group delay response                                                                                                   | 67 |

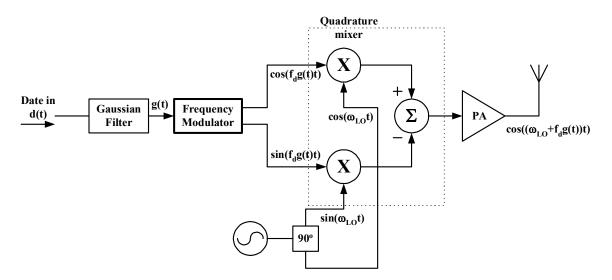

| Fig. 4.1 Bluetooth transmitter architecture                                                                                      | 69 |

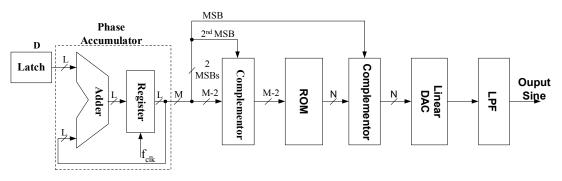

| Fig. 4.2 Conventional ROM-based DDFS                                                                                             | 71 |

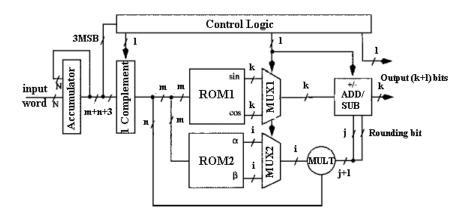

Fig. 4.4 Combining a small ROM and linear interpolation to generate sine function.....73

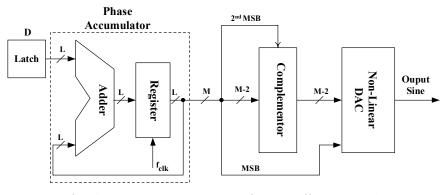

| Fig. | 4.5  | ROM-Less DDFS using non-linear DAC                                            | . 73 |

|------|------|-------------------------------------------------------------------------------|------|

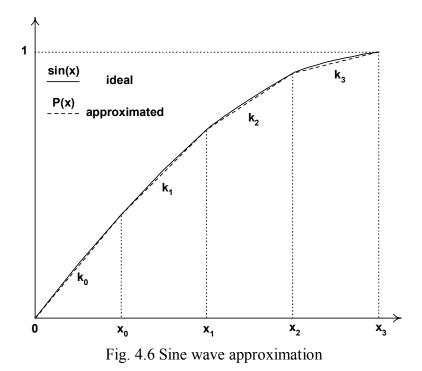

| Fig. | 4.6  | Sine wave approximation                                                       | . 74 |

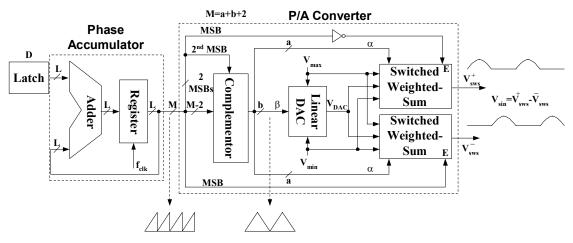

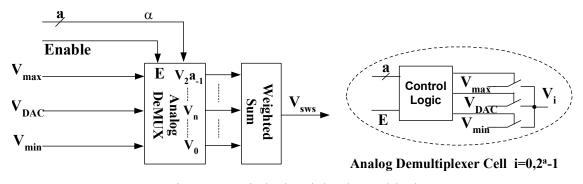

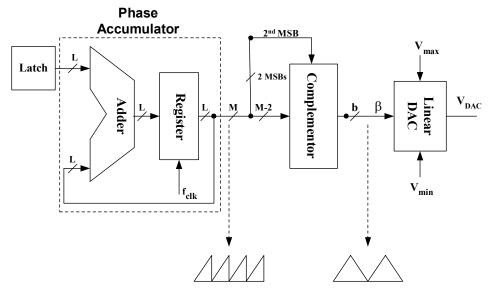

| Fig. | 4.7  | Block diagram of the proposed DDFS architecture                               | . 76 |

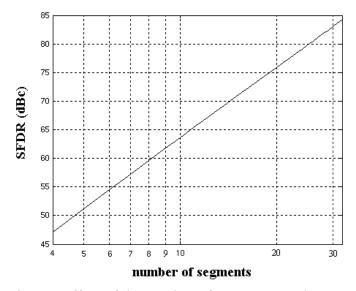

| Fig. | 4.8  | Effect of the number of segments on the SFDR                                  | . 77 |

| Fig. | 4.9  | Effect of phase resolution on the SFDR                                        | . 77 |

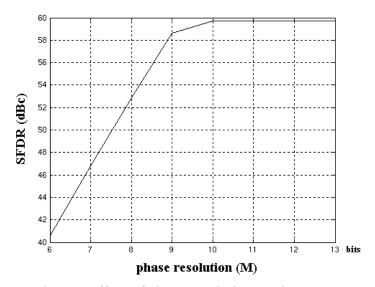

| Fig. | 4.10 | Effect of finite unit resistance on the SFDR                                  | . 78 |

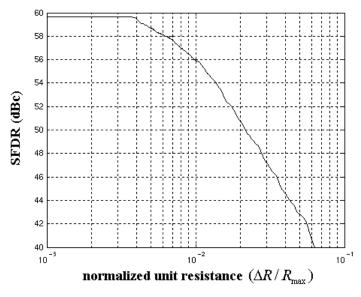

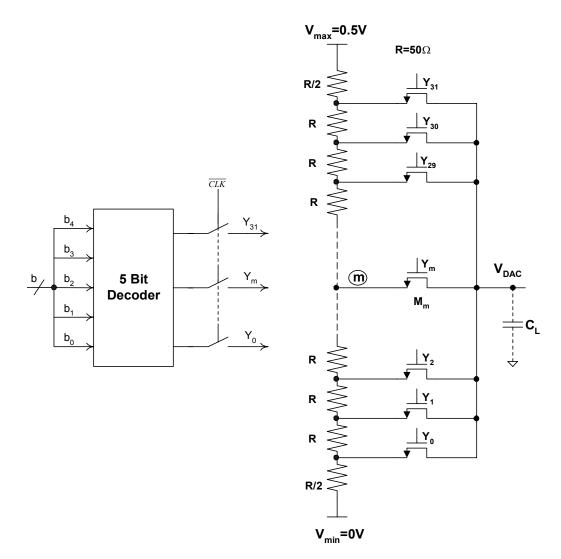

| Fig. | 4.11 | Linear DAC circuit implementation                                             | . 80 |

| Fig. | 4.12 | Switched weighted-sum block                                                   | . 81 |

| Fig. | 4.13 | Implementation of the weighted-sum block                                      | . 83 |

| Fig. | 4.14 | Alternative implementation of the weighted-sum block                          | . 86 |

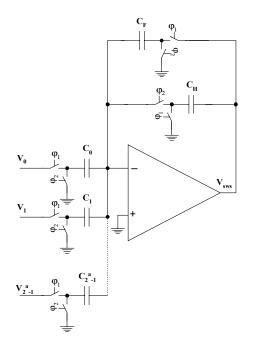

| Fig. | 4.15 | Chip micrograph                                                               | . 90 |

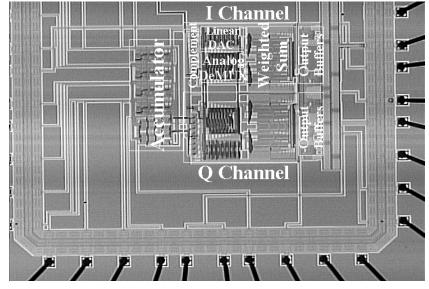

| Fig. | 4.16 | Testing setup                                                                 | . 90 |

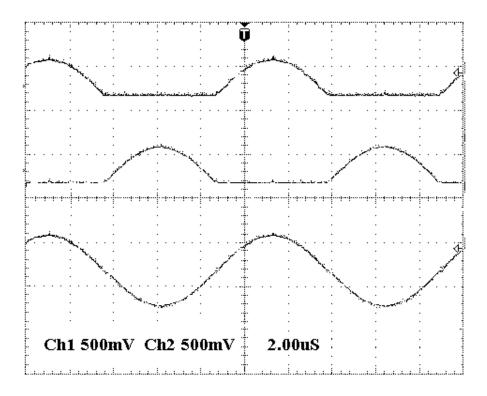

| Fig. | 4.17 | Single-ended and differential outputs of the I branch (fout=98kHz)            | . 91 |

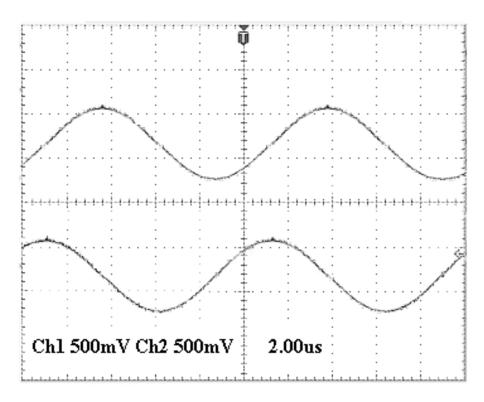

| Fig. | 4.18 | Quadrature outputs I and Q at fout=98kHz                                      | . 91 |

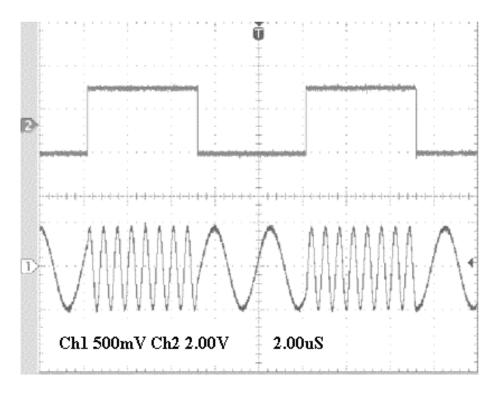

| Fig. | 4.19 | Frequency modulation                                                          | . 92 |

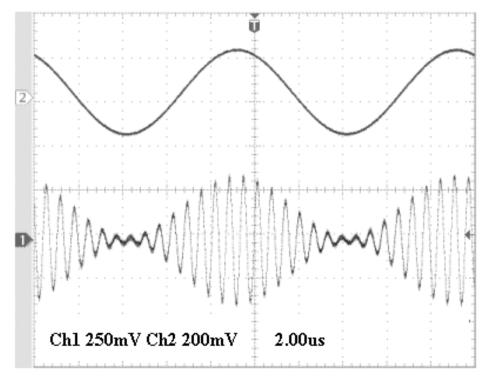

| Fig. | 4.20 | Amplitude modulation                                                          | . 92 |

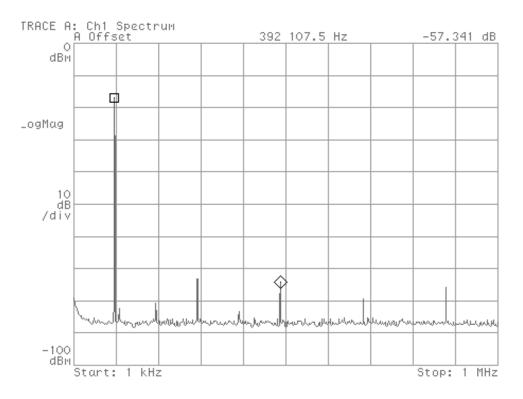

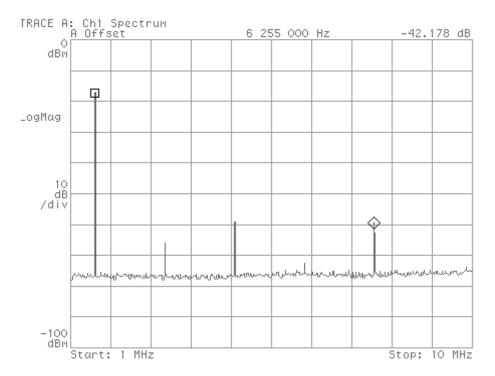

| Fig. | 4.21 | Output spectrum at $f_{clk}$ =100MHz and $f_{out}$ =98kHz with SFDR=57.3dBc   | . 93 |

| Fig. | 4.22 | Output spectrum at $f_{clk}$ =100MHz and $f_{out}$ =1.56MHz with SFDR=42.1dBc | . 93 |

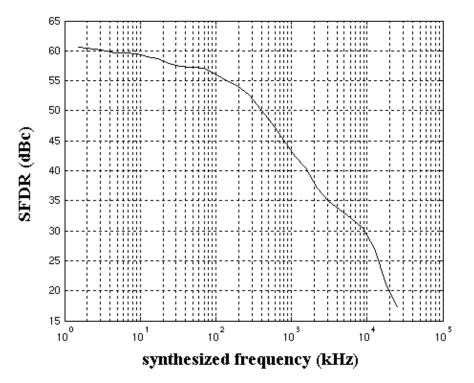

| Fig. | 4.23 | SFDR versus synthesized frequency at $f_{clk}$ =100MHz                        | . 94 |

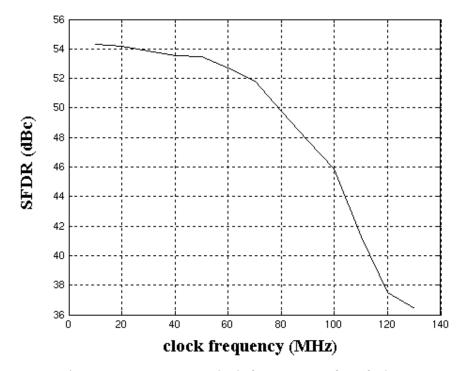

| Fig. | 4.24 | SFDR versus clock frequency at $f_{out} = f_{clk}/128$                        | . 94 |

| Fig. | 4.25 | Front end of DDFS                                                             | .97  |

| Fig. | 5.1  | Dual mode receiver architecture used in [37]                                  | 101  |

| Fig. | 5.2  | Dual mode receiver architecture used in [38]                                  | 102  |

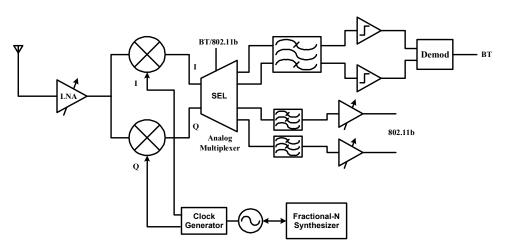

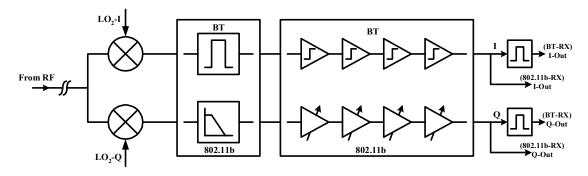

| Fig. | 5.3  | Dual-mode 802.11b/Bluetooth receiver.                                         | 103  |

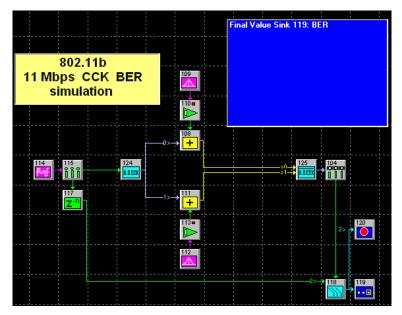

| Fig. 5.4 Basic Wi-Fi simulation setup in System View                                                                                | 106    |

|-------------------------------------------------------------------------------------------------------------------------------------|--------|

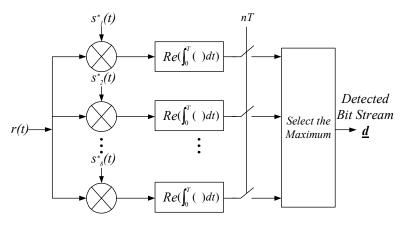

| Fig. 5.5 Bluetooth GFSK non-coherent demodulator used in MATLAB                                                                     | 106    |

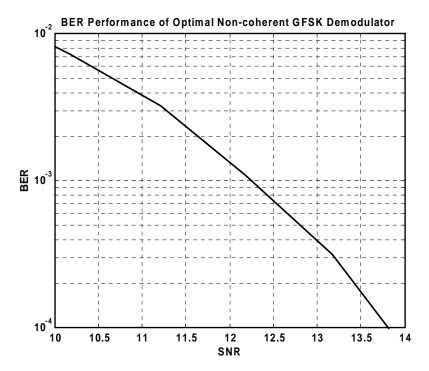

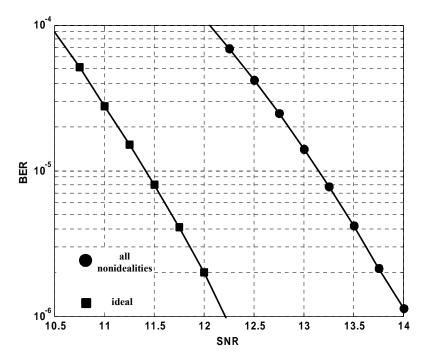

| Fig. 5.6 BER versus SNR in Bluetooth mode in the ideal case (Sampling rate = 20MSample/s)                                           | 107    |

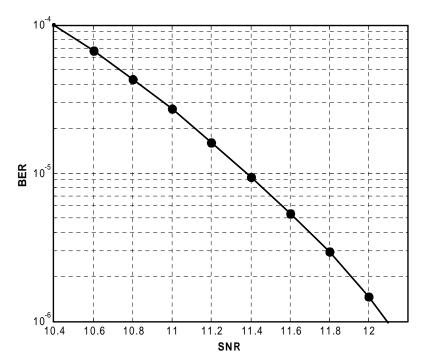

| Fig. 5.7 BER versus SNR performance of Wi-Fi 11Mbit/s CCK demodulator<br>(Sampling rate = 88 MSample/s)                             | 107    |

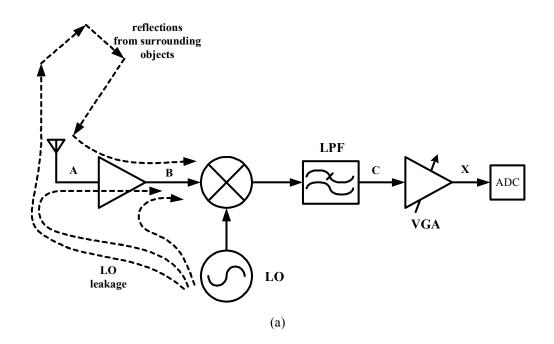

| Fig. 5.8 Self-mixing of (a) LO. (b) Interferers.                                                                                    | 108    |

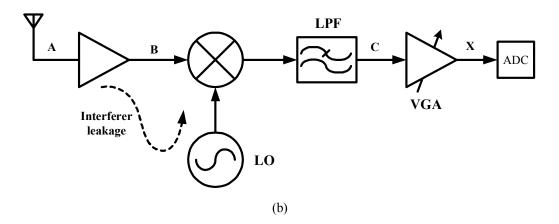

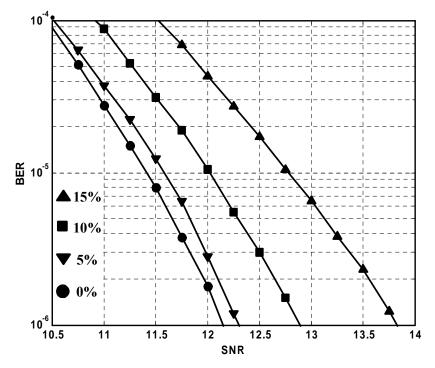

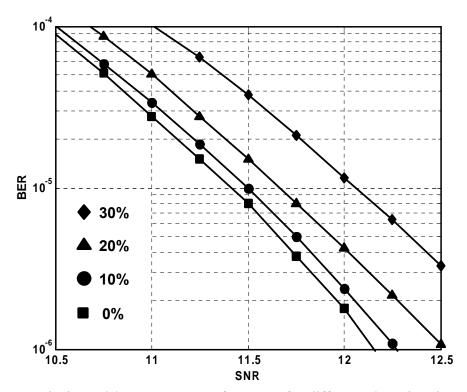

| Fig. 5.9 BER performance of Bluetooth GFSK demodulator for different DC offse (percentage relative to the peak signal value)        |        |

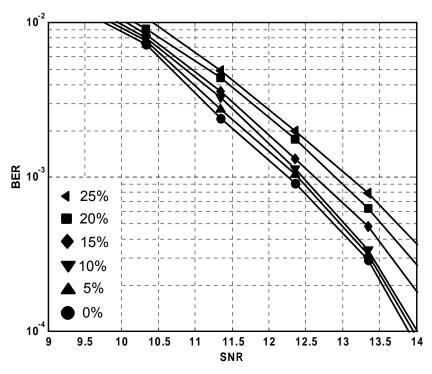

| Fig. 5.10 BER performance of Wi-Fi 11Mbit/s CCK demodulator for different DC offsets percentage (relative to the peak signal value) | 111    |

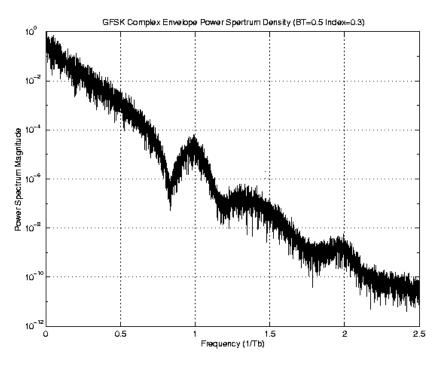

| Fig. 5.11 Power spectral density of Bluetooth GFSK signal                                                                           | 113    |

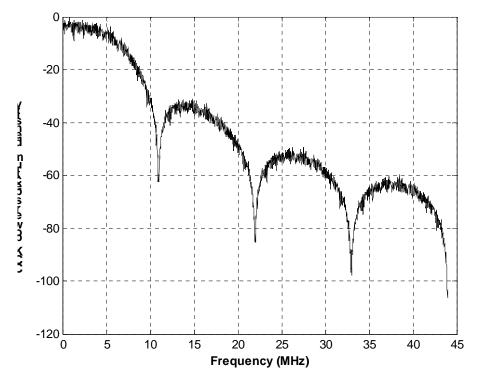

| Fig. 5.12 Power spectral density of Wi-Fi CCK signal                                                                                | 113    |

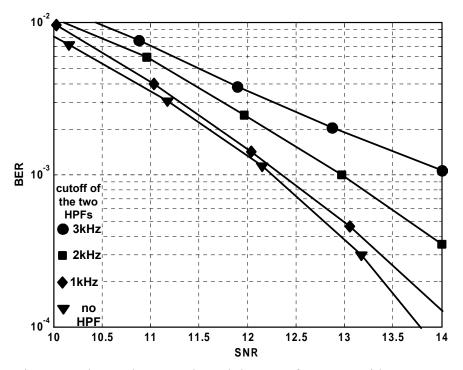

| Fig. 5.13 Bluetooth GFSK demodulator performance with two HPFs                                                                      | 114    |

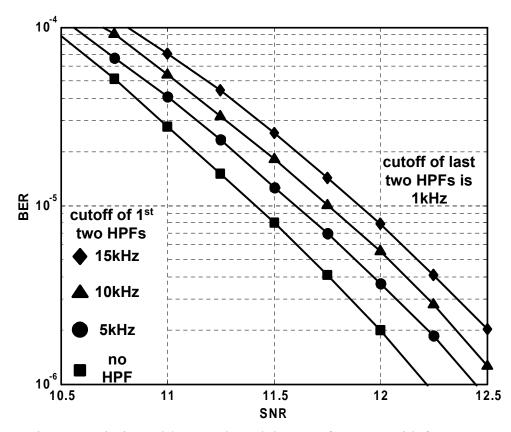

| Fig. 5.14 Wi-Fi 11Mb/s CCK demodulator performance with four HPFs                                                                   | 114    |

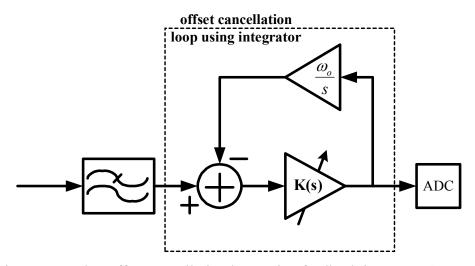

| Fig. 5.15 Analog offset cancellation loop using feedback integrator [41, 42]                                                        | 116    |

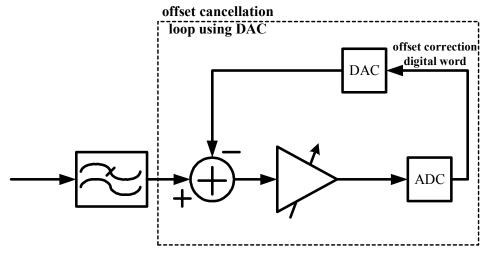

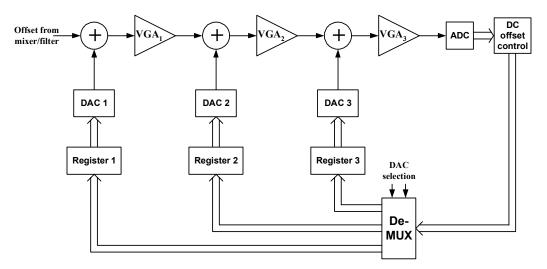

| Fig. 5.16 Offset cancellation loop using DAC [43]                                                                                   | 117    |

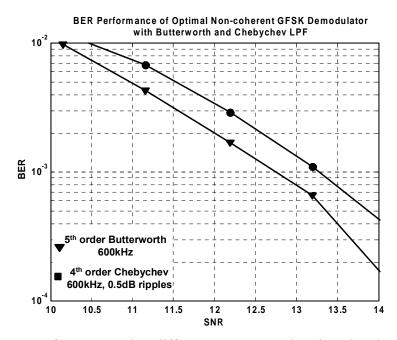

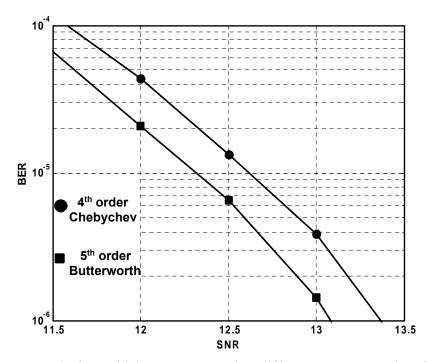

| Fig. 5.17 BER performance using different LPF approximations in Bluetooth mode                                                      | 118    |

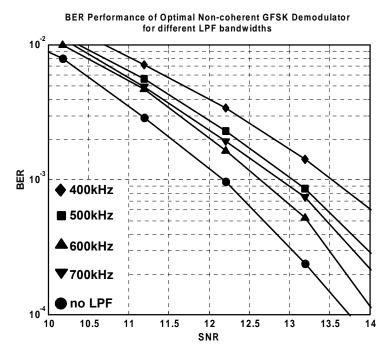

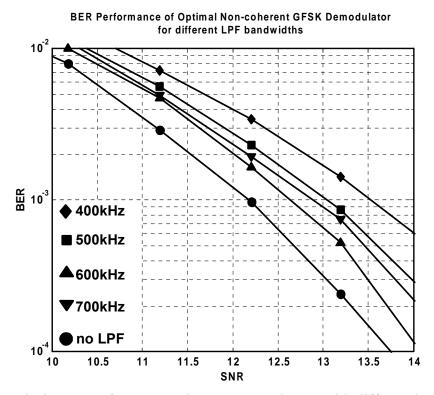

| Fig. 5.18 Bluetooth BER performance using Butterworth LPF with different bandwidths                                                 | 119    |

| Fig. 5.19 Wi-Fi 11Mbit/s CCK BER using different LPF approximations                                                                 | 119    |

| Fig. 5.20 Wi-Fi BER performance using Butterworth LPF with different bandwidth                                                      | ıs 120 |

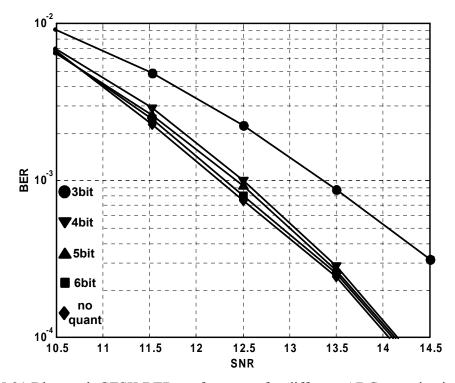

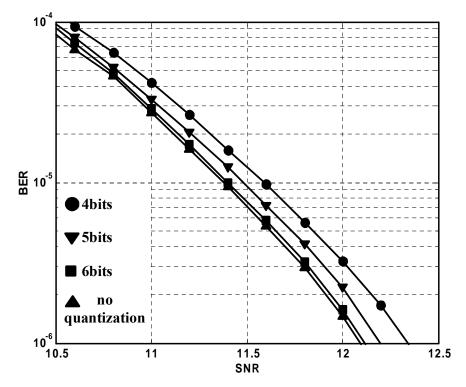

| Fig. 5.21 Bluetooth GFSK BER performance for different ADC quantization bits                                                        | 121    |

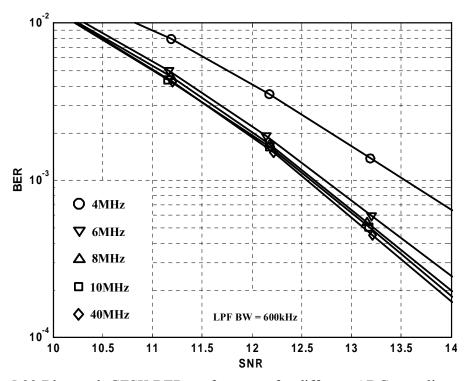

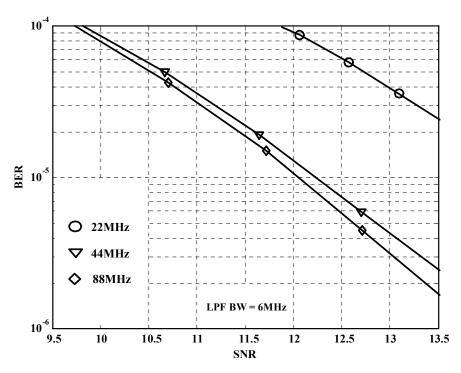

| Fig. 5.22 Bluetooth GFSK BER performance for different ADC sampling rates                                                           | 122    |

| Fig. 5.23 ADC quantization effect on BER performance of Wi-Fi 11Mb/s CCK                                                            | 122    |

| Fig. 5.24 Wi-Fi 11Mb/s CCK BER performance for different ADC sampling rates                                                         | 123    |

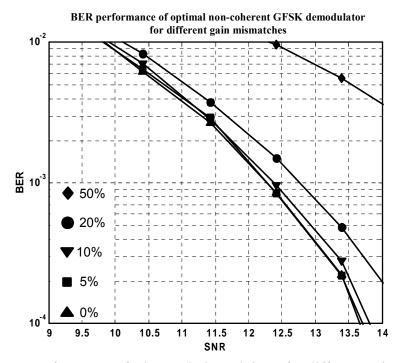

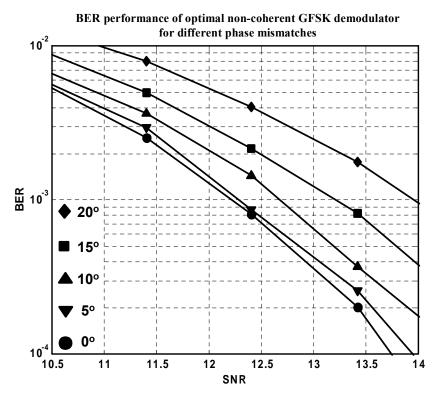

| Fig. 5.25 BER performance of Bluetooth demodulator for different gain mismatches .        | 125   |

|-------------------------------------------------------------------------------------------|-------|

| Fig. 5.26 BER performance of Bluetooth demodulator for different phase mismatches         | s 125 |

| Fig. 5.27 Wi-Fi 11Mb/s CCK BER performance for different I/Q gain mismatches              | 126   |

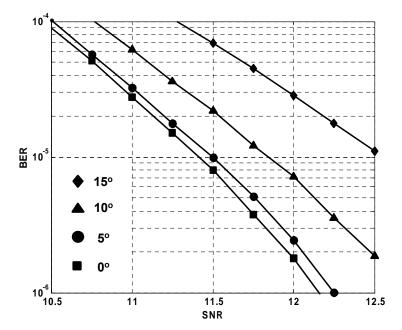

| Fig. 5.28 Wi-Fi 11Mb/s CCK BER performance for different I/Q phase mismatches.            | 126   |

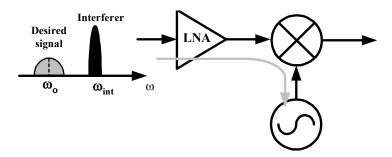

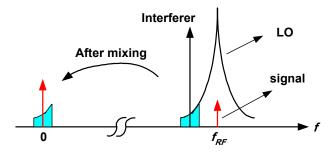

| Fig. 5.29 Injection pulling due to large interferer                                       | 128   |

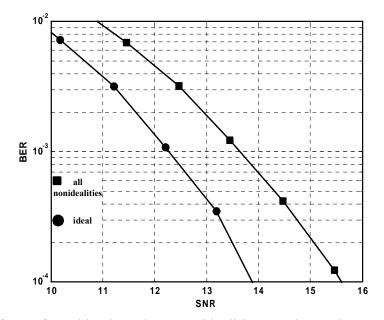

| Fig. 5.30 Effects of combined receiver non-idealities on Bluetooth BER performance        | . 129 |

| Fig. 5.31 Effects of combined receiver non-idealities on Wi-Fi BER performance            | 130   |

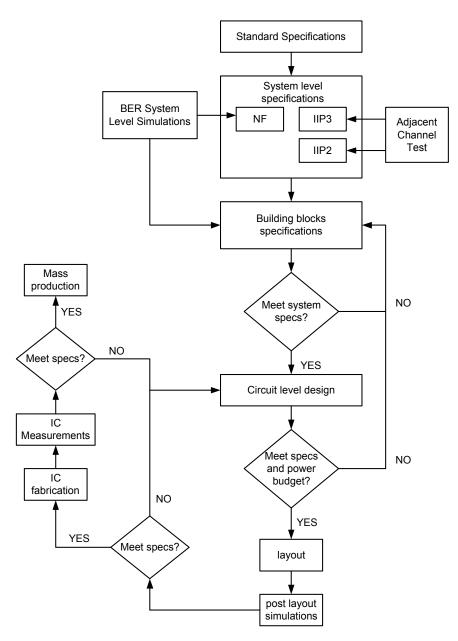

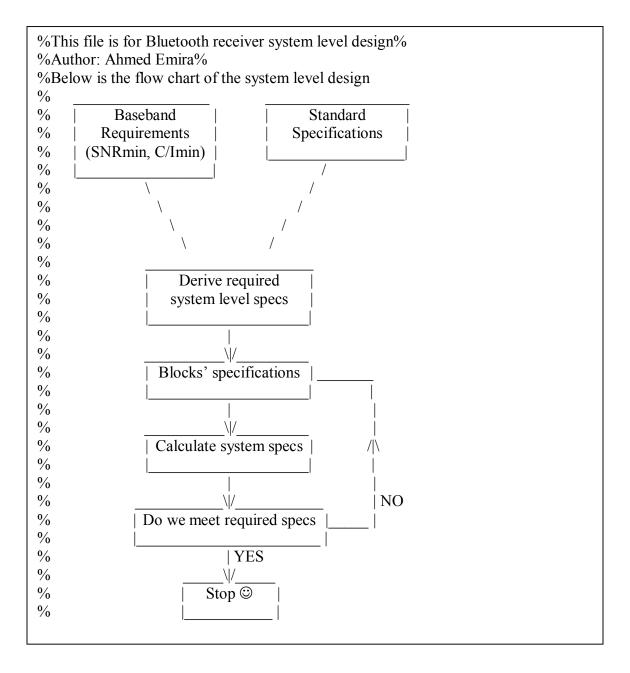

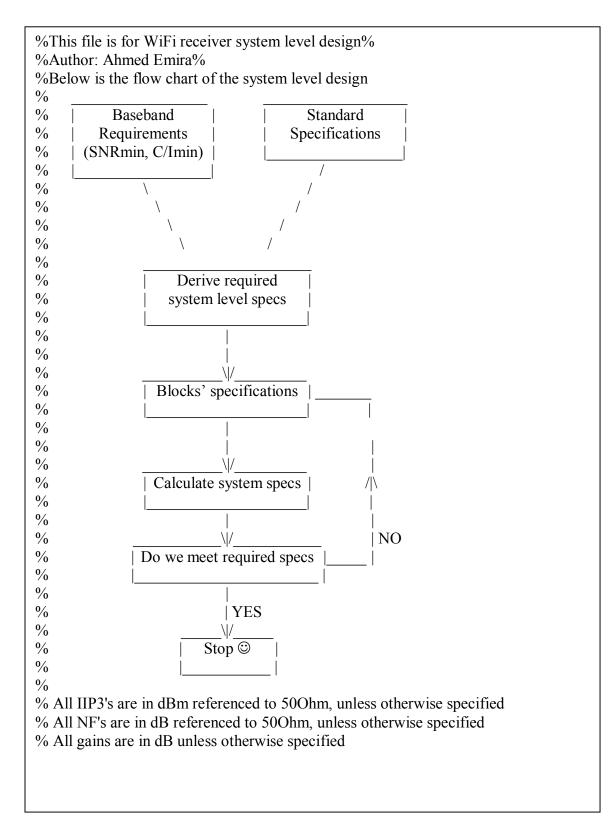

| Fig. 5.32 Flowchart of the system design process                                          | 131   |

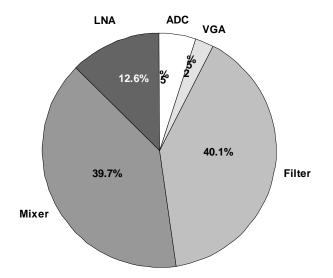

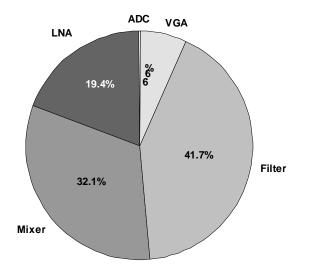

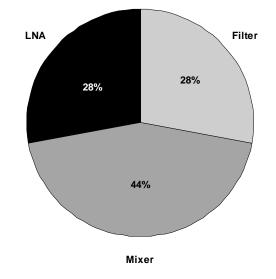

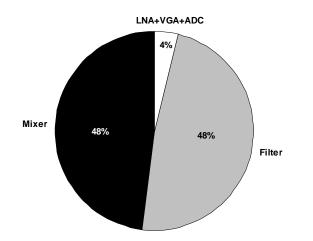

| Fig. 5.33 Noise contributions from the different receiver blocks in Bluetooth mode        | 142   |

| Fig. 5.34 Noise contributions from the different receiver blocks in Wi-Fi mode            | 142   |

| Fig. 5.35 IIP3 contributions from receiver blocks in both modes                           | 143   |

| Fig. 5.36 IIP2 contributions from receiver blocks in both modes                           | . 144 |

| Fig. 5.37 LO phase noise effect                                                           | 145   |

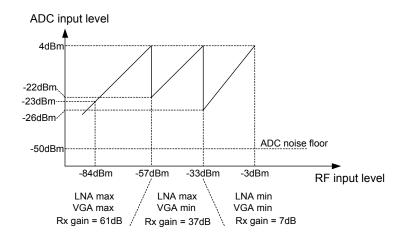

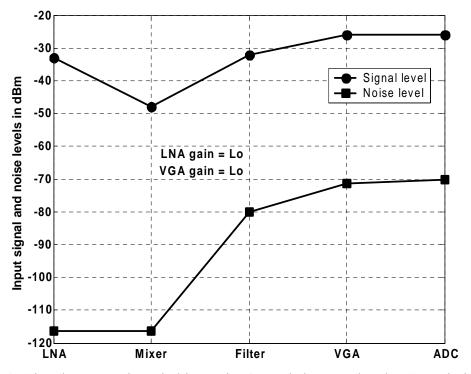

| Fig. 5.38 ADC input level versus RF input power in Bluetooth mode                         | 149   |

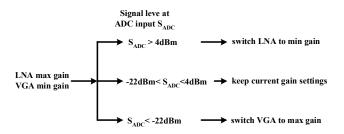

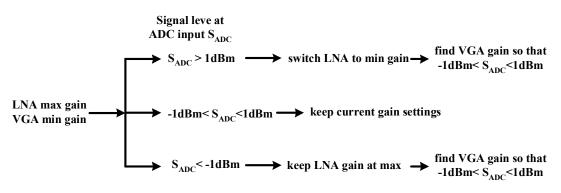

| Fig. 5.39 Gain switching strategy in Bluetooth mode                                       | 149   |

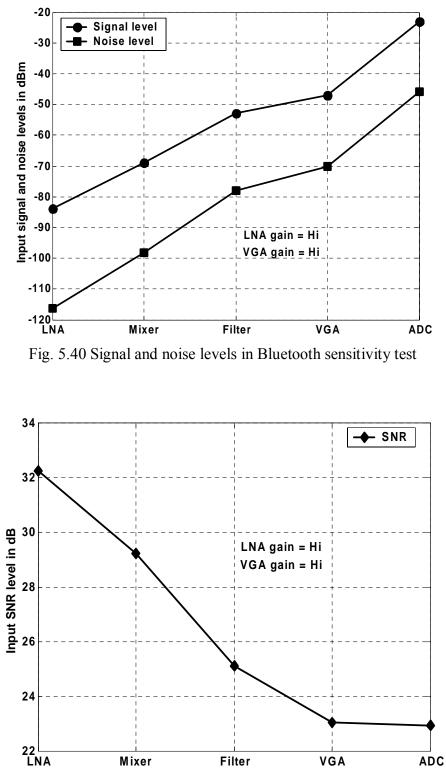

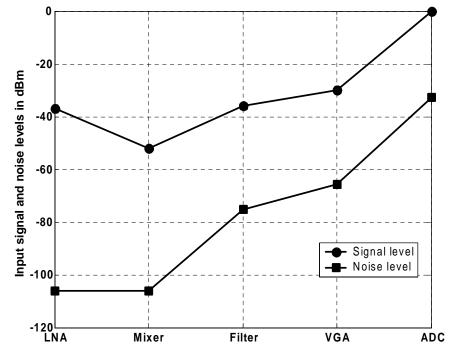

| Fig. 5.40 Signal and noise levels in Bluetooth sensitivity test                           | 150   |

| Fig. 5.41 Signal-to-noise ratio in Bluetooth sensitivity test                             | 150   |

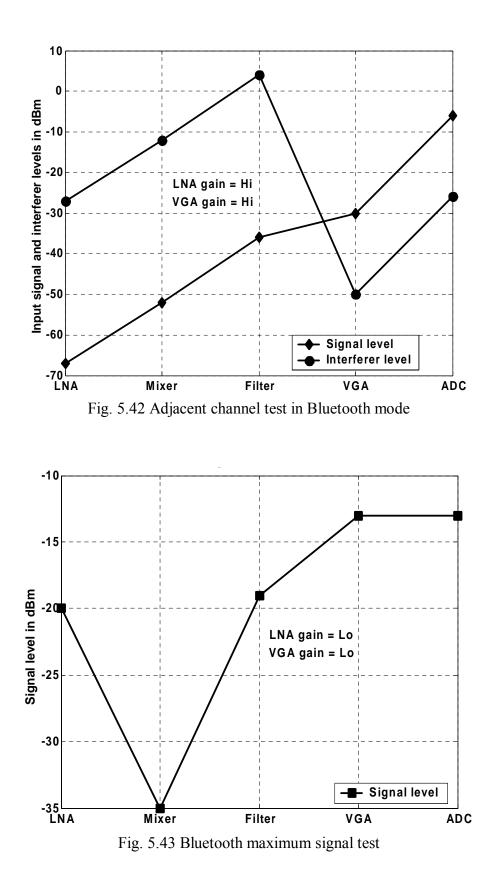

| Fig. 5.42 Adjacent channel test in Bluetooth mode                                         | 151   |

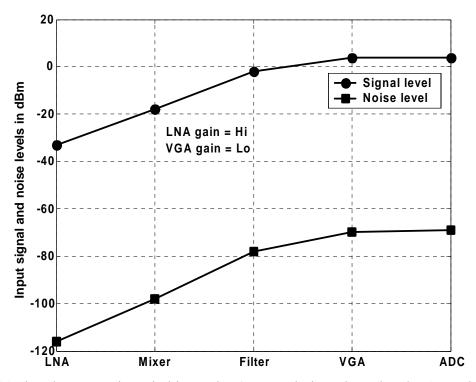

| Fig. 5.43 Bluetooth maximum signal test                                                   | . 151 |

| Fig. 5.44 Signal test at gain switching point (LNA gain is activated and VGA gain is low) | 152   |

| Fig. 5.45 Signal test at gain switching point (LNA is bypassed and VGA gain is low)       | . 152 |

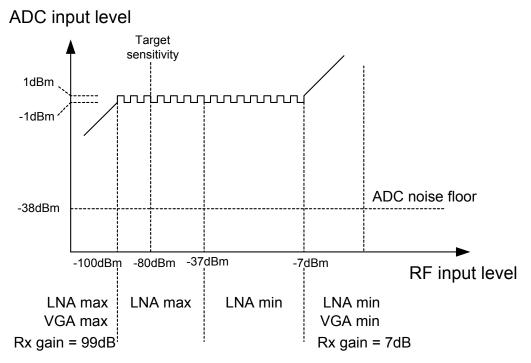

| Fig. 5.46 ADC input level versus RF input power in Wi-Fi mode                             | 154   |

| Fig. 5.47 Gain switching strategy in Wi-Fi mode                                           | 154   |

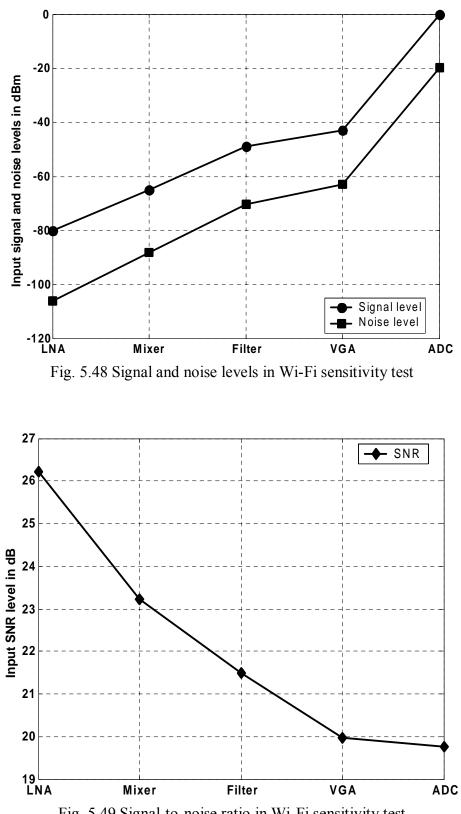

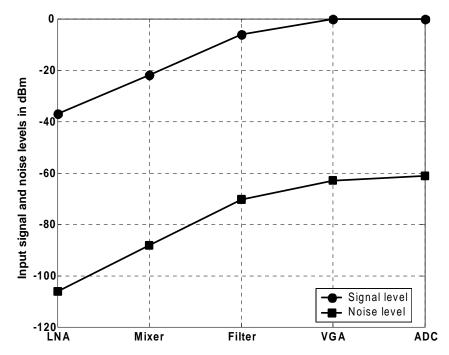

| Fig. 5.48 Signal and noise levels in Wi-Fi sensitivity test                               | 155   |

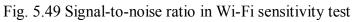

| Fig. 5.49 Signal-to-noise ratio in Wi-Fi sensitivity test                              |

|----------------------------------------------------------------------------------------|

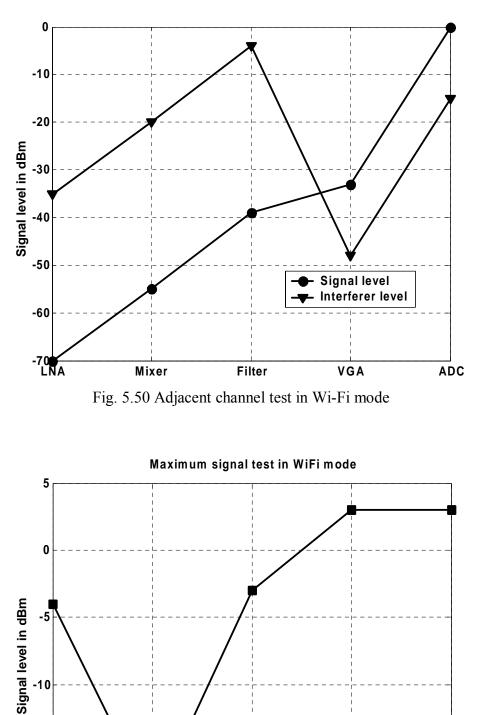

| Fig. 5.50 Adjacent channel test in Wi-Fi mode                                          |

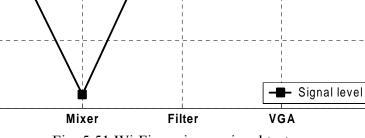

| Fig. 5.51 Wi-Fi maximum signal test                                                    |

| Fig. 5.52 Signal test at gain switching point in Wi-Fi mode (LNA gain is activated)157 |

| Fig. 5.53 Signal test at gain switching point in Wi-Fi mode (LNA is bypassed) 157      |

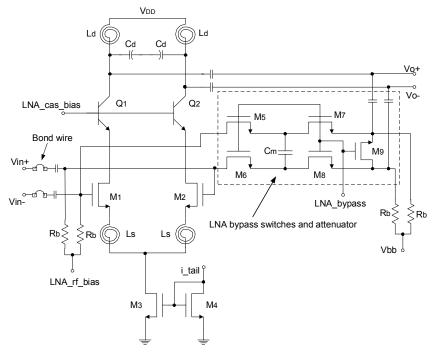

| Fig. 6.1 LNA circuit                                                                   |

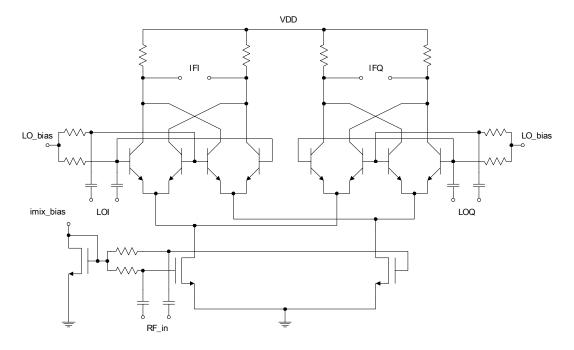

| Fig. 6.2 Mixer circuit                                                                 |

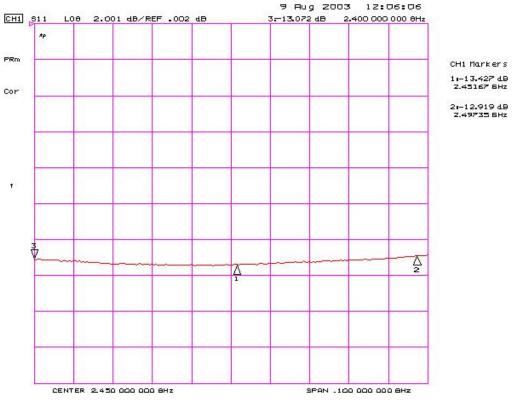

| Fig. 6.3 Input matching for the high gain mode                                         |

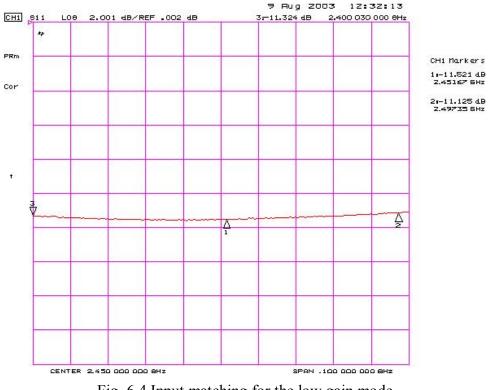

| Fig. 6.4 Input matching for the low gain mode                                          |

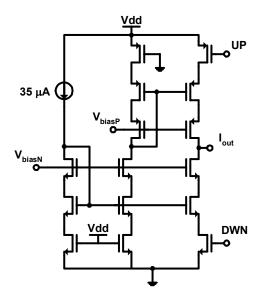

| Fig. 6.5 Cascode charge pump schematic                                                 |

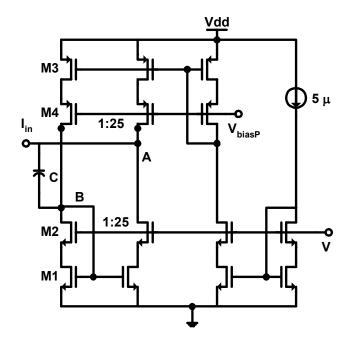

| Fig. 6.6 Capacitance multiplier schematic                                              |

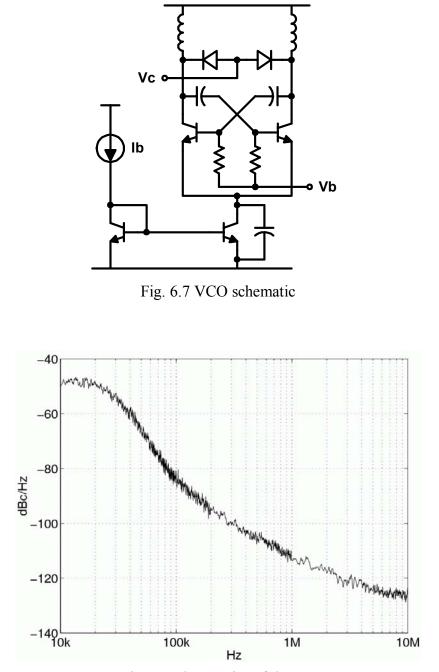

| Fig. 6.7 VCO schematic                                                                 |

| Fig. 6.8 Phase noise of the LO                                                         |

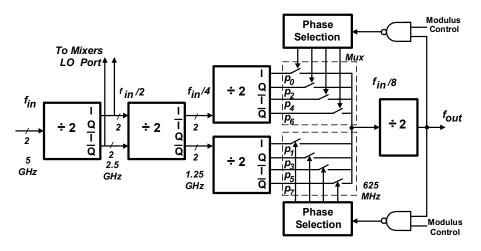

| Fig. 6.9 Phase switching prescaler                                                     |

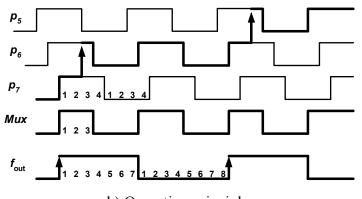

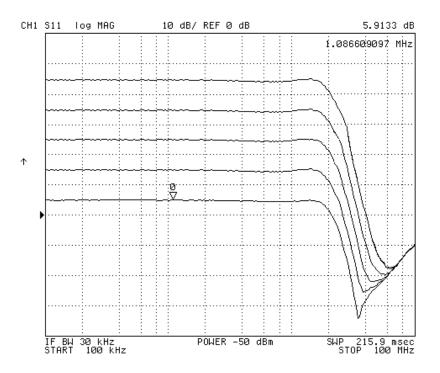

| Fig. 6.10 Butterworth filter block diagram                                             |

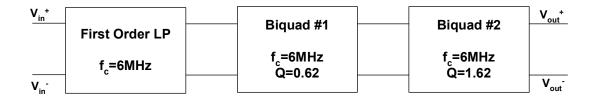

| Fig. 6.11 Biquadratic section                                                          |

| Fig. 6.12 Implementation of the dual-mode OTA                                          |

| Fig. 6.13 Dual-mode operation and programmability of the LPF                           |

| Fig. 6.14 DC offset correction using digital feedback                                  |

| Fig. 6.15 DC offset correction using passive HPF                                       |

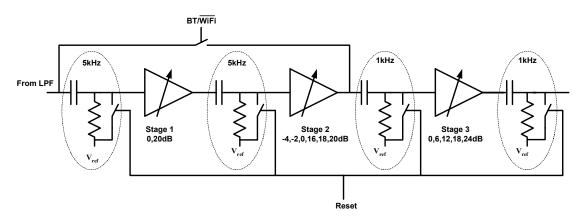

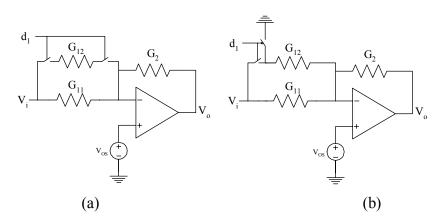

| Fig. 6.16 (a) Conventional OpAmp-R VGA (b) Proposed constant output offset VGA 175     |

| Fig. 6.17 Proposed constant output offset VGA circuit using OpAmp-R                    |

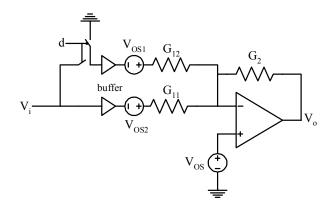

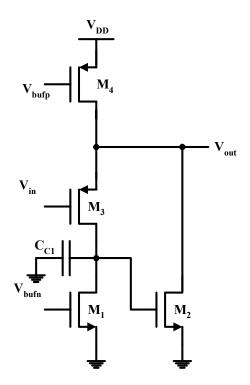

| Fig. 6.18 3-stage OpAmp schematic                                                      |

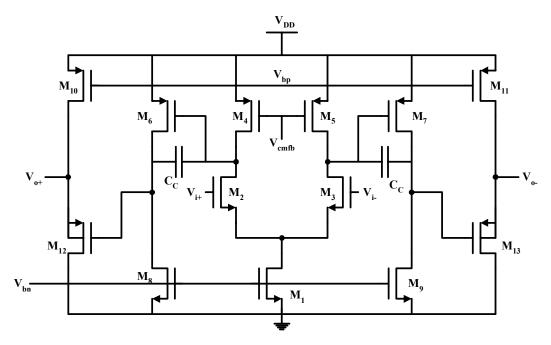

| Fig. 6.19 CMFB circuit                                                                 |

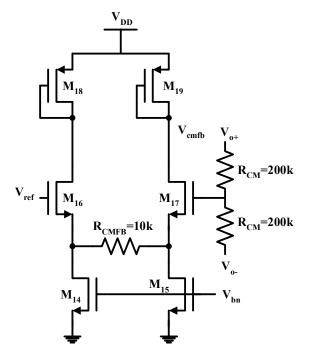

| Fig. 6.20 The buffer circuit                                                                                         | 178 |

|----------------------------------------------------------------------------------------------------------------------|-----|

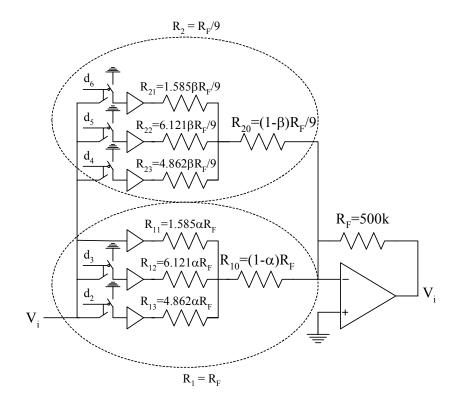

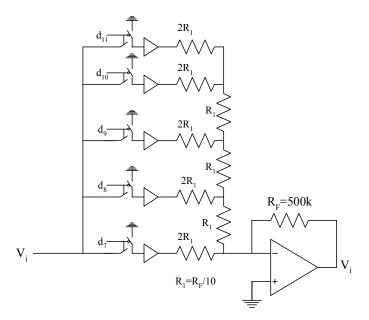

| Fig. 6.21 Second stage VGA circuit                                                                                   | 180 |

| Fig. 6.22 Third stage VGA circuit                                                                                    | 181 |

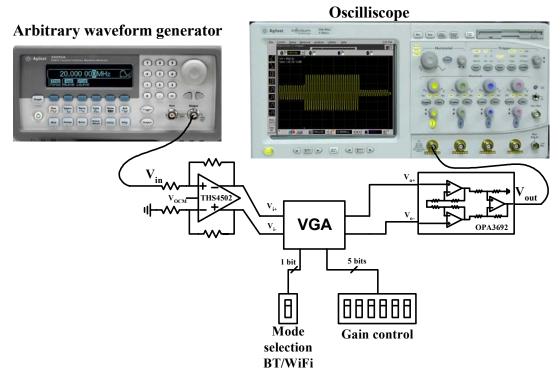

| Fig. 6.23 VGA test setup                                                                                             | 184 |

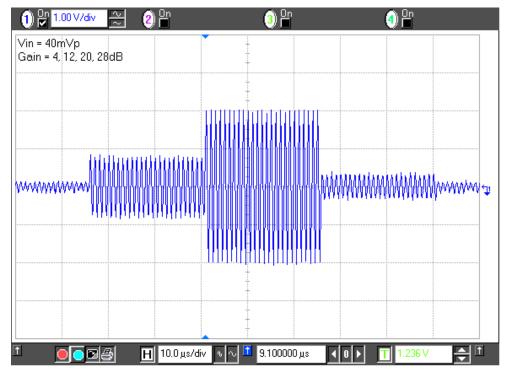

| Fig. 6.24 Time domain response of the VGA                                                                            | 184 |

| Fig. 6.25 Settling time of the VGA                                                                                   | 185 |

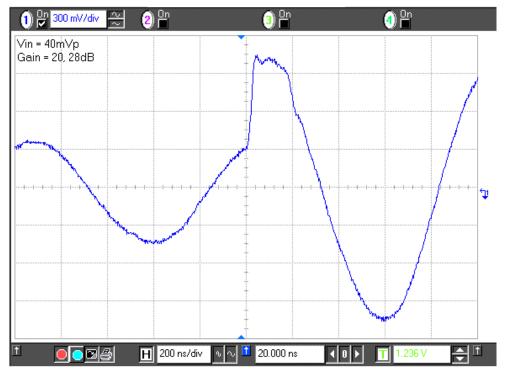

| Fig. 6.26 Frequency response of the VGA at different gain settings                                                   | 185 |

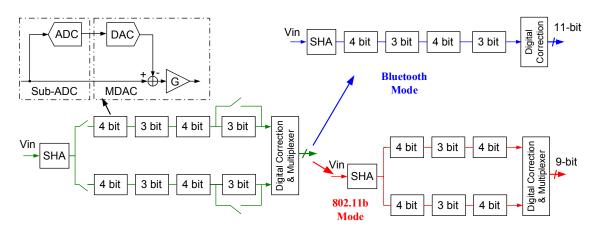

| Fig. 6.27 Time-interleaved pipeline ADC architecture                                                                 | 188 |

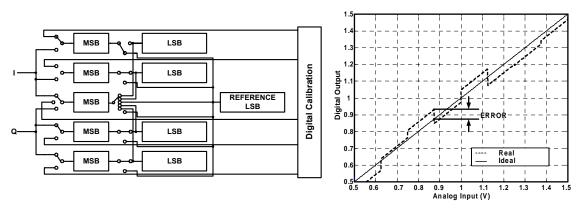

| Fig. 6.28 Online digital calibration                                                                                 | 189 |

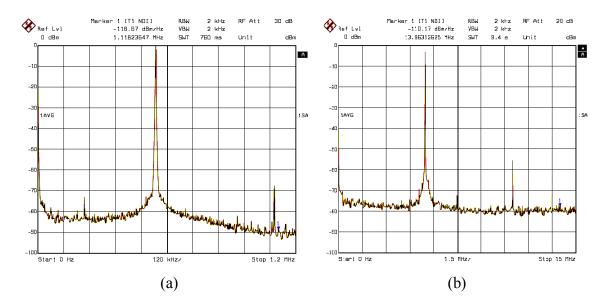

| Fig. 6.29 Measured SNR of the ADC in (a) Bluetooth mode (64dB at 11Msample/s)<br>(b) WiFi mode (48dB at 44Msample/s) |     |

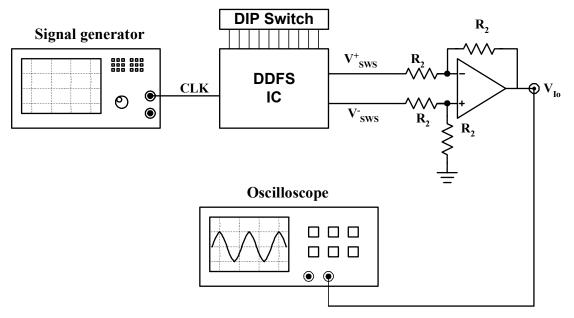

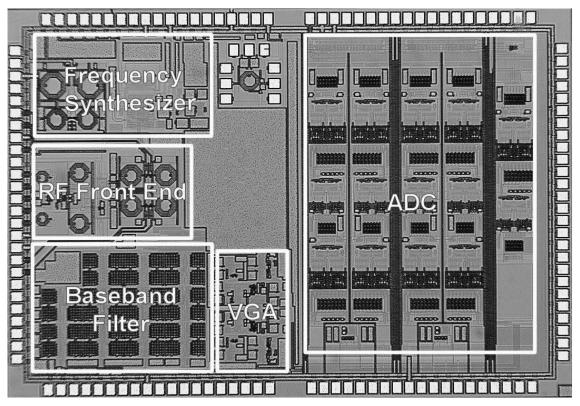

| Fig. 7.1 Chameleon die micrograph                                                                                    | 191 |

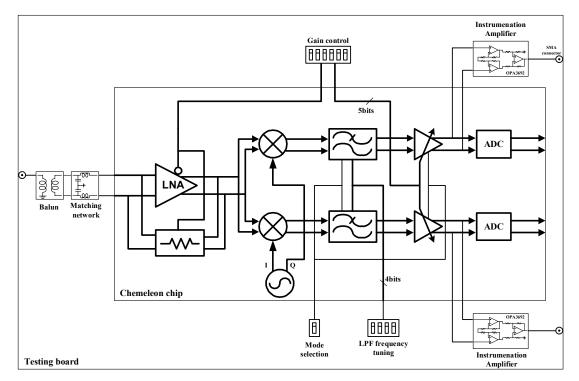

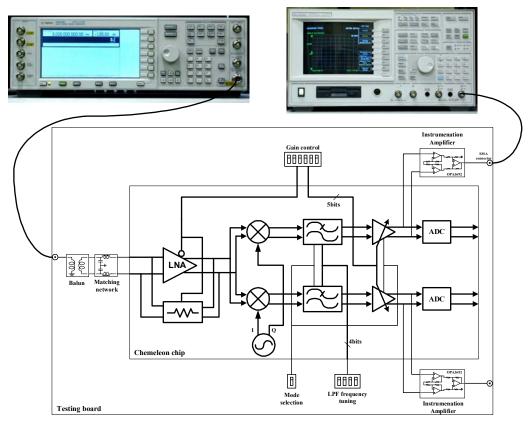

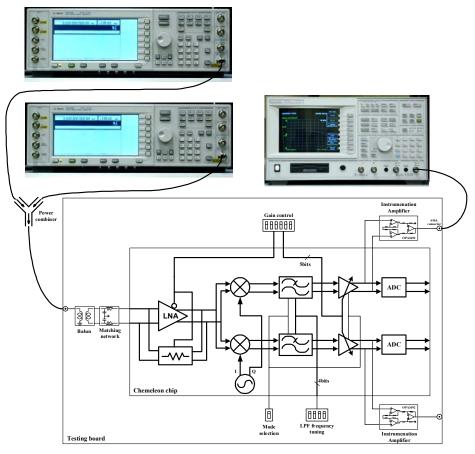

| Fig. 7.2 Simplified block diagram of the testing board for the Chameleon chip                                        | 191 |

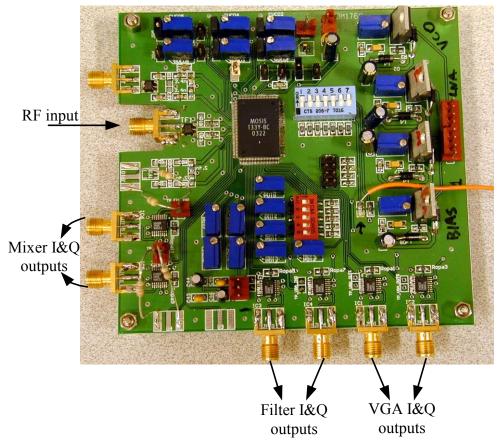

| Fig. 7.3 Photograph of the PCB used to test the Chameleon chip                                                       | 192 |

| Fig. 7.4 Testing setup for NF measurement                                                                            | 194 |

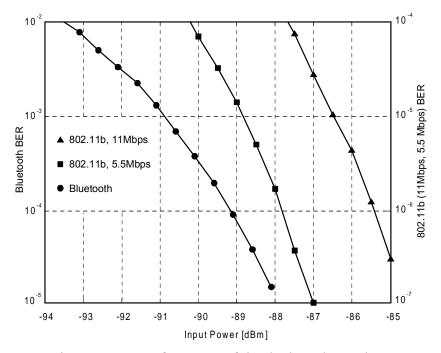

| Fig. 7.5 BER performance of the dual-mode receiver                                                                   | 194 |

| Fig. 7.6 Testing setup for IIP3/IIP2 two-tone test                                                                   | 196 |

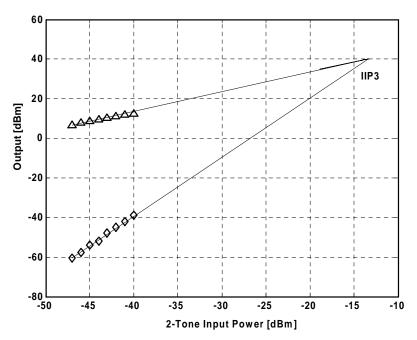

| Fig. 7.7 Receiver IIP3 when LNA is in high gain mode (VGA gain = 12dB)                                               | 196 |

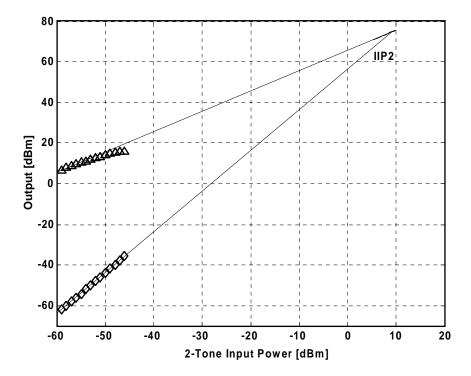

| Fig. 7.8 Receiver IIP2 when LNA is in high gain mode (VGA gain = 24dB)                                               | 197 |

# LIST OF TABLES

|           |                                                                                                         | Page |

|-----------|---------------------------------------------------------------------------------------------------------|------|

| Table 2.1 | Summary of characteristics of some leading WLAN/WPAN standards                                          | 7    |

| Table 2.2 | Bluetooth radio specifications                                                                          | 12   |

| Table 2.3 | 802.11b radio specifications                                                                            | 20   |

| Table 2.4 | DQPSK encoding table                                                                                    | 23   |

| Table 2.5 | 5.5Mb/s CCK encoding table                                                                              | 23   |

| Table 2.6 | QPSK encoding table                                                                                     | 24   |

| Table 3.1 | Summarized filter testing results                                                                       | 68   |

| Table 4.1 | Required values of (M), ( $\Delta R/R_{max}$ ), and corresponding SFDR for different number of segments |      |

| Table 4.2 | Comparison with recently published work                                                                 | 95   |

| Table 5.1 | Receiver parameters and non-idealities used in the BER simulations                                      | 129  |

| Table 5.2 | Summary of receiver specifications                                                                      | 138  |

| Table 5.3 | Receiver gain distribution                                                                              | 140  |

| Table 5.4 | NF, IIP3, and IIP2 distribution in Bluetooth/Wi-Fi mode                                                 | 141  |

| Table 5.5 | Required LO phase noise in Bluetooth mode                                                               | 146  |

| Table 6.1 | Summary of performance                                                                                  | 170  |

| Table 6.2 | Summary of required VGA specifications                                                                  | 171  |

| Table 6.3 | Gain values of the second stage and the corresponding digital inputs                                    | 180  |

| Table 6.4 | Gain values of the third stage and the corresponding digital inputs                                     | 182  |

| Table 6.5 | Gain distribution over the three VGA stages                                                             | 183  |

| Table 6.6 | Summary of VGA experimental results                                                                     | 186  |

| Table 7.1 | Receiver area breakdown                                                                                 | 190  |

| Table 7.2 | Performance summary of the Chameleon receiver                                                           | 198  |

|           |                                                       | Page |

|-----------|-------------------------------------------------------|------|

| Table 7.3 | Power consumption contribution of the receiver blocks | 198  |

#### **CHAPTER I**

#### **INTRODUCTION**

Stimulated by the increased consumer and commercial users demand or wireless communications applications, the advancement of sophistication in wireless circuit design has progressed at an unprecedented speed in recent years. The last few years have witnessed a remarkable miniaturization of portable equipment, a similar extension of battery life, and almost an order of magnitude in retail prices. Two ubiquitous examples of this phenomenon are the wireless local area networks (WLANs) and wireless personal area networks (WPANs).

#### **1.1. Background and Motivation**

Although not well known among everyday wireless communication consumers, commercial wireless communications technology has also experienced a similar impetus in its advancement, both in miniaturization and cost. In portable wireless communication industry it is well known that the design of the RF transceiver is usually the key element that determines the cost, size, and useful battery life of the equipment, as well as how the equipment is used.

One of the major forces sustaining continual research and development in the wireless communication arena is the general user acceptance of wireless communications standards. These standards provide coalescence within the industry to invest in the creation of suitable chip sets for the manufacturing of consumer subscriber units. The resulting high volume drives down the cost of the final product, and industry is able to

This dissertation follows the style of IEEE Journal of Solid-State Circuits.

take advantage of the same trends that have dramatically lowered prices in the PC industry.

The main goal of this dissertation is to present system level and building block level solutions for two of the most widespread short-range communications standards, Bluetooth and 802.11b (Wi-Fi). The motivation is to bridge the gap between the circuit and wireless vision in wireless design. Although the dissertation focuses on Bluetooth and Wi-Fi radio implementations, many design aspects can be generalized to most other radio implementations. The Bluetooth and Wi-Fi standards operate at RF frequency 2.4GHz that is also used by microwave ovens and cordless phones. While Wi-Fi is meant to be wireless version of Ethernet, Bluetooth is designed to replace cables that are used for relatively low speed data transfer. Wi-Fi offers data rates up to 11Mbit/s while Bluetooth's raw data rate is 1Mbits/s. Bluetooth is supposed to be lower cost than Wi-Fi. In this dissertation, the design of a low-IF Bluetooth receiver fabricated in a low cost mainstream CMOS technology is presented. On the other hand, there are many devices that require having both standards implanted. In such cases, the integration of both standards into a single chip would be cheaper than having two separate chip solutions. For this purpose, a dual-mode Bluetooth/Wi-Fi chip solutions is also described.

#### **1.2.** Dissertation Overview

Chapter II presents short-range communications methods. Wired and wireless communications standards are introduced with some focus on wireless standards since it is the topic of the following chapters. In particular, details about Bluetooth and 802.11b (Wi-Fi) standards are given to get the reader acquainted with these standards before presenting the receivers design specifications and implementations in later chapters.

Chapter III presents Bluetooth possible receiver architectures and discusses the pros and cons of each architecture. The proposed low-IF Bluetooth architecture is discussed with some detail. As part of the Bluetooth receiver, detailed design, implementation, and measurement results of channel selection complex filter are presented. In the Bluetooth transmitter, on the other hand, direct digital frequency synthesizer (DDFS) is used as the frequency modulator. DDFS design and implementation is discussed in details in chapter IV. A dual-mode 802.11b/Bluetooth receiver design is presented in chapter V. The dualmode receiver is named "Chameleon" for its ability to change operation modes. An overview of previous dual-mode receiver implementations is included. The proposed direct conversion architecture is presented. Effects of receiver non-idealities of its performance are simulated and quantified. Detailed design procedure starting from standard specifications to receiver specifications to building block requirements is presented. Chapter VI gives the design of the Chameleon receiver building blocks. Variable gain amplifier (VGA) design is presented in details. Measured characteristics of the receiver blocks are also included. In chapter VII, experimental results of the Chameleon receiver are presented. Test setup as well as measurement procedures are illustrated. Finally, chapter VIII summarizes the main contributions of this research work. It should be mentioned that the Bluetooth and Chameleon projects were carried-out by a team of seven Ph.D. students. This dissertation covers partially the entire design process and implementations, but the details of some system aspects and building blocks developed and proposed by the author are emphasized in the essence of this dissertation.

#### **CHAPTER II**

### SHORT-RANGE COMMUNICATION STANDARDS

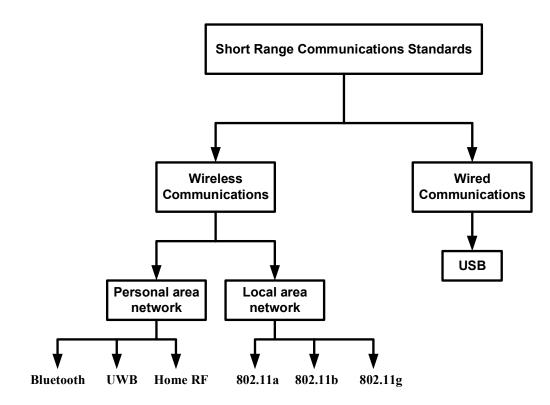

In recent years mobile digital devices such as personal digital assistants (PDAs), mobile phones, digital cameras, and laptops have penetrated the consumer market. All these devices require powerful short-range communication method for data exchange among each other, connections with printers or local area network (LAN) access. Basically, the communication methods can be based on cable connections, radio links, or infrared links as illustrated in Fig. 2.1. Since each has its individual strengths and weaknesses, each found its way into various products.

Fig. 2.1 Short range communication standards

#### 2.1. Short-Range Wired Communications

Data exchange via cables is a well established method; universal serial bus (USB) has become widely used standard interface. USB excels due to its high baud rates up to 480Mb/s, but suffers from its limited mobility due to cable connection. Therefore, USB is best for applications that require stable high-performance connections for transmission of high data volumes, where mobility is not very important. An example of application would be the connection of a videoconferencing camera to your laptop.

#### 2.2. Short-Range Wireless Communications

Contrary to USB, infrared transmission based on the Infrared Data Association (IrDA) standard enables fast connection establishment due to its point-and-shoot characteristic. Together with the high baud rates up to 16Mb/s, this makes transmission well suited to applications that require high performance as hoc point-to-point connections. Examples would include downloading of pictures from your digital camera to your laptop or paying for your meal in your company's cafeteria with your mobile phone via IrDA port. IrDA standards have been there for decades and are widely implemented in laptops, computers and PDAs. But until recently, either the cost was too high, or in the case of infrared, the technology was too difficult to use.

Radio-based short-range wireless (SRW) communication is an alternative class of emerging technologies designed primarily for indoor use over very short distances. It is intended to provide fast (tens or hundreds of megabits per second) and low cost, cablefree connections to the internet. SRW features transmission powers of several microwatts up to milliwatts yielding a communication range between 10 and 100 meter. SRW will provide connectivity to portable devices such as laptops, PDAs, cell phones and others.

Short-range communications standards fall into two broad but overlapping categories: personal area networks (PAN) and local area networks (LAN).

Wireless PAN technologies emphasize low cost and low power consumption, usually at the expense of range and peak speed. In a typical wireless PAN application, a short wireless link, typically under 10 meters, replaces a computer serial cable or USB cable. Standards, such as Bluetooth and HomeRF, have been created to regulate short-range wireless communications. Bluetooth has appeared recently in many mobile devices. Bluetooth can transmit data through solid nonmetal objects and supports a nominal link range of 10cm-10m at a moderate baud rate up to 720kb/s (raw data rate is 1Mb/s) [1]. An optional high power mode in the current specifications allows for ranges up to 100m. Because of the nature of radio, Bluetooth is a point to multipoint communication system, which supports connections of two devices as well as ad hoc networking between several devices. But in order to prevent unauthorized access, Bluetooth requires sophisticated authentication and encryption mechanisms, which hamper fast connection establishment. Therefore, Bluetooth is best for applications that require stable point-to-point or point-tomultipoint connections for data exchange at moderate speeds, where mobility is a key requirement. Ultra-wideband (UWB) is an emerging new technology that shows great potential for SRW applications. Unlike conventional wireless communications systems that are carrier-based, UWB-based communication is baseband. It uses a series of short pulses that spread the energy of the signal from near DC to a few GHz.

Wireless LAN technologies, on the other hand, emphasize a higher peak speed and longer range at the expense of cost and power consumption. Typically, wireless LANs provide wireless links from portable laptops to a wired LAN access point. To date, 802.11b has gained acceptance rapidly as a wireless LAN standard. It has a nominal open-space range of 100m and a peak over-the-air speed of 11Mb/s. Users can expect maximum available speeds of about 5.5Mb/s. Other communication standards offer even higher data rates, like 802.11a and 802.11g. Table 2.1 compares between the leading radio-based short-range communication standards.

| Characteristic             | Bluetooth            | IEEE 802.11b                                | IEEE 802.11g                                | IEEE 802.11a                     | UWB          |

|----------------------------|----------------------|---------------------------------------------|---------------------------------------------|----------------------------------|--------------|

| Standard<br>version/status | V 1.1 (Low-<br>Rate) | IEEE approved                               | Draft                                       | IEEE<br>approved                 | Draft        |

| Maximum<br>distance        | 10-100m              | 100m                                        | 100m                                        | 50m                              | 10m          |

| Frequency allocation       | 2.4GHz<br>(ISM)      | 2.4GHz (ISM)                                | 2.4GHz (ISM)                                | 5GHz (UNII)                      | 3.1-10.6GHz  |

| Number of<br>RF channels   | 79                   | 3                                           | 3                                           | 12 (U.S.)<br>8 (EU)<br>4 (Japan) | 1-15         |

| Modulation                 | GFSK                 | QPSK (CCK)                                  | OFDM                                        | OFDM                             | BPSK, QPSK   |

| Spreading                  | FH                   | DSSS CCK                                    | OFDM                                        | OFDM                             | (Multiband)  |

| Maximum<br>RF power        | 0-20dBm              | 30dBm (U.S.)<br>20dBm (EU)<br>10dBm (Japan) | 30dBm (U.S.)<br>20dBm (EU)<br>10dBm (Japan) | 17dBm,<br>24dBm,<br>30dBm        | -41.3dBm/MHz |

| receiver<br>sensitivity    | -70dBm               | -76dBm<br>for 11Mb/s                        | -74dBm for<br>33Mb/s                        | -65dBm or<br>54Mb/s              | -            |

Table 2.1 Summary of characteristics of some leading WLAN/WPAN standards

#### 2.3. What is Bluetooth?

Bluetooth technology was developed to create a short-range wireless voice and data link between a broad range of devices such as PCs, notebook computers, handhelds and PDAs (hereafter referred to as PDAs), Smart Phones, mobile phones and digital cameras. Consistent with its aim of operating in even the smallest battery-powered devices, the Bluetooth specification calls for a small form factor, low power consumption and low cost. The range and speed of the technology were kept intentionally low so as to ensure maximum battery life and minimum incremental cost for devices incorporating the technology. At its heart, Bluetooth is about creating a Wireless Personal Area Network (WPAN) consisting of all the Bluetooth-enabled electronic devices immediately surrounding a user, wherever that user may be located. This project is supported by a special interest group formed by hundreds of companies that lead technological development.

Specifications of Bluetooth provide the limitations and possibilities of the technology. Bluetooth operates in the 2.4GHz frequencies which is free for use to everyone globally. This frequency provides an effective data rate of 720 Kbit/s. There are multiple classes of transmission strengths which determine the use and the energy efficiency of these devices. The Bluetooth network protocol employs five layers which are implemented by software and hardware. They are:

- (a) Application Programming Interface (API) Allows the operating system (OS) and other applications to access the Bluetooth interface.

- (b) Logical Link Control and Adaptation Protocol (L2CAP) Maintains individual links to other devices in its transmission area.

- (c) Link Manager Responsible for establishing and terminating links and link security.

- (d) Baseband low level tasks including error correction.

- (e) Physical actual radio transmitter and antenna.

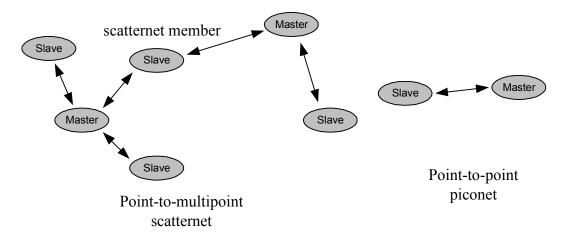

The topology for Bluetooth is very unique and this feature allows it to be completely scalable. The network link can be either point to point or can be point to multipoint, and devices participating in the network can be defined as master or slave. In the simplest network of one master device communicating with one slave device, a piconet is formed and all the bandwidth is dedicated to the link between the two devices. Larger networks can be formed with a single master and up to 7 slaves. The network architecture, however, allows up to 255 slaves to be in a standby mode. Bluetooth manages to achieve its functionality through its modulation and packeting scheme. This is also known as Gaussian Frequency Shift Keying (GFSK).

Bluetooth hops to one of 79 different channels (US and Europe), a repetitive process that keeps errors to a minimum. It is this packet hopping technique which leads to the interference with 802.11b technology. The channel hopping technology of Bluetooth is the secret behind its low power consumption, error correction and the distinct topology that it can support. Bluetooth divides the data to be sent into packets. Each packet is sent within a 625- microsecond slot. A frame is normally defined as a transmit and a receive slot, providing full duplex communication between a master and a slave in one time frame. To avoid noise and other interferences, Bluetooth hops to one of 79 different channels each time frame. The channel that it hops to is determined by the Master ID and the previous channel number. This algorithm is repeated again and again. For example if there is severe noise between 2.408GHz and 2.410GHz, it will be avoided the majority of the time. There is little to no time contention between masters within reach of each other which might result in the masters picking up the same channels at the same time. Because of this channel hopping mechanism, interference is kept to a minimum despite extremely dense scatternets. Master devices can use this frame division to communicate with each slave on the piconet consecutively, with 1 frame each, or they can devote multiple frames to the same slave device, depending on the priority of the job at hand.

Bluetooth was originally conceived by Ericsson in 1994, when they began a study to examine alternatives to cables that linked mobile phone accessories. Ericsson already had a strong capability in short range wireless, having been a key pioneer of the European DECT cordless telecommunications standard, which had been largely based upon their earlier proprietary DCT900 technology. Out of their study was born the specification for Bluetooth wireless.

Bluetooth was named after Harald Blatand (or Bluetooth), a tenth century Danish Viking king who had united and controlled large parts of Scandinavia which are today Denmark and Norway. The name was chosen to highlight the potential of the technology to unify the telecommunications and computing industries - although it was chosen as an internal codename, and it was never at the time expected to survive as the name used in the commercial arena.

In February 1998, the Bluetooth SIG (Special Interest Group) was founded by a small core of major companies - IBM, Intel, Nokia, Toshiba and Ericsson - to work together to develop the technology and to subsequently promote its widespread commercial acceptance.

Six months later the core Promoter Members publicly announced the global SIG and invited other companies to join, with free access to the technology as Bluetooth adopters in return for commitment to support the Bluetooth specification. Adoption was rapid and 1998-1999 saw a boom in the market for Bluetooth conference organizers, and vast amounts of hype regarding the potential of the technology. In December 1999 it was announced that four more major companies had joined the SIG as Promoter Members, viz. Microsoft, Agere Systems (then Lucent), 3Com and Motorola.

The detailed Bluetooth specifications are available in [1]. Table 2.2 is a summary of the key radio specifications.

#### **2.3.1. Bluetooth Operation**

Bluetooth controls timing on the network by designating one of the devices as a master and the other as a slave. The master is simply the unit that initiates the communication link, and the other participants are slaves. When that link is later broken, the master/slave designations no longer apply. In fact, every Bluetooth device has both master and slave hardware. The network itself is termed a piconet, meaning small network. When there is only one slave, then the link is called point-to-point. A master can control up to seven active slaves in a point-to-multipoint configuration. Slaves communicate only with the master, never with each other directly. Timing is such that members of the piconet cannot transmit simultaneously, so these devices will not jam each other. Finally, communication across piconets can be realized if a Bluetooth device can be a slave in more than one piconet, or a master in one and a slave in another. Piconets configured in this manner are called scatternets. These various arrangements are depicted in Fig. 2.2 [2].

| Free                                    | quency Band                       | 2400 – 2483.5 MHz                   |  |  |

|-----------------------------------------|-----------------------------------|-------------------------------------|--|--|

|                                         | Duplex                            | Time Division                       |  |  |

| Ν                                       | Iodulation                        | GFSK (BT = 0.5, Index: 0.28 – 0.35) |  |  |

| Ch                                      | annel Space                       | 1 MHz                               |  |  |

| S                                       | Sensitivity                       | -70 dBm (for 0.1% BER)              |  |  |

| Maxim                                   | um Signal Level                   | -20 dBm                             |  |  |

|                                         | C/I <sub>co-channel</sub>         | 11 dB                               |  |  |

| Interference                            | C/I <sub>1MHz</sub>               | 0 dB                                |  |  |

| interference                            | C/I <sub>2MHz</sub>               | -30 dB                              |  |  |

| Performance                             | C/I>=3MHz                         | -40 dB                              |  |  |

|                                         | C/I <sub>image</sub>              | -9 dB                               |  |  |

|                                         | 30 MHz – 2000 MHz                 | -10 dBm                             |  |  |

| Out of hourd                            | 2000 – 2399 MHz                   | -27 dBm                             |  |  |

| Out-of-band<br>Blocking                 | 2498 – 3000 MHz                   | -27 dBm                             |  |  |

| , i i i i i i i i i i i i i i i i i i i | 3000 MHz – 12.75 GHz              | -10 dBm                             |  |  |

|                                         | Interference Frequency            | 3, 4, 5 MHz                         |  |  |

| Intermodulation                         | Interference Level                | -39 dBm                             |  |  |

| Characteristics                         | Bluetooth Signal Level            | 6 dB above sensitivity              |  |  |

| RSSI                                    | Range                             | -60 dBm±4 + 20±6 dB                 |  |  |

|                                         | Accuracy                          | ±4 dB                               |  |  |

| Radio Frequency<br>Tolerance            | Transmitted Frequency<br>Accuracy | ±75 kHz                             |  |  |

|                                         | Frequency Drift                   | ±25 kHz in one slot                 |  |  |

Table 2.2 Bluetooth radio specifications

Fig. 2.2 Point-to-point and point-to-multipoint and scatternet topology in Bluetooth

#### 2.3.2. Modulation Format

The modulation format is Gaussian Frequency Shift Keying (GFSK) with a bandwidth×bit time product (BT) of 0.5. The modulation index is between 0.28 and 0.35. For the 1Mbps data rate in Bluetooth, frequency deviation can be from  $\pm 140$  to  $\pm 175$ kHz.

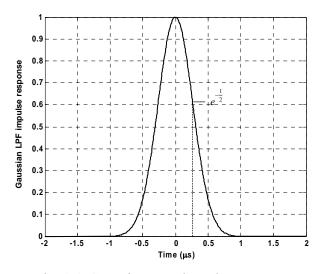

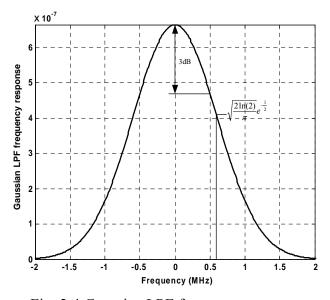

The GFSK signal is generated as follows: First the data stream d(t) is filtered using a Gaussian filter with the following impulse and frequency responses:

$$h(t) = e^{-\frac{1}{2}(\frac{t}{\tau})^2}$$

(2.1)

$$H(\omega) = \tau \cdot \sqrt{2\pi} e^{-\frac{1}{2}(\tau\omega)^2}$$

(2.2)

This is similar to the familiar  $e^{-x^2}$  shape of the Gaussian, or normal, probability density function. In the equation,  $\omega$  is the frequency in rad/sec and  $\tau$  is a constant. A peculiar property of the Gaussian filter is that both its frequency and impulse responses are Gaussian. Figs. 2.3 and 2.4 show the impulse and frequency responses of a Gaussian LPF, respectively. From equation (2.2), the bandwidth of the filter can be written as:

Fig. 2.3 Gaussian LPF impulse response

Fig. 2.4 Gaussian LPF frequency response

$$B = \frac{\sqrt{\ln(2)}}{2\pi} \frac{1}{\tau} \tag{2.3}$$

The Gaussian filter is often specified in terms of its *relative bandwidth*, relative to the bit rate, or BT:

$$BT = (Filter Bandwidth) \cdot (Bit Period) = \frac{Filter Bandwidth}{Bit Rate} = \frac{T_b}{\tau} \frac{\sqrt{\ln(2)}}{2\pi}$$

(2.4)

Higher BT means less intersymbol interference (ISI) but higher bandwidth. As a good compromise, BT=0.5 is specified in Bluetooth standard [1]. So the bandwidth is 500kHz. Therefore, the output of the Gaussian filter is given by:

$$gf(t) = d(t) * e^{-\frac{1}{2}(\frac{\pi}{\sqrt{\ln(2)}}\frac{t}{T_b})^2}$$

(2.5)

Note that both d(t) and gf(t) have a maximum and minimum of 1 and -1 representing 1 and 0 bits, respectively. The Gaussian filtered data gf(t) is then used to frequency modulates the carrier. The output GFSK signal is expressed as:

$$gfsk(t) = \sin(2\pi(f_C + f_d \cdot gf(t)))$$

(2.6)

Where  $f_c$  is the center frequency and  $f_d$  is the frequency deviation. Thus the instantaneous frequency of the GFSK signal transitions between a frequency of  $f_c - f_d$ , representing binary 0, and  $f_c + f_d$ , representing binary 1. In Bluetooth standard [1], the frequency modulation index is specified between 0.28 and 0.35. The modulation index is the ratio between the frequency deviation  $2 f_d$  and the bit rate. So the corresponding  $f_d$  must be between 140 and 175 kHz. Fig. 2.5 shows representative examples of the unfiltered, Gaussian filtered, and Gaussian FSK signal. For illustration purposes, the GFSK signal in Fig. 2.5 has 1MHz center frequency.

#### 2.3.3. Frequency Band

Bluetooth operates in the 2.4GHz Industrial Scientific Medicine (ISM) band. In a vast majority of countries around the world the range of this frequency band is 2400MHz – 2483.5MHz. By utilizing Time Division Duplex (TDD), transmitter and receiver share the same frequency band. The regulators expect lots of devices to be using the same spectrum, so they have set out rules for using ISM bandwidth to make sure that devices

can share the bandwidth. The rules state that you must spread the power of your transmissions across the ISM band somehow. Two main methods are used for spreading out the power: direct sequence spread spectrum (DSSS) and frequency-hopping spread spectrum (FHSS). DSSS smears a transmission across a wide range of frequencies at low power while FHSS spectrum uses a small bandwidth but changes (or hops) frequency after each packet.

Bluetooth uses frequency-hopping spread spectrum as shown in Fig. 2.6. There are 79 channels of 1MHz each. Transmitters change frequencies 1,600 times every second. Occasionally, two piconets may collide on the same channel, but they will just hop off to new frequencies and retransmit any data that was lost. This technique also minimizes the risk that portable phones or baby monitors will disrupt Bluetooth services, since the effect of any interferer on a particular frequency will last only a tiny fraction of a second. Bluetooth uses the master's device ID to algorithmically determine the frequency hopping pattern. This algorithm generates a unique pattern that is quite random and exhibits an extremely long repeat cycle.

Fig. 2.5 GFSK modulation steps

Fig. 2.6 Frequency hopping diagram

#### 2.3.4. Blocking Requirements

The blocking test for Bluetooth is performed by applying a Bluetooth-modulated desired signal 10 dB (for Co-channel, 1 MHz and 2 MHz interference) or 3 dB (for all other frequencies interference) over the reference sensitivity level. Then a Bluetooth-modulated interfering signal is applied to the receiver at discrete increments of 1 MHz from the desired signal with a magnitude as shown in Table 1. Five spurious response frequencies are allowed at frequencies with a distance of equal or greater than 2MHz from the wanted signal. On these spurious response frequencies a relaxed interference requirement C/I = -17 dB shall be met, where C is the carrier power and I is the interference power, respectively. Usually, each channel is allowed a different set of exceptions. If a low-IF receiver is implemented, C/I degrades if I represents the image signal. Spurious response frequency may be used to relax image rejection requirement in Low-IF receivers.

#### 2.3.5. Intermodulation Requirements

The adjacent channel immunity test is performed by applying one static sine wave signal at  $f_1$  with a power level of -39 dBm and one Bluetooth modulated signal at  $f_2$  with

also a power level of -39 dBm to the input of the receiver while a wanted signal 6 dB above the reference sensitivity is applied. The receiver must maintain a 0.1% BER. And be aware when performing this intermodulation test, the effects of noise in receiver channel are also there. It is necessary to make sure C/(I+N) is high enough to maintain required BER, where N is the noise floor level.

#### 2.3.6. Sensitivity

The actual sensitivity level is defined as the input level for which a raw bit error rate (BER) of 0.1% is met. The requirement for a Bluetooth receiver is an actual sensitivity level of -70dBm or better. The power level -70dBm is defined for 50 $\Omega$  impedance. This power can be written in terms of rms voltage and impedance as follows:

$$P(in \, dBm) = 10\log(\text{power in } mW) = 10\log(\frac{V_{ms}^2}{R}) + 30$$

(2.7)

So the power level -70dBm is equivalent to an rms voltage of  $70.7\mu$ Vrms. It is important at this point to clarify the different representations of signal power:

Power in  $dBm \equiv$  decibels relative to one milliwatt.

Power in dBW  $\equiv$  decibels relative to one watt.

Power in  $dBV \equiv$  decibels relative to one volt.

Power in dBc = decibels relative to carrier signal power.

# 2.4. What is 802.11b?

Also known as Wi-Fi (for Wireless Fidelity), 802.11b emerged in 1999 and is the most popular wireless networking standard. Operating in the 2.4GHz radio band, 802.11b is also the current mainstay of the 802.11 family of wireless networking standards

established by the IEEE (Institute of Electrical and Electronics Engineers). 802.11 defines the PHY (physical) and MAC (media access control) layers of the protocol. All of the other layers are identical to the 802.3 (Ethernet) protocol. 802.11a was proposed before 802.11b, hence the designation in 802.11a. 802.11b, however, came to the market first.

802.11a/b uses the unlicensed spectrum for transmission and thus it must use spread spectrum techniques. This process increases the communication channels interference immunity or the processing gain, decreases interference between multiple users and increases the ability to re-use the spectrum. 802.11b uses the 2.400 GHz to 2.483 GHz spectrum. 802.11 is the wireless extension of 802.3 and supports all the underlying protocols that Ethernet uses. An Access Point (AP) is the center of the Basic Service Set (BSS) which may overlap partially, completely or not at all with each other without fear of interfering with functionality. Mobile users can roam from AP to AP and these APs are connected together with other APs using the same ESS\_ID which forms an Extended Service Set (ESS). Each AP has its own MAC and IP addresses and they are fault tolerant when setup with multiple failure points. Addition of capacity to the network can be as simple as adding APs to a new Ethernet port which uses the same ESS\_ID.

802.11b uses DSSS (Direct Sequence Spread Spectrum) to disperse the data frame signal over a relatively wide (30 MHz) portion of the 2.4 GHz band. This results in greater immunity to radio frequency interference as compared to narrowband signaling. Because of the relatively wide DSSS signal, you must set the 802.11b AP to specific channels to avoid channel overlap which might cause a reduction in performance. In order to actually spread the signal, the transmitter combines the Physical Layer Convergence Procedure protocol data unit PLCP (PPDU) with a spreading sequence through the use of a binary adder. PLCP is a frame modification technique used by 802.11b which is out of the scope of discussion in this paper. For higher data rates (5Mbps, 11Mbps) 802.11b uses Complementary code keying (CCK) to provide spreading sequences.

Detailed 802.11b standard specifications can be found in [3]. A summary of Wi-Fi RF specifications is listed in Table 2.3.

| Frequency                     | Band                 | 2400 – 2483.5 MHz                                                           |  |  |

|-------------------------------|----------------------|-----------------------------------------------------------------------------|--|--|

| Duplex                        | X                    | Time Division                                                               |  |  |

| Modulat                       | ion                  | DBPSK/DQPSK/CCK                                                             |  |  |

| Channel Space/ num            | ber of channels      | 25 MHz / 3                                                                  |  |  |

| Sensitivity (1)               | l Mbit/s)            | $-76 \text{ dBm} (\text{for } 0.08 \text{ FER} \equiv 10^{-5} \text{ BER})$ |  |  |

| Maximum Signal Le             | evel (11Mbit/s)      | -10 dBm                                                                     |  |  |

| Adjacent Channel<br>Rejection | C/I <sub>25MHz</sub> | -35 dB                                                                      |  |  |

| Radio Frequency               | Tolerance            | ±60kHz                                                                      |  |  |

Table 2.3 802.11b radio specifications

# 2.4.1. Wi-Fi Operation

Wi-Fi networks operate in two modes: *ad hoc* networks and *infrastructure* networks. Ad hoc network is usually temporary. An ad hoc network is a self-contained group of stations with no connection to a larger LAN or the Internet. It includes two or more wireless stations with no access point or connection to the rest of the world. Ad hoc networks are also called peer-to-peer networks and Independent Basic Service Sets (IBSS). Fig. 2.7 shows a simple ad hoc network. Infrastructure networks have one or more access points, almost always connected to a wired network. Each wireless station exchanges messages and data with the access point, which relays them to other nodes on the wireless network or the wired LAN. Any network that requires a wired connection through an access point to a printer, a file server or an Internet gateway is an infrastructure network. Fig. 2.8 shows an infrastructure network [4].

Fig. 2.7 An ad hoc wireless network with three stations using Wi-Fi

Fig. 2.8 A simple infrastructure network using Wi-Fi

### 2.4.2. Modulation Format

802.11b is an extension of the 802.11 standard that uses two data rates, 1 and 2Mbits/s, use DBPSK and DQPSK modulation formats, respectively. In both data rates, an 11-bit Barker sequence (+1, -1, +1, +1, -1, +1, +1, -1, -1, -1) is used to spread the signal at 11MHz chipping rate. In addition to these two rates, 802.11b provides 5.5 and 11Mbit/s data rates. 8-chip complementary code keying (CCK) is employed as the modulation scheme at 11MHz chipping rate which is the same as the chipping rate in 802.11 standard, thus providing the same occupied channel bandwidth.

Fig. 2.9 Construction of the CCK modulated signal

CCK is a form of M-ary code word modulation where one from a set of M unique signal code words is chosen for transmission [5]. The spreading function for CCK is chosen from a set of M nearly orthogonal vectors by the data word. CCK uses one vector from a set of 64 complex (QPSK) vectors for the symbol and thereby modulates 6-bits (one-of-64) on each 8 chip spreading code symbol. Two additional bits are sent by QPSK modulating the whole code symbol and this thus modulates 8-bits onto each symbol. Fig. 2.9 illustrates how the CCK modulated signal is constructed from the 8-bits data word.

The following formula is used to derive the CCK code words and is used for spreading both the 5.5Mb/s and 11Mb/s:

$$C = e^{j\varphi_1} \times \left\{ e^{j(\varphi_2 + \varphi_3 + \varphi_4)}, e^{j(\varphi_3 + \varphi_4)}, e^{j(\varphi_2 + \varphi_4)}, -e^{j(\varphi_4)}, e^{j(\varphi_2 + \varphi_3)}, e^{j(\varphi_3)}, -e^{j(\varphi_2)}, 1 \right\}$$

(2.8)

Note that  $\varphi_1$  is added to all code chips,  $\varphi_2$  is added to all odd code chips,  $\varphi_3$  is added to all odd pairs of code chips, and  $\varphi_4$  is added to all odd quads of code chips. The phases  $\varphi_1$ ,  $\varphi_2$ ,  $\varphi_3$ ,  $\varphi_4$  are obtained in the 5.5Mb/s and 11Mb/s cases as follows:

## 2.4.2.1. CCK 5.5Mb/s Modulation

Four input bits,  $d_0 - d_3$ , are used to encode CCK phases  $\varphi_1 - \varphi_4$ . The two bits  $d_0 - d_1$  encode  $\varphi_1$  based on DQPSK as shown in table 2.4. The data di-bits  $d_2$  and  $d_3$  CCK encode the basic symbol, as specified in Table 2.5. This table is derived from the formula above by setting  $\varphi_2 = (d2 \times \pi) + \pi/2$ ,  $\varphi_3 = 0$ , and  $\varphi_4 = d3 \times \pi$ .

Table 2.4 DQPSK encoding table

| $d_0 \ d_1$ | Even symbols phase change | Odd symbols phase change |  |  |  |

|-------------|---------------------------|--------------------------|--|--|--|

| 00          | 0                         | π                        |  |  |  |

| 01          | $\pi/2$                   | -π/2                     |  |  |  |

| 11          | π                         | 0                        |  |  |  |

| 10          | -π/2                      | $\pi/2$                  |  |  |  |

Table 2.5 5.5Mb/s CCK encoding table

| $d_2 d_3$ | <b>c</b> <sub>1</sub> | <b>c</b> <sub>2</sub> | <b>c</b> <sub>3</sub> | <b>c</b> <sub>4</sub> | <b>c</b> <sub>5</sub> | c <sub>6</sub> | <b>c</b> <sub>7</sub> | c <sub>8</sub> |

|-----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|----------------|

| 00        | j                     | 1                     | j                     | -1                    | j                     | 1              | -j                    | 1              |

| 01        | -j                    | -1                    | -j                    | 1                     | j                     | 1              | -j                    | 1              |

| 10        | -j                    | 1                     | -j                    | -1                    | -j                    | 1              | j                     | 1              |

| 11        | j                     | -1                    | j                     | 1                     | -j                    | 1              | j                     | 1              |

| Di-bit pattern (d <sub>i</sub> d <sub>i+1</sub> ) | Phase   |  |  |

|---------------------------------------------------|---------|--|--|

| 00                                                | 0       |  |  |

| 01                                                | $\pi/2$ |  |  |

| 10                                                | π       |  |  |

| 11                                                | -π/2    |  |  |

Table 2.6 QPSK encoding table

## 2.4.2.2. CCK 11Mb/s Modulation

At 11 Mb/s, 8 bits are transmitted per symbol. The first di-bit ( $d_0 d_1$ ) encodes  $\varphi_1$  based on DQPSK as shown in table 2.4. The phase change of  $\varphi_1$  is relative to the phase  $\varphi_1$  of the preceding symbol. The data dibits ( $d_2$ ,  $d_3$ ), ( $d_4$ ,  $d_5$ ), and ( $d_6$ ,  $d_7$ ) encode  $\varphi_2$ ,  $\varphi_3$ , and  $\varphi_4$ , respectively, based on QPSK as specified in Table 2.6.

# 2.4.3. Operating Frequency Range

Wi-Fi operates in the same frequency range 2.4-2.4385GHz as Bluetooth.

# 2.4.4. Blocking Requirements

Adjacent channel rejection is defined between any two channels with >25 MHz separation in each channel group. The adjacent channel rejection should be equal to or better than 35 dB using

11 Mbit/s CCK modulation for both the desired and adjacent channels. The blocking test is done at an input signal level 6 dB greater than the sensitivity level.

## 2.4.5. Intermodulation Requirements