## A Thesis Submitted for the Degree of PhD at the University of Warwick

#### **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/80142

## **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# Evaluating Technologies and Techniques for Transitioning Hydrodynamics Applications to Future Generations of Supercomputers

by

## Andrew Colin Mallinson

A thesis submitted to The University of Warwick in partial fulfilment of the requirements  $\qquad \qquad \text{for admission to the degree of}$

Doctor of Philosophy

## Department of Computer Science

The University of Warwick

May 2016

### **Abstract**

Current supercomputer development trends present severe challenges for scientific codebases. Moore's law continues to hold, however, power constraints have brought an end to Dennard scaling, forcing significant increases in overall concurrency. The performance imbalance between the processor and memory sub-systems is also increasing and architectures are becoming significantly more complex. Scientific computing centres need to harness more computational resources in order to facilitate new scientific insights and maintaining their codebases requires significant investments. Centres therefore have to decide how best to develop their applications to take advantage of future architectures. To prevent vendor "lock-in" and maximise investments, achieving portable-performance across multiple architectures is also a significant concern.

Efficiently scaling applications will be essential for achieving improvements in science and the MPI (Message Passing Interface) only model is reaching its scalability limits. Hybrid approaches which utilise shared memory programming models are a promising approach for improving scalability. Additionally PGAS (Partitioned Global Address Space) models have the potential to address productivity and scalability concerns. Furthermore, OpenCL has been developed with the aim of enabling applications to achieve portable-performance across a range of heterogeneous architectures.

This research examines approaches for achieving greater levels of performance for hydrodynamics applications on future supercomputer architectures. The development of a Lagrangian-Eulerian hydrodynamics application is presented together with its utility for conducting such research. Strategies for improving application performance, including PGAS- and hybrid-based approaches are evaluated at large node-counts on several state-of-the-art architectures. Techniques to maximise the performance and scalability of OpenMP-based hy-

brid implementations are presented together with an assessment of how these constructs should be combined with existing approaches. OpenCL is evaluated as an additional technology for implementing a hybrid programming model and improving performance-portability. To enhance productivity several tools for automatically hybridising applications and improving process-to-topology mappings are evaluated.

Power constraints are starting to limit supercomputer deployments, potentially necessitating the use of more energy efficient technologies. Advanced processor architectures are therefore evaluated as future candidate technologies, together with several application optimisations which will likely be necessary. An FPGA-based solution is examined, including an analysis of how effectively it can be utilised via a high-level programming model, as an alternative to the specialist approaches which currently limit the applicability of this technology.

## Acknowledgements

The completion of this thesis, and the research work contained within it, was made possible by the support of a number of people. Their academic advice and personal support throughout my time at Warwick, has helped to maintain my research focus.

I would like to thank AWE plc for funding this work. Specifically Andy Herdman and Wayne Gaudin for providing guidance throughout; you have both been a pleasure to work for.

My beloved partner Ruth, to whom I am eternally grateful, deserves huge credit for all her love and support during my Ph.D. without which I would not have been able to complete this work. Additionally, for their continued and invaluable support throughout, I would also like to thank my Mum, Dad, Sister and Brother-in-law.

Within my research group at Warwick I am very grateful to Dr. Oliver Perks, David Beckingsale, Robert Bird, Dr. John Pennycook and James Davis for their advice and constructive critiques of my ideas. Finally, I would also like to thank Prof. Stephen Jarvis for accepting me onto the Ph.D. programme and for supervising my research.

## **Declarations**

This thesis is submitted to the University of Warwick in support of the author's application for the degree of Doctor of Philosophy. It has been composed by the author and has not been submitted in any previous application for any degree.

The work presented (including data generated and data analysis) was carried out by the author except in the cases outlined below:

• The collection of the execution times of the OpenCL version of CloverLeaf on the Teller platform at SNL, was performed by Andy Herdman of AWE plc.

Parts of this thesis have been previously published by the author in the following:

- A. C. Mallinson, D. A. Beckingsale, W. P. Gaudin, J. A. Herdman, J. M. Levesque and S. A. Jarvis. CloverLeaf: Preparing Hydrodynamics Codes for Exascale, In *Proceedings of the Cray User Group 2013* (CUG), Napa Valley, USA, May 2013 [132].

- A. C. Mallinson, D. A. Beckingsale, W. P. Gaudin, J. A. Herdman and S. A. Jarvis. Towards Portable Performance for Explicit Hydrodynamics Codes, In *Proceedings of the International Workshop on OpenCL 2013* (IWOCL), Atlanta, USA, May 2013 [131].

- 3. W. P. Gaudin, A. C. Mallinson, O. Perks, J. A. Herdman, D. A. Beckingsale, J. M. Levesque, M. Boulton, S. McIntosh-Smith and S. A. Jarvis. Optimising Hydrodynamics applications for the Cray XC30 with the application tool suite, In *Proceedings of the Cray User Group 2014* (CUG), Lugano, Switzerland, May 2014 [69]. Awarded best research paper.

- 4. A. C. Mallinson, W. P. Gaudin, J. A. Herdman and S. A. Jarvis. Experiences at scale with PGAS versions of a Hydrodynamics Application, In Proceedings of the 8<sup>th</sup> International Conference on Partitioned Global Address Space Programming Models (PGAS2014), Eugene, Oregon, USA, Oct 2014 [133].

- J. A. Herdman, W. P. Gaudin, D. A. Beckingsale, A. C. Mallinson, M. Boulton, S. McIntosh-Smith and S. A. Jarvis. Accelerating Hydrocodes with OpenACC, OpenCL and CUDA, In Proceedings of the 3rd International Workshop on Performance Modelling, Benchmarking and Simulation, (PMBS12), Salt Lake City, Utah, USA, Nov 2012 [104].

# Sponsorship and Grants

The research presented in this thesis was made possible by the support of the following benefactors and sources:

$\bullet\,$  UK Atomic Weapons Establishment, under grants:

"The Production of Predictive Models for Future Computing

Requirements" (CDK0660)

"AWE Technical Outreach Programme" (CDK0724)

"AWE CASE studentship" (ref. 30197965)

## Abbreviations

**ADRES** Architecture for Dynamically Reconfigurable Embedded Systems AMDAdvanced Micro Devices APIApplication Programming Interface APUAccelerated Processing Unit **ASIC** Application Specific Integrated Circuit AVXAdvanced Vector Extensions  $\mathbf{AWE}$ Atomic Weapons Establishment, UK BG/QBlue Gene Q BSPBulk Synchronous Parallel CAAR Center for Application Acceleration Readiness CAF Co-array Fortran CCECray Compilation Environment **CFD** Computational Fluid Dynamics Central Processing Unit CPU**CUDA** Compute Unified Device Architecture **DARPA** Defence Advanced Research Projects Agency DDR Double Data Rate DMADirect Memory Access DOD Department of Defence DOE Department of Energy DRAM Dynamic Random Access Memory DSP Digital Signal Processor Electronic Design Automation EDA $\mathbf{ESL}$ Electric System Level FLOP/s Floating-Point Operations per Second **FPGA** Field Programmable Gate Array (GP)GPU (General Purpose) Graphics Processing Unit

HDD Hard Disk Drive

HDL Hardware Description Language

HMC Hybrid Memory Cube

HMPP Hybrid Multicore Parallel Programming

**HPC** High-Performance Computing

IB InfiniBand

IBM International Business Machines Corporation

**IEEE** Institute of Electrical Engineers

IFE Inertial Fusion Energy

LANL Los Alamos National Laboratory

LLC Last Level Cache

LLNL Lawrence Livermore National Laboratory

LLVM Low Level Virtual Machine

LUT Look Up Table

MPI Message Passing Interface

MTTI Mean Time to Interruption

MW Megawatt

NIC Network Interface Card

NIF National Ignition Facility, USA

NOC Network on a chip

NUMA Non-Uniform Memory Access

ORNL Oak Ridge National Laboratory

OS Operating System

PCIe Peripheral Component Interconnect Express

PGAS Partitioned Global Address Space

PGI Portland Group Incorporated

PRAM Parallel Random Access Machine

PTX Parallel Thread Execution

RAM Random Access Memory

RDMARemote Direct Memory Access RTLRegister Transfer Level  $\mathbf{SDK}$ Software Development Kit SIMD Single Instruction Multiple Data  $\mathbf{SMP}$ Symmetric Multi-Processor  $\mathbf{SNL}$ Sandia National Laboratories SOCSystem on a Chip Smoothed Particle Hydrodynamics SPH **SPMD** Single Program Multiple Data SSEStreaming SIMD Extensions TDPTotal Power Draw  $\mathbf{TLB}$ Translation Lookaside Buffer

Very High Speed Integrated Circuit Hardware Description Language

Unified Parallel C

UPC

VHDL

## **Definitions**

#### Collective

Refers to a communication event, within parallel application programming, in which more than two end-points are involved. Communication of this type can potentially involve multiple source or destination end-points (or both).

#### Computational Kernel

A collection of application program code, such as multiple loop-block structures, which has been logically co-located within the same program function or subroutine, and collectively performs a particular well-defined task or operation.

#### **Compute Bound**

Is a term used to refer to one or a series of operations whose overall runtime is dominated by the length of time required to process the particular instructions and associated data-values within the computational device.

#### Exascale

Is a term which refers to high performance computing systems which are capable of executing a thousand Petaflops or a quintillion  $(10^{18})$  floating point operations per second.

#### **Elemental Function**

Denotes a function which operates on a scalar argument or single array element but can also be applied in parallel to a series of, potentially multi-dimensional, array elements.

#### **Energy to Solution**

Refers to the total energy (Joules) consumed by an application during the course of its execution on a particular processing architecture.

#### Global Address Space

In parallel programming this relates to the ability of any thread of execution to directly access any memory location, which as been designated as being globally accessible, within the overall parallel application.

#### **Halo Cells**

The design of parallel applications often involves the decomposition of the overall problem domain across multiple processors, such that each process is responsible for a distinct subset of the domain. The operations performed by each processor, however, often require data-values from parts of the problem domain which are managed by other processes within the overall computation. This frequently occurs on the boundary between the contiguous domains managed by different processes. To minimise the accesses to remote memory locations on other processes, boundary data cells from logically adjacent processes are often replicated in a layer of cells around the domain managed by each process. This additional layer of cells is referred to as a "halo" region and can be of varying depths depending on the requirements of the algorithm currently being executed.

#### Kernel Driver

A program which is able to unit-test a particular *computational kernel* routine in terms of both its overall performance and correctness.

#### Memory Bound

Is a term used to refer to one or a series of operations whose overall runtime is dominated by the length of time required to load (or store) the particular instructions and associated data-values from the memory sub-system rather than to actually process them within the computational device.

#### Network On a Chip (NOC)

Is a term used to refer to the inclusion of a dedicated interconnection network between the processing components of a System On a Chip design i.e. within the same integrated circuit.

#### Non-Uniform Memory Access (NUMA)

Refers to a particular design of multi-processing system in which the time to access individual memory locations varies depending on the proximity of the particular memory locations to the accessing processor. A "NUMA" region is

used to refer to a collection of memory locations which all have the same access time relative to a particular processor.

#### Parallel Speedup

Is calculated by the time recorded for the execution of the application in serial divided by the execution time of the application when run in parallel.

$$S(parallel) = \frac{T(serial)}{T(parallel)} \tag{1}$$

#### Petascale

Is a term which refers to high performance computing systems which are capable of executing one quadrillion  $(10^{15})$  floating point operations per second.

#### Point-to-Point

Refers to a communication event, within parallel application programming, between a distinct pair of end-points i.e. with a well-defined source and a destination.

#### Portable Performance

Refers to the goal of achieving optimal or acceptable levels of performance across multiple different types of system architectures from a single source code representative of an application, that is without including optimisations or modifications for specific architectures.

#### Remote Direct Memory Access (RDMA)

Is a form of communication in which the initiating CPU sends information regarding the message transfer (length, remote memory address etc) to its local NIC, which then manages the actual data transfer across the network [22]. Communication is one-sided and consequently the remote CPU is not involved in the data transmission, the network hardware at the destination handles all of the processing involved in the receipt of the data and committing it to memory.

#### Strong Scaling

Solving a fixed problem size by utilising an increasing amount of computational resources.

#### System On a Chip (SOC)

Is a term used to refer to an integrated circuit that incorporates all of the necessary components required for a computational device within a single chip substrate.

#### Wall-clock

A measure of application performance (the actual length of execution time) recorded by an observer external to the application. This is different to CPU or user time which relates to the total amount of time processor devices actually spend executing applications.

#### Weak Scaling

In these studies the overall simulated problem size is increased proportionally in line with the computational resources employed in the computation.

# Contents

| Al | Abstract             |                                   |              |  |  |

|----|----------------------|-----------------------------------|--------------|--|--|

| A  | cknov                | wledgements                       | iv           |  |  |

| De | eclar                | ations                            | $\mathbf{v}$ |  |  |

| Sp | onso                 | orship and Grants                 | <b>ii</b>    |  |  |

| Al | bbre                 | viations                          | iii          |  |  |

| De | efinit               | ions                              | хi           |  |  |

| Li | st of                | Figures                           | cii          |  |  |

| Li | List of Tables xxiii |                                   |              |  |  |

| 1  | Intr                 | roduction 1                       |              |  |  |

|    | 1.1                  | Motivations and Problem Statement | 3            |  |  |

|    | 1.2                  | Domain                            | 5            |  |  |

|    | 1.3                  | Research Questions and Hypothesis | 6            |  |  |

|    | 1.4                  | Research Methodology              | 7            |  |  |

|    | 1.5                  | Thesis Contributions              | 10           |  |  |

|    | 1.6                  | CloverLeaf                        | 13           |  |  |

|    |                      | 1.6.1 Implementation              | 13           |  |  |

|    | 1.7                  | Thesis Structure                  | 15           |  |  |

|    | 1.8                  | Project Availability              | 16           |  |  |

| 2  | Bac                  | kground Information               | L <b>8</b>   |  |  |

|    | 2.1                  | Hardware Background and Trends    | 18           |  |  |

|    |                      | 2.1.1 Power Consumption           | 18           |  |  |

|   |      | 2.1.2  | HPC Interconnect Technology                                        | 19 |

|---|------|--------|--------------------------------------------------------------------|----|

|   |      | 2.1.3  | Processor Subsystem Technology                                     | 21 |

|   |      | 2.1.4  | Memory Subsystem Technology                                        | 23 |

|   | 2.2  | Softwa | re Background and Trends                                           | 24 |

|   |      | 2.2.1  | OpenMP                                                             | 24 |

|   |      | 2.2.2  | OpenCL                                                             | 25 |

|   |      | 2.2.3  | CUDA                                                               | 26 |

|   |      | 2.2.4  | OpenACC                                                            | 26 |

|   |      | 2.2.5  | VHDL and Verilog                                                   | 27 |

|   |      | 2.2.6  | BSP Programming Model                                              | 28 |

|   |      | 2.2.7  | MPI Programming Model                                              | 29 |

|   |      | 2.2.8  | PGAS Programming Model                                             | 29 |

|   |      | 2.2.9  | Hybrid Programming Models                                          | 32 |

|   |      | 2.2.10 | Current & Future Trends $\dots \dots \dots \dots$ .                | 33 |

|   | 2.3  | Hydro  | dynamics Mathematical Foundations & Applications $\dots$           | 34 |

|   |      | 2.3.1  | Euler's Equations of Compressible Fluid Dynamics                   | 34 |

|   |      | 2.3.2  | Motivations for Improving the State-of-the-art $\ \ldots \ \ldots$ | 36 |

|   | 2.4  | Summ   | ary                                                                | 37 |

| 3 | Intr | a-Nod  | e Performance Optimisations                                        | 39 |

|   | 3.1  | Relate | d Work                                                             | 39 |

|   | 3.2  | OpenN  | MP-based Optimisations Examined                                    | 40 |

|   |      | 3.2.1  | First-touch Memory Placement                                       | 40 |

|   |      | 3.2.2  | Array-of-arrays Data Structure                                     | 42 |

|   |      | 3.2.3  | Data Alignment & Cache Line Padding                                | 43 |

|   |      | 3.2.4  | High-level OpenMP Parallel Region                                  | 43 |

|   |      | 3.2.5  | Duplicating Constant Data per NUMA-region                          | 44 |

|   |      | 3.2.6  | Explicit Loop Schedules                                            | 44 |

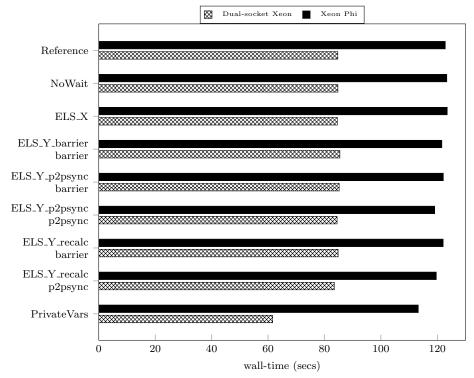

|   |      | 3.2.7  | Inter-thread Synchronisation Elimination                           | 45 |

|   |      | 3.2.8  | Reducing Inter-thread Synchronisation                              | 45 |

|   |     | 3.2.9   | Thread-private Temporary Variables                | 47  |

|---|-----|---------|---------------------------------------------------|-----|

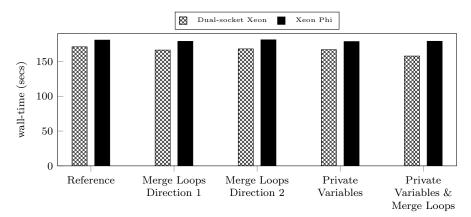

|   |     | 3.2.10  | Loop Vectorisation                                | 48  |

|   |     | 3.2.11  | Accelerate Kernel Optimisations                   | 49  |

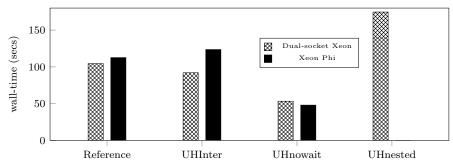

|   |     | 3.2.12  | Update-Halo Kernel Optimisations                  | 49  |

|   |     | 3.2.13  | Automatic Application Hybridisation               | 51  |

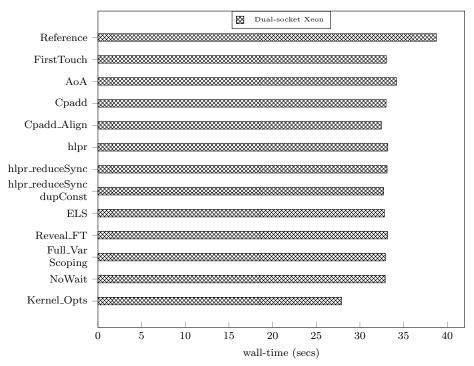

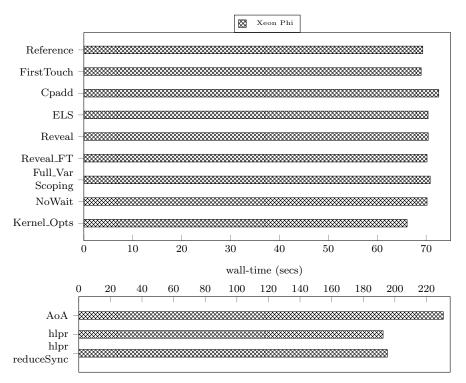

|   | 3.3 | Result  | s Analysis                                        | 51  |

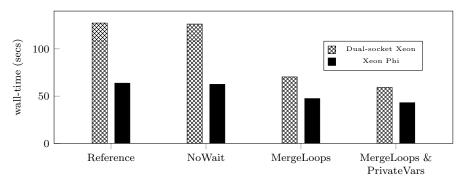

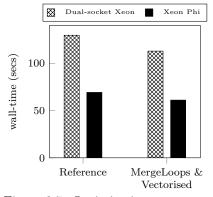

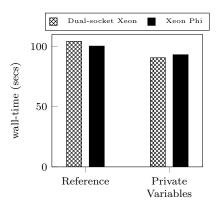

|   |     | 3.3.1   | Individual Kernel Optimisation Analysis           | 52  |

|   |     | 3.3.2   | Application Performance Analysis                  | 58  |

|   | 3.4 | Summa   | ary                                               | 63  |

| 4 | Ach | ieving  | Efficient Application Execution at Extreme Scale  | 66  |

|   | 4.1 | Relate  | d Work                                            | 66  |

|   | 4.2 | MPI-o   | nly Based Versions                                | 68  |

|   |     | 4.2.1   | Optimisations Examined                            | 69  |

|   |     | 4.2.2   | Power Consumption Instrumentation                 | 76  |

|   | 4.3 | Hybrid  | l (MPI+OpenMP) Based Versions                     | 77  |

|   |     | 4.3.1   | Optimisations Examined                            | 78  |

|   | 4.4 | Results | s Analysis                                        | 80  |

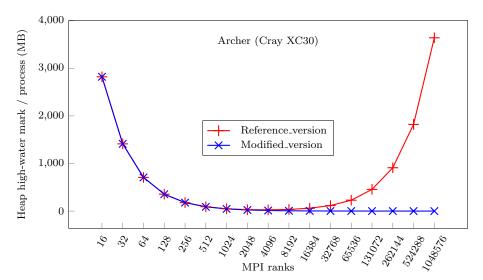

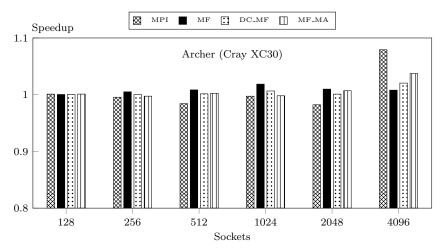

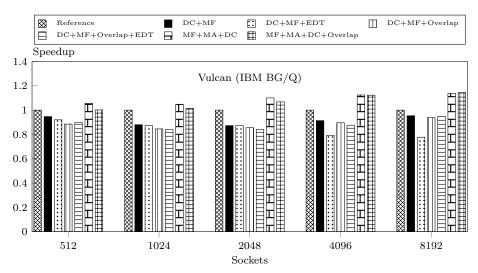

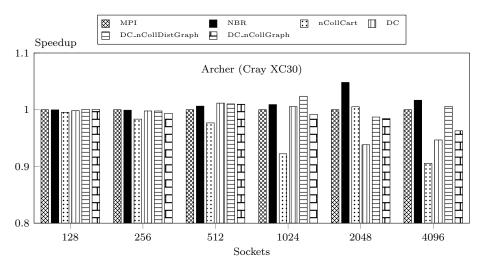

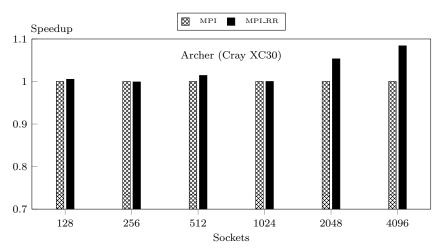

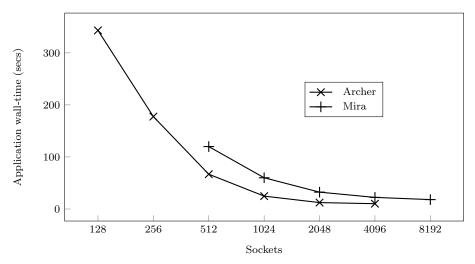

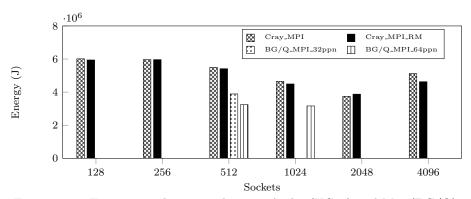

|   |     | 4.4.1   | MPI-only Results Analysis                         | 81  |

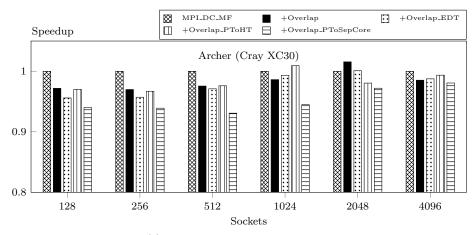

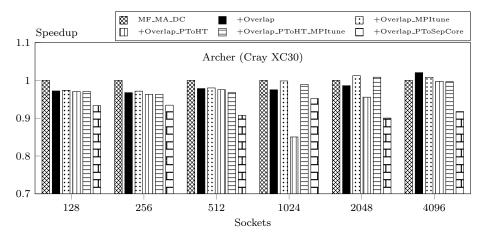

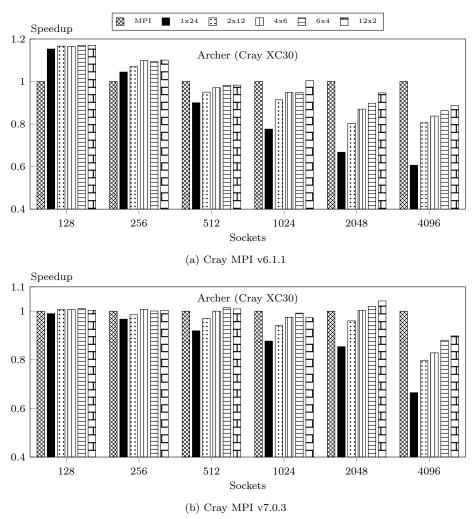

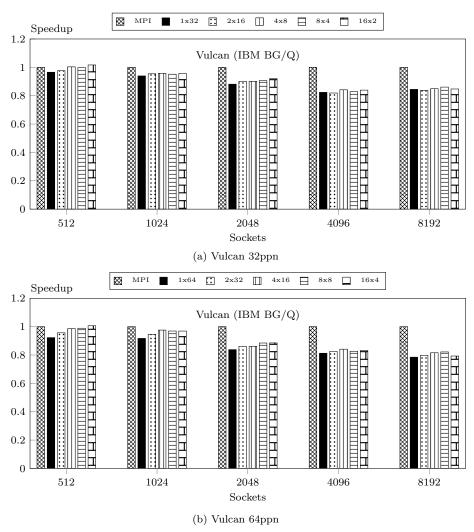

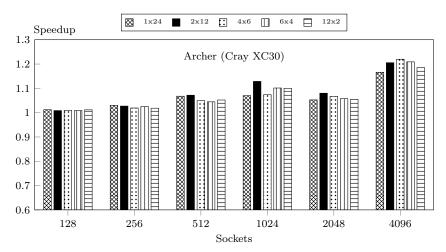

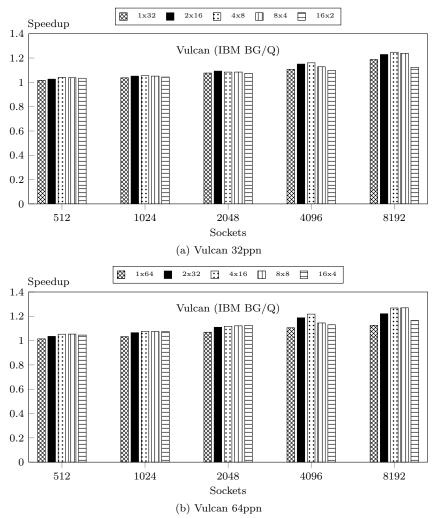

|   |     | 4.4.2   | Hybrid (MPI+OpenMP)<br>Results Analysis           | 95  |

|   | 4.5 | Summa   | ary                                               | 107 |

| 5 | Eva | luating | g the Utility of PGAS-based Approaches            | 111 |

|   | 5.1 | Relate  | d Work                                            | 111 |

|   | 5.2 | SHME    | M Implementation                                  | 113 |

|   | 5.3 | CAF I   | mplementation                                     | 114 |

|   | 5.4 | Results | s Analysis                                        | 116 |

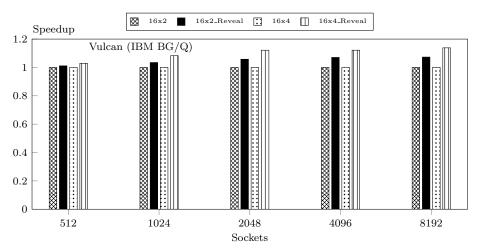

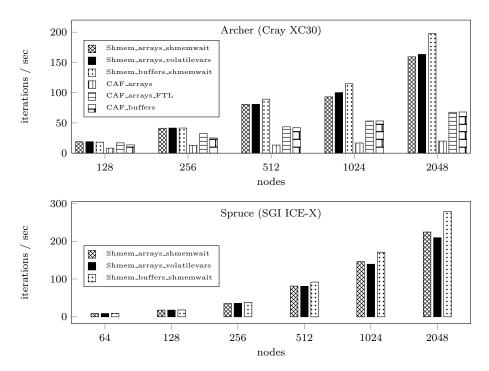

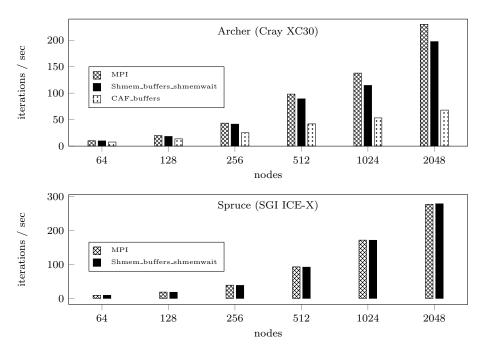

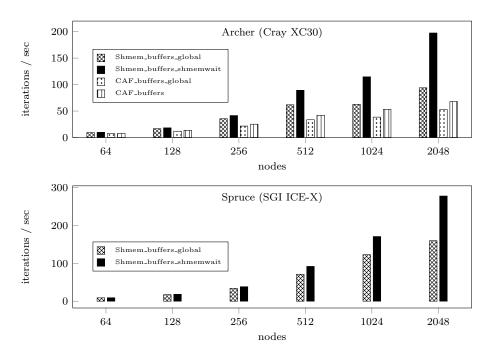

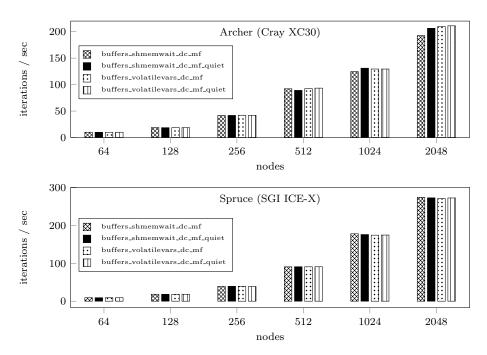

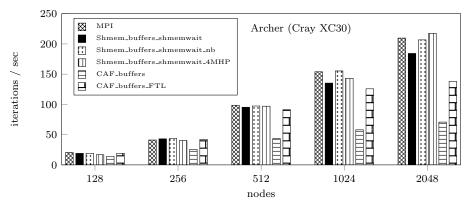

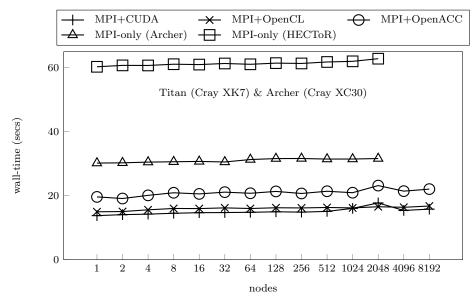

|   |     | 5.4.1   | First Strong-scaling Experiment Results Analysis  | 117 |

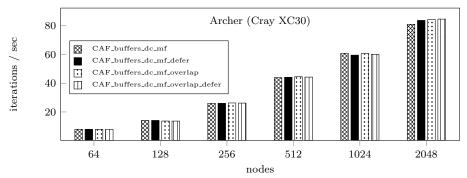

|   |     | 5.4.2   | Second Strong-scaling Experiment Results Analysis | 123 |

|   | 5.5 | Summa   | ary                                               | 124 |

| 6 | Por | table l | Performance Through OpenCL                | 126 |

|---|-----|---------|-------------------------------------------|-----|

|   | 6.1 | Relate  | ed Work                                   | 126 |

|   | 6.2 | Open    | CL Implementation                         | 128 |

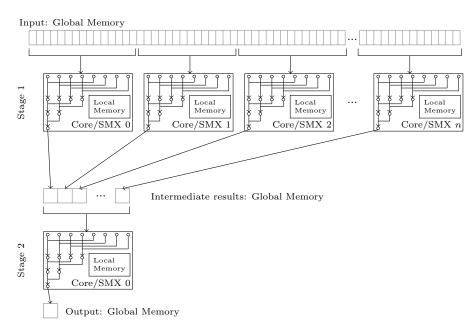

|   |     | 6.2.1   | Reduction Operators                       | 130 |

|   |     | 6.2.2   | Optimisations                             | 133 |

|   | 6.3 | Result  | ts Analysis                               | 139 |

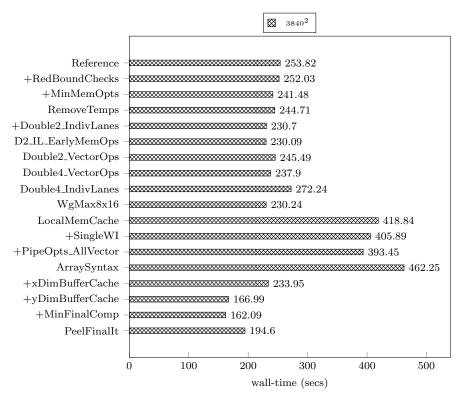

|   |     | 6.3.1   | Optimisations Analysis                    | 140 |

|   |     | 6.3.2   | Single-node Performance Analysis          | 151 |

|   |     | 6.3.3   | Multi-node Performance Analysis           | 154 |

|   | 6.4 | Summ    | nary                                      | 159 |

| 7 | Eva | luating | g FPGAs as Low Power Processing Solutions | 162 |

|   | 7.1 | Relate  | ed Work                                   | 162 |

|   | 7.2 | FPGA    | A Targeted OpenCL Implementations         | 164 |

|   |     | 7.2.1   | Optimisations Examined                    | 164 |

|   | 7.3 | Result  | ts Analysis                               | 175 |

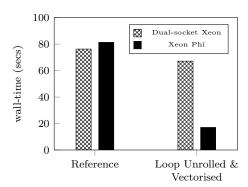

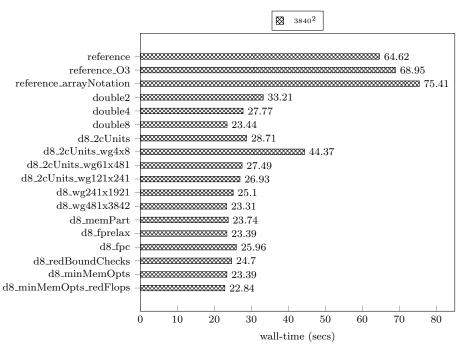

|   |     | 7.3.1   | Optimisations Analysis                    | 176 |

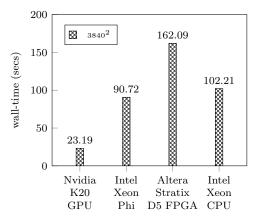

|   |     | 7.3.2   | Time to Solution Analysis                 | 184 |

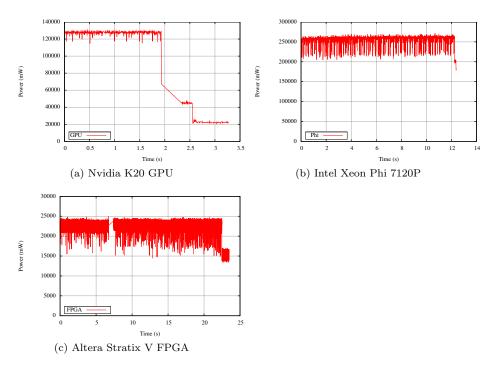

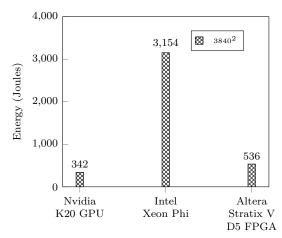

|   |     | 7.3.3   | Energy to Solution Analysis               | 186 |

|   | 7.4 | Summ    | nary                                      | 188 |

| 8 | Cor | nclusio | n                                         | 190 |

|   | 8.1 | Contr   | ibutions                                  | 191 |

|   |     | 8.1.1   | Mini-app Development and Utilisation      | 191 |

|   |     | 8.1.2   | Evaluation of PGAS Programming Models     | 191 |

|   |     | 8.1.3   | Examination of Hybrid Programming Models  | 192 |

|   |     | 8.1.4   | Development of Application Optimisations  | 194 |

|   |     | 8.1.5   | Supercomputer Architecture Analysis       | 195 |

|   | 8.2 | Benefi  | iciaries                                  | 196 |

|   | 8.3 | Limita  | ations                                    | 196 |

|   |     | 8.3.1   | Application Characteristics               | 196 |

|                           |       | 8.3.2   | The Utility of FPGA Architectures                   | 197 |

|---------------------------|-------|---------|-----------------------------------------------------|-----|

|                           | 8.4   | Future  | e Work                                              | 198 |

|                           |       | 8.4.1   | Extending the PGAS Language Evaluation              | 198 |

|                           |       | 8.4.2   | Intra-node Programming Models                       | 199 |

|                           |       | 8.4.3   | Energy Efficient Processing Technologies            | 200 |

| Bi                        | bliog | graphy  |                                                     | 202 |

| $\mathbf{A}_{\mathbf{J}}$ | ppen  | dices   |                                                     | 223 |

| $\mathbf{A}$              | Exp   | erimeı  | ntal Platforms/Architectures                        | 224 |

|                           | A.1   | Produc  | ction Supercomputer Platforms                       | 224 |

|                           |       | A.1.1   | HECToR                                              | 224 |

|                           |       | A.1.2   | Archer                                              | 225 |

|                           |       | A.1.3   | Spruce                                              | 225 |

|                           |       | A.1.4   | Mira                                                | 226 |

|                           |       | A.1.5   | Titan                                               | 226 |

|                           |       | A.1.6   | Vulcan                                              | 227 |

|                           | A.2   | Test-be | ed Platforms                                        | 227 |

|                           |       | A.2.1   | Teller, Compton & Shannon                           | 227 |

|                           |       | A.2.2   | Chilean Pine                                        | 229 |

|                           |       | A.2.3   | ${\rm Tuck} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 230 |

|                           | A.3   | Summ    | ary                                                 | 230 |

# List of Figures

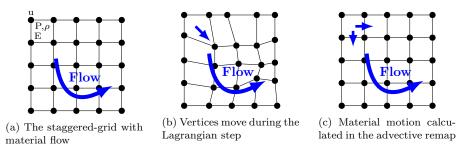

| 1.1  | Staggered grid employed in CloverLeaf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | The Euler equations of compressible flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35 |

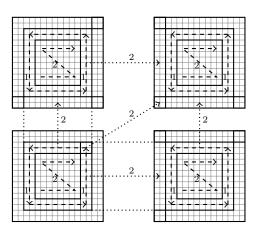

| 3.1  | The modified "first-touch" memory initialisation approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41 |

| 3.2  | OpenMP $point-to-point$ synchronisation approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46 |

| 3.3  | The "vectorising" version of the Calc-DT kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48 |

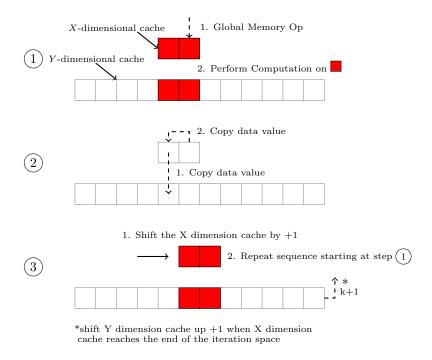

| 3.4  | Optimisations to the $Cell$ - $Advection$ kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53 |

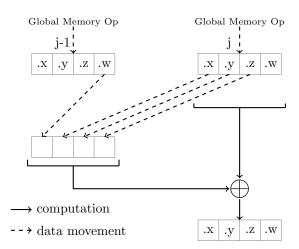

| 3.5  | Optimisations to the <i>Momentum-Advection</i> kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54 |

| 3.6  | Optimisations to the <i>Accelerate</i> kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55 |

| 3.7  | Optimisations to the $Calc-DT$ kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56 |

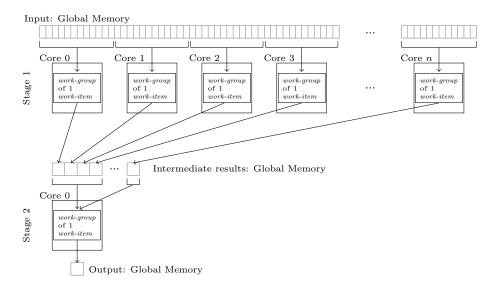

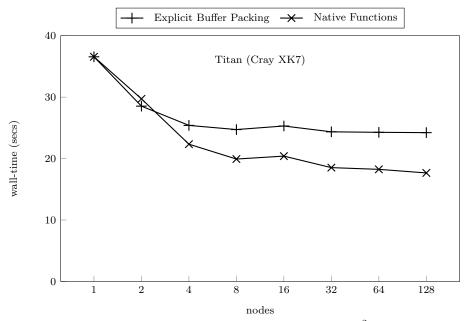

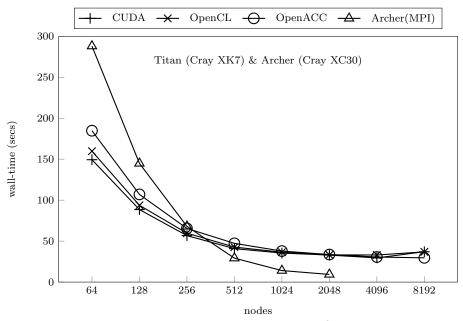

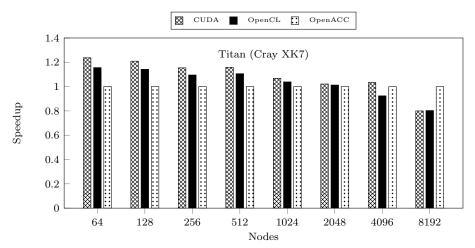

| 3.8  | Optimisations to the $PdV$ kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |