#### Stewart, Bob and Crockett, Louise and Barlee, Kenneth and Atkinson, Dale (2016) Model based design for 4G and 5G wireless communications software defined radio using MATLAB. In: 2016 Design, Automation & Test in Europe Conference & Exhibition, 2016-03-14 - 2016-03-18.

This version is available at https://strathprints.strath.ac.uk/56213/

**Strathprints** is designed to allow users to access the research output of the University of Strathclyde. Unless otherwise explicitly stated on the manuscript, Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Please check the manuscript for details of any other licences that may have been applied. You may not engage in further distribution of the material for any profitmaking activities or any commercial gain. You may freely distribute both the url (<u>https://strathprints.strath.ac.uk/</u>) and the content of this paper for research or private study, educational, or not-for-profit purposes without prior permission or charge.

Any correspondence concerning this service should be sent to the Strathprints administrator: <a href="mailto:strathprints@strath.ac.uk">strathprints@strath.ac.uk</a>

#### DESIGN, AUTOMATION & TEST IN EUROPE

14 – 18 March, 2016 · ICC · Dresden · Germany The European Event for Electronic System Design & Test

# Model Based Design For 4G And 5G Wireless Communications *Software Defined Radio* Using Matlab & Simulink

# Bob Stewart (Presenter) Louise Crockett, Kenneth Barlee, Dale Atkinson

University of Strathclyde, Glasgow, Scotland

Model Based Design and Verification, 16<sup>th</sup> March 2016

### **Model Based Design** for 4G & 5G Wireless Communications Software Defined Radio Using Matlab & Simulink

# Simulation Verification Code Generation

Bob Stewart, MathWorks Professor, University of Strathclyde

# **Software Defined Radio – 'White Space' Networks**

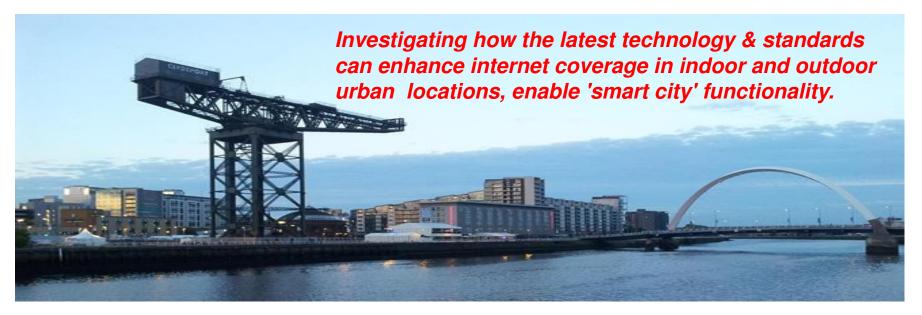

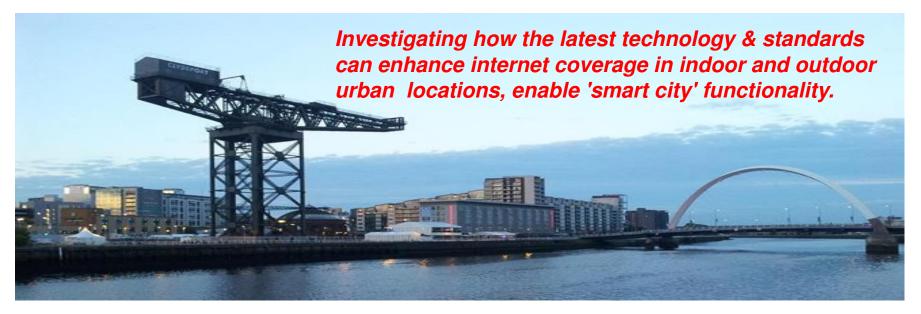

## Glasgow TV White Space Pilot: 2013-2015

(Part of UK OfCom Pilot Programmes: <u>http://media.ofcom.org.uk/news/2015/tvws-statement/</u>)

#### **Project Partners:**

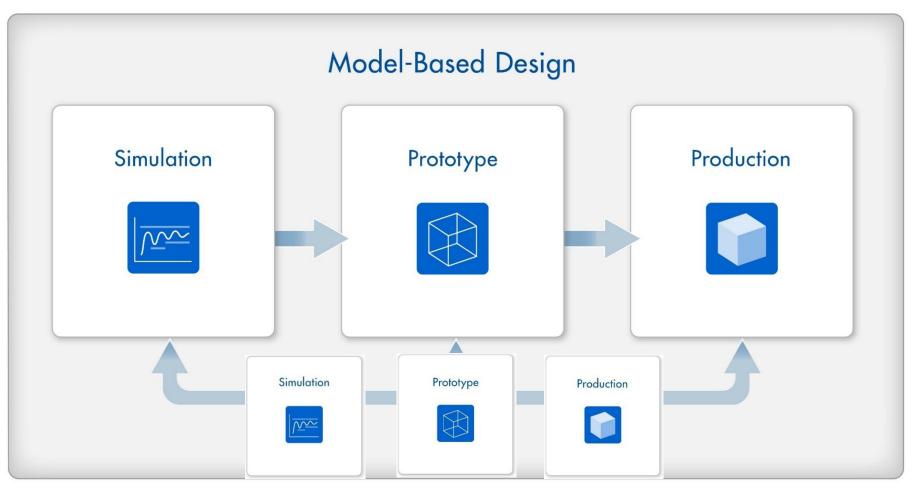

# **Model-Based Design**

A single shared development environment

# **Model-Based Design**

A single shared development environment

Simulate DSP & Communications algorithms and realise fixed point implementations

Prototype HDL implementations and validate performance via co-simulation

Production

Produce design on target FPGA and Supported radio hardware.

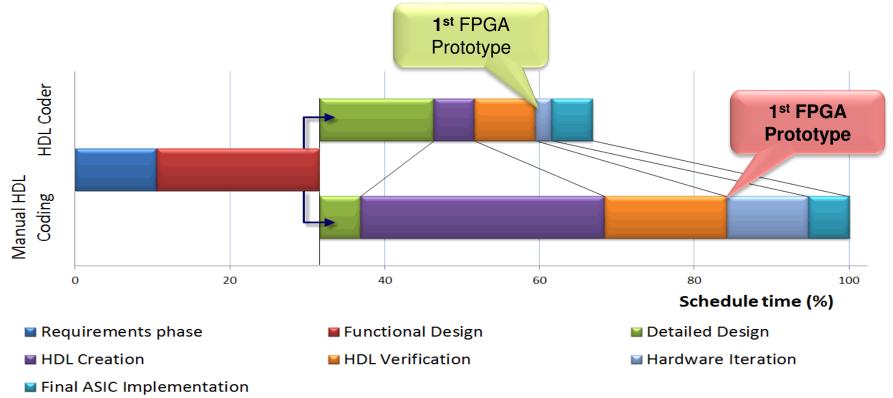

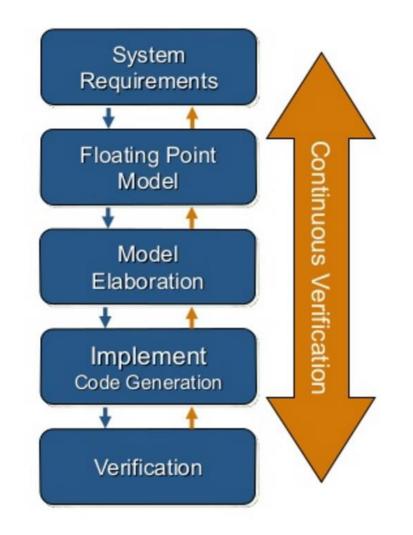

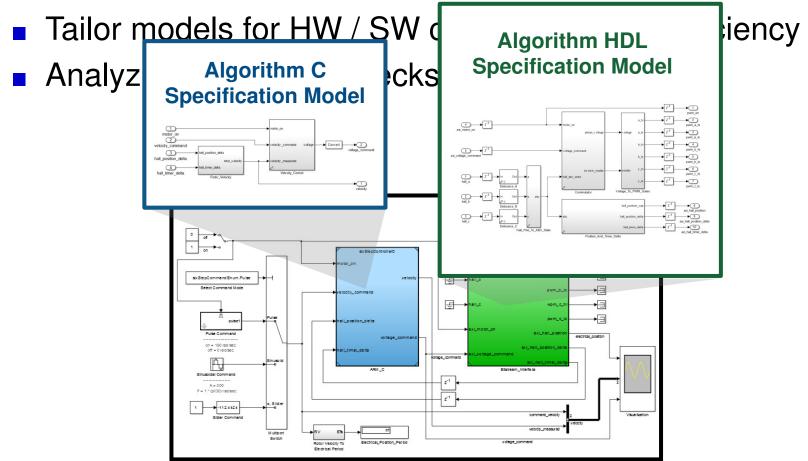

# Why Model-Based Design for FPGA Systems? Reduce implementation time

- Reduced FPGA prototype development schedule

- Shorter design iteration cycles

- Improved product quality

Bob Stewart, MathWorks Professor, University of Strathclyde

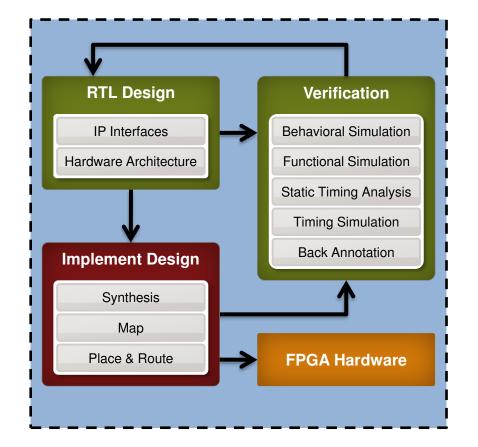

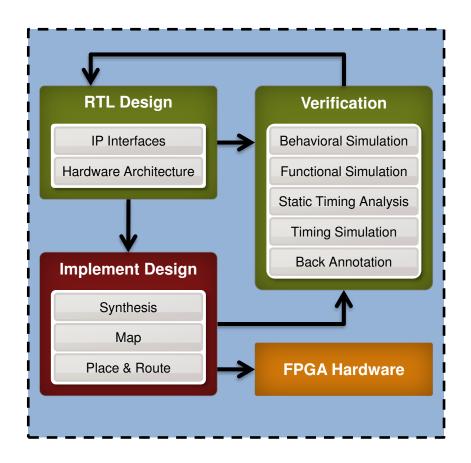

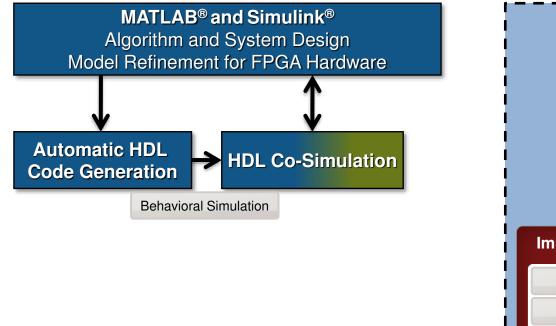

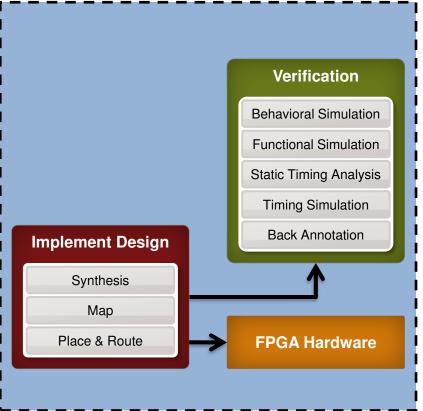

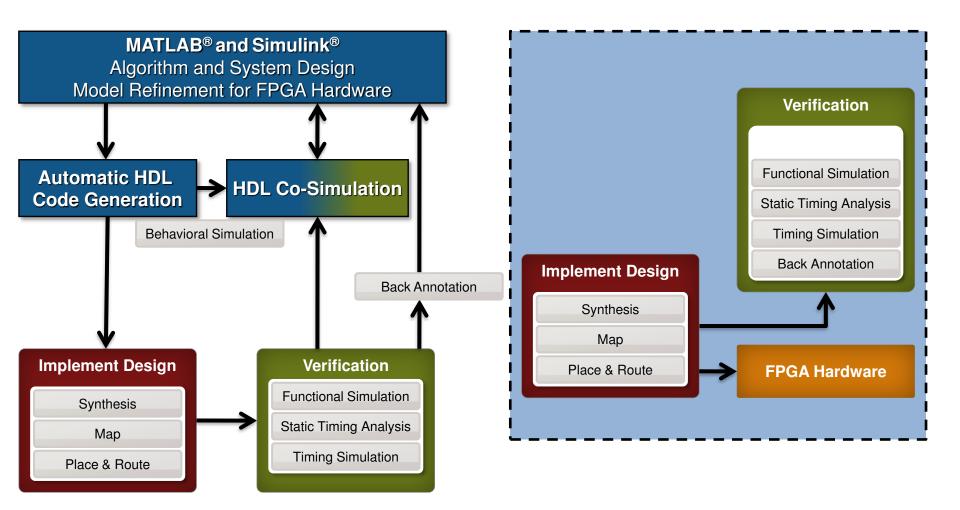

# **Separate Views Implementation**

#### **Algorithm Designer**

#### **FPGA Designer**

MATLAB<sup>®</sup> and Simulink<sup>®</sup> Algorithm and System Design

MATLAB<sup>®</sup> and Simulink<sup>®</sup> Algorithm and System Design Model Refinement for FPGA Hardware

Automatic HDL Code Generation

**FPGA Hardware**

Bob Stewart, MathWorks Professor, University of Strathclyde

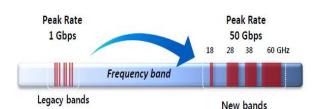

# Some 5G DSP and Comms Challenges

## New Modulation Schemes

- Performance characteristics of FBMC, UFMC, etc.

# More Antennas

- Beamforming and precoding algorithms

- Antenna arrays and Massive MIMO

# New Frequency Bands

- RF system architectures design in

- Advanced Antenna, RF and DSP Co-Design

- Channel modeling from real-world measurement data

# Dynamic Spectrum and SDR

- Versatile cognitive radios

- Secondary spectrum users

- Spectrum databases

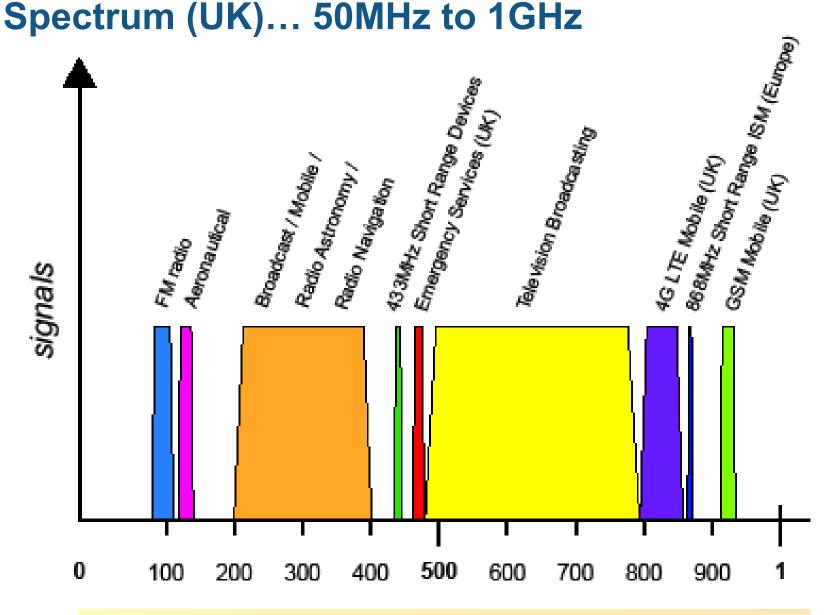

frequency (MHz)

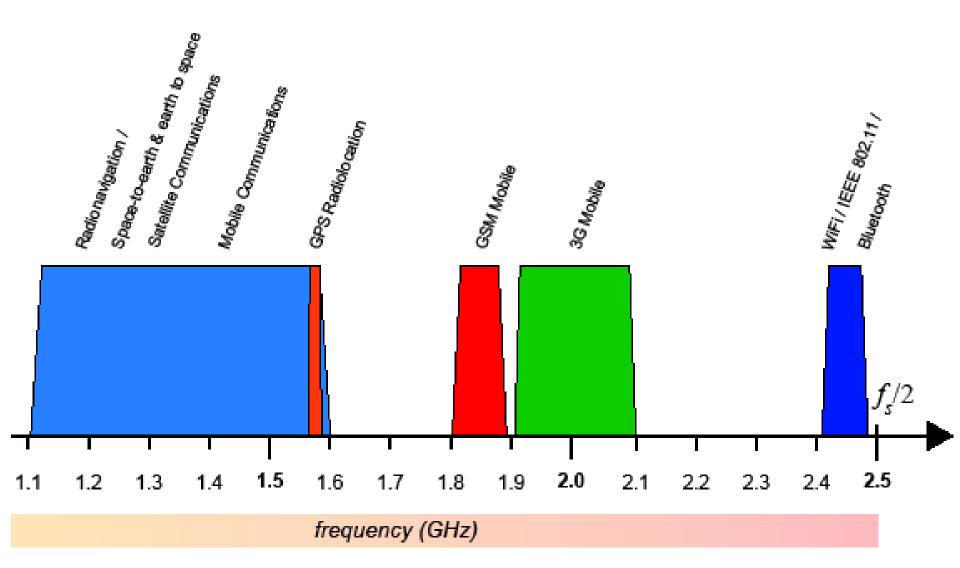

# Spectrum (UK)... 1GHz to 2.5Hz

# **Software Defined Radio – 'White Space' Networks**

## Glasgow TV White Space Pilot: 2013-2015

(Part of UK OfCom Pilot Programmes: <u>http://media.ofcom.org.uk/news/2015/tvws-statement/</u>)

#### **Project Partners:**

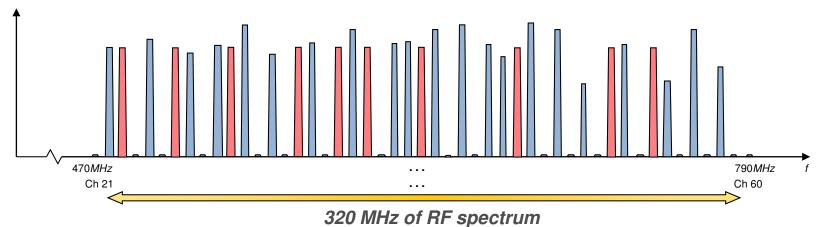

# What are the TV 'White Space' frequencies?

- Up to 40 channels of 8MHz each from 470MHz to 740MHz.

- Depends where you are as to available frequencies.

- In UK TV white space (TVWS) you are a secondary user

... the primary users are the terrestrial TV broadcasters.

- If you *transmit* on TVWS then do by the *rules*.

- Requests go to the TVWS database.

# **TV White Space – Dynamic Spectrum Access**

- Regulators around the world are recognizing the importance of TV white space and have been progressing towards the creation of regulatory frameworks

- Licence-exempt

- Access controlled by regulator-approved database

- US regulator (FCC) was first to legalize licence-exempt access to TV white spaces in the US, in 2008, and revised in 2010.

- UK regulator (Ofcom) has proposed a more ambitious and more flexible approach, which will increase the efficiency with which this spectrum can be harnessed – access opened January 2016

- Many other regulators are also progressing towards regulation.

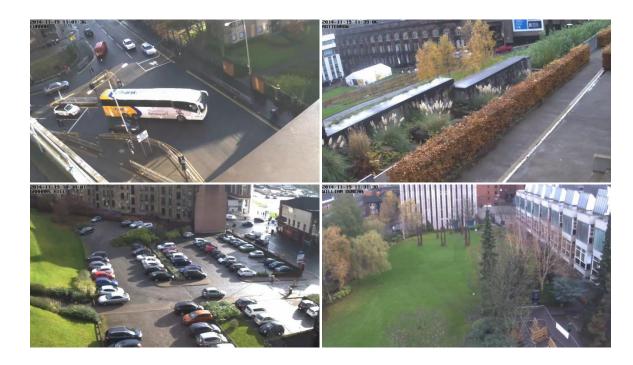

# **Glasgow TVWS Pilot: Testing & Demonstrating**

- Testing TVWS performance in built-up urban areas

- Demonstrating applications:

- Video Camera

- Sensor Networks

- Contributing to OfCom regulatory activities:

- Ofcom test team visits

- Contributing to Ofcom consultations

- Working with industry partners and Government

# **Glasgow TVWS Pilot Activities**

- Helping Ofcom to validate its proposed dynamic access framework

- Demonstrating higher-level benefits of using White Space spectrum

- Outdoor webcams

- Wi-Fi internet access in campus garden areas

- Helping to assess new technologies

- e.g: IEEE 802.11af (Wi-Fi in TVWS)

- Protoyping and proof of concept of other standards

- LTE implementation

# **Glasgow White Space Network**

- Phase 1: 2014/15 : PTMP TVWS network:

- Wi-Fi internet access in outdoor garden areas

- Outdoor webcams

- Deployed at Strathclyde University City Campus

# **Radios used in Glasgow TVWS Pilot**

- TVWS Pilot used 3 different radios from vendors:

- Adaptrum (Proprietary Standard)

- 6 Harmonics (based on IEEE 802.11)

- MediaTek (IEEE 802.11af based)

- (Also test radios; *Ubiquity* XR7)

- But what if we want to test LTE in White Space frequencies – there is no radio available (*at present*!)?

- So we achieve with fast SDR LTE TVWS prototyping using Model Based Design to target FPGA SDR platforms.

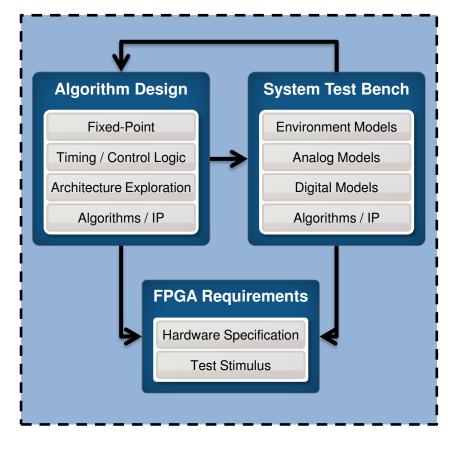

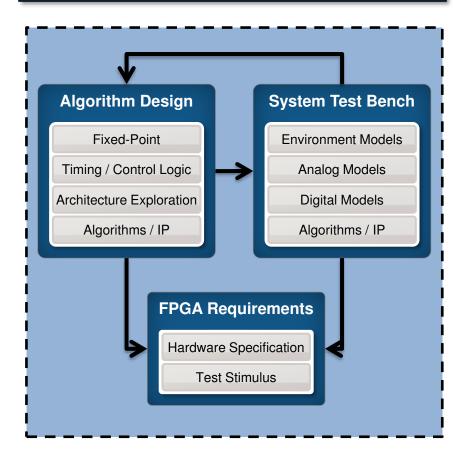

# **Prototyping for SDR in TV White Spaces**

**DSP/Comms Design & Verification** Simulate DSP baseband and IF/RF systems

**Fixed Point HDL implementation & LTE** *LTE Tx and Rx and TVWS Channeliser/Modulator*

**Prototyping and Implementation** Deploy algorithms onto target FPGA / SDR system

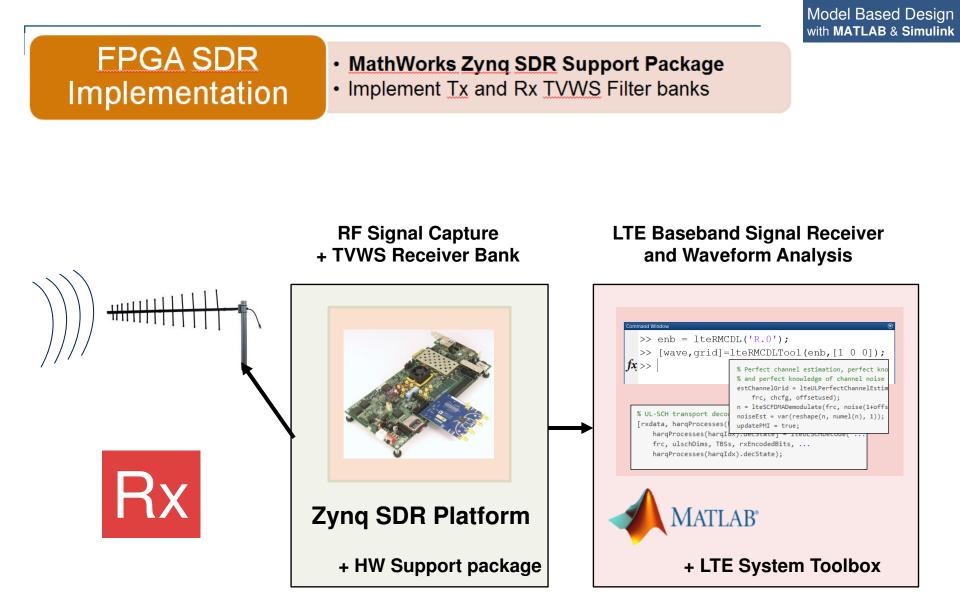

# Model Based Design of SDR for LTE in TVWS

| Floating Point<br>Simulation | <ul> <li>MathWorks DSP System &amp; Comms Toolbox</li> <li>Design 470-740 MHz TVWS Filter Bank</li> </ul>    |

|------------------------------|--------------------------------------------------------------------------------------------------------------|

| Fixed Point<br>Optimisation  | <ul> <li>MathWorks <i>Fixed Point Designer</i></li> <li>Implement TVWS Filter Bank in Fixed Point</li> </ul> |

| VHDL<br>Implementation       | <ul> <li>MathWorks HDL Coder</li> <li>Design verified HDL code for TVWS Filter Bank</li> </ul>               |

| LTE Baseband                 | <ul> <li>MathWorks LTE Systems Toolbox</li> <li>Implement LTE Transmit and Receive</li> </ul>                |

| FPGA SDR<br>Implementation   | <ul> <li>MathWorks Zynq SDR Support Package</li> <li>Implement Tx and Rx TVWS Filter banks</li> </ul>        |

# So what do we need for the TVWS LTE SDR?

## Software:

- MATLAB & Simulink

- DSP Systems Toolbox

- Communications System Toolbox

- LTE Systems Toolbox

- Fixed Point Designer

- HDL Coder

- Zynq SDR Hardware Support Package

## Hardware

- Xilinx Zynq FPGA Board & ADI FMComms RF Tx/Rx Card

- Radio front ends/amplifier and antennas

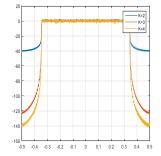

- MathWorks DSP System & Comms Toolbox

Design 470-740 MHz TVWS Filter Bank

- Need a 40 channel agile filter bank

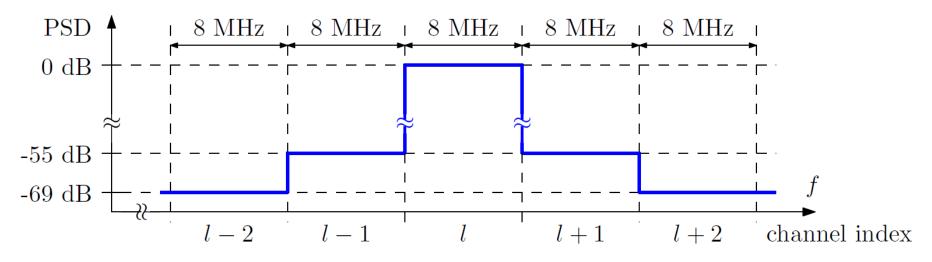

- First design prototype FIR filter using **DSP System Toolbox**

- Compliant with TVWS 8MHz channel mask

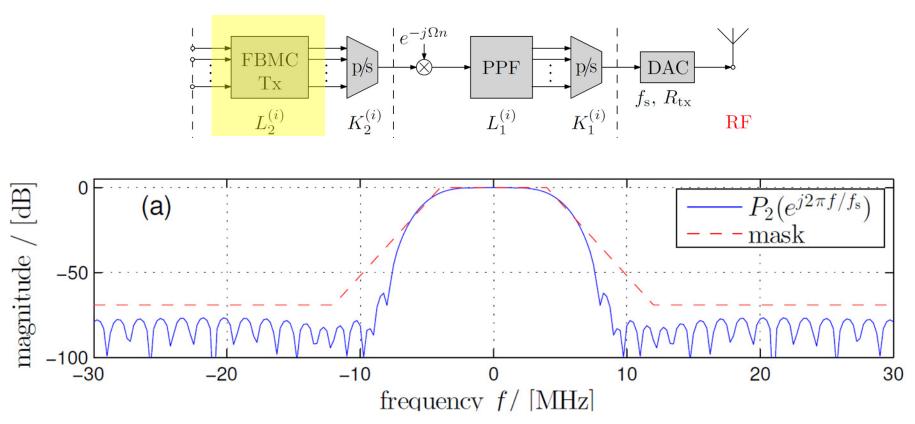

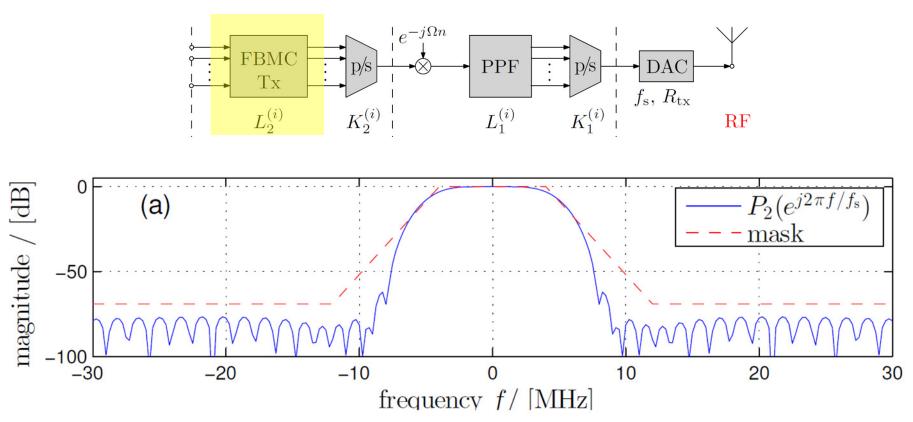

- TVWS Transmit design satisfies the spectral mask below

- MathWorks DSP System & Comms Toolbox

Design 470 740 MUZ TV/MC Filter Bank

- Design 470-740 MHz TVWS Filter Bank

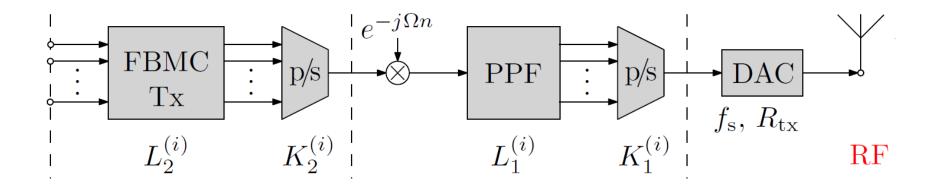

- Filter Bank Multicarrier (FBMC) synthesis bank combines 40 TVWS baseband channels each of 8MHz.

- Polyphase filter (PPF) and complex frequency correction translates the baseband to TVWS 470MHz to 790MHz.

(Full paper on design at: R. A. Elliot, M. A. Enderwitz, K. Thompson, L. H. Crockett, S. Weiss and R. W. Stewart, "Wideband TV White Space Transceiver Design and Implementation," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 63, no. 1, pp. 24-28, Jan. 2016.)

MathWorks DSP System & Comms Toolbox

Design 470-740 MHz TVWS Filter Bank

Prototype Filter Design – Nyquist Root Raised Cosine with adjacent channel leakage of -69dB.

Bob Stewart, MathWorks Professor, University of Strathclyde

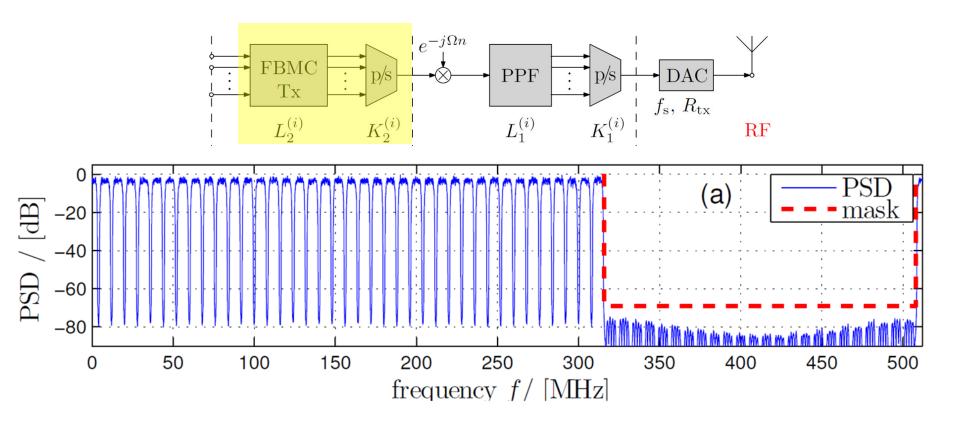

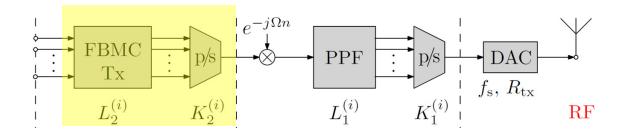

MathWorks DSP System & Comms Toolbox

Design 470-740 MHz TVWS Filter Bank

Power spectral densities (PSD) after 40 x 8MHz filter bank (each TVWS channel loaded here with a 5.33MHz signal).

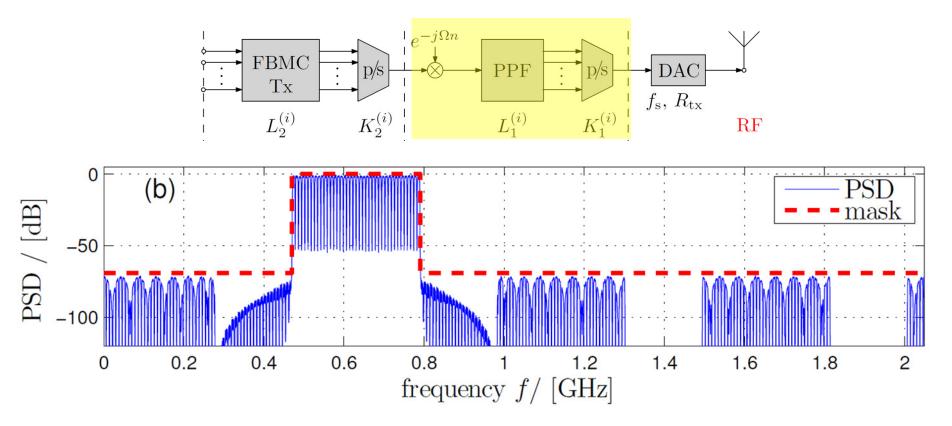

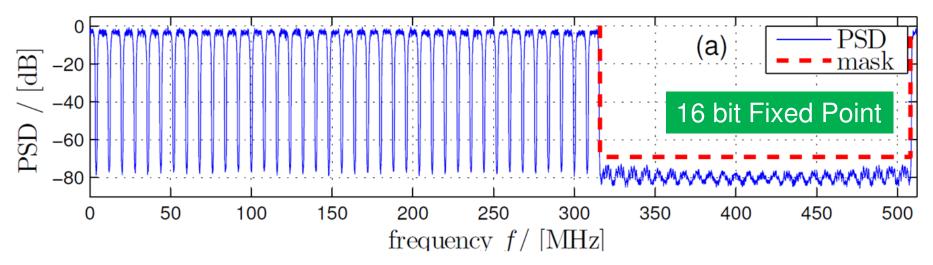

- MathWorks DSP System & Comms Toolbox

- Design 470-740 MHz TVWS Filter Bank

Modulation of 320MHz baseband of 40 channels to centre frequency at 630MHz, with f<sub>s</sub> = 2.048 GHz

Bob Stewart, MathWorks Professor, University of Strathclyde

- MathWorks Fixed Point Designer

- Implement TVWS Filter Bank in Fixed Point

# **Floating to Fixed Point Conversion**

- Fixed-point data type specification for:

- MATLAB

- Simulink

- Bit-true accelerated simulation

- Recommendations for word length and scaling

- Floating to fixed-point results comparison

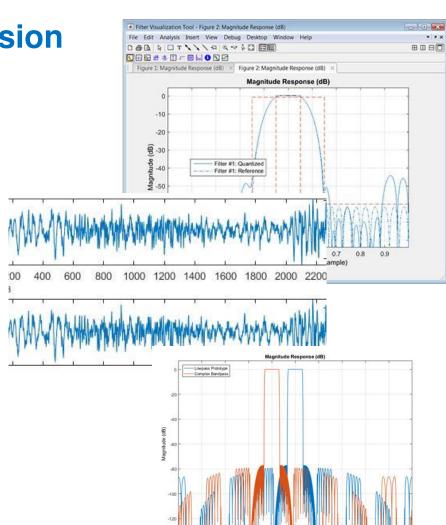

MathWorks Fixed Point Designer

Implement TVWS Filter Bank in Fixed Point

Prototype Filter Design – Nyquist Root Raised Cosine with adjacent channel leakage of -69dB.

Bob Stewart, MathWorks Professor, University of Strathclyde

MathWorks Fixed Point Designer

Implement TVWS Filter Bank in Fixed Point

Power spectral densities (PSD) after 40 x 8MHz filter bank (each TVWS channel loaded with a 5.33MHz signal).

Bob Stewart, MathWorks Professor, University of Strathclyde

MathWorks Fixed Point Designer

Implement TVWS Filter Bank in Fixed Point

Modulation of 320MHz baseband of 40 channel to centre frequency at 630MHz, with f<sub>s</sub> = 2.048 GHz

Bob Stewart, MathWorks Professor, University of Strathclyde

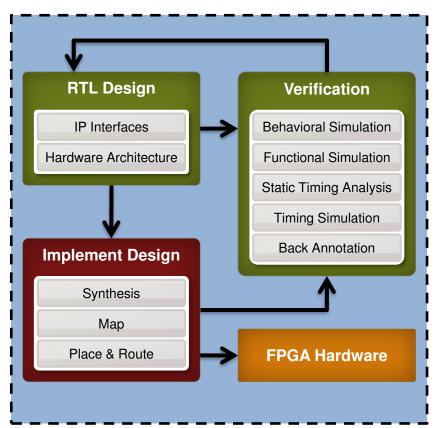

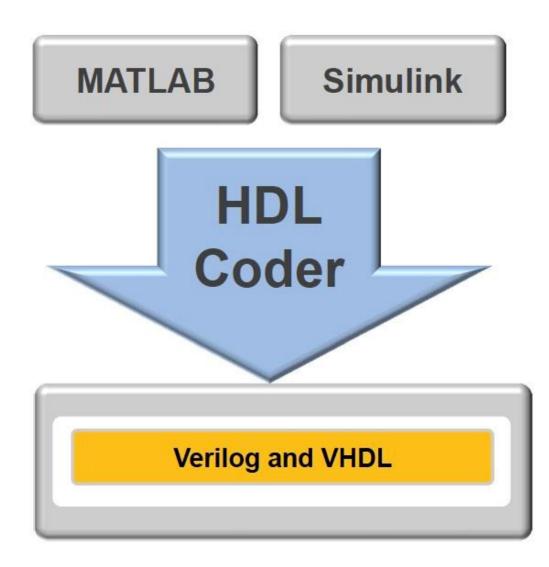

## VHDL • Ma Implementation • De

- MathWorks HDL Coder

- Design verified HDL code for TVWS Filter Bank

## VHDL Implementation

**HDL Coder** generates portable, synthesizable VHDL and Verilog code from MATLAB functions, Simulink models.

- The generated HDL code can be used for FPGA programming or ASIC prototyping and design.

- Provides a workflow advisor for working with Xilinx and Altera software tools and design flows.

- Controls architecture and implementation and highlight critical timing paths limiting clocking frequencies.

- Generate hardware resource utilization estimates for designs to target FPGA hardware.

- Provides traceability between Simulink model and the generated Verilog and VHDL code.

Model Based Design with MATLAB & Simulink

## VHDL Implementation

- MathWorks HDL Coder

- Design verified HDL code for TVWS Filter Bank

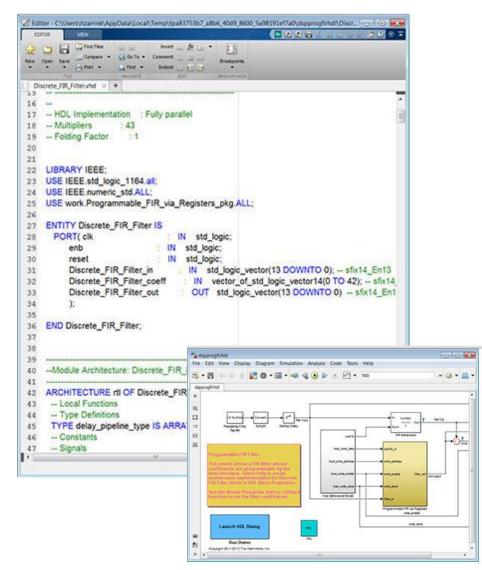

## VHDL Implementation

- MathWorks HDL Coder

- Design verified <u>HDL</u> code for <u>TVWS</u> Filter Bank

- Generation of VHDL for filter bank design and modulator design.

- VHDL verification and design of fixed point bit true Simulink model.

- FBMC, PPF and modulator

## VHDL Implementation

- From fixed point design, we can use the HDL Coder workflow to verify design and review implementation achievable on FPGA devices.

- Transmit and Receiver Costs integrated on one table from Xilinx VIVADO tools.

- Design is *viable* and implementable on FPGA target

| logic utilisation | number used | available | percentage used |

|-------------------|-------------|-----------|-----------------|

| LUTs              | 83566       | 346400    | 24%             |

| FFs               | 63108       | 692800    | 9%              |

| slices            | 26297       | 86600     | 30%             |

| DSP48E1 units     | 1748        | 2880      | 60%             |

## VIRTEX7-XC7VX550T FPGA DEVICE.

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

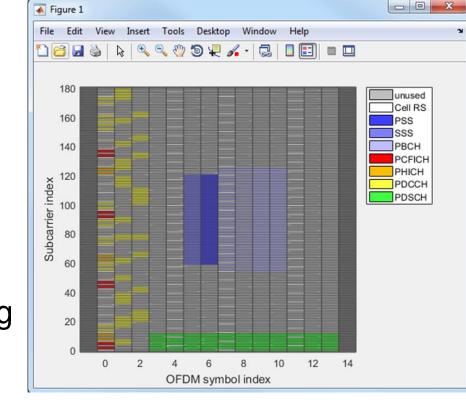

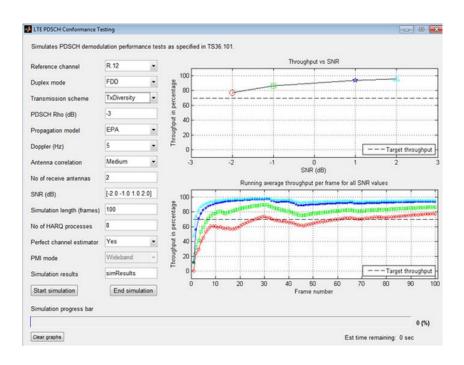

# LTE Systems Toolbox

- Simulates the physical layer of LTE and LTE-Advanced wireless communications systems.

- Standard-compliant functions and apps for the design, simulation, and verification of LTE and LTE-Advanced.

- Accelerates LTE algorithm and physical layer (PHY) development, supporting golden reference verification.

- Conformance testing, and also enabling test waveform generation, suitable for our TVWS links.

- Can configure, simulate, measure, and analyze end-toend communications links.

Model Based Design with MATLAB & Simulink

## LTE Baseband

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

Coding/decoding

# LTE Systems Toolbox

- Physical Signals

- Physical Channels

- Transport Channels \_

- Control Information

- OFDM/SC-FDMA; Modulation/Demodulation

- Reception and recovery:

- Synchronisation

- Channel Estimation

- Equalisation

- Cell search procedure

- Channel Models

- Functions for Test and Measurement

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

# LTE Systems Toolbox

Standard-compliant physical layer models in MATLAB: Releases 8, 9, 10, 11 and 12

# Scope:

- FDD / TDD

- Uplink / Downlink

- Transmitter / Receiver

- Conformance tests

- link level simulation

- More than 200 functions for physical layer modelling

6-Mar-18

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

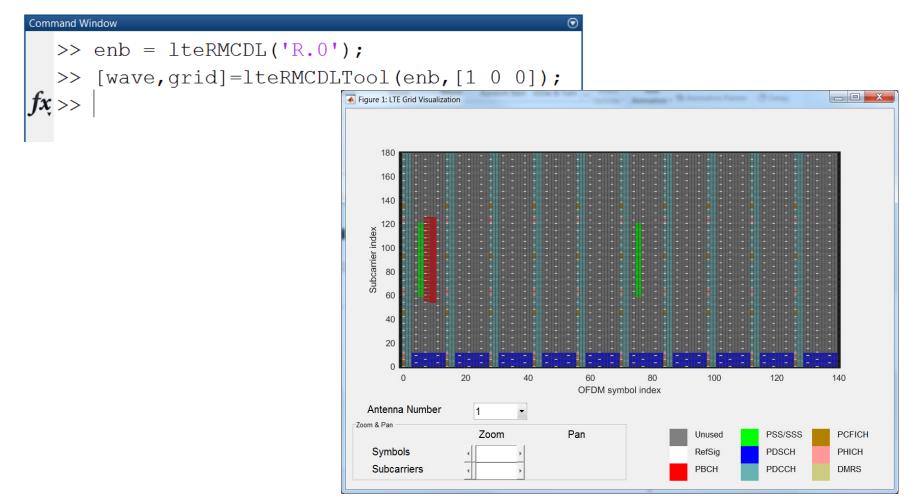

## Easy LTE Signal Generation from MATLAB code lines:

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

## LTE Systems Toolbox has high level signal generators.

| <pre>% Establish the number of component carriers.<br/>numCC = length(NDLRB);<br/>% Create transmission for each component carri</pre> | er                 | MAT                                                                                                                                 | LAB function                                              |                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|--|

| enb = cell(1,numCC);                                                                                                                   | LTE Downlink RMC   | Generator                                                                                                                           |                                                           |                  |  |

| <pre>for i = 1:numCC     enb{i} = lteRMCDL('R.5');</pre>                                                                               |                    | Generate PDSCH reference measurement channel (RMC) waveforms. These are specified in TS36.101 Annex A.3 for UE performance testing. |                                                           |                  |  |

| enb{i}.NDLRB = NDLRB(i);                                                                                                               | Reference channel  | R.0                                                                                                                                 | RMC parameter summary                                     |                  |  |

|                                                                                                                                        | Duplex mode        | FDD                                                                                                                                 | Number of downlink resource blocks                        |                  |  |

|                                                                                                                                        | Transmission sche  | me Port0                                                                                                                            | Transmit antenna ports<br>Modulation                      | 1<br>16QAM       |  |

|                                                                                                                                        | Cell identity      | 0                                                                                                                                   | Transmission layers                                       | 1                |  |

|                                                                                                                                        | RNTI               | 1                                                                                                                                   | Total info bits per frame per codewor                     | d 2016 bits      |  |

|                                                                                                                                        | RV sequence        | [0 1 2 3]                                                                                                                           |                                                           |                  |  |

|                                                                                                                                        | Rho (dB)           | 0                                                                                                                                   | Codeword input data                                       |                  |  |

|                                                                                                                                        | OCNG               | Off                                                                                                                                 | <ul> <li>Transport info bit stream (codeword 1</li> </ul> | ) User defined 💌 |  |

|                                                                                                                                        | Number of subfram  | les 10                                                                                                                              |                                                           | [1; 0; 0; 1]     |  |

|                                                                                                                                        | Number of codewo   | rds 1                                                                                                                               | •                                                         |                  |  |

|                                                                                                                                        | PMI set            | [1]                                                                                                                                 | Transport info bit stream (codeword 2                     | ) User defined 👻 |  |

|                                                                                                                                        | Number of HARQ p   | processes 8                                                                                                                         |                                                           | [1; 0; 0; 1]     |  |

| GUI Based                                                                                                                              | Windowing (sample  | es) 0                                                                                                                               |                                                           |                  |  |

| GUI Daseu                                                                                                                              | Waveform output v  | ariable rmcwaveform                                                                                                                 | n                                                         |                  |  |

|                                                                                                                                        | Resource grid outp | out variable rmcgrid                                                                                                                |                                                           |                  |  |

|                                                                                                                                        | RMC configuration  | output variable rmcconfig                                                                                                           |                                                           |                  |  |

|                                                                                                                                        |                    |                                                                                                                                     | Generate waveform                                         |                  |  |

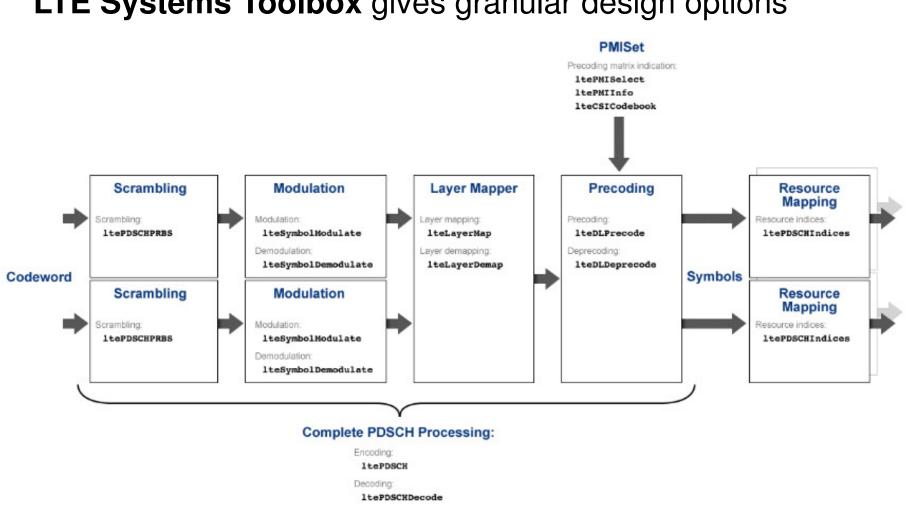

## LTE Systems Toolbox gives granular design options

MathWorks LTE Systems Toolbox LTE Baseband Implement LTE Transmit and Receive

#### Bob Stewart, MathWorks Professor, University of Strathclyde

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

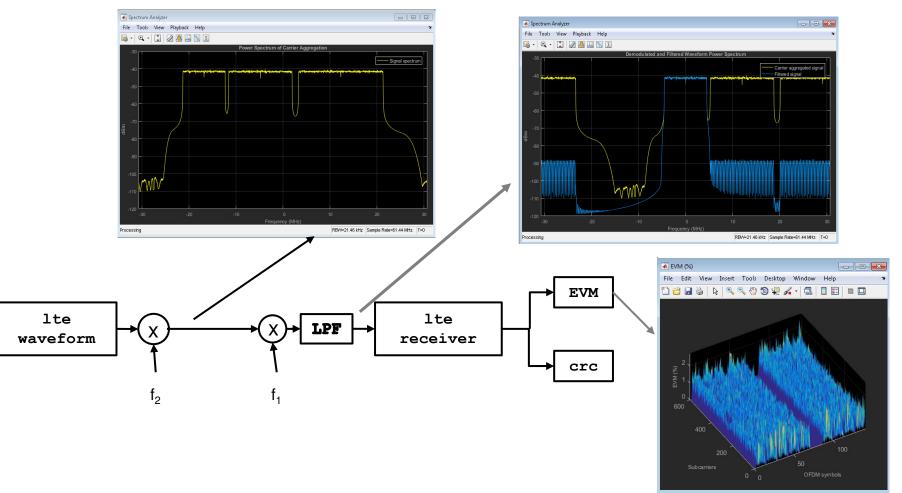

## LTE Systems Toolbox: Full transmit and receive chain.

Model Based Design with MATLAB & Simulink

## LTE Baseband

MathWorks LTE Systems Toolbox

Implement LTE Transmit and Receive

# LTE System Toolbox: using TDD for TVWS:

- Bandwidth: 5 MHz

- Modulation:

- BPSK / QPSK / 16QAM / 64QAM

- BPSK : Control

- 64QAM: data channel

- Duplex method: TDD / FDD

Model Based Design with MATLAB & Simulink

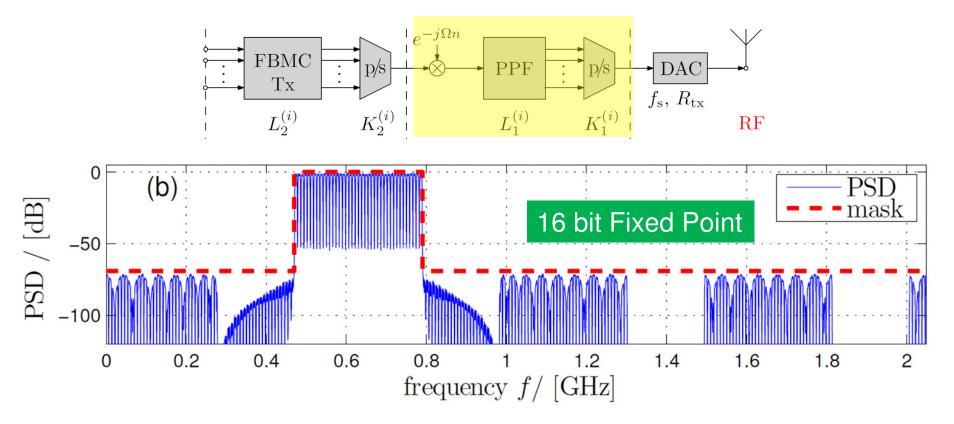

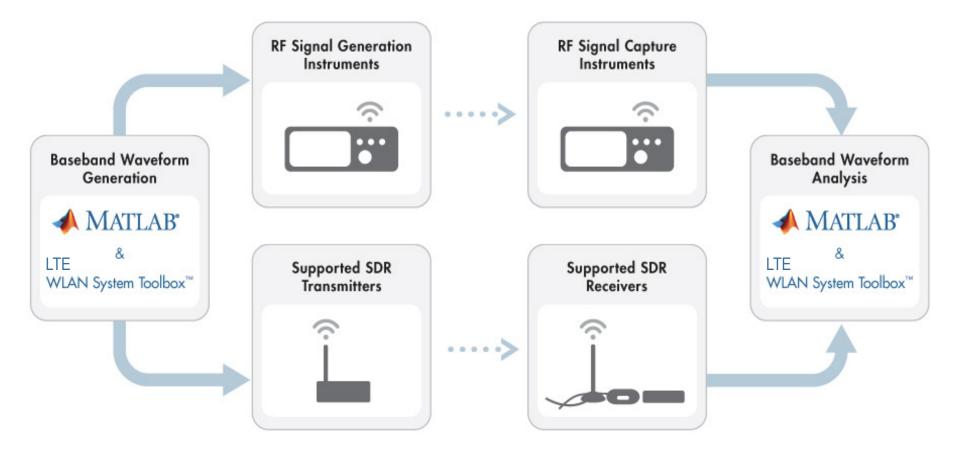

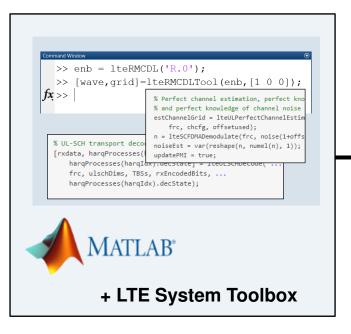

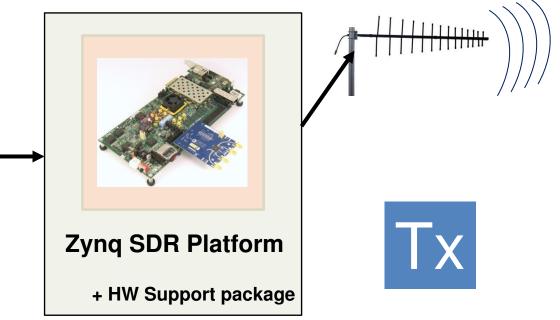

## FPGA SDR Implementation

- MathWorks Zyng SDR Support Package

- Implement Tx and Rx TVWS Filter banks

## FPGA SDR Implementation

MathWorks Zyng SDR Support Package

Implement <u>Tx</u> and Rx <u>TVWS</u> Filter banks

## Hardware

- Xilinx Zynq ZC706 Development Board

- Featuring Zynq-7045 AP SoC, 900 DSP48E1 slices; 350K Logic Cells

- 2 FMC Expansion Slots

## - ADI FMCCOMMS3 FMC Card

- AD9361 Agile RF Transceiver

- 2 x 2 transceiver with integrated

- 12-bit DACs and ADCs

- Band: 70MHz to 6.0GHz

- Channel Bandwidth: < 200kHz to 56MHz

- RF amplifier stage / Yagi Antenna

Model Based Design with MATLAB & Simulink

## FPGA SDR Implementation

- MathWorks Zyng SDR Support Package

- Implement Tx and Rx TVWS Filter banks

#### LTE Baseband Signal Transmitter and Waveform Generation

#### RF Signal Capture + TVWS FBMC Transmitter

# Model Based Design of SDR for LTE in TVWS

| Floating Point<br>Simulation | <ul> <li>MathWorks DSP System &amp; Comms Toolbox</li> <li>Design 470-740 MHz TVWS Filter Bank</li> </ul> |

|------------------------------|-----------------------------------------------------------------------------------------------------------|

| Fixed Point<br>Optimisation  | <ul> <li>MathWorks Fixed Point Designer</li> <li>Implement TVWS Filter Bank in Fixed Point</li> </ul>     |

| VHDL<br>Implementation       | <ul> <li>MathWorks HDL Coder</li> <li>Design verified HDL code for TVWS Filter Bank</li> </ul>            |

| LTE Baseband                 | <ul> <li>MathWorks LTE Systems Toolbox</li> <li>Implement LTE Transmit and Receive</li> </ul>             |

| FPGA SDR<br>Implementation   | <ul> <li>MathWorks Zynq SDR Support Package</li> <li>Implement Tx and Rx TVWS Filter banks</li> </ul>     |

## **Conclusions**

- Model Based Design of *LTE-SDR-TVWS-FPGA* protoype!

- Floating Point DSP Filter Bank and modulator design

- Fixed point optimisation of DSP system

- HDL implementation of DSP system

- LTE Systems toolbox signal generator (Tx) & receiver (Rx)

- Implementation of LTE Tx and Rx on host

- Implement HDL of DSP System using Zynq SDR support

- Test over the TVWS air!

# **Acknowledgements**

Iain Chalmers, Sarunas Kalade, David Crawford, David Northcote, Dani Anderson, Stephan Weiss

at University of Strathclyde

Daniel Garcia-Alis, Neil MacEwen, Ken Karnoksky

at MathWorks

Model Based Design with MATLAB & Simulink

## **Additional Reserve Slides**

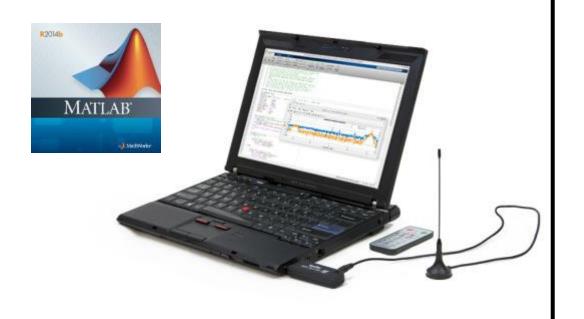

# SOFTWARE MATLAB & MATLAB & Simulia & Matlab & Simulia &

# 670 Page Textbook

+ more than 100 MATLAB & Simulink examples...

Download e-book and examples from:

# www.desktopSDR.com

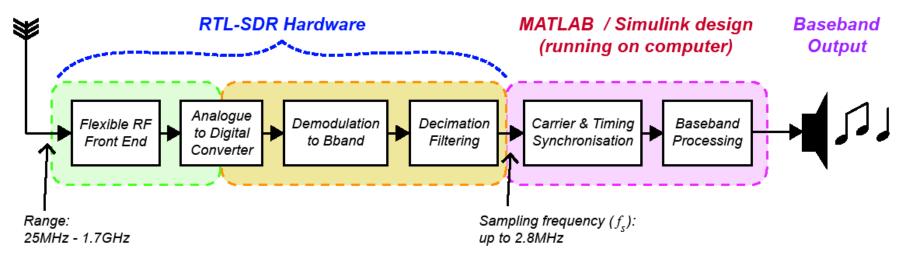

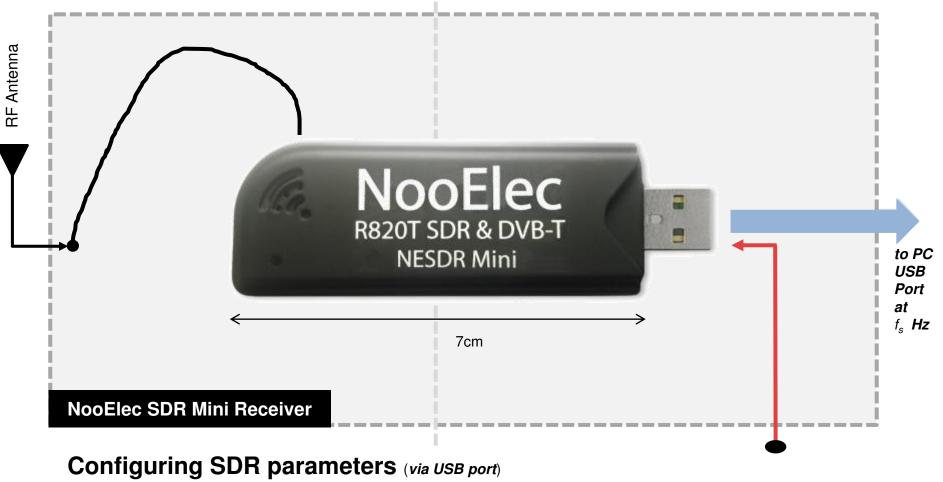

# **RTL-SDR** DSP enabled Radio

#### RF Antenna

# Hardware Setup for Real World SDR

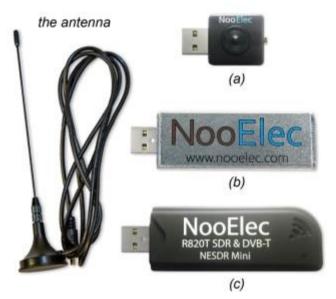

- Windows, Linux or Mac Computer

- An RTL-SDR + Antenna

A few RTL-SDR devices available...

(same hardware different packaging and component tolerances.)

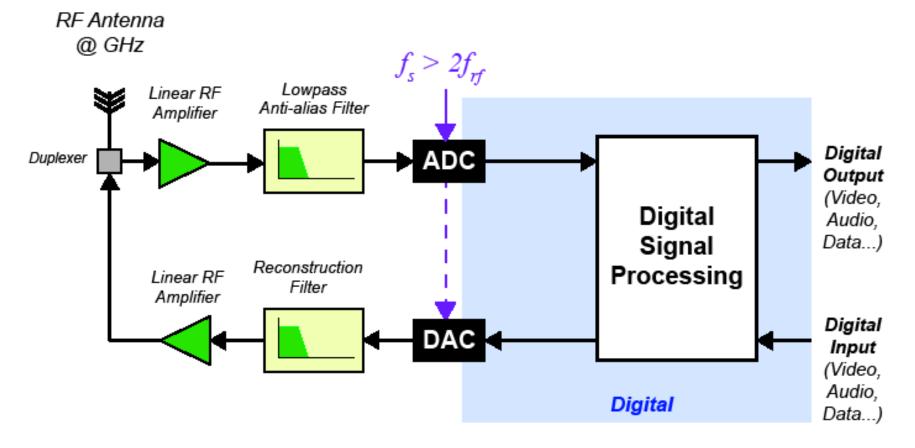

# The Ultimate (DSP enabled) Software Defined Radio

### 20MHz to 6GHz range

## ASICs, FPGAs, DSP Cores

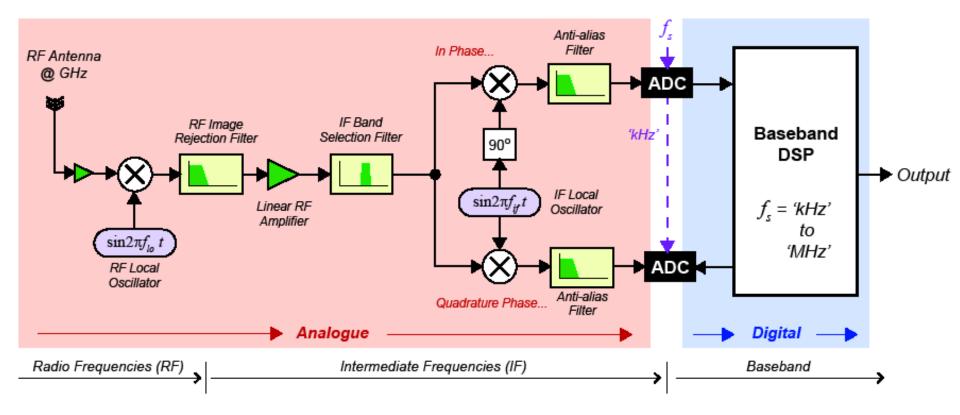

# First Generation Digital Radio (around 1995):

ADC Sampling Rates at baseband up to 100's kHz

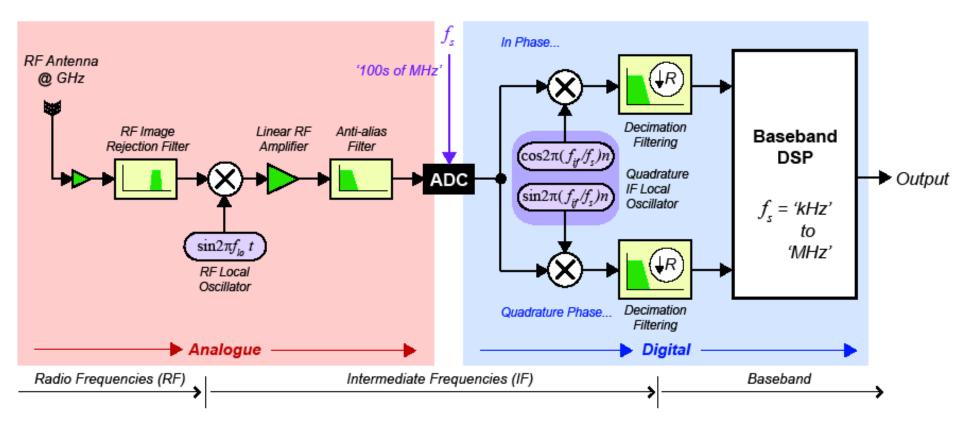

# Intermediate Frequency (IF) Digital Radio (2000s)

ADC Sampling Rates up to a few 100MHz

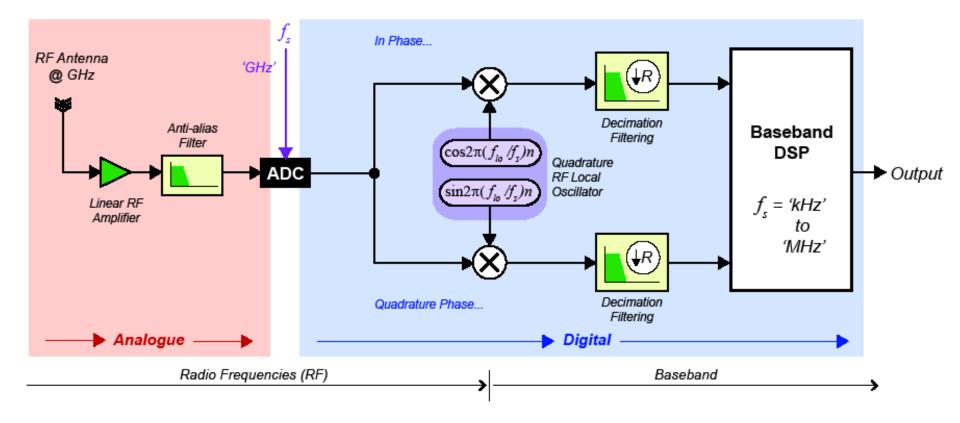

# The RF Sampled (zero-IF) Digital Radio (2012...)

ADC Sampling Rates of a GHz and (getting) higher.

Model Based Design with MATLAB & Simulink

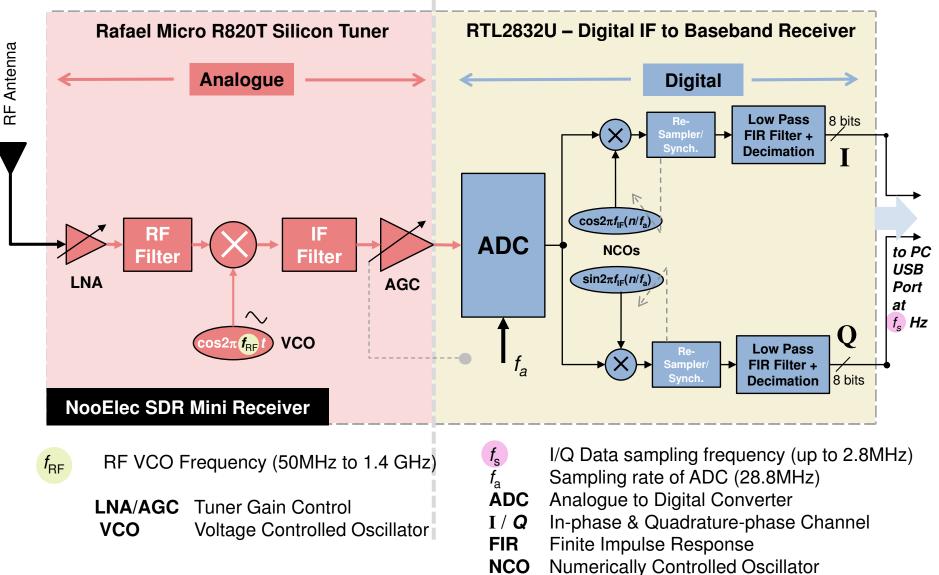

# **The RTL-SDR USB RF Receiver**

•  $f_{RF}$  - RF Center frequency

- $f_s I/Q$  Data Sampling Frequency

- Gain Control Parameters

- Frequency Correction

# An IF Software Defined Radio

(IF – Intermediate Frequency)

Bob Stewart, MathWorks Professor, University of Strathclyde

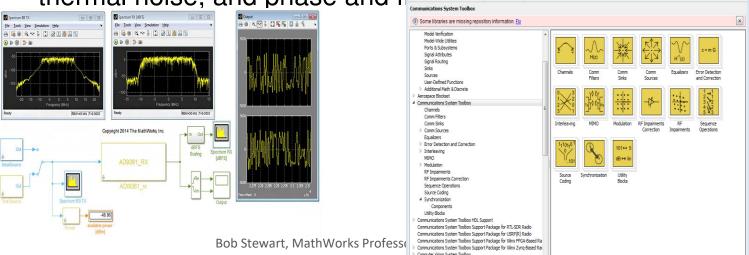

# Integration with MathWorks toolboxes

- Back up your modelling with the full strength of MW tools.

- Communications, Phased Array, LTE, WLAN, <u>SimRF</u>

- Analysis tools and measurement scopes, including a bit-error-rate app, constellation diagrams, and eye diagrams

- Channel models, including AWGN, multipath Rayleigh fading, Rician fading, MIMO multipath fading, and LTE MIMO multipath fading

- Basic RF impairment models, including nonlinearity, phase noise, thermal noise, and phase and for the second second

6-Mar-18

# **SDR Examples**

- Full prototyping flow

- Repeating transmitter mode

- QPSK Tx/Rx + FPGA targeting + HW/SW co-desig

- Advanced communications standards

- LTE using LTE System Toolbox

- 802.11 using WLAN System Toolbox

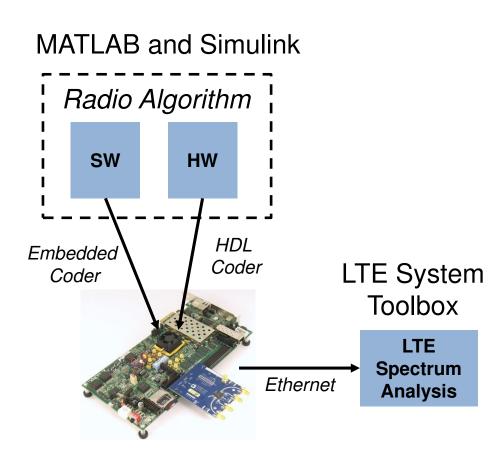

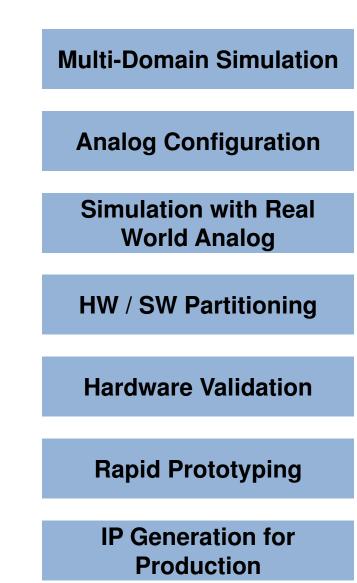

# **Radio Design Framework**

- Quickly develop radio algorithms from customer requirements in MATLAB<sup>®</sup> and Simulink<sup>®</sup>

- Common environment used by design teams for system modeling through to production

- Accelerate development with code generation and continuous verification

- Validate, prototype and deploy in hardware

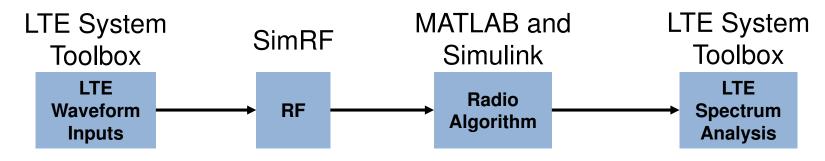

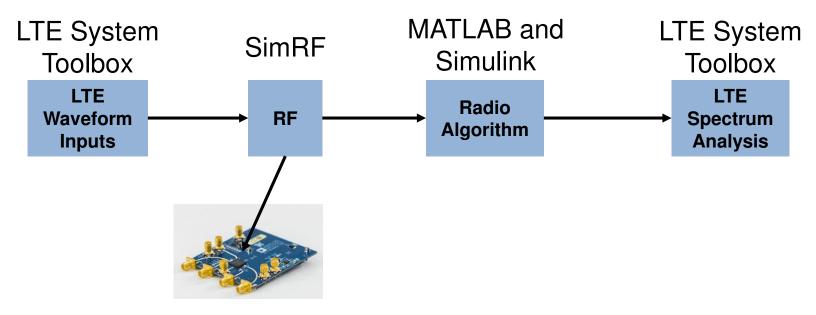

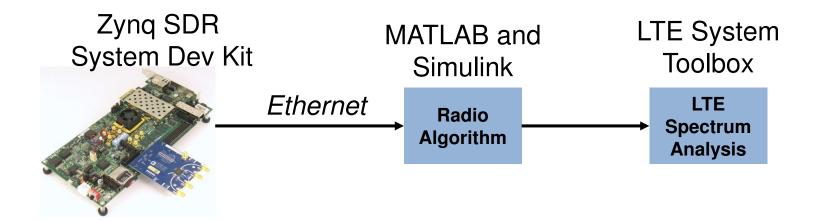

# **Radio Design Framework**

## Multi-Domain Simulation

- LTE System Toolbox<sup>™</sup> provides advanced waveform generation and spectrum analysis

- Model both the RF and DSP

- AD9361 simulation model available from MathWorks

- Rapidly explore radio algorithms to meet customer requirements in simulation

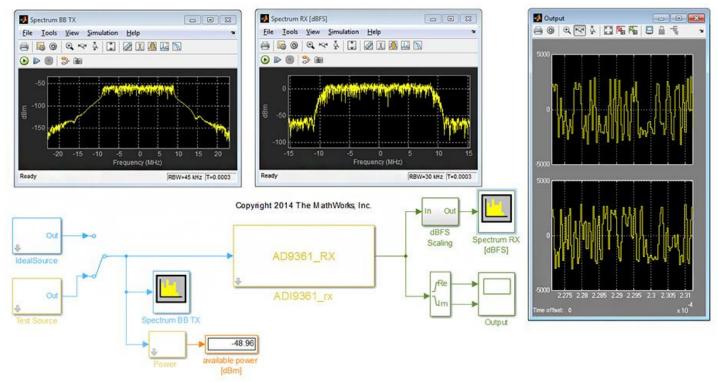

# **Multi-Domain Simulation Example**

Model RF transceivers using MATLAB and Simulink

- Built from device functional specification

- Tested with LTE-compliant waveforms

- Verified by vendor to match silicon behavior

# **LTE System Toolbox**

- Standard-compliant models for LTE and LTE-Advanced

- End-to-end physical layer transmit and receive processing functions

- Test models and reference measurement channel waveform generators

# **Radio Design Framework**

## Analog Configuration

- Tune and Configure Analog Front End in Simulink

- Simulation model for AD9361 built using Simulink and SimRF<sup>™</sup>

- Supports device configuration

# **AD9361 Simulation Model**

- Predict the impact of RF Imperfections in test signals

- Use reference tones and LTE Signals

- Evaluate the effects of nonlinearity, noise, gain and phase imbalance

- Generate AD9361

configuration file

## AD9361 Agile RF Transceiver

# Radio Design Framework

Simulation with Real World Analog

- Validate and tune algorithms with real world analog data through analog interface

- Zynq SDR System Development Kit supports analog capture and export to Simulink

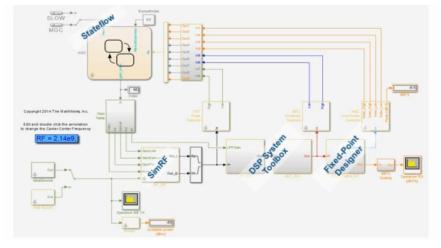

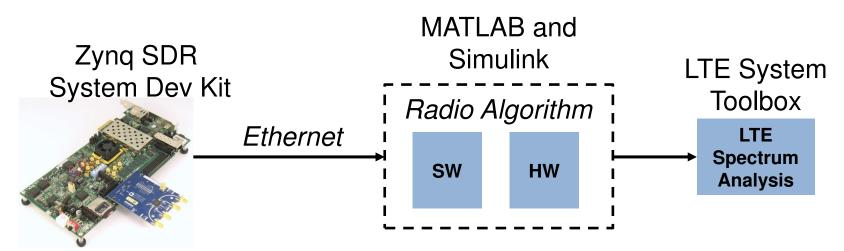

# **Radio Design Framework**

HW / SW Partitioning

Use Simulink to partition algorithm into HW and SW

- Cycle Accurate System Simulation

- Validate system performance

- Specify system concurrency

# **System Partitioning**

Hardware / Software system partitioning using Simulink

- User-defined system partitioning

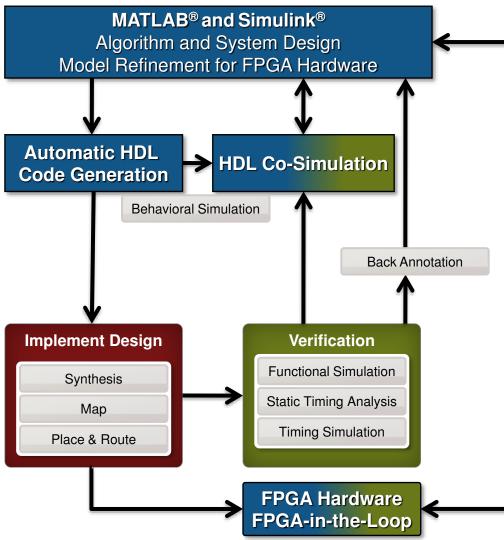

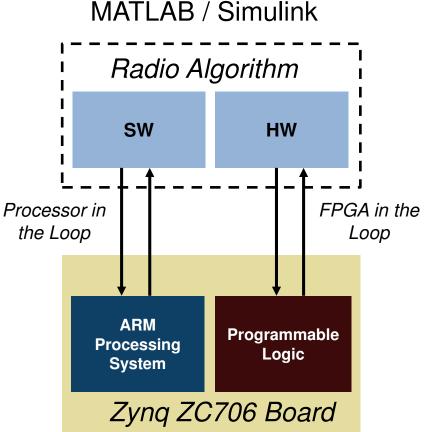

# **Radio Design Framework**

Hardware and Software Hardware Validation on Zynq

- Processor in the Loop

- Monitor data and tune parameters on hardware in real time from Simulink

- External Mode enables

Simulink control of software execution

- FPGA in the Loop

- Generate and download bitstream to Zynq programmable logic

- Validate design in hardware from Simulink

# **Radio Design Framework**

Rapid Prototyping

- Simulink Zynq Workflow for Rapid Prototyping

- Automatic code generation

- Embedded Coder generates NEON optimized code for Zynq ARM

- HDL Coder Generates

AXI IP Core for Zynq

Programmable Logic

- Visualize results using LTE Spectrum Analysis