## Strathprints Institutional Repository

Abdelsalam, Ibrahim and Adam, Grain Philip and Holliday, Derrick and Williams, Barry W. (2016) Single-stage ac–dc buck–boost converter for medium-voltage high-power applications. IET Renewable Power Generation, 10 (2). pp. 184-193. ISSN 1752-1416 , http://dx.doi.org/10.1049/iet-rpg.2015.0136

This version is available at http://strathprints.strath.ac.uk/56151/

**Strathprints** is designed to allow users to access the research output of the University of Strathclyde. Unless otherwise explicitly stated on the manuscript, Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Please check the manuscript for details of any other licences that may have been applied. You may not engage in further distribution of the material for any profitmaking activities or any commercial gain. You may freely distribute both the url (<u>http://strathprints.strath.ac.uk/</u>) and the content of this paper for research or private study, educational, or not-for-profit purposes without prior permission or charge.

Any correspondence concerning this service should be sent to Strathprints administrator: <a href="mailto:strathprints@strath.ac.uk">strathprints@strath.ac.uk</a>

This paper is a postprint of a paper submitted to and accepted for publication in IET Renewable Power Generation and is subject to Institution of Engineering and Technology Copyright. The copy of record is available at IET Digital Library

# A single-stage ac-dc buck-boost converter for medium-voltage high-power

## applications

I. Abdelsalam<sup>1,2</sup>, G.P. Adam<sup>1</sup>,D. Holliday<sup>1</sup>and B.W. Williams<sup>1</sup> Electronic and Electrical Engineering Department, University of Strathclyde, Glasgow, UK<sup>1</sup> Electrical Power Department, Arab Academy for Science and Technology and Maritime Transport, Cairo, Egypt<sup>2</sup> Email: <u>Ibrahim.abdallah@strath.ac.uk and grain.adam@strath.ac.uk.</u>

*Abstract* —This paper proposes three topologies based on single-stage three-phase ac-dc buck-boost converters suitable for medium-voltage high-power applications. The first two topologies are based on a dual three-phase buck-boost converter, with a three-winding phase-shifted transformer to achieve sinusoidal input currents, with relatively small ac filters. The limitation of these two topologies are the switching devices are exposed either to a high voltage beyond that tolerable by a single device. The third topology is based on three single-phase buck-boost converters; with their dc output terminals connected in series to generate high voltage. By using this approach, voltage stresses on the switching devices are greatly reduced, and sinusoidal input currents with nearly unity power factor is achieved over the entire operating range when using small ac filters. Analysis, PSCAD/EMTDC simulations and experimentation are used to assess the feasibility of the proposed topologies during normal operation. Major findings of this study are discussed and summarised as a comparison between the three topologies.

Key words: ac-dc converters, buck-boost converters, wind energy conversion system and back-to-back converters

## I. INTRODUCTION

AC-dc converters are used intensively as back-to-back converters in renewable energy systems such as wind and solar; dc-motor drives and dc distributed generation systems (micro-grids); and in power supplies for industrial and domestic electric appliances. Utility recognition of ac-dc conversion power quality problems, especially, harmonic currents injected into ac side, has meant practical measures are taken to improve the power factor and quality of the ac grid currents of these converters. Also, effort is being invested to develop new generations of ac-dc converters that can meet strict power quality regulations and offer the flexibilities needed in renewable power conversion systems[1-5]. Generally, three-phase ac-dc converters can be categorised as follows: buck, boost, and buck-boost converters, and single-stage and two-stage converters. In the majority of the two-stage converters, the first stage is dedicated to power factor correction (PFC) and shaping of the input current, while

the second stage is used to regulate the dc output voltage. But this category of ac-dc converters has a number of drawbacks such as: high cost and complex power circuit structures. Therefore, their application is limited.

The following part summarises research on three-phase single-stage ac-dc converters that attempted to reduce the number of active switches and overall cost. For example, the single-switch single-stage buck type converter discussed in [6, 7] is attractive, because it has a simple controller and produces highly quality continuous input currents. Its main drawback is that it operates at a high switching frequency (25 kHz [7]) and exposes the switching devices to high voltage stress due to the high peaks of the discontinuous input capacitor currents. The single-stage buck converter proposed in [8] uses two active switches exposed to half the voltage of that in [6, 7]. However, it requires a switching frequency beyond that appropriate for medium-voltage applications. The threephase conventional ac-dc boost converter presented in [9-11] has a simple circuit topology and is found in many applications. But the use of a boost converter after the diode stage restricts the scalability of this type of converter (requires a high switching frequency and the need to pre-charge the dc-side capacitor) and it has poor short-circuit protection if an external dc chopper is not incorporated at the dc terminals of the grid side converter. Reference [12] proposed a single-switch boost converter with reduced voltage stress, equal to half the output dc voltage; which is achieved by using a coupled inductor and two buffering capacitors. For higher power rating, a version that uses parallel boost stages is proposed in [13, 14]. The three-phase single-switch acdc buck-boost converter proposed in [7, 15, 16] has discontinuous input capacitor current (thus, high-voltage stress per device) and sinusoidal input current. But this approach is not suitable for high-power applications as it uses a high switching frequency of 25 kHz. Reference [17] reintroduces the three-phase buck-boost converter where the input capacitor operates in a continuous current mode and the switching frequency is reduced dramatically to 1.2 kHz to suit medium-voltage applications. However, it requires a sizable ac filter to achieve sinusoidal input current, and exposes the switching devices to high voltage stresses. The authors in [18] presented a new buck-boost ac-dc converter that uses two semiconductor switches, with reduced voltage stress.

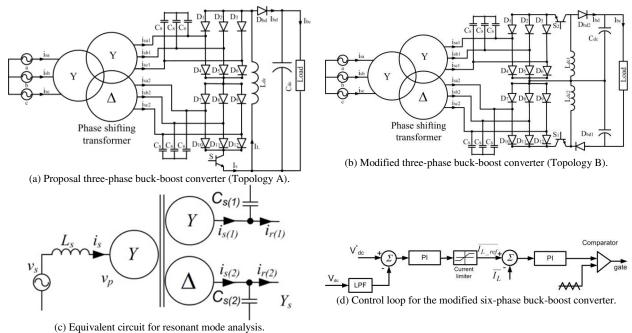

In this paper, three single-stage buck-boost converter based topologies suitable for medium-voltage high-power application are proposed. Topology 'A' is the dual three-phase buck-boost converter in Fig.1(a), which is an extension of a single-stage three-phase buck-boost converter discussed in [17]. Topology 'A' can operate at a relatively low switching frequency such as 1.2kHz. However, it requires sizable ac filters to produce sinusoidal input currents, and its main switching device and the blocking diode are exposed to voltage stress. To overcome this problem, an improved version of topology 'A' is proposed as shown in Fig.1(b) (referred to as topology 'B'), where the total voltage stress is shared evenly between two switching devices S<sub>1</sub> and S<sub>2</sub> and two blocking

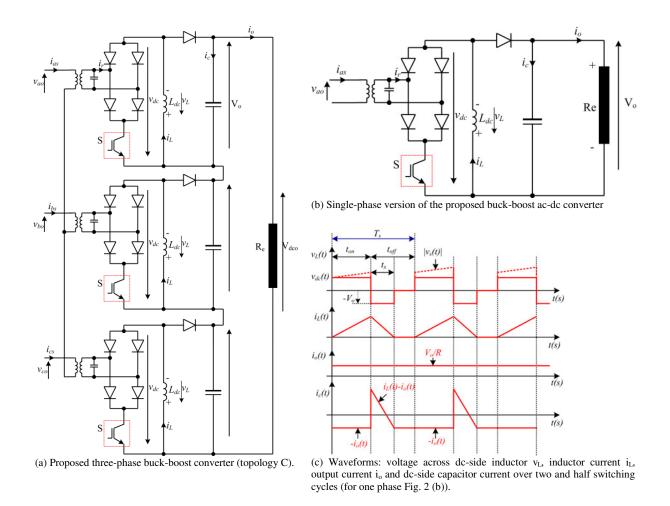

diodes  $D_{bd1}$  and  $D_{bd2}$ . Both topologies 'A' and 'B' exploit the harmonic cancelation feature of the three-phase three windings phase-shifted transformer to decrease the size of the ac side C-filter needed to produce high quality input currents. The third topology proposed in this paper is topology 'C', which consists of three singlephase buck-boost converters with dc outputs connected in series as shown in Fig. 2(a). Each sub-converter is rated at  $\frac{1}{3}$  the total converter rated power and the voltage stress per switch is reduce to the line-to-neutral voltage plus  $\frac{1}{3}$  the output voltage. Although topology 'C' can operate under continuous or discontinuous dclink inductance current modes (CCM or DCM), simulation studies show that DCM is better as it reduces the voltage stress on the main switching device and the blocking diode in each sub-converter. This is achieved with higher current stresses in these devices compared to CCM.

The three proposed topologies have the following features: buck and boost capability in a single stage with a minimum switch count, modular structure, simple control system, and sinusoidal supply current with unity power factor.

This paper is organised as follows: Section II describes the operating principle of the proposed dual three-phase ac–dc buck–boost converters (topologies 'A' and 'B'), including their control loop systems and filter design. Section III describes the operating principle of topology 'C', and establishes the basic equations that govern its steady-state operation under CCM and DCM. Its control loops are defined. Section IV uses simulation results from PSCAD/EMTDC to demonstrate the technical feasibility of topologies 'B' and 'C' (under CCM and DCM), including a comparison between topologies 'B' and 'C'. Section V presents experimental results from a 10kW prototype of topology 'C' to verify its steady state and dynamic performance during DCM operation. Conclusions and major findings are highlighted in Section VI.

#### II. DUAL THREE-PHASE BUCK-BOOST CONVERTER TOPOLOGIES 'A' AND 'B'

#### a) Circuit description

Fig.1(a) shows a medium-voltage high-power dual three-phase buck-boost converter (topology 'A'), which is an improved version of the single and three-phase buck-boost converters discussed in [17]. It consists of two cascaded three-phase diode bridges and series commutable switch 'S', see Fig.1(a). Switch 'S' is used to control the output dc voltage by modulating inductor current I<sub>L</sub>. Turning on switch 'S' boosts the energy stored in dc inductor L<sub>dc</sub>, and this stored energy supplies the load when switch 'S' is off. The proposed converter uses a three winding transformer, with secondary and tertiary windings are phase shifted 30° ( $\Delta$ /Y) from each other to attenuate the 5<sup>th</sup> and 7<sup>th</sup> harmonic currents. The ac filters (C<sub>s</sub>) connected to transformer secondary and tertiary windings are tuned to remove low-order harmonic currents not eliminated by phase shift transformer, and those

associated with the switching frequency components and their sidebands. To simplify the analysis, the rated rms line-to-line voltage of all windings are assumed equal,  $v_p = v_{s1} = v_{s2}$ ; this means the transformer turns ratios are  $N_1/N_2=1$  (for the star secondary) and  $N_1/N_3=1/\sqrt{3}$  (for the delta secondary). The average output voltage of each bridge rectifier is  $-\frac{3\sqrt{3}}{\pi}V_{Cm}$ , where  $V_{cm}$  is the peak fundamental ac voltage across the filter capacitor  $C_s$ . The negative sign reflects the inversion of the bridge output voltage with respect to the load. By using the approach described in [17, 19, 20], the average output dc voltage  $V_{dc}$  in CCM is:

$$V_{dc} = 2 \times \frac{\delta}{1 - \delta} \times \frac{3\sqrt{3}}{\pi} V_{cm}$$

(1)

where  $\delta$  represents the duty cycle of the switch 'S'. By controlling  $\delta$  over a wide range  $0 < \delta < 1$ , buck ( $\delta < \frac{1}{2}$ ) and boost ( $\delta > \frac{1}{2}$ ) operation can be achieved. The major shortcoming of the converter in Fig.1 (a) is that the blocking diode  $D_{bd}$  and switch S are exposed to extremity high voltage stresses of  $V_{dc}+2V_{Cm}$ . This may limit use of the proposed buck-boost converter to the lower end of medium-voltage applications. Topology 'B' is proposed as shown in Fig.1(b), which is an improved version of the converter in Fig.1 (a), where the problem of voltage stresses are partially solved by using two switching devices  $S_1$  and  $S_2$  and two blocking diodes  $D_{bd1}$  and  $D_{bd2}$  to evenly share the overall voltage stress. This is achieved by splitting the dc inductance  $L_{dc}$  into  $L_{dc1}$  and  $L_{dc2}$ (where  $L_{dc1}=L_{dc2}=\frac{1}{4}L_{dc}$ ), and the two dc side capacitors ( $C_{dc1}=C_{dc2}$ ) are connected as Fig.1(b). Although topology 'B' is slightly changed from topology 'A', it still maintains the simplicity and performance of the original circuit, and switches  $S_1$  and  $S_2$  receive identical gating signals.

#### b) Filter design and power factor performance

Fig.1(c) shows the equivalent circuit for resonant mode analysis, and filter admittance can written in terms of filter capacitance and transformer inductances as:

$$Y(s) = sC_{s} + \frac{1}{sL_{r} + \frac{1}{\frac{1}{sL_{s}} + \frac{sC_{s}}{s^{2}L_{r}C_{s} + 1}}}$$

(2)

where  $L_s$  is the transformer primary leakage inductance plus the inductance of the supply lines, and  $L_r$  is the transformer secondary and tertiary leakage inductances. It is possible to make the leakage inductances of the Y and  $\Delta$  transformer equal [21]. The parallel resonant frequency can be calculated from the zeros of the Y(s) admittance:

$$\omega_1 = \frac{1}{\sqrt{L_r C_s}} \tag{3}$$

$$\omega_2 = \frac{1}{\sqrt{\left(2L_s + L_r\right)C_s}} \tag{4}$$

The transformer is used to cancel the 5<sup>th</sup>, 7<sup>th</sup>, 17<sup>th</sup>, and 19<sup>th</sup> harmonic currents [22-24], and  $\omega_1$  depends on the transformer secondary leakage inductance. Since the transformer leakage inductances are known, the value of the ac-side C-filter is selected such that the cut-off frequency is placed at nine times the base frequency,  $9\omega_B$ . With the ac filter designed on this basis, simulation studies show that acceptable supply current THD is achieved over the full control range.

#### c) Control strategy

Fig.1(d) summarises the control scheme used to control the dual three-phase buck-boost converters in Fig.1(a) and (b). The control system in Fig.1(d) consists of an outer voltage loop that controls the converter total output dc voltage ( $V_{dc}$ ) and sets reference inductor current ( $I_L^*$ ); and an inner current loop that forces the dc inductor current  $I_L$  to follow its reference, and generates duty cycle  $\delta$  for the switch S or (S<sub>1</sub> and S<sub>2</sub>). The output of the second proportional-integral (PI) controller is compared with a triangular carrier wave to generate the gating signal with fixed pulse width for given operating point to control the buck-boost converter switch (S) or switches (S<sub>1</sub>and S<sub>2</sub>). Operation of switch S with fixed pulse width allows the converter output dc voltage to be controlled, but does not improve the harmonic attenuate of the input ac currents due to discontinuity of the input currents caused by the 120° conduction pattern of the diode rectifier bridges [17].

## III. THREE-PHASE BUCK-BOOST CONVERTER TOPOLOGY 'C'

#### a) Circuit description

To further reduce the voltage stresses on the semiconductor devices, the three-phase buck-boost converter proposed in Fig. 2 (a) is proposed, Topology 'C' which uses each single-phase diode bridge in series with a switch. The ac terminals of the diode bridge of each phase are connected to three single-phase transformers with isolated secondary windings, while the primary sides can be connected star or delta; however, star connection is shown in Fig. 2 (a). The co-existence of each diode bridge in series with an active switch allows the proposed converter to regulate its dc output voltage in buck and boost mode, with reduced voltage stress per active switch (S<sub>1</sub>, S<sub>2</sub> and S<sub>3</sub>) and blocking diode (D<sub>bd1</sub>, D<sub>bd2</sub> and D<sub>bd3</sub>): reduced to the line-to-neutral voltage plus  $\frac{1}{3}$  the output voltage. The proposed converter in Fig. 2 (a) can be operated in CCM or DCM. Its operation modes and control strategy in CCM are the same as discussed in [19] for a single-phase version. The output dc voltage for the three-phase buck-boost converter in Fig. 2 (a) is:

$$V_{dc} = 3 \times \frac{\delta}{1 - \delta} \times \frac{2V_{m}}{\pi}$$

(5)

- .

Fig.1: Three-phase dual buck-boost converters and their control systems.

#### b) DCM analysis

For simplicity, the analysis of the proposed converter during DCM operation is carried out on per phase basis, and then extended to the three-phase version. Per phase analysis of the output dc voltage of a single-phase fullbridge diode is adopted.

Assume the switching and supply fundamental frequencies are  $f_s$  and f, during the analysis of each switch period the supply voltage is assumed fixed, and the voltage drop in the series elements of input L-C filter is assumed to be sufficiently small to be neglectable. Fig. 2(c) shows that the ac-dc buck-boost converter being studied has three operating intervals in DCM:

First interval ( $0 < t < t_{on}$ ): This mode represents the situation when the switch S is on and the dc-link inductor  $L_{dc}$  is being energised from the supply, and dc-side capacitor supplies the load with near constant current if its capacitance is sufficiently large. In this interval, the dc-link inductor voltage and current, and dc capacitor current are:

$$\mathbf{v}_{\mathrm{L}}(t) = \left|\mathbf{v}_{\mathrm{s}}(t_{\mathrm{s}})\right| = \left|\mathbf{V}_{\mathrm{m}}\sin\omega t_{\mathrm{s}}\right| \tag{6}$$

$$\frac{di_{L}(t)}{dt} = \frac{|V_{m} \sin \omega t_{s}|}{L_{dc}}$$

(7)

$$i_{c}(t) = -\frac{V_{o}}{R}$$

(8)

After solving these equations,  $i_L(t)$  in this interval is:

$$i_{L}(t) = \frac{\left|V_{m}\sin\omega t_{s}\right|}{L_{dc}}t$$

(9)

With switching frequency  $f_s$  selected to be much higher than supply frequency f, equation 10 can be used to approximate the peak inductor current ( $I_{Lmax}$ ) at the instant when the switch S is turned off (at t=  $t_{on} = \delta T_s$ ).

$$I_{L_{max}} = \frac{\left| \nabla_{m} \sin \omega t_{s} \right|}{L_{dc}} \delta T_{s}$$

(10)

Fig. 2: Proposed three-phase ac-dc buck-boost converter.

Second interval ( $t_{on} < t < t_x$ ): This is the period when switch S is off and the dc-link inductor supplies the load and charges the dc-side capacitor, and the voltage impressed across  $L_{dc}$  is equal to the load voltage but with

negative polarity as shown in Fig. 2 (c). Thus, the dc-link inductor voltage and current, and dc capacitor current are:

$$\mathbf{v}_{\mathrm{L}}(t) = -\mathbf{V}_{\mathrm{o}} \tag{11}$$

$$\frac{\mathrm{di}_{\mathrm{L}}(t)}{\mathrm{dt}} = -\frac{\mathrm{V}_{\mathrm{o}}}{\mathrm{L}_{\mathrm{dc}}} \Rightarrow i_{\mathrm{L}}(t) = -\frac{\mathrm{V}_{\mathrm{o}}}{\mathrm{L}_{\mathrm{dc}}}(t-t_{\mathrm{on}}) + I_{\mathrm{Lmax}} = -\frac{\mathrm{V}_{\mathrm{o}}}{\mathrm{L}_{\mathrm{dc}}}(t-\delta T_{\mathrm{s}}) + \frac{\left|\mathrm{V}_{\mathrm{m}}\sin\omega t_{\mathrm{s}}\right|}{\mathrm{L}_{\mathrm{dc}}}\delta T_{\mathrm{s}}$$

(12)

$$i_{c}(t) = i_{L}(t) - i_{o}(t) = -\frac{V_{o}}{L_{dc}}(t - \delta T_{s}) + \frac{|V_{m} \sin \omega t_{s}|}{L_{dc}} \delta T_{s} - \frac{V_{o}}{R}$$

(13)

From Fig. 2 (c), $i_L(t_{on}+t_x)=0$  when the energy stored in the dc link inductor  $L_{dc}$  is exhausted; thus,  $t_x$  is:

$$t_{x} = \frac{\left|V_{m}\sin(\omega t_{s})\right|}{V_{o}}\delta T_{s}$$

(14)

Alternatively, this equation can be obtained by setting the average dc link inductor voltage to zero.

Third interval  $(t_{on}+t_x < t \le T_s)$ : This interval represents the period when the energy stored in the dc link inductor  $L_{dc}$  is fully exhausted when its current drops to zero at  $t=t_{on}+t_x$  before the next switching period and remains at zero. In this interval, inductor current and voltage are  $i_L(t)=0$  and  $v_L(t)=0$ , and the dc link capacitor current is:

$$i_{c}(t) = -i_{o} = -\frac{V_{o}}{R}$$

(15)

Considering the three intervals, the average capacitor current during one switching cycle is:

$$\bar{\iota}_{c} = \frac{1}{T_{s}} \left[ \int_{0}^{t_{on}} i_{c}(t) dt + \int_{t_{on}}^{t_{on}+t_{x}} i_{c}(t) dt + \int_{t_{on}+t_{x}}^{T_{s}} i_{c}(t) dt \right] = -\frac{V_{o}}{R} - \frac{\frac{1}{2} V_{o} t_{x}^{2} + V_{o} t_{on} t_{x} - V_{o} \delta T_{s} t_{x} - |V_{m} \sin \omega t_{s}| \delta T_{s} t_{x}}{L_{dc} T_{s}}$$

(16)

Since the input current and output dc voltage of a single-phase full-bridge diode rectifier have half wave symmetry  $(0 < \omega t < \pi)$ , the average capacitor current during one half of the supply cycle is:

$$\overline{\iota_{C_{-HC}}} = \frac{1}{\pi} \int_0^\pi \left( -\frac{V_o}{R} - \frac{1}{L_{dc}T_s} \left[ \frac{1}{2} V_o t_x^2 + V_o t_{on} t_x - V_o \delta T_s t_x - |V_m \sin \omega t_s| \delta T_s t_s \right] \right) d\omega t_s$$

(17)

$$\overline{i}_{c_{-}HC} = \frac{T_s V_m^2 \delta^2}{4L_{dc} V_o} - \frac{V_o}{R}$$

(18)

The steady state average capacitor current tends to zero; the converter voltage gain can be calculated as:

$$v_0 = \frac{1}{2} \delta Vm \sqrt{\frac{T_s R}{L_{dc}}}$$

(19)

For a given dc link inductance  $L_{dc}$ , the critical duty cycle  $\delta_c$  that defines the boundary between CCM and DCM can be obtained by setting  $t_x = T_{off} = (1 - \delta_c)T_s$  and  $|V_m \sin \omega t_s| = V_m$ . From equations (14) and (19)  $\delta_c$  is:

$$\delta_{c} = 1 - \frac{2}{\sqrt{\frac{T_{s}R}{L_{dc}}}}$$

(20)

In each switching period during DCM operation, the equivalent continuous current in the switch S and pre-filter input current are:

$$i_{s}(t) = \begin{cases} \frac{1}{2L} \delta^{2} T_{s} V_{m} \sin \omega t, & 0 \le \omega t \le \pi \end{cases}$$

(21)

$$i_{r}(t) = \begin{cases} \frac{1}{2L} \delta^{2} T_{s} V_{m} \sin \omega t, & 0 \le \omega t \le 2\pi \end{cases}$$

(22)

Equation (21) represent the equivalent continuous current in switch S, and (22) represents the fundamental component of the pre-filter input current, which is sinusoidal and in-phase with the supply voltage. Since the switched version of the input current  $i_{sr}(t)$  is contained within the envelope of the supply voltage,  $i_{sr}(t)$  only contains switching frequency harmonic components and their sidebands. This feature makes the ac-side L-C filter size smaller and simpler in design than that of the dual three-phase buck-boost converter discussed. These observations indicate that with a small ac filter and fixed duty cycle, the input current of the three-phase buck-boost converter in Fig. 2 (a) can be ensured to be sinusoidal (as there are no low-order harmonics to distort the input current).

The average and root mean square current in the switch S are:

$$\overline{I}_{S} = \frac{1}{\pi} \int_{0}^{\pi} \frac{\delta^{2} T_{S} V_{b} \sin \omega t}{2L_{dc}} d\omega t = \frac{\delta^{2} T_{s} V_{m}}{\pi L_{dc}}$$

(23)

$$I_{S\_rms} = \sqrt{\frac{1}{\pi} \int_0^{\pi} \frac{\delta^4 T_s^2 V_m^2 \sin \omega t}{4L_{dc}^2} d\omega t} = \frac{\delta^2 T_s V_m}{2\sqrt{2}L_{dc}}$$

(24)

The average and root mean square current in each diode of the single-phase bridge are:

$$\bar{I}_{D} = \frac{1}{2\pi} \int_{0}^{\pi} \frac{\delta^2 T_s V_m \sin \omega t}{2L_{dc}} d\omega t = \frac{\delta^2 T_s V_m}{2\pi L_{dc}}$$

(25)

$$I_{D_{rms}} = \sqrt{\frac{1}{2\pi}} \int_0^{\pi} \frac{\delta^2 T_s^2 V_m^2 \sin \omega t}{4L_{dc}^2} d\omega t = \frac{\delta^2 T_s V_m}{4L_{dc}}$$

(26)

Since the proposed three-phase buck-boost convert consists of three single phase modules, each phase provides  $\frac{1}{3}$  the output power, and the voltage gain  $V_{o_3ph}$  and  $\delta_{cr_3ph}$  are:

$$v_{0_{2}3 \text{ ph}} = \frac{3}{2} \delta V_{m} \sqrt{\frac{T_{s} R}{3 L_{dc}}}$$

(27)

$$\delta_{cr-3\,ph} = 1 - 2\sqrt{\frac{T_*R}{3L_{dc}}}$$

<sup>(28)</sup>

#### c) Control strategy

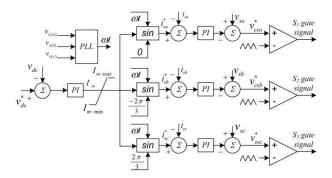

Fig. 3(a) shows the proposed controller for the converter in Fig. 2(a) under CCM, where there is one outer control loop and three inner control loops (one per phase). The outer control loop regulates the converter dc output voltage and estimates the peak fundamental current  $i_m$  required to maintain the dc link voltage at any desired level. The inner control loops provide reference currents  $(i_{sa}^*, i_{sb}^*, i_{sc}^*)$  synchronised to the grid voltage, see Fig. 3(a). In addition, to ensuring sinusoidal input currents independent of the load conditions, these inner control loops estimate the fundamental component of the ac side capacitor voltages  $(v_{csa}^*, v_{csb}^*, v_{csc}^*)$  required to force the input current to follow its control reference  $(i_{sa}^*, i_{sb}^*, i_{sc}^*)$  and ensure power balance between the ac and dc sides.

Fig. 3(b) summarises the control structure used to control the proposed converter in Fig. 2(a) under DCM operation, which consists of inner and outer control loops. The outer control loop regulates the total output dc voltage  $V_{dc}$ , where a PI controller estimates the reference peak fundamental supply current  $I_p^*$  to achieve any desired dc link voltage  $V_{dc}$ , a current limiter is added in the outer control loop to protect the converter from over load. The inner loop forces the peak of the supply current to follow its reference set by the outer loop and estimates the duty cycle  $\delta$  of switch S.

(a) Proposed controller for CCM operation

(b) Proposed controller for DCM operation .

Fig. 3: Proposed controller for topology 'C'

## IV. SIMULATION RESULTS

This section presents simulation results obtained from PSCAD/EMTDC models of the proposed buck-boost converters topologies. This simulation section consists of four parts. The first part shows the closed loop results of the proposed converter shown in Fig.1(b), while the second and the third parts show the simulation results of the proposed converter shown Fig. 2(a) under CCM and DCM respectively. The converter parameters are listed in Table 1. To highlight the features of the proposed converters, they are simulated under the same operating scenarios. Initially, the dc voltage across a 150 $\Omega$  load resistance is set to 10kV. At time t=0.75s, the load resistance reduced to 100  $\Omega$  to test the dynamic response of both converters.

| Parameter                 | Topologies 'B'                                    | Topology 'C' CCM                             | Topology 'C' DCM                             |

|---------------------------|---------------------------------------------------|----------------------------------------------|----------------------------------------------|

| Rated power               | 1MW                                               | 1MW                                          | 1MW                                          |

| Supply voltage            | 3.3 kV L-L                                        | 3.3kV L-L                                    | 3.3kV L-L                                    |

| Supply frequency          | 50Hz                                              | 50Hz                                         | 50Hz                                         |

| Switching frequency       | 1.2kHz                                            | 5kHz                                         | 2.4kHz                                       |

| Transformer rated power   | 5MVA phase shift transformer                      | Three single-phase<br>transformers 1.7MVA    | Three single-phase<br>transformers 1.7MVA    |

| Transformer rated voltage | Primary side 3.3kV / two<br>secondary sides 3.3kV | Three single-phase<br>transformers 1.9/1.9kV | Three single-phase<br>transformers 1.9/1.9kV |

| Ac-side C-filter          | Two 36 µF three-phase bank(0.123MVAr)             | Three 5µF<br>(0.017MVAr)                     | Three 50µF<br>(0.17MVAr)                     |

| dc-side inductance        | Central taped 8mH inductance                      | Three 3mH                                    | Three 750µH                                  |

| dc-side capacitance       | Two 2200 μF                                       | Three 2200 µF                                | Three 2200 µF                                |

Table 1: Simulation parameters of the three buck-boost converter topologies presented in Fig.1(b) and Fig. 2(a).

a) Buck-boost converter (topology 'B')

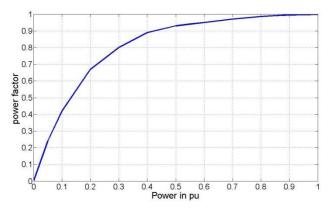

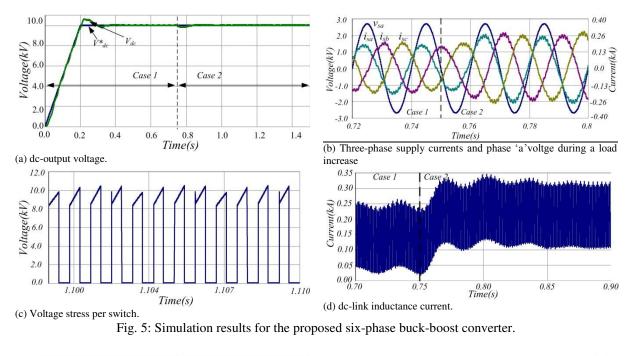

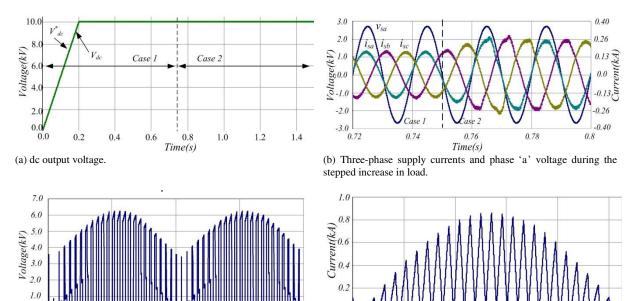

The simulation results for topology 'B' are shown in Fig. 5. The transformer primary side inductance plus the supply inductance is 0.15pu, and the secondary leakage inductance is 0.1 pu for each winding. The ac-side C-filter value is selected such that the cut-off frequency is nine times the base frequency ( $9\omega_B$ ), according to equation (3), the capacitance is 0.123pu. Using these filter parameters, the plot for the power factor profile in Fig. 4 is obtained from simulations of topology 'B' when the load is varied from no load to full load. This profile is also valid for topology 'A', independent of buck or boost modes. With this filter design topologies 'A' and 'B' operate at unity power factor from 90% of full load to rated load. The input power factor is higher than 0.95 lead when loading is between 60% to 90% of rated power, see Fig. 5(b).

Fig. 4: Power factor profile of topologies 'A' and 'B'

Fig. 5(a) show that the proposal converter is able to track the reference output voltage, with minimum overshoot when the load resistance is halved. Fig. 5(b) shows the three-phase supply currents and phase 'a' voltage during the step increase in load. From Fig. 5 (b) the proposed converter draws sinusoidal current from the supply, with 0.935 power factor leading in case 1 and unity power factor when the load resistance decreases to  $100\Omega$ . The switch S is exposed to a voltage stress of 10kV approximately; see Fig. 5(c). Fig. 5(d) shows the dc-link inductor current where the current increases to compensate the step load change

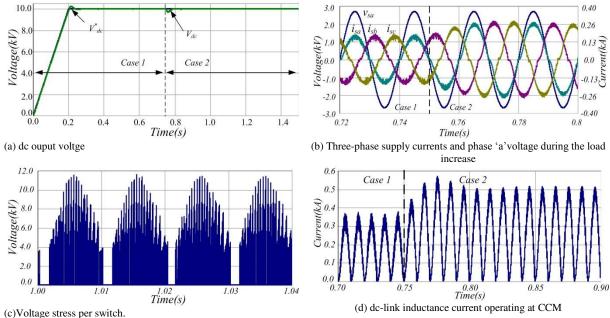

#### b) Buck-boost converter (topology 'C') in CCM

The closed loop results of the converter shown in Fig. 2(a) under CCM conditions are shown in Fig. 6. Fig. 6(a) shows the proposed converter is able to force its dc output voltage to follow the reference voltage in buck and boost modes, including when the load resistance is decreased from  $150\Omega$  to  $100 \Omega$ . The under-shoot observed in Fig. 6(a) takes longer to be corrected, due to the large dc side inductances needed for CCM. These inductors do not allow rapid dc current change; thus, produce a slowed dynamic performance compared to the DCM case to be presented in the following subsection. Fig. 6(b) shows samples of the three-phase current inputs and phase 'a' voltage, all zoomed around the instant when the load resistance changes. Fig. 6(c) shows a sample of the voltage stress across the switch S<sub>1</sub>. The voltage stress across this switch is comparable to the theoretical value stated in section III, with a magnitude associated with a small ac-side C-filter (discontinuous input capacitor currents). Fig 4(d) shows the dc-side inductor current is continuous as expected and increases when the load resistance is decreased.

#### c) Buck-boost converter (topology C) under DCM operating conditions

Fig. 7 shows the closed loop operation waveforms of the three-phase buck-boost converter operating under DCM. Fig. 7(a) shows that the converter is able to track the reference output voltage, including during a step change in load resistance, and this is achieved rapidly and with minimum under-shoot (compared to CCM presented in subsection IVb). From Fig. 7(b) the supply current is sinusoidal and in phase with the supply voltage. Fig. 7(c) shows the voltage stress on switch  $S_1$  is inline with the theoretical prediction stated in section

III. Fig. 7(d) shows a zoomed version of the dc-link inductor current, and the converter is seen to operate on

boundary between CCM and DCM.

1.110 Time(s) 1.10 (c) Voltage stress per switch.

0.0

100

(d) dc-link inductor current. Fig. 7: Simulation results of the perofrmance of the three-phase buck-boost converter under DCM.

1.120

0.0

1.000

1.006 Time(s)

1 004

Comparison between the proposed buck-boost converters in Fig.1 (a) and Fig. 2 (a) d)

1.115

- The three-phase converter under DCM has a faster dynamic response due to using smaller dc-side inductance and a medium size ac-side C-filter, see Fig. 5(a), Fig. 6(a) and Fig. 7 (a)

- Sinusoidal current with near unity pf is achieved with topology 'C' in both CDM and DCM modes, • over a wide range of operating conditions. This is unlike the dual three-phase buck-boost converters in Fig. 1(a) and (b) that ensure nearly unity power factor over a limited range according to a pre-defined profile.

- Topology 'C' under DCM has lower semiconductor voltage stress, but the highest current stress per switch.

- For the same supply voltage and rated output power, the three-phase buck-boost converter (topologies 'A' and 'B') have the lowest average dc-link inductor current as shown in Fig.8. This is because their rectified dc output voltages are higher than that of the three series connected single phase case, by a

factor of  $\sqrt{\frac{2}{3}}$ .

The simulation results in Fig. 5, Fig. 6 and Fig. 7 show that the proposed buck-boost converters provide highquality sinusoidal input current with stable dc output voltage. This qualifies the proposed converters to operate as an interfacing converter for permanent magnetic wind-turbine generators, and for operation as a front-end converter for grid-connected current and voltage source converters, with black-start and shutdown capabilities. Also the modified dual three-phase buck-boost converter (Topology 'B') has the advantage of lower current stress per device, and the three-phase buck-boost converters under DCM (Topology 'C') has the advantages of lower voltage stress per switch and lower supply current THD.

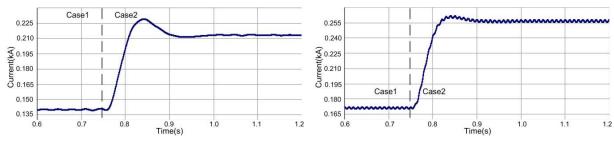

(a) Average dc-link inductor current of topology 'B'.

(b) Average dc-link inductor current of topology 'C'

Fig.8: Average dc-link inductor current.

## V. EXPERIMENTAL RESULTS

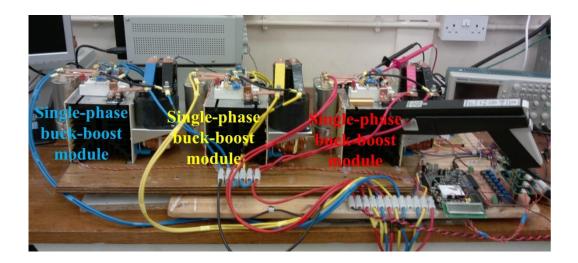

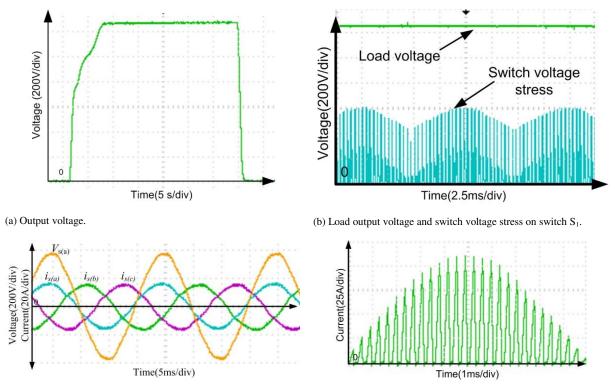

A 10kW prototype of the proposed three-phase buck-boost converter (topology 'C', see Fig. 9) was assessed to establish its steady state and dynamic performance during DCM operation, with system parameters listed in Table 2. To demonstrate the soft start and shut-down capability, the output dc link voltage ( $V_{dco}$ ) is increased from 0 to 1250V and then reduce to zero within 30s. The results are displayed in Fig. 10. From Fig. 10(a) the proposed converter provides high boost with good dynamic response during soft start up, steady state and shutdown. Fig. 10 (b) shows the steady state output voltage and the voltage stress across switch S, where the voltage stress across the switch is 600V, as expected  $(130\sqrt{2} + \frac{1}{3} \times 1250 \approx 600 \text{ V})$ , which is much lower than in topologies A and B). Fig. 10(c) shows that the supply current is sinusoidal with nearly unity power factor (this is achieved without any dedicated control to force unity power factor operation). The dc-side inductor current ( $i_L$ ) in Fig. 10(d) confirms DCM operation of the proposed buck-boost converter.

| Parameter                 | Value                   |  |

|---------------------------|-------------------------|--|

| Supply voltage            | $260V_{L\_N}$           |  |

| Transformer rated power   | 8kVA                    |  |

| Transformer rated voltage | 440/220V <sub>L-L</sub> |  |

| ac-side capacitance       | 80µF                    |  |

| dc-side inductance        | 330 µH                  |  |

| dc-side capacitance       | 2200 µF                 |  |

Table 2 Experimental setup parameters.

Fig. 9: Experimental test rig.

(c) Three-phase supply currents and phase 'a' voltge at steady state. (d) dc-link inductor current.

Fig. 10: Waveforms showing the overall performance of the proposed three-phase buck-boost converter.

## VI. CONCLUSION

In this paper, three single-stage three-phase ac-dc buck-boost converter topologies suitable for high-power medium-voltage applications were proposed. The ac side filter design for topologies 'A' and 'B' ensures high power factor at rated power, and low input current THD. They expose some of the switching devices to excessive voltage stress. The simulation and experiments conducted on topology 'C' under DCM showed that it can operate both in buck and boost modes, likes topologies 'A' and 'B', but with reduced voltage stress on the

blocking diodes and switch S. Also, it has better harmonic performance and input power factor profile, from noload to full-load conditions, than topologies 'A' and 'B'. But the switching devices are exposure to higher current stresses. The theory, simulations, and experimental results presented establish that the proposed ac-dc buck-boost converters are viable for medium-voltage, high-power, ac-dc conversion applications, including grid interfacing of wind energy systems.

## VII. REFERENCES

- G. K. Andersen and F. Blaabjerg, "Current programmed control of a single-phase two-switch buckboost power factor correction circuit," Industrial Electronics, IEEE Transactions on, vol. 53, pp. 263-271, 2006.

- [2] F. Q. Wang, H. Zhang, and X. K. Ma, "Intermediate-scale instability in two-stage power-factor correction converters," Power Electronics, IET, vol. 3, pp. 438-445, 2010.

- [3] A. El Aroudi, M. Orabi, R. Haroun, and L. Martinez-Salamero, "Asymptotic Slow-Scale Stability Boundary of PFC AC–DC Power Converters: Theoretical Prediction and Experimental Validation," Industrial Electronics, IEEE Transactions on, vol. 58, pp. 3448-3460, 2011.

- [4] L. Yu-Kang, Y. Shang-Chin, and L. Chung-Yi, "A High-Efficiency AC-to-DC Adaptor With a Low Standby Power Consumption," Industrial Electronics, IEEE Transactions on, vol. 55, pp. 963-965, 2008.

- [5] M. I. Marei, I. Abdallah, and H. Ashour, "Transformerless uninterruptible power supply with reduced power device count," Electric Power Components and Systems, vol. 39, pp. 1097-1116, 2011.

- [6] Y. Jang and R. W. Erickson, "New single-switch three-phase high-power-factor rectifiers using multiresonant zero-current switching," Power Electronics, IEEE Transactions on, vol. 13, pp. 194-201, 1998.

- [7] E. H. Ismail and R. Erickson, "Single-switch 3φ PWM low harmonic rectifiers," Power Electronics, IEEE Transactions on, vol. 11, pp. 338-346, 1996.

- [8] S. K. Bassan, D. S. Wijeratne, and G. Moschopoulos, "A Three-Phase Reduced-Switch High-Power-Factor Buck-Type Converter," Power Electronics, IEEE Transactions on, vol. 25, pp. 2772-2785, 2010.

- [9] R. L. Alves and I. Barbi, "Analysis and Implementation of a Hybrid High-Power-Factor Three-Phase Unidirectional Rectifier," Power Electronics, IEEE Transactions on, vol. 24, pp. 632-640, 2009.

- [10] C. Jui-Yuan, C. Yuan-Chih, and L. Chang-Ming, "On the Switched-Reluctance Motor Drive With Three-Phase Single-Switch Switch-Mode Rectifier Front-End," Power Electronics, IEEE Transactions on, vol. 25, pp. 1135-1148, 2010.

- [11] Y. Kai, R. Xinbo, Z. Chi, and Y. Zhihong, "Three-phase single-switch boost PFC converter with high input power factor," in Energy Conversion Congress and Exposition (ECCE), 2010 IEEE, 2010, pp. 2921-2928.

- [12] J. Yu Lin, "Single switch three-phase ac to dc converter with reduced voltage stress and current total harmonic distortion," Power Electronics, IET, vol. 7, pp. 1121-1126, 2014.

- [13] S. Weiwei, L. Hui, and J. Jiuchun, "Analysis and implementation of instantaneous current control for multiple boost converter in WECS," in Applied Power Electronics Conference and Exposition, 2008. APEC 2008. Twenty-Third Annual IEEE, 2008, pp. 1490-1495.

- [14] S. Kim and P. N. Enjeti, "Control of multiple single-phase PFC modules with a single low-cost DSP," Industry Applications, IEEE Transactions on, vol. 39, pp. 1379-1385, 2003.

- [15] J. Yungtaek and R. W. Erickson, "New single-switch three-phase high power factor rectifiers using multi-resonant zero current switching," presented at the Applied Power Electronics Conference and Exposition, 1994. APEC '94. Conference Proceedings 1994., Ninth Annual, 1994.

- [16] J. Yungtaek and R. W. Erickson, "New single-switch three-phase high power factor rectifiers using multi-resonant zero current switching," in Applied Power Electronics Conference and Exposition, 1994. APEC '94. Conference Proceedings 1994., Ninth Annual, 1994, pp. 711-717 vol.2.

- [17] I. Abdelsalam, G. P. Adam, D. Holliday, and B. W. Williams, "Three-phase ac-dc buck-boost converter with a reduced number of switches," IET Renewable Power Generation, 2015.

- [18] D. Wijeratne and G. Moschopoulos, "A novel three-phase buck-boost ac-dc converter," in Applied Power Electronics Conference and Exposition (APEC), 2011 Twenty-Sixth Annual IEEE, 2011, pp. 513-520.

- [19] I. Abdelsalam, G. P. Adam, D. Holliday, and B. W. Williams, "Single-stage, single-phase, ac-dc buckboost converter for low-voltage applications," Power Electronics, IET, vol. 7, pp. 2496-2505, 2014.

- [20] H. Rashid, Power Electronics: Circuits, Devices, and Applications: Pearson/Prentice Hall, 2004.

- [21] X. Yuan, W. Bin, F. A. Dewinter, and R. Sotudeh, "A dual GTO current-source converter topology with sinusoidal inputs for high-power applications," Industry Applications, IEEE Transactions on, vol. 34, pp. 878-884, 1998.

- [22] B. Wu, High-power converters and AC drives: John Wiley & Sons, 2006.

- [23] J. R. Rodriguez, J. W. Dixon, J. R. Espinoza, J. Pontt, and P. Lezana, "PWM regenerative rectifiers: state of the art," Industrial Electronics, IEEE Transactions on, vol. 52, pp. 5-22, 2005.

- [24] I. Abdelsalam, G. P. Adam, D. Holliday, and B. W. Williams, "Assessment of a wind energy conversion system based on a six-phase permanent magnet synchronous generator with a twelve-pulse PWM current source converter," in ECCE Asia Downunder (ECCE Asia), 2013 IEEE, 2013, pp. 849-854.