## Strathprints Institutional Repository

Sha, Jin and Xu, Duo and Chen, Yiming and Xu, Jianping and Williams, Barry W. (2015) A peak capacitor current pulse-train controlled buck converter with fast transient response and a wide load range. IEEE Transactions on Industrial Electronics. ISSN 0278-0046 , http://dx.doi.org/10.1109/TIE.2015.2494851

This version is available at http://strathprints.strath.ac.uk/54876/

**Strathprints** is designed to allow users to access the research output of the University of Strathclyde. Unless otherwise explicitly stated on the manuscript, Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Please check the manuscript for details of any other licences that may have been applied. You may not engage in further distribution of the material for any profitmaking activities or any commercial gain. You may freely distribute both the url (<u>http://strathprints.strath.ac.uk/</u>) and the content of this paper for research or private study, educational, or not-for-profit purposes without prior permission or charge.

Any correspondence concerning this service should be sent to Strathprints administrator: <a href="mailto:strathprints@strath.ac.uk">strathprints@strath.ac.uk</a>

# A Peak Capacitor Current Pulse-Train Controlled Buck Converter with Fast Transient Response and a Wide Load Range

Jin Sha, Duo Xu, Yiming Chen, Jianping Xu and Barry W. Williams

Abstract—It is known that ripple-based control of a switching dc-dc converter benefits from a faster transient response than a conventional PWM control switching dc-dc converter. However, ripple-based control switching dc-dc converters may suffer from fast-scale oscillation. In order to achieve fast transient response and ensure stable operation of a switching dc-dc converter over a wide load range, based on a conventional pulse train control technique, a peak capacitor current pulse train (PCC-PT) control technique is proposed in this paper. With a buck converter as an example, the operating modes, steady-state performance and transient respond performance of a PCC-PT controlled buck converter are presented and assessed. To eliminate fast-scale oscillation, circuit and control parameter design consideration are given. An accurate discrete iteration model of a PCC-PT controlled buck converter is established, based on which, the effects of circuit parameters on stability of converter operating in a DCM mode, mixed DCM-CCM mode, and CCM mode are studied. Simulation and experimental results are presented to verify the analysis results.

### Index Terms— Capacitor current feedback, pulse train control, switching DC-DC converter, wide load range

#### I. INTRODUCTION

**S** WITCHING DC-DC converters have been widely used in portable electronic devices, such as mobile phones, notebooks and tablet PC. In some applications, the load power of switching dc-dc converters varies widely and rapidly [1-3]. Various control techniques, such as  $V^2$  control, constant-ontime (COT) control or constant-off-time (CFT) control, and pulse train (PT) control [4-10], have been reported to improve transient response speed of switching dc-dc converters. These control techniques, called 'ripple-based control' techniques [11], regulate the output voltage of switching DC-DC

This work was supported by the National Natural Science Foundation of China under Grant (51177140), the Fundamental Research Funds for the Central Universities under grant (2682013ZT20) and National Natural Science Foundation of China under Grant (51407054).

J. Sha, D. Xu, Y. Chen, J. Xu are with the Key Laboratory of Magnetic Suspension Technology and Maglev Vehicle, Ministry of Education, School of Electrical Engineering, Southwest Jiaotong University, Chengdu 610031, China (e-mail: shajin1-3@163.com; duoxu215@163.com; chen90sky@163.com; jpxu-swjtu@163.com).

B. Williams is with the Department of Electronic and Electrical Engineering, Strathclyde University, Glasgow, UK (e-mail: barry.williams@strath.ac.uk). converters by using output voltage ripple. Ripple-based control techniques do not require an error amplifier and its associated compensation circuit, thus, they benefit from simple control circuit design, fast transient response, and high reliability.

However, ripple-based control techniques of switching DC-DC converters usually suffer from fast-scale instability [12]. The V<sup>2</sup> controlled buck converter has the sub-harmonic instability issue when the duty ratio D <  $\frac{1}{2}$  [5]. COT and CFT controlled buck converter become unstable and suffer fast-scale oscillation when the time constant of output capacitor R<sub>ESR</sub>C, where R<sub>ESR</sub> is equivalent series resistance (ESR) of output capacitor C, is smaller than  $\frac{1}{2}\tau_{on}$  and  $\frac{1}{2}\tau_{off}$  ( $\tau_{on}$  and  $\tau_{off}$  are on and off times of the COT and CFT control respectively) [6, 7, 10]. For a PT controlled buck converter, the ESR also significant affects control performance, with fast-scale oscillation when the ESR is small, but disappears when the ESR is large enough [13].

Studies of critical ESR have been recently reported, which provide guidelines for the design of ripple-based controlled switching DC-DC converters [4, 10, 13]. However, critical ESR is derived based on ideal conditions. The fast-scale oscillation phenomenon may still occur even when critical ESR is satisfied. In addition, larger output capacitor ESR produces larger output voltage ripple. To avoid such fast-scale oscillation, some control techniques, such as COT control with added inductor current ramp [7] and PT control with inductor current ripple injection feedback (ICRIF) [13], have been proposed. These improved control techniques combine inductor current with output voltage ripple for output voltage regulation. In this paper, based on a conventional PT control technique [14], a peak capacitor-current PT (PCC-PT) control technique is proposed. Fast-scale oscillation in the conventional PT controlled CCM buck converter is eliminated in the PCC-PT controlled buck converter. Moreover, the PCC-PT controlled buck converter benefits from simple design, fast transient response, small output voltage ripple, and a wide load range.

This paper is organized as follows. The control principle and corresponding operating modes of the PCC-PT control technique are presented in Section II. Section III addresses stability analysis of the PCC-PT controlled buck converter. The converter's output voltage variation, output power range and line and load regulation are studied, and circuit parameter

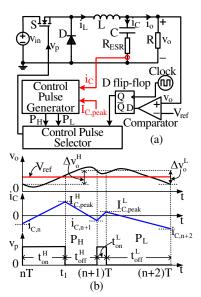

Fig. 1. PCC-PT controlled buck converter: (a) schematic diagram and (b) time domain waveforms of PCC-PT controlled buck converter.

design consideration is presented. A discrete iteration model of the buck converter is established in Section IV. Upon this model, circuit parameter effects on stability performance of PCC-PT controlled buck converter operating in DCM mode, mixed DCM-CCM mode, and CCM mode are studied. In Section V, steady-state and transient response simulation and experimental results are presented to verify the analysis.

#### II. PCC-PT CONTROL TECHNIQUE

#### A. PCC-PT Control Technique Principle

Fig. 1 shows the schematic diagram and time domain waveforms of the PCC-PT controlled buck converter. At the start of each switching cycle, in the outer control loop, output voltage  $v_o$  is sampled and compared with reference voltage  $V_{ref}$  to determine whether high power control pulse  $P_H$  or low power control pulse  $P_L$  should be selected as the active control pulse in this switching cycle. As shown in Fig. 1(b), at t=nT,  $v_o$  is lower than  $V_{ref}$ ,  $P_H$  is selected as the active control pulse to increase the output voltage. Similarly, at t=(nT+1),  $v_o$  is higher than  $V_{ref}$ ,  $P_L$  is selected as the active control pulse to decrease the output voltage.

In the inner control loop, capacitor current  $i_C$  is sensed and compared with reference peak current  $I_{C, peak}$  to determine when to turn off switch S. For buck converter,  $i_L=i_C+i_o$ , where output current  $i_o=v_o/R$  can be considered as a constant in steady-state. Thus, the inductor current ripple flows through the output capacitor, i.e.,  $i_C$  is in phase with  $i_L$ . At the start of a switching cycle, switch S is turned on,  $i_C$  increases, and S is turned off when  $i_C$  increases to  $I_{C, peak}$ , as shown in Fig. 1(b). For high power control pulse  $P_H$ ,  $I_{C, peak} = I_{C, peak}^H$ , and for low power control pulse  $P_L$ ,  $I_{C, peak} = I_{C, peak}^L$ , that is

$$I_{C, peak} = \begin{cases} I_{C, peak}^{H} & \text{if } v_{o} \leq V_{ref} \\ I_{C, peak}^{L} & \text{if } v_{o} > V_{ref} \end{cases}$$

(1)

where  $I_{C, peak}^{H} > I_{C, peak}^{L}$ .

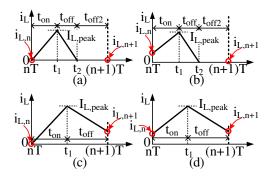

Fig. 2. Different inductor current modes: (a)  $i_{L,n}=0$  and  $i_{L,n+1}=0$ , (b)  $i_{L,n}\neq 0$  and  $i_{L,n+1}=0$ , (c)  $i_{L,n}=0$  and  $i_{L,n+1}\neq 0$ , and (d)  $i_{L,n}\neq 0$  and  $i_{L,n+1}\neq 0$ .

PCC-PT control and conventional PT control have the same outer control loop [8, 9], but a different inner control loop, where PCC-PT controller utilizes capacitor current as the feedback signal to control the turn-off of pulses  $P_H$  and  $P_L$ .

In one switching cycle, the output voltage variation is  $\Delta v_o = v_o((n+1)T) - v_o(nT)$ . According to the principle of PCC-PT control technique, control pulse P<sub>H</sub> should be applied to make the output voltage increase, that is, output voltage variation  $\Delta v_o^{H} > 0$ . Similarly, control pulse P<sub>L</sub> should be applied to make the output voltage decrease, that is, output voltage variation  $\Delta v_o^{L} < 0$ . PCC-PT operates in period-n states with control pulses P<sub>H</sub> and P<sub>L</sub> in n successive switching cycles constituting a controlled pulse repetition cycle, as its output voltage variation  $\Delta v_o^{L}$ , rather than period-1 in the PWM switching converter [9]. Let the number of P<sub>H</sub> and  $\mu_L$  in a control pulse repetition cycle be denoted as  $\mu_H$  and  $\mu_L$  respectively, then  $\mu_H$  and  $\mu_L$  satisfy  $\mu_H/\mu_L = \Delta v_o^L / \Delta v_o^H$  [15], and the control pulse repetition cycle period T<sub>r</sub> is T<sub>r</sub> = ( $\mu_H + \mu_L$ )T.

#### B. Operating Modes of PCC-PT Controlled Buck Converter

Let  $i_{L, n}$  and  $i_{L, n+1}$  denote the inductor currents at the beginning of the n<sup>th</sup> and (n+1)<sup>th</sup> switching cycle respectively. For inductor current  $i_L$  of the PCC-PT controlled buck converter, there are four inductor current operation cases, as shown in Fig. 2,

- Case 1:  $i_{L,n} = 0$  and  $i_{L,n+1} = 0$ , as shown in Fig. 2(a);

- Case 2:  $i_{L, n} \neq 0$  and  $i_{L, n+1} = 0$ , as shown in Fig. 2(b);

- Case 3:  $i_{L,n} = 0$  and  $i_{L,n+1} \neq 0$ , as shown in Fig. 2(c);

- Case 4:  $i_{L,n} \neq 0$  and  $i_{L,n+1} \neq 0$ , as shown in Fig. 2(d).

Assume output voltage ripple is small enough to be ignored, that is, the output voltage can be considered as constant in a switching cycle. As  $i_L=i_C+i_o$  and  $i_o=v_o/R$ , the peak inductor current  $I_{L, peak}=I_{C, peak}+v_o/R$ .

If  $t_{on}+t_{off} < T$ ,  $i_{L, n+1}=0$ , which corresponds to Case 1 and 2, as shown in Fig. 2(a) and (b). In Cases 1 and 2,  $i_L(t)$  in the n<sup>th</sup> switching cycle are

$$\dot{\mathbf{u}}_{L}(t) = \dot{\mathbf{u}}_{L,n} + \frac{(\mathbf{v}_{in} - \mathbf{v}_{o})t}{L}, \quad [nT, nT + t_{on}]$$

(2a)

$$i_{L}(t) = I_{L, peak} - \frac{V_{o}}{L}t, [nT + t_{on}, nT + t_{on} + t_{off}]$$

(2b)

$$i_{L}(t) = 0, [nT + t_{on} + t_{off}, (n+1)T]$$

(2c)

As  $i_L(nT+t_{on}) = I_{L, peak}$ , from (2), the time durations  $t_{on}$ ,  $t_{off}$  and  $t_{off2}$  of the PCC-PT controlled buck converter in Fig. 2(a) and (b) can be calculated as

$$t_{on} = \frac{L(I_{C, peak} - i_{L, n} + v_o / R)}{v_{.} - v},$$

(3a)

$$t_{off} = \frac{L(I_{C, peak} + v_o / R)}{v_o}, \qquad (3b)$$

$$\mathbf{t}_{\rm off2} = \mathbf{T} - \mathbf{t}_{\rm on} - \mathbf{t}_{\rm off} \,. \tag{3c}$$

If ton and toff in Eq. (3) satisfy  $t_{on}+t_{off} > T$ ,  $i_{L, n+1} > 0$ , which corresponds to Cases 3 and 4, as shown in Fig. 2(c) and (d). In Cases 3 and 4, in the n<sup>th</sup> switching cycle,  $i_L(t)$  and the time durations  $t_{on}$  and  $t_{off}$  should be rewritten as

$$i_{L}(t) = i_{L,n} + \frac{V_{in} - V_{o}}{L}t, \qquad [nT, nT + t_{on}]$$

(4a)

$$i_{L}(t) = (I_{C, peak} + \frac{V_{o}}{R}) - \frac{V_{o}}{L}t, [nT + t_{on}, (n+1)T]$$

(4b)

$$t_{on} = \frac{L(-i_{L,n} + I_{C,peak} + v_o / R)}{v_{in} - v_o},$$

(4c)

$$\mathbf{t}_{\rm off} = \mathbf{T} - \mathbf{t}_{\rm on}. \tag{4d}$$

When  $t_{on}$  and  $t_{off}$  in Eq. (3) satisfy  $t_{on}+t_{off}=T$ ,  $i_{L, n+1}=0$ , there exists an inductor current boundary. From (3a) and (3b), such an inductor current boundary can be written as

$$\frac{L(I_{C, peak} - i_{L, n} + v_o / R)}{v_{in} - v_o} + \frac{L(I_{C, peak} + v_o / R)}{v_o} - T = 0$$

(5a)

Let R in (5a) be variable, and the right part of the equation in (5a) be f(R), then

f

$$F(\mathbf{R}) = (\mathbf{RLI}_{C, \text{ peak}} + \mathbf{Lv}_{o} - \mathbf{Rv}_{o}\mathbf{T})\mathbf{v}_{in}$$

$$+ (\mathbf{Rv}_{o}\mathbf{T} - \mathbf{Li}_{L, n})\mathbf{v}_{o}$$

(5b)

$$= 0$$

where  $f(R) = f_L(R)$  for the low power control pulse  $P_L$ , and  $f(R) = f_H(R)$  for the high power control pulse  $P_H$ . When f(R)<0,  $i_{L,n+1}<0$ ; and when f(R)>0,  $i_{L,n+1}>0$ .

Thus, in a switching cycle, when  $i_{L, n}=0$ , f(R)<0, which corresponding to Case 1 as shown in Fig. 2(a), means the converter operates in a DCM in this switching cycle; when  $i_{L,n}\neq 0$ , f(R)>0, which corresponding to Case 4, as shown in Fig. 2(d), means the converter operates in a CCM in this switching cycle.

As the PCC-PT controlled buck converter operates in period-n states rather than period-1, that is, control pulses  $P_H$  and  $P_L$  in n successive switching cycles constituting a control pulse repetition cycle, rather than period-1 in a PWM switching converter [9]. In a control pulse repetition cycle, the PCC-PT controlled buck converter may operate in DCM, CCM and mixed DCM-CCM, herein mixed DCM-CCM is defined as the operating mode when both CCM and DCM exists in a control pulse repetition cycle. In mixed DCM-CCM,  $i_{L,n}\neq 0$ , f(R)<0 (corresponding to Case 2 as shown in Fig. 2(c)) may

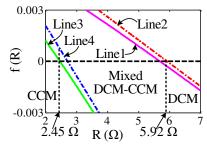

Fig. 3. The operating modes and corresponding borders of PCC-PT controlled buck converter.

occur. Thus, different from a PWM controlled buck converter which has two operating modes: DCM and CCM, the PCC-PT controlled buck converter has three operating modes: DCM, CCM and mixed DCM-CCM. When all switching cycles of a control pulse repetition cycle satisfy  $i_{L,n}=0$ ,  $f_L(R)<0$  and  $f_H(R)<0$ , the converter operates in DCM; when all switching cycles of a control pulse repetition cycle satisfy  $i_{L,n}\neq 0$ ,  $f_L(R)>0$  and  $f_H(R)>0$ , the converter operates in CCM; and when none of these conditions are satisfied, the converter operates in mixed DCM-CCM.

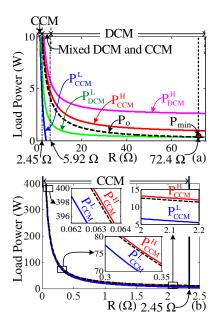

Fig. 3 shows the distributions of CCM, DCM and mixed DCM-CCM operating modes with the main circuit parameters as  $v_{in}=20V$ ,  $v_{ref}=5V$ ,  $L=80\mu$ H, C=440 $\mu$ F, and the controller parameters of the PCC-PT as T=50 $\mu$ s,  $I_{peak}^{H}=1.5A$ ,  $I_{peak}^{L}=0.5A$ . In Fig. 3, Line 1 is  $i_{L, n} \neq 0$ ,  $f_{H}(R)$ ; Line 2 is  $i_{L, n} = 0$ ,  $f_{H}(R)$ ; Line 3 is  $i_{L, n} \neq 0$ ,  $f_{L}(R)$ ; and Line 4 is  $i_{L, n} = 0$ ,  $f_{L}(R)$ .

From Fig. 3, when  $R < 2.45 \Omega$ , both lines 1 and 3 are above zero, that is,  $i_{L, n} \neq 0$ ,  $f_H(R) > 0$  and  $f_L(R) > 0$ , the converter operates in CCM. When  $R > 5.92 \Omega$ , both lines 2 and 4 are below zero, that is,  $i_{L, n} = 0$ ,  $f_H(R) < 0$  and  $f_L(R) < 0$ , the converter operates in DCM. When 2.45  $\Omega < R < 5.92 \Omega$ , the converter operates in mixed DCM-CCM.

#### **III. STEADY-STATE ANALYSIS**

A. Output Voltage Variations of the PCC-PT Controlled Buck Converter

From the discussion in Section II, the PCC-PT controlled buck converter has four inductor current operation cases, the only difference between Case 1 (Case 3) and Case 2 (Case 4) is inductor current  $i_{L, n}$  at the beginning of switching cycle. When  $i_{L, n} = 0$ , Case 1 is the same as Case 2, and Case 3 is the same as Case 4. Thus, for convenience, only Cases 2 and 4 are analyzed in this section, and Cases 1 and 3 can be analyzed by considering  $i_{L, n} = 0$ .

#### 1) Output Voltage Variation of Case 2 (Case 1)

As  $i_C = i_L - i_o$ , from (2)

$$i_{C}(t) = i_{C,n} + \frac{v_{in} - v_{o}}{L}t \quad [nT, nT + t_{on}],$$

(6a)

$$\dot{H}_{C}(t) = I_{C, peak} - \frac{V_{o}}{L}t [nT + t_{on}, nT + t_{on} + t_{off}]$$

(6b)

$$i_{\rm C}(t) = -\frac{V_{\rm o}}{R} [nT + t_{\rm on} + t_{\rm off}, (n+1)T]$$

(6c)

where  $i_{C, n} = i_{L, n} - v_0/R$  is the capacitor current at the beginning

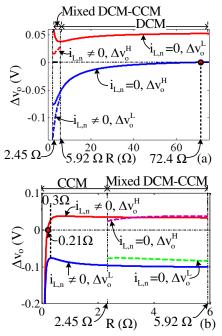

Fig. 4. Output voltage variations of the PCC-PT controlled buck converter: (a) DCM and mixed DCM-CCM and (b) mixed DCM-CCM and CCM.

of a switching cycle. Thus when  $i_{L, n} = 0$ ,  $i_{C, n} = -v_0/R$ .

From (3) and (6), output voltage variation  $\Delta v_0$  within one switching cycle is

$$\Delta v_{o} = \frac{1}{C} \int_{(n+1)T}^{nT} i_{C} dt$$

$$= \frac{L(v_{in} I_{C, peak}^{2} - v_{o} i_{C, n}^{2})}{2Cv_{o}(v_{in} - v_{o})} + \frac{L(v_{in} I_{C, peak} - v_{o} i_{C, n})}{RC(v_{in} - v_{o})} + \frac{v_{o}(L - 2RT)}{2R^{2}C}$$

where  $\Delta v_o = \Delta v_o^H$  for  $P_H$  and  $\Delta v_o = \Delta v_o^L$  for  $P_L$ .

With the same circuit parameters as given in section II, Fig.4(a) shows output voltage variations  $\Delta v_o^H$  and  $\Delta v_o^L$  of the PCC-PT controlled DCM buck converter, where solid lines show  $\Delta v_o^H$  and  $\Delta v_o^L$  for Case 1 when the converter operates in DCM, that is,  $i_{C, n} = -v_o/R$ , and dotted lines show  $\Delta v_o^H$  and  $\Delta v_o^L$  for Case 2 when the converter operates in mixed DCM-CCM, that is,  $i_{C, n} \neq -v_o/R$ .

For 2.45  $\Omega$ <R<5.92  $\Omega$ , the converter operates in mixed DCM-CCM,  $\Delta v_o^H > 0$  and  $\Delta v_o^L < 0$  are always satisfied as shown in Fig. 4(a). For R > 5.92  $\Omega$ , the converter operates in DCM,  $\Delta v_o^H$  and  $\Delta v_o^L$  increase with increased R,  $\Delta v_o^H > 0$  and  $\Delta v_o^L < 0$  until R increases to R = 72.4  $\Omega$ . For R > 72.4  $\Omega$ ,  $\Delta v_o^L > 0$ , that is, even if P<sub>L</sub> is selected as the active control pulse, the output voltage cannot decrease, and the PCC-PT controller cannot regulate the converter any more.

#### 2) Output Voltage Variation of Case 4 (Case 3)

From (4) and (6), output voltage variation  $\Delta v_0$  within one switching cycle is

$$\Delta v_{o} = -\frac{Lv_{in}(I_{C, peak} - i_{C, n})^{2}}{2C(v_{in} - v_{o})^{2}} + \frac{(v_{in}I_{C, peak} - v_{o}i_{C, n})T}{C(v_{in} - v_{o})} - \frac{v_{o}T^{2}}{2LC}$$

(8)

With the same circuit parameters as given in section II,

When 2.45  $\Omega$ <R<5.92  $\Omega$ , the converter operates in mixed DCM-CCM,  $\Delta v_o^H > 0$  and  $\Delta v_o^L < 0$  are always satisfied as shown in Fig. 4(b). When R < 2.45  $\Omega$ , the converter operates in CCM, with the decrease of R,  $\Delta v_o^H$  decreases and  $\Delta v_o^L$  increases slightly. When R<0.3  $\Omega$ , both  $\Delta v_o^H$  and  $\Delta v_o^L$  decrease dramatically. When R<0.21  $\Omega$ ,  $\Delta v_o^H < 0$ , that is, even if P<sub>H</sub> is selected as the active control pulse, the output voltage cannot increase, and the PCC-PT controller cannot regulate the converter any more.

B. Circuit Parameter Design of the PCC-PT Controlled Buck Converter

From the previous discussion, for the PCC-PT controlled buck converter, when a high power control pulse  $P_H$  is applied, the output voltage variation may be lower than zero, that is,  $\Delta v_o^H > 0$  is not satisfied, and when a low power control pulse  $P_L$ is applied, the output voltage variation may be larger than zero, that is,  $\Delta v_o^L < 0$  is not satisfied. Thus,  $\Delta v_o^H > 0$  and  $\Delta v_o^L < 0$ should be considered in the parameter design. The design of control parameters follows.

For a light load condition, from (7), as  $i_{C,n} = -v_o/R$ ,  $\Delta v_o^L < 0$ and  $\Delta v_o^H > 0$ :

$$I_{C, peak}^{L} < \sqrt{\frac{2(v_{in} - v_{o})v_{o}^{2}T}{RLv_{in}}} - \frac{v_{o}}{R}$$

(9a)

$$I_{C, peak}^{H} > \sqrt{\frac{2(v_{in} - v_{o})v_{o}^{2}T}{RLv_{in}}} - \frac{v_{o}}{R}$$

(9b)

For a heavy load condition, from (8), as  $\Delta v_o^L < 0$  and  $\Delta v_o^H > 0$ :

$$I_{C, peak}^{2} - 2(i_{C, n} + \frac{(v_{in} - v_{o})T}{L})I_{C, peak} + [i_{C, n}^{2} + \frac{2v_{o}(v_{in} - v_{o})T}{Lv_{in}}i_{C, n} + \frac{v_{o}(v_{in} - v_{o})^{2}T^{2}}{L^{2}v_{in}}] < 0$$

(10a)

which can be rewritten as

$$I_{C, \text{ peak}} < i_{C, n} + \frac{(v_{in} - v_o)T}{L} \left[1 + \sqrt{1 + \frac{2Li_{C, n} - v_oT}{v_{in}T}}\right]$$

(10b)

To ensure  $\Delta v_o^H >0$ ,  $I_{C, peak}$  should be smaller than the minimum of the right part of (10b), which occurs when  $i_{C, n} = -v_o/R$

$$I_{C, peak} < -\frac{v_{o}}{R} + \frac{(v_{in} - v_{o})T}{L} [1 + \sqrt{1 - \frac{2Lv_{o} + Rv_{o}T}{Rv_{in}T}}]$$

(10c)

Thus, (9) and (10c) should be satisfied for the parameter design of the PCC-PT controlled buck converter.

#### C. Output Power Range

Base on the previous discussion, under a light load condition, the PCC-PT controlled buck converter operates in DCM. With increased load power, converter goes into mixed DCM-CCM, and then goes into CCM. Thus, the minimum and maximum load powers  $P_{min}$  and  $P_{max}$  occur in DCM and CCM, respectively.

When the converter operates in DCM, the power from the input power source is completely transferred to the load within one switching cycle. Assuming the converter is lossless, then the power delivered from input power source to the load in one switching cycle is given by [9]

$$P_{\rm DCM} = v_{\rm in} I_{\rm ave} = \frac{L v_{\rm in}}{2 (v_{\rm in} - v_{\rm o}) T} (I_{\rm C, \, peak} + \frac{v_{\rm o}}{R})^2$$

(11)

where  $I_{ave}$  is the average current flowing through S in a switching cycle. When  $P_H$  is selected,  $P_{DCM} = P_{DCM}^H$ ; and when  $P_L$  is selected,  $P_{DCM} = P_{DCM}^L$ , that is

$$P_{\text{DCM}} = \begin{cases} P_{\text{DCM}}^{\text{H}}, \mbox{ if } v_{\text{o}} \leq V_{\text{ref}} \\ P_{\text{DCM}}^{\text{L}}, \mbox{ if } v_{\text{o}} > V_{\text{ref}} \end{cases}.$$

From (11),  $P_{DCM}$  varies with the variation of load resistance R, rather than fixed as with the conventional PT controlled buck converter [9]. For the PCC-PT controlled buck converter,  $P_{DCM}^{H}$  and  $P_{DCM}^{L}$  should satisfy

$$P_{\text{DCM}}^{\text{H}} > P_{\text{o}} = \frac{V_{\text{o}}^{2}}{R},$$

$$P_{\text{DCM}}^{\text{L}} \le P_{\text{o}} = \frac{V_{\text{o}}^{2}}{R}.$$

(12)

where P<sub>o</sub> is load power.

When the converter operates in CCM, the inductor may store or release energy in one switching cycle, thus load power not only transferred from input power but also from the energy stored in the inductor. The input power P<sub>in</sub> in one switching cycle is

$$P_{in} = v_{in} I_{ave} = \frac{v_{in} t_{on}}{2T} (i_{L,n} + I_{C, peak} + \frac{v_o}{R})^2$$

(13)

From (2) and (4),  $i_{L, n+1}$  can be obtained as  $i_{L, n+1}=I_{C, peak}+v_o/R$  $-v_o(T-t_{on})/L$ . The energy variation of the inductor  $\Delta E_L$  is

$$\Delta E_{\rm L} = \frac{1}{2} L (i_{\rm L, n+1}^2 - i_{\rm L, n}^2)$$

(14)

Then the power delivered from the input power source to the load in one switching cycle is

$$P_{\rm CCM} = P_{\rm in} - \frac{\Delta E_{\rm L}}{T}$$

(15)

With the same circuit parameters as given in section II,  $P_{DCM}^{H}$ ,  $P_{DCM}^{L}$ ,  $P_{CCM}^{H}$ ,  $P_{CCM}^{L}$ ,  $P_{CCM}^{L}$ ,  $P_{CCM}^{L}$ ,  $P_{CCM}^{L}$ ,  $P_{CCM}^{L}$ ,  $P_{CCM}^{L}$ ,  $P_{OCM}^{L}$ ,  $P_{OCM}$ , and  $P_{o}$  with respect to R are shown in Fig. 5. As shown in Fig. 5(a), all decrease with increased R. For R > 5.92  $\Omega$ , the converter operates in DCM, as shown in Fig. 5(a). For R > 72.4  $\Omega$ ,  $P_{DCM}^{L}$  >  $P_{o}$ , that is, when  $P_{L}$  is selected as a control pulse, more power than load power  $P_{o}$  is delivered from input power source to the load, which increases the output

Fig. 5 The output powers of PCC-PT controlled buck converter: (a) the output power range of PCC-PT controlled buck converter and (b) zoom in view of (a).

voltage rather than decreasing it. Thus, as with conventional PT control,  $P_L$  of the PCC-PT controller determines the minimum load power  $P_{min}$ , which can be calculated from (12) as

$$P_{min} = \frac{v_{o}^{2}(v_{in} - v_{o})T}{Lv_{in}} - v_{o}I_{C, peak} + v_{o}\sqrt{\left(\frac{v_{o}^{2}(v_{in} - v_{o})T}{Lv_{in}} - 2v_{o}I_{C, peak}\right)\frac{(v_{in} - v_{o})T}{Lv_{in}}}$$

(16)

For 5.92  $\Omega$  < R < 72.4  $\Omega$ , as shown in Fig. 5(a),  $P_{\text{DCM}}^{L}$  < P<sub>o</sub> <

$P_{\text{DCM}}^{\text{H}}$ , that is, in this condition, when  $P_{\text{H}}$  is selected, more power than load power  $P_{\text{o}}$  is delivered from the input power source to the load, which makes output voltage increase; and when  $P_{\text{L}}$  is selected, less power than load power  $P_{\text{o}}$  is delivered from the input power source to the load, which decreases the output voltage. Thus, PCC-PT control can adjust the buck converter output voltage by selecting  $P_{\text{H}}$  or  $P_{\text{L}}$ .

For 2.45  $\Omega < R < 5.92 \Omega$ , the converter operates in mixed DCM-CCM, as shown in Fig. 5(a), both  $P_{DCM}^{L} < P_{o} < P_{DCM}^{H}$  and  $P_{CCM}^{L} < P_{o} < P_{CCM}^{H}$  are satisfied, that is, the PCC-PT controller can control the buck converter.

For  $R < 2.45 \Omega$ , the converter operates in CCM, as shown in Fig. 5(b), it always has  $P_{CCM}^{L} < P_o < P_{CCM}^{H}$ , thus, the converter can be controlled at heavy load conditions. Different from conventional PT control, the maximum load power of the PCC-PT controlled buck converter does not only depend on  $P_{H}$ , the output power can be high if the input power source can provide sufficient power.

From this analysis, as power delivered from the input power source to the load in one switching cycle increases (decreases) with the increase (decrease) of load power, the PCC-PT controlled buck converter can operate under a wide load power range.

Fig. 6. Circuit performances: (a) line regulations of PCC-PT and PIC-PT controlled buck converters, and (b) load regulations of PCC-PT and PIC-PT controlled buck converters.

#### D. Line and Load Regulation

With the same circuit parameters as given in section II, line regulations of PCC-PT controlled buck converter and peak inductor current PT (PIC-PT) controlled buck converter are shown in Fig. 6 (a). The line regulations of PCC-PT and PIC-PT controlled buck converters for input voltage varying from 20 V to 300 V are 0.103% and 0.112%, respectively. PCC-PT and PIC-PT controlled buck converters have the similar line regulations.

Load regulations of PCC-PT and PIC-PT controlled buck converters with  $v_{in}$ =20 V are shown in Fig. 6 (b), note that the x-axis in zoom-in window is at uneven increments. The load regulation of PCC-PT controlled buck converter from a minimum output current (0.1 A) to 6 A is 0.437%. The load regulation of PIC-PT controlled buck converter from a minimum output current (0.5 A) to a maximum output voltage current (1.25 A) is 1.305%. From Fig. 6 (b), PCC-PT controlled buck converter has wider load range and better load regulation than that of PIC-PT controlled buck converter.

#### IV. DISCRETE ITERATION MODEL

To verify the analysis in Section III, a discrete iteration model of the PCC-PT controlled buck converter, with output capacitor ESR considered, is established in this section.

#### A. Operation States

For the PCC-PT controlled buck converter, when switch S is turned on and diode D is turned off, the converter operates in switch state 1. During this switch state, the inductor current  $i_L$ and capacitor voltage  $v_C$  are

$$\begin{bmatrix}

L \frac{di_{L}(t)}{dt} = v_{in} - \frac{RR_{ESR}}{R + R_{ESR}} i_{L}(t) - \frac{R}{R + R_{ESR}} v_{C}(t), \\

C \frac{dv_{C}(t)}{dt} = \frac{R}{R + R_{ESR}} i_{L}(t) - \frac{1}{R + R_{ESR}} v_{C}(t).

\end{cases}$$

(17)

which can be solved as

$$\begin{cases} v_{\rm C}(t) = e^{-\alpha t} [(v_{\rm C, n} - v_{\rm in})\cos(\omega t) + k_{\rm l}\sin(\omega t)] + v_{\rm in}, \\ i_{\rm L}(t) = e^{-\alpha t} [(i_{\rm L, n} - \frac{V_{\rm in}}{R})\cos(\omega t) + k_{\rm 2}\sin(\omega t)] + \frac{v_{\rm in}}{R}. \end{cases}$$

(18)

where  $\alpha$ , k<sub>1</sub> and k<sub>2</sub> are

$$\alpha = \frac{RR_{ESR}C + L}{2(R + R_{ESR})LC}, \quad \omega = \sqrt{\frac{R}{(R + R_{ESR})LC} - \alpha^2},$$

$$k_1 = \frac{R}{(R + R_{ESR})C\omega}i_{L,n} + \frac{RR_{ESR}C - L}{2(R + R_{ESR})LC\omega}v_{C,n} - \frac{\alpha}{\omega}v_{in},$$

$$k_2 = \frac{(L - RR_{ESR}C)}{2(R + R_{ESR})LC\omega}i_{L,n} - \frac{R}{(R + R_{ESR})L\omega}v_{C,n} + \frac{R - \alpha L}{RL\omega}v_{in}.$$

As  $i_C(t_{on}) = I_{C, peak}$ , from (18), the time duration  $t_{on}$  of switch state 1 is

$$t_{on} = \frac{-\beta_2 + \sqrt{\beta_2^2 - 2\beta_1\beta_3}}{\beta_1}$$

(19)

where

$$\beta_{1} = 2(\alpha^{2} - \frac{R}{(R + R_{ESR})LC})(Ri_{L,n} - v_{C,n}) - \alpha(Rk_{2} - k_{1})\omega,$$

$$\beta_{2} = (Rk_{2} - k_{1})\omega - \alpha(Ri_{L,n} - v_{C,n}), \text{ and}$$

$$\beta_{3} = (Ri_{L,n} - v_{C,n}) - (R + R_{ESR})I_{C, \text{ peak}}.$$

After time duration  $t_{on}$ , switch S is turned off and diode D is turned on, the converter operates in switch state 2. During this switch state, the inductor current  $i_L$  and capacitor voltage  $v_C$  are

$$\begin{cases} L\frac{di_{L}(t)}{dt} = -\frac{R}{R+R_{ESR}}v_{C}(t) - \frac{RR_{ESR}}{R+R_{ESR}}i_{L}(t), \\ C\frac{dv_{C}(t)}{dt} = \frac{R}{R+R_{ESR}}i_{L}(t) - \frac{1}{R+R_{ESR}}v_{C}(t). \end{cases}$$

(20)

which can be solved as

$$\begin{cases} v_{\rm C}(t) = e^{-\alpha t} [v_{\rm C}(t_{\rm on}) \cos(\omega t) + k_3 \sin(\omega t)], \\ i_{\rm L}(t) = e^{-\alpha t} [i_{\rm L}(t_{\rm on}) \cos(\omega t) + k_4 \sin(\omega t)]. \end{cases}$$

(21)

where  $i_L(t_{on}) = I_{L, peak}$  and  $v_C(t_{on})$  are the initial conditions of switch state 2,  $v_C(t_{on})$  can be obtained from (18), and  $k_3$  and  $k_4$  in (21) are

$$k_{3} = \frac{R}{(R + R_{ESR})C\omega}i_{L}(t_{on}) + \frac{RR_{ESR}C - L}{2(R + R_{ESR})LC\omega}v_{C}(t_{on}),$$

$$k_{4} = -\frac{RR_{ESR}C - L}{2(R + R_{ESR})LC\omega}i_{L}(t_{on}) - \frac{R}{(R + R_{ESR})L\omega}v_{C}(t_{on}).$$

In switch state 2,  $i_L$  decreases. When  $i_L$  decreases to zero before the end of the switching cycle, the converter operates in DCM, otherwise, it operates in CCM.

When the PCC-PT controlled buck converter operates in CCM, time duration  $t_{\rm off}$  in this switch state is

$$t_{off} = T - t_{on} \tag{22}$$

When converter operates in DCM, as  $i_L(t_2) = 0$ , where  $t_2 = t_{on}+t_{off}$  from (21), the time duration  $t_{off}$  in this switch state is

$$t_{off} = \frac{1}{\omega} \arctan \frac{RI_{C, peak} - v_{C}(t_{on})}{k_{3} - Rk_{4}}$$

(23)

After  $i_L$  decreases to zero, it remains at zero, and both switch S and diode D are turned off. The converter operates in switch state 3. During this switch state, the inductor current  $i_L$  and

capacitor voltage  $v_C$  are

$$\begin{bmatrix} L \frac{di_{L}(t)}{dt} = 0, \\ C \frac{dv_{C}(t)}{dt} = -\frac{1}{R + R_{ESR}} v_{C}(t). \end{bmatrix}$$

(24)

which can be solved as

$$v_{c}(t) = e^{-\frac{t}{(R+R_{ESR})C}} v_{c}(t_{2}),$$

(25)

$i_{L}(t) = 0.$

where  $v_C(t_2)$  is the initial condition of switch state 3, which can be obtained from (21). The time duration of switch state 3 is  $t_{off2} = T-t_{on}-t_{off}$ .

#### B. Discrete Iteration Model

- aTr

٢

From (18), (19), (21) and (22), the discrete iteration model of the PCC-PT controlled CCM buck converter can be derived as

$$\begin{cases} v_{C, n+1} = e^{-\alpha T} \left[ (v_{C, n} - v_{in}) \cos \omega T + k_1 \sin \omega T \right] \\ + v_{in} \left[ \cos(\omega t_{off}) + \frac{\alpha}{\omega} \sin(\omega t_{off}) \right] e^{-\alpha t_{off}}, \\ i_{L, n+1} = e^{-\alpha T} \left[ (i_{L, n} - \frac{v_{in}}{R}) \cos \omega T + k_2 \sin \omega T \right] \\ + \frac{v_{in}}{R} \left[ \cos(\omega t_{off}) + \frac{\alpha L - R}{\omega L} \sin(\omega t_{off}) \right] e^{-\alpha t_{off}}. \end{cases}$$

(26)

From (18), (19), (21), (23) and (25), the discrete iteration model of the PCC-PT controlled DCM buck converter is

$$\begin{cases} v_{C, n+1} = e^{-\alpha(t_{on} + t_{off} + \frac{\omega_{off}}{(R+R_{ESR})C})} [(v_{C, n} - v_{in}) \cos \omega(t_{on} + t_{off}) \\ + k_{i} \sin \omega(t_{on} + t_{off})] \\ + v_{in} [\cos(\omega t_{off}) + \frac{\alpha}{\omega} \sin(\omega t_{off})] e^{-\frac{t_{off}}{(R+R_{ESR})C} - \alpha t_{off}}, \\ i_{L, n+1} = 0. \end{cases}$$

(27)

C. Effects of Circuit Parameters on the Stability of the PCC-PT Controlled Buck Converter

Based on discrete iteration models (26) and (27), the effect of load resistance on the steady-state performance of the PCC-PT controlled buck converter is studied in this section.

Fig. 7(a) shows the bifurcation diagrams of the output voltage  $v_o$  with load resistance R as the bifurcation parameter. As shown in Fig. 7(a), with increased R, the converter goes from multi-periodicities to period-1 at R =72.4  $\Omega$ , which is consistent with the analysis in Section III.

Fig. 7(b) shows the bifurcation diagrams of inductor current  $i_L$  with load resistance R as the bifurcation parameter. Fig. 7(b) shows the operating modes of the PCC-PT controlled buck converter: for R < 2.36  $\Omega$ , inductor current orbits are always higher than zero, that is, the converter operates in CCM; for 2.36  $\Omega$  < R < 5.69  $\Omega$ , there exists  $i_L$  =0, that is, the converter operates in mixed DCM-CCM; and for R > 5.69  $\Omega$ , all inductor current orbits decrease to zero and remain at zero, that is, the converter operates in DCM. The small difference between the ranges of these three operating modes and the ranges calculated in Section III is caused by the ESR and the accuracy of model.

Fig. 7(c) shows that for all R, the maximal Lyapunov exponent is less than zero, which illustrates that the converter is stable.

Fig. 7(d)-(g) are the zoom-in views of Fig. 7 (a), where some

Fig. 7. Effects of circuit parameters on the steady-state performance of PCC-PT controlled buck converter: (a) bifurcation diagram of  $v_0$  with the increase of R, (b) bifurcation diagram of  $i_L$  with the increase of R, (c) maximal Lyapunov exponent with the increase of R, (d) zoom in view of (a), (e) zoom in view of (a), (f) zoom in view of (a), and (g) zoom in view of (a).

special periodicities are presented. Fig. 7 (d) and (e) show bifurcation diagrams when the converter operates in DCM. The converter operates in period-3 with control pulse combination  $1P_{H}-2P_{L}$  for 14.93  $\Omega < R < 15.08 \Omega$ , and operates in period-2 with control pulse combination  $1P_{H}-1P_{L}$  for 8.62  $\Omega < R < 8.81$  $\Omega$ . Fig. 7 (f) shows bifurcation diagrams when the converter operates in mixed DCM-CCM. Wth the decrease of R, the converter operates in period-8 with control pulse combination  $5P_{H}$ - $3P_{L}$ , period-3 with control pulse combination  $2P_{H}$ - $1P_{L}$ , and period-7 with control pulse combination 5P<sub>H</sub>-2P<sub>L</sub>. The same control pulse combination, such as period-3 with control pulse combination 2P<sub>H</sub>-1P<sub>L</sub>, can exist in different operating modes of the PCC-PT controlled buck converter. Fig. 7 (g) shows bifurcation diagrams when the converter operates in CCM. The converter operates in period-4 with control pulse combination  $3P_{H}$ - $1P_{L}$  for 1.12  $\Omega$ <R<1.61  $\Omega$ . From Fig. 7(d)-(g). with increased R, the ratio between the number of high power control pulse  $\mu_{\rm H}$  and low power control pulse  $\mu_{\rm L}$  increases.

#### V. SIMULATION AND EXPERIMENTAL RESULTS

Fig. 8 shows simulation results of the PCC-PT controlled buck converter with the same circuit parameters as given in section II for different load resistances. Fig. 8(a) shows waveforms of output voltage  $v_o$ , capacitor current  $i_c$ , inductor current i<sub>L</sub> and switch driving voltage  $v_p$  for R = 75  $\Omega$ . The load is too light to be controlled by the PCC-PT controller,  $v_o$  is always higher than reference voltage V<sub>ref</sub>, low power control pulse P<sub>L</sub> is thus continuously applied as the control pulse, and the converter operates in period-1 with the control pulse repetition cycle consisting of only P<sub>L</sub>.

Fig. 8(b) and (c) show the waveforms for  $R = 15 \Omega$  and  $R = 8.7 \Omega$ . The converter operates in DCM. For  $R = 15 \Omega$ , the converter operates in period-3 with control pulse combination  $1P_{H}-2P_{L}$ . For  $R = 8.7 \Omega$ , converter operates in period-2 with control pulse combination  $1P_{H}-1P_{L}$ .

Fig. 8(d)-(f) show the waveforms for R = 5.1  $\Omega$ , R = 4  $\Omega$  and R=2.9  $\Omega$ . The converter operates in mixed DCM-CCM. For R=5.1  $\Omega$ , the converter operates in period-8 consisting of 5P<sub>H</sub> and 3P<sub>L</sub>, and the control pulse combination is 2(2P<sub>H</sub>-1P<sub>L</sub>) -1(1P<sub>H</sub>-1P<sub>L</sub>). For R=4  $\Omega$ , the converter operates in period-3 with control pulse combination 2P<sub>H</sub>-1P<sub>L</sub>. For R=2.9  $\Omega$ , the converter operates in period-7 which consists of 5<sub>H</sub> and 2P<sub>L</sub>, and the control pulse combination is 1(3P<sub>H</sub>-1P<sub>L</sub>)-1(2P<sub>H</sub>-1P<sub>L</sub>).

Fig. 8(g)-(h) show the waveforms for R = 1.5  $\Omega$  and R = 0.3  $\Omega$ . The converter operates in CCM. For R = 1.5  $\Omega$ , the converter operates in period-4 with control pulse combination  $3P_{H}$ - $1P_{L}$ . For R = 0.3  $\Omega$ , the converter operates in period-3 with control pulse combination  $2P_{H}$ - $1P_{L}$ . Simulation results of Fig. 8 are consistent with the theoretical analysis results.

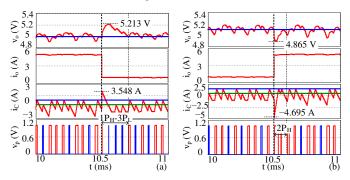

Fig. 9 shows transient response of PCC-PT controlled buck converter under step load current variation from 5 A to 1 A and from 1 A to 5 A, respectively. As shown in Fig. 9(a), when load current i<sub>o</sub> step decreases at time t=10.5 ms, as inductor current i<sub>L</sub> can not change immediately, and because of  $i_C=i_L-i_o$ , output capacitor current i<sub>c</sub> abruptly jumps to 3.548 A which is larger than  $I_{C, peak}^{H}$ , the switch S is then turned off immediately. Three low power control pulses are selected as active control pulses to decrease the output voltage. After four switching cycles, the converter goes into a steady-state. The transient time is 4 switching cycles (200 µs) and the output voltage overshoot is 0.213 V (4.26%).

When load current  $i_o$  step increases at time t=10.5 ms as shown in Fig. 9(b),  $i_C$  decreases to -4.695A. Two high power control pulses are selected as active control pulses to increase the output voltage. After 2 switching cycles, the converter goes into a steady-state. The transient time is 2 switching cycles (100 µs) and the output voltage sag is 0.135 V (2.7%).

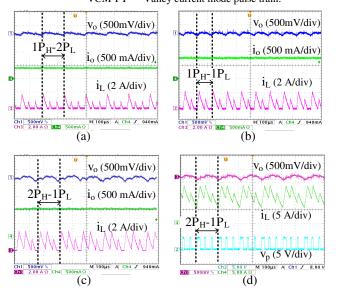

By using the same circuit parameters, experimental results of the PCC-PT controlled buck converters are shown in Fig. 10. For R = 15  $\Omega$ , the converter operates in period-3 with control pulse combination 1P<sub>H</sub>-2P<sub>L</sub>, as shown in Fig. 10(a). For R = 8.7  $\Omega$ , the converter operates in period-2 with control pulse combination 1P<sub>H</sub>-1P<sub>L</sub>, as shown in Fig. 10(b). As shown in Figs. 10(a) and (b), the converter operates in DCM.

Fig.10(c) shows that for  $R = 4 \Omega$ , the converter operates in mixed DCM-CCM and in period-3 with control pulse combination  $2P_{H}$ - $1P_{L}$ . Fig.10(d) shows that for  $R = 0.3 \Omega$ , the converter operates in CCM and in period-3 with control pulse combination  $2P_{H}$ - $1P_{L}$ . These experimental results verify the theoretical analysis and simulation results.

€ 5 °4.9 2 ં જેવ 5 -1P<sub>1</sub> . 96 2  $i_{C}(A)$ ic (A)  $\overline{\begin{smallmatrix} 1\\ 0 \end{smallmatrix}}$ õ €<sub>0.5</sub> i<sub>L</sub> (A) 1 .= 0 0 1.2  $v_{p}(v)$ v<sub>p</sub> (V) 0.6 0 10.2 (a) 10.1 t (ms V<sub>0</sub>(V) 5 1P<sub>H</sub>-1P  $i_{\rm C}(A)$ i<sub>c</sub> (A) 0 -1 4 i<sub>L</sub> (A) i<sub>L</sub> (A) 2 0 1.2  $v_{p}(V)$ 5 0.6 10.4 (c) 10.2 t (ms) t (ms)  $(d)^{12}$ 5.1 5 5.  $v_{o}\left(V\right)$ v<sub>o</sub> (V) 5 4.9 4.9 3 1P<sub>1</sub>)-1(2P<sub>H</sub>-1P<sub>1</sub> 1(3P 2 1 0 i<sub>c</sub> (A) i<sub>C</sub>(A) 0 -1 4 -3 4 i<sub>L</sub> (A) i<sub>L</sub> (A) 2 2 0 0 1.2  $v_{\rm b}$  (V) v<sub>p</sub> (V) 0.6 0.6 0 0 10.610.4 t (ms) §<sup>5.2</sup> 5.1 v<sub>o</sub>(V) 5 ° 4.8 4.9 3P<sub>H</sub>-1P<sub>I</sub> Pu-1F ic (A)  $i_{C}(A)$ 0 0 -3 6 -3 20 i<sub>L</sub> (A) i<sub>L</sub> (A) 18 3 16 0 1.2 1.2 S  $\sqrt{v_{\rm o}}$ 0.6 0.6 0 0 10.2 t (ms) t (ms)

Fig. 8. Simulation result: (a) DCM, R = 75  $\Omega$ , (b) DCM, R = 15  $\Omega$ , (c) DCM, R = 8.7  $\Omega$ , (d) mixed DCM-CCM, R = 5.1  $\Omega$ , (e) mixed DCM-CCM, R = 4  $\Omega$ , (f) mixed DCM-CCM, R = 2.9  $\Omega$ , (g) CCM, R = 1.5  $\Omega$ , and (h) CCM, R = 0.3  $\Omega$ .

Fig. 9. Transient response simulation results: (a) load current step decreases from 5A to 1 A, and (b) load current step increases from 1 A to 5 A.

|                                        | Proposed in this paper     | Ref.[4]                                      | Ref. [14,15]              | Ref. [16]               | Ref. [17]              | Ref. [18]  |

|----------------------------------------|----------------------------|----------------------------------------------|---------------------------|-------------------------|------------------------|------------|

| Control technique                      | PCC-PT                     | Digital enhanced V <sup>2</sup> -type<br>COT | PIC-PT                    | PCM-BF                  | IPR                    | VCM-PT     |

| Input voltage (v <sub>in</sub> )       | 20 V                       | 12 V                                         | 20 V                      | 20 V                    | 15 V                   | 12 V       |

| Output voltage (v <sub>o</sub> )       | 5 V                        | 1.2 V                                        | 5 V                       | 6 V                     | 5 V                    | 5 V        |

| Output capacitor (C)                   | 440 µF                     | 1600 μF                                      | 440 µF                    | 1880 µF                 | 800 µF                 | 470 μF     |

| Switching frequency (f)                | 20 kHz                     | 15 MHz (Maximum frequency)                   | 20 kHz                    | 16.7-66.7 kHz           | 20 kHz                 | 40-125 kHz |

| Load range (P <sub>o</sub> )           | 0.35-119.05 W              |                                              | 2.5-6.25 W                | 6-12 W                  | 0.5-4.9 W              | 6-13 W     |

| Operating modes                        | DCM, Mixed<br>DCM-CCM, CCM | ССМ                                          | DCM                       | DCM                     | DCM                    | ССМ        |

| Line regulation                        | 0.103 % (20 V-300<br>V)    |                                              | 0.112 %<br>(20 V-300 V)   |                         |                        |            |

| Load regulation                        | 0.437 % (0.1 A-6 A)        |                                              | 1.305 %<br>(0.5 A-1.25 A) |                         | 1.386% (0.08-0.8<br>A) |            |

| Load transient                         | 1 -5 A                     | 6 -18 A                                      | 1 -2 A                    | 1-2 A                   | 0.08-0.8 A             |            |

| Recovery time (T <sub>R</sub> )        | 50-250 μs                  | 38 µs                                        | 1.8 ms                    | 125 µs                  | 50 µs                  |            |

| Switching cycle number<br>for recovery | 2-5 Switching cycles       | About 50 Switching cycles                    | 9 Switching<br>cycles     | 2-8 Switching<br>cycles | 1 Switching<br>cycles  |            |

TABLE I. COMPARISON TABLE WITH THE PREVIOUS WORKS

Abbreviations: PCM-BF — Peak current mode bifrequency control;

ICRIF — Inductor current ripple injection feedback circuit; IPR — Improved pulse regulation;

VCM-PT — Valley current mode pulse train.

Fig. 10. Experimental results: (a) DCM,  $R = 15 \Omega$ , (b) DCM,  $R = 8.7 \Omega$ , (c) mixed DCM-CCM,  $R = 4 \Omega$ , and (d) CCM,  $R = 0.3 \Omega$ .

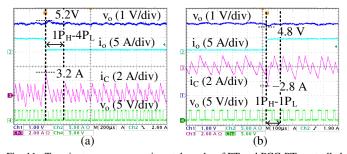

Fig. 11. Transient response experimental results of PT and PCC-PT controlled buck converter: (a) load current step decreases from 5A to 1 A, and (b) load current step increases from 1 A to 5 A.

Fig. 11 shows the transient response experimental results of conventional PT and PCC-PT controlled buck converter under step load variation from 5 A to 1 A and from 1 A to 5 A, respectively. As shown in Fig. 11(a), when load current  $i_0$  step

decreases from 5 A to 1 A, output capacitor current  $i_C$  increases to 3.2 A, which is larger than  $I_{C, peak}^H$ , the switch S is then turned off immediately. Four low power control pulses are selected as active control pulses to decrease the output voltage. After five switching cycles, the converter goes into a steady-state. The transient response time is 5 switching cycles and the output voltage overshoot is about 0.2 V (4%). As shown in Fig. 11(b), when load current  $i_o$  step increases from 1 A to 5 A,  $i_C$  decreases to -2.8 A. One low power control pulse and one high power control pulse are selected as active control pulses to increase the output voltage. After 2 switching cycles, the converter goes into a steady-state. The transient response time is 2 switching cycles and the output voltage sag is 0.2 V (4%), approximately.

Moreover, the comparisons with the previous ripple-based control techniques are shown in Table I. From Table I, because of different switching frequences f, the comparative study of transient responses of different control techniques is not obvious by comparing recovery times  $T_R$ . Thus, the switching cycle numbers of transient process, which reduces the effect of switching frequence, are considered to evaluate the transient performance. For PCC-PT controlled buck converter, only 2-5 switching cycles are required to get into steady state, which is less than the other control techniques. Moreover, the transient response of PCC-PT controlled converters can be improved by increasing switching frequency.

#### VI. CONCLUSION

In this paper, based on a discrete control technique, conventional PT control, for switching dc-dc converters, a PCC-PT control technique for the buck converter is proposed and analysed. Different from PT control, PCC-PT control uses peak capacitor current as a feedback control variable to generate high power control pulse  $P_H$  and low power control pulse  $P_L$ . The output voltage variations,  $\Delta v_o^H$  and  $\Delta v_o^L$ , of the

PCC-PT controlled buck converter with output load variation are studied; from which, control parameter design is presented. From theory and simulation analysis, within a wide load range,  $\Delta v_o^{\rm H} > 0$  and  $\Delta v_o^{\rm L} < 0$  can always be satisfied, that is, the fast-scale oscillation in a conventional PT controlled buck converter can be eliminated. In order to better understand the characteristics of the PCC-PT control buck converter, an accurate discrete iteration model of the PCC-PT controlled buck converter was established. From this model, the effects of circuit parameters on stability performance of the PCC-PT controlled buck converter operating in DCM, mixed DCM-CCM, and CCM are studied. The presented simulation and experimental results verify the analysis.

#### REFERENCES

- C. Ji-Soo, O. Hyoung-Seok, J. Young-Hyun, and K. Bai-Sun, "Fast Output Voltage-Regulated PWM Buck Converter With an Adaptive Ramp Amplitude Control," IEEE Trans. Circuits Syst. II: Express Briefs, vol. 60, pp. 712-716, Oct. 2013.

- [2] Y. Bing, L. Xin-Quan, W. Hong-Yi, and S. Ling-Feng, "High-Efficient Hybrid Buck Converter With Switch-on-Demand Modulation and Switch Size Control for Wide-Load Low-Ripple Applications," IEEE Trans. Microw. Theory Tech., vol. 61, pp. 3329-3338, Sep. 2013.

- [3] S. Maity and Y. Suraj, "A fixed frequency dual-mode DC-DC buck converter with fast-transient response and high efficiency over a wide load range," in 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2013, pp. 415-420.

- [4] K. Cheng, F. Yu, F. C. Lee, and P. Mattavelli, "Digital Enhanced V2-Type Constant On-Time Control Using Inductor Current Ramp Estimation for a Buck Converter With Low-ESR Capacitors," IEEE Trans. Power Electron., vol. 28, pp. 1241-1252, March 2013.

- [5] G. Zhou, J. Xu, and J. Wang, "Constant-Frequency Peak-Ripple-Based Control of Buck Converter in CCM: Review, Unification, and Duality," IEEE Trans. Ind. Electron., vol. 61, pp. 1280-1291, March 2014.

- [6] T. Qian, W. Wu, and W. Zhu, "Effect of Combined Output Capacitors for Stability of Buck Converters With Constant On-Time Control," IEEE Trans. Ind. Electron., vol. 60, pp. 5585-5592, Dec. 2013.

- [7] T. Qian, "Study of Subharmonic Oscillation Mechanism and Effect of Circuit Propagation Delay for Buck Converters With Constant On-Time Control," IEEE Trans. Circuits Syst. I: Regular Papers, vol. 60, pp. 788-795, March 2013.

- [8] M. Ferdowsi, A. Emadi, M. Telefus, and C. Davis, "Pulse regulation control technique for flyback converter," IEEE Trans. Power Electron., vol. 20, pp. 798-805, Aug. 2005.

- [9] S. Jin, X. Jianping, B. Bocheng, and Y. Tiesheng, "Effects of Circuit Parameters on Dynamics of Current-Mode-Pulse-Train-Controlled Buck Converter," IEEE Trans. Ind. Electron., vol. 61, pp. 1562-1573, March 2014.

- [10] J. Wang, B. Bao, J. Xu, G. Zhou, and W. Hu, "Dynamical Effects of Equivalent Series Resistance of Output Capacitor in Constant On-Time Controlled Buck Converter," IEEE Trans. Ind. Electron., vol. 60, pp. 1759-1768, May 2013.

- [11]J. Sun, "Characterization and performance comparison of ripple-based control for voltage regulator modules," IEEE Trans. Power Electron., vol. 21, pp. 346-353, March 2006.

- [12]R. Redl and S. Jian, "Ripple-Based Control of Switching Regulators--An Overview," IEEE Trans. Power Electron., vol. 24, pp. 2669-2680, Dec. 2009.

- [13] J. Wang, J. Xu, G. Zhou, and B. Bao, "Pulse-Train-Controlled CCM Buck Converter With Small ESR Output-Capacitor," IEEE Trans. Ind. Electron., vol. 60, pp. 5875-5881, Dec. 2013.

- [14] J. Sha, J. Xu, L. Xu, and S. Zhong, "Capacitor current feedback pulse train control technique for switching DC-DC converters," Electron. Lett., vol. 50, pp. 1088-1090, July 2014.

- [15]J. Sha, J. Xu, S. Zhong, S. Liu, and L. Xu, "Control Pulse Combination-Based Analysis of Pulse Train Controlled DCM Switching DC-DC Converters," IEEE Trans. Ind. Electron., vol. 62, pp. 246-255, Jan. 2015.

- [16] J. Wang, and J. Xu, "Peak Current Mode Bifrequency Control Technique for Switching DC–DC Converters in DCM With Fast Transient Response and Low EMI," IEEE Trans. Power Electron., vol. 27, pp. 1876-1884, Apr. 2012.

- [17] M. Qin, and J. Xu, "Multiduty Ratio Modulation Technique for Switching DC–DC Converters Operating in Discontinuous Conduction Mode," IEEE Trans. Ind. Electron., vol. 60, pp. 1819 - 1830, Oct. 2013.

- [18] J. Sha, J. Xu, S. Zhong, and S. Liu, "Valley current mode pulse train control technique for switching DC-DC converters," Electron. Lett., vol. 50, pp. 311 - 313, Feb. 2014.

Jin Sha was born in Shandong, China, in 1987. She received the B.S. degree in electrical engineering and automation from Southwest Jiaotong University, Chengdu, China, in 2009, where, she is currently pursuing the Ph.D. degree in the School of Electrical Engineering. During her Ph. D studies, she was a sponsored visiting researcher in the Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, UK, from Sep. 2013 to Aug. 2015.

Her research interests include control technique of switching-mode power supplies and modeling, simulation and analysis of dynamical behavior of switching dc–dc converters.

**Duo Xu** was born in Sichuan, China, in 1992. He received the B.S. degree in electronic information engineering from University of Science and Technology of China, Hefei, China, in 2014. He is currently pursuing the M.S. degree in the School of Electrical Engineering, Southwest Jiaotong University, Chengdu, China.

His research interests include control technique of switching-mode power supplies and modeling, simulation and analysis of topology of switching dc–dc converters.

His research interests include the ripple control technique of switching-mode power supply and the modeling of switching DC-DC converter.

**Jianping Xu** received the B.S. and Ph.D. degrees in electronic engineering from the University of Electronics Science and Technology of China, Chengdu, Sichuan, China, in 1984 and 1989, respectively.

Since 1989, he has been with the School of Electrical Engineering, Southwest Jiaotong University, Chengdu 610031, China, where he has been a Professor since 1995. From November 1991 to February 1993, he was with the Department of

Electrical Engineering, University of Federal Defense Munich, Germany, as a Visiting Research Fellow. From February 1993 to July 1994, he was with the Department of Electrical Engineering and Computer Science, University of Illinois at Chicago, as a Visiting Scholar. His research interests include modeling, analysis, and control of power electronic systems.

**B.W. Williams** received the M.Eng.Sc. degree from the University of Adelaide, Australia, in 1978, and the Ph.D. degree from Cambridge University, Cambridge, U.K., in 1980. After seven years as a Lecturer at Imperial College, University of London, U.K., he was appointed to a Chair of Electrical Engineering at Heriot-Watt University, Edinburgh, U.K, in 1986. He is currently a Professor at Strathclyde University, UK. His teaching covers power electronics (in which he has a free internet text) and drive systems. His

research activities include power semiconductor modelling and protection, converter topologies, soft switching techniques, and application of ASICs and microprocessors to industrial electronics.