# 360 nW Gate-Driven Ultra-Low Voltage CMOS Linear Transconductor with 1 MHz Bandwidth and Wide Input Range

Hector D. Rico-Aniles, Jaime Ramirez-Angulo, *Life Fellow, IEEE*, Antonio J. Lopez-Martin, *Senior Member, IEEE*, and Ramon G. Carvajal, *Fellow, IEEE*.

Abstract— A low voltage linear transconductor is introduced. The circuit is a pseudo differential architecture that operates with ±0.2V supplies and uses 900nA total biasing current. It employs a floating battery technique to achieve low voltage operation. The transconductor has a 1MHz bandwidth. It exhibits a SNR = 72dB, SFDR = 42dB and THD = 0.83% for a 100mVpp 10kHz sinusoidal input signal. Moreover, stability is not affected by the capacitance of the signal source. The circuit has been validated with a prototype chip fabricated in a 130nm CMOS technology.

Index Terms—Analog integrated circuits, low-power, low voltage, linear operational transconductance amplifier.

## I. INTRODUCTION

Linear voltage-to-current converters (transconductors or OTAs) and operational amplifiers (OP-AMPs) are core circuits of analog IC design. A transconductor that is linear over a wide differential input signal range  $V_d$  is a key element to implement current-mode and OTA-C systems. Some examples of the utilization of OTAs are: wide-band amplifiers, high frequency gm-C filters [1][2], multipliers [3] and precision rectifiers [4], among many others.

Transconductors are used in current mode feedforward systems with only low impedance (high frequency) and low swing nodes in the signal path. These systems mainly rely on current mirrors [5] and they can have very wide bandwidth.

Conventional transconductor and OP-AMP architectures use a differential input stage. The headroom of the differential pair  $HR_{DP}$  constrains the differential and common mode input swing to a relatively small value  $V_{ppswing} = V_{supply} - HR_{DP}$ , where  $HR_{DP} \sim V_{GS} + V_{DSsat}$ . The headroom is directly affected by  $V_{supply}$ . With the scaling down of CMOS fabrication technologies, the nominal supply voltage has continuously decreased. On the other hand, the threshold voltage of PMOS and NMOS transistors has not been reduced at the same rate. As a comparison example a 130nm CMOS process has a nominal

This work was partially supported by Grant TEC2016-80396-C2 (AEI/FEDER). H. D. Rico-Aniles acknowledges the Mexican Consejo Nacional de Ciencia y Tecnologia (CONACYT) for the support through an academic scholarship with number 408946.

H. D. Rico-Aniles and J. Ramirez-Angulo are with Klipsch School of Electrical and Computer Engineering NMSU, Las Cruces, NM, 88003 (hdrico@nmsu.edu, jairamir@nmsu.edu).

A. J. Lopez-Martin is with the Institute of Smart Cities, Public University of Navarra, Pamplona, Spain, 31006 (<a href="mailto:antonio.lopez@unavarra.es">antonio.lopez@unavarra.es</a>).

- R. G. Carvajal is with the Departamento de Ingenieria Electronica, Escuela Superior de Ingenieros Universidad de Sevilla, E-41092, Spain (carvajal@us.es).

- J. Ramirez-Angulo is also affiliated with INAOE, Puebla, Mexico. supply voltage  $V_{supply}{=}1.2\mathrm{V}$  and PMOS and NMOS threshold voltages  $V_{THN}\approx \mid V_{THP}\mid \approx 0.4\mathrm{V}$ . While for a 16nm CMOS process supply voltage has been reduced to  $V_{supply}{=}0.7\mathrm{V}$  while the threshold voltage is approximately the same  $V_{TH}{\approx}0.4\mathrm{V}$ . This limits the portability of a circuit design with scaling down of CMOS technologies.

Even in older technologies that can use higher supply voltages it is convenient to operate with very low supply voltages in order to achieve very low power dissipation which is of paramount importance in some applications such as biomedical [6][7] and wireless applications.

Subthreshold operation of MOS transistors is a natural option for low voltage systems because it allows gate-source voltages lower than  $V_{TH}$  which lessen supply requirements [8].

Another technique that allows operation of linear transconductors with very low supply voltages and with close to rail to rail differential input swing is based on floating gate transistors [9]. They use capacitive voltage dividers to reduce swing at the input terminals of the transconductor and to shift the DC common mode input voltage at the gates of the differential pair close to one of the rails in order to provide additional headroom for the input differential pair. Since they are based on charge conservation, they cannot be used in CMOS technologies with gate leakage. Quasi floating gate techniques [10][11] allow implementation of dynamic low voltage transconductors with wider differential input range. Due to their dynamic nature and the utilization of pseudo resistors implementing very large resistive elements they may have large turn on times.

Another technique that allows implementation of low voltage linear OTA's is the bulk driven (BD) technique [12]-[15]. In this technique input signals are injected at the bulk terminals rather than at the gate terminals of the MOS transistor. In order to avoid forward biasing of the bulk PN junctions at the input terminals of the MOS transistor the differential (and common mode) input swing is limited to approximately  $\pm 0.3$ V. Larger swings result in very large input currents that load the input signal source.

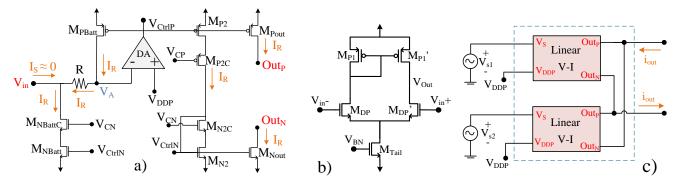

Fig. 1 a) Low voltage linear V-I conversion unit. b) Transistor level implementation of the differential amplifier (DA). c) Low voltage OTA with differential input  $V_d = V_{sI} - V_{s2}$  and complementary output currents using two linear V to I conversion units.

Both the floating gate technique and the bulk driven technique suffer from significant degradation (typically a factor 5 or higher) of input noise, input offset voltage and of the gain-bandwidth (GB) product. In floating gate circuits this is caused by the input capacitive divider, while, in bulk-driven circuits it is due to the fact that the bulk transconductance gain  $g_{mb}$  is approximately a factor 5 smaller than the main transconductance gain  $g_m$ .

A gate-driven technique to implement low voltage OTAs is based on CMOS inverters [16]. In this technique in order to keep linear transconductance both inverter transistors must be on at all times. For this reason (similar to BD circuits) the technique of [16] has very small signal swing  $V_{swingpp} = V_{supply} - V_{GS} - V_{SG}$ , with low supply voltage. Other limitations that affect this technique are that the transconductance is strongly supply and temperature dependent, it has poor CMRR and the quiescent current (static power dissipation) is also strongly dependent on the common mode input voltage.

In this paper we report and show experimental verification of a gate-driven differential linear voltage-to-current converter that operates with  $\pm 0.2 \text{V}$  supply voltages, with large differential and common mode input signal range and without the GB, offset and noise degradation associated with floating gate and bulk driven circuits. In addition, the transconductor has high input impedance and high CMRR.

This paper is organized as follows: Section II describes the proposed circuit. The AC and noise analysis are presented in Sections III and 0, respectively. In Section V the simulated and experimental results of a test chip are discussed. Conclusions are presented in Section VI.

# II. CIRCUIT DESCRIPTION

Fig. 1a shows an auxiliary circuit used to implement a wide input range low-voltage linear V to I conversion unit. The differential amplifier (DA) with NMOS input transistors used in this circuit is shown in Fig. 1b. The circuit of Fig. 1a operates as follows:

The positive input terminal of the DA is connected to a voltage  $V_{DDP}$  which is very close to  $V_{DD}$ ,  $(V_{DDP} \approx V_{DD} - 0.07V)$ . This provides a headroom for the DA with value  $HR_{DP} = V_{supply} - 0.07V$  which allows the circuit to operate with a minimum supply voltage  $V_{supplyMin} = HR_{DP} = V_{GS} + V_{DSsat}$ . A current  $I_R$  is generated by connecting the voltages  $V_{CtrlP}$  and voltage  $V_{CtrlN}$

at the gates of transistors  $M_{PBatt}$  and  $M_{NBatt}$ . They generate equal sourcing and sinking currents  $I_R$  that flow through R and have a value that satisfies the conditions of eq. (1) and (2), where  $I_Q = V_{DDP}/R$  and  $i_s = V_s/R$ . This causes the voltage  $V_A$  at the negative input terminal of the DA to have a value  $V_{DDP}$  equal to the voltage at the positive input terminal. Note that the current  $I_s$  supplied by the signal source  $V_s$  is ideally zero. This avoids loading the signal source  $V_s$  by the V to I conversion unit. Additional sinking and sourcing (eventually scaled) replicas of the current  $I_R$  can be generated using the voltages  $V_{CtrlP}$  and  $V_{CtrlN}$  to drive PMOS and NMOS transistors.

$$I_{R} = \frac{V_{DDP} - V_{s}}{R} = \frac{V_{DDP}}{R} - \frac{V_{s}}{R}$$

$$I_{R} = I_{O} - i_{s}$$

(1)

The generation of complementary output current signals  $\pm i_{out}$  free from the offset term  $I_Q$  and common mode components requires two auxiliary V-I conversion circuits with their input terminals connected to differential input signals  $V_{s1}$  and  $V_{s2}$  as shown in Fig. 1c. The two V-I converts generate sinking and sourcing currents with values  $I_{R1}=I_Q-V_{s1}/R$  and  $I_{R2}=I_Q-V_{s2}/R$  that are used to generate complementary offset free output currents  $\pm i_{out}=\pm (V_{s1}-V_{s2})/R$ . The transconductor has a transconductance gain  $g_{mOTA}=i_{out}/(V_{s1}-V_{s2})=1/R$ .

Note that  $V_{DDP}$  has a value  $V_{DDP}=V_{DD}$  - 0.07V to leave headroom for the PMOS transistor M<sub>PBatt</sub> in Fig. 1a to operate as a current source. The output voltage range is limited by the drain-source saturation voltage of transistors MPBatt, MNBattC and  $M_{NBatt}$ , to a value  $V_s = (V_{DD} - V_{SS}) - 2|V_{DSsat}| \approx 0.26 \text{V}$ . (assuming  $V_{supply}$ =0.4V and  $V_{DSsat}$ =0.07V). On the input side the range is also limited in the positive direction by the voltage  $V_{DDP}$  since the input signal cannot be higher than  $V_{DDP}$ . Although linear V to I conversion is achieved using the DA with negative feedback the bandwidth of the V-I conversion can be high since it is a local feedback loop with only parasitic capacitances at all nodes in the circuit of Fig. 1a. If necessary, a small compensation capacitance Cc can be used at node  $V_{CtrlP}$  of the DA to generate a dominant pole that achieves a phase margin greater than 60°. A detailed analysis is presented in the following section.

The proposed approach is based on two single ended circuits in parallel and can be classified as a pseudo differential scheme. In most pseudo differential systems (like an MOS differential amplifier with its sources connected to a rail)

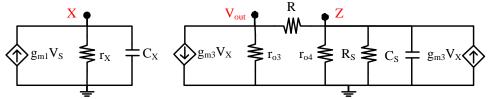

Fig. 2 Small signal representation of battery and output branch.

common mode and static current components are strongly dependent on the common mode input voltage which can lead to large and unpredictable common mode drain current values. In pseudo differential pairs drain currents have a strong nonlinear dependency on the input static and common mode voltages, on transistor parameters and on temperature. In the presence of a common mode voltage  $V_{CM}$ , the common mode current  $i_{CM}$  varies following the transistor square law in strong inversion or has an exponential dependence when the transistors operates in subthreshold. This can cause the power dissipation of a circuit with a pseudo differential MOS amplifier to increase significantly with the common mode input voltage  $V_{CM}$ . This is not the case for the scheme presented here. If  $V_{s1}$ ,  $V_{S2}$  are non-complementary voltages and have a common mode input component  $V_{CM}=(V_{s1}+V_{s2})/2$ , then  $I_{R1}$  and  $I_{R2}$  will be given by (3) and (4). Where  $V_d = V_{s1} - V_{s2}$ ,  $i_{out}=V_d/2R$  and  $I_{CM}=(V_{s1}+V_{s2})/2R$ . Although the proposed architecture can be considered as a pseudo differential scheme, it offers the advantage of having a well-defined common mode current  $I_{CM}$ . This current is linearly dependent on  $V_{CM}$  and on G=1/R. Moreover, its maximum value  $I_{CMMAX}$  is reached when  $V_{CM} = V_{SS} + V_{DSsat}$  and is less than twice the quiescent current.

The common mode current  $I_{CM}$  along with the quiescent current  $I_Q$  that appears in  $I_{RI}$  and  $I_{R2}$  are cancelled when the current  $i_{out}$  is derived.

$$I_{R1} = \frac{V_{DDP} - (V_{CM} + (V_d/2))}{R} = I_Q - I_{CM} - \frac{i_{out}}{2}$$

(3)

$$I_{R2} = \frac{V_{DDP} - (V_{CM} - (V_d / 2))}{R} = I_Q - I_{CM} + \frac{i_{out}}{2}$$

(4)

If required, the transconductance can be made tunable by:

a) replacing R by an MOS transistor in triode region such that

the resistance can be controlled by the gate voltage of the

transistor, b) utilization of gain programmable current mirrors

in the V to I conversion unit.

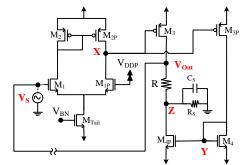

# III. AC ANALYSIS

A simplified AC equivalent circuit to derive the open loop gain of the circuit of Fig. 1a is shown in Fig. 3 whose small signal representation is shown in Fig. 2. The feedback loop is opened, and a test voltage  $V_s$  is applied at the gate of  $M_1$ . The signal source  $V_s$  applied at node Z is represented only by its internal impedance  $R_s$  in parallel with  $C_s$ . The resistance  $R_s$  is assumed to satisfy the condition  $R_s << r_o$ . The case of a high impedance signal source  $R_s \sim r_o$  (or higher) is not of interest since a high impedance source performs already as a current source and for this reason a voltage to current conversion is not required.

Fig. 3 Simplified equivalent circuit of Fig. 1a with non-ideal signal source  $V_s$ .

Fig. 4 Circuit representation for noise analysis.

Assuming  $r_o >> R$ ,  $R_s$ ,  $1/g_m$  it can be shown that the open loop gain  $A_{OL}$  is approximately given by (5), having a single pole  $\omega_{PX}$  defined by (9), where  $C_X$  and  $r_X$  are the capacitance and resistance at node X, being  $r_X = r_{ol} / |r_{o2}|$ .

The open loop DC gain ( $A_{OLDC}$ ) is expressed in (6), where  $A_I$  (7) is the gain of the first stage and  $A_{II}$  (8) is the gain of the second stage, ( $V_{out}/V_S$  corresponds to the negative of the open loop gain). For the second stage there is a pole-zero cancellation.

The gain bandwidth product (GB) of the circuit is given by (10). From this equation it can be seen that the circuit performs approximately as a one pole system with high GB. Therefore, the impact of the source capacitance on the stability of the circuit can be neglected.

$$A_{OL} = \frac{A_{OLDC}}{1 + (s/\omega_{PX})} \tag{5}$$

$$A_{OLDC} = A_I A_{II} = g_{m1} r_X \cdot g_{m3} R \tag{6}$$

$$A_I = g_{m1} r_X \tag{7}$$

$$A_{II} = -g_{m3}R \tag{8}$$

$$\omega_{PX} = \frac{1}{r_{\nu} C_{\nu}} \tag{9}$$

$$GB = A_{OLDC} \cdot \omega_{PX} = \frac{g_{m1} A_{II}}{C_{X}}$$

(10)

TABLE I PERFORMANCE AND DESIGN PARAMETERS OF LOW-VOLTAGE LINEAR TRANSCONDUCTOR

| Enterior Transconduction |       |                     |       |  |  |  |  |

|--------------------------|-------|---------------------|-------|--|--|--|--|

| Parameter                | Value | Parameter           | Value |  |  |  |  |

| $g_{mOTA}(\mu A/V)$      | 0.769 | $I_{BIAS}(\mu A)$   | 0.1   |  |  |  |  |

| $W_{PMOS}(\mu m)$        | 18    | Supply Voltage (V)  | ±0.2  |  |  |  |  |

| $W_{NMOS}(\mu m)$        | 2.88  | $A_{OL}(dB)$        | 37.4  |  |  |  |  |

| $L_{PMOS / NMOS}(nm)$    | 360   | $f_{-3dB}$ OTA(MHz) | 1.099 |  |  |  |  |

| $R(M\Omega)$             | 1.3   | GB (kHz)            | 600   |  |  |  |  |

| $R_L(M\Omega)$           | 1.3   | Phase Margin (°)    | 52    |  |  |  |  |

| $V_{DDP}(V)$             | 0.12  | Rout $(M\Omega)$    | 100   |  |  |  |  |

<sup>\*</sup> with short circuit at output

<sup>\*\*</sup> with open circuit at output

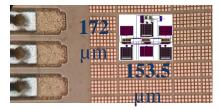

Fig. 5 Microphotograph of the fabricated chip with the layout.

Fig. 6 Testbench diagram of the low voltage OTA with external components and equipment.

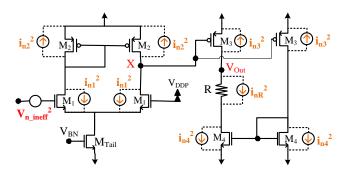

# IV. NOISE ANALYSIS

The noise representation of the circuit of Fig. 1a is shown in Fig. 4 that includes noise current sources. The noise analysis of this circuit, assuming  $A_I >> 1$ , leads to an equivalent input noise voltage approximately given by (11). This expression includes the thermal and 1/f noises. The noise bandwidth is given by (12). In the specific case of thermal noise, it is given by (13). If  $g_{ml} \approx g_{m2}$  the squared RMS noise  $V_{RMS}^2$  is given by (14).

$$V_{n\_ineff}^{2} = 2i_{n1}^{2} \left(1 + \frac{i_{n2}^{2}}{i_{n1}^{2}}\right) \frac{1}{g_{m1}^{2}}$$

(11)

$$BW_{noise} = \frac{\pi}{2}GB = \frac{g_{ml}}{4C_{v}} \tag{12}$$

$$V_{RMS}^{2} = V_{n\_ineff}^{2} \cdot BW_{noise} = \frac{2(1 + (g_{m2} / g_{m1}))kT}{3} \frac{kT}{C_{v}}$$

(13)

$$V_{RMS}^2 = \frac{4}{3} \frac{kT}{C_v} \tag{14}$$

# V. SIMULATION AND EXPERIMENTAL RESULTS

The proposed circuit of Fig. 1 with a single-ended output was fabricated in a 130nm CMOS nwell process. This technology has nominal NMOS and PMOS threshold voltages

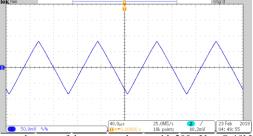

Fig. 7 Measured output of the transconductor with 200mVpp @ 10kHz single-ended triangular input.

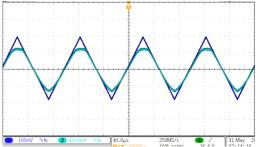

Fig. 8 Experimental output waveform of the transconductor with 400mVpp @ 10kHz triangular single-ended input signal.

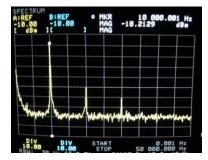

Fig. 9 Measured spectrum with a  $0.1 \mbox{Vpp}$  @ $10 \mbox{kHz}$  sinusoidal single-ended input.

$V_{THN} \approx |V_{THP}| \approx 0.4 \text{V}$  and nominal supply voltage  $V_{supplyTech} = |V_{DD} - V_{SS}| = 1.2 \text{V}$ . The circuit was designed to operate in subthreshold with a bias current  $I_{bias} = 100 \text{nA}$  with dual supply voltages  $\pm 0.2 \text{V}$  and  $V_{DSsat} = 0.07 \text{V}$ . The bias current leads to gate-source voltages of NMOS transistors with approximate values  $V_{GSNMOS} \approx 0.16 \text{V}$  and source-gate voltage of PMOS transistors with values  $V_{SGPMOS} \approx 0.14 \text{V}$ . Fig. 5 shows a micrograph of the fabricated circuit, while the test bench of the circuit is shown in Fig. 6.

Table I shows the transductor design values employed. The resistance used in the transconductor has a value  $R=1.3M\Omega$ . The associated area occupied by R was 0.00134mm<sup>2</sup>. The chip also has an integrated load resistor  $R_L=1.3M\Omega$  that is connected between the output of the transconductor and ground. This implements a feedforward amplifier with a gain  $A_V=g_{mOTA}R_L=R_L/R=1V/V$ . An on-chip buffer with input capacitance of approximately  $C_L\approx0.2$ pF was used at the output of the trasconductor. The transconductor works with dual supply voltages of  $\pm0.2$ V and it was tested with a single-ended input signal  $V_{s1}$ ,  $(V_{s2}=0)$ .

$$FOM_{LOTA} = \frac{\left(\frac{V_{inMax}}{V_{Supply}}\right)BW}{P_{Diss}} \left[\frac{MHz}{mW}\right]$$

(15)

|                                        | 2007 [17]     | 2013 [18]       | 2014 [19]           | 2019 [20]                 | This work          |

|----------------------------------------|---------------|-----------------|---------------------|---------------------------|--------------------|

| Tech. (µm)                             | 0.5           | 0.18            | 0.13                | 0.18                      | 0.13               |

| Driven by                              | Gate          | Gate            | Bulk                | Bulk                      | Gate               |

| Supply (V)                             | ±1.5          | 1.2             | 0.25                | 0.3                       | ±0.2               |

| $G_M(\mu S)$                           | 10            | 12.5            | 0.022               | 0.255                     | 0.76               |

| Input range (V)                        | 0 - 3         | 0 - 1.10        | -                   | 0-0.3                     | ±0.1               |

| OTA Bandwidth (MHz)                    | 90            | 14.1            | -                   | 0.000334                  | 1.1                |

| Noise (nV / √Hz)                       | 1780          | 258.4           | 100(μV <i>RMS</i> ) | 1330 @10Hz <sup>Sim</sup> | 988 <sup>Sim</sup> |

| THD (dB) @V <sub>PP</sub> @ Freq (MHz) | -60 @ 6 @ 0.1 | -44.2 @ 1 @ 0.1 | -45.51 @ 0.1 @      | -56.47@ 0.1 @             | -41.61@ 0.2 @ 0.01 |

| PSRR (dB)                              | 35/43         | 47.8            |                     | 39.9                      | 52 Sim             |

| CMRR(dB)                               | 62            |                 |                     | 57                        | 70 <sup>Sim</sup>  |

| Power (µW)                             | 3000          | 85              | 0.01                | 0.05                      | 0.36               |

| FoM (MHz/mW)                           | 30            | 152             |                     | 6.68                      | 1525               |

| Area (mm <sup>2</sup> )                | 0.1           | 0.0144          | 0.053(active)       | 0.035                     | 0.0264             |

TABLE II PERFORMANCE COMPARISON WITH OTHER LOW-VOLTAGE TRANSCONDUCTORS

The measured ouput voltage of the circuit operating with  $\pm 0.2$ V is depicted in Fig. 7; the input signal is a 10kHz 200mVpp triangular signal. As it can be seen it has a linear output. The ouput with a rail-rail input signal is shown in Fig. 8. This is limited by the value of voltage  $V_{DDP}$ . When  $V_S$  has a value equal to  $V_{DDP}$  the current  $I_R$  is equal to zero (1).

The measured amplitude spectrum of the output upon application of a 10kHz 100mVpp sinusoidal single-ended input signal is shown in

Fig. 9. Under this conditions the transconductor with the resistive load exhibits a SFDR= 42dB, SNR=72dB and THD = 0.83%.

The amplifier's experimental bandwidth was 500kHz. This bandwidth results from the internal pole of the transconductor (approximately 1.1MHz) and the output pole of the transconductor generated by the parallel combination of  $C_L$  and  $R_L$  (approximately 1 MHz). Table II shows a performance comparison with other published linear transconductor works. No comparison has been done to OTAs used as op-amps in close loop since they are not linear and have a very small differential input range. The FoM used for comparison was proposed by [18] and expressed in (15), where  $V_{inMax}$  is the maximum input signal (for 1% THD) and  $V_{Supply} = V_{DD} - V_{SS}$ .

PVT corners simulations have been performed to characterize the operation of the design under different environmental conditions. It was found that the design is robust to PVT variations: temperature variations 0-85 °C, on the power supply voltage variations  $V_{DD}\pm10\%$  and the process corners: tt, ss, ff, sf and fs. The design is robust to process and temperature variations since the circuit's transient and AC responses show negligible changes. Variations in the power supply result in an ouput DC offset with maximum value of 10mV.

# VI. CONCLUSION

A method to implement gate-driven ultra-low voltage linear transconductors that are capable to operate with  $\pm 0.2 \text{V}$  supply voltage and wide input linear range was introduced. The design uses 900nA total biasing current. Despite the low biasing current and supply voltages, it achieves a relatively high transconductor bandwidth of 1MHz. The scheme was experimentally validated with a test chip prototype in 130nm CMOS technology.

### REFERENCES

- [1] J. Perez-Bailon, A. Marquez, B. Calvo, N. Medrano and M. T. Sanz-Pascual, "A 1V-1.75uW Gm-C low pass filter for bio-sensing applications," in *Proc. IEEE 9<sup>th</sup> Latin American Symposium on Circuits & Systems (LASCAS)*, Puerto Vallarta, Mexico, Feb. 25-28, 2018.

- [2] K. Garradhi, N. Hassen and K. Besbes, "Low-voltage and low-power OTA using source degeneration technique and its application in Gm-C Filter," in *Proc.* 11<sup>th</sup> International Design & Test Symposium (IDT), Hamment, Tunisia, Dec. 18-20, 2016.

- [3] G. Han and E. Sanchez-Sinencio, "CMOS Transconductance multipliers: a tutorial," *IEEE Trans. Cir. Syst. II: Analog Digital Signal Proc.*, vol. 45, no. 12, pp. 1550-1563, Dec. 1998.

- [4] S. Pourashraf, J. Ramirez-Angulo, J. M. Hinojo Montero, R. G. Carvajal and A. J. Lopez-Martin, "± 0.25-V class-AB CMOS capacitance multiplier and precision rectifier," *IEEE Trans. VLSI Syst.*, vol. 27, no. 4, pp. 830-842, Apr. 2019.

- [5] J. Ramirez-Angulo, M. Robinson and E. Sanchez-Sinencio, "Current-mode continuous-time filters: two design approaches," *IEEE Trans. Cir. Syst. II: Analog Digital Signal Proc.*, vol. 39, no. 6, pp. 337-341, Jun 1992.

- [6] R. Rakhi, A. D. Taralkar, M. H. Vasantha and Y. B. Nithin, "A 0.5V low power OTA-C low pass filter for ECG detection," in *Proc. IEEE Comp Society Annual Symposium on VLSI*, Bochum, Germany, Jul. 3-5, 2017.

- [7] J. Zhang, H. Zhang, Q. Sun and R. Zhang, "A low-noise, low-power amplifier with current-reused OTA for ECG recordings," *IEEE Trans. Biomed. Cir. Syst.*, vol. 12, no. 3, pp. 700-707, Jun. 2018.

- [8] J A. E. Mourabit, Guo-Neng Lu and P. Pittet, "Wide-linear-range subthreshold OTA for low-power, low-Voltage, and low-frequency applications," *IEEE Trans. Cir. Syst. I: Reg. Papers*, vol. 52, no. 8, pp. 1481-1488, Aug. 2005.

- [9] F. Muñoz Chavero, A. Torralba, R. G. Carvajal, J. Tombs and J. Ramirez-Angulo, "Floating-gate-based tunable CMOS low-voltage linear transconductor and its application to HF GM-C filter design," *IEEE Trans. Cir. Syst. II: Analog Digital Signal Proc.*, vol. 48, no. 1, pp. 106-110, 2001.

- [10] F. Khateb, M. Kumngern, T. Kulej and V. Kledrowetz, "Low-voltage fully differential difference transconductance amplifier," *IET Circuits, Devices & Systems*, vol 12, no. 1, pp. 73-81, 2018.

- [11] J. Ramirez-Angulo, A. J. Lopez-Martin, R. G. Carvajal and F. M. Chavero, "Very low-voltage analog signal processing based on quasi-floating gate transistors," *IEEE J. Solid-State Cir.*, vol. 39, no. 3, pp. 434-442, 2004.

- [12] L. H. C. Ferreira and S. R. Sonkusale, "A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process," *IEEE Trans. Cir. Syst. I: Reg. Papers*, vol. 61, no. 6, pp. 1609-1617, Jun. 2014.

- [13] E. D. Cotrim and L. H. Ferreira, "An ultra-low-power CMOS symmetrical OTA for low-frequency G<sub>m</sub>-C applications," *Analog Integr. Circ. Sig. Proc.*, vol. 71, no.2, pp. 275-282, 2012.

- [14] F. Khateb, T. Kulej, S. Vlassis, "Extremely low-voltage bulk-driven tunable transconductor," *Circ. Syst. and Sig Process.*, vol. 36, no. 2, pp. 511-524, 2017.

- [15] O. Abdelfattah, G. W. Roberts, I. Shih and Y. Shih, "An ultra-low-voltage CMOS process-insensitive self-biased OTA with rail-to-rail input range," *IEEE Trans. Cir. Syst. I: Reg. Papers*, vol. 62, no. 10, pp. 2380-2390, Oct. 2015.

- [16] S. Vlassis, "0.5 V CMOS inverter-based tunable transconductor," *Analog Integr. Circ. Sig. Proc.*, vol. 72, pp 289–292, 2012.

- [17] A. J. Lopez-Martin, J. Ramirez-Angulo, and R. G. Carvajal, "±1.5 V 3mW CMOS V-I converter with 75 dB SFDR for 6 V<sub>PP</sub> input swings," *Electron. Lett.*, vol. 43, no. 6, pp. 31-32, Mar. 2007.

- [18] C. Azcona, B. Calvo, S. Celma, N. Medrano and P. A. Martinez, "Low-voltage low-power CMOS Rail-to-Rail Voltage-to-Current Converters," *IEEE Trans. Cir. Syst. I: Reg. Papers*, vol. 60, no. 9, Sep. 2013.

- [19] G. D. Colletta, L. H. C. Ferreira and T. C. Pimenta, "A 0.25-V 22-nS symmetrical bulk-driven OTA for low-frequency Gm–C applications in 130-nm digital CMOS process," *Analog Integr. Circ. Sig. Proc.*, vol. 1, no. 2, pp. 377-383, 2014.

- [20] F. Khateb, T. Kulej, M. Akbari, P. Steffan, "0.3-V Bulk-Driven Nanopower OTA-C Integrator in 0.18 µm CMOS", *Circ. Syst. and Sig Process.*, vol. 38, no. 3, pp. 1333–1341, 2019.