Romano, Gianpaolo and Fayyaz, Asad and Riccio, Michele and Maresca, Luca and Breglio, Giovanni and Castellazzi, Alberto and Irace, Andrea (2016) A comprehensive study of the short-circuit ruggedness of silicon carbide power MOSFETs. IEEE Journal of Emerging and Selected Topics in Power Electronics . ISSN 2168-6785 (In Press)

# Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/33509/1/A%20Comprehensive%20Study%20of%20the %20Short-Circuit%20Ruggedness%20of%20Silicon%20Carbide%20Power %20MOSFETs.pdf

# Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

## A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# A Comprehensive Study of Short-Circuit Ruggedness of Silicon Carbide Power MOSFETs

Gianpaolo Romano, Asad Fayyaz, Michele Riccio, Luca Maresca, Giovanni Breglio, Alberto Castellazzi, Member, IEEE, and Andrea Irace, Senior Member, IEEE

Abstract-The behavior of silicon carbide (SiC) power MOSFETs under stressful short-circuit (SC) conditions is inves-2 tigated in this paper. Two different SC failure phenomena for 3 SiC power MOSFETs are thoroughly reported. Experimental 4 evidence and TCAD electrothermal simulations are exploited to 5 describe and discriminate the failure sources. Physical causes are 6 finally investigated and explained by means of properly calibrated numerical investigations and are reported along with their effects 8 on devices' SC capability. 9

*Terms*—Short-circuit (SC) failure mechanism, Index 10 SC ruggedness, silicon carbide (SiC) power MOSFETs, thermal 11 runaway. 12

13

#### I. INTRODUCTION

C ILICON carbide (SiC) power MOSFETs have experienced 14 rapid technological developments, making them a com-15 mercial reality in the field of power semiconductor devices. 16 Such devices are gradually replacing silicon device counter-17 parts in different power electronic systems. Their application 18 range includes energy conversion and distribution, avionics 19 and automotive, renewable energy, and electric traction. The 20 major upsides come from several material features generally 21 considered superior to those of silicon [1], [2]. Higher critical 22 electric field, lower leakage current, and higher thermal con-23 ductivity, to name a few, reflect a lower ON resistance, a higher 24 switching frequency, and a better temperature capability for 25 SiC devices. Even though over the years there has been a fast 26 progress in device technology [3], which allowed for the 27 production of commercial devices with better performances 28 (switching frequency, power efficiency, long term reliabil-29 ity, etc.), there is still margin for quality and cost improvement. 30 The cost of single device is not yet competitive but benefits 31 can become dominant at application level where compact and 32 highly efficient systems could be realized [4], [5]. 33

Manuscript received December 18, 2015; revised February 23, 2016; accepted April 14, 2016. Recommended for publication by Associate Editor Brett Hull.

G. Romano, M. Riccio, L. Maresca, G. Breglio, and A. Irace are with the Department of Electrical Engineering and Information Technologies, University of Naples Federico II, Naples 80125, Italy (e-mail: gianpaolo.romano@unina.it; michele.riccio@unina.it; luca.maresca@unina.it; breglio@unina.it: a.irace@unina.it).

A. Fayyaz and A. Castellazzi are with the Power Electronics, Machines, and Control Group, The University of Nottingham, Nottingham NG7 2RD, U.K. (e-mail: eexaf12@nottingham.ac.uk; alberto.castellazzi@nottingham.ac.uk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JESTPE.2016.2563220

In recent years, many works [6]-[10] have carried out 34 investigation and characterization of reliability of SiC devices; 35 nevertheless, many issues still have to be fully addressed.

Through in-depth investigations it will be possible to suggest design rules and engineering improvements that will push up devices' performance boundaries.

In order to define their limit to withstand the most demanding working operations, devices are usually analyzed during highly stressful conditions, that is, most commonly during unclamped inductive switching and short circuit (SC), two routine techniques regularly used for characterizing silicon power devices (see [11], [12]).

An SC event can occur in a variety of ways in an industrial environment. This is especially true for motor driving systems, where different kinds of protection circuits were proposed to avoid catastrophic failure during overload and SC events at the inverter stage (see [13]–[16]). Therefore, in this scenario, a device should be designed to have reasonable SC withstand time prior to the intervention of the protection circuitry. Nevertheless, this could not be achieved without an understanding of the underlying physical mechanisms that bring the device to failure.

In the recent past, different papers addressed the SC robust-56 ness of SiC power MOSFETs. In [17]-[19], an experimental 57 evaluation of robustness and performances of commercially 58 available devices was given. The reported results showed 59 the weakness of the gate during SC tests and at different 60 failure modes. Experiments on SiC power MOSFET and 61 JFET were carried out in [20] under SC fault condition. 62 The device temperature was also estimated to be very high, 63 leading to melting of aluminum and finally to device failure. 64 Wide experimental data on different commercial devices and 65 numerical investigations through electrically and thermally 66 coupled models were exploited to analyze the temperature 67 dependence of SC withstanding capability in [21]. In [22], 68 electrothermal simulations are shown to analyze the SC SOA 69 using compact models. Reference [23] presents numerical 70 and experimental analyses of a failure mode during pulsed 71 overcurrent. However, these results did not examine the pos-72 sible failure mode in SC, which must be analyzed through 73 testing and modeling. In this context, the aim of this paper 74 is to present an interpretation of the inner physical dynam-75 ics limiting the SC capability of SiC MOSFETs. A broad 76 set of experimental measurements is performed to evaluate 77

2168-6777 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

1

40 AQ:1

36

37

38

39

41

42

43

44

45

46

47

48

49

50

51

52

53

54

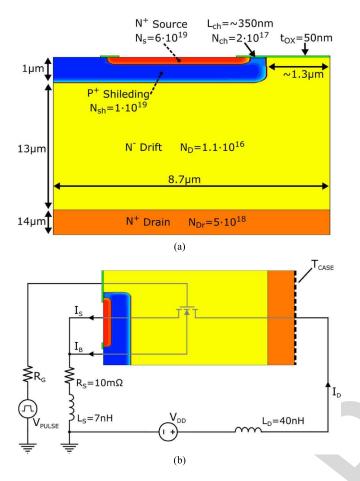

Fig. 1. (a) Simulated structure (not in scale). (b) Mixed-mode schematic.

different SC failure modes of commercially available SiC MOSFETs. 79

After an introduction, in Section II, both the experimen-80 tal and simulation methods used to carry out the analysis 81 are illustrated, giving information on the test setup and the 82 TCAD structure. Section III reports in detail the main results 83 gained, and their analysis leads to determining two separate 84 failure modes. In Section IV, the physical phenomena limiting 85 the SC reliability of devices are discussed, recognizing that 86 temperature is the main impacting factor. 87

#### **II. ANALYSIS APPROACHES**

Experimental data were collected through extensive testing 89 of commercially available devices that were characterized 90 during the failure event under different operating conditions. 91 The outcomes were subsequently investigated, and with the 92 aid of numerical electrothermal simulations, the physical 93 mechanisms involved in the failure event have been properly 94 inspected, giving an insight into different phenomena occur-95 ring inside the device. 96

#### A. Simulated Structure 97

Thanks to device symmetry, a half elementary cell of a 98 planar MOSFET [Fig. 1(a)] was reproduced for this study and 99 analyzed with the TCAD Synopsys Suite. 100

Even though the structure was calibrated to match the 101 behavior of a commercial device, it does not represent the 102

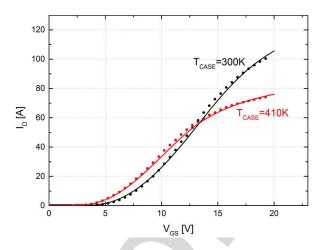

Fig. 2. Measured (symbols) and simulated (solid) isothermal  $I_D - V_{GS}$ characteristics ( $V_{\text{DS}} = 20 \text{ V}$ ).

actual device structure. Hence, it could be taken as a more 103 general case study. Theoretical assumptions and literature data 104 (see [24]) were used to define doping and dimensions [reported 105 in Fig. 1(a)]. Principal models and corresponding parameters 106 are listed in the Appendix. For simulation purpose, body and 107 source terminals were physically separated but connected at 108 the same electrical node. 109

Mixed-mode simulations were performed, in which a phys-110 ically based device was placed alongside a circuit descrip-111 tion (in a SPICE netlist format) as depicted in Fig. 1(b). 112 Additional components were included to consider the parasitic 113 elements introduced in a real circuit by wires and connections. 114 Specifically, stray inductance and parasitic resistance on 115 the source loop  $(L_S, R_S)$  affect the *di/dt* during the turn-ON 116 phase; stray inductance on the drain  $(L_D)$  is responsible for 117 voltage spikes during switching transients. Fig. 1(b) shows 118 their estimated values. 119

It is well known that temperature strongly affects the 120 behavior of power devices, and therefore self-heating effects 121 could not be neglected. Accordingly, temperature-dependent 122 parameters were included, and heat generation and transport 123 equations were solved in conjunction with semiconductor 124 equations. The thermal problem was solved applying the 125 isothermal condition on the back of the device  $(T_{CASE})$  and 126 adiabatic conditions on the remaining edges. 127

In order to reflect the operation of an actual device, 128 the structure was calibrated obtaining a suitable match with 129 isothermal  $I_D - V_{GS}$  characteristics of a 1.2-kV 36-A 80-m $\Omega$ 130 commercial device [25], selected as case study. The curves 131 were measured at  $V_{\rm DS} = 20$  V by means of a pulsed curve 132 tracer and are illustrated in Fig. 2 for backside temperatures 133 of 300 and 410 K.

134

The calibration procedure implied the choice of suitable 135 physical models (e.g., mobility doping dependence, carrier 136 recombination, etc.) and the proper tuning of their parameters. 137 Device behavior is largely dependent on the quality of the 138 oxide-semiconductor interface and could not be correctly 139 reproduced without including fixed charges and trap lev-140 els usually present therein. References [26] and [27] have 141 reported the impact of interface defects and dislocations on 142

AO:2

78

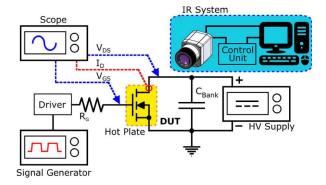

Fig. 3. Test setup diagram.

MOSFET devices. These trap levels are commonly considered to be acceptor-like above mid-gap energy  $E_i$ , i.e., negatively charged when occupied. One of the effects is a positive shift of the threshold voltage, which can then be analytically expressed as [28]

$$V_{\text{TH}} = V_{\text{FB}} + 2\phi_B$$

$$+ \frac{1}{C_{\text{OX}}} \left( \sqrt{2\varepsilon_s q N_A(2\phi_B)} + q \int_{E_i}^{E_i + q\phi_B} D_{\text{it}}(E) dE \right)$$

$$(1)$$

where  $D_{it}$  is the interface trap density, and other symbols have the common meaning. Furthermore, the filled traps give rise to Coulomb scattering that turns into a mobility decrease of channel electrons flowing close to the surface.

The number of filled traps decreases as the temperature increases since trapped electrons tend to be emitted. This leads to a lowering of the threshold voltage. In addition, both a reduction in Coulomb scattering and a higher number of free carriers improve the channel mobility. Therefore, there is a temperature range in which mobility actually increases with temperature, until all electrons are released.

#### 162 B. Experimental Setup

AQ:3

AO:4

<sup>163</sup> SC tests were performed on the aforementioned device for <sup>164</sup> different operating conditions (i.e.,  $V_{\text{DS}}$ ,  $T_{\text{CASE}}$ ,  $V_{\text{GS}}$ ,  $t_{\text{PULSE}}$ ). <sup>165</sup> In addition, in order to give a widespread validation of <sup>166</sup> the obtained results, other manufactures' devices that were <sup>167</sup> 1.2-kV 80-m $\Omega$  rated were tested [29], [30].

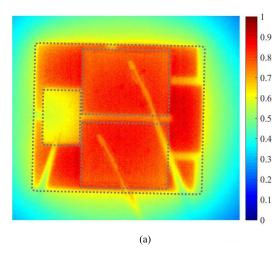

A schematic of the experimental system is shown in 168 Fig. 3. The gate driving system consists of a MCP1404 driver 169 IC manufactured by Microchip and a 5- $\Omega$  gate resistor. The 170 gate voltage goes from 0 to 20 V. Voltage is applied by 171 a HVdc power supply, and it is held during the SC pulse 172 by a 1-mF capacitor bank. The DUT is placed on a hot 173 plate through which it is possible to set the case temperature. 174 A custom advanced infrared (IR) thermography system, fully 175 described in [31], was used to acquire the surface temperature 176 of the device during the SC test. Featuring an equivalent 177 time sampling technique, it is able to acquire fast transient 178 dynamics, with 1 MHz equivalent frame rate. Thus, it is 179 possible to track the temperature evolution, and therefore the 180 current distribution, during the applied SC pulse. In addition, 181 the system allows a single-shot capture of the temperature 182 map at any desired time instant along the test. This feature 183

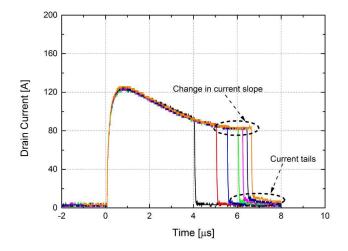

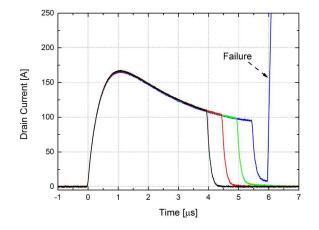

Fig. 4.  $I_D$  short-circuit waveforms ( $V_{DS} = 600$  V;  $V_{GS} = 16$  V;  $T_{CASE} = 75$  °C; CREE).

was used, as will be shown later, to catch the heat spreading 184 at its maximum, i.e., at the pulse turn-OFF edge. If the device 185 fails, this corresponds to spotting the current distribution right 186 before the failure event, which could lead to useful information 187 about the failure mechanism itself. IR camera integration time 188 was set to 1  $\mu$ s and a two-point calibration procedure was 189 performed to compensate the emissivity contrast effect [32]. 190 Furthermore, due to high temperature reached during the 191 experiment exceeding the camera calibration range, thermal 192 images were elaborated in postprocessing to represent the 193 normalized temperature increase 194

$$T_n = \frac{T - T_0}{T_{\text{max}} - T_0}$$

(2) 195

198

199

200

201

202

203

207

where  $T_0$  is the case temperature and  $T_{\text{max}}$  is the maximum temperature for each thermal map.

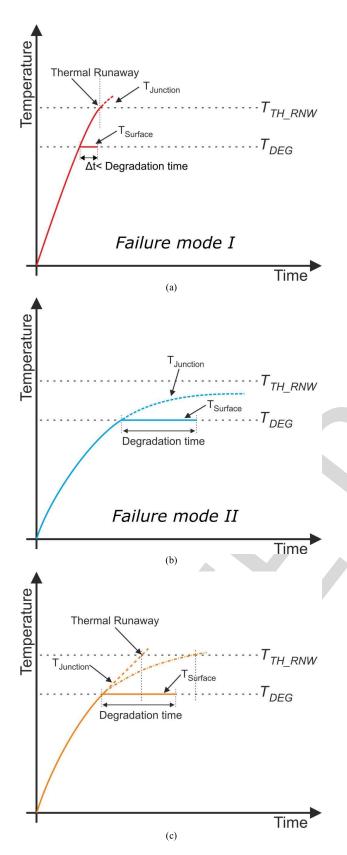

#### III. EXPERIMENTAL AND SIMULATION RESULTS

This paragraph describes the main results obtained through experiments and simulations. Tests were carried out using two distinct approaches:

1) short pulses ( $\leq 20 \ \mu$ s) at high voltage ( $\geq 400 \ V$ );

2) long pulses (100  $\mu$ s) at low voltage ( $\leq 200$  V).

Based on the results it was possible to infer two different failure mechanisms during SC, both related to temperature increase inside the structure, as will be discussed later. 206

#### A. High-Voltage Short-Pulse Tests

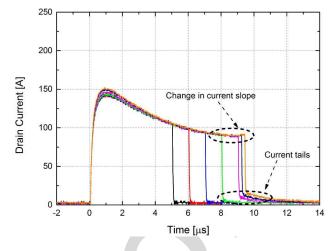

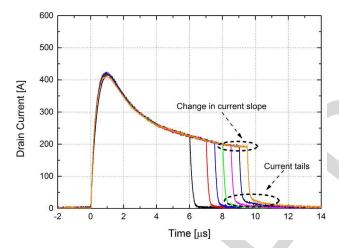

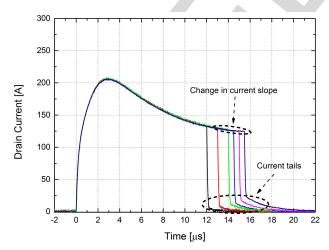

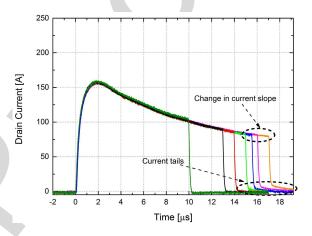

In the following, the most relevant results are summarized. From single-pulse SCt waveforms (Figs. 4 and 5), the appearance of two phenomena becomes immediately evident; specifically, the current tends to change slope at the end of the pulse and current tails, usually present in bipolar devices, which originate after the turn OFF.

These effects were already reported in [33], and they are 214 present in different devices as well, upheld by test results 215 (Figs. 6 and 7). 216

Generally, it is an uncommon behavior for a power 217 MOSFET, since as a unipolar device, it should not have any 218

Fig. 5.  $I_D$  short-circuit waveforms ( $V_{\rm DS}$  = 800 V;  $V_{\rm GS}$  = 18 V;  $T_{\rm CASE}$  = 150 °C; CREE).

Fig. 6.  $I_D$  short-circuit waveforms ( $V_{\rm DS} = 400$  V;  $V_{\rm GS} = 20$  V;  $T_{\rm CASE} = 27$  °C; ST).

Fig. 7.  $I_D$  short-circuit waveforms ( $V_{DS} = 600$  V;  $V_{GS} = 18$  V;  $T_{CASE} = 27$  °C; ROHM).

current tails, and it should have a negative current slope whenbiased above the temperature compensation point.

These two effects could be considered temperature related, since as the pulse length increases and/or applied voltage and

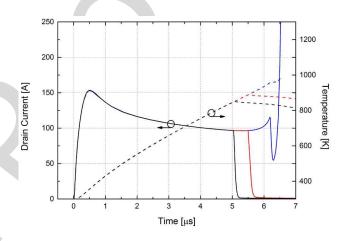

Fig. 8. Simulated drain current and surface temperature ( $V_{\text{DS}} = 400 \text{ V}$ ;  $V_{\text{GS}} = 18 \text{ V}$ ;  $T_{\text{CASE}} = 27 \text{ °C}$ ).

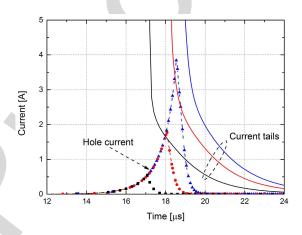

Fig. 9. Details of current tails (solid line) and hole current (dashed line) from the simulation of Fig. 8 ( $V_{DS} = 400$  V;  $V_{GS} = 18$  V;  $T_{CASE} = 27$  °C).

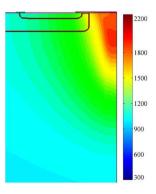

Fig. 10. Temperature distribution at  $t = 18.5 \ \mu s \ (V_{\text{DS}} = 400 \text{ V}; V_{\text{GS}} = 18 \text{ V}; T_{\text{CASE}} = 27 \text{ °C}$ , scale in K).

back temperature are higher, they become more and more relevant up to device catastrophic failure. 224

Deeper investigations were carried through physical electrothermal simulations.

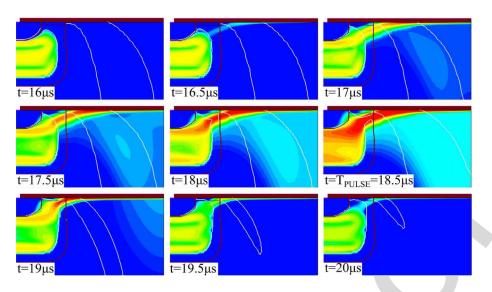

Fig. 11. Simulated hole current density ( $V_{\text{DS}} = 400$  V;  $V_{\text{GS}} = 18$  V;  $T_{\text{CASE}} = 27$  °C).

The second aspect that can be spotted is that the heat is mainly 233 generated in the JFET region and an extreme high-temperature 234 peak value is reached therein (Fig. 10). Fig. 11 depicts the 235 hole current density at different time instants along a  $18.5 - \mu s$ 236 SC pulse. In the beginning, the hole concentration has a very 237 low value, and therefore the leakage current of the body/drift 238 p-n junction is negligible. As the temperature increases, it 239 leads to an increase in the number of holes, and consequently 240 leakage current keeps increasing gradually. This phenomenon 241 gives rise to the hole current coming out the body terminal. 242 Using formulas and values reported in [24], [34], and [35], 243 it is possible to carry out an approximate estimation of the 244 leakage current as a function of temperature 245

$$j_s = q n_i^2 \left(\frac{D_p}{L_p N_D}\right) \tag{3}$$

where  $D_p$  and  $L_p$  (1–2  $\mu$ m, [24]) are the diffusivity and the diffusion length, respectively, and  $n_i$  is given by

$$n_i = 1.7 \cdot 10^{16} T^{3/2} e^{-2.08 \cdot 10^4/T} \tag{4}$$

<sup>250</sup>  $D_p$  can be calculated from mobility  $\mu_p$

249

$$\mu_p = 125 \left(\frac{T}{300}\right)^{-2.7}.$$

(5)

Combining (3)–(5) with the assumption of a device approxi-252 mately  $3 \text{ mm} \times 3 \text{ mm}$  and SiC physical parameters from [36], 253 the leakage current can roughly be estimated to be  $\sim 30$  A 254 at T = 2000 K. Far from being an accurate calculation, 255 this result indicates the temperature range in which the leak-256 age current is expected to have a value comparable to the 257 ON-state current value during SC, that is, when the device 258 is experiencing thermal runaway. On the other hand, to get 259 a current tail similar to the one experimentally observed, the 260 temperature peak value should not be much far from the one 261 obtained in simulation. Thus, holes are thermally generated 262 due to locally elevated temperature increase. The electric field 263 in the drift region drags the generated carriers toward the top 264 of the device. Hole density keeps increasing until a certain 265

Fig. 12. Simulated drain current and surface temperature ( $V_{\text{DS}} = 800 \text{ V}$ ;  $V_{\text{GS}} = 18 \text{ V}$ ;  $T_{\text{CASE}} = 27 \text{ °C}$ ).

point along the body/drift edge when the p-n junction does not266exist anymore. This is due to excessive carrier concentration267that punches through the junction.268

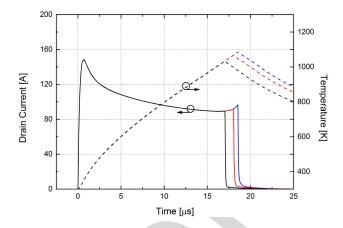

Obviously, electrons are thermally generated at the same 269 time and are free to flow from source to drain even when the 270 applied gate voltage is zero. The current tail is indeed built up 271 by the merging of the aforementioned leakage currents. The 272 tail then slowly decreases to zero within a time linked to the 273 one needed to remove all the generated carriers. Nevertheless, 274 the leakage current could reach a level at which thermal 275 runaway takes place leading to device failure. This is a positive 276 feedback phenomenon inducing an uncontrollable increase in 277 the drain current up to MOSFET destruction (Fig. 13). It is 278 furthermore inferred that these devices do not comply with the 279 usual required SC capability of silicon power devices, which 280 is at the minimum withstanding a SC pulse of 10  $\mu$ s with 281 two-third rated voltage applied. 282

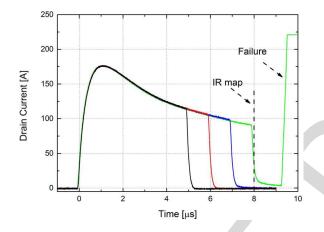

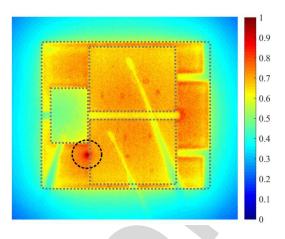

To better comprehend the inner device dynamics preceding the failure event (i.e., during the current tail), temperature distribution was acquired at the turn OFF of a  $8-\mu s$  SC pulse. To easily accomplish this task, the temperature evolution was

5

AQ:6

AO:5

Fig. 13.  $I_D$  short-circuit waveforms ( $V_{DS} = 800$  V;  $V_{GS} = 18$  V;  $T_{CASE} = 27$  °C; CREE).

Fig. 14.  $I_D$  short-circuit waveforms ( $V_{DS} = 600$  V;  $V_{GS} = 18$  V;  $T_{CASE} = 27$  °C; CREE).

<sup>287</sup> slowed down choosing  $V_{\rm DS} = 600$  V. The thermal map of <sup>288</sup> Fig. 15 corresponds to the current distribution at turn OFF, <sup>289</sup> that is, just before the failure event (as indicated in the figure). <sup>290</sup> It clearly reveals that the failure arises from high power density <sup>291</sup> being confined to an extremely small area (encircled red dots <sup>292</sup> in the figure) corresponding to the formation of a hot spot.

When there is local growth of leakage carriers, a cluster 293 of adjacent cells might tend to drain more current triggering 294 the thermal runaway event. The current crowds in a limited 295 portion of the total area, activating a self-sustained process that 296 promptly entails the creation of the hot spot. The increase in 297 the current at the end of the SC pulse (before thermal runaway 298 takes place) is much more pronounced in simulation than 299 in experimental waveforms. It is a consequence of the used 300 simulation approach, in which just a single cell is investigated. 301 Thus, the electrothermal interaction with surrounding cells, 302 leading to a stronger positive feedback, is not taken into 303 account. 304

Nonetheless, the mechanism explained above is not the only source of failure that was observed.

At some different applied conditions, for which the power applied is lower (e.g., the one in Fig. 16), current tails still appear but the device experiences a different phenomenon.

Fig. 15. Normalized temperature increase at  $t = 8 \ \mu s$  for the experiment of Fig. 14.

Fig. 16.  $I_D$  short-circuit waveforms ( $V_{DS} = 400$  V;  $V_{GS} = 18$  V;  $T_{CASE} = 27$  °C; CREE).

For this test, SC pulses of gradually increasing width were 310 applied to the DUT and thermal maps were acquired at 311 the end of each experiment. After a certain pulse length 312 (17  $\mu$ s in this case), the device does not turn ON anymore. 313 Inspection of temperature distribution at the end of different 314 pulses (Fig. 17) illustrates areas on the device surface that are 315 activated partially. Focusing on the encircled area of Fig. 17(b) 316 and the same device portion in Fig. 17(a), a transition from an 317 almost uniform current to a less homogeneous one is visible. 318 Since for a MOSFET without any unstable behavior the current 319 should expand in all active areas, it could be assumed that 320 those areas were somehow degraded. They are thus prone 321 to carry less current, eventually being inoperative. Moreover, 322 a residual resistance of tens of ohms was measured between 323 the gate and the source. 324

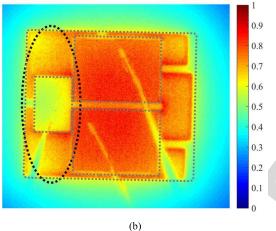

#### B. Low-Voltage Long-Pulse Tests

In order to try to get a better understanding of the origin of the aforementioned observed failure, different tests were performed. Devices were subjected to SC for long pulse widths (100  $\mu$ s) but with a low applied voltage (<250 V). In this way, it is possible to slow down the temperature dynamics, and hence to analyze the device response to long thermal stress. The pulse length is kept constant and the voltage

325

AO:7

AO:8

Fig. 17. Normalized temperature increase for the experiment of Fig. 16 at (a)  $t = 10 \ \mu s$  and (b)  $t = 17 \ \mu s$ .

is increased at each step. Resulting current waveforms at 333 different  $V_{DS}$  are reported in Fig. 18, where the effect of 334 temperature rise on the current profile is clearly visible. When 335 a certain voltage value is reached (175 V in this case), the 336 device is not able to withstand the entire pulse duration and 337 fails after approximately 85  $\mu$ s, corresponding to the time 338 instant at which the drain current drops to zero. In addition, 339 it is interesting to note that, at the same time, the gate-source 340 voltage drops to zero as well, and the gate current suddenly 341 increases (Fig. 18). It is then straightforward to assume that 342 the device turned OFF because an SC had happened between 343 the gate and the source, confirmed by the subsequent measure 344 of  $R_{\rm GS}$  (<1  $\Omega$ ). It could be supposed that the metallization 345 and/or passivation layers on the top of a MOSFET might be 346 melted or somehow corrupted. 347

Hence, in this case, the device does not undergo catastrophic 348 failure as previously explained, but it is not operative anymore 349 because of damage to the gate/source structure. 350

#### **IV. DISCUSSION**

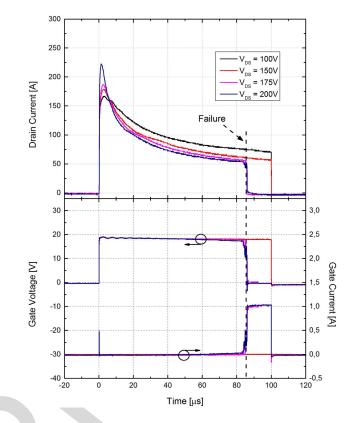

After description in the previous section, here an explana-352 tion of different failure mechanisms during SC for a SiC power 353 MOSFET is given. As made clear by the reported results, 354 two separate phenomena might happen when a device fails. 355

351

Fig. 18.  $I_D$ ,  $V_{GS}$ ,  $I_G$  waveforms for a 100- $\mu$ s pulse test.

It is convenient to indicate them as failure mode I and 356 failure mode II.

357 In the first type, the device experiences a destructive mech-358 anism due to exponential rise in drain current subsequent to 359 thermal runaway triggering. The second type failure, on the 360 other hand, involves the degradation of the gate structure, with 361 subsequent inability to turn the device ON, which is why it 362 could be considered a soft failure. 363 Both are regulated by the temperature increase inside the 364

365

366

367

368

369

374

device, and more precisely by its growth rate. The concept can be better clarified with the aid of Fig. 19.

- It is useful to define two temperature values:

- 1)  $T_{\text{DEG}}$ , when surface degradation occurs;

- 2)  $T_{\text{TH RNW}}$ , when thermal runaway takes place.

The value at which top-layer materials get corrupted is 370 related to the temperature at which melting or change in 37 properties happens in passivation and metallization layers, and 372 it is obviously lower than the triggering point of thermal 373 runaway.

Temperature rise is, of course, related to the amount of 375 power that a device is subjected to, and therefore to the 376 applied voltage. When the power applied is low, temperature 377 has slow dynamics and might reach  $T_{\text{DEG}}$ , but it cannot reach 378  $T_{\text{TH RNW}}$ . If the surface is exposed to  $T_{\text{DEG}}$  for sufficient time, 379 permanent damage occurs [Fig. 19(b), failure mode II]. The 380 gate/source structure is compromised, and therefore the device 381 loses partially or totally its ability to conduct current. 382

On the other hand, a higher power leads to a prompt temper-383 ature increase. It suddenly reaches  $T_{\text{TH RNW}}$ ; a large amount 384 of carriers are then generated, and the leakage current reaches 385

Fig. 19. Interpretation of two types of failure. AO:9

a value at which thermal runaway is activated. Drain current 386 rises uncontrollably and the device blows up (failure mode I). 387 In this case, the time duration for which the device AQ:10 388

TABLE I ARORA MOBILITY MODEL PARAMETERS

| Amin [cm <sup>2</sup> /Vs] | 22.83             |

|----------------------------|-------------------|

| α <sub>m</sub>             | -0.536            |

| $A_d [cm^2/Vs]$            | 53.92             |

| $\alpha_{d}$               | -2.2              |

| $A_N [cm^{-3}]$            | $2 \cdot 10^{17}$ |

| α <sub>N</sub>             | 0.72              |

| Aa                         | 0.76              |

| α <sub>a</sub>             | 0.722             |

remains at  $T_{\text{DEG}}$  is not enough for the surface to be fully 389 damaged [Fig. 19(a)]. 390

Under all other conditions, for a moderate applied power, 391 the failure is regulated by the time needed to degrade the 392 device and the one needed to reach the thermal runaway point. 393 When the former is higher, even if the temperature has a value 394 able to produce detrimental degradation, thermal runaway is 395 the predominant mechanism. 396

### V. CONCLUSION

In this paper, interpretation of SC failure event of SiC Power 398 MOSFETs has been given. The aim is to define the limits of 300 their SC capability. 400

Thanks to the investigation of experimental data, two different failure dynamics have been identified. The first is related to thermal runaway induced by the high value of leakage current. Gate-source shorting due to breakup of top layers is the second failure mechanism observed. Which one occurs depends on the power the device has to dissipate (i.e., by the bus voltage) 406 which affects the temperature rise time.

Thanks to numerical simulations, it has been possible to 408 carry out an in-depth analysis of the physics involved in those 409 phenomena. 410

It is then possible to state that the SC withstanding capability of SiC power MOSFETs is limited by the heat generated inside the structure, specifically in the JFET region.

Even though one of the most marked properties of SiC is 414 the material's higher thermal conductivity, SiC devices have 415 usually reduced volume compared to the same rated silicon 416 devices. It results in extremely high temperature increase, 417 which drastically reduces the device SC ruggedness. 418

#### **APPENDIX**

In Section II-A, the structure implemented was reported, 420 along with the geometrical dimensions [Fig. 1(a)]. 421 As explained, numerical parameters were calibrated to fit the 422 static  $I_D - V_{GS}$  curves of a commercial device and to reproduce 423 the same behavior observed experimentally during SC. Among 424 all, mobility and interface traps play a key role. 425

Channel mobility was modeled using the Arora model 426 implemented in the simulator [37], whose parameters for elec-427 trons were chosen during the calibration procedure (Table I), 428 and its analytical expressions are 429

1

$$\mu_{\text{Arora}} = \mu_{\min} + \frac{\mu_d}{1 + (N_D/N_0)^{A^*}}$$

(A.1) 430

AQ:11 404

397

401

402

403

405

407

411

412

413

487

488

489

490

491

492

493

494

495

496

497

498

499

500

501

502

503

504

505

506

507

508

509

510

511

512

513

514

515

516

517

518

519

520

521

522

523

524

525

526

527

529

530

531

532

536

537

538

539

540

541

542

543

544

545

546

547

548

549

550

551

552

554

556

557

558

TABLE II INTERFACE DEFECT PARAMETERS

| $Q_F [cm^{-2}]$                 | $2.68 \cdot 10^{12}$ |

|---------------------------------|----------------------|

| $Q_{\rm A}$ [cm <sup>-2</sup> ] | $7 \cdot 10^{11}$    |

| $E_0 [eV]$                      | 0.18                 |

| $E_s$ [eV]                      | 0.1                  |

with 431

437

441

454

456

457

458

459

461

463

432

$$\mu_{\min} = A_{\min} \left(\frac{T}{300 \text{ K}}\right)^{\alpha_m}, \quad \mu_d = A_d \left(\frac{T}{300 \text{ K}}\right)^{\alpha_d}$$

(A.2)

433

$$N_0 = A_N \left(\frac{T}{300 \text{ K}}\right)^{\alpha_N}, \quad A^* = A_a \left(\frac{T}{300 \text{ K}}\right)^{\alpha_a}.$$

(A.3)

In addition, both positive fixed charges  $Q_F$  and acceptor-434 type traps  $Q_A$  were introduced at the SiO<sub>2</sub>/SiC interface. Traps 435 were described with a uniform energy distribution [37] 436

$$E_0 - 0.5E_S < E < E_0 + 0.5E_S \tag{A.4}$$

where  $E_0$  is the center of the energy distribution from the 438 conduction band level  $E_C$ . Table II reports the used numeric 439 values. 440

#### REFERENCES

- [1] P. Alexakis, O. Alatise, J. Hu, S. Jahdi, L. Ran, and P. A. Mawby, 442 "Improved electrothermal ruggedness in SiC MOSFETs compared 443 444 with silicon IGBTs," IEEE Trans. Electron Devices, vol. 61, no. 7, pp. 2278–2286, Jul. 2014. 445

- [2] P. Losee et al., "1.2 kV class SiC MOSFETs with improved performance 446 over wide operating temperature," in Proc. 26th ISPSD, Waikoloa, HI, 447 USA, 2014, pp. 297-300. AQ:12 448

- 449 [3] R. Tanaka et al., "Impact of grounding the bottom oxide protection layer on the short-circuit ruggedness of 4H-SiC trench MOSFETs," in Proc. 450 451 26th ISPSD, Waikoloa, HI, USA, 2014, pp. 75-78.

- [4] Z. Chen, Y. Yao, D. Boroyevich, K. D. T. Ngo, P. Mattavelli, and 452 K. Rajashekara, "A 1200-V, 60-A SiC MOSFET multichip phase-leg 453 module for high-temperature, high-frequency applications," IEEE Trans. Power Electron., vol. 29, no. 5, pp. 2307-2320, May 2014. 455

- [5] J. A. Schrock et al., "High-mobility stable 1200-V, 150-A 4H-SiC DMOSFET long-term reliability analysis under high current density transient conditions," IEEE Trans. Power Electron., vol. 30, no. 6, pp. 2891-2895, Jun. 2015.

- X. Huang, G. Wang, L. Jiang, and A. Q. Huang, "Ruggedness analy-[6] 460 sis of 600 V 4H-SiC JBS diodes under repetitive avalanche conditions," in Proc. 27th APEC, 2012, pp. 1688-1691. [Online]. Available: 462 http://dx.doi.org/10.1109/APEC.2012.6166048

- A. Konstantinov, S. Jinman, S. Young, F. Allerstam, and T. Neyer, 464 Silicon carbide Schottky-barrier diode rectifiers with high avalanche 465 466 robustness," in Proc. PCIM Europe, May 2015, pp. 1-7.

- X. Huang, G. Wang, M.-C. Lee, and A. Q. Huang, "Reliability [8] 467 of 4H-SiC SBD/JBS diodes under repetitive surge current stress,' 468 469 in Proc. ECCE, Sep. 2012, pp. 2245-2248. [Online]. Available: http://dx.doi.org/10.1109/ECCE.2012.6342436 470

- 471 [9] R. A. Wood and T. E. Salem, "Long-term operation and reliability study of a 1200-V, 880-A all-SiC dual module," in Proc. SPEEDAM, 472 Jun. 2012, pp. 1520-1525. [Online]. Available: http://dx.doi.org/ 473 474 10.1109/SPEEDAM.2012.6264530

- M. Riccio, A. Castellazzi, G. De Falco, and A. Irace, "Experimen-[10] 475 tal analysis of electro-thermal instability in SiC power MOSFETs," 476 Microelectron. Rel., vol. 53, nos. 9-11, pp. 1739-1744, Sep./Nov. 2013. 477 [Online]. Available: http://dx.doi.org/10.1016/j.microrel.2013.07.014 478

- [11] M. Trivedi and K. Shenai, "Failure mechanisms of IGBTs under short-479 circuit and clamped inductive switching stress," IEEE Trans. Power 480 Electron., vol. 14, no. 1, pp. 108-116, Jan. 1999. 481

- [12] K. Chinnaswamy, P. Khandelwal, M. Trivedi, and K. Shenai, 482 'Unclamped inductive switching dynamics in lateral and vertical power 483 DMOSFETs," in Proc. 34th IAS Annu. Meeting Conf. Rec. IEEE 484 Ind. Appl. Conf., vol. 2. 1999, pp. 1085-1092. [Online]. Available: 485 http://dx.doi.org/10.1109/IAS.1999.801639 AO:13 486

- [13] J.-B. Lee and D.-S. Hyun, "Gate voltage pattern analyze for shortcircuit protection in IGBT inverters," in Proc. IEEE PESC, Jun. 2007, pp. 1913-1917.

- [14] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, and B. J. Blalock, "A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules," IEEE Trans. Power Electron., vol. 29, no. 7, pp. 3720-3732, Jul. 2014.

- [15] M. A. Rodríguez-Blanco, A. Vázquez-Pérez, L. Hernández-González, V. Golikov, J. Aguayo-Alquicira, and M. May-Alarcón, "Fault detection for IGBT using adaptive thresholds during the turn-on transient," IEEE Trans. Ind. Electron., vol. 62, no. 3, pp. 1975-1983, Mar. 2015.

- [16] Z. Wang, X. Shi, Y. Xue, L. M. Tolbert, F. Wang, and B. J. Blalock, "Design and performance evaluation of overcurrent protection schemes for silicon carbide (SiC) power MOSFETs," IEEE Trans. Ind. Electron., vol. 61, no. 10, pp. 5570-5581, Oct. 2014.

- [17] D. Othman, S. Lefebvre, M. Berkani, Z. Khatir, A. Ibrahim, and A. Bouzourene, "Robustness of 1.2 kV SiC MOSFET devices," Microelectron. Rel., vol. 53, nos. 9-11, pp. 1735-1738, Sep./Nov. 2013. [Online]. Available: http://dx.doi.org/10.1016/j.microrel.2013.07.072

- [18] C. Chen, D. Labrousse, S. Lefebvre, M. Petit, C. Buttay, and H. Morel, "Robustness in short-circuit mode of SiC MOSFETs," in Proc. PCIM Europe, May 2015, pp. 1-8.

- G. Kampitsis, S. Papathanassiou, and S. Manias, "Comparative eval-[19] uation of the short-circuit withstand capability of 1.2 kV silicon carbide (SiC) power transistors in real life applications," Microelectron. Rel., vol. 55, no. 12, pp. 2640-2646, Dec. 2015.

- [20] J. A. Schrock et al., "Failure analysis of 1200-V/150-A SiC MOSFET under repetitive pulsed overcurrent conditions," IEEE Trans. Power Electron., vol. 31, no. 3, pp. 1816-1821, Mar. 2016.

- Z. Wang et al., "Temperature-dependent short-circuit capability of [21] silicon carbide power MOSFETs," IEEE Trans. Power Electron., vol. 31, no. 2, pp. 1555-1566, Feb. 2016.

- [22] T. H. Duong, J. M. Ortiz, D. W. Berning, A. R. Hefner, S.-H. Ryu, and J. W. Palmour, "Electro-thermal simulation of 1200 V 4H-SiC MOSFET short-circuit SOA," in Proc. 27th ISPSD, Hong Kong, 2015, pp. 217-220.

- [23] X. Huang, G. Wang, Y. Li, A. Q. Huang, and B. J. Baliga, "Short-circuit capability of 1200 V SiC MOSFET and JFET for fault protection," in Proc. 28th APEC, Mar. 2013, pp. 197-200.

- B. J. Baliga, *Silicon Carbide Power Devices*. Singapore: World Scientific, 2005. [24] В.

- [25] C2M0080120D Datasheet, Wolfspeed, Durham, NC, USA.

- V. d'Alessandro et al., "SPICE modeling and dynamic elec-[26] trothermal simulation of SiC power MOSFETs," in Proc. 26th ISPSD, Waikoloa, HI, USA, 2014, pp. 285-288. [Online]. Available: http://dx.doi.org/10.1109/ISPSD.2014.6856032

- [27] H. Yano, T. Hirao, T. Kimoto, H. Matsunami, and H. Shiomi, "Interface properties in metal-oxide-semiconductor structures on n-type 4H-SiC (0338)," App. Phys. Lett., vol. 81, no. 25, pp. 4772-4774, 2002.

- [28] K. Matocha, "Challenges in SiC power MOSFET design," Solid-State Electron., vol. 52, no. 10, pp. 1631-1635, 2008.

- [29] SCT2080KE Datasheet, ROHM Semicond., Kyoto, Japan.

- [30] SCT30N120 Datasheet, STMicroelectronics, Geneva, Switzerland.

- [31] G. Romano, M. Riccio, G. De Falco, L. Maresca, A. Irace, and G. Breglio, "An ultrafast IR thermography system for transient temperature detection on electronic devices," in Proc. 30th SEMI-THERM, Mar. 2014, pp. 80-84. [Online]. Available: http:// dx.doi.org/10.1109/SEMI-THERM.2014.6892219

- [32] M. Riccio, A. Pantellini, A. Irace, G. Breglio, A. Nanni, and C. Lanzieri, "Electro-thermal characterization of AlGaN/GaN HEMT on silicon microstrip technology," Microelectron. Rel., vol. 51, nos. 9-11, pp. 1725-1729, Sep./Nov. 2011. [Online]. Available: http://dx.doi.org/ 10.1016/j.microrel.2011.07.003

- [33] A. Castellazzi, A. Fayyaz, L. Yang, M. Riccio, and A. Irace, "Shortcircuit robustness of SiC power MOSFETs: Experimental analysis," in Proc. 26th ISPSD, Waikoloa, HI, USA, 2014, pp. 71-74.

- [34] J. Lutz, H. Schlangenotto, U. Scheuermann, and R. De Doncker, Semiconductor Power Devices: Physics, Characteristics, Reliability. Springer, 2011.

- [35] T. T. Mnatsakanov, L. I. Pomortseva, and S. N. Yurkov, "Semiempirical model of carrier mobility in silicon carbide for analyzing its dependence on temperature and doping level," Semiconductors, vol. 35, no. 4, pp. 394-397, 2001.

- [Online]. Available: http://www.ioffe.ru/SVA/NSM/ [36]

- SentaurusTM Device User Guide, Version K-2015.06, Synopsis Inc., [37] 561 Mountain View, CA, USA, Jun. 2015.

528 AQ:14

533 534 535

553

- 555 AQ:15

559 560 AQ:16

562 AQ:17

10

AO:18 563 564 565 566 567 568 569 570 571 572

Gianpaolo Romano received the B.Sc., M.S. (cum laude), and Ph.D. degrees from the University of Naples Federico II, Naples, Italy, in 2011, 2013, and 2016, respectively, all in electronics engineering.

His research area is mainly focused on SiC power MOSFETs. His current research interests include electrothermal characterization and simulation of power semiconductor devices, and advanced testing of electron devices.

Giovanni Breglio received the Degree (cum laude) in electronics engineering and the Ph.D. degree in electronic engineering and computer science from the University of Naples Federico II, Naples, Italy, in 1990 and 1994, respectively.

He is currently an Associate Professor of Electron-615 ics with the University of Naples Federico II. He has 616 authored more than 50 peer-reviewed journal papers 617 and more than 110 proceedings of international 618 conferences. His current research interests include the electrothermal modeling and characterization of 620

semiconductor devices, the design of optoelectronic devices, and the development of new fiber optical sensors.

Asad Fayyaz received the M.Eng. (Hons.) degree in electronic and communications engineering from The University of Nottingham, Nottingham, U.K., in 2013, where he is currently pursuing the Ph.D. degree with the Power Electronics, Machines and Control Group.

His current research interests include characterization and electrothermal modeling of widebandgap power devices, mainly SiC power MOSFETs.

592

593 devices Michele Riccio received the B.Sc., M.S., and Ph.D. degrees from the University of Naples Federico II, Naples, Italy, in 2004, 2007, and 2011, respectively, all in electronics engineering.

He is currently a Research Fellow with the Department of Electric and Information Technology Engineering, University of Naples Federico II. His current research interests include electrothermal modeling and simulation of power devices, and advanced experimental characterization of electrical and thermal behavior of solid-state electronic

AQ:19 594 595 596 597 598 599 600 601 602 603

Luca Maresca was born in 1983. He received the B.S., M.S., and Ph.D. degrees from the University of Naples Federico II, Naples, Italy, in 2005, 2009, and 2013, respectively, all in electronics engineering.

He aided the development of advanced IGBTs through advanced and calibrated electrothermal TCAD device simulations. He was involved in the development of SiPm as well. He is currently developing modeling and simulation capability of bipolar devices in avalanche conditions, aiding in the devel-

604 opment of high-reliability power devices. He is currently a Research Fellow 605 with the Department of Electrical Engineering and Information Technologies, 606 607 University of Naples Federico II. His current research interests include modeling, simulation, and experimental characterization of semiconductor 608 power devices. 609

Alberto Castellazzi (M'-) received the Laurea degree in physics from the University of Milan, Milan, Italy, in 1998, and the Ph.D. degree in electrical engineering from the Munich University of Technology, Munich, Germany, in 2004. He is currently an Associate Professor of Power

628 Electronics with The University of Nottingham, 629 Nottingham, U.K. He has been active in power 630 electronics research and development for over 631 15 years and has had extensive collaborations with 632 major European and international industrial research 633

laboratories and groups on publicly and privately funded research projects. 634 He has authored or co-authored over 130 papers in peer-reviewed specialist 635 journals and conference proceedings, for which he also regularly acts as a 636 Reviewer. His current research interests include characterization, modeling, 637 application, packaging, and cooling of power devices. 638 639

Dr. Castellazzi is a member of the Technical Program Committee of the ISPSD, ESTC, ESREF, and ECCE-Asia conferences.

Andrea Irace (M'98-SM'12) received the Laurea 641 and Ph.D. degrees in electronics engineering from 642 the University of Naples Federico II, Naples, Italy, 643 in 1994 and 1998, respectively. 644

He is currently an Associate Professor with the 645 Department of Electrical Engineering and Informa-646 tion Technology, University of Naples Federico II, 647 Naples, Italy, where he teaches integrated analog 648 circuits and electronics. He has co-authored over 649 150 papers in refereed international journals and 650 conference proceedings. His current research inter-651

ests include power semiconductor devices, with especial emphasis on their thermal behavior, and optoelectronic devices.

Prof. Irace is a member of the Technical Program Committee of the IEEE International Symposium on Power Semiconductor Devices and ICs, and a Reviewer for several international journals and conferences.

623 AQ:22

610 AQ:20

611 AQ:21

612

613

614

619

621

622

624

640

652

653

654

655

656

625 626