Reyes-Moraga, Eduardo Felipe (2015) Predictive control of a direct series resonant converter with active output voltage compensation. PhD thesis, University of Nottingham.

# Access from the University of Nottingham repository: http://eprints.nottingham.ac.uk/31263/1/Thesis EFRM.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# Predictive Control of a Direct Series Resonant Converter with Active Output Voltage Compensation

Eduardo Felipe Reyes-Moraga

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

FEBRUARY 2015

#### **Abstract**

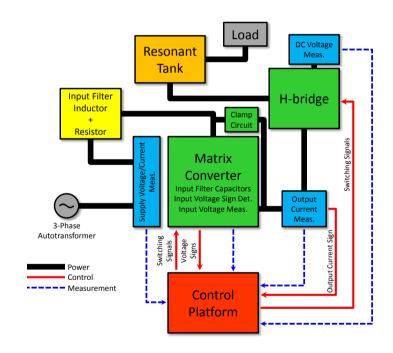

Modern high power supplies are based on resonant converters in order to use high frequency reactive elements (for reduced size) without sacrificing converter efficiency. In an effort to achieve compact high power supplies, direct power converter topologies have been considered, since these are mainly characterised by their high power density. A direct resonant converter topology combines matrix converters with conventional resonant converters.

This work focused on achieving high quality input/output power and high efficiency. Thus, this thesis presents the research on the control of a direct series resonant converter. Since the resonant converter allows a sinusoidal high frequency output current to be generated, zero current switching (ZCS) was considered to reduce the power losses. Hence, since the converter is switched at every zero crossing of the output current (fixed period), model predictive control was considered.

Different predictive approaches for controlling the input and output currents were developed and analysed, however, owing to the characteristics of the topology, these strategies resulted in a suboptimal control. Therefore, in order to improve the input and output qualities (reduce distortion), an output voltage compensation strategy was proposed. This compensation approach is based on adding an H-bridge converter in series between the matrix converter and the resonant tank. This converter improves the voltage applied to the resonant tank, thus, reducing the distortion at the output and, as a consequence, also the distortion at the input. The H-bridge converter utilises only a small capacitor on the dc side in comparison with conventional resonant converters and operates at a low voltage.

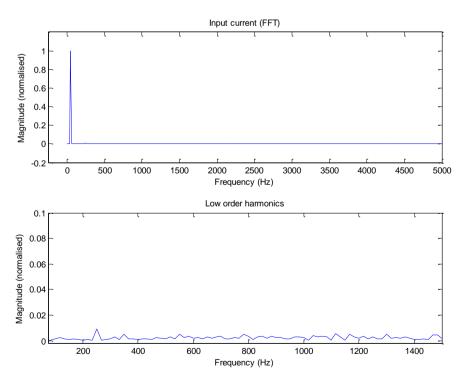

Simulations were carried out using MATLAB/Simulink and an experimental prototype was built to validate the strategies proposed, achieving a reduction of the input current THD from 4.4% to 2.7%, a reduction of the output current distortion of approximately 40% and an analytically derived efficiency of 89.5%.

## Acknowledgements

I would like to express my gratitude to my supervisors Prof Jon Clare and Dr Alan Watson for their support and guidance over the duration of this work. Also, I would like to thank Prof Patrick Wheeler for giving me the opportunity to do my PhD in the PEMC group, and Prof Pericle Zanchetta for his advice and help.

I would also like to express my gratitude to Dr Paul Mitcheson and Dr Alberto Castellazzi for sparing their time to be my examiners.

Moreover, I would like to thank my former supervisor Prof Rubén Peña Guíñez for his help and for believing in me.

Thanks to the PEMC group, especially, Dr Liliana de Lillo, Dr Lee Empringham, Dr Saúl López Arévalo, and future doctors Bilal Arif, Seang Yeoh, Adane Kassa Solomon, Fei Gao, Xiaoyi Bai, Mi Tang and Constanza Ahumada for their great friendship, help and support. Thanks also to Karen Eveson for her precious friendship and help over all these years.

I would like to express my gratitude to the Chilean National Commission for Scientific and Technological Research (Comisión Nacional de Investigación Científica y Tecnológica, CONICYT) for giving me the opportunity to study abroad by granting me a scholarship. Also, thanks to the University of Magallanes for the support during my studies.

Finally, I would like to thank my family for all their support and help over all this time far away from home, and my fiancée, Nuapett, for being so supportive and affectionate, and for your infinite help.

# **Contents**

### CHAPTER 1

| Introduction                                        | 1  |

|-----------------------------------------------------|----|

| 1.1 Introduction                                    | 1  |

| 1.2 Project objectives                              | 2  |

| 1.3 Thesis plan                                     | 3  |

| CHAPTER 2                                           |    |

| Overview of Resonant Power Converters               | 5  |

| 2.1 Introduction                                    | 5  |

| 2.2 Resonant tank configurations                    | 7  |

| 2.3 Load resonant dc-dc converters                  | 10 |

| 2.3.1 Series resonant converter                     | 11 |

| 2.3.2 Parallel resonant converter                   | 11 |

| 2.3.3 Control of load resonant converters           | 12 |

| 2.3.3.1 Frequency control                           | 14 |

| 2.3.3.2 Phase control                               | 16 |

| 2.3.3.3 Frequency-Phase control                     | 18 |

| 2.4 Summary                                         | 20 |

| CHAPTER 3                                           |    |

| Predictive Control of Power Converters              | 21 |

| 3.1 Introduction                                    | 21 |

| 3.2 MPC for a SISO system                           | 23 |

| 3.3 Predictive control methods for power converters | 24 |

| 3.4 MPC applied to power converters                 | 25 |

| 3.4.1 Switching model of a power converter          | 26 |

| 3.4.2 Prediction equations                          | 29 |

| 3.4.3 Cost function and optimisation                | 30 |

| 3.4.4 Delay compensation                            | 31 |

| 3.4.5 Predictive control implementation             | 33 |

| 2.5 Summary                                         | 25 |

# CHAPTER 4

| Direct Resonant Power Converter                                      | 36 |

|----------------------------------------------------------------------|----|

| 4.1 Introduction                                                     | 36 |

| 4.2 Direct resonant converter                                        | 36 |

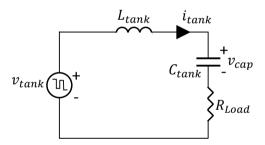

| 4.2.1 Resonant tank                                                  | 37 |

| 4.2.2 Model and switching states                                     | 38 |

| 4.2.3 Bidirectional switches and commutation strategies              | 40 |

| 4.2.4 Input filter                                                   | 42 |

| 4.2.5 Overvoltage protection                                         | 42 |

| 4.3 Zero current switching operation                                 | 43 |

| 4.3.1 Input converter current under ZCS                              | 44 |

| 4.3.2 Parallel resonant tank under ZCS                               | 45 |

| 4.3.3 Series resonant tank under ZCS                                 | 47 |

| 4.4 Limitations under ZCS                                            | 47 |

| 4.4.1 Input current limitation                                       | 47 |

| 4.4.1.1 Input current limitation for a DPRC                          | 48 |

| 4.4.1.2 Input current limitation for a DSRC                          | 48 |

| 4.4.1.3 Input current limitation in terms of converter voltage ratio | 49 |

| 4.4.2 Output converter voltage limitation                            | 50 |

| 4.5 Control of a DRC                                                 | 52 |

| 4.6 Summary                                                          | 52 |

| CHAPTER 5                                                            |    |

| Predictive Control Strategies for a Direct Series Resonant Converter | 53 |

| 5.1 Introduction                                                     | 53 |

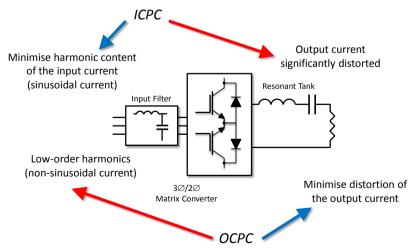

| 5.2 Input current predictive control (ICPC)                          | 54 |

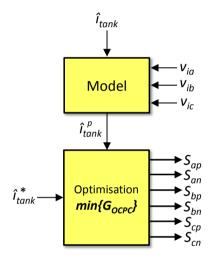

| 5.3 Output current predictive control (OCPC)                         | 57 |

| 5.3.1 Output current prediction as a function of Q                   | 59 |

| 5.4 Input-Output predictive control (IOPC)                           | 60 |

| 5.4.1 Calculation of the input current reference                     | 61 |

| 5.5 Delay compensation                                               | 63 |

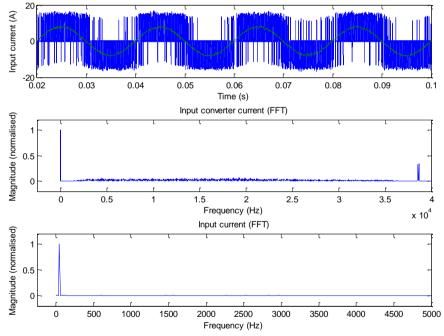

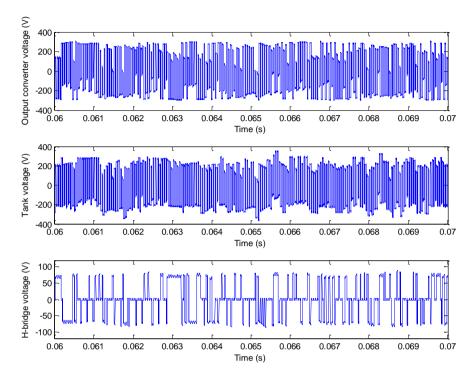

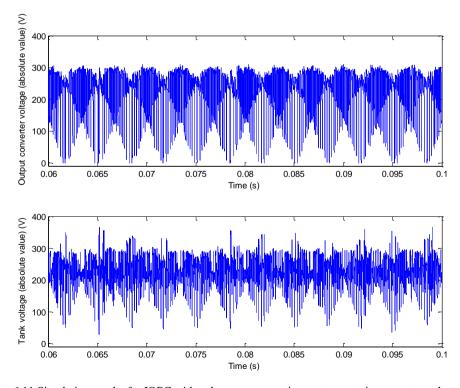

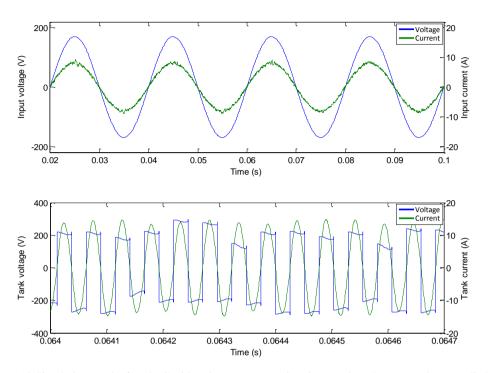

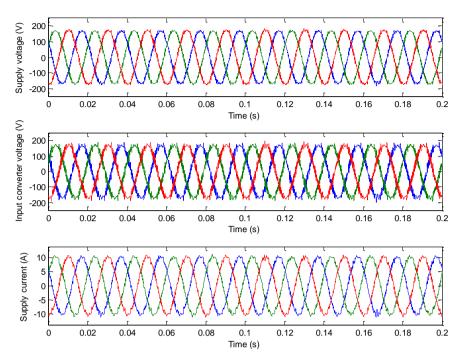

| 5.6 Simulation results                                               | 64 |

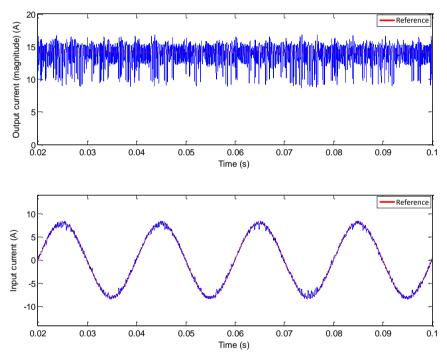

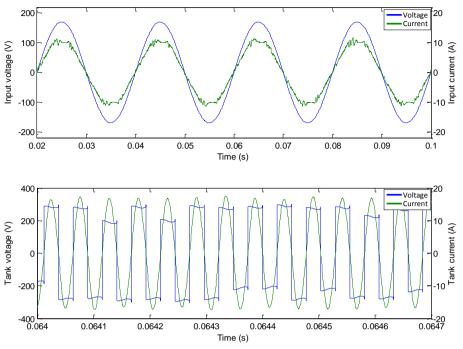

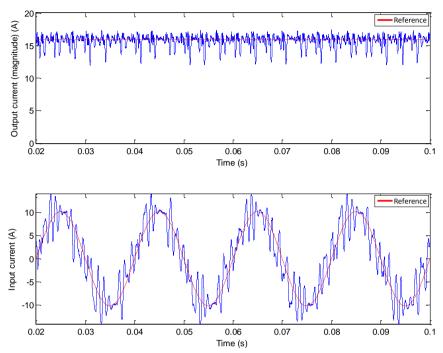

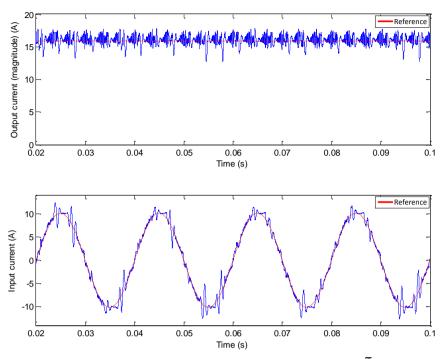

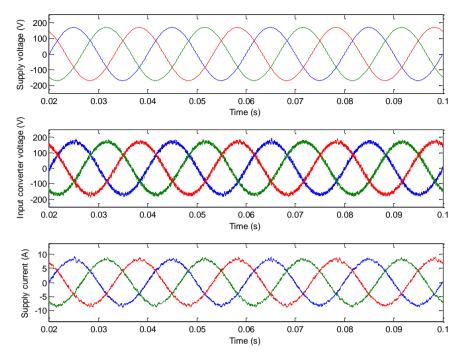

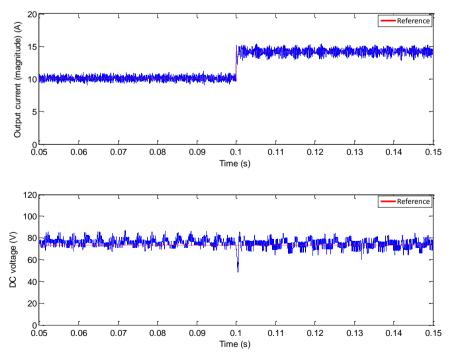

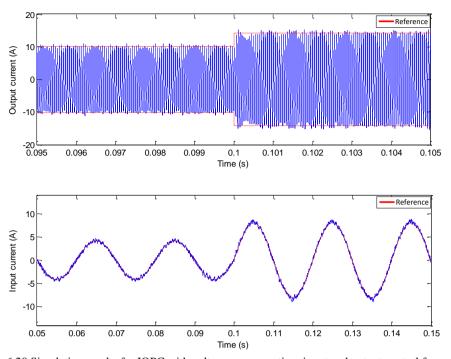

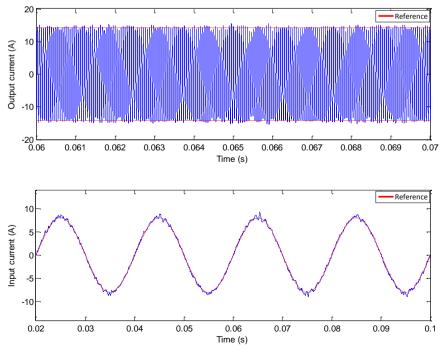

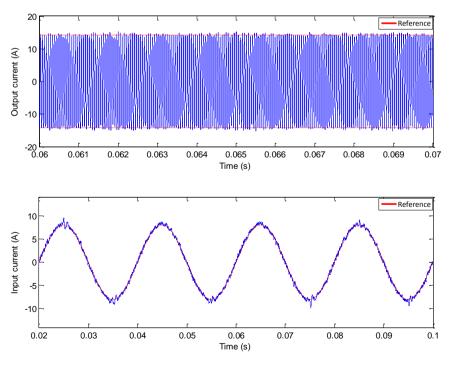

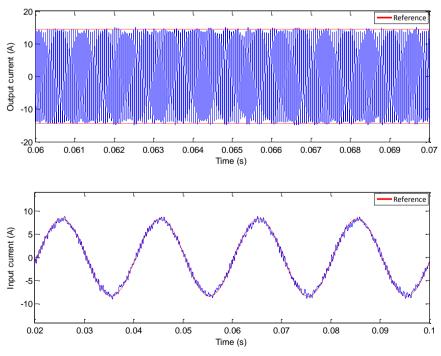

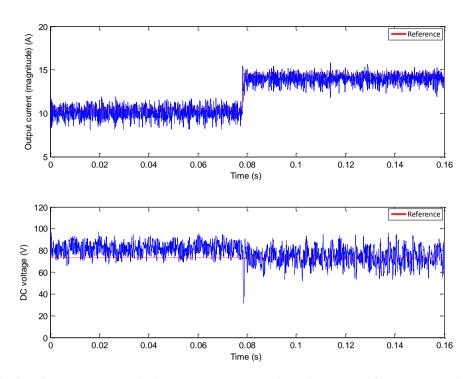

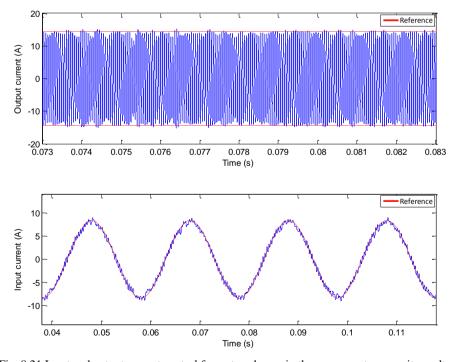

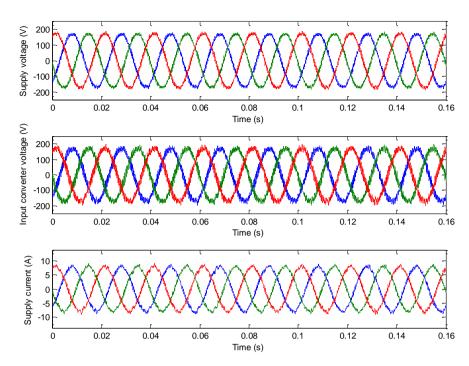

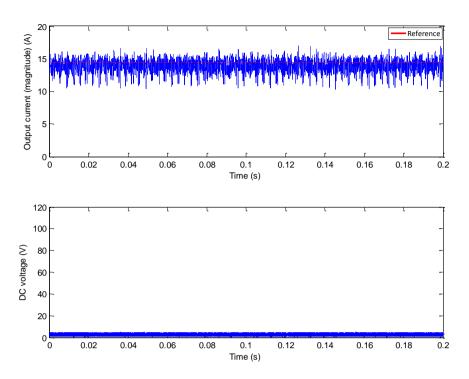

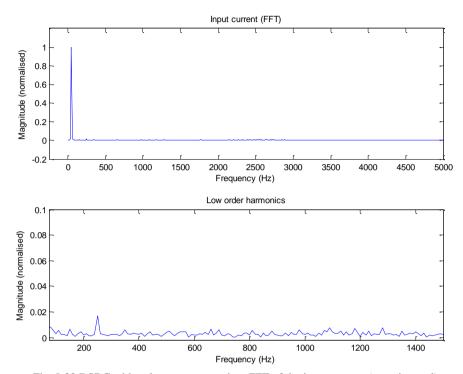

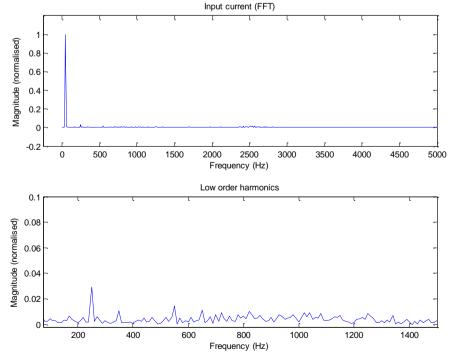

| 5.6.1 Simulation results for ICPC                                    | 65 |

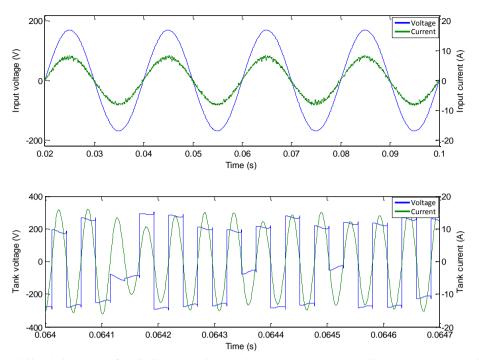

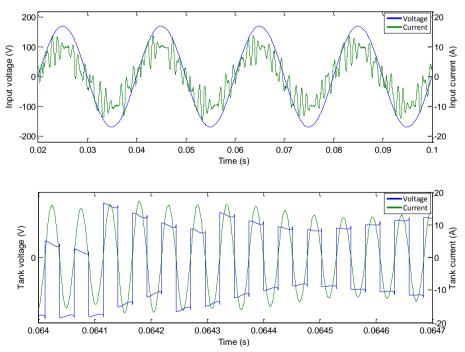

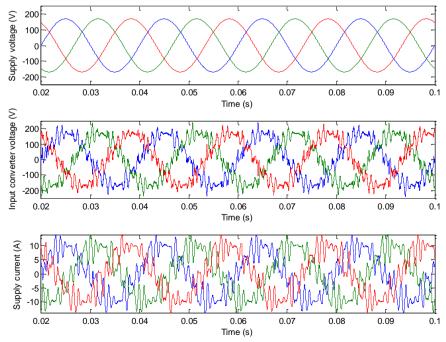

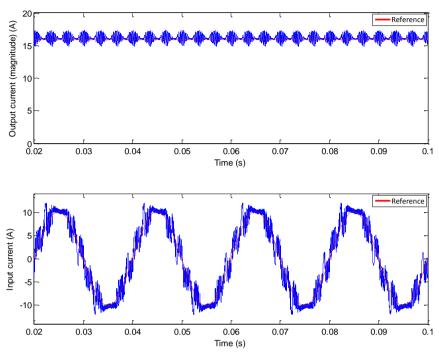

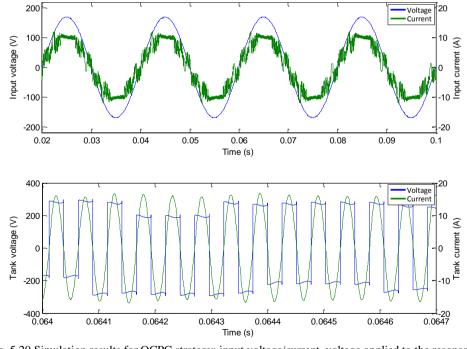

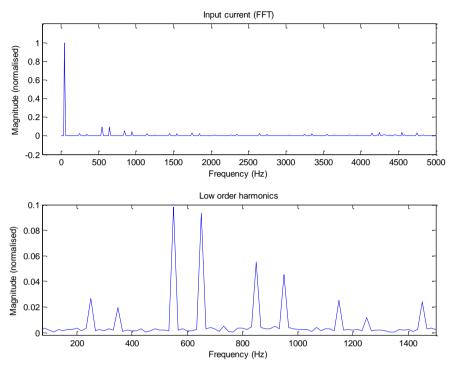

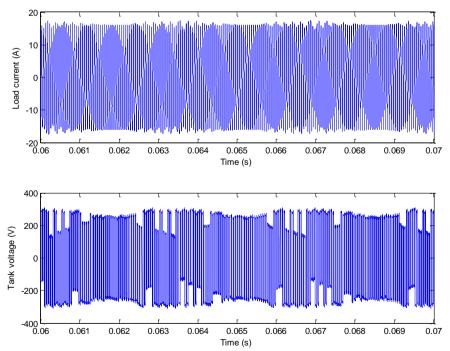

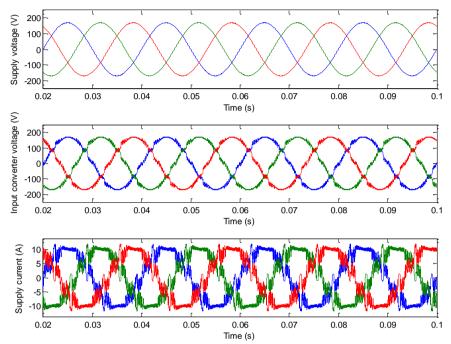

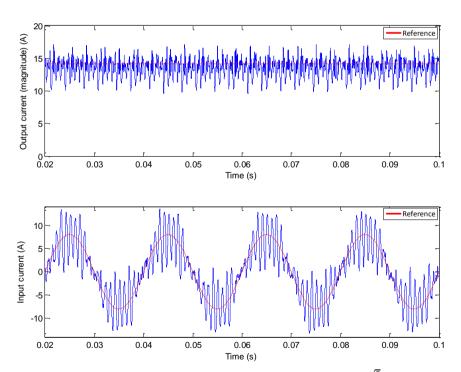

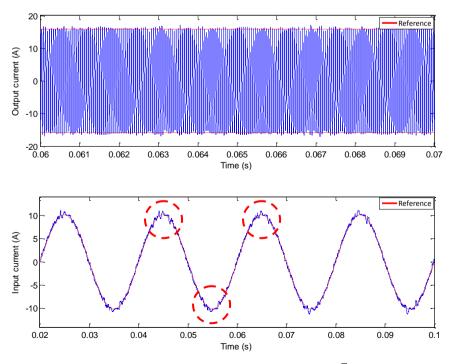

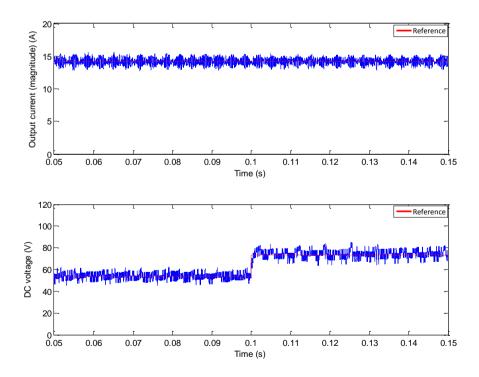

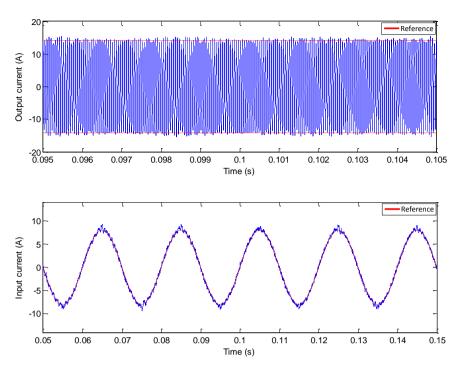

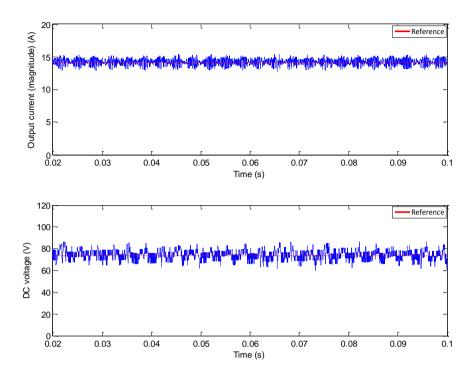

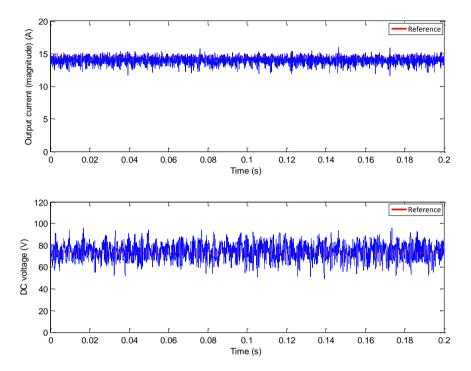

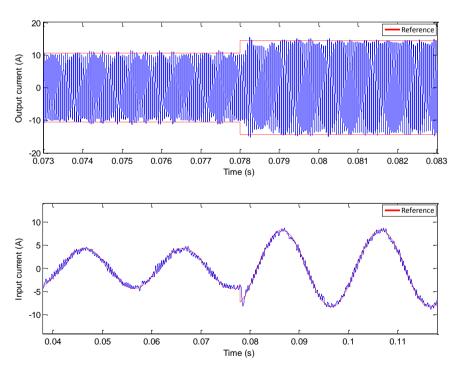

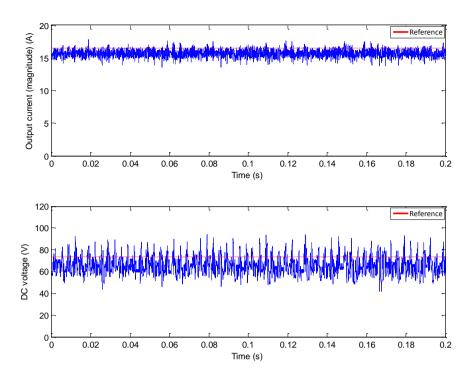

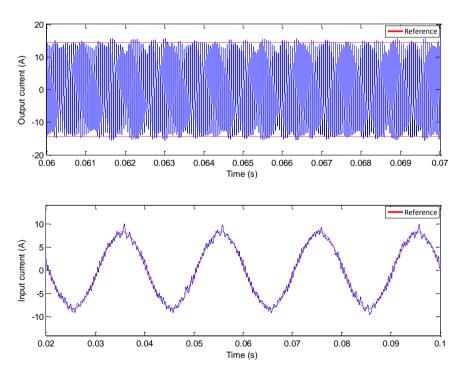

| 5.6.2 Simulation results for OCPC                                    | 69 |

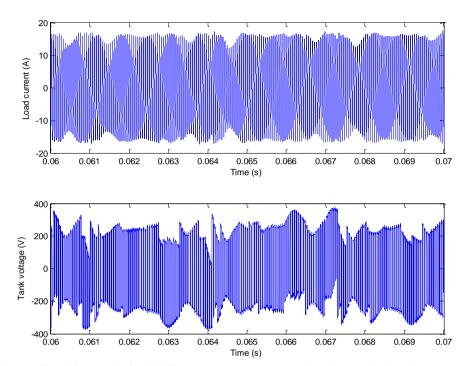

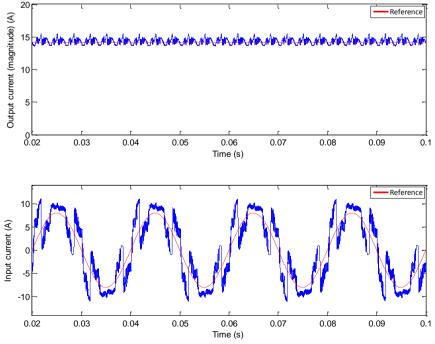

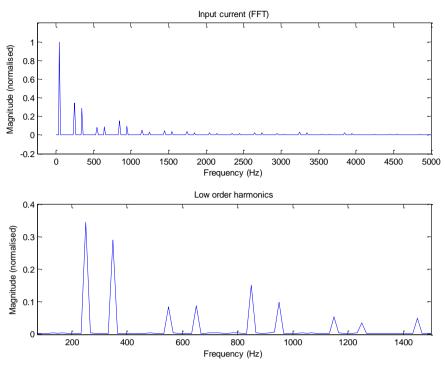

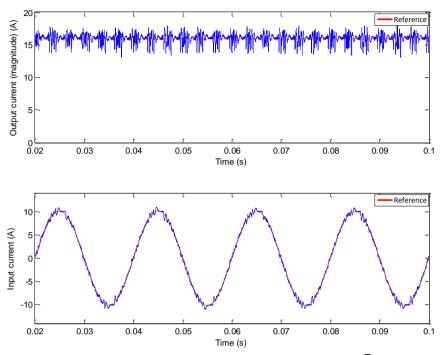

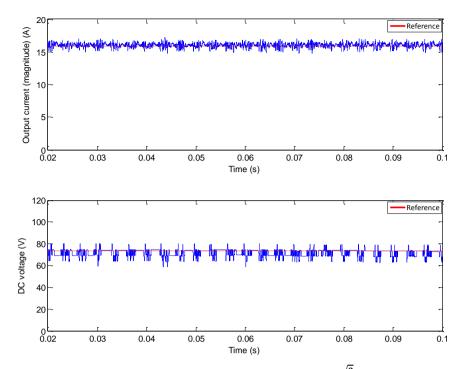

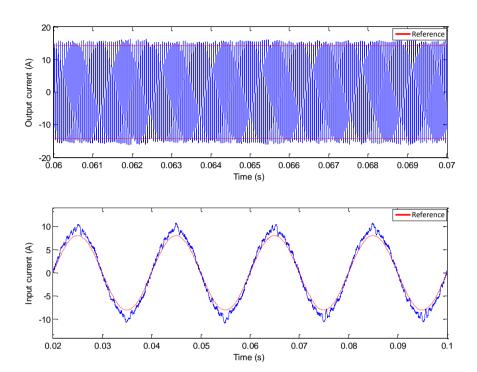

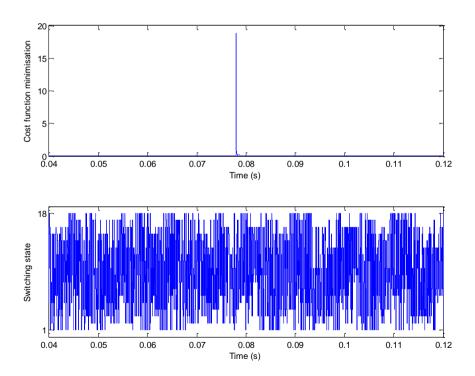

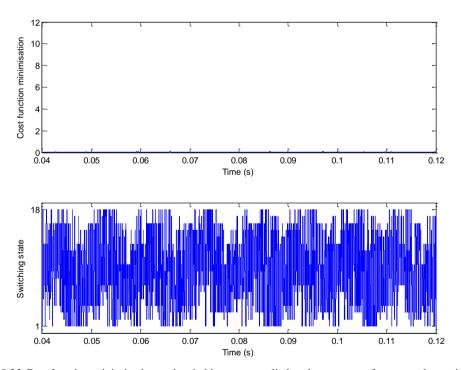

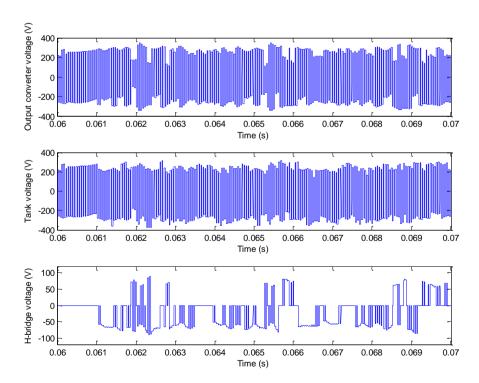

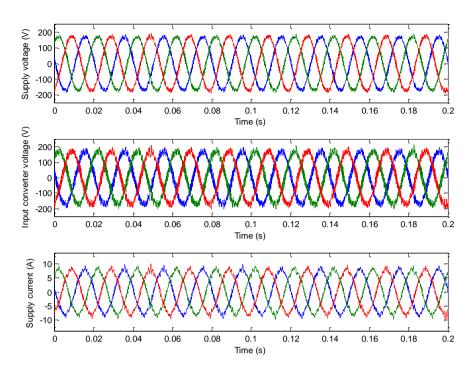

| 5.6.3 Simulation results for IOPC                                    | 75 |

| 5.7 Summary                                                       | 78  |

|-------------------------------------------------------------------|-----|

| CHAPTER 6                                                         |     |

| Direct Series Resonant Converter with Output Voltage Compensation | 79  |

| 6.1 Introduction                                                  | 79  |

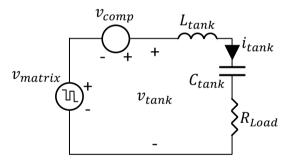

| 6.2 Concept of the output voltage compensation                    | 80  |

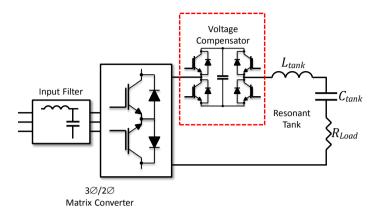

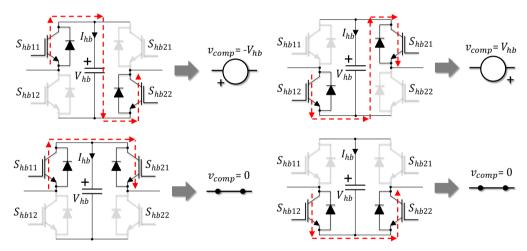

| 6.3 Implementation of the output voltage compensator              | 80  |

| 6.4 Predictive control of the compensator capacitor voltage       | 82  |

| 6.5 Control of a DSRC with output voltage compensation            | 82  |

| 6.5.1 Compensator capacitance calculation                         | 84  |

| 6.5.2 Compensator capacitor voltage reference                     | 84  |

| 6.5.3 IOPC with output voltage compensation                       | 85  |

| 6.5.4 Input current reference                                     | 86  |

| 6.5.5 Delay compensation                                          | 87  |

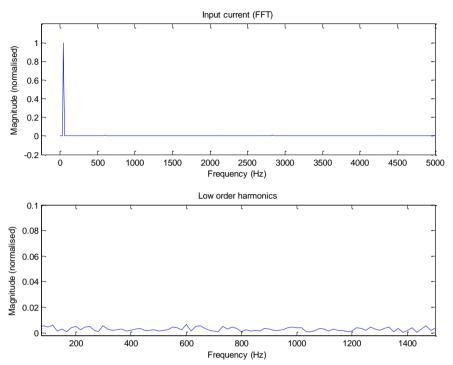

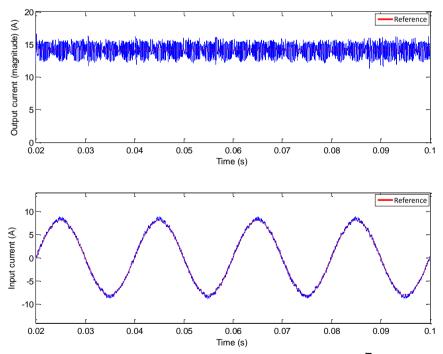

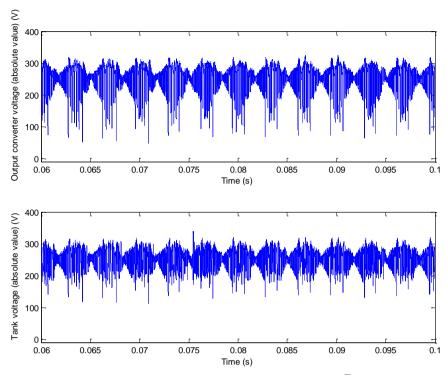

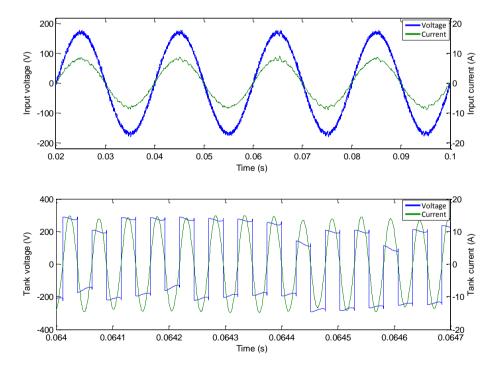

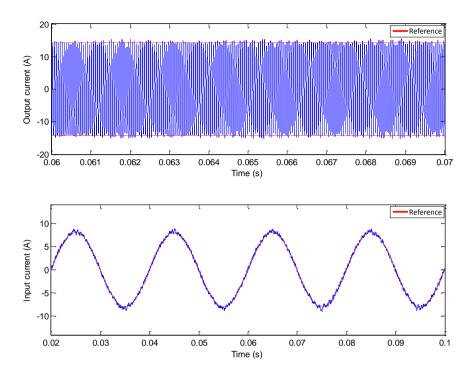

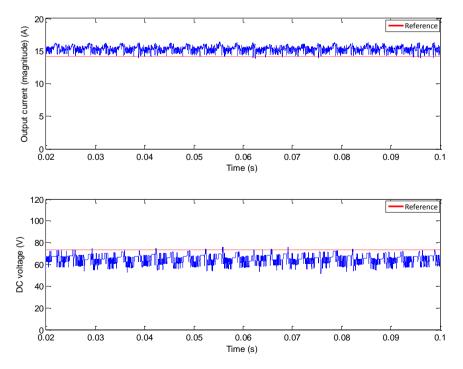

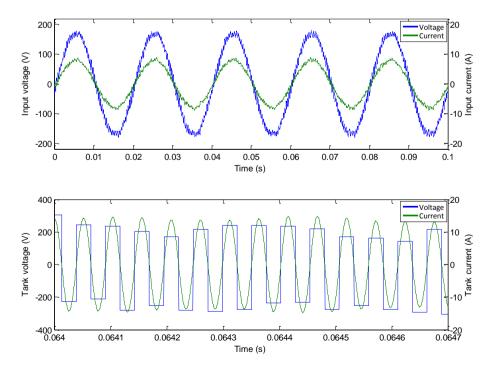

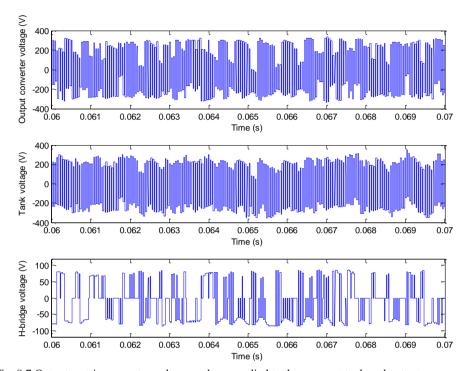

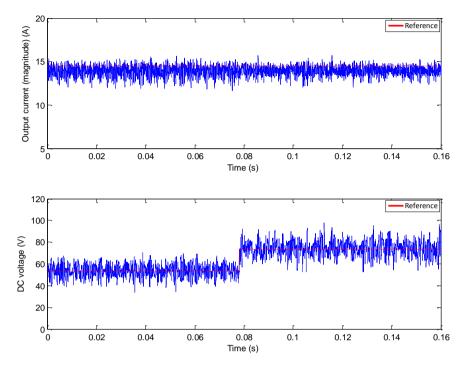

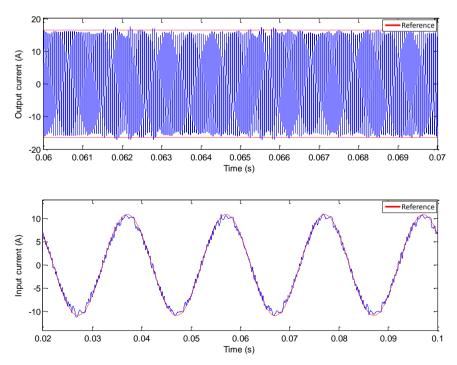

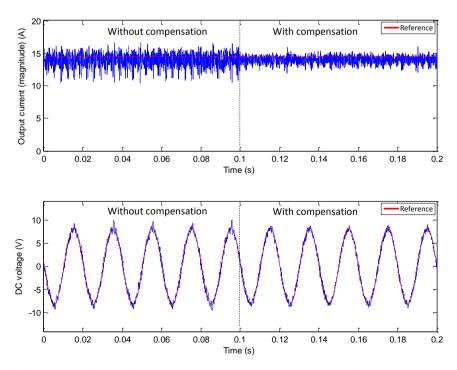

| 6.6 Simulation results                                            | 88  |

| 6.6.1 Effect of model parameter errors                            | 98  |

| 6.7 Summary                                                       | 101 |

| CHAPTER 7                                                         |     |

| Experimental Implementation                                       | 102 |

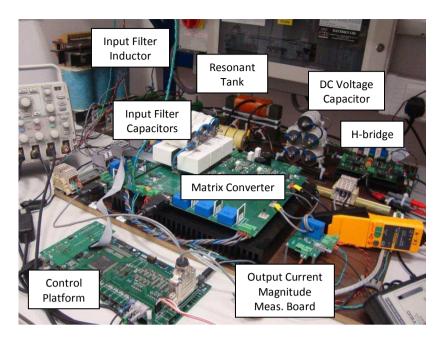

| 7.1 Introduction                                                  | 102 |

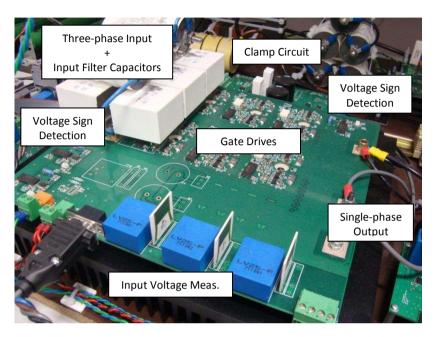

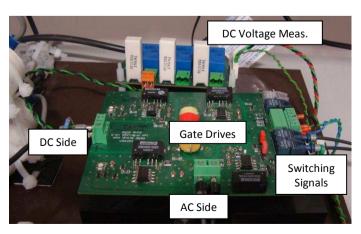

| 7.2 Matrix converter                                              | 103 |

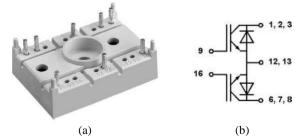

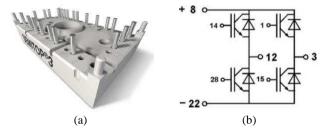

| 7.2.1 Power modules                                               | 104 |

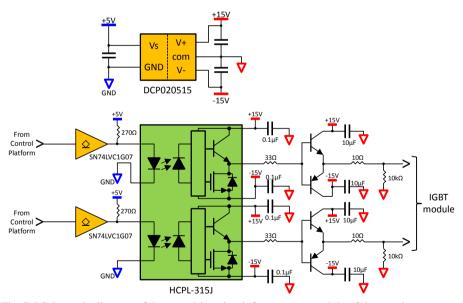

| 7.2.2 Gate drive circuits                                         | 105 |

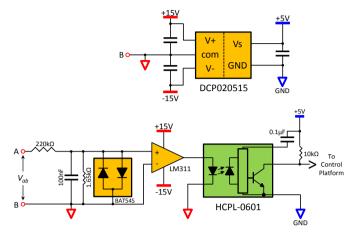

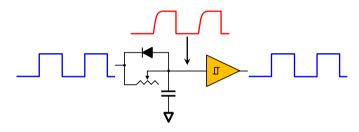

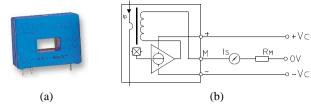

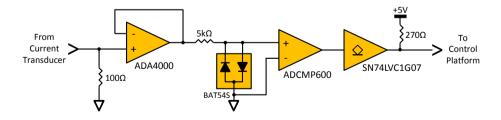

| 7.2.3 Input voltage sign detection                                | 105 |

| 7.2.4 Clamp circuit                                               | 106 |

| 7.2.5 Input filter                                                | 107 |

| 7.3 H-bridge converter                                            | 107 |

| 7.3.1 H-bridge power module                                       | 108 |

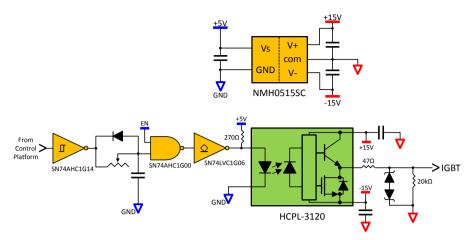

| 7.3.2 Gate drive circuits                                         | 108 |

| 7.3.3 Dead-time implementation                                    | 108 |

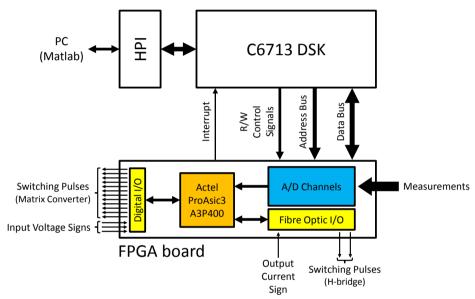

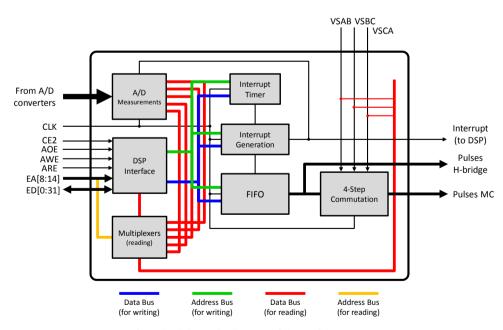

| 7.4 Control platform                                              | 109 |

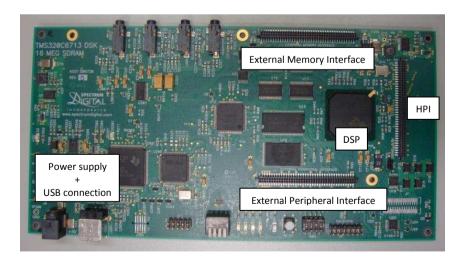

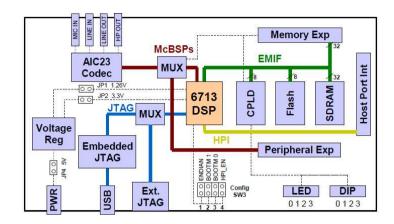

| 7.4.1 C6713 DSK board                                             | 109 |

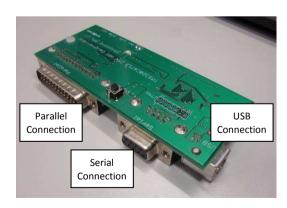

| 7.4.2 HPI card                                                    | 111 |

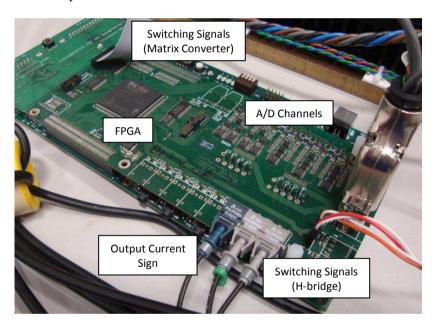

| 7.4.3 FPGA board                                                  | 112 |

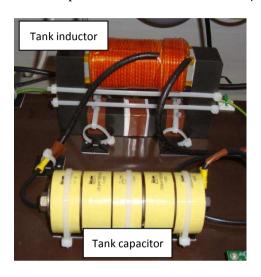

| 7.5 Resonant tank                                    |

|------------------------------------------------------|

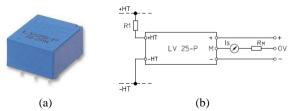

| 7.6 Voltage and current measurements                 |

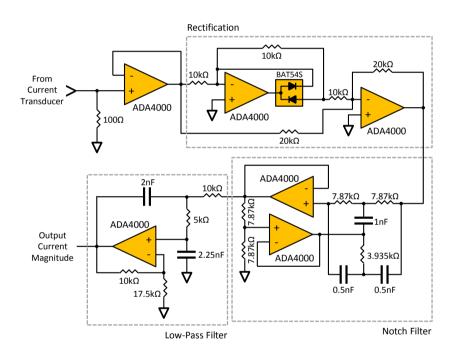

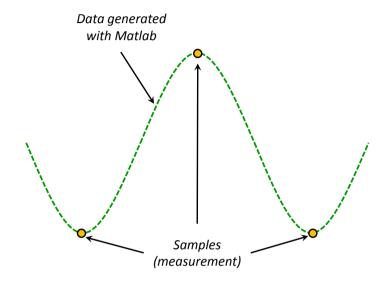

| 7.6.1 Output current magnitude measurement           |

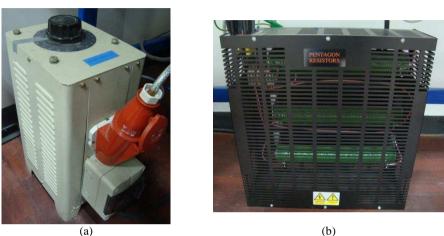

| 7.7 Autotransformer and load                         |

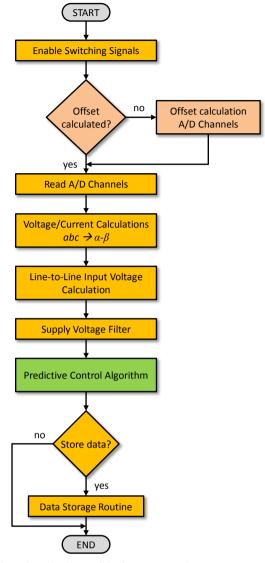

| 7.8 Control program                                  |

| 7.8.1 Initialisation                                 |

| 7.8.2 Interrupt routine                              |

| 7.8.2.1 A/D channels offset calculation              |

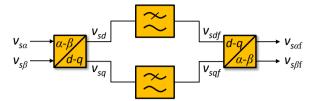

| 7.8.2.2 Supply voltage filtering                     |

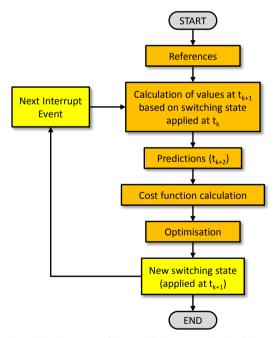

| 7.8.2.3 Predictive control algorithm                 |

| 7.8.2.4 Data storage                                 |

| 7.9 FPGA program119                                  |

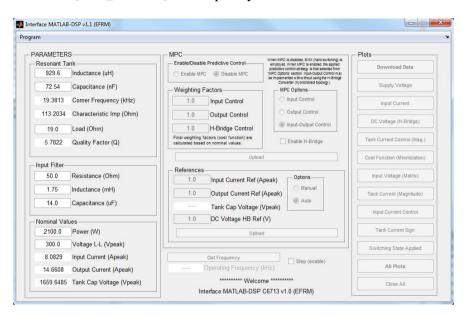

| 7.10 MATLAB Interface                                |

| 7.11 Summary                                         |

| CHAPTER 8                                            |

| Experimental Results                                 |

| 8.1 Introduction                                     |

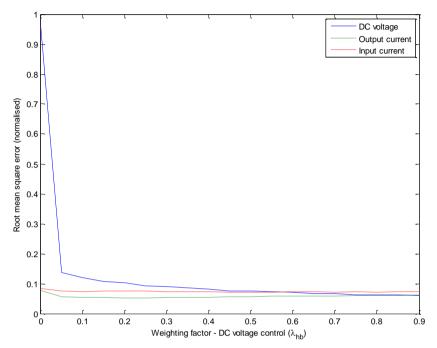

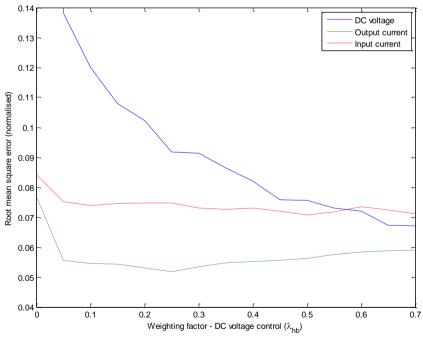

| 8.2 Selection of the weighting factor $\lambda_{hb}$ |

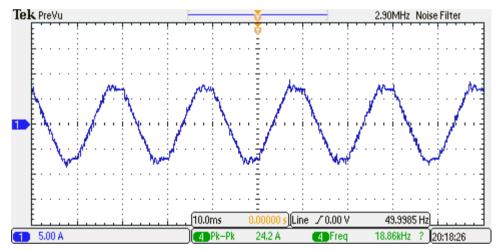

| 8.3 Experimental results at nominal output current   |

| 8.4 Control responses under step change references   |

| 8.5 Effects of the converter overmodulation          |

| 8.6 Results without voltage compensation             |

| 8.7 Power losses and efficiency estimations          |

| 8.8 Summary                                          |

| CHAPTER 9                                            |

| Conclusions                                          |

| 9.1 Further work                                     |

| 9.2 Published papers                                 |

| APPENDIX A                                           |

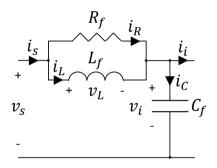

| Input Filter Model 145                               |

# APPENDIX B

| Resonant Tank Model                                                                                | 148 |

|----------------------------------------------------------------------------------------------------|-----|

| REFERENCES                                                                                         | 150 |

| List of Figures                                                                                    |     |

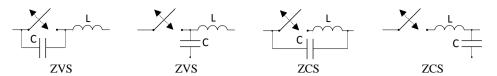

| Fig. 2.1 Resonant switches                                                                         | 6   |

| Fig. 2.2 Buck converter topologies                                                                 |     |

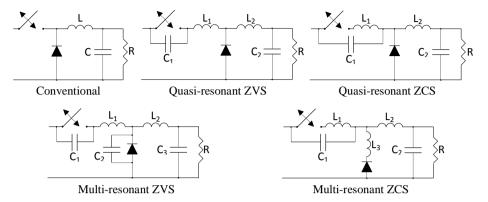

| Fig. 2.3 Resonant dc-link inverter                                                                 |     |

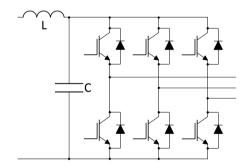

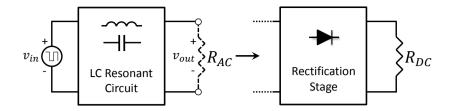

| Fig. 2.4 Diagram of a load resonant dc-dc converter                                                |     |

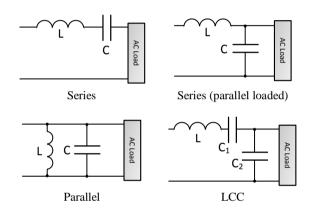

| Fig. 2.5 Resonant tank topologies                                                                  |     |

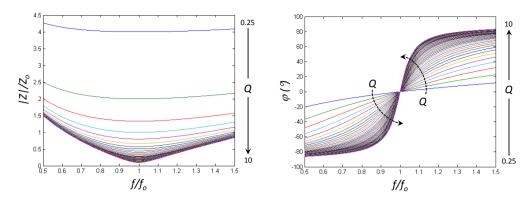

| Fig. 2.6 Magnitude and angle of the total impedance of a series resonant circuit                   | 10  |

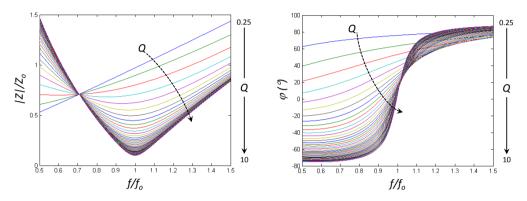

| Fig. 2.7 Magnitude and angle of the total impedance of a series (parallel loaded) resonant circuit | 10  |

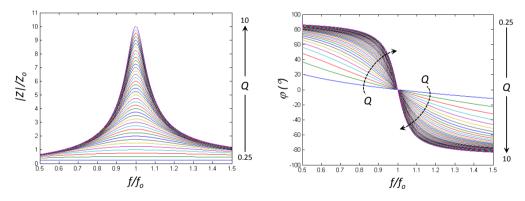

| Fig. 2.8 Magnitude and angle of the total impedance of a parallel resonant circuit                 |     |

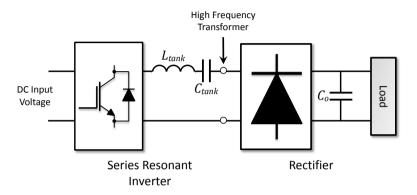

| Fig. 2.9 Schematic diagram of the topology of a series resonant converter                          | 11  |

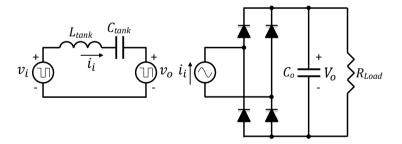

| Fig. 2.10 Equivalent circuit of a series resonant converter                                        | 11  |

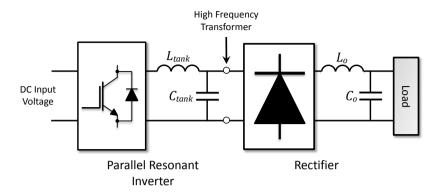

| Fig. 2.11 Schematic diagram of the topology of a parallel resonant converter                       | 12  |

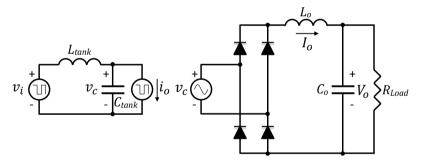

| Fig. 2.12 Equivalent circuit of a parallel resonant converter                                      |     |

| Fig. 2.13 Equivalent ac load                                                                       |     |

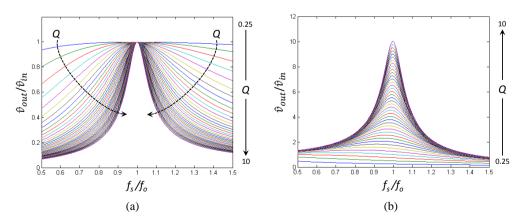

| Fig. 2.14 Input/output voltage relationship                                                        | 13  |

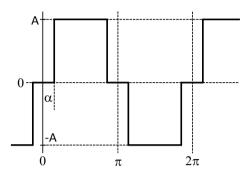

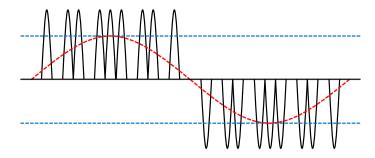

| Fig. 2.15 Quasi-square wave signal                                                                 | 14  |

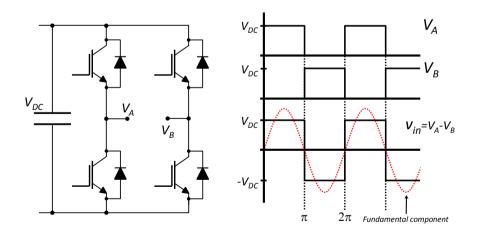

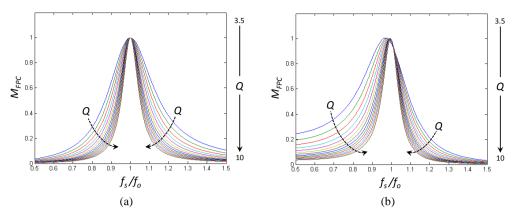

| Fig. 2.16 Modulation index for frequency control                                                   | 15  |

| Fig. 2.17 Voltage applied to the resonant tank by employing frequency control                      |     |

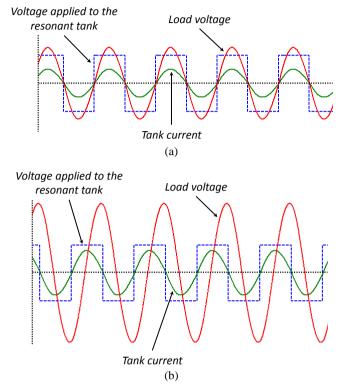

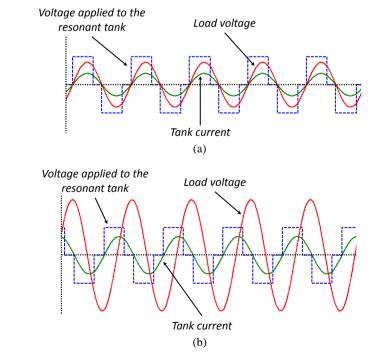

| Fig. 2.18 Waveforms using frequency control                                                        | 16  |

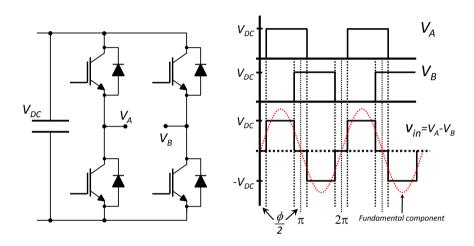

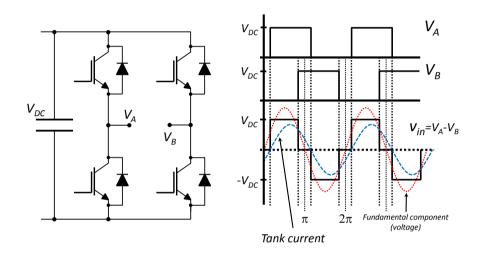

| Fig. 2.19 Voltage applied to the resonant tank by using phase control                              | 17  |

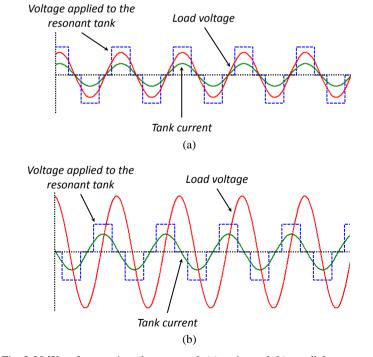

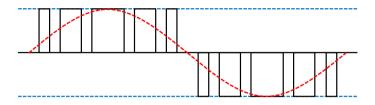

| Fig. 2.20 Waveforms using phase control                                                            | 17  |

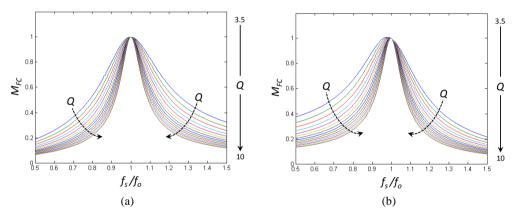

| Fig. 2.21 Modulation index for frequency-phase control                                             | 19  |

| Fig. 2.22 Voltage applied to the resonant tank by using frequency-phase control                    | 19  |

| Fig. 2.23 Waveforms using frequency-phase control                                                  | 19  |

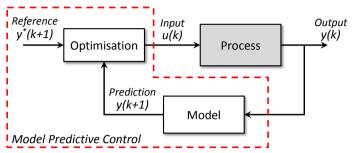

| Fig. 3.1 Scheme for model predictive control ( $N_p=N_c=1$ )                                       | 22  |

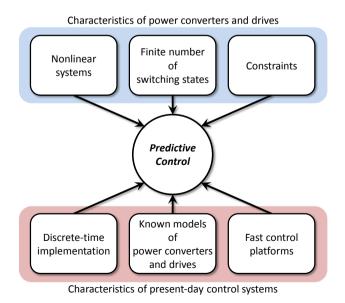

| Fig. 3.2 Characteristics of power electronic systems which make MPC a suitable control option      | 22  |

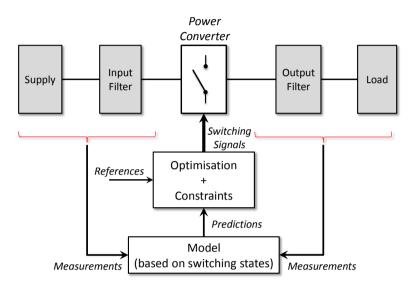

| Fig. 3.3 Scheme of FCS-MPC for a power electronic system                                           | 26  |

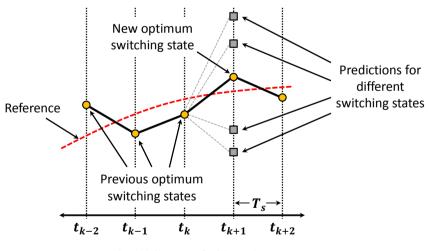

| Fig. 3.4 Concept of FCS-MPC                                                                        | 26  |

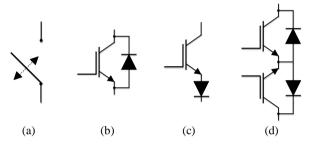

| Fig. 3.5 Some power switches using IGBTs                                                           | 27  |

| Fig. 3.6 Three-phase inverter with ideal switches                                                  | 28  |

| Fig. 3.7 Three-phase inverter                                                                      | 28  |

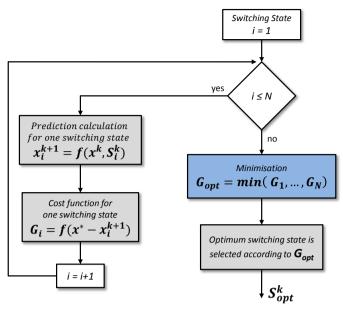

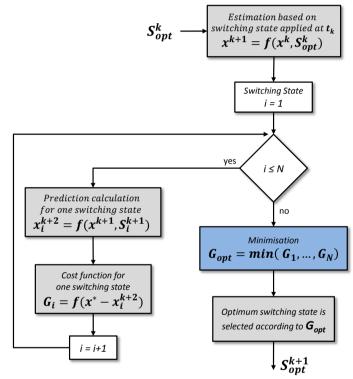

| Fig. 3.8 Optimisation process                                                                      | 31  |

| Fig. 3.9 Ideal implementation of FCS-MPC                                                           |     |

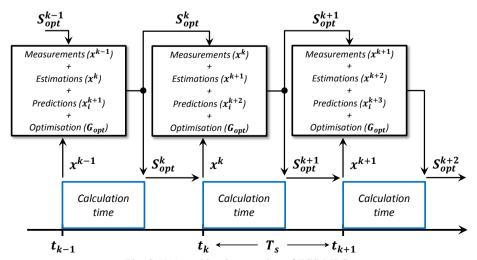

| Fig. 3.10 Optimisation process with calculation delay                                              | 22  |

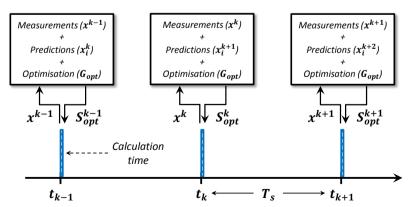

| Fig. 3.11 Actual implementation of FCS-MPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

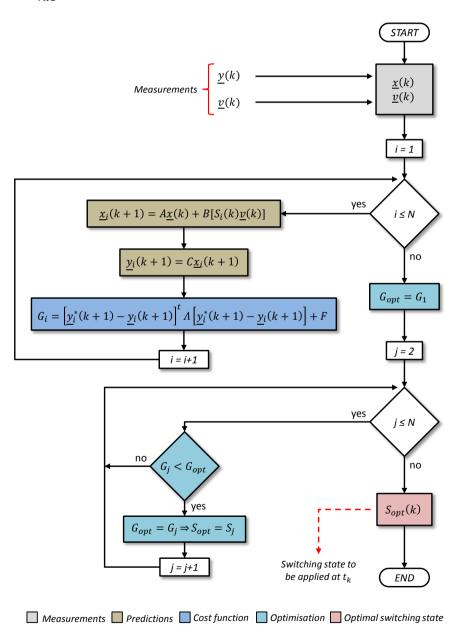

| Fig. 3.12 Flowchart of FCS-MPC without delay compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34  |

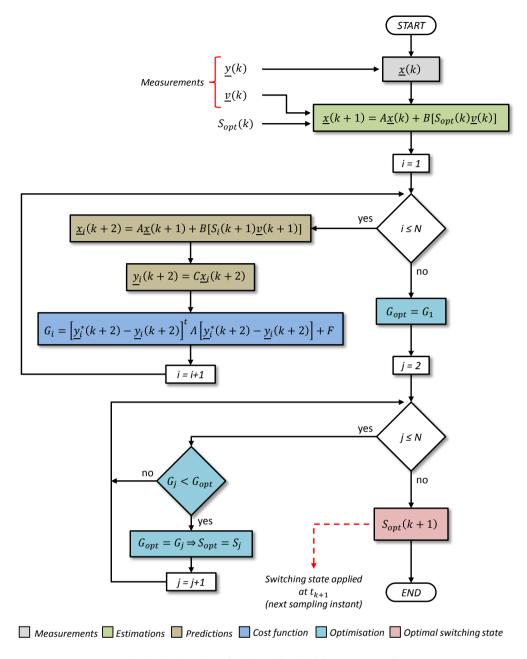

| Fig. 3.13 Flowchart of FCS-MPC with delay compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

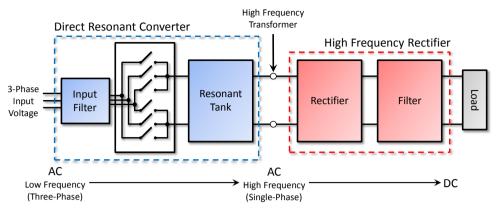

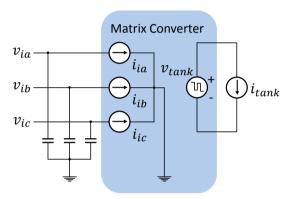

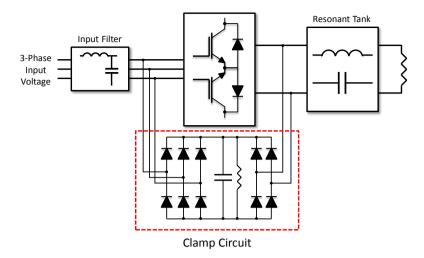

| Fig. 4.1 Diagram of a high voltage DC power supply based on a direct resonant converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37  |

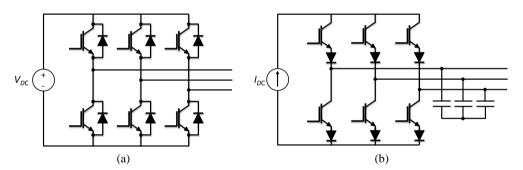

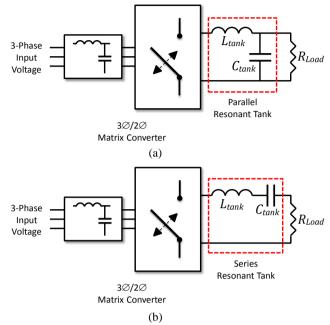

| Fig. 4.2 Scheme of a DRC with resistive load: (a) DPRC and (b) DSRC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

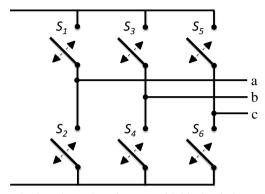

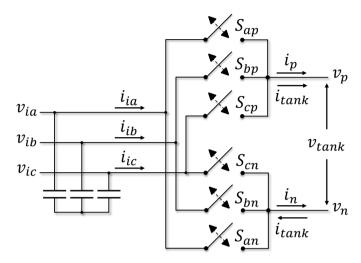

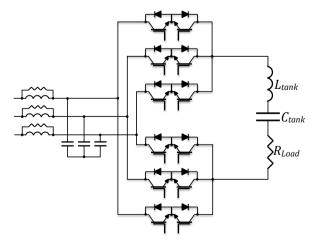

| Fig. 4.3 Three-phase to single-phase matrix converter with ideal switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

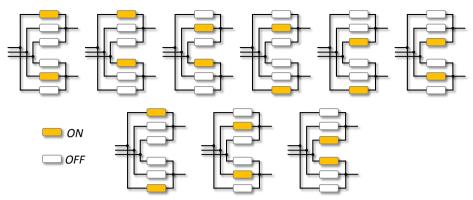

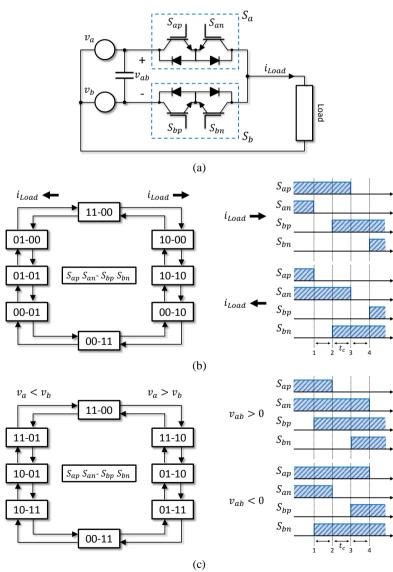

| Fig. 4.4 Switching states for a DRC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Fig. 4.5 Switching model of a DRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

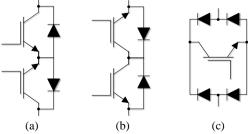

| Fig. 4.6 Bidirectional switch configurations using IGBTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| Fig. 4.7 Four-step commutation strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

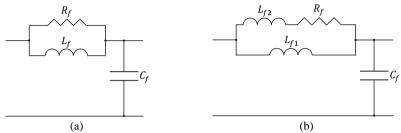

| Fig. 4.8 Input filter configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Fig. 4.9 Clamp circuit for a DRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

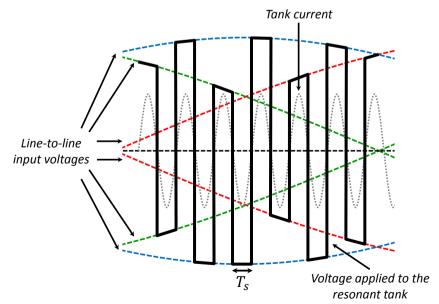

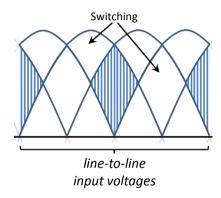

| Fig. 4.10 Voltage applied to the resonant tank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

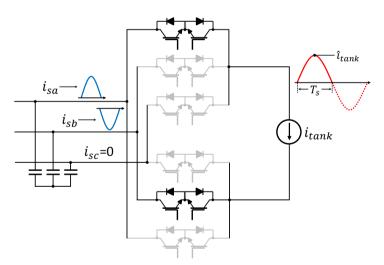

| Fig. 4.11 Input converter current for a switching state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

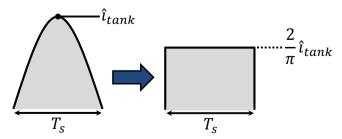

| Fig. 4.12 Equivalent current pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Fig. 4.14 Fig. 4.14 Fig. 1.14 Fig. 1 |     |

| Fig. 4.14 Equivalent input converter current (average)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

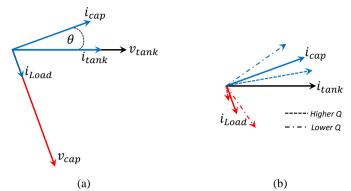

| Fig. 4.15 Phasor diagram for a SRPL tank under ZCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

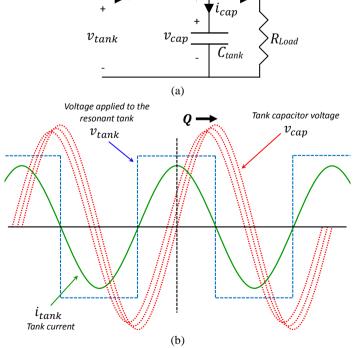

| Fig. 4.16 SRPL tank under ZCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

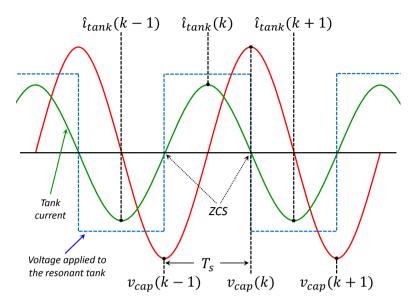

| Fig. 4.17 Series resonant tank under ZCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

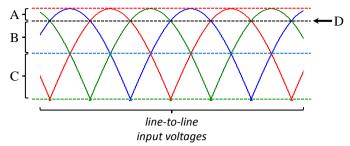

| Fig. 4.18 Voltage levels considered for output converter voltage analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

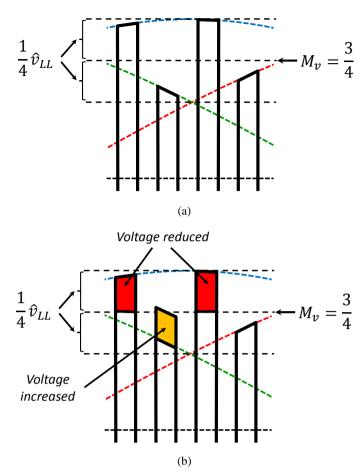

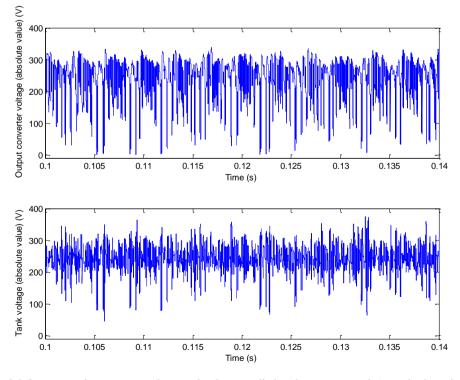

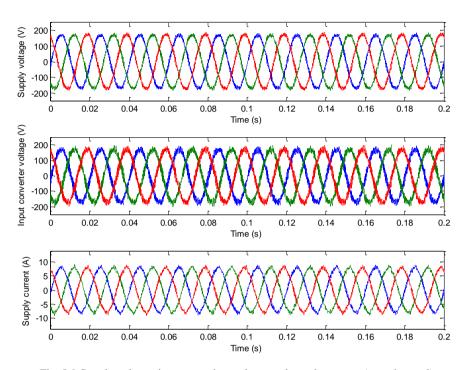

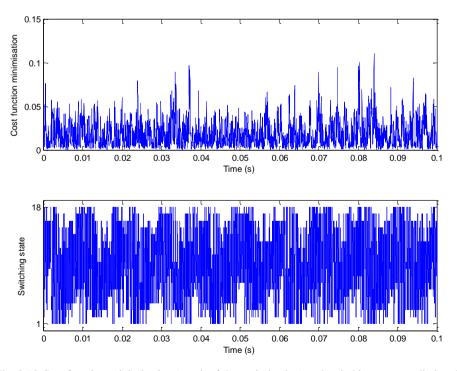

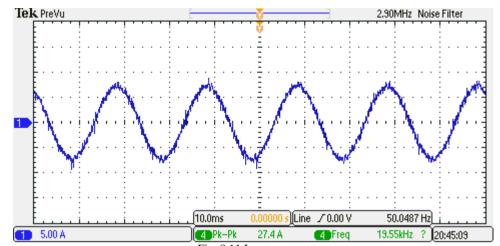

| Fig. 4.19 Output converter voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

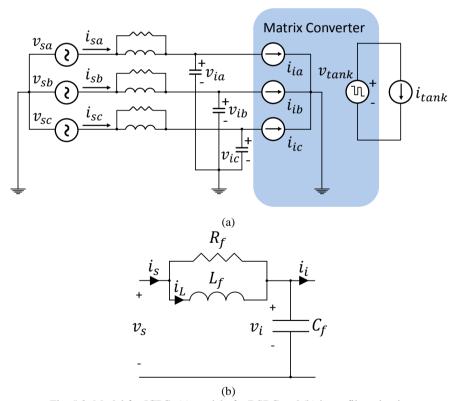

| Fig. 5.1 Direct series resonant converter with resistive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Fig. 5.2 Model for ICPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

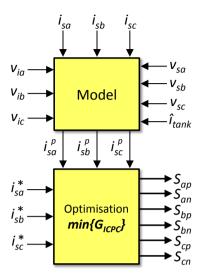

| Fig. 5.3 Scheme of ICPC strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

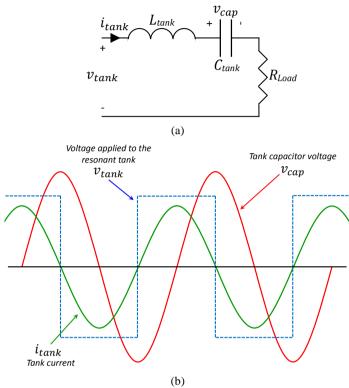

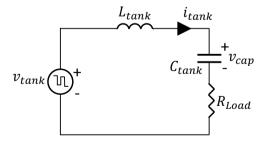

| Fig. 5.4 Series resonant tank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |