Yaqub, Imran (2015) Investigation into stable failure to short circuit in IGBT power modules. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/30305/1/PhD%20Thesis%20Sept%202015%20by%20Imran%20Yaqub%20HQ.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# INVESTIGATION INTO STABLE FAILURE TO SHORT CIRCUIT IN IGBT POWER MODULES

BY Imran YAQUB

Supervisor: Prof. C. M. Johnson

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

September 2015

## **A**BSTRACT

This doctoral thesis investigates modes of failure of the IGBT power module and how these modes can be coerced from an open circuit failure mode (OCFM) to a stable short circuit failure mode (SCFM) by using different interconnect technologies and material systems. SCFM is of great importance for a number of applications where IGBT power modules are connected in series string e.g. high voltage modular multi-level converters (M<sup>2</sup>LC) where one module failing to an OCFM can shut down the whole converter.

The failure modes of IGBT samples based on wirebond, flexible PCB, sandwich and press pack structured interconnect technologies have been investigated. Destructive Type-II failure test were performed which concluded that the SCFM is dependent on the energy level dissipating in the power module and the interconnect technology. The higher thermal mass and stronger mechanical constraint of the interconnect enables module to withstand higher energy dissipation.

The cross-sections of the tested samples have been characterised with the scanning electron microscope and three dimensional X-ray computed tomography imaging. It was observed that the networked conductive phases within the solidification structure and the Sn-3.5Ag filled in cracks of the residual Si IGBT are responsible for low resistance conduction paths. The best networked conductive phase with lowest electrical resistance and high stability was offered by Ag if used as an intermediate interconnect material on emitter side of an IGBT.

To offer a stable SCFM, a module has to be custom designed for a particular application. Hence for the applications which demand a stable SCFM, the IGBT module design becomes an integrated part of the complete power electronics system design.

"To my loving parents Mr. M. Yaqub & Mrs. Razia Sultana"

"To my beloved wife Ayesha and my daughter Zara"

## **ACKNOWLEDGEMENTS**

First and foremost I would like to offer my utmost respect and thanks to my supervisor Prof. C. M. Johnson for his guidance, encouragement and support during the research which led to this thesis.

I would also wish to thank my co supervisors, Dr. Jianfeng Li, Dr. Lee Empringham, Dr. Lilo Lilianna and Dr. Paul Evans and my colleagues Dr. Pearl Agyakwa, Dr. Martin Corfield, Dr. Li Yang, Dr. Bassem Mouawad, Mr. Amir Eleffendi and Mrs. Elaheh Arjmand for their kind help and support throughout the work.

I would also like to thank my current employer and sponsor, Dynex Semiconductor Ltd. for their financial support of this project. In particular Mr. Bill McGhie, Mr. Andy Dunlop, Mr. Richard Scott, Mr. Tony Gough and Mr. Adrian Taylor who have always supported me of the work carried out in this thesis.

Finally, I would like to thank my sister Mrs. Komal Yaseen and my brother Dr. Zeeshan Yaqub for their encouragement throughout my PhD

# **TABLE OF CONTENTS**

| A) | BSTR  | ACT  | I                                     |

|----|-------|------|---------------------------------------|

| A  | CKNC  | WLI  | EDGEMENTSIII                          |

| Lı | ST OF | FIC  | GURESIX                               |

| Lı | ST OF | F TA | BLESXV                                |

| 1  | In    | ΓRΟΙ | DUCTION                               |

|    | 1.1   | Mo   | tivation1                             |

|    | 1.2   | Cor  | nventional Packaging and its Problems |

|    | 1.3   | Pro  | blems addressed in this Thesis        |

|    | 1.4   | Res  | earch Contributions                   |

|    | 1.5   | App  | plication of the Project9             |

|    | 1.5   | .1   | Modular Multi-level Converters        |

|    | 1.5   | .2   | High Speed switching Devices          |

|    | 1.5   | .3   | Explosion Proof Packaging             |

|    | 1.5   | .4   | High Reliability11                    |

|    | 1.5   | .5   | New Manufacturing Approach            |

|    | 1.5   | .6   | Double Sided Cooling                  |

|    | 1.6   | Ove  | erview of the Thesis                  |

| 2  | Li    | ΓERA | ATURE REVIEW                          |

|    | 2.1   | Ele  | ctrical Failure modes of an IGBT      |

|    | 2.1   | .1   | Open circuit failure                  |

|    | 2.1   | 2    | Short Circuit Failure                 |

| 2.2  | Inte       | erconnect Technologies                                     | 20 |

|------|------------|------------------------------------------------------------|----|

| 2.   | 2.1        | Wirebond                                                   | 20 |

| 2.   | 2.2        | Ribbon Bonding                                             | 21 |

| 2.   | 2.3        | Embedded Chip Technology                                   | 22 |

| 2.   | 2.4        | Metal Post-Interconnected Parallel-Plate Structure         | 23 |

| 2.   | 2.5        | Dimple Array Interconnect                                  | 25 |

| 2.   | 2.6        | Planar Interconnect Technology                             | 26 |

| 2.   | 2.7        | Wirebonded Module with Pressure Contact Technology (SKiiP) | 29 |

| 2.   | 2.8        | Flexible PCB based Packaging Technology (SKiN)             | 30 |

| 2.3  | IGI        | BT Modules Favouring Failure to Short Circuit              | 32 |

| 2.   | 2.1 P      | ress Pack IGBT module                                      | 32 |

| 2    | 3.1        | StakPak IGBT module                                        | 35 |

| 2.4  | Sui        | mmary                                                      | 39 |

| 3 F. | AILU       | RE MODES OF WIREBONDED IGBT TEST VEHICLE                   | 41 |

| 3.1  | Intı       | roduction                                                  | 41 |

| 3.2  | Exp        | periment                                                   | 42 |

| 3.   | 2.1        | Sample Preparation                                         | 42 |

| 3.   | 2.2        | Setting up Test Rig                                        | 44 |

| 3.   | 2.3        | Principal of Testing                                       | 46 |

| 3.3  | Exp        | perimental Results                                         | 48 |

| 3    | <b>.</b> . | Electrical Testing                                         | 48 |

| J.,  | 3.1        | $\boldsymbol{c}$                                           |    |

|      | 3.1        | Microstructural Observation                                |    |

|      | 3.2        |                                                            | 54 |

| 4 | FA    | ILU  | RE MODES OF FLEXIBLE PCB INTERCONNECTED IGB'.              | I TEST |

|---|-------|------|------------------------------------------------------------|--------|

| V | EHICI | LES. |                                                            | 60     |

|   | 4.1   | Int  | roduction                                                  | 60     |

|   | 4.2   | Ex   | periment                                                   | 60     |

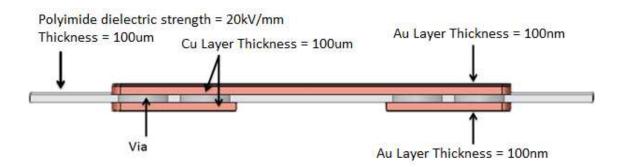

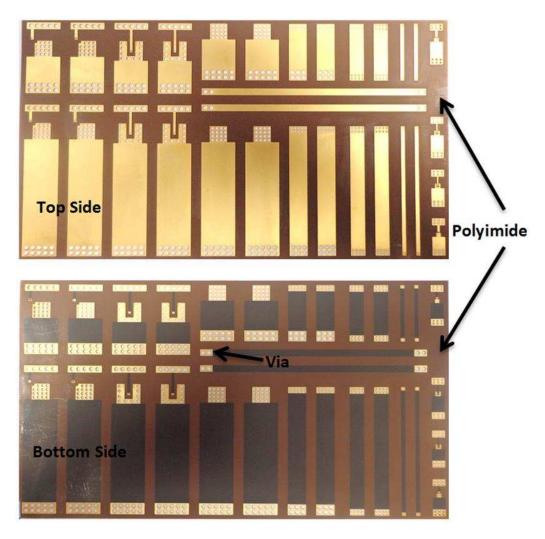

|   | 4.2   | .1   | Flexible PCB                                               | 60     |

|   | 4.2   | .2   | Sample Preparation                                         | 62     |

|   | 4.2   | .3   | Test Procedure                                             | 65     |

|   | 4.3   | Ex   | perimental Results                                         | 65     |

|   | 4.3   | .1   | Electrical Testing                                         | 65     |

|   | 4.3   | .2   | Microstructural Observation                                | 67     |

|   | 4.4   | Dis  | scussion                                                   | 71     |

|   | 4.5   | Sui  | mmary                                                      | 73     |

| 5 | FA    | .ILU | RE MODES OF SANDWICH STRUCTURE IGBT TEST VEHICL            | ES 74  |

|   | 5.1   | Int  | roduction                                                  | 74     |

|   | 5.2   | Ex   | periment                                                   | 74     |

|   | 5.2   | .1   | Sample Preparation                                         | 74     |

|   | 5.2   | .2   | Test Procedure                                             | 75     |

|   | 5.3   | Ex   | perimental Results                                         | 75     |

|   | 5.3   | .1   | Electrical Testing                                         | 75     |

|   | 5.3   | .2   | 3D Microstructural Observations                            | 76     |

|   | 5.4   | Pha  | ase change of metals and its correlation with input energy | 78     |

|   | 5.5   | Sta  | bility of SCFM                                             | 86     |

|   | 5.6   | Dis  | scussion                                                   | 86     |

|   | 5.7   | Siii | mmary                                                      | 87     |

| 6 | F   | FAILU | JRE MODES OF PRESS PACK IGBT TEST VEHICLE          | 89  |

|---|-----|-------|----------------------------------------------------|-----|

|   | 6.1 | In    | troduction                                         | 89  |

|   | 6.2 | E     | xperiment                                          | 89  |

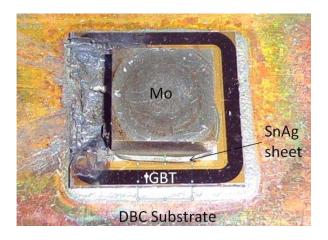

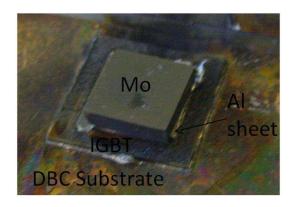

|   | 6   | 5.2.1 | Test Vehicle Preparation                           | 89  |

|   | 6   | 5.2.2 | Test Procedure                                     | 93  |

|   | 6.3 | E     | xperimental Results                                | 94  |

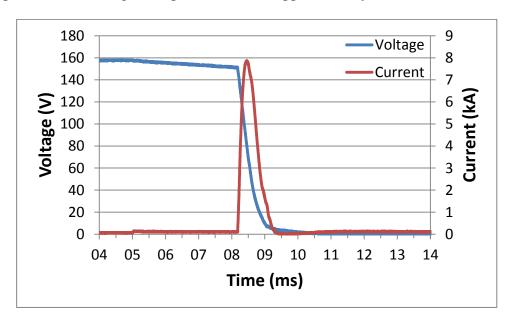

|   | 6   | 5.3.1 | Electrical Testing                                 | 94  |

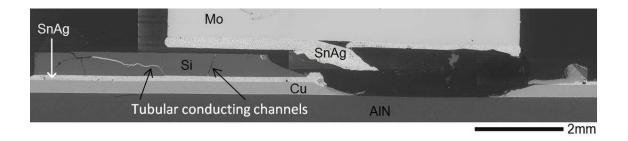

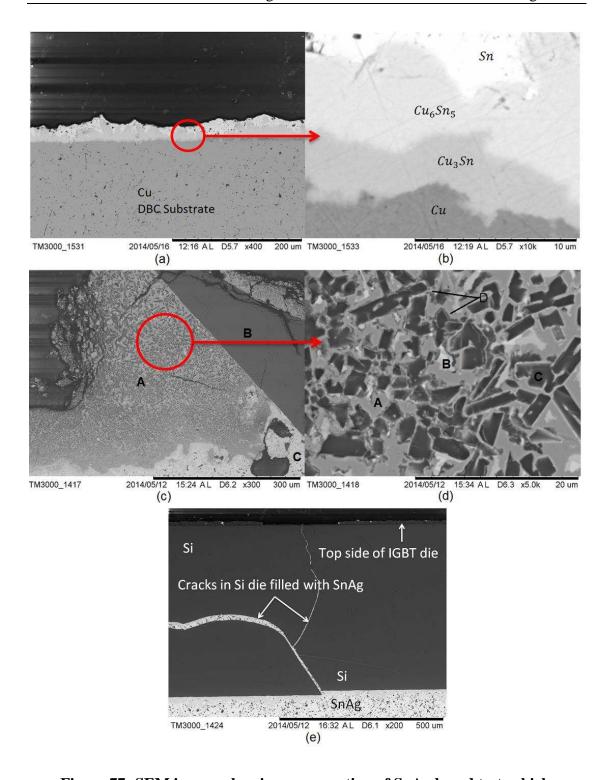

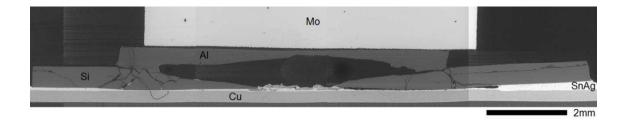

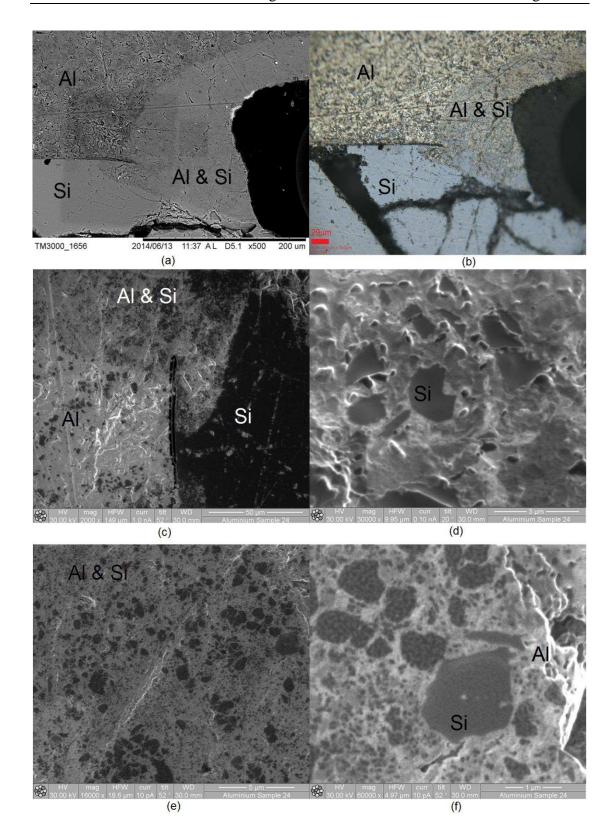

|   | 6   | 5.3.2 | Microstructural Observations                       | 95  |

|   | 6.4 | D     | iscussion                                          | 99  |

|   | 6.5 | Sı    | ımmary                                             | 100 |

| 7 | I   | NVE   | STIGATION OF SUITABLE MATERIALS FOR ACHIEVING SCFM | 101 |

|   | 7.1 | In    | troduction                                         | 101 |

|   | 7.2 | E     | xperiment                                          | 101 |

|   | 7   | 7.2.1 | Test Vehicle preparation                           | 101 |

|   | 7   | 7.2.2 | Test Procedure                                     | 102 |

|   | 7   | 7.2.3 | Sample Cross-section & Analysis                    | 103 |

|   | 7.3 | Ez    | sperimental Results                                | 104 |

|   | 7   | 7.3.1 | Cu as intermediate material                        | 104 |

|   | 7   | 7.3.2 | SnAg as intermediate material                      | 109 |

|   | 7   | 7.3.3 | Al as intermediate material                        | 114 |

|   | 7   | 7.3.4 | Ag as intermediate material                        | 118 |

|   | 7.4 | D     | iscussion                                          | 121 |

|   | 7   | 7.4.1 | Comparison of the Electrical Test Results          | 121 |

|   | 7   | 7.4.2 | Comparison of Material Properties                  | 125 |

| 7.4   | 4.3 Comparison of Microstructural Observations | 126 |

|-------|------------------------------------------------|-----|

| 7.5   | Effect of Thickness                            | 132 |

| 7.6   | Summary                                        | 135 |

| 8 C   | ONCLUSION AND FUTURE WORK                      | 136 |

| 8.1   | Conclusion.                                    | 136 |

| 8.2   | Future Work                                    | 140 |

| REFER | ENCES                                          | 141 |

# **LIST OF FIGURES**

| Figure 1: Modular multi-level converter [1]2                                           |

|----------------------------------------------------------------------------------------|

| Figure 2: IGBT power module4                                                           |

| Figure 3: Cross-section of conventional power IGBT module                              |

| Figure 4: IGBT modules (left) from 80's, (right) latest IGBT module6                   |

| Figure 5: The equivalent circuit of IGBT [17]16                                        |

| Figure 6: Test circuit to perform short circuit [21]                                   |

| Figure 7: Idealised voltage and current waveforms of (a) Type-I and (b) Type-II test.  |

|                                                                                        |

| Figure 8: Wirebonds interconnection in IGBT module                                     |

| Figure 9: Ribbon Bonding[28]21                                                         |

| Figure 10: Embedded Chip Module [30]22                                                 |

| Figure 11: Metal Post Interconnect Parallel Plate Structure module (a) Photograph (b)  |

| cross-section [33]                                                                     |

| Figure 12: Integrated power electronic module [35] (a) module, (b) cross-section, (c)  |

| power module, (d) cross-section of power module24                                      |

| Figure 13: Dimple array interconnect technology [37] (a) cross-section, (b) structure, |

| (c) module26                                                                           |

| Figure 14: Cross-section of Power Overlay Technology [39]27                            |

| Figure 15: (a) SiPLIT module by Siemens[42], (b) Cross-section of SiPLIT               |

| module[41]28                                                                           |

| Figure 16: SiPLIT module by Siemens [41], (a) to (g) shows manufacturing process       |

| flow29                                                                                 |

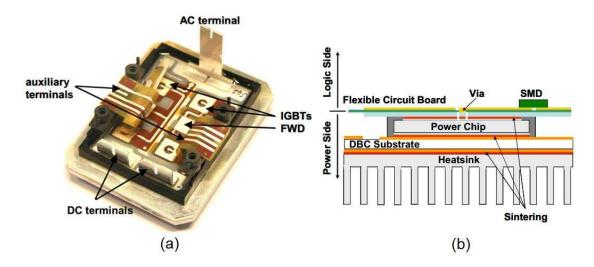

| Figure 17: Semikron SKiiP 4 [43], (a) Module, (b) Cross-section                        |

| Figure 18: SKiN by Semikron[46](a) Module, (b) Cross-section                           |

| Figure 19: Press-Pack IGBT introduced by IXYS UK Westcode Ltd [47, 52] 34              |

|----------------------------------------------------------------------------------------|

| Figure 20: StakPak IGBT manufactured by ABB [55]                                       |

| Figure 21: (a) Contact system for one single chip, (b) Direct pressure contact on gate |

| [55]                                                                                   |

| Figure 22: (a) shows the full IGBT module (b) Simplified wirebonded IGBT test          |

| vehicle41                                                                              |

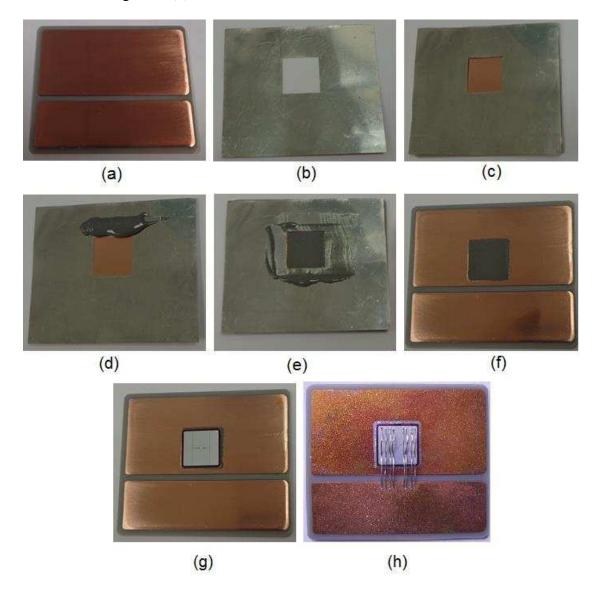

| Figure 23: Sample preparation (a) two island DBC substrate (b) Aluminium mask (c)      |

| Mask placed on the substrate (d) Solder paste applied to the mask (e) Solder paste     |

| spread using squeegee (f) mask removed from the substrate (g) IGBT placed over the     |

| solder paste (h) finished test vehicle after passing through reflow oven and           |

| wirebonding process                                                                    |

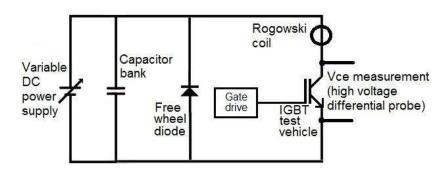

| Figure 24: Schematic diagram of test rig                                               |

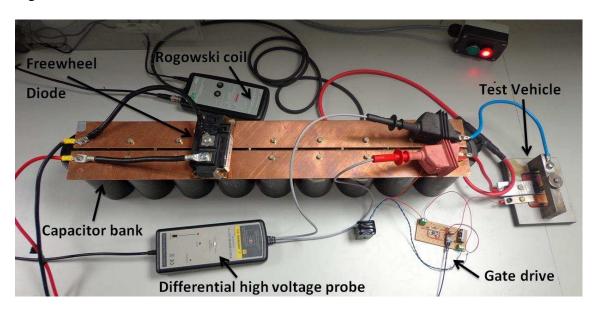

| Figure 25: The Test Rig                                                                |

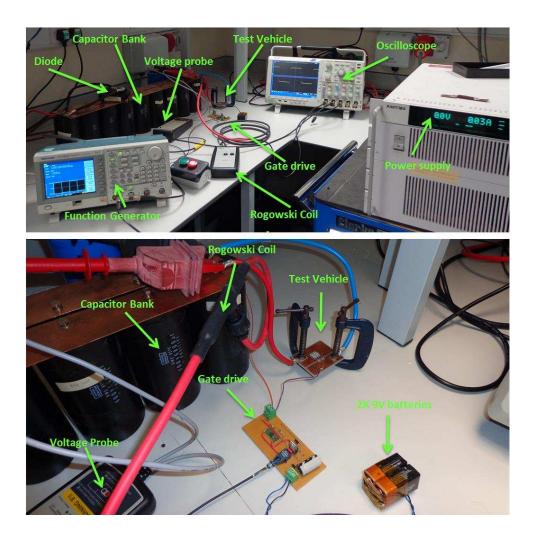

| Figure 26: Gate Drive Unit                                                             |

| Figure 27: Voltage and current waveforms of wirebond based test vehicle (a) achieved   |

| OCFM at 500J (b) achieved SCFM at 62.5 J                                               |

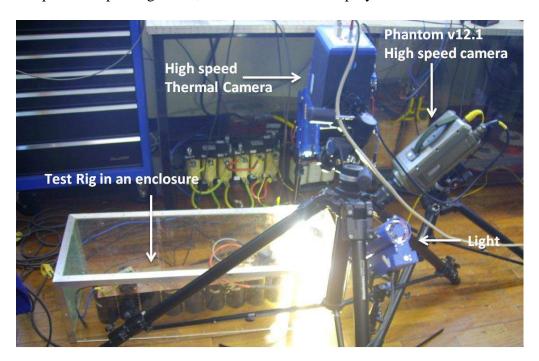

| Figure 28: Setup for high speed camera                                                 |

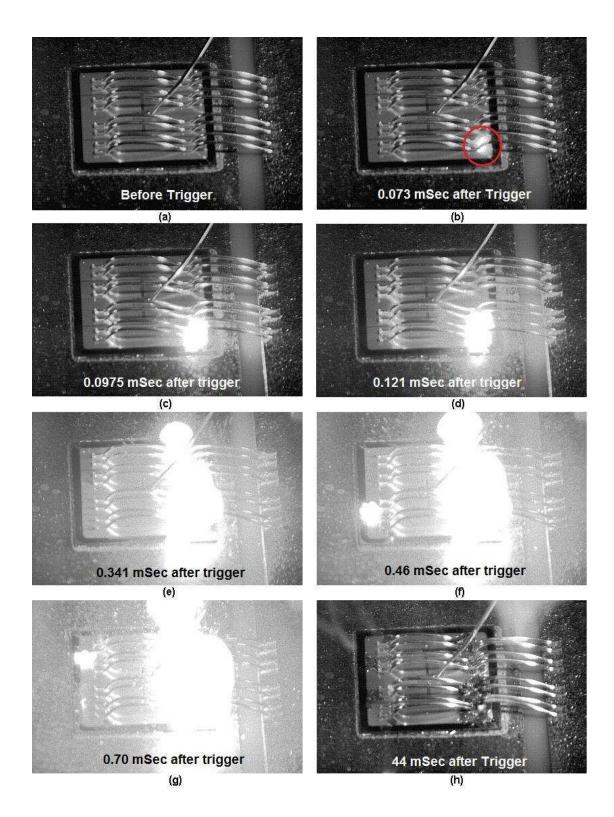

| Figure 29: High speed imaging of exploding IGBT die in a sequence from (a) to (h) 50   |

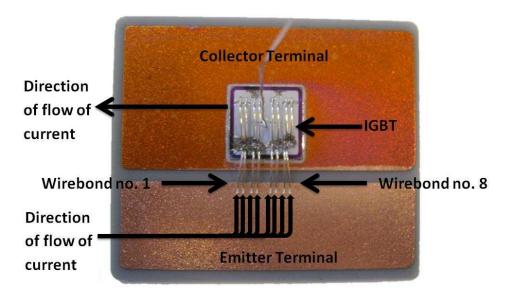

| Figure 30: Current path on DBC                                                         |

| Figure 31: Simplified model of wirebonded test vehicle                                 |

| Figure 32: Mesh plot along with faces where current signal is applied                  |

| Figure 33: Current density plot                                                        |

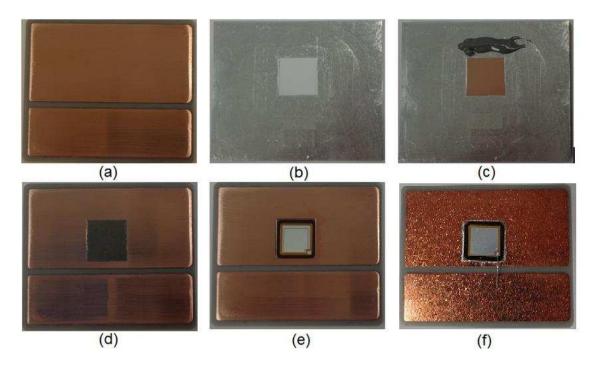

| Figure 34: Test vehicles (a) achieved OCFM at 500J (b) achieved SCFM at 62.5J 55       |

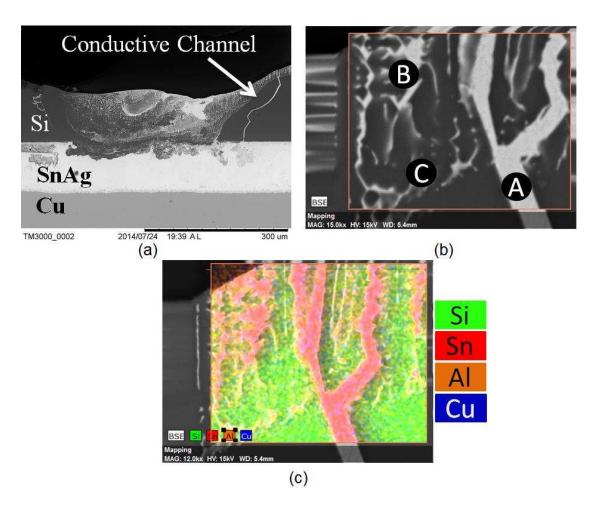

| Figure 35: SEM images of cross-section of the test vehicle which achieved OCFM (a)     |

| conductive channel, (b) EDX points and (c) EDX element map                             |

| Figure 36: SEM images of cross-section of the test vehicle which achieved SCFM (a)     |

|----------------------------------------------------------------------------------------|

| shows the conductive channel (b) shows location of EDX points A B & C (c) EDX          |

| element map                                                                            |

| Figure 37: Flexible PCB60                                                              |

| Figure 38: Flexible PCB for different type of devices                                  |

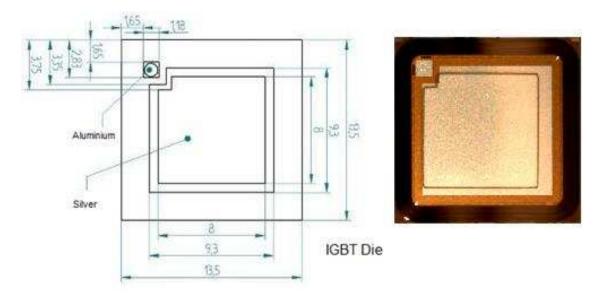

| Figure 39: Silver top corner gate IGBT die (used in chapter 4 and chapter 5)           |

| Figure 40: schematic diagram of the flexible PCB based test vehicle                    |

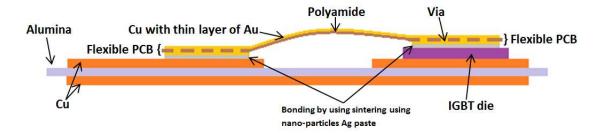

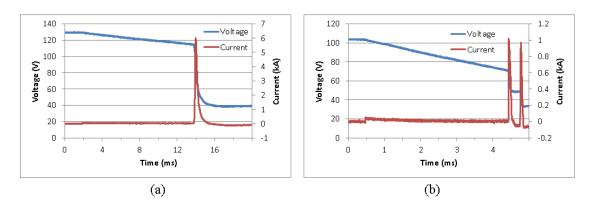

| Figure 41: Sample preparation (a) two island DBC substrate (b) Aluminium mask (c)      |

| Mask placed on the substrate with silver paste applied to the mask (d) silver paste    |

| spread using squeegee (e) mask removed from the substrate (f) Flexible PCB (g)         |

| IGBT placed over the silver paste (h) flexible PCB placed on the IGBT and substrate    |

| (i) Final test vehicle after sintering and wirebonding gate contact                    |

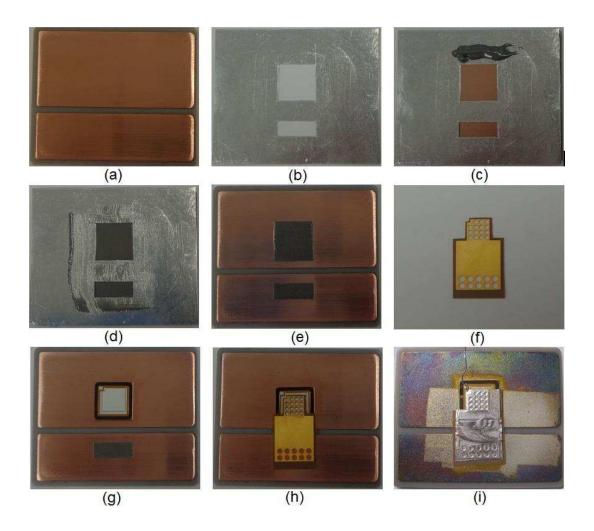

| Figure 42: Voltage and current waveforms of flexible PCB bases test vehicles (a)       |

| achieved OCFM at 500 J (b) achieved SCFM at 312.5 J                                    |

| Figure 43: Test vehicles (a) achieved OCFM at 500 J, (b) achieved SCFM at 312.5 J      |

| 67                                                                                     |

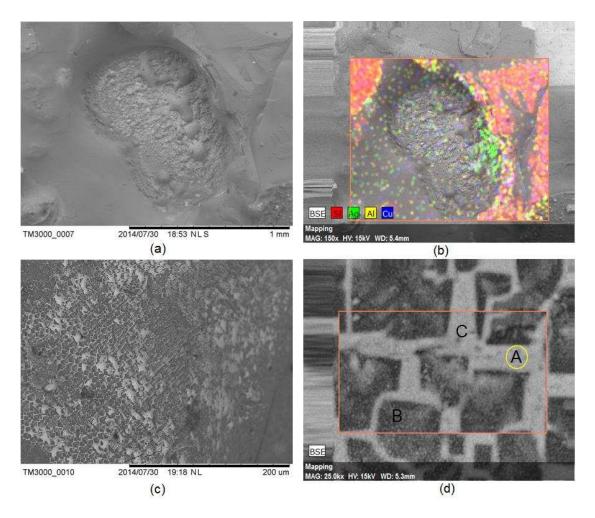

| Figure 44: SEM image of the surface of an IGBT failed to open circuit, (a) conductive  |

| crater, (b) EDX element map, (c) side wall of crater and (d) EDX points 68             |

| Figure 45: (a) Cross-section of test vehicle which achieved OCFM at 500 J, (b) EDX     |

| points                                                                                 |

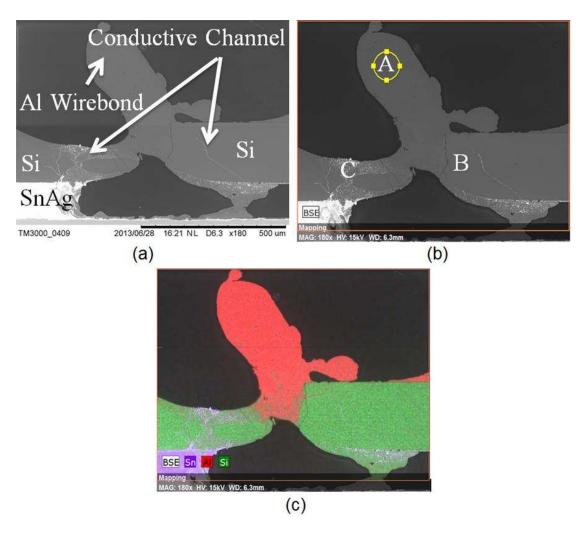

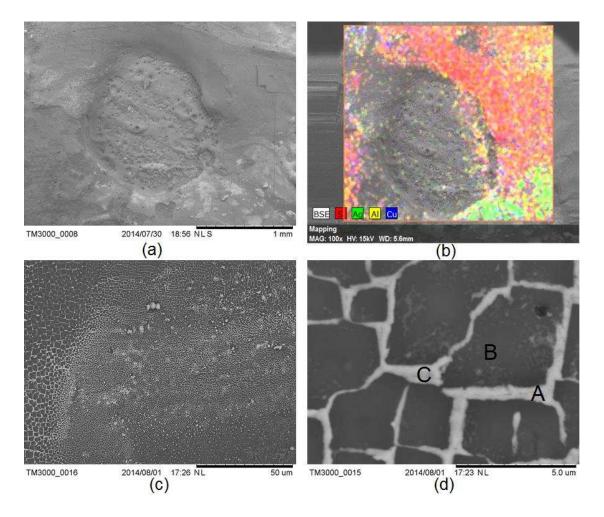

| Figure 46: SEM image of the surface of an IGBT failed to short circuit, (a) conductive |

| crater, (b) EDX element map, (c) side wall of crater and (d) EDX points70              |

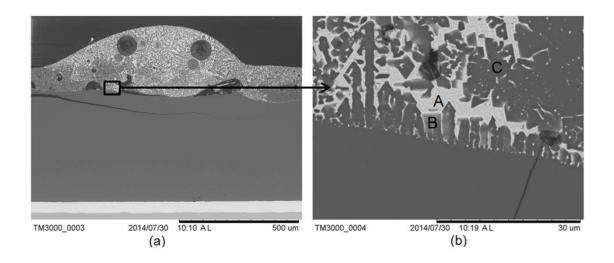

| Figure 47: SEM of the test vehicle which attained SCFM at 312.5 J (a) the cross-       |

| section showing crater (b) contact interface between Si die top and flexible PCB 71    |

| Figure 48: Schematic of sandwich test vehicle                                          |

| Figure 49: Voltage and current waveforms of sandwich structure based test vehicles     |

|----------------------------------------------------------------------------------------|

| (a) achieved SCFM at 750 J (b) achieved OCFM at 1500 J                                 |

| Figure 50: Test vehicle (a) achieved SCFM 750 J (b) achieved OCFM at 1500 J 77         |

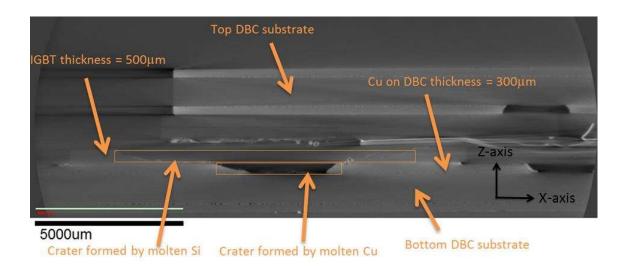

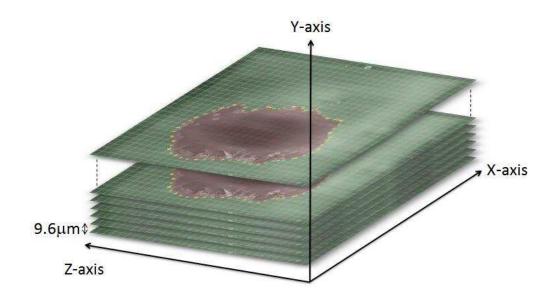

| Figure 51: Cross-sectional view taken from reconstructed 3D X-ray CT images of         |

| sample which failed to short circuit                                                   |

| Figure 52: (a) Current pulse (b) Energy                                                |

| Figure 53: Image in XZ plane showing the crater                                        |

| Figure 54 Images in XY plane showing crater area enclosed in yellow circle 80          |

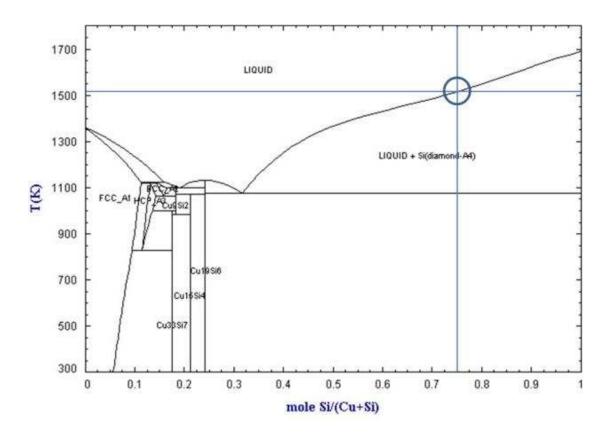

| Figure 55: Binary phase diagram of Cu-Si [61]                                          |

| Figure 56: The re-usable frame of the test vehicle                                     |

| Figure 57: Preparation of test sample (a) two island DBC substrate (b) Aluminium       |

| mask (c) Mask placed on the substrate with solder paste applied to the mask (d) Solder |

| paste spread using squeegee (e) IGBT placed over the solder paste (f) finished test    |

| vehicle after passing through reflow oven and wirebonding process91                    |

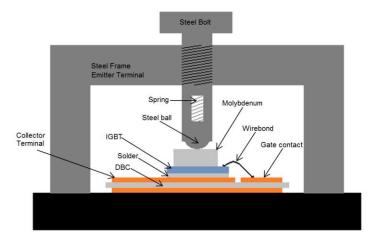

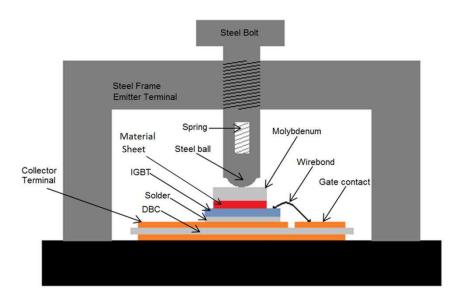

| Figure 58: Schematic diagram of press pack IGBT test vehicle                           |

| Figure 59: The complete test vehicle.                                                  |

| Figure 60: Test vehicle connected to test rig                                          |

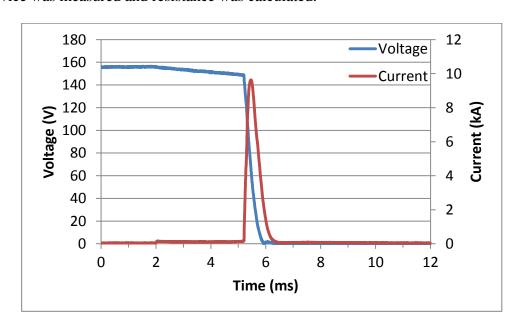

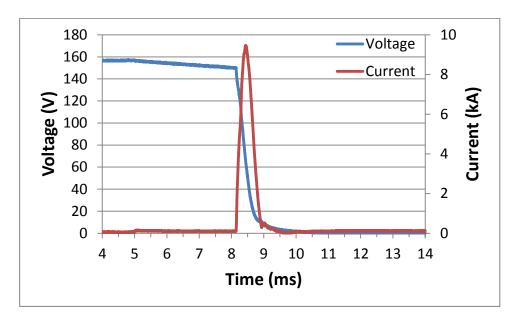

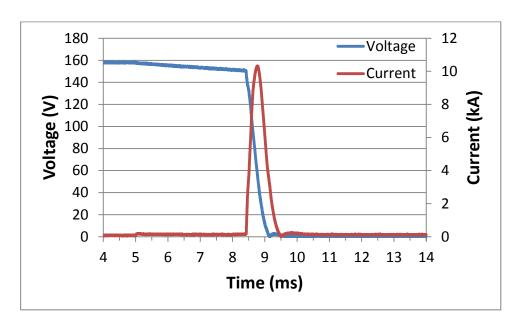

| Figure 61: Voltage and current waveforms of Mo based test sample exploded at 750 J     |

| 94                                                                                     |

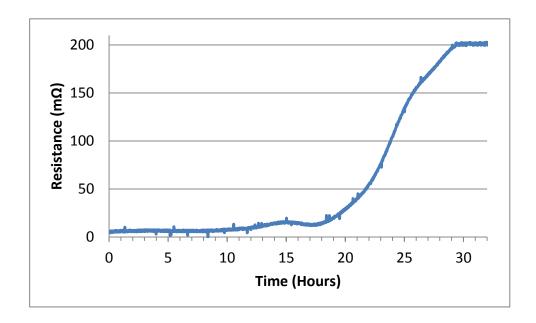

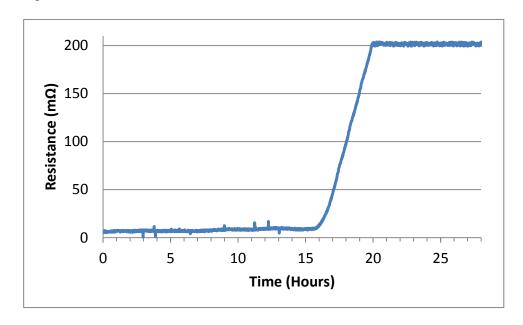

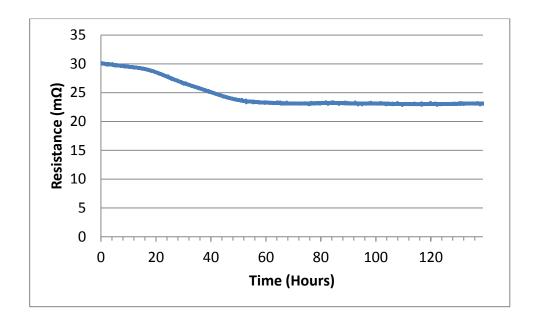

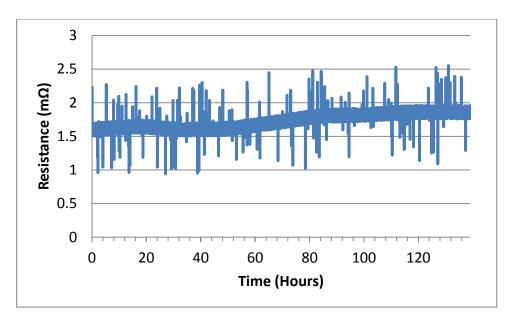

| Figure 62: Resistance profile of Mo based test sample                                  |

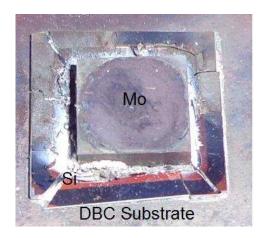

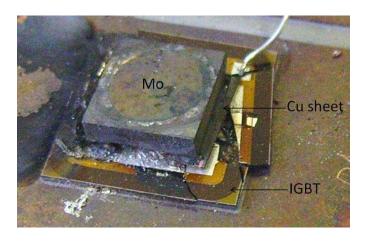

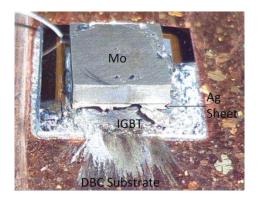

| Figure 63: Mo based test sample after passing 50A for 33 Hours                         |

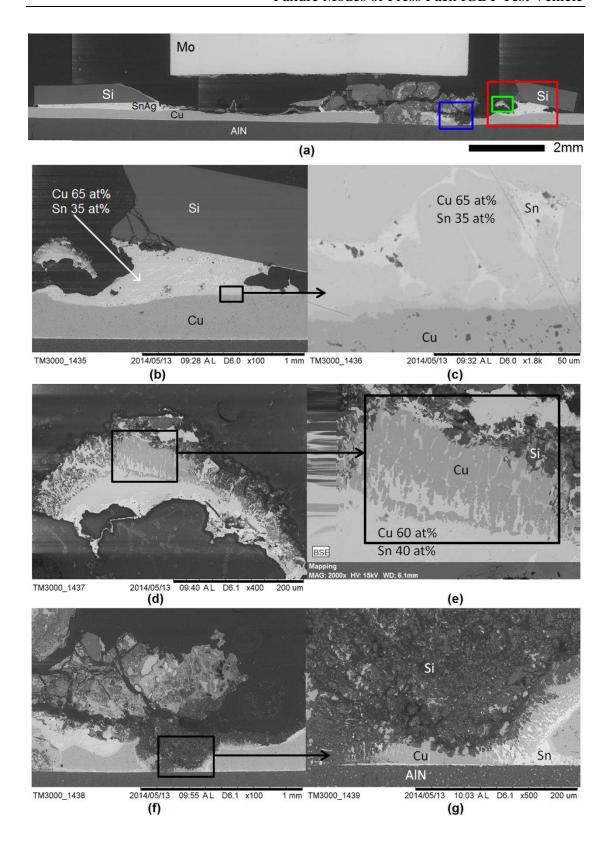

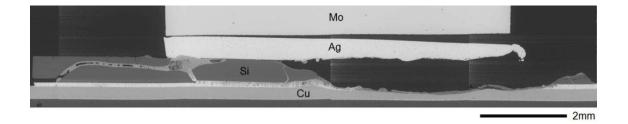

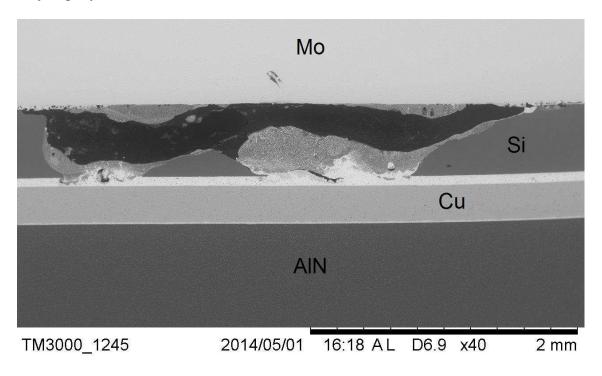

| Figure 64: Overview of cross-section of Mo based test sample under SEM96               |

| Figure 65: Image showing cross-section of Mo based test vehicle under SEM 97           |

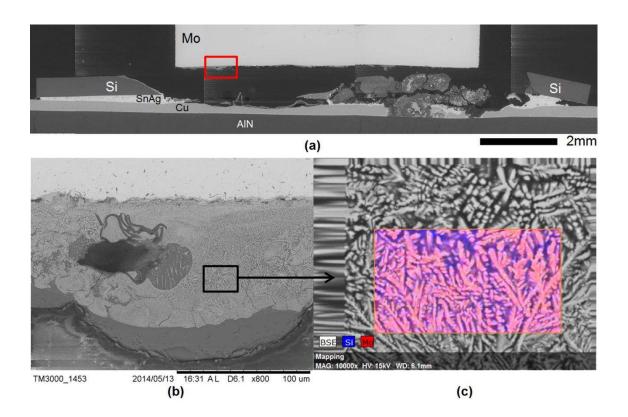

| Figure 66: SEM images showing evidence of the intermetallic compound between the       |

| Mo and Si                                                                              |

| Figure 67: Schematic of test vehicle showing physical location of metal sheet 102  |

|------------------------------------------------------------------------------------|

| Figure 68: Voltage and current waveforms of Cu based test sample exploded at 750 J |

|                                                                                    |

| Figure 69: Contact resistance of Cu based test sample                              |

| Figure 70: Cu based test sample after passing 50A for 29 Hours                     |

| Figure 71: Overview of cross-section of Cu based test sample under SEM 106         |

| Figure 72: Image showing cross-section of Cu based test vehicle analysed using the |

| SEM                                                                                |

| Figure 73: Voltage and current waveforms of SnAg based test sample exploded at     |

| 750 J                                                                              |

| Figure 74: Contact resistance of SnAg based test sample                            |

| Figure 75: SnAg based test sample after passing 50A for 140 Hours                  |

| Figure 76: Overview of cross-section of SnAg based test sample under SEM 111       |

| Figure 77: SEM images showing cross-section of SnAg based test vehicle             |

| Figure 78: Voltage and current waveforms of Al based test sample exploded at 750 J |

|                                                                                    |

| Figure 79: Contact resistance of Al based test sample                              |

| Figure 80: Al based test sample after passing 50A for 150 Hours                    |

| Figure 81: Overview of cross-section of Al based test sample under SEM 116         |

| Figure 82: Image showing cross-section of Al based test vehicle under (a) SEM, (b) |

| Optical microscope, (c), (d), (e) and (f) under FIB                                |

| Figure 83: Voltage and current waveforms of Ag based test sample exploded at 750 J |

|                                                                                    |

| Figure 84: Contact resistance of Ag based test sample                              |

| Figure 85: Ag based test sample after passing 50A for 150 Hours                    |

| Figure 86: Overview of cross-section of Ag based test sample under SEM             |

|------------------------------------------------------------------------------------|

| Figure 87: Image showing cross-section of Ag based test vehicle under SEM 121      |

| Figure 88: Resistance profile of Mo, Cu, SnAg, Al and Ag                           |

| Figure 89: Phase diagram of Mo-Si [61]                                             |

| Figure 90: Phase diagram of Cu-Si [61]                                             |

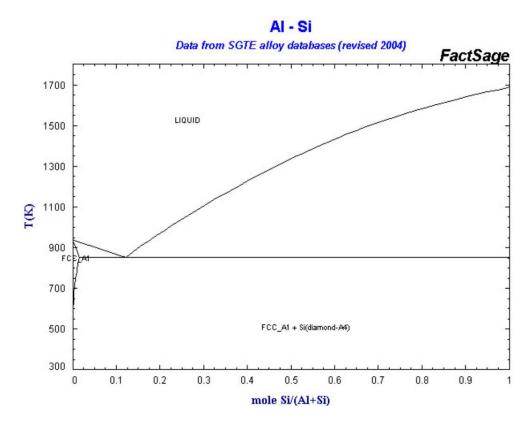

| Figure 91: Phase diagram of Al-Si [61]                                             |

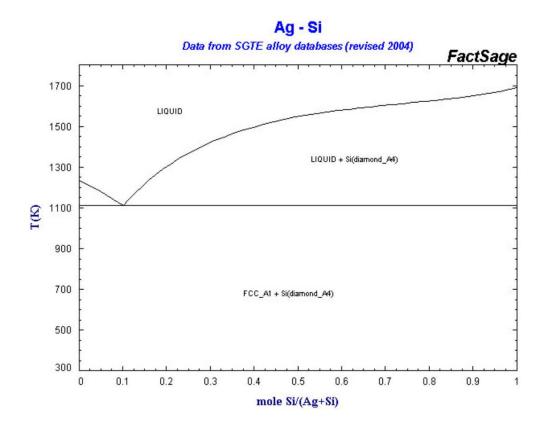

| Figure 92: Phase diagram of Ag-Si [61]                                             |

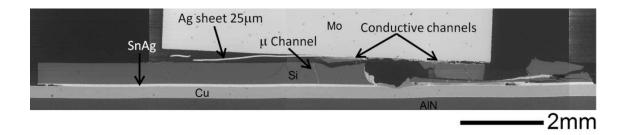

| Figure 93: SEM image showing cross section of 25 µm Ag sheet based test sample.133 |

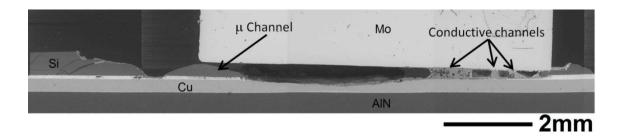

| Figure 94: SEM image showing cross section of Mo coated with                       |

| 50μm Ag nano particles preform. 134                                                |

| Figure 95: SEM image showing cross section of 5µm Ag sheet based test sample 134   |

# **LIST OF TABLES**

| Table 1: Summary of results from wirebond based test samples                           |

|----------------------------------------------------------------------------------------|

| Table 2: List and property of materials used in the simulation                         |

| Table 3: Summary of the results from flexible PCB based test vehicles                  |

| Table 4: Summary of results from sandwich structure based test vehicles                |

| Table 5: Saturation time and peak current of test samples                              |

| Table 6: Summary of contact resistance profile using different intermediate metals 125 |

| Table 7: Physical properties of annealed materials                                     |

| Table 8: Summary of different intermetallic compounds and alloys which are directly    |

| in contact with intermediate metal residual                                            |

## 1 Introduction

#### 1.1 Motivation

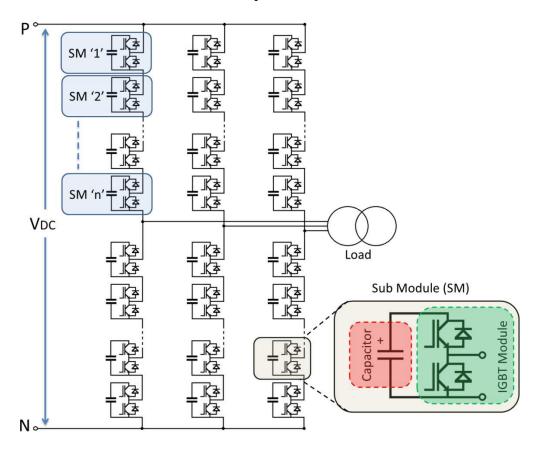

IGBT power modules are a workhorse of modern industry where they are used as switching devices in various applications such as modular multi-level converters (M²LC), traction motor drives, renewable energy, pulse power systems (PPS), switch mode power supplies (SMPS), uninterruptable power supplies (UPS) and aerospace applications. Recently, modular multi-level converters or M²LC have gained popularity particularly for their use in high voltage direct current (HVDC) transmission systems. They offer higher efficiency and very low level of the harmonic distortion which eliminates requirement of the harmonic filters in the HVDC system. Figure 1 shows the circuit diagram of the power stage of a modular multi-level converter in which 'n' numbers of sub modules are connected in series in each leg to support high voltage. Each sub module consists of an IGBT power module in half-bridge configuration along with a local DC storage capacitor [1].

Although the converters are designed with extreme care and consideration enabling them to deal with various kind of fault scenarios e.g. over current, over voltage etc. still it is highly likely that they will fail by experiencing a fault condition which it was not designed to tolerate, either because this was overlooked by the designer, or because it was not commercially viable to design for such a condition. The fault condition can be caused by various reasons e.g. gate drive fault, control system fault or short/open circuit at load etc.

In a converter, there are other components besides IGBT power modules: for example control system, gate drives and passive components such as filter capacitors and reactors. When the fault occurs, depending on the fault type and current that flows

through the circuit during fault condition, filter capacitors and reactors usually survive as they are quite robust and are capable to withstand instantaneous large peak currents. IGBT power modules on the other hand have limited capacity to withstand large peak currents, hence resulting in their failure. Therefore the weakest link in power circuit of a converter is the IGBT power module [2, 3].

Figure 1: Modular multi-level converter [1].

Figure 1 shows that each sub module has a local DC storage capacitor which acts as a DC voltage divider and also protects the IGBT from unwanted voltage spikes caused by the parasitic inductance of DC bus when IGBT devices are switched. In a sub module, if the capacitance of the capacitor is 24mF and is charged up to 1300V, the energy stored in capacitor would be 20.3 kJ and if an IGBT power module fails, this local stored energy can dissipated inside the IGBT power module causing a massive explosion and possibility of emission of shrapnel [4].

After the failure of the IGBT power module, the workability of the converter is dependent on the failure mode of IGBT power module. If the module has achieved an open circuit failure mode (OCFM), there will be no current passing through the leg where the failure has occurred; hence the converter will stop working. Whereas, if the module has achieved the short circuit failure mode (SCFM), current can still pass through the failed sub module and if the rest of the sub modules in the converter leg can block the V<sub>DC</sub> safely, the converter would continue its operation in spite of the sub module failure. This implies that if the converter is designed with additional or redundant sub modules, having failure to short circuit ability, the operational life span of the converter can be increased.

The large operational life span of the converter is especially important for the systems which are installed very remotely, at places which are not easy to excess or where the cost of unscheduled maintenance is very high [3]. The failed sub module can be replaced later during the scheduled maintenance. This implies that once an IGBT power module achieves SCFM, the life time of the SCFM or stability of SCFM is also equally important, and the module has to offer a stable current conduction path for at least the time period equal to the time period of the scheduled maintenance.

This raises a series of interesting questions, for example: what is the mode of failure of a conventional IGBT module? What are the factors that cause an IGBT module to fail to open or short circuit? Can the design of an IGBT module, the materials used in its construction, or the techniques used to provide interconnects to the semiconductor die within, influence the likelihood of a module failing to short-circuit, and what factors contribute to the stability of SCFM?

The aim of this thesis is to find answers to these questions and to understand the conditions which are necessary to facilitate and form a stable failure to short circuit in IGBT power modules.

#### 1.2 Conventional Packaging and its Problems

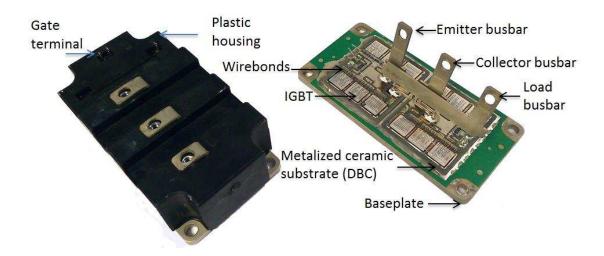

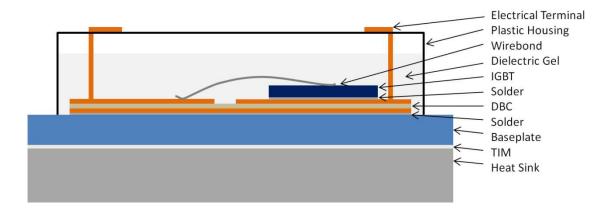

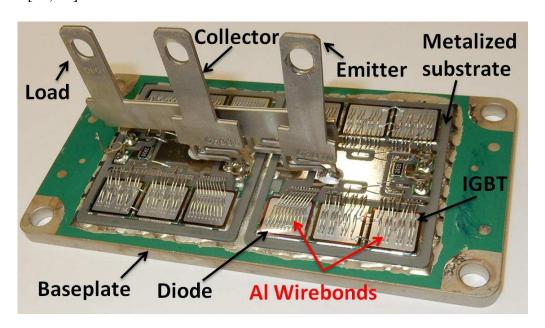

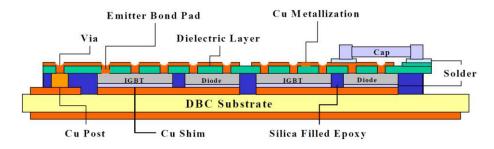

A typical power IGBT module can be seen in Figure 2. In a conventional power IGBT module, the IGBT dies are attached to the metalized ceramic substrate. The latter consists of a ceramic layer (aluminium nitride, alumina) sandwiched between two copper layers.

Figure 2: IGBT power module

The top copper layer of substrate provides copper tracks of customised design for different circuit configuration e.g. chopper or half bridge etc. The interconnections between the emitter and gate and the copper tracks of substrate is done by using ultrasonically bonded/welded Al wires. The collector, emitter and gate terminals of the device are finally taken out of module using busbars which are also soldered on to the top copper tracks of the substrate. The middle ceramic layer has high thermal conductivity and dielectric strength hence it provides electrical isolation from top

metallization to the bottom metallization and offers a channel to the heat losses incurred in the junction of the devices during their normal operation. The bottom metallization of the substrate is soldered on the baseplate which is normally made of AlSiC and is slightly curved i.e. either plano-convex or plano-concave shape to enhance the thermal contact when it is fixed by screws on the mounting. A small layer of Thermal interface Material (TIM) is applied between the heat sink and baseplate interface which improves the thermal contact between the heat sink and baseplate. Silicone dielectric gel which has high dielectric strength is used to encapsulate the components which further enhances the breakdown voltage of the module hence enabling it to be operated at high voltages. The module is then covered with a plastic housing which provides electrical insulation between the electrical terminals, a large creepage distance and mechanical stability under elevated temperature and polluted environmental conditions.

Figure 3: Cross-section of conventional power IGBT module

The analysis of the IGBT market suggests that it is dominated by the classic wirebonded IGBT modules and its variants. It is possibly because of the fact that this packaging technology was introduced in the 80's and was originally applied to packaging of metal oxide semiconductor field effect transistors (MOSFET) and

bipolar junction transistors (BJT). After the invention of IGBT, similar packaging technology was used for IGBT power modules.

Since the introduction of the first commercially available power IGBT module the emphasis was more inclined towards solving the problems related to the power semiconductor device. Lot of research was carried out to make the devices more reliable, efficient and rugged. Unfortunately packaging on the other hand was not given much emphasis possibly because it was fulfilling the requirements of the applications with slight compromises or because at that time applications were not as challenging as they are now. Figure 4 shows the comparison of an old module with a new one, where it can be seen that both old and the new module have same external appearance.

Figure 4: IGBT modules (left) from 80's, (right) latest IGBT module.

On the other hand, due to the ongoing technological developments in power electronics, industrial applications are evolving and becoming more demanding. Industrial applications require IGBT modules with SCFM capability, low inductance, high surge current rating, high current density, high operating temperature and high reliability. The parasitic inductance offered by the packaging of a conventional wirebonded IGBT module is more or less adequate enough to switch the Si based semiconductor devices because they only switch at a few kHz. On the other hand for SiC based semiconductor devices which operate few hundreds of kHz, even a small

parasitic inductance offered by the packaging would result into a massive voltage overshoot during the turn off period, hence SiC based semiconductor devices cannot be packaged in the same packaging. Likewise, single sided cooling offered by the conventional IGBT module is adequate enough to remove thermal losses produced by Si based semiconductor devices because their current density is less as compared to SiC based semiconductor devices which has high current density. Hence it needs double sided cooling which unfortunately is not possible to achieve by using conventional packaging technology.

In summary modern and future industrial applications require the development of an IGBT power module with high current density, SCFM capability, double side cooling, low inductance, high surge current, low loss and reduced cost. All these industrial application demands cannot be completed by using conventionally packaged power IGBT modules hence research in advance packaging techniques is of great importance to develop an alternative packaging technology which can make power modules more compatible with modern industrial applications.

#### 1.3 Problems addressed in this Thesis

This thesis will address the problems associated with the existing solutions to achieve SCFM in IGBT power modules, which include the high costs incurred with achieving extremely flat surfaces of different components, the complicated structure and the complex manufacture procedure. Therefore, the main objective of this research work is to understand the failure mechanism of the IGBT power module by investigation into the interconnect structures and its relation to energy absorption and how to achieve low and stable contact resistance in the failed module. The results obtained are expected to provide guidance for further investigation and development of IGBT

power modules featuring SCFM with the possibility of a simple structure and a low manufacturing cost.

To achieve the above specified objectives, the first challenge of the research work is to develop an understanding about the **modes of failure** of a conventional IGBT power module. The second is to find out the effect on failure modes of using different **interconnect technology**. The third task is to find out the **structure** of the power module which facilitates SCFM. The final task is to find out the **material system and minimum thickness** which enables a stable SCFM.

#### 1.4 Research Contributions

The main contribution of this work is the investigation and the identification of a relatively simple and cost effective solution for design and manufacturing of IGBT modules which feature failure to short circuit behaviour. The specific contributions include:

- The failure behaviours of the IGBT modules constructed with four interconnect technologies including conventional aluminium wirebond, flexible PCB, sandwich structure and press pack structure have been investigated;

- The ability of featuring failure to short circuit behaviour for the sandwich structure IGBT module under realistic energy levels in the event of IGBT destruction has been demonstrated;

- The microstructures of the tested IGBT modules with both failure to open circuit behaviour and failure to short circuit behaviour have been characterised;

- The phase changes of the component materials in the IGBT modules during overcurrent testing have been looked into;

- The material systems which result into stable SCFM have been investigated along with the identification of the most suitable material;

- The minimum thickness of intermediate layer for achieving the stable SCFM has been quantified.

#### 1.5 Application of the Project

#### 1.5.1 Modular Multi-level Converters

High voltage modular multi-level ( $M^2LC$ ) converters will be used in high voltage direct current transmission networks. In this application several low voltage IGBT modules are connected in a series string to achieve the required voltage rating [1, 5]. If one of the series connected modules fails to open circuit, the whole converter can no longer be functional as there would be no current path. The outcome of this research can be used to make modules which can achieve a stable SCFM and hence can enable the converter to continue its operation even if modules have failed as long as the rest of the modules can withstand the overall input DC rail voltage.

#### 1.5.2 High Speed switching Devices

Another potential application of this research is in the area of high speed switching device packaging. In comparison to Si based devices, Silicon Carbide (SiC) devices operate at quite high switching frequencies. If SiC devices are packaged in the conventional way, at higher switching frequencies, the rate of change of current di/dt becomes high and if there is even a very small parasitic inductance in the current commutation loop, it will result in a high voltage overshoot which can destroy the

device [6, 7]. In other words SiC devices are capable of operating at a high switching frequency but the current packaging technology is limiting it. By using the physical layout of the packaging which enables the achievement of SCFM, the parasitic inductance can be decreased significantly hence enabling the operation of SiC devices at higher frequencies and higher voltages.

#### 1.5.3 Explosion Proof Packaging

In a typical voltage source converter application, the energy from the supply is temporarily stored locally in a large capacitor before being fed to the IGBT power module. If the module fails short circuit, all of the energy from the capacitor gets dissipated inside the module which leads to a massive destruction to not only the module itself but to the area surrounding it [4].

The reason for this explosion is as the device goes short circuit, a very large current passes through it which causes the meltdown of the wire bonds, hence initiating arcing. The arcing then produces high temperature plasma. This rise in temperature causes the materials inside the conventional IGBT module to vaporise and as the structure of the module is not confined, metallic shrapnel escapes the packaging at very high velocities. These high velocity shrapnel along with other debris can damage the delicate control circuitry and injure or harm nearby personnel.

The outcome of this research can be utilised to make explosion proof packaging because unlike the conventional IGBT module where the packaging is not confined, the new layout is based on the confined structure which will not permit any debris to escape the packaging hence not only saving the rest of the converter from the debris of failed device but also reduce the risk of personnel injury.

#### 1.5.4 High Reliability

The IGBT devices by themselves are very reliable as long as they are operated within the limits defined in their datasheet. The weakest link is the interconnect technology i.e. the wirebonds and the soldering of the device on the substrate in which failure can easily take place when the module is subjected to the electro-thermal stress [8, 9]. The outcome of this research has led to the wirebond less silver sintered interconnect technique which can extend the operational lifespan of the module.

#### 1.5.5 New Manufacturing Approach

The conventional IGBT module packaging process is quite slow labour intensive, expensive and inefficient. The emitter contact of each IGBT die involves at least 25 ultrasonic bonds and if there is a 200A module, it will require approximately 300 individual bonds which is a very slow process and often results in a low yield.

As there are no wirebonds involved in manufacturing of a module which can achieve SCFM, it can open a doorway to explore the new possibilities of more efficient and high yield manufacturing processes which might have potential to reduce the manufacturing cost and this needs to be investigated.

#### 1.5.6 Double Sided Cooling

When the device turns on, it conducts current and dissipates heat. This heat causes the junction temperature of the device to rise and if the temperature exceeds the maximum junction temperature of the device, the device fails. Power modules must extract this heat as efficiently as possible. Conventional IGBT modules are single sided cooled because of their construction, this means that the heat goes out of the system in one direction, only normally through baseplate and the heat sink. The physical layout of

the module which achieves SCFM allows cooling from both sides which can help in more efficient cooling of the devices.

#### 1.6 Overview of the Thesis

This thesis consists of eight chapters. Chapter 1 highlights the impact of this research work i.e. the applications which can benefit from the outcomes of this research. It also provides summary of existing packaging technologies their advantages and shortfalls. The current problems and challenges faced by the application industry have been identified which is basically the motivation behind this research work.

Chapter 2 is the literature review of the existing packaging technologies. In Chapter 3 tests were carried out on a simple wirebonded test vehicle to understand whether it fails to open or short circuit and relationship of the failure mode with the input energy is also discussed. Chapter 4 presents the experimental results of failure mode of flexible PCB based interconnect technology. The failure mode of sandwich structure is explored in Chapter 5.

In chapter 6 a simplified press pack IGBT (PPI) test vehicle is constructed and tested for its abilities for the failure to short circuit. Chapter 7 deals with the investigation into the most suitable material which could facilitate a failure to stable short circuit along with finding out its minimum thickness. Finally Chapter 8 contains the conclusions of the research and contribution of this research towards the packaging technology to develop a SCFM capable module.

## 2 LITERATURE REVIEW

Interconnect in IGBT power modules is the use of materials and technologies to electrically and mechanically connect the collector, emitter and gate of the device to the internal/external circuit for forming the intended electrically conductive paths while ensuring mechanical stability. It is the important part of the packaging process for achieving stable failure to short circuit behaviour of the power module. This is because the failure in IGBT power modules is in general caused by extremely rapid electric-thermal energy dissipation, while both the mechanical structure and the thermal and electric conducting paths of the power module during the operation heavily depend on the interconnect technology. Destructive testing of IGBTs is an essential part of this research therefore different electrical short circuit failure types encountered by IGBTs will be reviewed in sub-section 2.1. Then conventional aluminium wirebond technology along with all the interconnect technologies under investigation and development for overcoming the thermal and electric limits of aluminium wirebond will be reviewed. They include ribbon bond, embedded chip technology, metal post-interconnect parallel-plate structure, dimple array interconnect, planar interconnect technology, pressure contact technology, flexible PCB based packaging technology and press pack IGBT. Despite the fact that the majority of these interconnect technologies have not directly been intended for achieving failure to short circuit behaviour, analysis and understanding of them can be useful and closely associated with the present work. This is because a systematic review of these interconnect technologies can gain knowledge and clues on how to design the mechanical structure and select interconnect materials for obtaining the desirable electric-thermal energy dissipation to favour failure to short circuit behaviour of the power module. Therefore, the interconnect technologies not directly intended for achieving failure to short circuit behaviour, together with conventional aluminium wirebond technology, will be reviewed in sub-section 2.2. On the other hand, two of the IGBT power modules using the press pack interconnect technology have been proposed and developed for achieving failure to short circuit behaviour of the power module. They are more closely related to the present work, and hence a more detailed review of them will be given in a separate sub-section (2.3).

#### 2.1 Electrical Failure modes of an IGBT

Generally the electrical failure modes of IGBT power modules can be classified as open circuit failure and short circuit failure. Open circuit failure can be caused by an external loose electrical connection, rupture of wire due to passage of high current or wirebonds lift off. This can lead to discontinuous, reduced or intermittent flow of current, which consequently may lead to secondary failure which can be catastrophic. The electrical short circuit failure of an IGBT module involves the flow of uncontrolled surge current in a converter which can lead to potential destruction to not only the failed device but the other components as well [10, 11].

#### 2.1.1 Open circuit failure

The open circuit failure can be further classified into two types

#### 2.1.1.1 Wirebond Lift-off

Aluminium wirebond is an interconnect technology which is used to make electrical connections with the gate and emitter side of IGBTs. During the normal operation of the device, the IGBTs are subjected to the power/thermal cycling which causes the wirebond lift off. The lift off is due to the mismatch in the coefficient of thermal expansion (CTE) between the Al wirebond and the Si device. The thermal cycling

causes the initiation of cracks in the periphery of the bond and finally results in lift off [12].

#### 2.1.1.2 Gate Drive Failure

The gate drive failure can be due to damaged device or disconnected/loose wires between gate drive and IGBT module [13]. This may lead to intermittent misfiring which can initiate secondary failure which can be catastrophic. If gate terminal goes open circuit i.e. become floating, it can possibly result in thermal runaway or high power dissipation [14].

#### 2.1.2 Short Circuit Failure

The short circuit failure can be classified into the following types:

#### 2.1.2.1 High Voltage Breakdown

It is caused by the high voltage overshoot which is induced by high di/dt of the collector current and stray inductance during the device turn off switching transient. If the voltage overshoot is high, the electric field can reach the critical region which will initially result in breakdown of a few cells in the IGBT first. This will result in high leakage current which will rise local temperature forming hotspots. Subsequently, this leads to the heat diffusion from the hot spots to the neighbouring cells eventually resulting in catastrophic failure [15]. The high voltage breakdown can also happen due to high value of collector to emitter voltage Vce and gate to emitter voltage Vge. It results into abrupt destruction followed by a surge of current during turn on of the device [16].

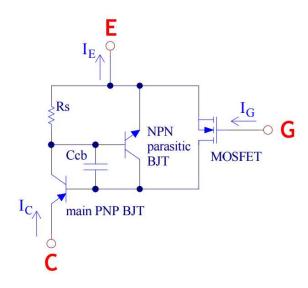

#### 2.1.2.2 Static and Dynamic Latch-up

In IGBTs, latch-up occurs when collector current (Ic) can no longer be controlled by the gate. The equivalent circuit of an IGBT is shown in Figure 5. Latch-up happens due to the turn on of the parasitic NPN transistor which causes the main PNP transistor to act as a thyristor and hence control over the collector current can no longer be established by using the gate terminal. The latch-up is of two types, static and dynamic latch-up [17]

Figure 5: The equivalent circuit of IGBT [17]

Static latch-up happens due to high Ic which causes a high voltage drop across the parasitic resistance Rs resulting in turn on of the NPN parasitic bipolar junction transistor (BJT). The dynamic latch-up happens normally during the turn off of the IGBT when the NPN parasitic BJT is biased by the junction capacitance Ccb. Both types of latch-up result into catastrophic failure as the control over the gate is lost. The latest generation of IGBT devices having a trench gate structure and the heavily doped P-base region under N-emitter have demonstrated good latch-up immunity and is not considered as a common failure in modern IGBT devices [18].

#### 2.1.2.3 Second Breakdown

It is a thermal breakdown of the device due to high stress current. The sequence of events for second breakdown is as follows: the increase in collector current causes increase in collector-base junction space-charge density. This decreases the breakdown voltage which in return further increases the current density. The process continues until the high current density region reduces to the minimum area of a stable current filament. This results in the rapid rise in temperature and collapse of voltage across IGBT [11, 19].

#### 2.1.2.4 Energy Shocks

When an IGBT encounters a short circuit during its normal operation, high power is dissipated in the module which can result in the failure of the device. The energy shock is the dissipation of high power in the device in a short time interval. This results in the flow of short circuit current which rapidly rises temperature[20, 21]. During the energy shock, the device does not fail until the heat generated due to the power dissipation exceeds the Intrinsic Temperature (250°C) of the Si. The intrinsic temperature is dependent on the voltage rating of the device and it normally decreases with the increase in operating voltage of the device. Once the device reaches its intrinsic temperature, any further rise in junction temperature would increase the charge carriers exponentially resulting in thermal runaway.

Type-I and Type-II short circuit failure can both be classified as energy shock failure. Type-I failure happens when the already turned 'on' device encounters a short circuit. It is also known as fault under load [21].

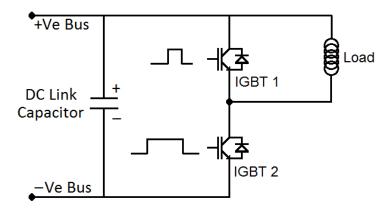

Figure 6: Test circuit to perform short circuit [21]

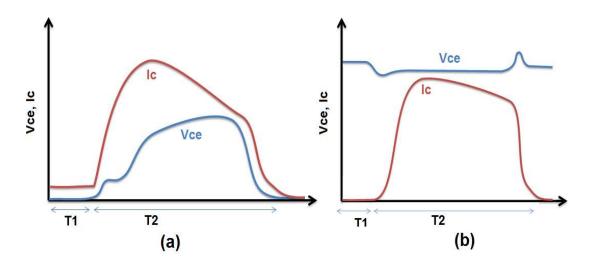

Figure 6 shows the test circuit to perform the short circuit test. The idealised waveforms of the type-I test can be seen in Figure 7 (a). Here Ic is the collector current and Vce is the voltage across the device. During time interval T1, the IGBT2 is in 'on' state and is working normally and it can be seen that Vce level is low. During time interval T2, the IGBT 1 erroneously turns 'on', this will cause a huge rise in current which can be seen in time interval T2. The IGBT2 leaves from the conduction state and enters the active region. This will result in high power dissipation in the device causing the thermal overload and hence eventually failure of the device.

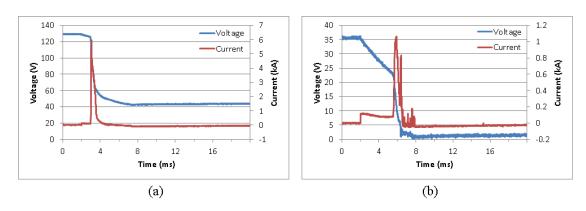

Figure 7: Idealised voltage and current waveforms of (a) Type-I and (b) Type-II test.

A Type-II short circuit happens when the device is turned 'on' into an already existing short circuit. Type II failure is also known as the hard switch fault [21]. This type of short circuit fault can be created by putting a short circuit across the load and turning on IGBT2. This will turn 'on' the IGBT straight into a short circuit. The idealised voltage and current waveforms can be seen in Figure 7(b). In time interval T1, the device is off and Vce is equal to the DC input voltage. In time interval T2, the device is switched 'on' which will basically put a short circuit across the DC link capacitor

resulting in flow of short circuit current through the device. This will result in dissipation of all the energy stored in the DC link capacitor to dissipate in the device resulting in thermal overload and catastrophic failure of the device.

The method used to achieve destructive failure of IGBTs in this research work resembles the Type-II method which results in thermal overload failure. It involves turning on of the IGBT into a short circuit which cause an uncontrolled flow of current through the device resulting in thermally overloading the device and hence its failure.

# 2.2 Interconnect Technologies

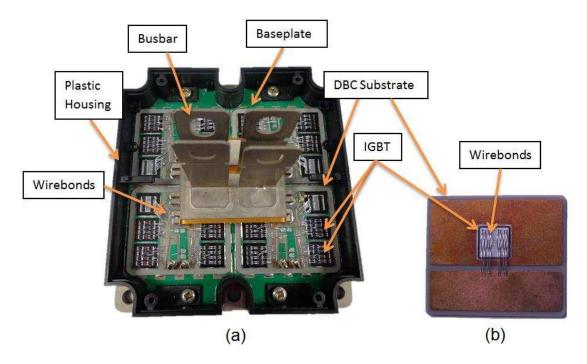

#### 2.2.1 Wirebond

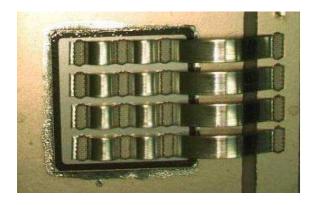

Wirebond is the most common interconnect technology which is widely employed in power IGBT modules. Figure 8 shows an IGBT module in which wirebond on top of the IGBTs provides an electrical connection with the emitter and gate terminal of the device. The bond is made by a tool which vibrates from 40 to 100 kHz to bond the wire [22, 23].

Figure 8: Wirebonds interconnection in IGBT module

The most common wire used for bonding is aluminium but copper wire is appearing to be used by few manufacturers for high power modules[24, 25]. The main reasons for the popularity of aluminium wirebonding are the established manufacturing process and the availability of support in the form of both infrastructure and literature from industry. The bonding process itself is highly flexible especially for handling complex geometries of substrates and dies and the bonding equipment is easy to program for automated manufacturing. However, wirebonding is a slow process and its disadvantages include reduced electrical performance, parasitic inductance, non-

uniform current distribution which results into poor transient current sharing [26]. It is also prone to fatigue which causes it to lift off during power/thermal cycling [12, 27].

#### 2.2.2 Ribbon Bonding

Ribbon bonding has been developed to replace wire bonding for improving electrical performance and reliability [28]. Figure 9 shows a ribbon bond. Instead of bonding a large number of wires, a few thick Al ribbons are bonded. For example if eight 15mils diameter Al wires are bonded on the IGBT, these can be replaced by using three 70mil x 8mils Al ribbons. The bonding process is similar to that of wires except that a special tool is required to perform the bonding. Its advantages are a large area of electrical contact resulting in better electrical performance and reduction in parasitic inductance.

Figure 9: Ribbon Bonding[28]

It was reported that when subjected to temperature cycling from -60°C to 170°C for 2000 cycles, it resulted in exceptional bond strength and reliability as compared to the wirebonds [28]. As compared to the wirebonds, the bonding of thick ribbon requires high pressure on the die and to compensate for that a thick metallisation is required on the die to avoid cracking and the problem can get worse if bonding is performed on a thin device [29].

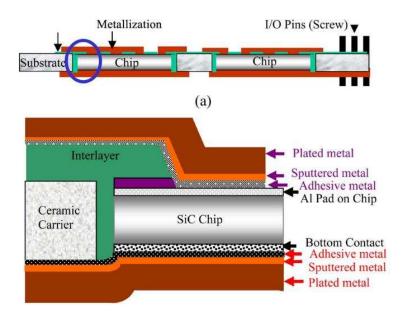

#### 2.2.3 Embedded Chip Technology

The embedded chip technology (ECT) has been developed to not only eliminate the use of die attachment and wire bonds, but also achieve high temperature operation, reduction in parasitic inductance and increase in power density [30]. Figure 10 shows the cross-section of an embedded chip module which has been built using ECT [30]. It consists of a ceramic substrate containing openings to hold the device; the power semiconductor die is placed in the opening and is fixed with adhesive. A dielectric layer is printed on the top of device which contains a via. Seed layers are sputtered on both the top side and bottom side of the device, and interconnects are achieved with further electroplated Cu [30].

Figure 10: Embedded Chip Module [30]

The experimental results show that the module can be operated at  $200^{\circ}$ C. In order to operate at high temperature, a close matching of coefficient of thermal expansion (CTE) between different layers of module has been achieved by placing a chromium layer between the chip and the top copper interface. It has also been highlighted that a power density of  $284W/in^3$  under forced convection at room temperature has been

achieved which is 5 times the power density of a Si based module under similar conditions[30]. However, no reliability study has been carried out. Although the authors claim that the mechanical stresses generated by the CTE mismatch has been reduced, but the thermal stress analysis performed by Lee Pik et al. suggests the mechanical stress of an embedded chip module increases with thickness of the device [31].

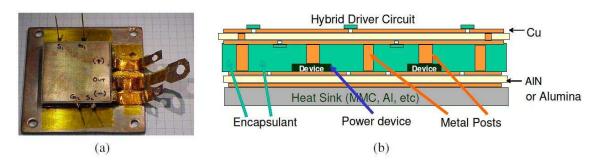

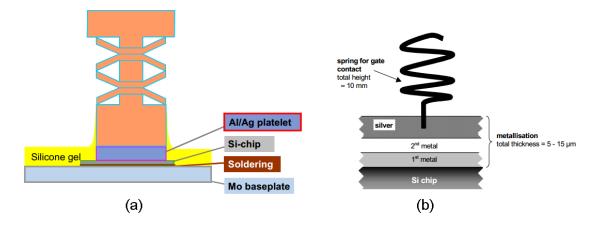

#### 2.2.4 Metal Post-Interconnected Parallel-Plate Structure

The metal post-interconnected parallel-plate structure (MPIPPS) is another packaging technology which uses metal posts instead of wirebonds to make connections with the emitter and gate of the device [32, 33]. As shown in Figure 11, in a MPIPPS module, the IGBT die is soldered on the direct bonded copper (DBC) substrate which can be directly mounted on a heat sink. The copper posts are bonded to the top side of the die by soldering and a specially manufactured DBC is then soldered on top of the metal posts creating a sandwich structure [32, 33].

Figure 11: Metal Post Interconnect Parallel Plate Structure module (a)

Photograph (b) cross-section [33].

The MPIPPS offers low DC resistance, reduced parasitic inductance and capacitance, better thermal management, easy integration of passive components, easy manufacturability and robustness [32, 33]. The electrical performance data of the packaged device shows that an air cooled 15 kW inverter operating from a 400V dc

bus at 20kHz switching frequency can be constructed by using three MPIPPS module which is almost twice the power that can be achieved using commercially packaged devices with similar ratings [32].

However, the authors have not highlighted any reliability issues arising from the CTE mismatch between the copper post and the silicon die. Soldering the copper posts on the device requires the top metallization of the device to be changed from aluminium to silver or copper which is a difficult process and can result into high contact resistance if the metallization is not done properly [34].

MPIPPS has also been used to develop an integrated power electronic module (IPEM) which offers superior thermal performance and high power density as it has integrated gate drives, decoupling capacitors and cooling mechanism[35].

Figure 12: Integrated power electronic module [35] (a) module, (b) cross-section, (c) power module, (d) cross-section of power module.

Figure 12 shows a 600V 10kW three phase IPEM inverter where the metal posts are formed on the specially designed substrates by etching. It requires two reflow steps for assembly, first die and bottom substrate attachment is done using high temperature

solder e.g. AuSn, secondly bottom DBC, the top DBC attachment is done by low temperature solder e.g. SnAg hence resulting in a sandwich structure. It does not have any baseplate which implies that it has a shorter heat transfer path and lower stress levels during thermal cycling. The module is double side cooled by direct water impingement which provides more efficient cooling[35].

The complete module is quite compact in size with volumetric power density 30*W*/*cm*<sup>3</sup> and gravimetric power density of 17kW/kg [35]. The turn on/off electrical test results shows that there was no noticeable voltage overshoot which indicates that the module has very low parasitic inductance. The pressure drop vs flowrate curve suggests that the pressure drop in the cooling system was very low and can be further adapted to requirements by series/parallel combination of impingement cells [36]. The junction to case thermal resistance is 1.2 °C/W which enables it to dissipate three times more heat to reach the same junction temperature as in conventional wirebonded module [36]. However, the active power cycling from +45°C to 105°C performed on the module shows the premature failure of the module after 500 cycles which could be attributed to the poor quality of nickel layer on top of the devices which can be improved [36]. From the perspective of thermal conductivity, power density and low parasitic inductance, the module has very good performance, however the manufacturing is very difficult and time consuming especially etching of the substrates which can result in higher manufacturing cost.

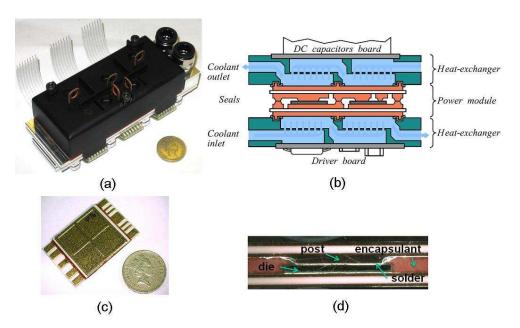

# 2.2.5 Dimple Array Interconnect

Dimple array interconnect technology has been investigated to improve the thermal conductance and reduce the electrical resistance and parasitic capacitance and inductance [37]. In this interconnect technique, the electrical connections with the device are made using dimpled metal sheet and solder bumps. Figure 13 shows one

module made using dimple array interconnect technology. This structure has better thermal conductance as compared to the wirebonded module due to large area of contact and thermal conductivity of flexible copper sheet on the top. It also offers low electrical resistance and parasitic capacitance and inductance.

Figure 13: Dimple array interconnect technology [37] (a) cross-section, (b) structure, (c) module.

The test results from turn on/off tests performed on a 600V 50A module shows 60V overshoot during turn off of the device which is considerably lower than the commercially available wirebonded module of similar specifications. This shows the lower parasitic inductance of the module [38]. In this structure, a large amount of mechanical stress concentrates between the die to solder and solder to dimple interface if bonding is done using controlled collapse barrel shaped solder joints [37]. Results from thermal and power cycling test shows that fatigue resistance can be improved if hour glass shaped solder joints are used instead controlled collapse barrel shaped solder joints [38]. However, the authors have not devised any method to control the CTE mismatch issue. Also its reliability relies on the shape of the solder joints which is very hard to control.

# 2.2.6 Planar Interconnect Technology

A planar interconnect technology, thin film power overlay technology has been introduced for high voltage, high current, low parasitic inductance, decreased

packaging volume, high reliability due to absence of wirebonds and easy adaptability to accommodate different device types in the packaging [39]. Figure 14 shows the cross-section of power overlay technology which was introduced by General Electric. In this technology, the top side of power devices (which is normally aluminium) used are first sputtered with a titanium layer and then a copper layer. The Ti layer acts as an adhesive layer between Cu and Al. The power devices are then soldered on top of the DBC. Polyamide film is attached on top of the soldered devices which is ablated using a laser to expose the electrical connection pads of the devices on which the thick Cu layer is grown using an electroplating process[39, 40].

Figure 14: Cross-section of Power Overlay Technology [39]

The key advantages of this technology are increase in electrical contact area, decrease in the parasitic inductance, lower weight and size, higher packaging density and efficient removal of heat from both sides of the device. Although the authors have made some demonstrator modules using this technology e.g. 1200V 400A IGBT based module and 150V 1-2 kW 6.78MHz class-D power amplifier using MOSFETs where they have reduced the height profile of module by 50% compared with wirebonded module but no thermal and electrical test results have been discussed. The issues related to the CTE mismatch between Si and thick Cu metallization in this design have not been completely investigated and there is no published data available regarding its reliability studies.

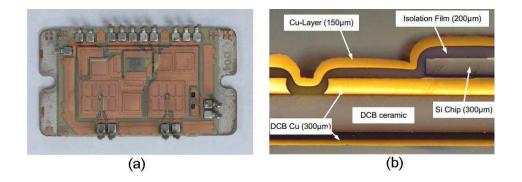

Similar planar interconnect technology has also been employed by Siemens to develop its planar power module called Siemens planar interconnect technology (SiPLIT). Its salient features low package induced electrical impedance, reduced are electromagnetic interference, and reduced thermal resistance [41]. Figure 15 shows a SiPLIT module, the manufacturing involves soldering of chips on the DBC substrate and depositing a 200 micron thick insulating film on top. Specific areas of the film are then ablated by using a laser. 150µm of copper is electroplated on top of the exposed areas to make the electrical connections [41]. This interconnect technique has better electrical and thermal performance; it has been reported that there has been approximately 20% reduction in on-state resistance and 50% reduction in stray inductance whereas, junction to ambient thermal resistance was 20% less if compared with wirebonded module. Its reliability study shows 600V 100A module has passed over 1000 thermal shocks from -40°C to 150°C whereas it passed 230000 cycles when subjected to 95°C-175°C ΔT power cycling consequently resulting into module failure because of solder die attach fatigue [40, 41].

Figure 15: (a) SiPLIT module by Siemens[42], (b) Cross-section of SiPLIT module[41]

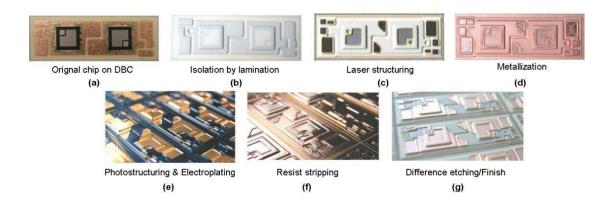

Figure 16: SiPLIT module by Siemens [41], (a) to (g) shows manufacturing process flow

Figure 16 shows the manufacturing process which involves numerous precise and laborious steps which can result into high manufacturing cost also the module cannot be worked back if some manufacturing fault occurs which can result in poor yield.

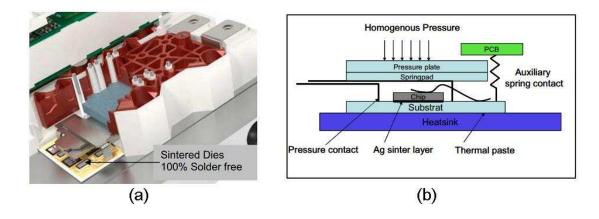

# 2.2.7 Wirebonded Module with Pressure Contact Technology (SKiiP)

The distinctive feature offered by pressure contact technology is the sintered devices, high temperature operation, high reliability and absence of solder joints and baseplate. Figure 17 shows the latest SKiiP-4 module; the devices are first sintered on the substrate and then wirebonded. The electrical/auxiliary contacts are made by using different kinds of springs depending upon application. The metalized substrate is directly mounted on the heat sink because of the absence of a baseplate which reduces the thermal resistance hence resulting in an increase in power density. The design of the module is 100% solder free which enables it to eliminate reliability problems related to solder joints [43]. It has been reported that the SKiiP-4 sintered module passed more than 90000 cycles during power cycling test based on IEC60749-34 specifications which is 3 times more than SKM45 module [43].

However, as the devices are wirebonded, the reliability problems related to wirebond still exists.

Figure 17: Semikron SKiiP 4 [43], (a) Module, (b) Cross-section

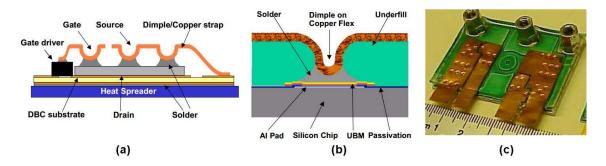

#### 2.2.8 Flexible PCB based Packaging Technology (SKiN)

The unique attribute of flexible PCB based packaging technologies is free from both wirebonds and solder joints, low parasitic inductance, high surge current improved thermal conduction and high reliability [44]. In this technology, the devices are first sintered on to the DBC and instead of wirebonding; a flexible PCB is attached to the top side of the device by sintering which eliminates the reliability issues related to both soldering and wirebonds. The electrical connections are also sintered on the DBC and the DBC is sintered directly on top of the heat sink eliminating the baseplate and thermal interface material. It has been reported that the elimination of the thermal material interface results in the reduction of thermal resistance by 25% as compared to the benchmark conventional module [44]. The large electrical contact area achieved by sintering a flexible PCB also resulted in an increase of 27% in surge current rating as compared to the benchmark conventional module. In passive temperature cycling (-50 to 150°C), the SKiN module passed several hundred cycles before the delamination of DBC to heat sink interface whereas during active power cycling (40 to 150°C), the

SKiN module proved itself to be 10 times more reliable than the Al wirebond based modules[45].

Figure 18: SKiN by Semikron[46](a) Module, (b) Cross-section

In summary, all the interconnect technologies mentioned above offer several advantages over the conventional packaging where they offer reduction in electrical contact resistance, reduction in parasitic capacitance and inductance, improved thermal conduction, double side cooling and increased operational lifetime of module. They are achieved by means of increasing the contact/conducting areas, thermal mass for heat dissipation and mechanical constraint, reducing electrical conducting length, and selecting suitable interconnect materials. Therefore, the mechanical structure and interconnect materials used in these interconnect technologies may be referred to and adopted in the present work to investigate and develop the IGBT power modules with desirable electric-thermal energy dissipation for favouring failure to short circuit behaviour.

## 2.3 IGBT Modules Favouring Failure to Short Circuit

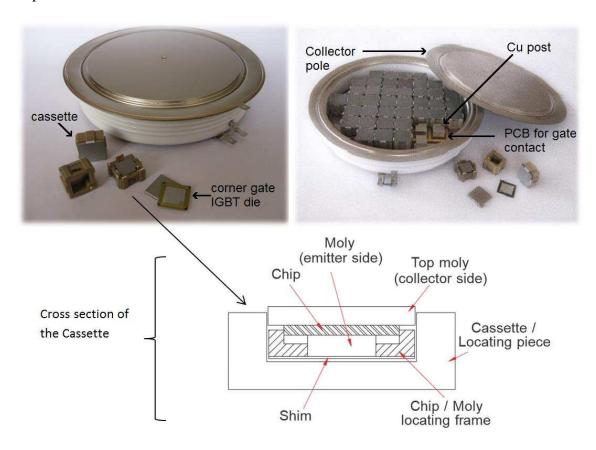

#### 2.2.1 Press Pack IGBT module

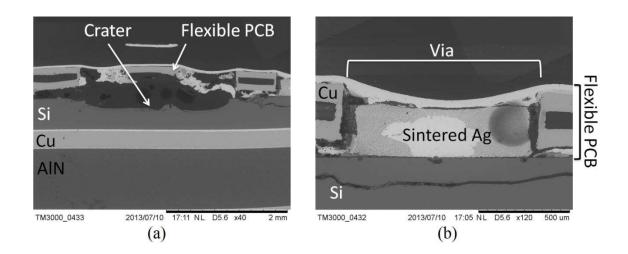

The first commercially available IGBT module (called press pack IGBT (PPI)) which is claimed to have the ability to fail to short circuit was introduced by IXYS UK Westcode Ltd. Figure 19 shows an IXYS UK Westcode Ltd PPI [47]. Its design consists of two parts i.e. the cassette and the ceramic housing. As it would be very difficult to make a pressure contact with a device whose gate is located in the centre therefore, a specially designed IGBT die with gate located at corner has been used. The cassette consists of a plastic housing in which a metallic shim is placed along with a corner gate IGBT die sandwiched between two floating Mo shims. The Mo shims serve two purposes, first they homogenise the pressure distribution on the die to avoid shattering of the die due to pressure peaks. Secondly as the Mo has CTE closer to Si, that makes it the most suitable conductive material to be placed next to the die. The cassette also offers a pogo pin gate contact which when mounted on the copper post located on the pole face of the ceramic housing, gets in contact with the PCB which connects all the gates of the IGBT dies together making a single gate terminal with very low inductance. This configuration completely eliminates all the bonded and soldered interfaces [48]. The number of cassettes is dependent on the current capability of the module. After testing each cassette externally especially for forward voltage blocking capability, the cassettes are carefully mounted on the Cu posts offered by the pole face of the ceramic housing and finally the module is hermetically sealed. One of the advantages of using the ceramic housing is retrofitting of these PPI with the existing designed assemblies based on thyristors and gate turn off thyristors without any modification of the clamping structure. The ceramic housing also reduces the chances of rupture after catastrophic failure of module which exists with the conventional IGBT module [4, 49].

In contrast to a conventional IGBT module, it has been reported that the low inductance (< 4nH) due to internal structure of PPI and the presence of large thermal mass on the devices makes it very suitable for the pulse power applications with high repetition rates [50]. The ceramic housing normally contains large numbers of individual IGBT cassettes connected in parallel along with diode cassettes which collectively act as a single IGBT along with an antiparallel diode. The low inductance which has been reported is measured from pole to pole of the PPI. However, the parasitic inductance which is responsible for voltage overshoot at the device turn-off event is not the pole to pole inductance; rather it is the commutation loop inductance which depending upon the physical size of the commutation loop path, can be larger in the case of the PPI as compared to a conventional IGBT module.

Some reliability studies have been carried out by the manufacturer where it has been claimed that the components are an order of magnitude better than the conventional thyristors during power cycling [49].

As the whole module is bond free i.e. floating and the module contains several cassettes, the uniform distribution of pressure is very important both for current and thermal conduction and even a slight uneven distribution of pressure can lead to the difference in thermal resistance amongst cassettes during its normal operation [51].

The close examination of the press pack IGBT module shows that the mechanism of pressure distribution relies on the compliance offered by the Cu posts and the metal shim which is placed under the emitter side Mo shim. Nevertheless, in order for this packaging to achieve uniform pressure distribution and to avoid breaking the fragile

cassettes, everything has to be very flat and precise which makes it very complex and expensive to manufacture.

Figure 19: Press-Pack IGBT introduced by IXYS UK Westcode Ltd [47, 52].

Regarding its abilities for a failure to stable short circuit there is no published literature except, the manufacturer claims that in the press pack thyristor and GTO the failure mechanism is a failure to short circuit and as the PPI also utilises the same packaging therefore it is highly likely that it will also fail to short circuit but does not give a guarantee that the contact resistance of the failed device will be comparable to the device in normal operation [53]. Besides that there is no publication from the manufacturer where it has been investigated. A study was carried out by ABB for which they have filed a patent [54]. This indicates that in the case of press pack thyristor, the large Si disc is normally sandwiched between two Mo discs and when failure happens, the Si melts first as its melting point is less than Mo and as current

continues to pass, Si melts forming a conducting channel which spreads throughout the cross-section. In the absence of the oxygen (in a hermetically sealed package), the Si reacts with Mo to form a type of non-conductive powder and the process continues until all Si has been consumed which may last for years [54].

It should be noticed that in thyristors, the physical size of the Si disc is much larger than the physical size of an IGBT die. Hence there is a fair chance that the PPI would not last too long before all the Si is consumed to form powder after reacting with the Mo shims.

#### 2.3.1 StakPak IGBT module

Figure 20: StakPak IGBT manufactured by ABB [55].

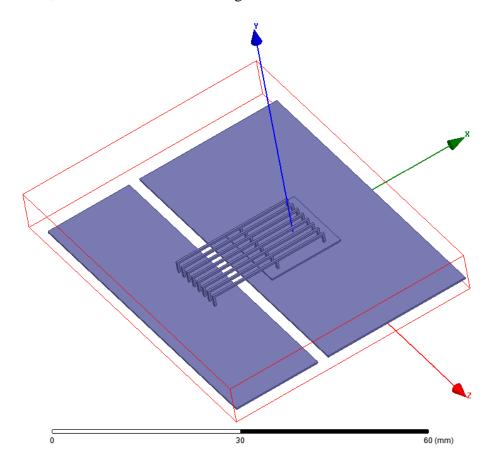

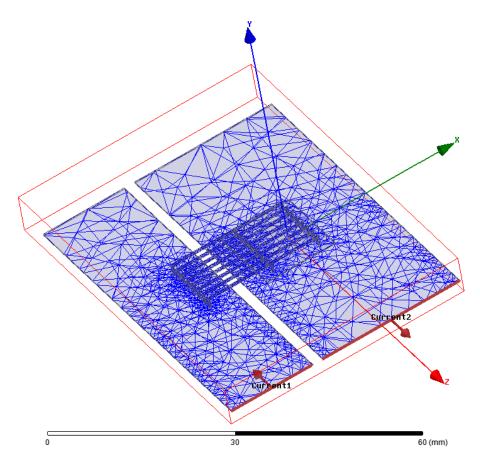

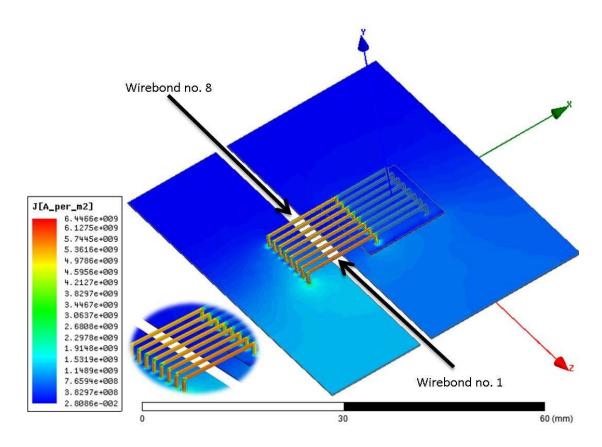

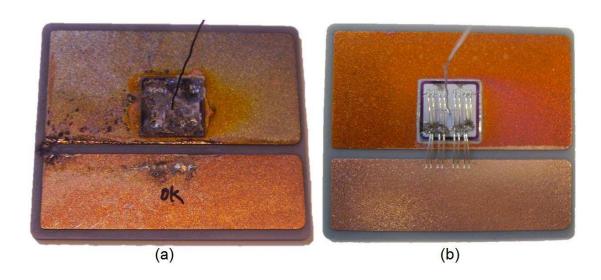

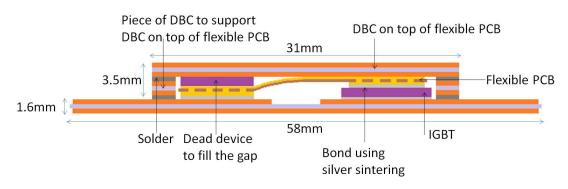

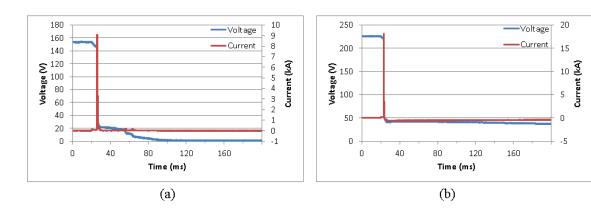

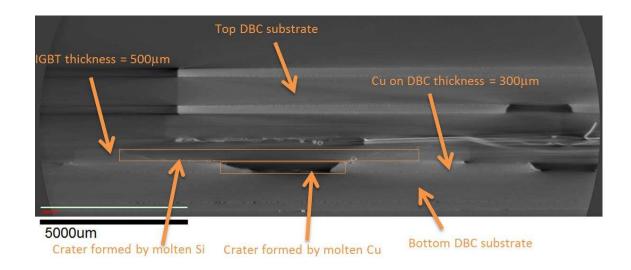

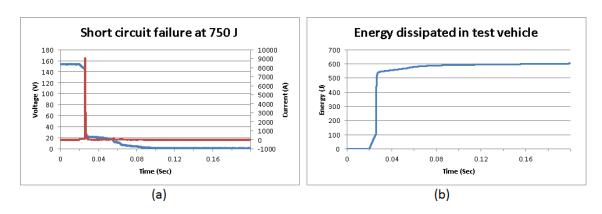

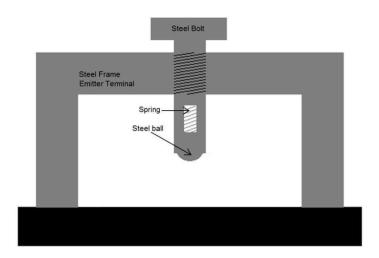

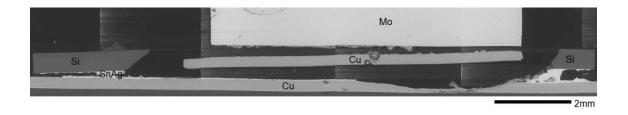

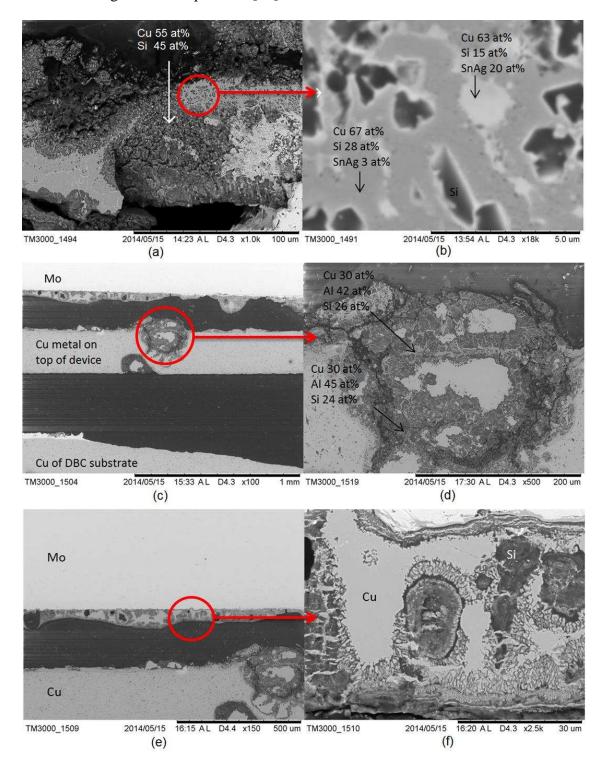

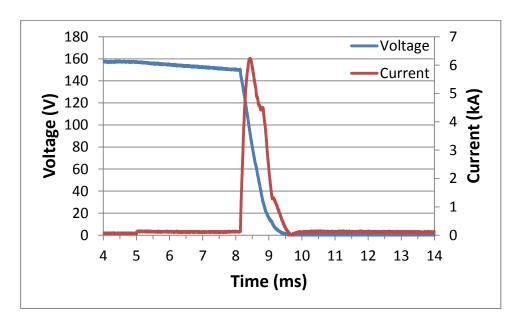

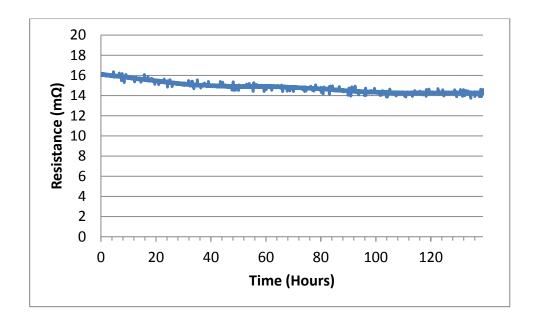

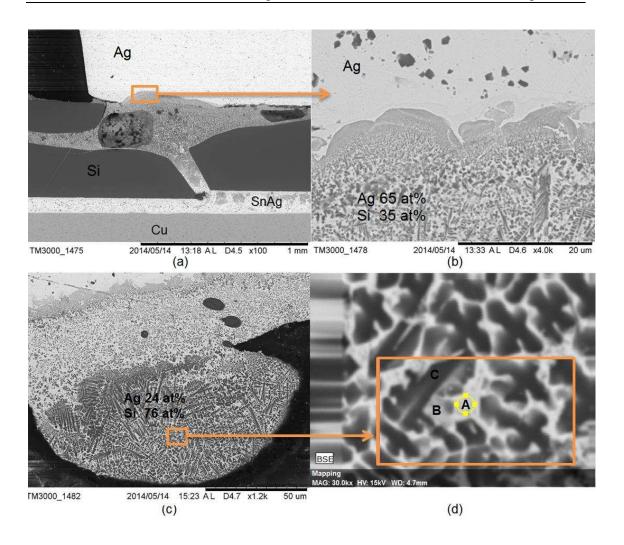

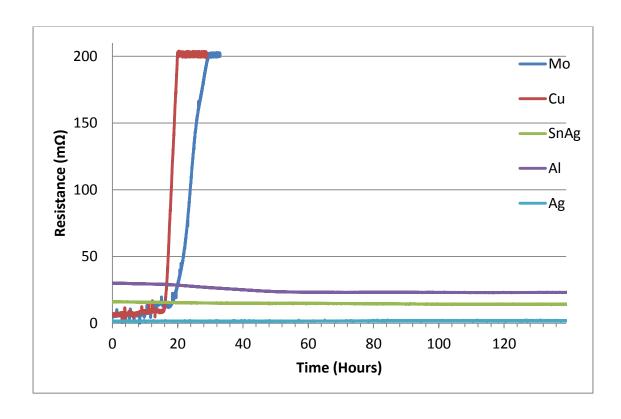

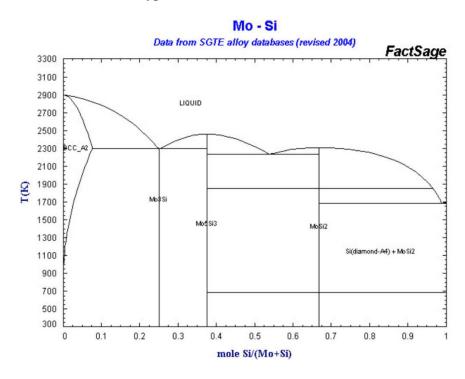

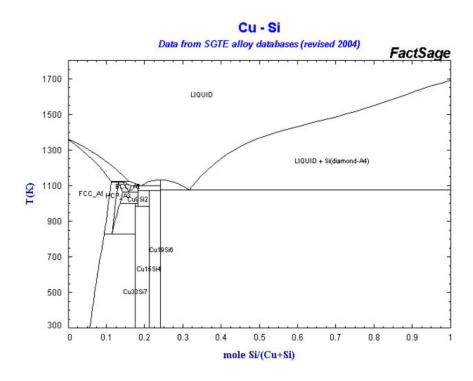

Another packaging technology for PPI was introduced by ABB called StakPak. Figure 20 shows the StakPak IGBT module in which the individual dies are packaged with a spring on top called the "press pin". When the module is clamped, each press pin experiences a force F = c.  $\Delta x$  where c is spring constant and  $\Delta x$  is the distance travelled by the spring. The non-uniform distribution of the force on different press pins will result in different distances travelled by the spring and any surplus force exceeding the sum of all the forces on individual press pins will be absorbed by the rigid frame. Hence any asymmetry in the design can be normalised by the press pins resulting in a uniform distribution of pressure on an individual die without worrying about the flatness and tolerance issues [55].