Shao, Shuai (2015) The application of sliding mode observers to fault detection and isolation for multilevel converters. PhD thesis, University of Nottingham.

Access from the University of Nottingham repository: http://eprints.nottingham.ac.uk/29098/1/thesis Shuai Shao.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end user agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# The application of Sliding Mode Observers to Fault Detection and Isolation for Multilevel Converters

Shuai Shao, BEng

Thesis submitted to The University of Nottingham for the degree of Doctor of Philosophy, July 2015

# Abstract

Multilevel converters have received significant interest recently as a result of their high power capability and good power quality. However due to the large number of sensitive components including power semiconductor devices and capacitors used in such circuits there is a high likelihood of component failures.

This thesis considers one of the most promising multilevel topologies—the modular multilevel converter (MMC). Several methods are presented to detect and locate open-circuit faults in the power semiconductor devices in an MMC. These methods are based on sliding mode observers (SMOs). The signals used in the proposed methods are already available as measurement inputs to the control system and no additional measurement elements are required. An experimental MMC rig has been designed and built to validate these fault detection and isolation methods. The methods can be used with other multilevel converter topologies employing similar analysis and principles.

# List of Papers

# Published papers:

- S. Shao, A. J. Watson, J. C. Clare and P. W. Wheeler. "Robustness analysis and experimental validation of a fault detection and isolation method for a modular multilevel converter," *Power Electronics, IEEE Transactions on* (Conditionally accepted).

- S. Shao, P. W. Wheeler, J. C. Clare, and A. J. Watson. "Fault detection for modular multilevel converters based on sliding mode observer," *Power Electronics*, *IEEE Transactions on*, vol. 28, no. 11, pp. 4867-4872, 2013.

- S. Shao, J. C. Clare, A. J. Watson, P. W. Wheeler, "Detection and isolation of multiple faults in a modular multilevel converter based on a sliding mode observer," in *Energy Conversion Congress and Exposition (ECCE)*, 2014 IEEE, pp. 3491-3495.

- S. Shao, P. W. Wheeler, J. C. Clare, and A. J. Watson. "Open-circuit fault detection and isolation for modular multilevel converter based on sliding mode observer," in *Power Electronics and Applications (EPE)*, 2013 15th European Conference on, pp. 1-9.

# Submitted journal papers:

• S. Shao, A. J. Watson, J. C. Clare and P. W. Wheeler. Health monitoring of cells in a modular multilevel converter. In *Power Electronics, IEEE Transactions on*.

# Acknowledgement

I would like to thank my supervisors Prof. Jon Clare, Prof. Pat Wheeler and Dr. Alan Watson for their guidance throughout this study. Many of the new ideas are developed through the discussions with them. I can never complete the PhD without their help and support. I am also grateful to Prof. Mike Barnes (University of Manchester) and Prof. Mark Johnson for examining this work; to Prof. Greg Asher for reviewing the annual reports.

Thanks to the China Scholarship Council for the scholarship which allows me to undertake the study.

I have received a lot of help in the experimentation from the knowledgeable research fellows and PhD students in the PEMC group, in particular, I would like to thank Dr. Chintan Patel, Dr. Edward Christopher, Dr. Liliana De Lillo and Dr Nuwantha Fernando for their suggestions.

Thanks to Xiang Wang, Otto Bakker, Chao Ji, Tao Yang, Savvas Papadopoulos, Ewan Farr, Manju Vijayagopal, Marija Jankovic, Bilal Arif, Al-tahir Aliyu, Emre Gurpinar and many other friends for the friendship and happy memories.

My parents deserve a substantial share of the credit for everything I have done. My heartfelt thanks to my girlfriend, Hui Chen, for her love and encouragement.

# Contents

| $\mathbf{A}$ | cknov              | wledge  | ements                                    | iii |  |

|--------------|--------------------|---------|-------------------------------------------|-----|--|

| Li           | List of Figures ix |         |                                           |     |  |

| Li           | st of              | Table   | $\mathbf{s}$                              | xvi |  |

| 1            | Intr               | oducti  | ion                                       | 1   |  |

|              | 1.1                | Motiv   | ation                                     | 1   |  |

|              | 1.2                | Contri  | ibution                                   | 3   |  |

|              | 1.3                | Thesis  | s Structure                               | 4   |  |

| <b>2</b>     | ${ m Lit}\epsilon$ | erature | e Review                                  | 7   |  |

|              | 2.1                | Multil  | level Converters                          | 7   |  |

|              | 2.2                | Device  | e Reliability in Power Converters         | 10  |  |

|              |                    | 2.2.1   | IGBT Failure Mechanism                    | 12  |  |

|              |                    | 2.2.2   | Capacitor Failure Mechanism               | 13  |  |

|              |                    | 2.2.3   | Effect of Component Failure               | 16  |  |

|              | 2.3                | Fault   | Detection and Isolation                   | 16  |  |

|              |                    | 2.3.1   | Hardware FDI                              | 17  |  |

|              |                    | 2.3.2   | Analytical FDI                            | 18  |  |

|              |                    | 2.3.3   | Performance Criteria of an FDI Scheme     | 19  |  |

|              |                    | 2.3.4   | Fault Detection for Multilevel Converters | 20  |  |

|              | 2.4                | Sliding | g Mode Control and Observer               | 23  |  |

|              |                    | 2.4.1   | Sliding Mode Control                      | 23  |  |

|   |      | 2.4.2   | Basic Concepts of the Sliding Mode Control            | 27 |

|---|------|---------|-------------------------------------------------------|----|

|   |      | 2.4.3   | Sliding Mode Observers                                | 28 |

|   | 2.5  | Conclu  | ısion                                                 | 30 |

| 3 | Ope  | ration  | and Controller Design of Modular Multilevel Converter | 31 |

|   | 3.1  | Introd  | uction                                                | 31 |

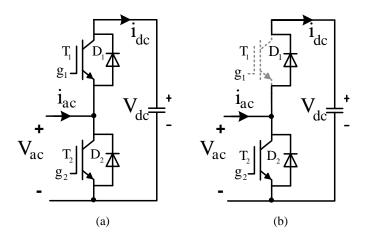

|   | 3.2  | Opera   | ting Principle                                        | 31 |

|   | 3.3  | System  | n Model                                               | 35 |

|   | 3.4  | Design  | Considerations of the MMC                             | 37 |

|   |      | 3.4.1   | Selection of cell capacitance                         | 38 |

|   |      | 3.4.2   | Selection of arm inductance                           | 41 |

|   |      | 3.4.3   | Summary of the MMC parameters                         | 43 |

|   | 3.5  | Contro  | ol Objectives and Suggested Control Scheme            | 43 |

|   |      | 3.5.1   | Control Objectives of an MMC                          | 43 |

|   |      | 3.5.2   | Suggested Control Scheme                              | 44 |

|   | 3.6  | Model   | of the Average Capacitor Voltage Control              | 46 |

|   | 3.7  | Contro  | oller Design of Average Capacitor Voltage             | 48 |

|   |      | 3.7.1   | Inner Loop Design                                     | 49 |

|   |      | 3.7.2   | Outer Loop Design                                     | 51 |

|   | 3.8  | Circula | ating Current Suppression                             | 52 |

|   | 3.9  | Capac   | itor Voltage Balance Control                          | 54 |

|   | 3.10 | Modul   | ation Methods for an MMC                              | 55 |

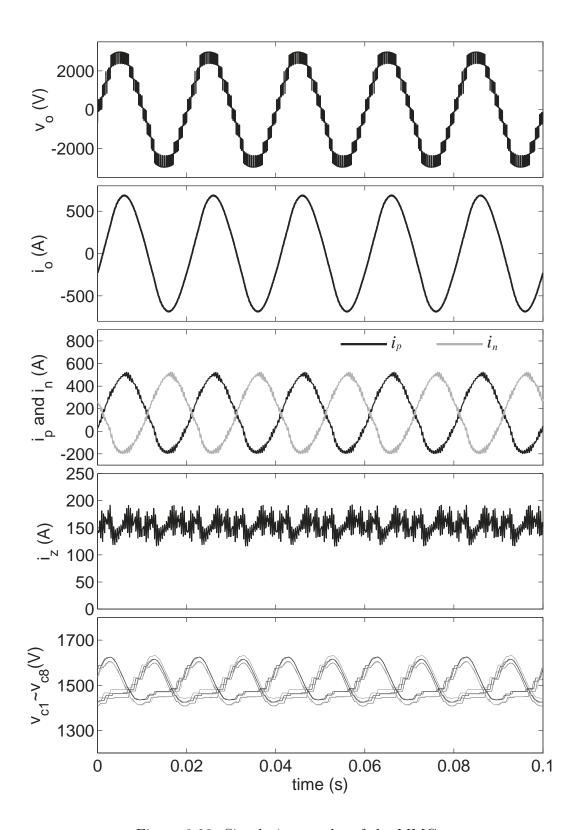

|   | 3.11 | Simula  | ation Results                                         | 57 |

|   | 3.12 | Conclu  | ısion                                                 | 59 |

| 4 | Fau  | lt Dete | ection and Isolation Method 1                         | 61 |

|   | 4.1  | Introd  | uction                                                | 61 |

|   | 4.2  | Switch  | ning Model of an MMC Cell                             | 62 |

|   | 4.3  | Sliding | g Mode Observer for an MMC                            | 63 |

|   | 4.4  | Fault   | Detection and Isolation Using SMO                     | 66 |

|   |                                           | 4.4.1 N    | Infathematical Basis                                        | 66        |  |

|---|-------------------------------------------|------------|-------------------------------------------------------------|-----------|--|

|   |                                           | 4.4.2 F    | lowchart                                                    | 69        |  |

|   | 4.5                                       | Robustne   | ess Analysis                                                | 72        |  |

|   |                                           | 4.5.1 In   | nfluence of Uncertainty and Disturbance on the First        |           |  |

|   |                                           | E          | Equation of $(4.2)$                                         | 73        |  |

|   |                                           | 4.5.2 In   | nfluence of Uncertainty and Disturbance on the Second       |           |  |

|   |                                           | E          | equation of $(4.2)$                                         | 77        |  |

|   |                                           | 4.5.3 S    | imulations of the FDI with Uncertainties and Disturbances . | 78        |  |

|   | 4.6                                       | Conclusio  | on                                                          | 80        |  |

| _ | <b>T</b> D                                | 14 D - 4 4 | Constant Total Address Markland O                           | 34        |  |

| 5 |                                           |            |                                                             | <b>31</b> |  |

|   | 5.1                                       |            | ology of the Improved FDI Method                            |           |  |

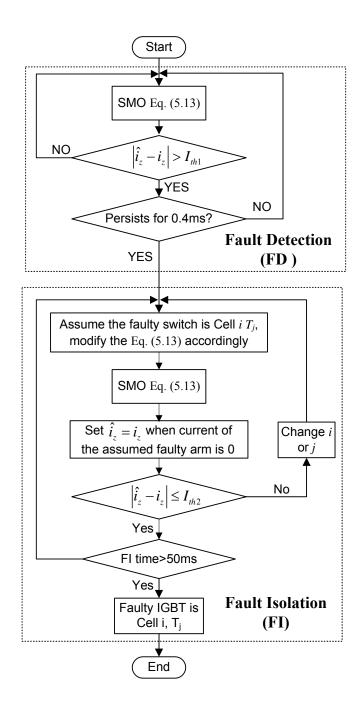

|   | 5.2                                       | Flowchar   | t                                                           | 84        |  |

|   | 5.3                                       | Compens    | sation of Uncertainties and Disturbances                    | 89        |  |

|   | 5.4                                       | Conclusio  | on                                                          | 92        |  |

| 6 | Fault Detection and Isolation Method 3 95 |            |                                                             |           |  |

|   | 6.1                                       | Introduc   | tion                                                        | 95        |  |

|   | 6.2                                       | Mathema    | atical Basis                                                | 97        |  |

|   |                                           | 6.2.1 C    | Convergence of $\hat{v}_{cj}$ and $v_{cj}$                  | 98        |  |

|   |                                           | 6.2.2 C    | Convergence of $\hat{a}_j$ and $a_j$                        | 96        |  |

|   | 6.3                                       | Flowchar   | t                                                           | 01        |  |

|   | 6.4                                       |            | on Results                                                  |           |  |

|   | 6.5                                       | Conclusio  | on                                                          | 07        |  |

| 7 | Exp                                       | perimenta  | al Modular Multilevel Converter 10                          | )9        |  |

|   | 7.1                                       | Introduc   | ${ m tion}$                                                 | 06        |  |

|   | 7.2                                       | Design C   | Considerations for the Experimental MMC Rig                 | 12        |  |

|   |                                           | 7.2.1 C    | Cell Capacitance Scaling                                    | 13        |  |

|   |                                           | 722 A      | rm Inductance Scaling                                       | 1.9       |  |

|   | 7.3 | IGBT Module and the Gate Driver                          |

|---|-----|----------------------------------------------------------|

|   |     | 7.3.1 IGBT Module                                        |

|   |     | 7.3.2 IGBT Gate Driver                                   |

|   |     | 7.3.3 Thermal Design                                     |

|   | 7.4 | Measurement Board                                        |

|   |     | 7.4.1 Current Transducer                                 |

|   |     | 7.4.2 Voltage Transducer                                 |

|   | 7.5 | Control Platform                                         |

|   | 7.6 | Control Implementations for the Experimental MMC         |

|   |     | 7.6.1 Control scheme                                     |

|   |     | 7.6.2 Compensators Digitization                          |

|   |     | 7.6.3 Start-up of the MMC                                |

|   | 7.7 | Experimental Waveforms of the MMC                        |

|   |     | 7.7.1 Experimental Waveforms                             |

|   |     | 7.7.2 Comparison with Simulation Results                 |

|   | 7.8 | Conclusion                                               |

| 8 | Pra | ctical Implementation and Results of the FDI Methods 137 |

|   | 8.1 | Introduction                                             |

|   | 8.2 | Practical Implementation of FDI Method 3                 |

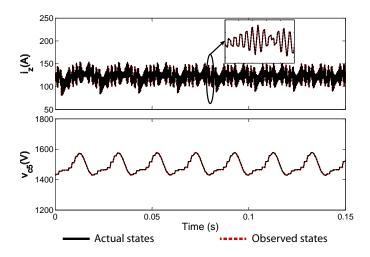

|   |     | 8.2.1 Digital Sliding Mode Observer                      |

|   |     | 8.2.2 Decision Module                                    |

|   | 8.3 | Experimental Results of FDI Method 3                     |

|   | 8.4 | Experimental Results of FDI Method 1                     |

|   | 8.5 | Experimental Results of FDI Method 2                     |

|   | 8.6 | Conclusion                                               |

| 9 | Cor | clusion and Future Works 160                             |

|   | 9.1 | Conclusion                                               |

|   | 9.2 | Future Work                                              |

References 164

# List of Figures

| 2.1  | Multilevel converter classification                                    | Ĝ  |

|------|------------------------------------------------------------------------|----|

| 2.2  | Schematic of a three phase MMC                                         | 10 |

| 2.3  | Industry based survey of component reliability in power converters     | 11 |

| 2.4  | Performance comparisons of the three main types of capacitors for      |    |

|      | DC-link applications                                                   | 14 |

| 2.5  | Classification of FDI methods                                          | 17 |

| 2.6  | Basic concept of parity space and observer based FDI techniques        | 19 |

| 2.7  | Typical hardware fault detection for an IGBT                           | 21 |

| 2.8  | Single-dimensional motion of a unit mass                               | 24 |

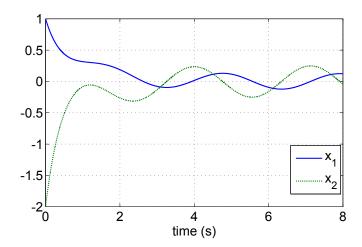

| 2.9  | Response of $x_1, x_2$ with linear feedback                            | 25 |

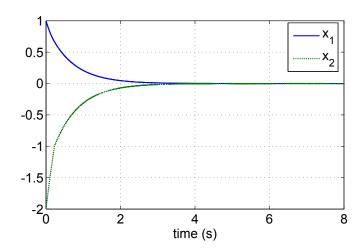

| 2.10 | Response of $x_1, x_2$ with sliding mode control                       | 26 |

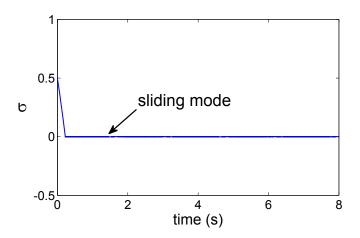

| 2.11 | Sliding variable $\sigma$                                              | 27 |

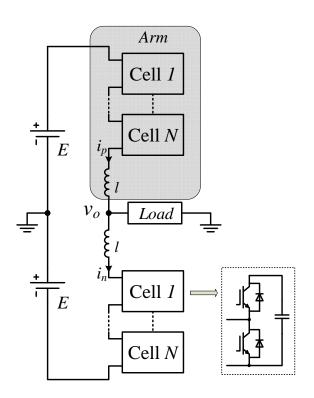

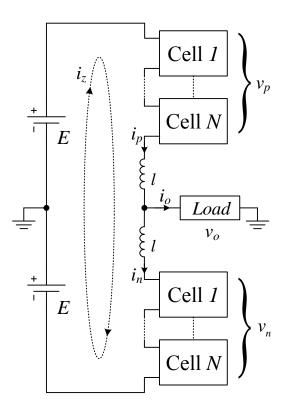

| 3.1  | Schematic of an MMC (single phase)                                     | 32 |

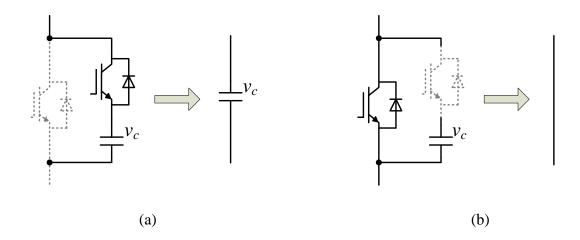

| 3.2  | States of a cell: (a) inserted—the upper switch is on, (b)bypassed—the |    |

|      | lower switch is on                                                     | 32 |

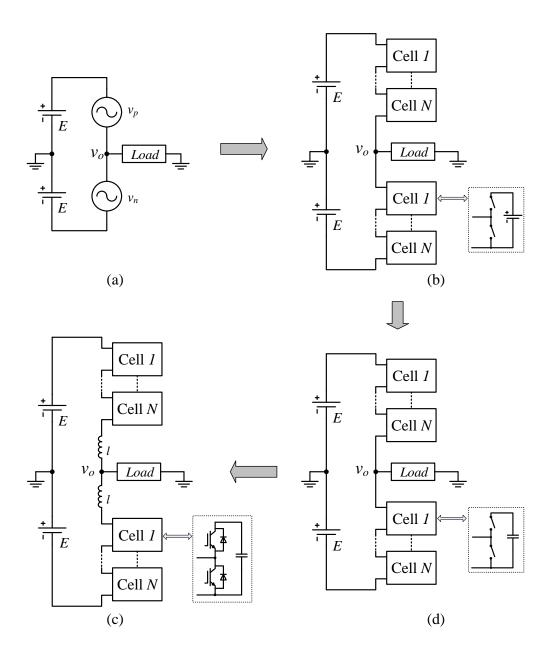

| 3.3  | Step by step introduction of the operating principle of MMC            | 33 |

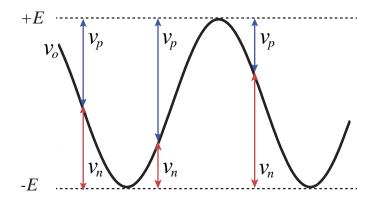

| 3.4  | Relationship of $v_p$ , $v_n$ and $v_o$                                | 34 |

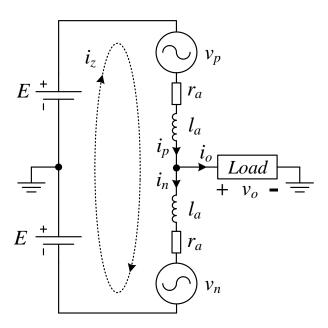

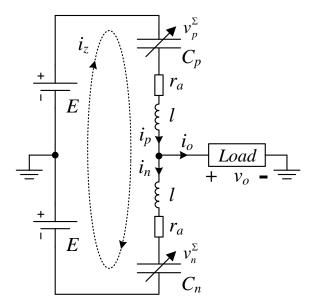

| 3.5  | Model of the MMC                                                       | 35 |

| 3.6  | Diagram of a capacitor                                                 | 38 |

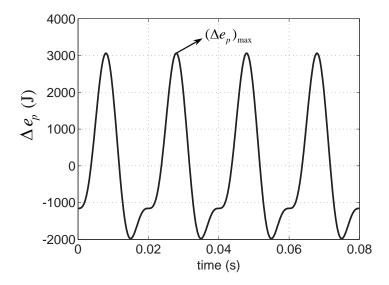

| 3.7  | Circuit diagram of a single phase MMC                                  | 39 |

| 3.8  | The energy variation of the upper arm capacitors over time             | 41 |

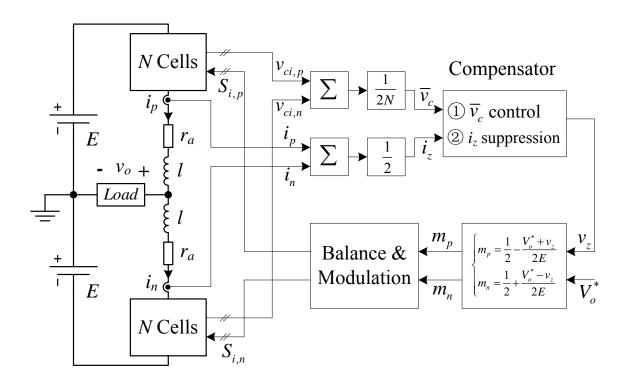

| 3.9  | A control scheme of the MMC                                                 | 45 |

|------|-----------------------------------------------------------------------------|----|

| 3.10 | MMC model with variable capacitance                                         | 46 |

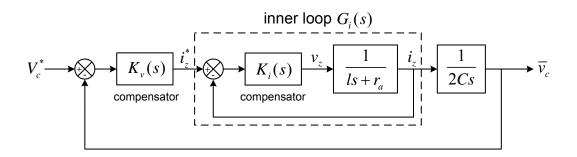

| 3.11 | Control block diagram of the average capacitor voltage                      | 49 |

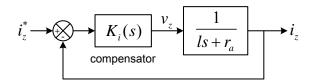

| 3.12 | Control block diagram of inner loop                                         | 49 |

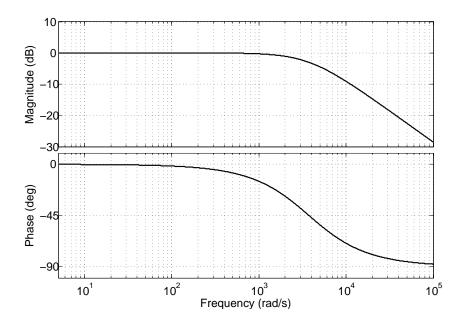

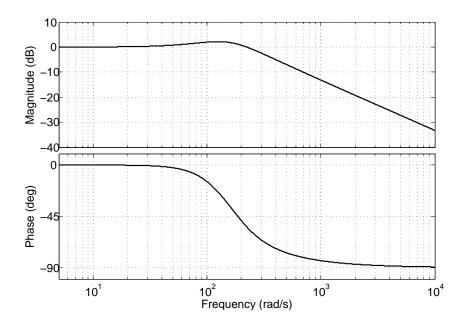

| 3.13 | Bode diagram of the closed inner loop                                       | 50 |

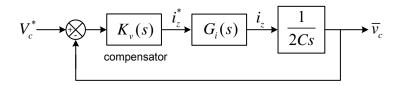

| 3.14 | Control block diagram of outer loop                                         | 51 |

| 3.15 | Bode diagram of the closed outer loop                                       | 52 |

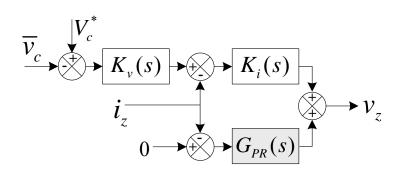

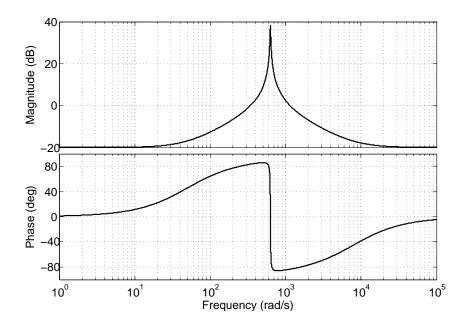

| 3.16 | Control block diagram of the $i_z$ suppression                              | 53 |

| 3.17 | Bode diagram of the PR controller                                           | 54 |

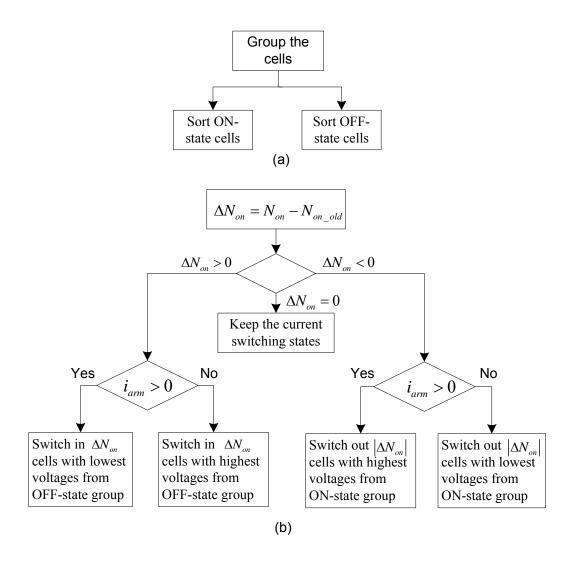

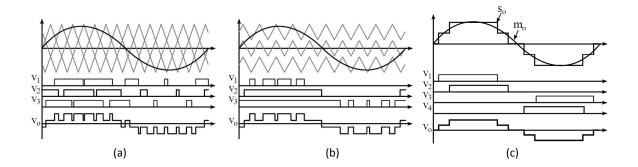

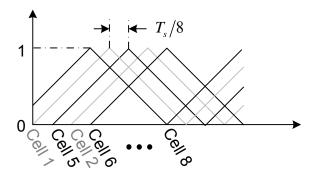

| 3.18 | Dual sort algorithm                                                         | 56 |

| 3.19 | Balance compensation                                                        | 56 |

| 3.20 | Commonly used modulation technique for MMC                                  | 57 |

| 3.21 | The phase-shifted carriers used in this work                                | 57 |

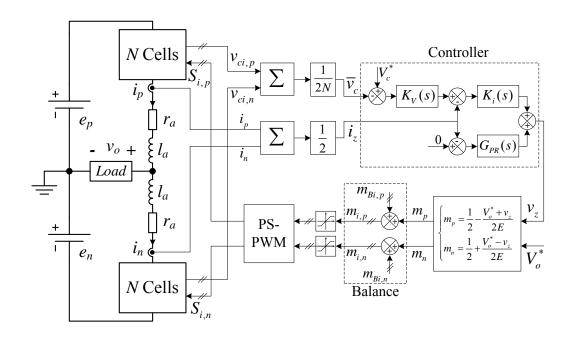

| 3.22 | The more detailed control scheme of the MMC                                 | 58 |

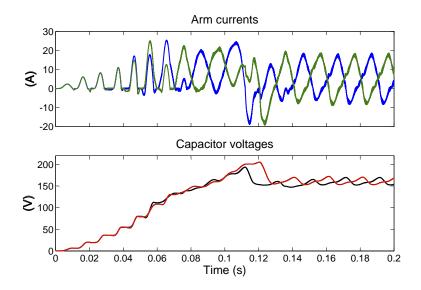

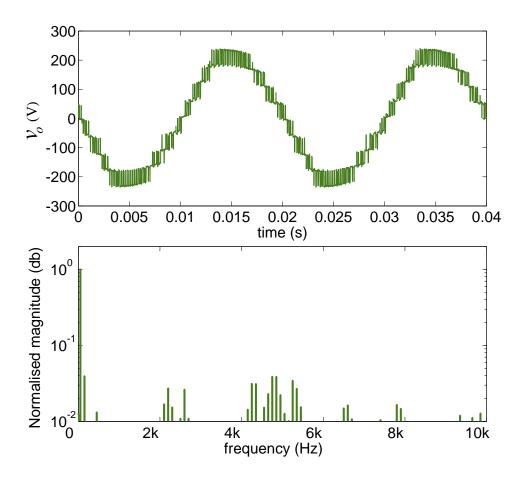

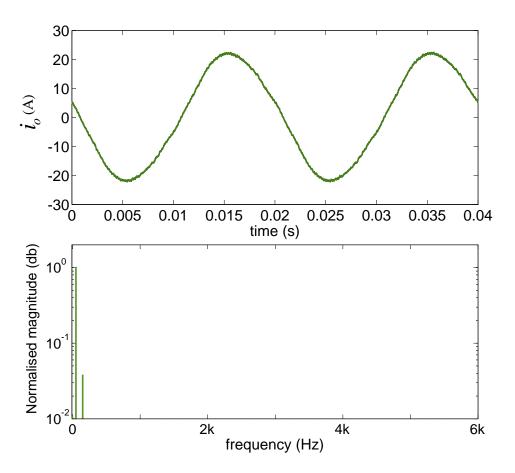

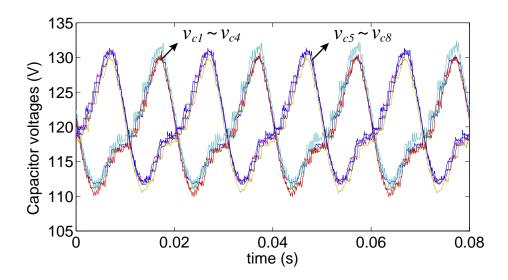

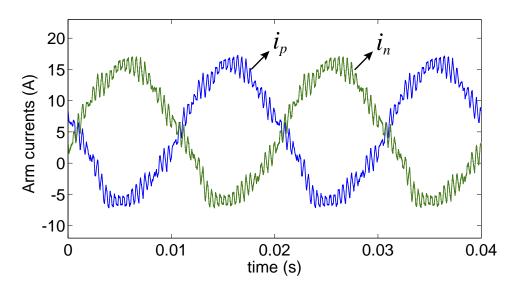

| 3.23 | Simulation results of the MMC                                               | 60 |

| 4.1  | Switching model of half-bridge                                              | 62 |

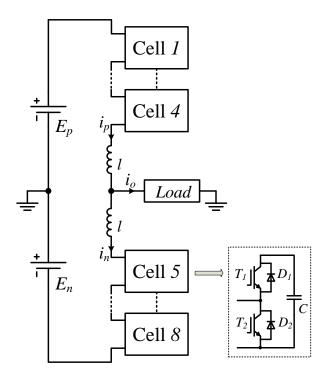

| 4.2  | The single-phase eight-cell MMC used for simulation                         | 64 |

| 4.3  | Simulation waveforms of the sliding mode observer for the MMC               | 66 |

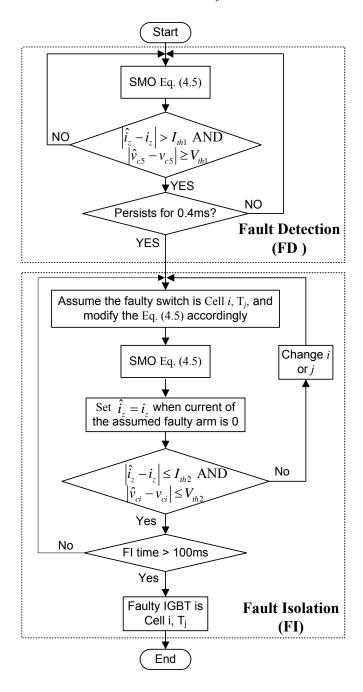

| 4.4  | Flowchart of the FDI algorithm for the MMC                                  | 68 |

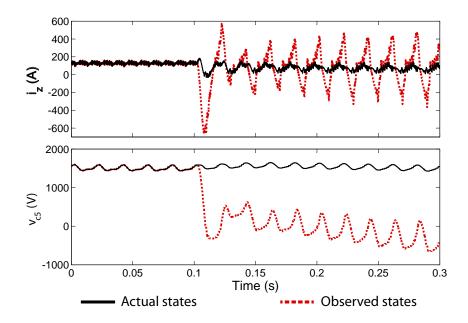

| 4.5  | Simulation results of the observed states when an open-circuit fault        |    |

|      | occurs at $Cell\ 6, T_1$ an 0.1s                                            | 70 |

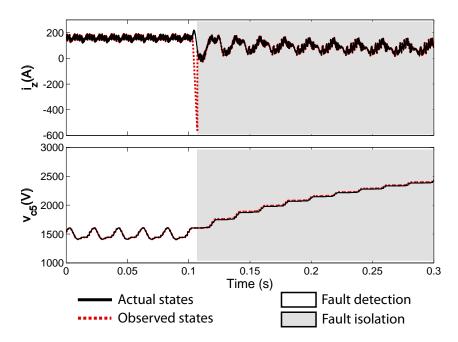

| 4.6  | Simulation results of FDI: the open-circuit fault occurs at $Cell\ 6, T_1$  |    |

|      | and the assumed faulty switch is $Cell\ 6, T_1.$                            | 70 |

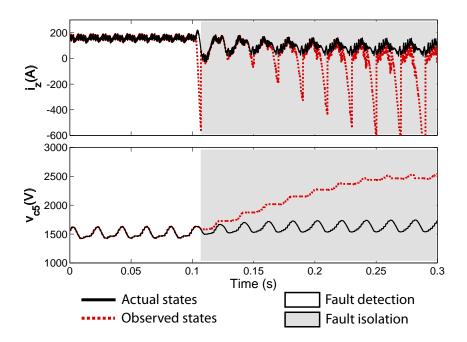

| 4.7  | Simulation results of FDI: the open-circuit fault occurs at $Cell\ 6, T_1,$ |    |

|      | while the assumed faulty switch is $Cell\ 7, T_1$                           | 71 |

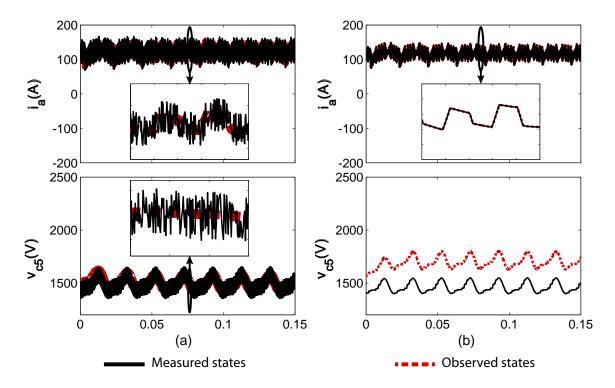

| 4.8  | Robustness simulation of the SMO: (a) only with random measured             |    |

|      | error (b) with parameter uncertainties and systematic measured error        | 75 |

| 4.9  | Robustness simulation of the SMO with parameter uncertainty on                     |    |

|------|------------------------------------------------------------------------------------|----|

|      | capacitance                                                                        | 78 |

| 4.10 | Simulation results of FDI with uncertainties and disturbances: open-               |    |

|      | circuit fault at $Cell~6, T_1$ and assumed faulty device at $Cell~6, T_1$          | 79 |

| 4.11 | Simulation results of FDI with uncertainties and disturbances: open-               |    |

|      | circuit fault at $Cell\ 6, T_1$ and assumed faulty device at $Cell\ 7, T_1.$       | 79 |

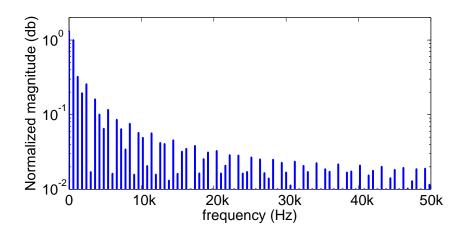

| 5.1  | spectrum of the switching component $\sum_{i=1}^{8} S_i v_{ci}$                    | 83 |

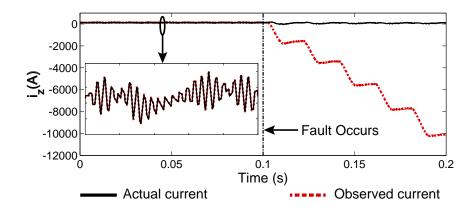

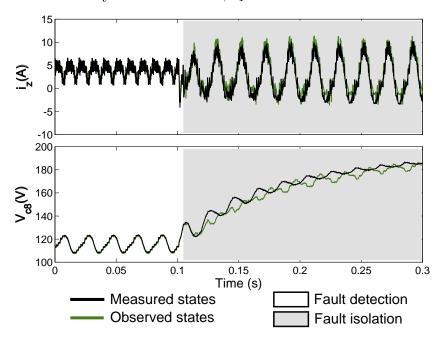

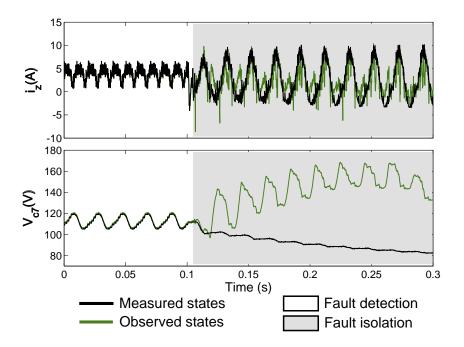

| 5.2  | Simulation results of the $\hat{i}_z$ and $i_z$ where an open-circuit fault occurs |    |

|      | at 0.1s                                                                            | 84 |

| 5.3  | Flowchart of the improved FDI method for an MMC                                    | 85 |

| 5.4  | Simulation results of FDI: the open-circuit fault occurs at $Cell\ 1, T_1$         |    |

|      | and the assumed faulty switch is $Cell\ 1, T_1.$                                   | 86 |

| 5.5  | Simulation results of FDI: the open-circuit fault occurs at $Cell\ 1, T_1$         |    |

|      | and the assumed faulty switch is $Cell\ 2, T_1.$                                   | 86 |

| 5.6  | Simulation results of FDI under light load: the open-circuit fault                 |    |

|      | occurs at $Cell\ 1, T_1$ and the assumed faulty switch is $Cell\ 1, T_1$           | 87 |

| 5.7  | Simulation results of FDI under light load: the open-circuit fault                 |    |

|      | occurs at $Cell\ 1, T_1$ and the assumed faulty switch is $Cell\ 2, T_1$           | 87 |

| 5.8  | Simulation results of FDI: the open-circuit faults occur at $Cell\ 2, T_1,$        |    |

|      | $Cell\ 3, T_2$ and the assumed faulty devices are the actual ones                  | 88 |

| 5.9  | Simulation results of FDI: the open-circuit faults occur at $Cell\ 2, T_1,$        |    |

|      | $Cell\ 3, T_2$ and the assumed faulty devices are $T_1$ and $T_2$ of $Cell\ 3.$    | 88 |

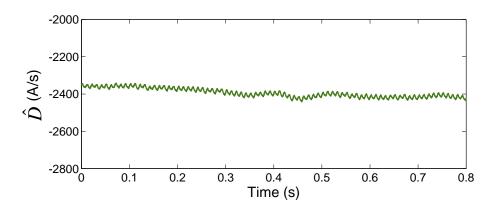

| 5.10 | Simulation results of $\hat{D}$ (estimated value of the uncertainties and          |    |

|      | disturbances)                                                                      | 91 |

| 5.11 | Simulation results of FDI without compensation of uncertainties and                |    |

|      | noise: open-circuit fault at $Cell\ 1, T_1$ and assumed faulty device at           |    |

|      | $Cell\ 1, T_1.$                                                                    | 92 |

| 5.12 | Simulation results of FDI without compensation of uncertainties and      |     |

|------|--------------------------------------------------------------------------|-----|

|      | noise: open-circuit fault at $Cell\ 1, T_1$ and assumed faulty device at |     |

|      | Cell $2, T_1$                                                            | 92  |

| 5.13 | Simulation results of FDI with compensation of uncertainties and         |     |

|      | noise: open-circuit fault at $Cell\ 1, T_1$ and assumed faulty device at |     |

|      | Cell $1, T_1, \ldots, T_n$                                               | 93  |

| 5.14 | Simulation results of FDI with compensation of uncertainties and         |     |

|      | noise: open-circuit fault at $Cell\ 1, T_1$ and assumed faulty device at |     |

|      | Cell $2, T_1$                                                            | 93  |

| 6.1  | Diagram of the cell of an industrial MMC                                 | 96  |

| 6.2  | Schematic of an eight-cell single phase MMC                              | 97  |

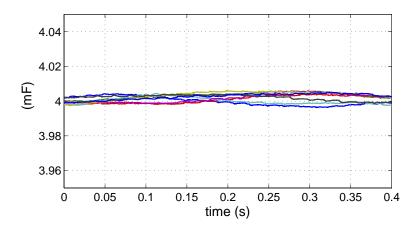

| 6.3  | Simulation results of the observed and actual capacitor voltages         | 100 |

| 6.4  | Simulation results of the estimated capacitance (the actual              |     |

|      | capacitances are 4 mF)                                                   | 101 |

| 6.5  | Flowchart                                                                | 102 |

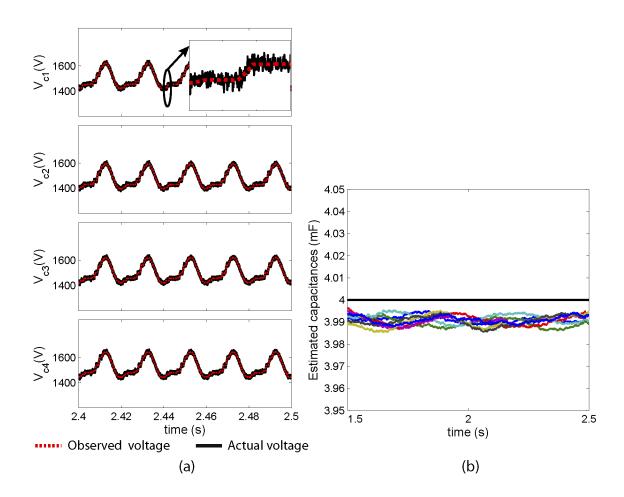

| 6.6  | Simulation results with 3% input noise: (a) observed and actual          |     |

|      | capacitor voltages (upper arm), (b) estimated capacitances (actual       |     |

|      | capacitances are 4 mF)                                                   | 103 |

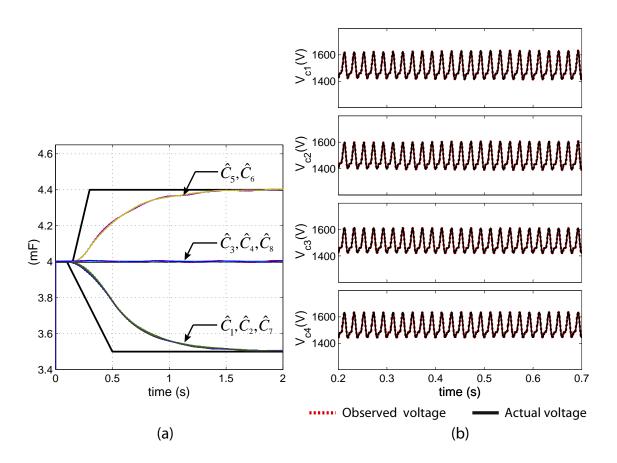

| 6.7  | Simulation results when there is variation of capacitance: (a)           |     |

|      | estimated capacitances, (b)<br>observed and actual voltages              | 104 |

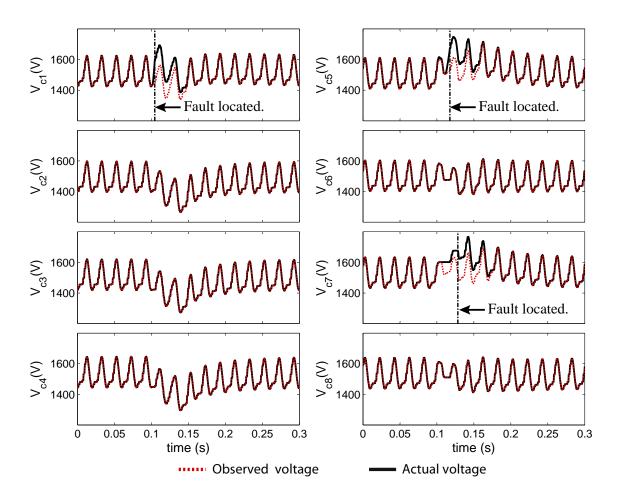

| 6.8  | Simulation result of the FDI when the output power is 1 MW: open-        |     |

|      | circuit faults occur in Cell 1, 5 and 7                                  | 105 |

| 6.9  | Simulation result of the FDI when the output power is 0.2 MW: open-      |     |

|      | circuit faults occur in Cell 2 and 6                                     | 106 |

| 6.10 | Simulation result of the FDI when the output power is 0.1 MW: open-      |     |

|      | circuit faults occur in Cell 8                                           | 107 |

| 7.1  | Diagram of the experimental rig                                          | 110 |

| 7.2  | A photograph of the experimental system                                  | 110 |

| 7.3  | A photograph of the two isolation transformers                              | 11 |

|------|-----------------------------------------------------------------------------|----|

| 7.4  | Diagram of the MMC for Systems 1 and 2                                      | 12 |

| 7.5  | Power module used in this work                                              | 15 |

| 7.6  | A photograph of the assembled power module                                  | 15 |

| 7.7  | Circuit diagram of the gate driver for an IGBT                              | 16 |

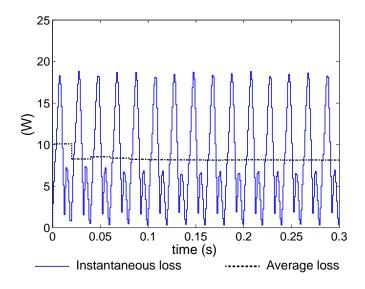

| 7.8  | Simulated power loss the cell using PLECS                                   | 17 |

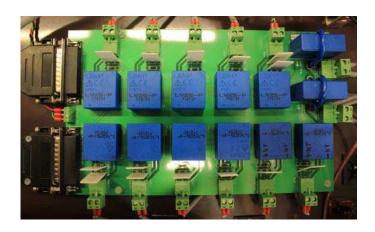

| 7.9  | A photograph of the measurement board                                       | 18 |

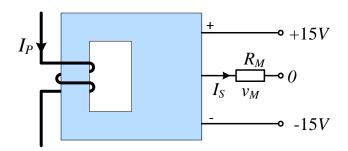

| 7.10 | Connection diagram for the current transducer LA55-P                        | 19 |

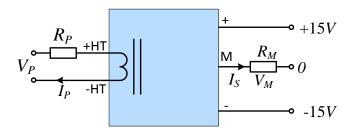

| 7.11 | Connection diagram for the voltage transducer LV25-P                        | 20 |

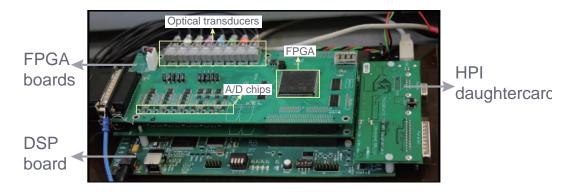

| 7.12 | Photography of the control platform                                         | 21 |

| 7.13 | The control scheme of the MMC rig                                           | 22 |

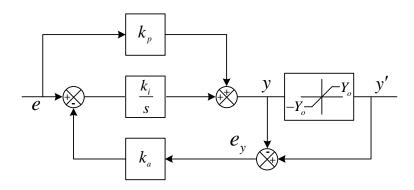

| 7.14 | Balance compensator                                                         | 24 |

| 7.15 | PI controller with anti-windup                                              | 25 |

| 7.16 | Simulated waveforms of the start-up of the MMC                              | 26 |

| 7.17 | Experimental output voltage $v_o$ waveform (Top) and the associated         |    |

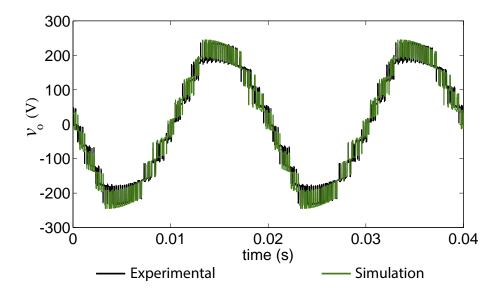

|      | spectrum (Bottom) of the MMC rig                                            | 28 |

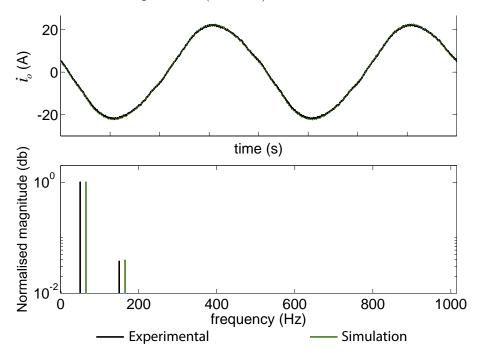

| 7.18 | Experimental output current $i_o$ waveform (Top) and associated             |    |

|      | spectrum (Bottom) of the MMC rig                                            | 29 |

| 7.19 | Experimental waveform of the cell capacitor voltages $v_{c1} \sim v_{c8}$ 1 | 30 |

| 7.20 | Experimental waveform of the arm currents $i_p$ and $i_n$                   | 30 |

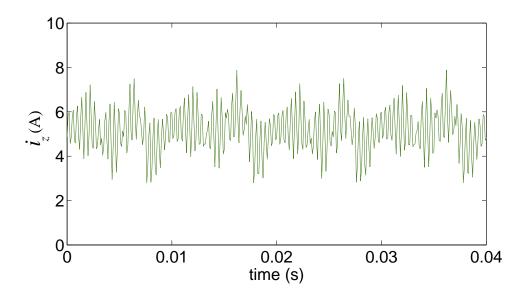

| 7.21 | Experimental waveform of the circulating current $i_z$                      | 31 |

| 7.22 | Comparison of the experimental and simulation MMC output voltage            |    |

|      | waveforms $(v_o)$                                                           | 31 |

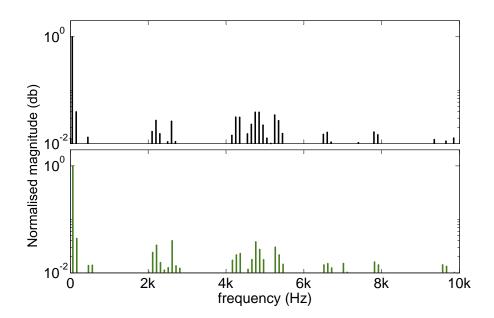

| 7.23 | Spectrum comparison of the experimental MMC output voltage (Top)            |    |

|      | and simulation associated spectrum (Bottom)                                 | 32 |

| 7.24 | Comparison of the experimental and simulation MMC output current            |    |

|      | (Top) and associated spectrum (Bottom)                                      | 32 |

| 7.25 | Comparison of the experimental and simulation arm currents ( $i_p$ and      |    |

|      | <i>i</i> <sub>n</sub> )                                                     | 33 |

| 7.26 | Spectrum comparison of the of the experimental and simulation upper          |

|------|------------------------------------------------------------------------------|

|      | arm currents $(i_p)$                                                         |

| 7.27 | Comparison of the experimental (Top) and simulation (Bottom)                 |

|      | circulating current $(i_z)$                                                  |

| 7.28 | Comparison of experimental (Top) and simulation (Bottom) cell                |

|      | capacitor voltages                                                           |

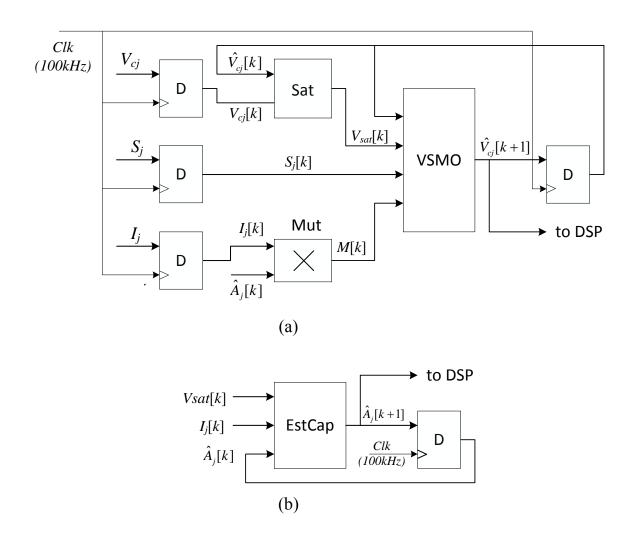

| 8.1  | Block diagram of the digital sliding mode observer (8.7) 140                 |

| 8.2  | Decision module of the FDI method 3                                          |

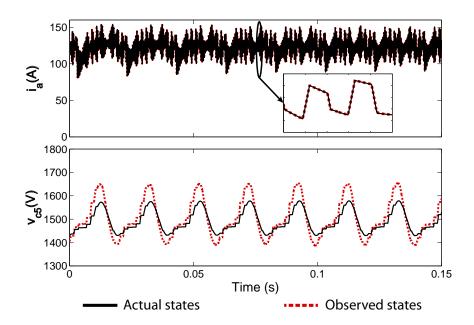

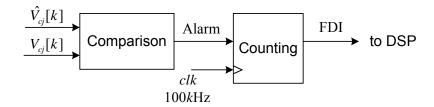

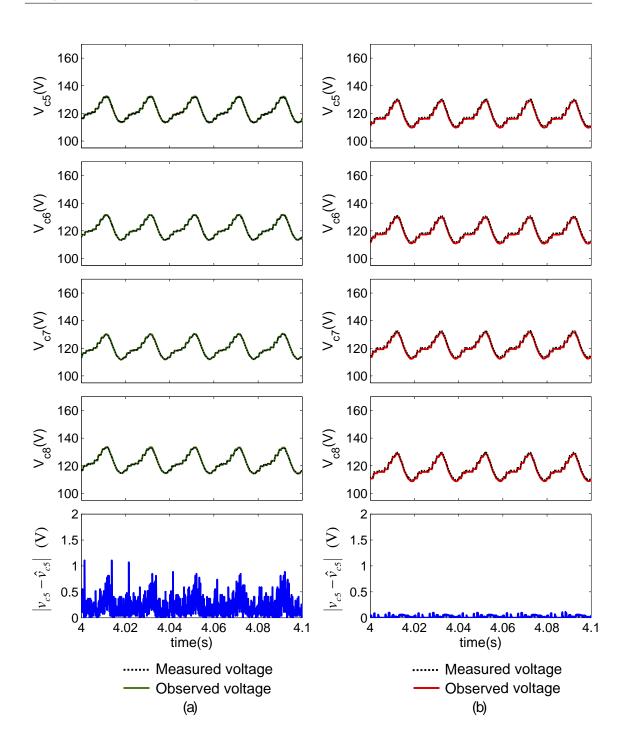

| 8.3  | Comparison of the capacitance estimation: (a) experimental results,          |

|      | (b) simulation results                                                       |

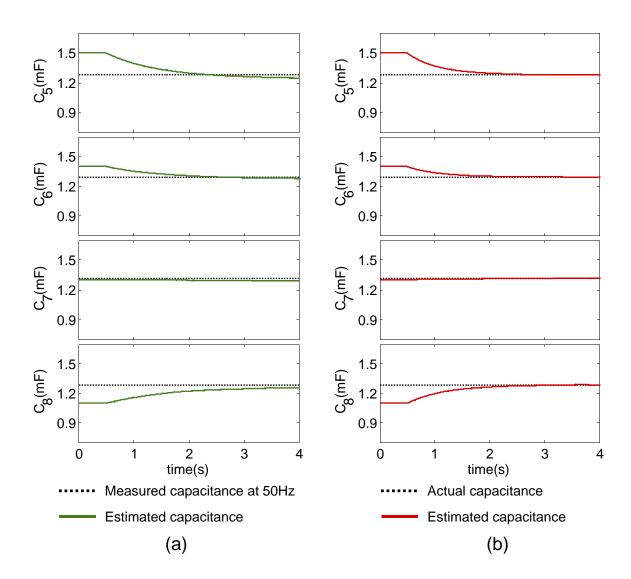

| 8.4  | Comparison of the voltage observation at the fault free condition:           |

|      | (a) experimental results, (b) simulation results                             |

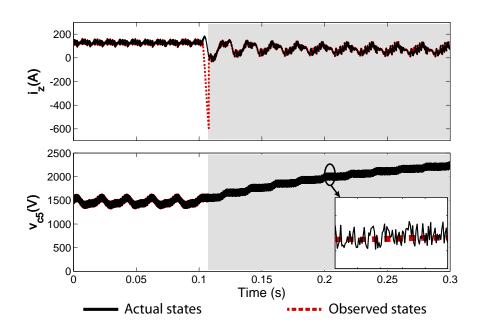

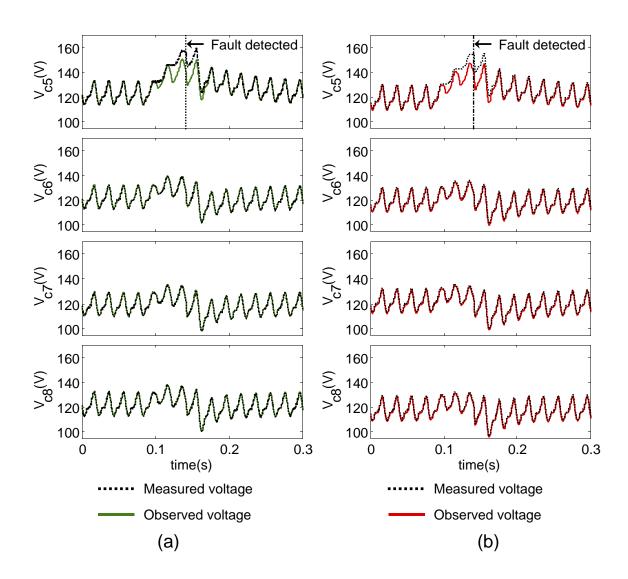

| 8.5  | Comparison of the voltage observation with open-circuit faults at Cell       |

|      | 5: (a)experimental results, (b)simulation results                            |

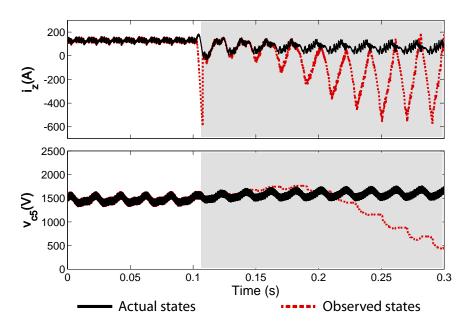

| 8.6  | Comparison of the voltage observation with open-circuit faults at Cell       |

|      | 6 and 8: (a)<br>experimental results, (b)<br>simulation results              |

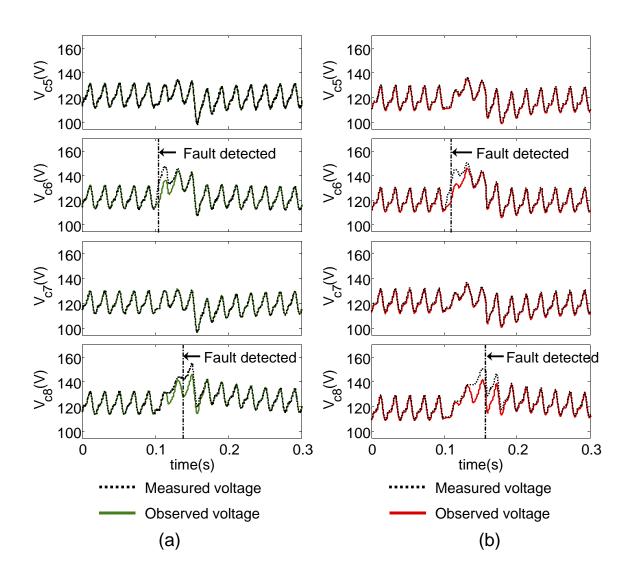

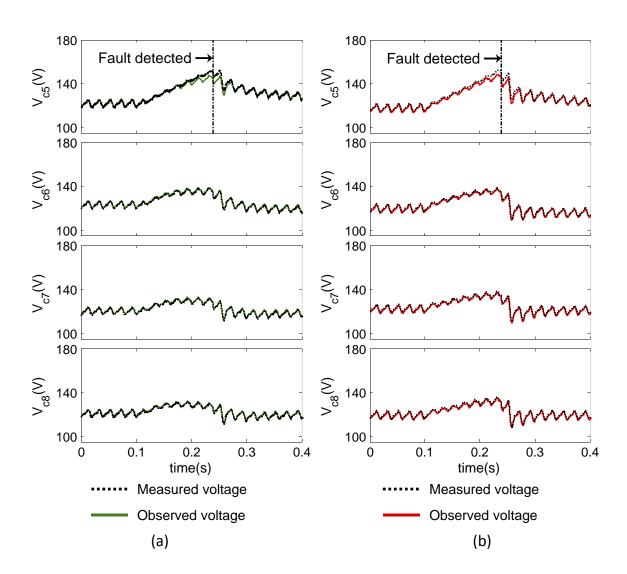

| 8.7  | Comparison of the voltage observation with open-circuit faults when          |

|      | the output power is 0.83 kW: (a) experimental results, (b) simulation        |

|      | results                                                                      |

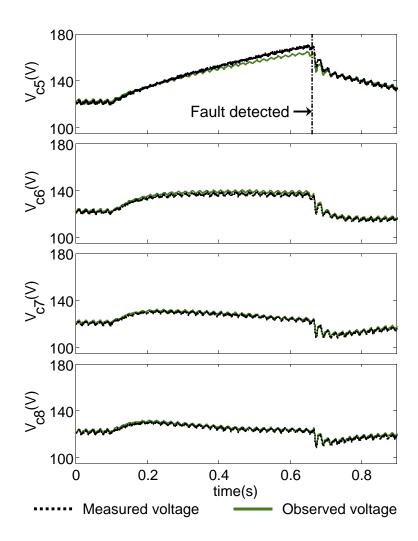

| 8.8  | Experimental results of voltage observation with open-circuit faults         |

|      | when the output power is 0.42 kW: (a) experimental results,                  |

|      | (b)simulation results                                                        |

| 8.9  | Experimental results of the observer at fault free condition 149             |

| 8.10 | Experimental results of the observed an measured states in the               |

|      | presence of an open-circuit fault                                            |

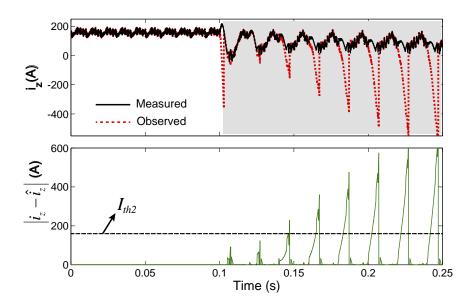

| 8.11 | Experimental results of the FDI: open-circuit fault occurs at $Cell\ 6, T_1$ |

|      | and the assumed faulty switch is $Cell\ 6, T_1.$                             |

| 8.12 | Experimental results of the FDI: open-circuit fault occurs at                    |

|------|----------------------------------------------------------------------------------|

|      | Cell 6, $T_1$ , while the assumed faulty switch is Cell 7, $T_1$                 |

| 8.13 | Experimental results of the FDI: open-circuit fault occurs at $Cell~8, T_2$      |

|      | and the assumed faulty switch is $Cell~8, T_2.$                                  |

| 8.14 | Experimental results of the FDI: open-circuit fault occurs at                    |

|      | Cell $8, T_2$ , while the assumed faulty switch is Cell $7, T_2, \ldots, 152$    |

| 8.15 | Experimental results of $\hat{D}$ (estimated uncertainties and disturbances) 153 |

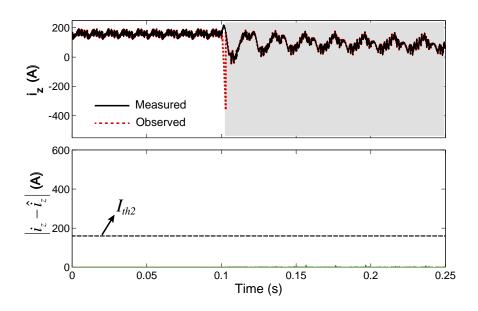

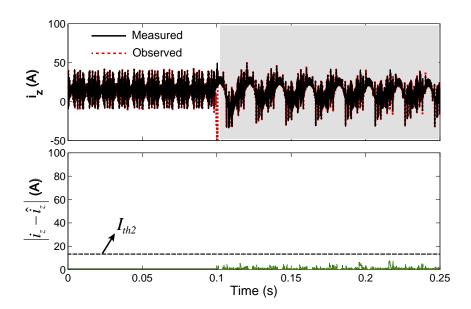

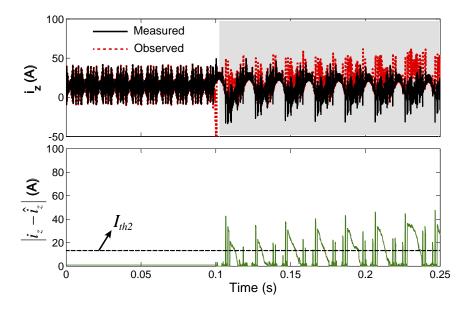

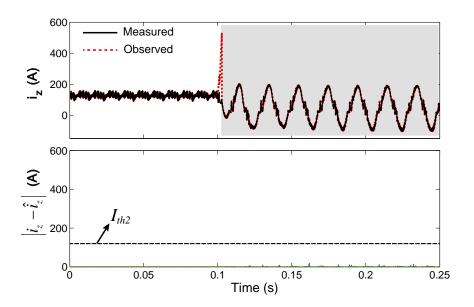

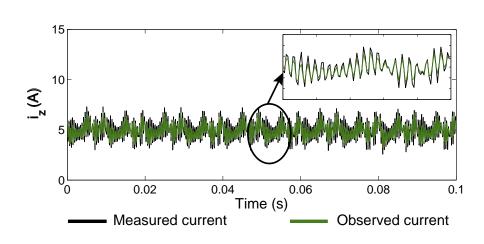

| 8.16 | Experimental results of $i_z$ and $\hat{i}_z$ when the MMC is fault free 153     |

| 8.17 | Experimental results of $i_z$ and $\hat{i}_z$ when an open-circuit fault occurs  |

|      | at an IGBT at 0.1s                                                               |

| 8.18 | Experimental results of the FDI: an open-circuit fault occurs at                 |

|      | Cell $6, T_2$ and the assumed faulty device is Cell $6, T_2, \ldots, 154$        |

| 8.19 | Experimental results of the FDI: an open-circuit fault occurs at                 |

|      | Cell $6, T_2$ , while the assumed faulty device is Cell $7, T_2, \ldots, 155$    |

| 8.20 | Experimental results of the FDI under light load: open-circuit fault             |

|      | occurs at $Cell\ 5, T_1$ and the assumed faulty switch is $Cell\ 5, T_1.$ 155    |

| 8.21 | Experimental results of the FDI: open-circuit fault occurs at                    |

|      | Cell 5, $T_1$ , while the assumed faulty switch is Cell 8, $T_1$                 |

| 8.22 | Experimental results of the automatic FDI                                        |

# List of Tables

| 2.1 | Recent HVDC projects based on MMC                                |

|-----|------------------------------------------------------------------|

| 2.2 | Wire-out mechanisms for the three main DC link capacitors 14     |

| 2.3 | Typical end-of-life criteria for capacitors                      |

| 3.1 | Circuit parameters used in the simulation                        |

| 4.1 | Switching state $S$ in normal condition                          |

| 4.2 | Switching state $S$ in fault condition                           |

| 6.1 | Switching state $S$ of a cell                                    |

| 6.2 | Observer gains when the MMC operating under full load 100        |

| 7.1 | List of key components                                           |

| 7.2 | Circuit parameters of the experimental rig                       |

| 7.3 | Junction to case thermal impedance of F4-50R06W1E3 module $117$  |

| 7.4 | Compensator gains of control scheme for the experimental rig 123 |

| 8.1 | Parameters of digital SMO (8.6)                                  |

| 8.2 | Measured and estimated capacitances of cell capacitors           |

# Chapter 1

# Introduction

## 1.1 Motivation

Some applications of power electronics, such as electrical energy transmission and large machine drives, require operation at voltages far beyond the rating of available power semi-conductor devices [1]. One way to meet these voltage requirements is to use multilevel converter topologies. Besides the high voltage capability, multilevel converters can generate multi-step output voltages, with lower distortion compared to conventional two level voltage source converters (VSCs). These properties make multilevel converters very attractive in some applications.

Over recent years three classical multilevel converter topologies, the neutral point clamped (NPC) [2], cascaded H-bridge (CHB) [3] and flying capacitor (FC) [4], have been widely accepted by the industry. Newer topologies such as the three-level active NPC (3L-ANPC) [5] and the modular multilevel converter (MMC) [6] have also found practical applications [7]. Among these new topologies the MMC is currently considered as the state-of-art multilevel converter [8] and the most promising topology in the area of high voltage applications such as high voltage direct current (HVDC) transmission [9].

Power semi-conductor devices and capacitors are the most voltage sensitive

components in a power converter [10, 11]. A practical multilevel converter usually comprises a large number of power semi-conductor devices and capacitors, for instance the MMC in Trans Bay Cable project [12] contains more than 2400 insulated-gate bipolar transistors (IGBTs) and 1200 capacitors [13]. With large numbers of these sensitive components the chance of a failure in a multilevel converter is much larger than in conventional low voltage power converters.

In the presence of a failure of a power semi-conductor device or a capacitor, a multilevel converter will operate with distorted output voltages and currents. High voltages and currents caused by the failed devices may also cause secondary damage to other devices if the faulty operation is allowed and a shut down of the converter may follow. To improve the availability of a multilevel converter it is important that any device failures are detected and located quickly and actions taken to reconfigure the converter.

Fault detection and isolation (FDI) deals with system monitoring with two tasks: detecting anomalous situations (fault detection) and addressing their causes (fault isolation) [14, 15]. In this work three FDI methods are proposed to improve the availability of an MMC. The methodology used in this work is based on a sliding mode observer (SMO). An SMO is a mathematical replica of a system used to estimate the system's internal states and has some desirable features such as insensitivity to external disturbances and internal parameter uncertainties. These advantages make the SMO a good candidate for applications in FDI.

There are two types of failures seen in fully controlled power semi-conductor devices: the short-circuit fault (the device remains ON regardless of the gate drive signal) and open-circuit fault (the device remains OFF regardless of the gate drive signal). Short-circuit faulty power devices are often detected using hardware methods such as de-saturation detection integrated within a gate driver [16]. This work concentrates on FDI for open-circuit faults in power semi-conductor devices in MMCs. In addition, this work also considers status monitoring for the capacitors.

## 1.2 Contribution

Three methods based on SMOs are proposed in this thesis for fault detection and isolation in an MMC. These methods utilize input signals which are already available as measurement inputs to the control system and require no additional measurement elements. These methods are detailed as follows.

- Method 1 is capable of detecting and locating an open-circuit fault of a power semi-conductor device in an MMC. An SMO is employed to observe the circulating current and capacitor voltage in an MMC. Normally the observed states converge to the corresponding measured states; but in the presence of a fault the observed states will diverge from the measured states. The fault can then be detected by comparing the difference between the observed and measured states with threshold values. The fault can be located by employing an assumption-verification process. If it is assumed that one of the power semi-conductor devices is faulty, the observer can be modified accordingly and the observed states are compared to the measured states again. The observed states converge to the measured states only if the assumption regarding the location of the fault is correct. According to the experimental results, an open-circuit faulty power device in an MMC operating under full load can be detected within 100ms.

- Method 2 is an improved version of the method 1. This method is simpler with only one SMO equation and can detect an open-circuit fault in an MMC operating under different load conditions within 50ms. Similar to method 1 the occurrence of an open-circuit faulty device can then be detected by comparing the difference between the observed and measured circulating currents with a threshold value. The fault can be located by employing an assumption-verification process. Additionally a technique based on the observer injection term is introduced to estimate the value of the uncertainties and disturbances, this estimated value can be used to

compensate the uncertainties and disturbances. As a result, the proposed FDI scheme can detect and locate an open-circuit fault in a power semiconductor device while ignoring parameter uncertainties, measurement error and other bounded disturbances.

• Method 3 is used to detect and isolate multiple device faults and monitor the status of the capacitors. An SMO is employed for each cell of the MMC to estimate the capacitor voltage and capacitance. The observed voltage is used to detect and isolate open-circuit faults in the power semi-conductor devices. A fault caused by power devices is identified if the difference between the observed and the corresponding measured voltage is larger than a given threshold level. The estimated capacitance is used to monitor the status of a capacitor as capacitor degradation can be indicated by the changes in capacitance.

It is noted that although only investigated for an MMC, these three methods can be applied to other multilevel converters by employing similar analysis and principles.

## 1.3 Thesis Structure

The thesis is structured as follows.

Chapter 2 introduces the multilevel converter topology, fault detection and isolation as well as the sliding mode observer. The classification and application of multilevel converters is briefly introduced. Components used in these converters including power semi-conductor devices and capacitors are discussed and the failure mechanisms associated with IGBTs and capacitors are introduced. The theory of FDI, as a branch of control engineering, is presented and the existing methods of FDI for multilevel converters are discussed. This chapter ends with an introduction to sliding mode control and observers.

In Chapter 3 the operating principles, mathematical model, component selection and controller design of a single phase MMC are presented. The operating principle of an MMC is introduced in an intuitive way and then the mathematical model is discussed. A scheme to control the average capacitor voltage and suppress the circulating current is presented. The operation of the complete control scheme is verified using simulation results.

In Chapter 4 the FDI method 1 is presented. This method can be used to detect and locate an open-circuit device fault. The chapter begins with a model of an MMC cell both in normal and faulty operating conditions. Then an SMO is described which is used to observe the circulating current and capacitor voltages. Based on these two frameworks, an algorithm for fault detection and isolation is introduced. The robustness analysis of this algorithm is considered. The proposed algorithm and the robustness analysis are validated using simulation results.

In Chapter 5 the FDI method 2 is presented. This method is an improved version of the FDI method 1. The mathematical basis, flowchart as well as the considerations of the observer gains and threshold values are given. A technique is presented to estimate the value of parameter uncertainties, measurement noise and other disturbances. This estimated value is used to compensate for uncertainties and disturbances to achieve a robust FDI. Simulation results under different load conditions are provided to validate the proposed method.

In Chapter 6 the FDI method 3 is proposed. This method can be used for the detection and isolation of multiple open-circuit faults and for monitoring the status of the cell capacitors. SMOs are introduced to estimate the capacitor voltages and capacitances of each cell. The convergence between the estimated and actual states are mathematically described. The automatic FDI and capacitance monitoring are presented and the effectiveness of the proposed method is verified with simulation results.

In Chapter 7 the design of both the hardware and software for the experimental MMC are described. The hardware including the DC power supply, MMC cells,

measurement board and control platform are introduced. Practical issues in the implementation of the control software are also discussed. Experimental waveforms for the output voltage, output current, circulating current and capacitor voltages are shown and compared to the simulation results.

In Chapter 8 the practical implementation of the proposed FDI methods and the corresponding experimental results are presented. The implementation procedure for the digital SMO using the Verilog hardware description language is described. Experimental results of the FDI methods are compared with the corresponding simulation results.

In Chapter 9 conclusions, potential applications of the proposed techniques and future work are discussed.

# Chapter 2

# Literature Review

This chapter presents a brief literature review on the topics of this thesis. The first section introduces multilevel converters and particularly the modular multilevel converter (MMC). In Section 2.2, the components used in a power converter and their failure mechanisms are discussed. A literature review of fault detection and isolation (FDI) is given in Section 2.3. Lastly Section 2.4 introduces sliding mode control and observers, the methodology used for FDI in the work discussed in this thesis.

## 2.1 Multilevel Converters

To use a power semiconductor device in an application in which the operating voltage exceeds the device rating one can either series connect devices or use a multilevel converter. By connecting power semi-conductor devices in series and driving them using one control signal the series connected power semi-conductor devices can work like one device with a much higher voltage rating. Using series-connected power semi-conductor devices conventional converter topology with a simple control strategy can be used, however there are two obvious challenges in applying this technology. The first is how to distribute the voltage evenly between the series connected devices during switching and voltage blocking.

The second challenge is how to deal with open-circuit failures in the devices. A few HVDC projects, ranging from 3MW to 400MW, based on series connected IGBTs have been commissioned [17].

The second approach uses more complex converter topologies called multilevel converters. The control of a multilevel converter is generally more complex than for conventional power converters, but this technical barrier has been overcome with the rapid development of computer technology. The advantage of multilevel converters is the multi-step output which has much lower distortion than the output of a conventional two level converter. This property makes multilevel converters very attractive and industrial products using multilevel converters can be found in a wide range of applications such as pumps, conveyors, reactive power compensation, marine propulsion and HVDC [1, 7, 18].

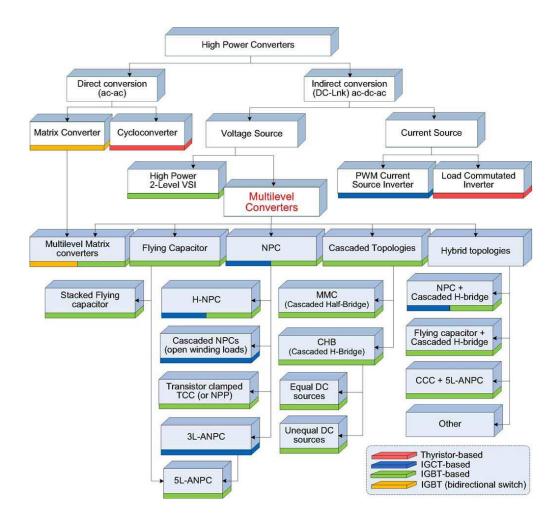

Figure 2.1 [7] shows the topology classification for multilevel converters. The three classical multilevel converter topologies are the neutral point clamped (NPC), cascaded H-bridge (CHB) and flying capacitor (FC) circuits. New multilevel converter topologies such as the five-level H-bridge NPC (5L-HNPC) [19], the three-level active NPC (3L-ANPC) [5], and the MMC [6] have found practical applications in recent years [7].

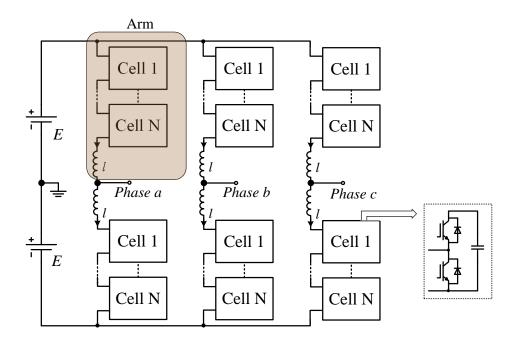

The modular multilevel converter (MMC), first reported by Prof. R. Marquardt in 2001 [9], is the state of art multilevel converter [8]. As shown in Figure 2.2, each phase of the MMC consists of two arms and each arm is constituted using chain-link cells and an arm inductor. A cell comprises two IGBTs and a capacitor. The capacitor voltage is regulated at its nominal voltage by a controller. Staircase voltage waveforms can be produced at the AC terminals. The detailed operating principles of this circuit will be introduced in Chapter 3.

The MMC is considered to be the most promising converter topology for high voltage applications with desirable features such as:

• Modular construction with manufacturable, standardised cells (half-bridge) [6].

Figure 2.1: Multilevel converter classification [7].

- High power and high voltage capability, extendable by adding additional cells.

- Low total harmonic distortion (THD) in output waveforms.

Although still an emerging topology the MMC has already found applications. Table 2.1 lists current HVDC projects based on the MMC topology [9]. Considerable research has been devoted to understanding the control of an MMC. The operating principle for an MMC is presented in [20]. The modelling and some control strategies are given in [21, 22, 23]. Different capacitor voltage balancing techniques such as sorting capacitor voltages [24], dual sorting [25], average and individual balancing [23] have been investigated; modulation techniques such as

Figure 2.2: Schematic of a three phase MMC.

phase-shifted pulse width modulation (PWM) [23], level shifted PWM [20], and nearest level modulation [26] have been proposed. Power losses of the MMC and normal voltage source converters (VSCs) have been compared by [26]. The review paper [9] summarises the latest work on the MMC in terms of modelling, control, modulation, applications and future trends.

# 2.2 Device Reliability in Power Converters

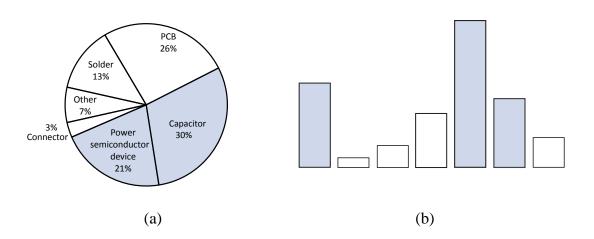

Power converters are often subjected to unexpected failure of components. These failures can degrade the performance of a power converter. In a power converter the power semiconductor device and capacitor are the components with the lowest reliability [10, 11, 27]. The results shown in Figure 2.3 (a) are based on 200 products from 80 companies where more than 50% of converter failures are caused by power semi-conductor devices and capacitors [11, 27]. The survey [10] also shows the similar results as illustrated in Figure 2.3 (b).

| Table 2.1: | Recent | HVDC         | projects | hased | on I | MMC    |

|------------|--------|--------------|----------|-------|------|--------|

| Table 4.1. | песень | 11 0 1 7 ( / | DIOTECTO | Daseu | ()   | VIIVIV |

| Table 2.1. Recent HVDC projects based on MWC. |                 |                |                 |              |  |

|-----------------------------------------------|-----------------|----------------|-----------------|--------------|--|

| Project Name                                  | Power $(MW)$    | Voltage $(kV)$ | Commission year | Manufacturer |  |

| Tres-Amigas, USA                              | $3 \times 750$  | 300            | 2014            | Alstom       |  |

| Skagerrak 4, Norway-Denmark                   | 700             | 500            | 2015            | ABB          |  |

| BorWin2, Germany                              | 800             | ±300           | 2015            | Siemens      |  |

| HelWin1, Germany                              | 576             | ±259           | 2015            | Siemens      |  |

| INELFE, France - Spain                        | $2 \times 1000$ | ±320           | 2015            | Siemens      |  |

| SylWin1, Germany                              | 864             | ±320           | 2015            | Siemens      |  |

| SW Link, Sweden                               | $2 \times 660$  | ±300           | 2015            | Alstom       |  |

| ElecLink UK-France                            | 1000            | ±320           | 2016            | /            |  |

| Dalian City                                   | 1000            | ±320           | 2017            | C-EPRI*      |  |

| NEMO GB-Belgium                               | 1000            | ±320 to 500    | 2018            | /            |  |

| Caithness-Moray-Shetland                      | 1200            | /              | 2018            | ABB          |  |

| Alegro, Belgium-Germany                       | 1000-1600       | /              | 2018            | /            |  |

| Nord Link                                     | 1400            | /              | 2019            | /            |  |

| AWC, USA                                      | 3 × 1000        | ±320           | 2019            | Alstom       |  |

| BorWin3                                       | 900             | ±320           | 2019            | Siemens      |  |

<sup>\*</sup>C-EPRI: China Electric Power Research Institute

Figure 2.3: Industry based survey of component reliability in power converters:(a) [11, 27], (b) [10].

The failure mechanisms for IGBTs (the most commonly used power semi-conductor devices [10]) and capacitors will be briefly introduced in the next section.

#### 2.2.1 IGBT Failure Mechanism

There are two types of failures seen in fully controlled power semiconductor devices: open-circuit failure (the device remains OFF state regardless of the gate drive signal) and short-circuit failure (the device remains remain ON regardless of the gate drive signal). For an IGBT there are two classifications of open-circuit failure and two for short-circuit failure [28, 16].

#### IGBT Open-circuit Failure Mechanisms

The first common failure mechanism is bond wire lift-off due to solder joint fatigue [28]. This failure is related to the mismatch between the thermal expansion coefficients of silicon and aluminium. After many cycles of operation, thermal expansion and contraction of the different materials leads to a crack of the bond wire and base connection [28]. Frequent system transients, ambient temperature variation and heavy loads will all accelerate this cracking process [10]. It is noted that alternative die attachment processes such as sintered silver joints [29] and transient liquid phase joints [30] can be used to increase the strength of the joint and hence decrease the fatigue failure rate.

The other cause of open-circuits for an IGBT is failure of the gate drive circuit. A gate drive is the interface between a controller and an IGBT. Failures of the gate drive circuit will lead to the IGBT staying OFF regardless of the driving signal and is equivalent to an open-circuit fault in the IGBT. The gate driver itself is recognised as the third most unreliable component in a power converter as shown in Figure 2.3 (b) [10]. Due to its complex structure, failures in any component of a gate driver, such as the isolated power supplies, optical couplers or gate resistors, will cause malfunction of the gate drive circuit. It is noted that over-voltage or over-current of the power devices may also cause damage of the corresponding gate drive.

#### IGBT Short-circuit Failure Mechanisms

The destruction of an IGBT due to a short-circuit is usually caused by an excessive dissipation of energy producing high temperatures beyond the limits of the silicon. The actual failure process can be briefly introduced as follows [16]:

- Exceeding thermal limit. In the presence of a shoot through fault in an IGBT, caused by a faulty gate drive signal, lack of dead time or other reason, the temperature in the die will increase extremely fast. When the junction temperature exceeds the the intrinsic temperature (about 250°C), the IGBT die will be fatally damaged due to the exponential increase in carrier concentration and thermal runaway. Another possible cause of device destruction at high temperature is contact metal (aluminium) migration into the junctions, which will permanently damage the blocking capability of the device [16].

- Exceeding Voltage Rating. Large voltage overshoots can cause the device to avalanche and the resultant thermal surge will damage the device permanently [16].

# 2.2.2 Capacitor Failure Mechanism

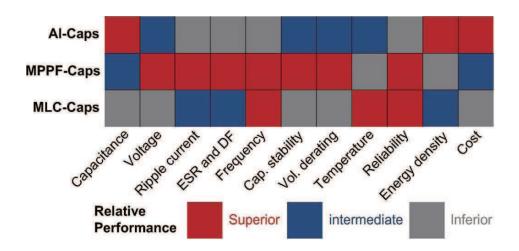

The capacitors discussed are the DC-link capacitors used in power electronics. Generally three types of capacitors are used for DC-link applications, which are the aluminum electrolytic capacitors (Al-Caps), metallized polypropylene film capacitors (MPPF-Caps) and high capacitance multi-layer ceramic capacitors (MLC-Caps) [31]. A qualitative performance comparison of these three types of capacitors is shown in Figure 2.4.

Based on Figure 2.4, an MPPF capacitor has desirable features of high reliability and stability, low dissipation factor <sup>1</sup>, and is capable of operating at high voltage,

<sup>&</sup>lt;sup>1</sup>Dissipation factor =  $\omega C \cdot \text{ESR}$ , where  $\omega$  is the angular frequency of the current through the capacitor, C the capacitance, ESR the equivalent series resistance

Figure 2.4: Performance comparison of the three main types of capacitors for DC-link applications [31].

high ripple current and wide frequency range. Hence an MPPF capacitor is a suitable choice for an industrial MMC [32].

Table 2.2: Wire-out mechanisms for the three main DC link capacitors [31].

| Table 2.2. (The out incommission one time main 2 c imin capacitors [o1]. |                                                          |                               |  |  |

|--------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|--|--|

| Capacitor type                                                           | Critical failure mechanisms                              | Critical influence factors    |  |  |

| Electrolytic vaporization                                                |                                                          | $T_a, i_C$                    |  |  |

| Al-caps                                                                  | Al-caps Electrolytic reaction (e.g. contaminates such as |                               |  |  |

|                                                                          | oxygen, moisture and halogens in the capacitor can       | $V_c, i_L$                    |  |  |

|                                                                          | lead to deterioration of the dielectric materials)       |                               |  |  |

| Self-healing                                                             |                                                          | Defects, $V_C, T_a, dV_c/dt$  |  |  |

| MPPF-Caps                                                                | Excessive capacitance reduction                          | Humidity, $V_C, T_a, dV_c/dt$ |  |  |

|                                                                          | Disconnection of terminals                               | $V_C, T_a, dV_c/dt$           |  |  |

| MLC-Caps                                                                 | Oxide vacancy migration; dielectric punctiure;           | $V_C, T_a, i_C$ , vibration   |  |  |

| MILC-Caps                                                                | insulation degradation; micro-crack within ceramic       |                               |  |  |

$T_a$ -ambient temperature,  $i_C$ -capacitor ripple current stress,  $V_C$ -capacitor voltage voltage stress,  $i_L$ -leakage current.

Failure mode of capacitors can be divided into catastrophic failure caused by a single event overstress and wear out failure caused by the degradation over time [31]. The dominant failure mode of a capacitor is the wear out failure. The critical failure

mechanisms for the three main DC-link capacitors are shown in Table 2.2. A more detailed failure mechanisms of the MPPF capacitors are presented below:

- Self-healing. Defects such as embedded foreign particles or voids inherited in crystallized structure can form weak spots that can lead to localized breakdown [32, 33]. The breakdown event results in the short time (< 20µs) discharge of a portion of the stored change with a sudden localized temperature and pressure build-up. Due to this intense discharge, a puncture develops in the polypropylene film and the metallization layer near the defect site is rapidly vaporized (similar to the blowing of a fuse), and the defect site becomes electrically isolated [33]. Self-healing makes an MPPF capacitor more reliable—after the self-healing process an MPPF capacitor can continue operation normally, however repetitive occurrence of self-healing can degrade a capacitor.

- Excessive capacitance reduction. In an MPPF capacitor, an electrochemical corrosion process can convert areas of the aluminium electrode into aluminium oxide, which will decrease the electrode thickness and lead to a large reduction in capacitance [33].

- Disconnection of terminals. The contact between the electrode edges and lead can degrade over time and will be disconnected eventually [34].

Table 2.3: Typical end-of-life criteria for capacitors [31].

|                        | Al-Cap                            | MPPF-Caps                    | MLC-Caps                                                  |

|------------------------|-----------------------------------|------------------------------|-----------------------------------------------------------|

| Failure criteria       | C: 20% reduction,<br>ESR: 2 times | C: 5% reduction, DF: 3 times | C: 10% reduction,<br>$R_p < 10^7 \Omega$ , DF: 2<br>times |

| Degradation precursors | C or ESR, or both                 | С                            | $C, R_p$                                                  |

DF-dissipation factor,  $R_p$ -insulation resistance

These failure mechanisms will cause the a capacitor to lose its capacitance and to increase its ESR. Table 2.3 lists the end-of-life criteria of the capacitors. It

can be seen in Table 2.3 that capacitance can be used as a precursor of capacitor degradation for all the three types of capacitors.

### 2.2.3 Effect of Component Failure

Failures in power semi-conductor devices or capacitors can lead to the malfunction of a power converter. These faults cannot usually be overcome by a controller and can distort the output voltages and currents. Any abnormal high voltage or high current caused by a failure may lead to secondary failures in other components. A shut down of the power converter may follow if the operation continues without any measures to detect these failures and reconfigure the power converter. In order to improve the availability of a power converter it is vital that component failures are detected and located so that the converter can be reconfigured.

With large numbers of power semiconductor devices and capacitors a multilevel converter is more likely to experience failures during its lifetime. For instance in the Trans Bay Cable project [13, 12] there are more than 400 cells in each power converter phase, i.e. over 2400 IGBTs and 1200 capacitors are installed. Each of these devices is a potential failure point.

## 2.3 Fault Detection and Isolation

Fault detection and isolation (FDI) deals with system monitoring with two objectives: detecting anomalous situations (fault detection) and addressing their causes (fault isolation) [14, 15]. By definition, the term *fault* means failure or malfunction in an actuator, component or sensor in a system [14].

FDI is an active topic in a wide range of research areas. System monitoring and fault isolation is one of the fundamental requirements for safety critical systems such as nuclear plants, as a failure could cause a hazard to the population as well as a huge economic loss [15]. Early isolation of system faults can avoid such disasters. Recently, the significance of FDI has been recognised in the ever

increasing complexity of the modern automated systems such as the MMC [14]. Systems with the capability to detect and locate faults can operate for longer and minimize the economic losses caused by component failures through improved availability.

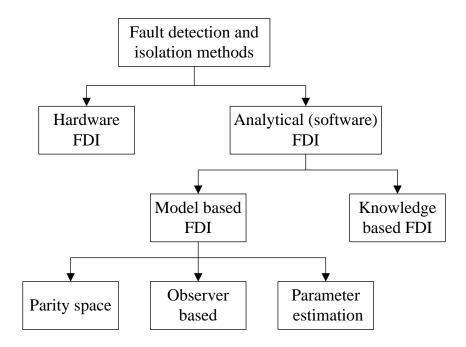

FDI schemes can be classified as hardware methods and analytical (software) methods as shown in Fig. 2.5.

Figure 2.5: Classification of FDI methods [35].

#### 2.3.1 Hardware FDI

Hardware FDI employs repeated hardware elements (actuators, components or sensors) [15]. An indication of a fault can be obtained if the behaviours of the process components are different from the redundant ones. Hardware FDI can also be implemented by adding additional sensors which are especially included for the purpose of monitoring and a fault can be located by comparison of measured signals with predefined thresholds. Hardware FDI can be straightforward and is widely used in many safety-critical applications such as aircraft sytems and nuclear

plants [15]. The main problem of this approach is the extra cost, space and weight [36]. Besides, the additional hardware itself will reduce the reliability of the system.

#### 2.3.2 Analytical FDI

Analytical FDI employs the internal relationships of the system states to estimate the behaviour of a system [37, 15]. The consistency between the actual behaviour of the system and its estimated behaviour is checked to detect the fault and the most likely faulty components can be located based on the quantities and locations of the inconsistency [36]. The internal relationship of a system can either be obtained from mathematical models of the system (model based) or from analysis of the historical data (knowledge based) [35]. Based on the method used to obtain the system model, analytical FDI is classified as shown in Fig. 2.5 [35]. Application of analytical FDI is boosted by the great advances in computer technology in recent decades [14]. With cheaper and faster microprocessors available, more and more analytical redundancy will be applied in industrial systems to improve the overall system availability.

#### Model Based FDI

The model used by this FDI technique is extracted from the healthy system directly. In the absence of a fault the estimated process behaviour converges to the measured behaviour with only tiny errors due to modelling uncertainty and measurement noise [36]. In the presence of a fault a significant inconsistency appears between the estimated and measured behaviour. A fault can be detected and isolated according to the quantities of this inconsistency [38]. The most common model based FDI techniques include parity space FDI [37], observer based FDI [36, 38] and parameter estimation [15].

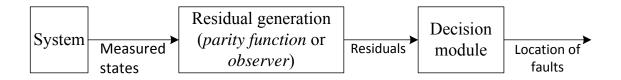

Parity space and observer based FDI techniques use models to estimate system outputs. The basic concept is shown in Fig. 2.6. The residuals are the magnitude of the difference between the estimated and measured outputs. Residuals can either be

generated by parity functions (parity space FDI) or observers (observer-based FDI). A decision module is then employed to determine the most likely faulty elements according to these residuals. According to [38] parity space and observer based FDI are equivalent because a transforming matrix exists for conversion between an observer and the corresponding parity space.

Figure 2.6: Basic concept of parity space and observer based FDI techniques [37].

Parameter estimation employs a model of a system to repeatedly estimate the system parameters. An indication of a fault is made when there is discrepancy between the estimated and actual parameters [35]. Typical parameter estimation techniques include least squares, recursive least squares and extended least squares [35].

#### Knowledge Based FDI

Instead of obtaining the models of systems directly, models for a knowledge based FDI are constructed from historical data using statistical decision theory or artificial intelligence (AI) techniques such as neural networks [15]. This method is a good choice for systems whose model is difficult to obtain: for example a chemical plant.

#### 2.3.3 Performance Criteria of an FDI Scheme

The often cited criteria for assessing the performance of an FDI scheme are [15]:

• Promptness of detection. Generally the faster the detection the better. Quick fault detection and isolation is important to avoid secondary failures caused by faulty elements and to allow enough time for deployment of mitigation.

- False alarm ratio. It is undesirable for an FDI scheme to report the occurrence of a fault when there are no failures in the system. Frequent false alarms can interrupt the normal operation of a system. Normally a false alarm is caused by an external disturbance, measurement noise or model uncertainty [15].

- Missed fault detection. An FDI scheme should detect the occurrence of all the faults. Failure to detect a fault would be an undesirable characteristic.

- *Incorrect fault isolation*. It is crucial to locate any fault correctly in order to apply appropriate mitigation.

- Sensitivity to incipient faults. Some faults evolve gradually, such as the ageing of a capacitor, and early identification of such faults can be very helpful to prevent the actual occurrence of component failures.

It is difficult for an FDI scheme to satisfy all these criteria perfectly as some of the criteria are contradictory [15]. For example a low false alarm ratio can lead to a long detection time or high missed fault detection rate. A trade-off is often necessary to meet all the performance criteria. In addition, multiple FDI methods can be used together to achieve high reliability of fault detection in a system.

#### 2.3.4 Fault Detection for Multilevel Converters

Generally a short-circuit fault in a power semi-conductor device requires quick detection to avoid shoot through of the complementary device and is usually detected using a hardware circuit. An open-circuit is not immediately fatal and can be tolerated by the power converter for some time. Therefore open-circuit faults can typically be detected using analytical methods which normally takes a few tens of milliseconds to detect and locate a fault.

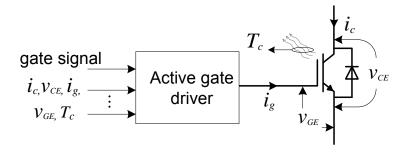

Hardware methods are widely used in fault detection and protection for power semi-conductor devices and are normally implemented along with the gate drive circuit. A gate drive with the capability for fault detection and over current protection is often called an active gate drive or smart gate drive. Typically one of or a combination of the following parameters are used: current through the device  $i_c$ , voltage across the device  $v_{CE}$ , device temperature  $T_c$ , gate drive voltage  $v_{GE}$  and charging current  $i_g$ . These parameters can be processed using a logic circuit as shown in Figure 2.7. An active gate drive can report the status of a power semi-conductor device and apply a corresponding protection strategy.

Figure 2.7: Typical hardware fault detection for an IGBT.

"De-saturation detection" is a commonly used hardware FDI method and a short-circuit fault is indicated if  $v_{CE}$  is larger than a given threshold value. Short-circuit or open-circuit faults of IGBTs can also be detected by comparing  $i_c$  or  $di_c/dt$  with threshold values when the IGBT switches [16, 39].  $i_c$  can be sensed by a current transducer [16] and  $di_c/dt$  can be obtained by measuring the voltage across the parasitic inductance between the Kelvin emitter and power emitter in an IGBT module [39]. A different way to detect failures of IGBTs is by analysing the electrical characteristics of the gate drives. Short-circuit or open-circuit faults can be reported by detecting the time of a gate voltage plateau caused by the Miller effect [40]. Similarly by comparing the amplitude of gate charging and discharging current  $i_g$  to threshold levels, IGBT faults can be detected [41], where  $i_g$  is obtained based on the voltage across the gate resistor. These methods can all be used for a range of different power converters including multilevel converters.

Analytical detection methods are also an active research topic for FDI in power converters. Different methods have been proposed to detect the failures in voltage source converters such as the calculation of the output current trajectory using Park's Vector [42] or the comparison of the actual ac voltage and associated reference [43], etc.. There are several analytical FDI methods for multilevel converters based on analysis of the output voltage waveforms. In a multilevel converter modulated by phase-shifted PWM the frequency characteristics of the output phase voltage can be used to detect faults in power semiconductor devices [44, 45]. Through processing by a bandpass filter and Discrete Fourier Transform, the component at the switching frequency in a multilevel converter can be obtained. Due to the phase shifted modulation the amplitude of this switching frequency component is very small in normal operation, and increases significantly in the presence of a device failure. The amplitude of the switching frequency component is compared to a threshold value to detect the device failure, and the angle of this component is used to locate the cell with the faulty devices [44, 45]. The time-domain characteristics of an output phase voltage can also be used to detect faults of power semi-conductor devices and the occurrence of a fault is detected by the degradation of the output voltage. The fault is located by comparing the output phase voltages with all the possible faulty phase voltages [46]. FDI algorithms based on the artificial intelligence (AI) have also been proposed for multilevel converters, where the historical data of the output phase voltages both in normal and faulty conditions are used to train a neural network [47].

Although hardware FDI methods like active gate drives are capable of detecting both short-circuit and open-circuit faults they add weakness to converters due to their complex structures and direct connection to high voltages and high temperatures. Failures of the gate drivers can be detected using analytical FDI methods. Additionally hardware FDI methods require extra sensors for each power device to measure the voltage, current and temperature as well as circuits to process these signals. Analytical methods often need no additional devices as the signal and digital processors used are already implemented for

feedback control. In power converters, applications of hardware and software FDI methods can work together to achieve higher power converter availability.

In this thesis three analytical methods based on sliding mode observers are proposed for FDI in an MMC.

#### 2.4 Sliding Mode Control and Observer

Historically the *sliding mode* was defined as a special mode in variable structure systems [48]. Such systems, which are normally unstable with a single control structure, employ a number of control structures with rules to allow switching between control structures to achieve suitable system performance [48, 49]. Variable structure systems with sliding mode control were first proposed in the early 1950's in the Soviet Union by Emepyanov et al. [50].

The basic idea of the sliding mode control is to drive the trajectories of the system to a user-chosen manifold (called the sliding manifold) and maintain the system motion on this manifold [48, 49]. The sliding manifold is chosen in such a way that the closed-loop system attains control goals such as stabilization, tracking, regulation, etc. [48, 49]. Once the system is on the sliding manifold the closed loop system performance is achieved and two main desirable features can be obtained [48]:

- Insensitivity to external disturbances and model uncertainties;

- Reduced-order dynamics of the compensated system.

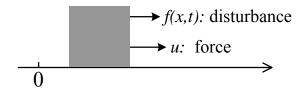

#### 2.4.1 Sliding Mode Control

An example considering the single-dimensional motion of a unit mass (Figure 2.8) from [48] is used to explain the basic concepts of sliding mode control. If the position and velocity are represented by  $x_1$  and  $x_2$  respectively, the following state

space equations can be used to describe the system:

$$\begin{cases} \dot{x}_1 = x_2 \\ \dot{x}_2 = u + f(x_1, x_2, t) \\ y = x_1 \end{cases}$$

(2.1)

where u denotes the control force,  $f(x_1, x_2, t)$  denotes the disturbance term and is assumed to be bounded, i.e.,  $|f(x_1, x_2, t)| \leq L > 0$ . In this example we let  $f(x_1, x_2, t) = \sin(2t)$ . The problem is to design a control force that moves the mass to the origin, i.e. drive  $x_1$  and  $x_2$  to 0 with an applied force u.

Figure 2.8: Single-dimensional motion of a unit mass [48].

A conventional linear feedback control strategy cannot achieve this goal. Assuming the linear control law  $u = a(0 - x_1) + b(0 - x_2)$  and substituting u into (2.1) yields:

$$\ddot{x}_1 + b\dot{x}_1 + ax_1 = f(x_1, t), \tag{2.2}$$

$x_1 = 0$  is not one of the roots of (2.2) and thus the linear feedback control cannot move the mass to the origin. The simulation results of the system with  $u = -3x_1 - 4x_2$  are shown in Figure 2.9.

Now let us introduce the desired compensated dynamics for system (2.1). A good candidate for these dynamics is:

$$\dot{x}_1 + cx_1 = 0, \quad c > 0 \tag{2.3}$$

therefore

$$x_1(t) = x_1(0)exp(-ct),$$

(2.4)

Figure 2.9: Response of  $x_1, x_2$  with linear feedback.

and  $x_1(t)$  converges to 0 asymptotically.

To achieve these dynamics a new variable in the state space of the system (2.1) is introduced:

$$\sigma = \dot{e} + ce \tag{2.5}$$

where e is error between the reference and actual state. In this example the mass needs to be moved to the origin therefore  $e = 0 - x_1 = -x_1$ . It is noted that equation (2.5) inherits the structure of the desired dynamics shown in equation (2.3).

In order to drive  $x_1$  to 0 we need to force  $\sigma$  to 0. A term  $\sigma\dot{\sigma}$  derived using the Lyapunov function technique [48] is considered. Based on (2.1) (2.5),  $\sigma\dot{\sigma}$  can be expressed as:

$$\sigma \dot{\sigma} = \sigma(-\ddot{x}_1 - c\dot{x}_1) = -\sigma(u + cx_2 + f(x_1, x_2, t)) \tag{2.6}$$

It is obvious that  $\sigma \to 0$  in a finite time if  $\sigma \dot{\sigma} < 0$ . One way to ensure  $\sigma \dot{\sigma} < 0$  is to choose:

$$u = -cx_2 + \rho \cdot \operatorname{sgn}(\sigma), \tag{2.7}$$

where sgn(x) is the sign function defined as:

$$\operatorname{sgn}(x) = \begin{cases} 1 & x > 0 \\ 0 & x = 0 \\ -1 & x < 0 \end{cases}$$

(2.8)

Substituting (2.7) into (2.6), we obtain

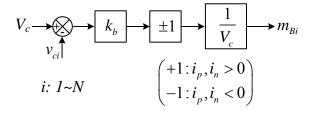

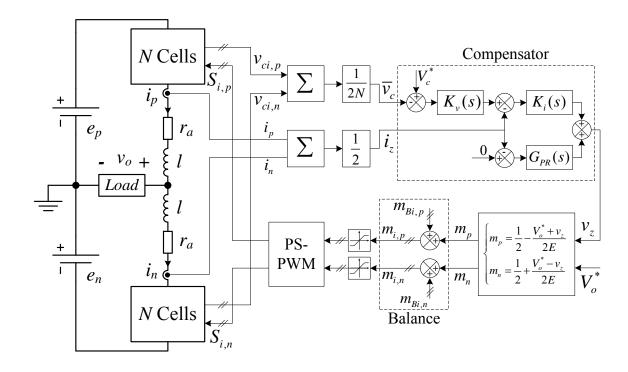

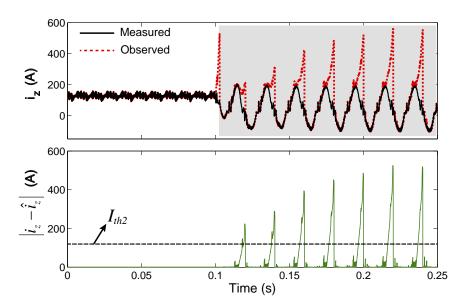

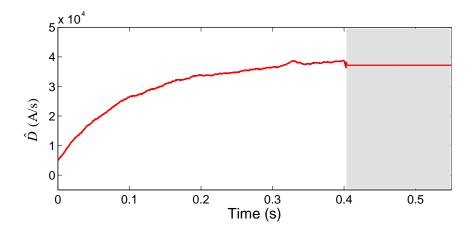

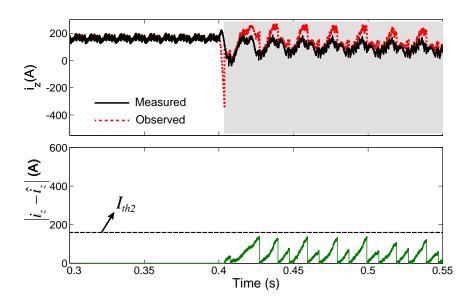

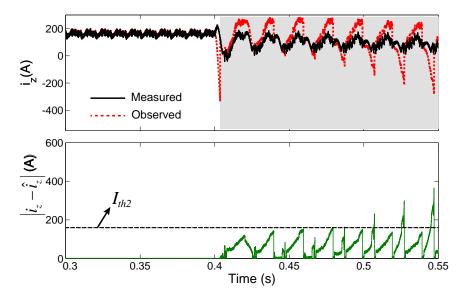

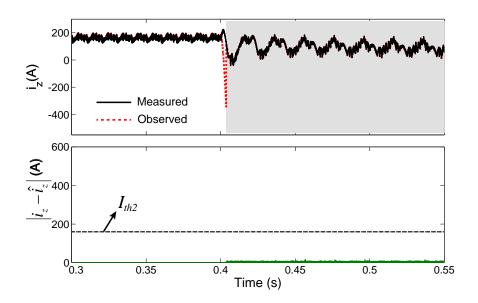

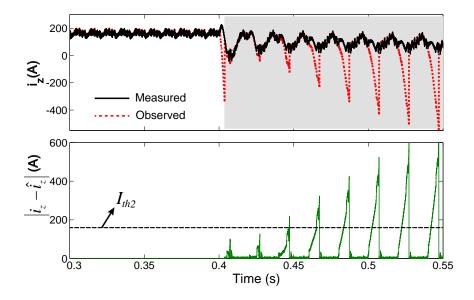

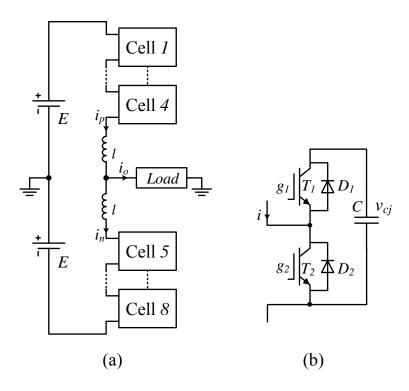

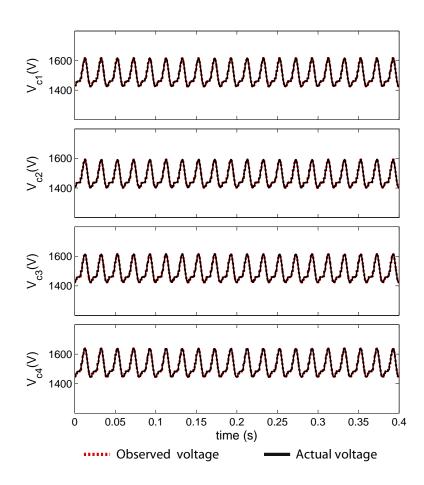

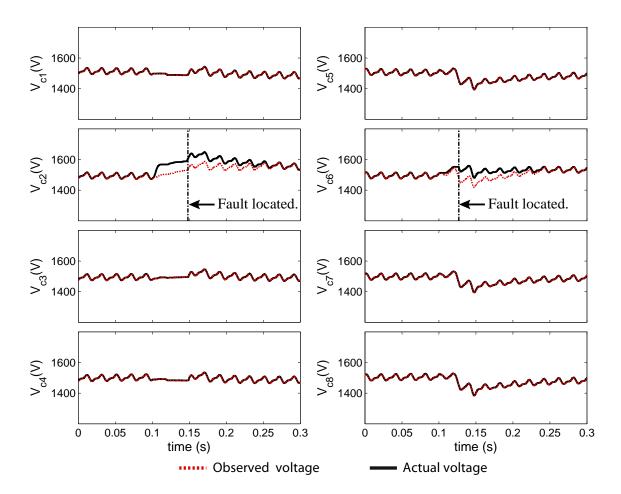

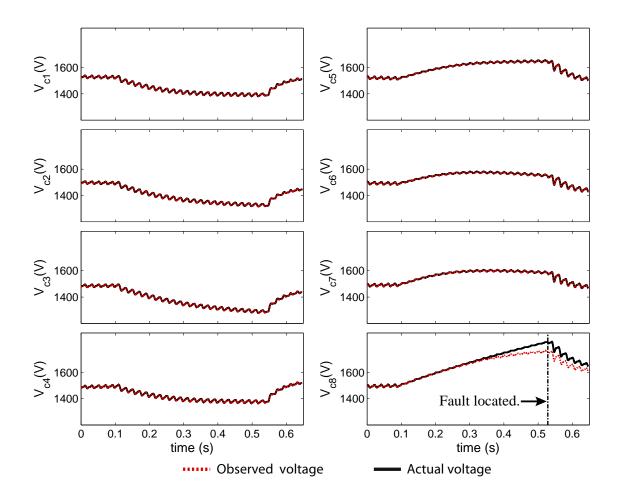

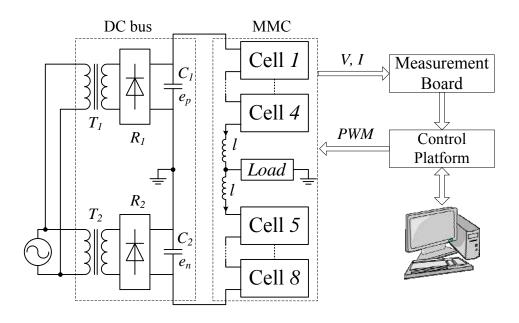

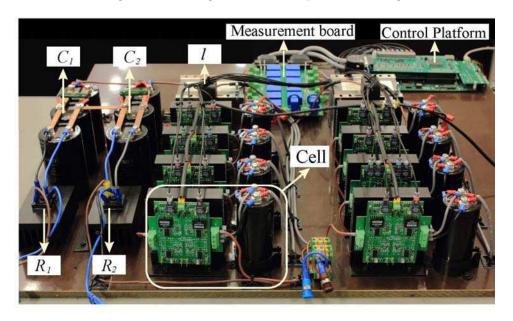

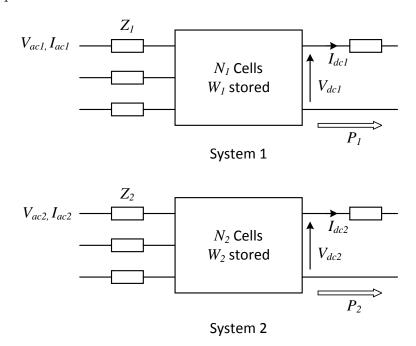

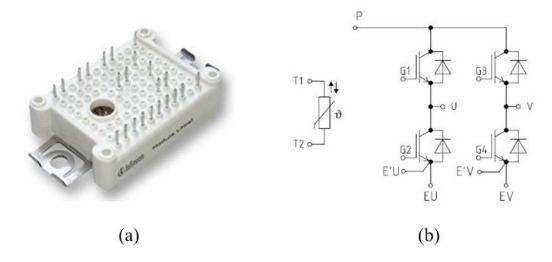

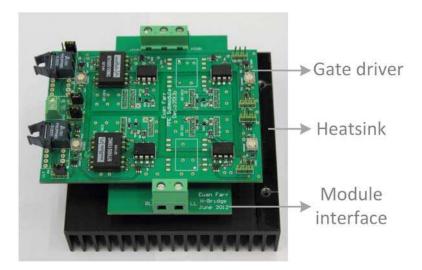

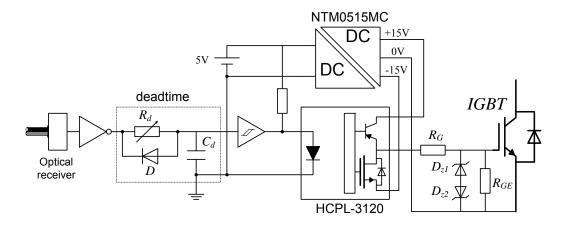

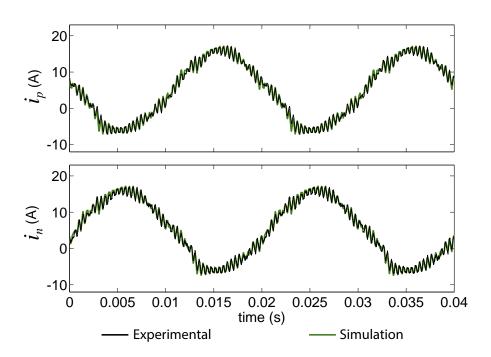

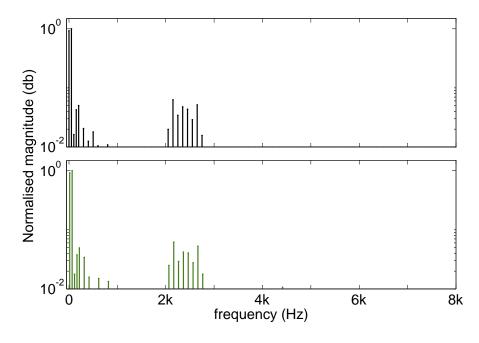

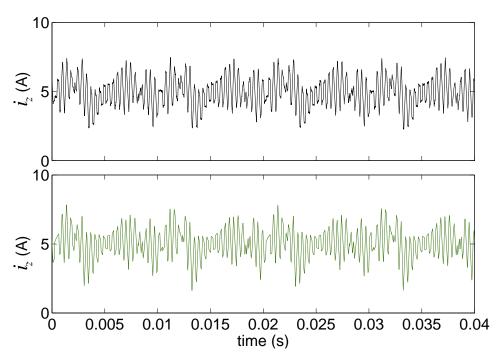

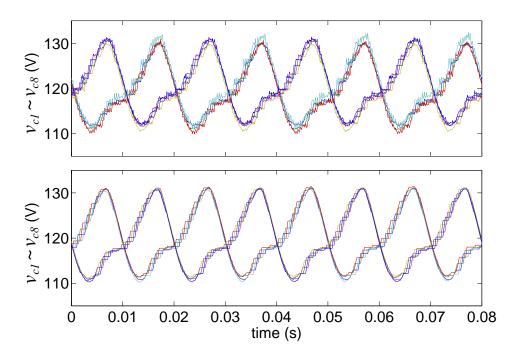

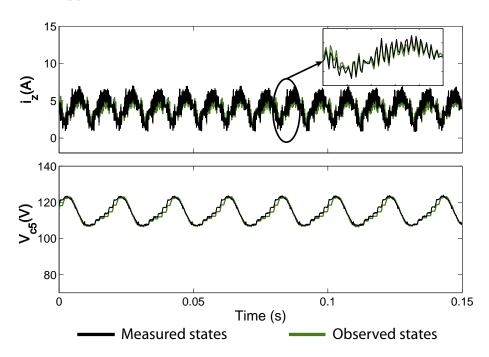

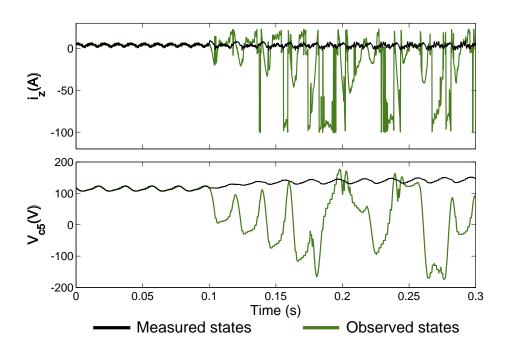

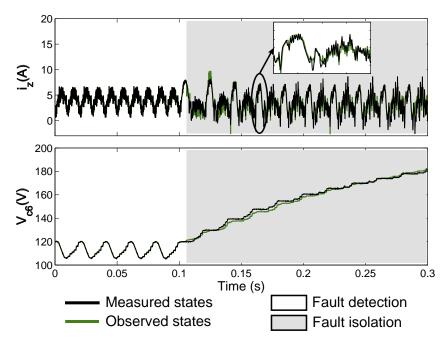

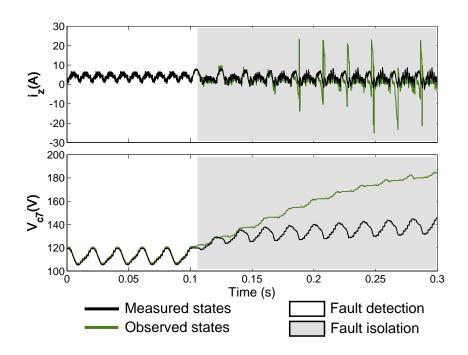

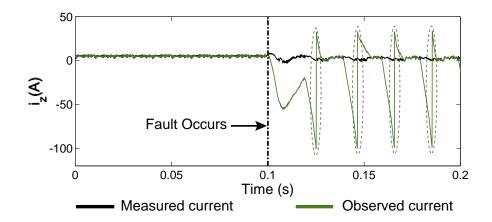

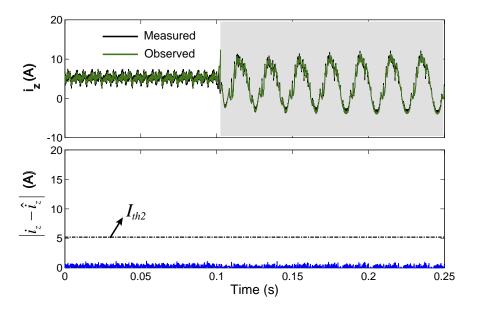

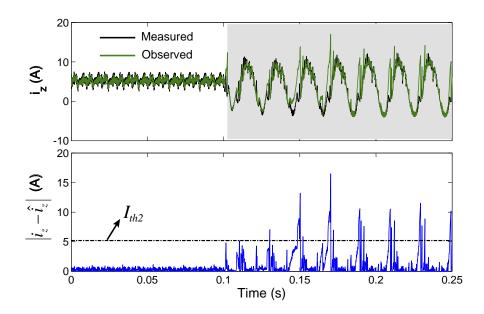

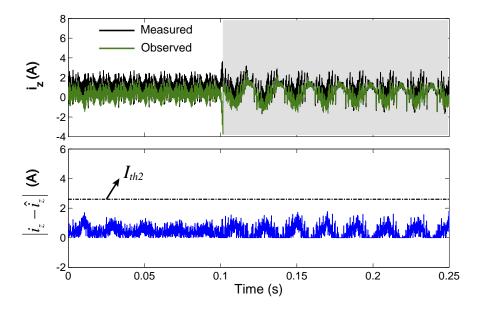

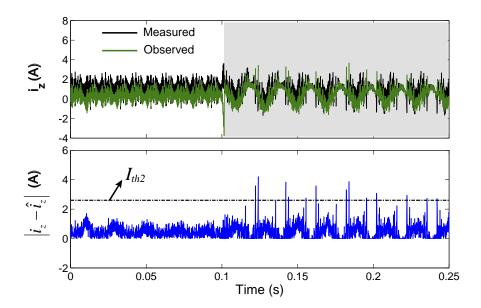

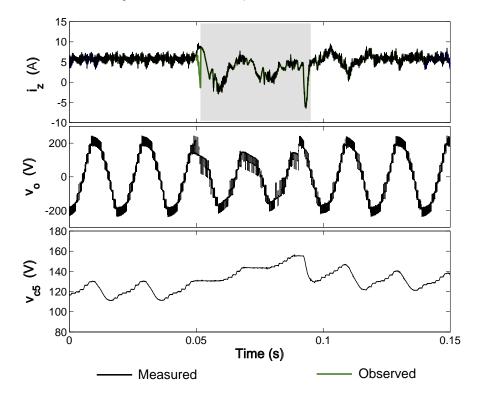

$$\sigma \dot{\sigma} = -\rho |\sigma| - \sigma f(x_1, x_2, t) \le -|\sigma| (\rho - |f(x_1, x_2, t)|). \tag{2.9}$$