# Kumar, Varindra (2014) I/O port macromodelling. PhD thesis, University of Nottingham.

Access from the University of Nottingham repository: http://eprints.nottingham.ac.uk/14294/1/Final thesis for upload.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# **I/O Port Macromodelling**

Varindra Kumar, MTech

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

May, 2014

UNITED KINGDOM · CHINA · MALAYSIA

### Abstract

3D electromagnetic modelling and simulation of various Printed Circuit Board (PCB) components is an important technique for characterising the Signal Integrity (SI) and Electromagnetic Compatibility (EMC) issues present in a PCB. However, due to limited computational resource and the complexity of the integrated circuits, it is currently not possible to fully model a complete PCB system with 3D electromagnetic solvers. An effort has been made to fully model the PCB with all its components and their S-parameters has been derived so as to integrate these S-parameters in 1D, 2D static or quasi-static field solver or circuit solver tool. The novelty of this thesis is the development and verification of active circuit such as Input and Output buffers and passive channel components such as interconnects, via and connectors and deriving their S-parameters in order to model and characterise the complete PCB using 3D full field solver based on Transmission Line Matrix modelling (TLM) method.

An integration of Input/Output (I/O) port in the 3D full field modelling method allows for modelling of the complete PCB system without being computationally expensive. This thesis presents a method for integration of Input/Output port in the 3D time domain modelling environment. Several software tools are available in the market which can characterise these PCBs in the frequency as well as the time domain using 1D, 2D techniques or using circuit solver such as spice. The work in this thesis looks at extending these 1D and 2D techniques for 3D Electromagnetic solvers in the time domain using the TLM technique for PCB analysis. The modelling technique presented in this thesis is based on in-house developed 3D TLM method along with a developed behavioural Integrated Circuit (IC) – macromodel. The method has been applied to a wide variety of PCB topologies along with a range of IC packages to fully validate the approach. The method has also been applied to show the switching effect arising out of the crosstalk in a logic device apart from modelling various discontinuities of PCB interconnects in the form of  $S_{11}$  and  $S_{21}$ parameters.

The proposed novel TLM based technique has been selected based on simplification of its approach, electrical equivalence (rather than complex mathematical functions), time domain analysis for transients in a PCB with an increased accuracy over other available methods in the literature. On the experimental side two, four and six layered PCBs with various interconnect discontinuities such as straight line, right angle, fan-out and via and IC packages such as SOT-23 (DBV), SC-70 (DCK) and SOT-553 (DRL) has been designed and manufactured. The modelling results have been verified with the experimental results of these PCBs and other commercial software such as HSPICE, CST design studio available in the market. While characterising SI issues, these modelling results can also help in analysing conducted and radiated EMC/EMI problems to meet various EMC regulations such as CE, FCC around the world.

# **Published Papers**

- Scott, I., Kumar, V., Greedy, S., Thomas, D. W. P., Christopoulos, C. & Sewell,

P. 2011.Time domain modelling of active electrically fine features in TLM,

*EMC Europe 2011*, York, UK, 284-287.

- [2] Scott, I., Kumar, V., Christopoulos, C., Thomas, D. W. P., Greedy, S. & Sewell,

P. 2012. Integration of behavioural models in the full-field TLM method, *Electromagnetic* Compatibility, IEEE Transactions *on*, 54(2), 359-366.

### Acknowledgement

I would like to sincerely thank my supervisors, Prof. DWP Thomas, Dr. Steve Greedy and Prof. Christos Christopoulos for providing me the invaluable guidance and direction throughout this PhD. During my first year, I was guided by Prof. Phillip Sewell, I would like to thank him for providing me the direction of my PhD with his valuable suggestions. They were especially helpful for their help and valuable suggestions at all of the time while encouraging me to complete my projects. I would also like to appreciate my co-supervisor Dr. Steve Greedy for providing me all the equipment, resources and support for the completion of the experimental work. These projects would not have been successful without their support and guidance.

The PhD has provided me an excellent level of academic research methodology which can be suitably applied at many industrial applications of hardware design and Electromagnetic Compatibility, Signal Integrity environment. I have learnt a great aspect of research and presentation skills during my work. In addition I would like to thank Dr. John Paul for providing me all the useful guidance in Transmission Line Matrix modelling and simulations. He is quite approachable and always there to support with minute details of Minisolve software and procedures. I would also like to thank Dr. Ian Scott for helping me in the IC simulation software. I would like to express my appreciation to Dr. Chris Smartt for useful guidance on some occasions.

Apart from this, I would like to thank Mr. Sam Cole, Mr. Puvaneswaran Arumugam, Mr. Rawin Vongurai, Ms. Oke Oluwabukola, Mr Rawa Muhyaddin, Mr. Yu Teo for creating a friendly environment for the entire duration. Very special thanks go to Mr. Rod Dykeman, Mr. Mark Birkin, Mr. Harjeet Johal for my PCB assembly support. I would also like to thank the entire technician at the ground floor workshop, particularly Mr. Paul Moss and Mr. Kevin Last for their timely support of the project.

I would like to sincerely thank the University of Nottingham for providing me the Dean of Engineering Research Scholarship under its world class GGIEMR group of the Department of Electrical and Electronic Engineering.

Finally I would like to express my gratitude to my parents, brother and sisters especially Dr. Anita kumari, my wife, Shalini and other family members for their patience, support and encouragement throughout my work. Without their support, I would not have been able carry and complete this thesis.

# Contents

| ABSTRACT                                                                                                                                                                                                             | 1                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| PUBLISHED PAPERS                                                                                                                                                                                                     | - III                                                        |

| ACKNOWLEDGEMENT                                                                                                                                                                                                      | IV                                                           |

| CONTENTS                                                                                                                                                                                                             | VI                                                           |

| LIST OF FIGURES AND TABLES                                                                                                                                                                                           | XI                                                           |

| LIST OF ACRONYMS AND SYMBOLS                                                                                                                                                                                         | - XX                                                         |

|                                                                                                                                                                                                                      |                                                              |

| Chapter 1– Introduction                                                                                                                                                                                              | -1                                                           |

| 1.1 Organisation of the thesis                                                                                                                                                                                       | 6                                                            |

| References                                                                                                                                                                                                           | - 8                                                          |

|                                                                                                                                                                                                                      |                                                              |

|                                                                                                                                                                                                                      |                                                              |

| Chapter 2 – High Frequency PCB Methodology and Analysis                                                                                                                                                              | . 10                                                         |

| <ul> <li>Chapter 2 – High Frequency PCB Methodology and Analysis</li> <li>2.1 Analysis of Discrete components</li> </ul>                                                                                             |                                                              |

|                                                                                                                                                                                                                      | 12                                                           |

| 2.1 Analysis of Discrete components                                                                                                                                                                                  | - 12                                                         |

| <ul><li>2.1 Analysis of Discrete components</li><li>2.1.1 Lumped Resistors</li></ul>                                                                                                                                 | - 12<br>- 12<br>- 14                                         |

| <ul> <li>2.1 Analysis of Discrete components</li> <li>2.1.1 Lumped Resistors</li> <li>2.1.2 Lumped Capacitors</li> </ul>                                                                                             | - 12<br>- 12<br>- 14<br>- 16                                 |

| <ul> <li>2.1 Analysis of Discrete components</li> <li>2.1.1 Lumped Resistors</li> <li>2.1.2 Lumped Capacitors</li> <li>2.1.3 Lumped Inductor</li> </ul>                                                              | - 12<br>- 12<br>- 14<br>- 16<br>- 18                         |

| <ul> <li>2.1 Analysis of Discrete components</li> <li>2.1.1 Lumped Resistors</li> <li>2.1.2 Lumped Capacitors</li> <li>2.1.3 Lumped Inductor</li> <li>2.2 PCB technology and its high frequency behaviour</li> </ul> | - 12<br>- 12<br>- 14<br>- 16<br>- 18<br>- 18                 |

| <ul> <li>2.1 Analysis of Discrete components</li> <li>2.1.1 Lumped Resistors</li> <li>2.1.2 Lumped Capacitors</li> <li>2.1.3 Lumped Inductor</li> <li>2.2 PCB technology and its high frequency behaviour</li></ul>  | - 12<br>- 12<br>- 14<br>- 16<br>- 18<br>- 18<br>- 20         |

| <ul> <li>2.1 Analysis of Discrete components</li> <li>2.1.1 Lumped Resistors</li> <li>2.1.2 Lumped Capacitors</li></ul>                                                                                              | - 12<br>- 12<br>- 14<br>- 16<br>- 18<br>- 18<br>- 20<br>- 20 |

| 2.2.3 Transmission line requirement on trace                 | - 24 |

|--------------------------------------------------------------|------|

| 2.3 Transmission line theory using circuit analysis          | - 28 |

| 2.3.1 Lattice diagram for transmission line                  | 34   |

| 2.4 Wave propagation in PCB using field theory               | 39   |

| 2.4.1 Maxwell's equation                                     | - 39 |

| 2.4.2 Boundary condition                                     | - 42 |

| 2.4.2.1 Interface between a dielectric and perfect conductor | 43   |

| 2.4.2.2 Perfect Electric Conductor                           | - 45 |

| 2.4.2.3 Perfect Magnetic Conductor                           | - 46 |

| 2.4.2.4 Absorbing Boundary Condition                         | - 47 |

| 2.5 Discontinuities in a transmission line trace             | 48   |

| 2.5.1 Trace over split plane                                 | 53   |

| 2.5.2 Tee-junction                                           | 55   |

| 2.5.3 Open end                                               | 57   |

| 2.5.4 Steps in width                                         | 59   |

| 2.5.5 Discontinuity by gaps                                  | 61   |

| 2.5.6 Shorted end                                            | 64   |

| 2.6 Conclusion                                               | 65   |

| References                                                   | - 67 |

|                                                              |      |

### Chapter 3 – Computational Electromagnetic Methods------70

| 3.1 Computational Electromagnetic modelling approach |    |

|------------------------------------------------------|----|

| 3.1.1 FDTD modelling                                 | 74 |

| 3.1.2 MoM modelling                                  |    |

| 3.1.3 FEM modelling                                  | 77 |

| 3.1.4 BEM modelling                                            | 81  |

|----------------------------------------------------------------|-----|

| 3.2 Conclusion                                                 | 82  |

| References                                                     | 84  |

|                                                                |     |

| Chapter 4 – TLM Methods                                        | 86  |

| 4.1 Development of 1D TLM model                                | 87  |

| 4.2 Development of 3D TLM method                               |     |

| 4.2.1 Field solution using SCN node                            |     |

| 4.2.2 Stub modelling                                           | 102 |

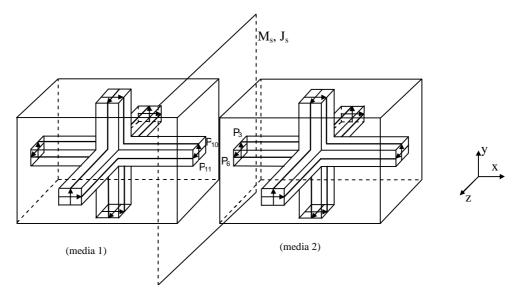

| 4.2.3 Heterogeneous media modelling with HSCN node using stubs | 105 |

| 4.2.4 Field solutions using HSCN node                          | 107 |

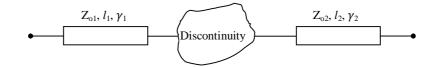

| 4.2.5 Discontinuity in transmission line using field theory    | 111 |

| 4.3 TLM modelling with a boundary condition                    | 113 |

| 4.4 Modelling dispersive media                                 | 114 |

| 4.4.1 Debye model                                              | 115 |

| 4.4.2 Lorentz model                                            | 118 |

| 4.4.3 Drude model                                              | 120 |

| 4.5 Conclusion                                                 | 121 |

| References                                                     | 123 |

### Chapter 5 – I/O Port Macromodelling------126

| 5.1 | IC modelling                                   | 128 |

|-----|------------------------------------------------|-----|

| 5.2 | IC port macromodelling                         | 129 |

|     | 5.2.1 IC port macromodelling and its procedure | 131 |

| 5.2.1.1 Estimation of the buffer characteristic      | 132   |

|------------------------------------------------------|-------|

| 5.2.1.2 Computation of the weighting coefficients    | - 135 |

| 5.2.1.3 Model implementation and validation          | 137   |

| 5.2.2 IBIS modelling and its procedure               | 137   |

| 5.3 IBIS/Macromodel-TLM interface                    | 141   |

| 5.4 Experimental and simulation setup for macromodel | 146   |

| 5.4.1 Measurement setup                              | 148   |

| 5.4.2 Simulation setup                               | 149   |

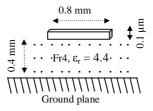

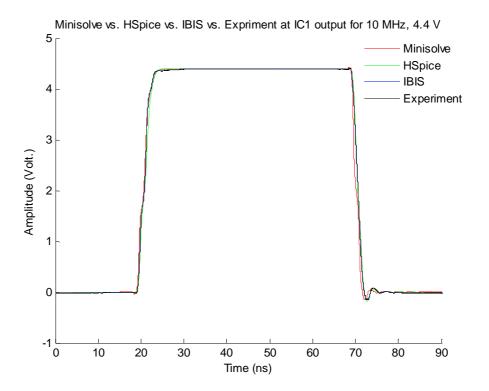

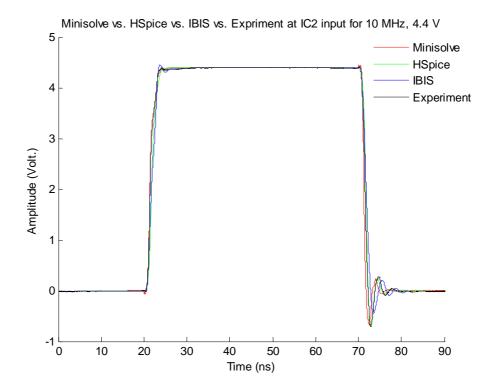

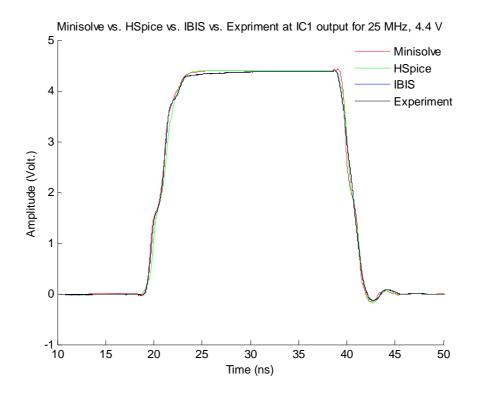

| 5.5 Results comparison for macromodel using TLM      | 150   |

| 5.6 Experimental and simulation setup for IBIS       | 154   |

| 5.6.1 Measurement setup                              | 157   |

| 5.7 Results comparison for IBIS using TLM            | 159   |

| 5.8 Conclusion                                       | - 166 |

| References                                           | 167   |

### Chapter 6 – Modelling of PCB Interconnects and IC Packages----- 169

| 6.1 | PCB schematics and stack-up for PCB manufacturing | 171 |

|-----|---------------------------------------------------|-----|

| 6.2 | PCB trace configurations and its S-parameters     | 175 |

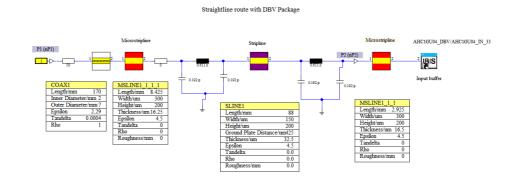

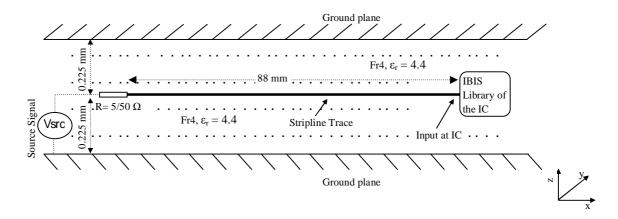

|     | 6.2.1 Straight line configuration                 | 176 |

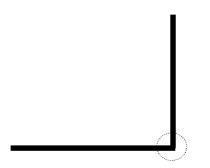

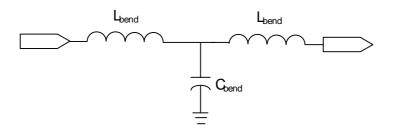

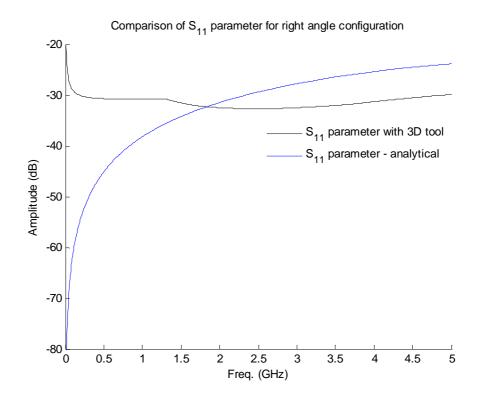

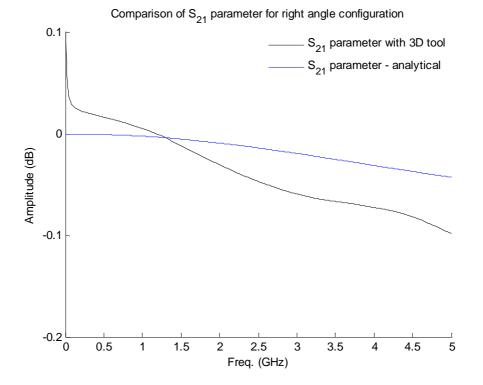

|     | 6.2.2 Right Angle configuration                   | 178 |

|     | 6.2.3 Fan-out configuration                       | 181 |

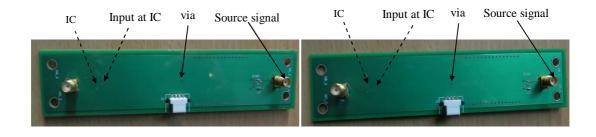

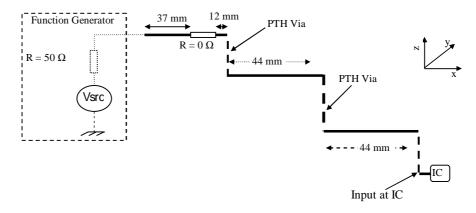

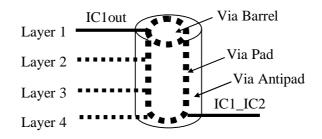

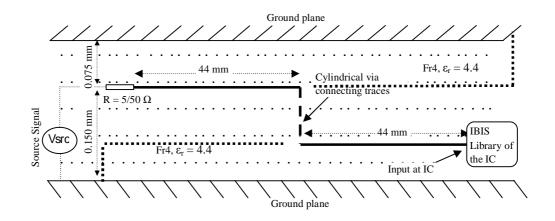

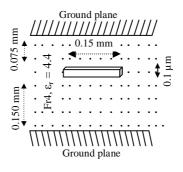

|     | 6.2.4 Via configuration                           | 183 |

| 6.3 | Experimental measurement setup                    | 185 |

| 6.4 | Electronic system simulation                      | 187 |

|     | 6.4.1 PCB trace simulation                        | 187 |

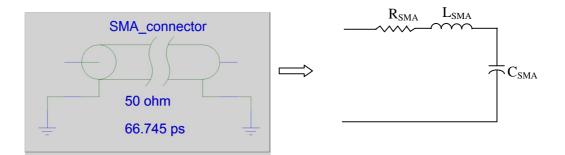

| 6.4.2 Equivalence for cable, SMA connector, via and bends | 190 |

|-----------------------------------------------------------|-----|

| 6.5 HSPICE simulation                                     | 200 |

| 6.6 Minisolve simulation                                  | 202 |

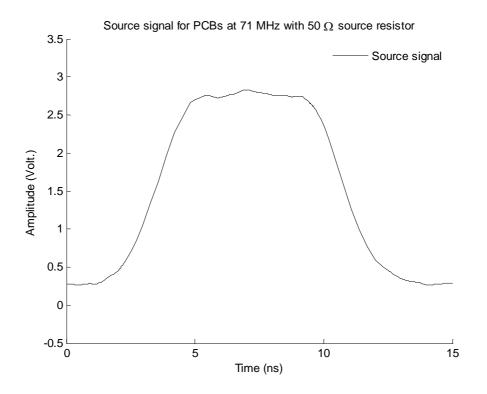

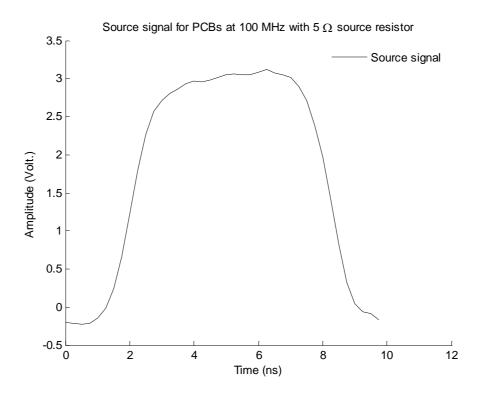

| 6.6.1 Source signal                                       | 203 |

| 6.6.2 Minisolve simulation description                    | 204 |

| 6.7 CST design studio description                         | 207 |

| 6.8 Minisolve results and its comparison with experiment  | 208 |

| 6.8.1 Straight line configuration                         | 209 |

| 6.8.2 Right Angle configuration                           | 212 |

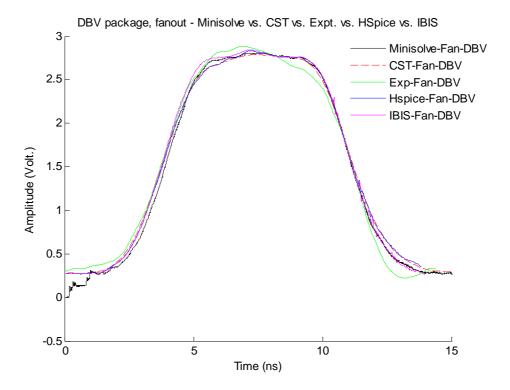

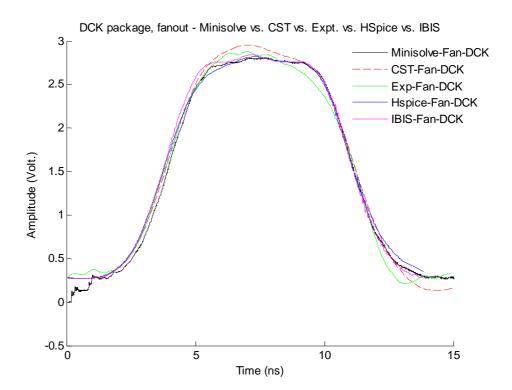

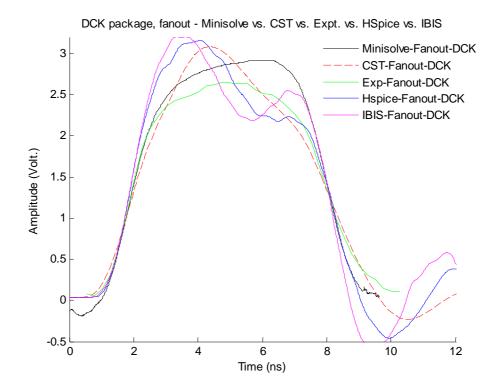

| 6.8.3 Fan-out configuration                               | 215 |

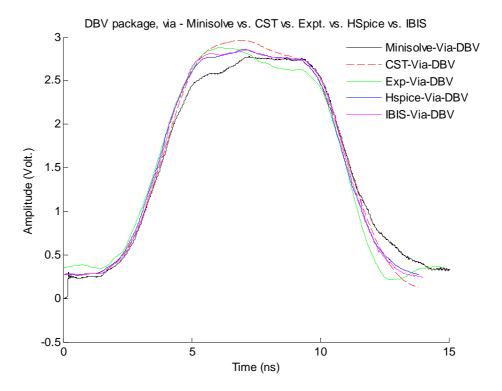

| 6.8.4 Via configuration2                                  | 218 |

| 6.9 Analysis of results                                   | 221 |

| References                                                | 225 |

|                                                           |     |

| Chapter 7 – Conclusion and Future works                   | 227 |

| 7.1 Future scope                                          | 231 |

| References                                                | 232 |

|                                                           |     |

| Appendix                                                  | 233 |

| References                                                | 242 |

### **List of Figures**

#### Chapter 1

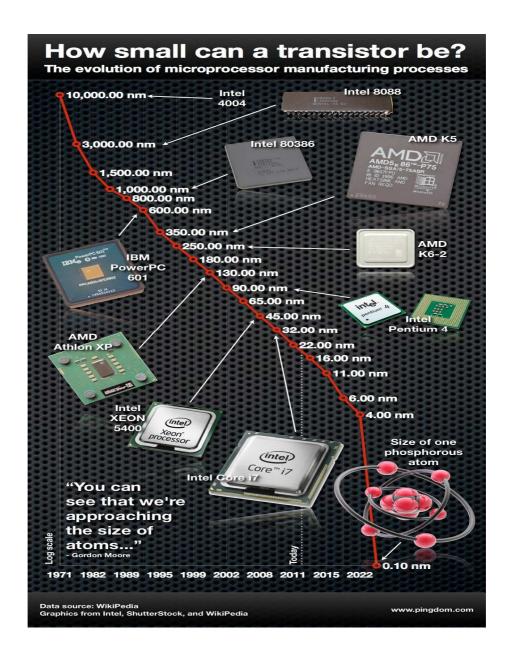

Fig. 1.1 Microprocessor architecture trends

#### Chapter 2

- Fig. 2.1 A typical six layered motherboard (source Intel)

- Fig. 2.2 Metal film resistor

- Fig. 2.3 Frequency dependent impedance plot for a typical thin film resistor

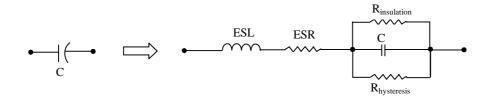

- Fig. 2.4 Equivalent capacitance model

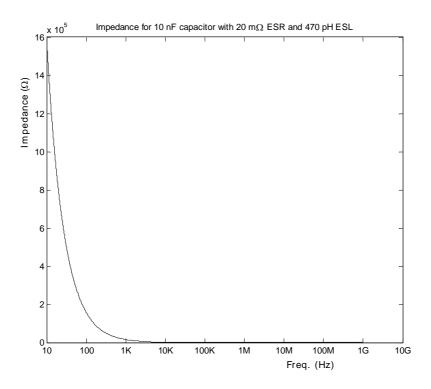

- Fig. 2.5 Frequency dependent impedance plot for a capacitor

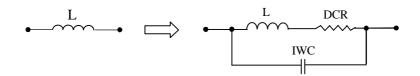

- Fig. 2.6 Equivalent inductance model

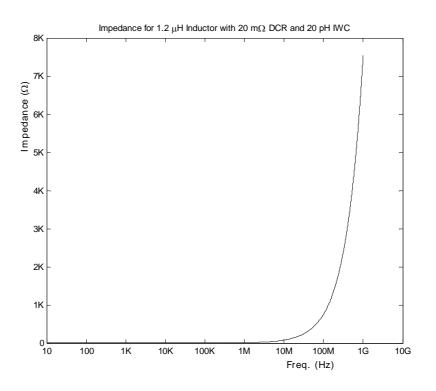

- Fig. 2.7 Frequency dependent impedance plot for an inductor

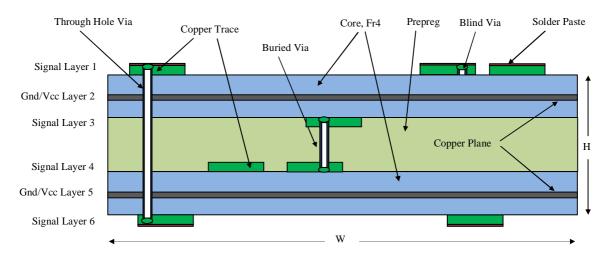

- Fig. 2.8 A six layered PCB overview

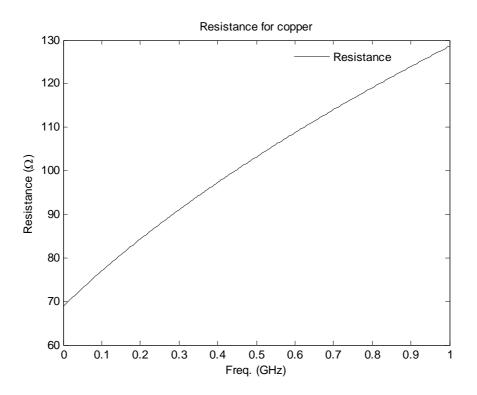

- Fig. 2.9 Resistive behaviour of copper used in PCB traces

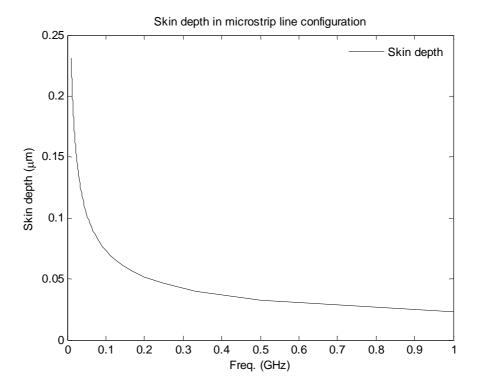

- Fig. 2.10 Frequency dependant skin depth

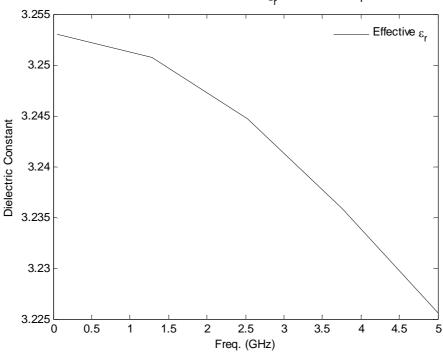

- Fig. 2.11 Effective dielectric constant for a microstrip line

- Fig. 2.12 Transmission line representation using circuit equivalence

- Fig. 2.13 RLC equivalent of an interconnect unit of a transmission line

- Fig. 2.14 Cascading of RLC network

- Fig. 2.15 Cascade representation of transmission line with discontinuity

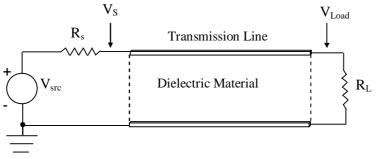

- Fig. 2.16 Transmission line for circuit simulation

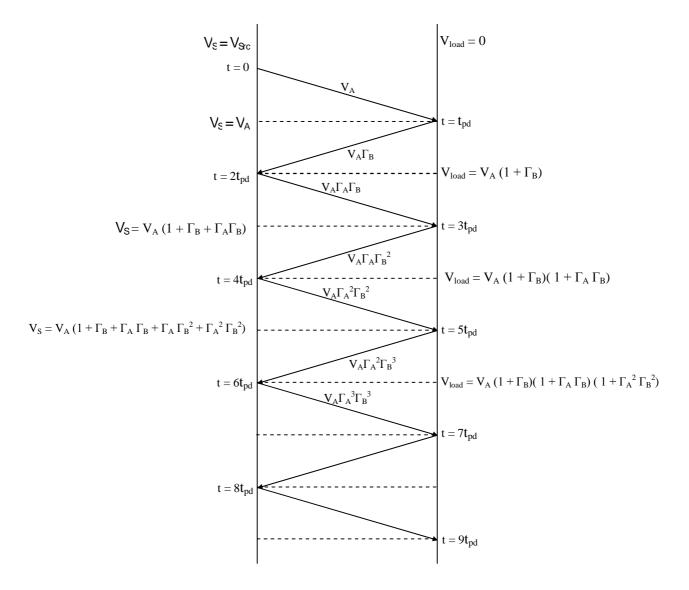

- Fig. 2.17 Lattice diagram for voltage

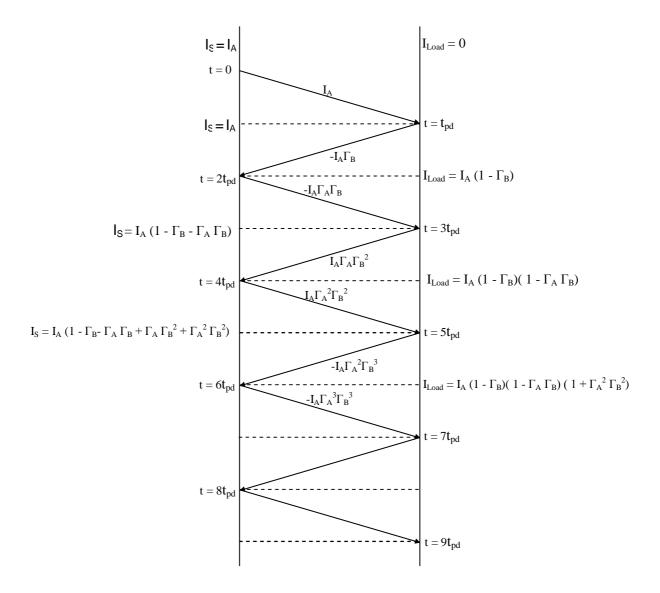

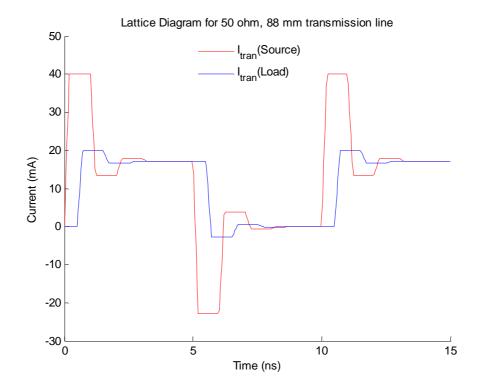

- Fig. 2.18 Lattice diagram for current

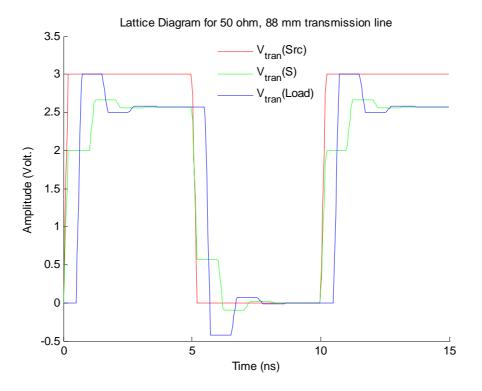

- Fig. 2.19 Voltage in transmission line for  $R_s = 25 \Omega$ ,  $R_L = 150 \Omega$

- Fig. 2.20 Current in transmission line for  $R_s = 25 \Omega$ ,  $R_L = 150 \Omega$

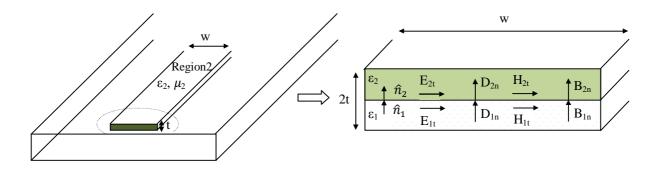

- Fig. 2.21 Boundary condition for a microstrip line

- Fig. 2.22 Perfect Electric Conducting surface

- Fig. 2.23 Perfect Magnetic Conducting surface

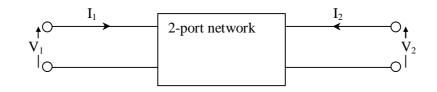

- Fig. 2.24 Z-parameter for a two port network

- Fig. 2.25 S-parameter for a two port network

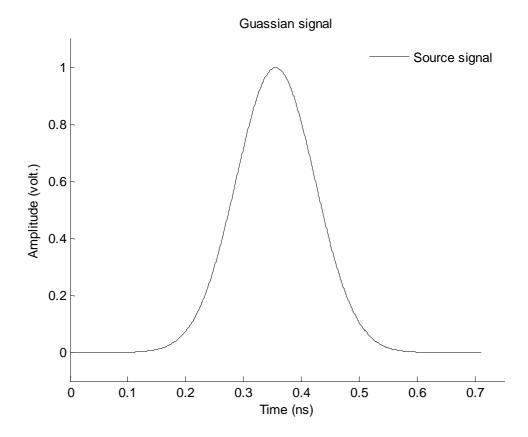

- Fig. 2.26 Gaussian source signal

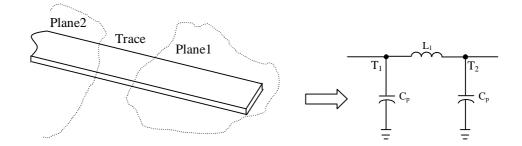

- Fig. 2.27 Trace configuration in split plane

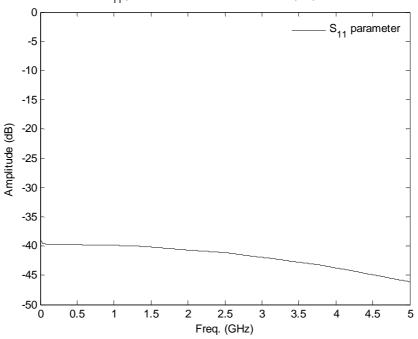

- Fig. 2.28 S<sub>11</sub> parameter for a trace routed over split plane

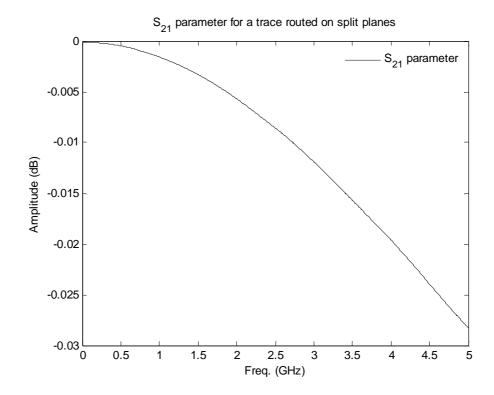

- Fig. 2.29 S<sub>21</sub> parameter for a trace routed over split plane

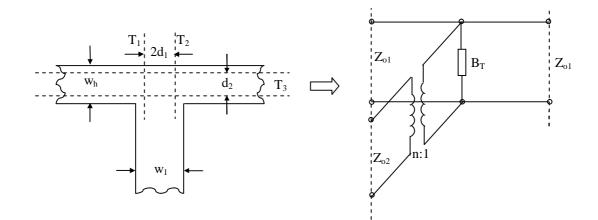

- Fig. 2.30 Tee junction and its equivalent circuit

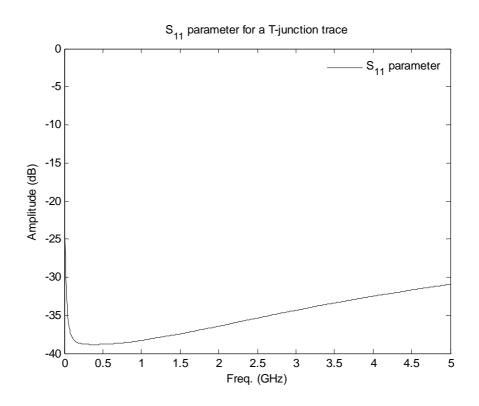

- Fig. 2.31  $S_{11}$  parameter in Tee junction trace

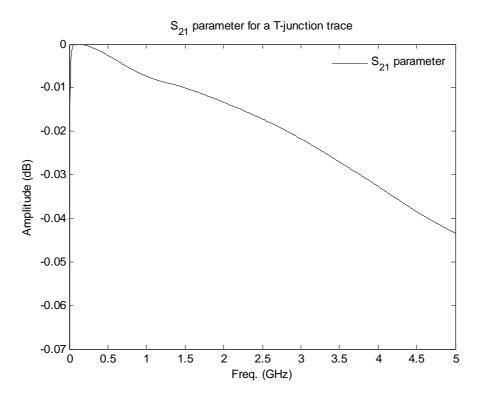

- Fig. 2.32 S<sub>21</sub> parameter in Tee junction trace

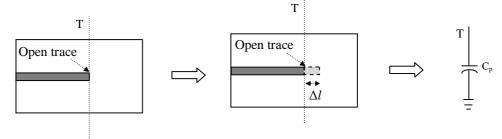

- Fig. 2.33 Open end configuration and its equivalent circuit

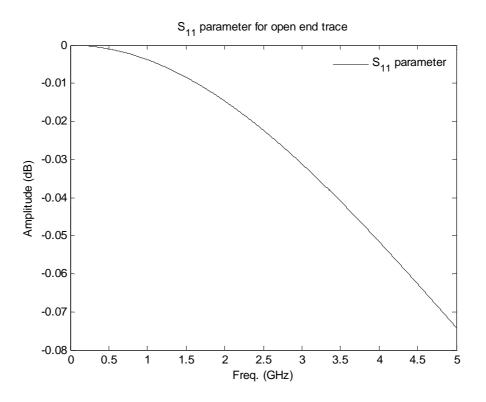

- Fig. 2.34  $S_{11}$  parameter for open end trace

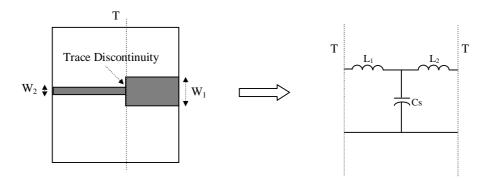

- Fig. 2.35 Step discontinuity in trace width and its equivalent circuit

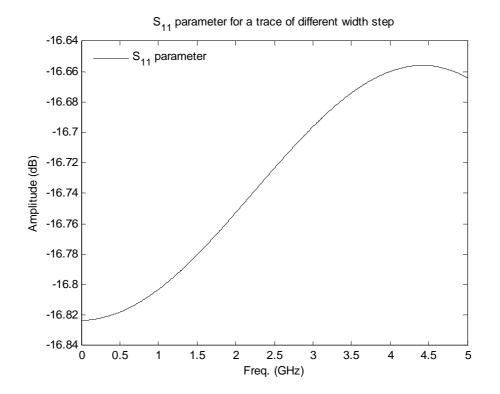

- Fig. 2.36  $S_{11}$  parameter for the step discontinuity

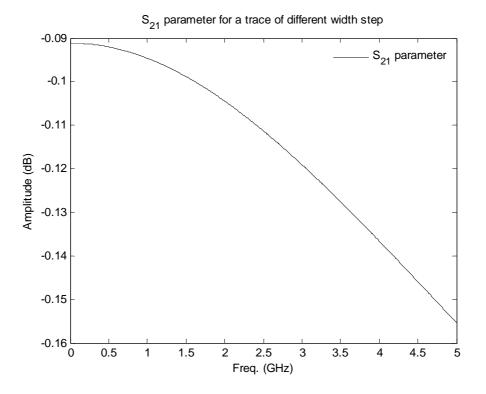

- Fig. 2.37  $S_{21}$  parameter for the step discontinuity

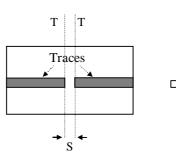

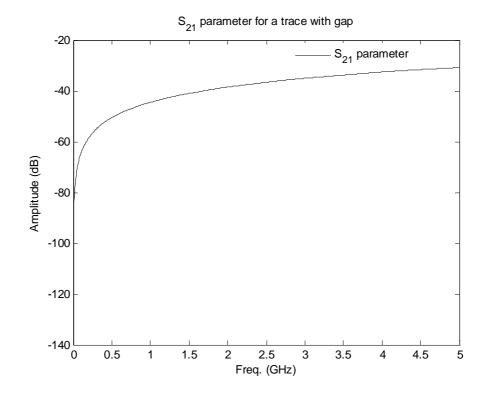

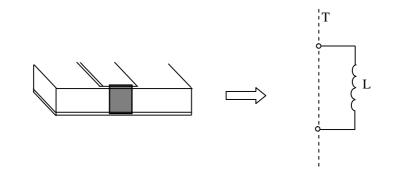

- Fig. 2.38 Gap in trace and its equivalent circuit

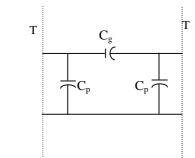

- Fig. 2.39  $S_{11}$  parameter for a gap in trace

- Fig. 2.40 S<sub>21</sub> parameter for a gap in trace

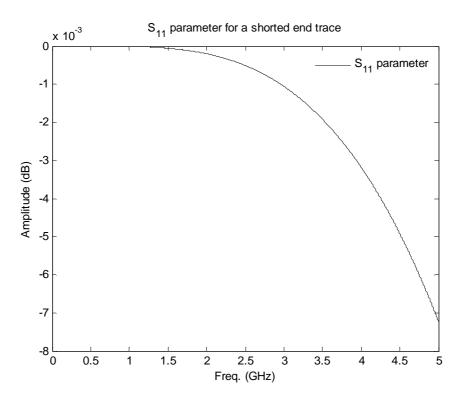

- Fig. 2.41 Shorted end trace and its equivalent circuit

- Fig. 2.42 S<sub>11</sub> parameter for Shorted end trace

#### Chapter 3

Fig. 3.1 Yee's diagram

Fig. 3.2 Triangular meshing of a microstrip line

#### **Chapter 4**

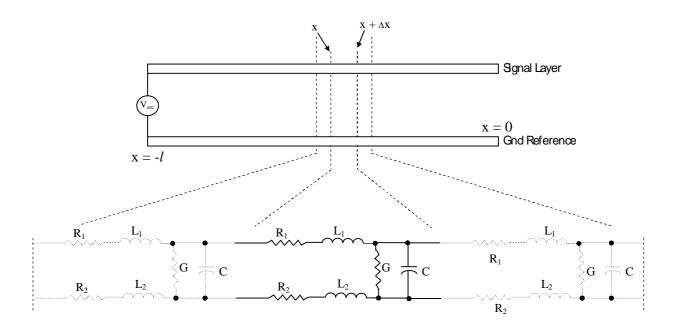

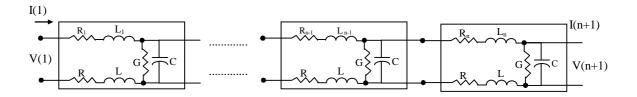

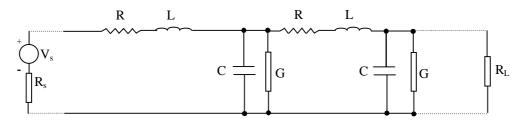

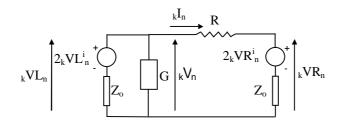

- Fig. 4.1 Transmission line analysis using [RLGC]

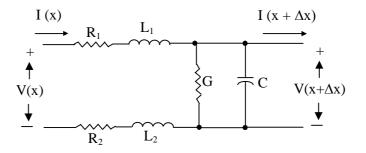

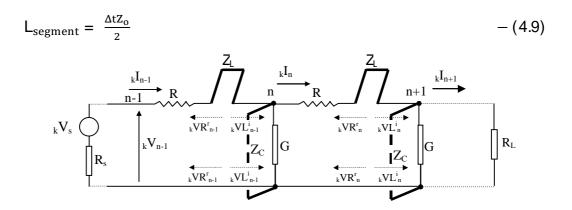

- Fig. 4.2 TLM representation of a transmission line

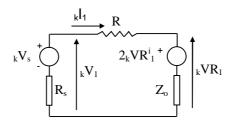

- Fig. 4.3 Equivalent circuit for source circuit

- Fig. 4.4 Equivalent circuit for [RLGC] circuit

- Fig. 4.5 Equivalent circuit for load circuit

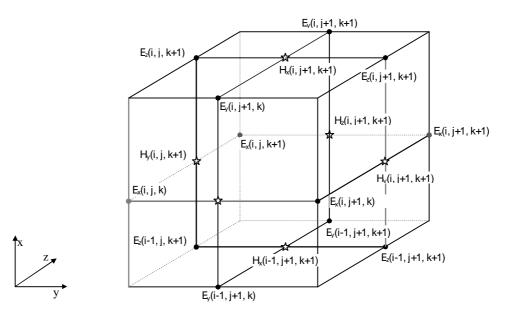

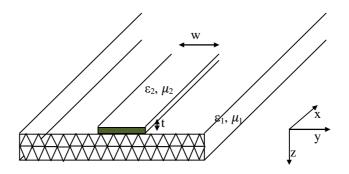

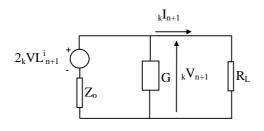

- Fig. 4.6 Cubical meshing of a microstrip line

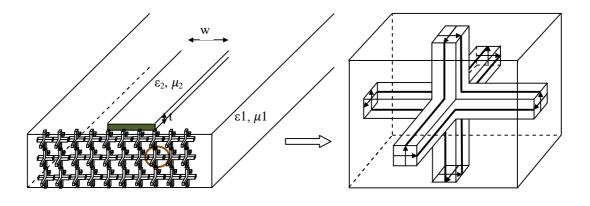

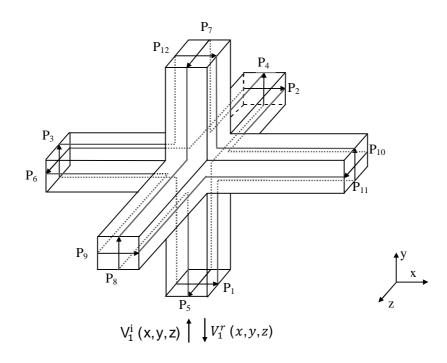

- Fig. 4.7 A typical SCN node

- Fig. 4.8 A symmetrical condensed node with field ports

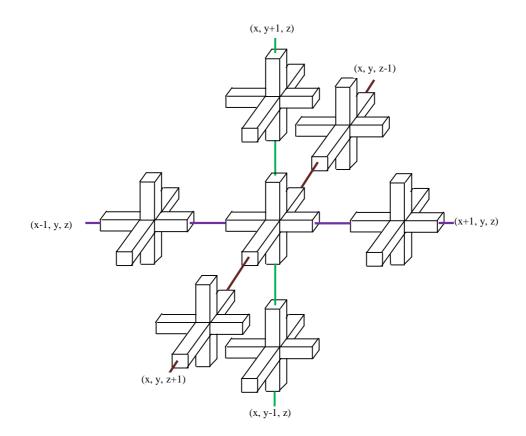

- Fig. 4.9 Wave propagation in 3D TLM node

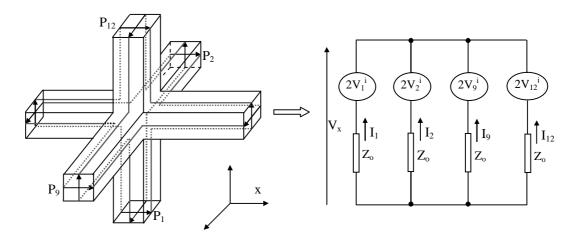

- Fig. 4.10 Equivalent Thevenin configuration for SCN node in x direction

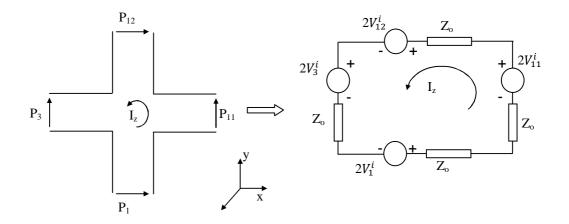

- Fig. 4.11 Scattering in x-y plane for SCN node

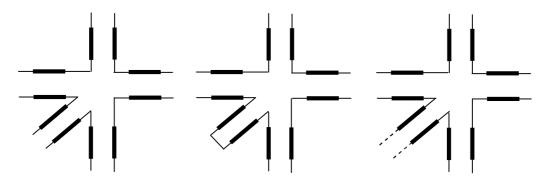

- Fig. 4.12 Open circuit stub

- Fig. 4.13 Short circuit stub

- Fig. 4.14 Lossy circuit stub

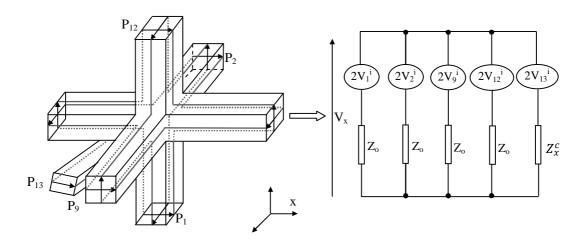

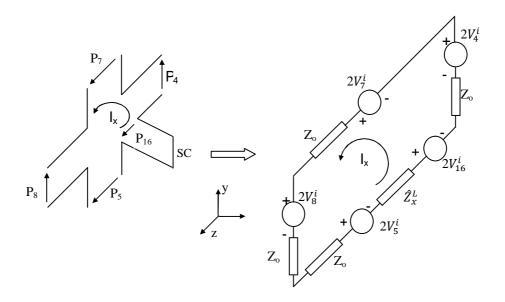

Fig. 4.15 Equivalent Thevenin configuration for HSCN node in x – direction

- Fig. 4.16 Scattering and equivalent Thevenin circuit in y-z plane for HSCN node

- Fig. 4.17 Connecting boundary condition for TLM simulation

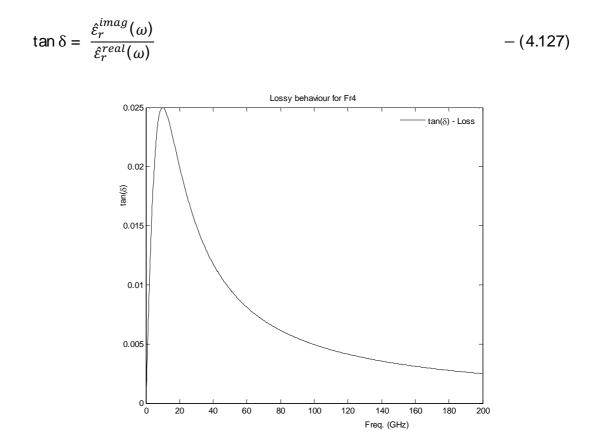

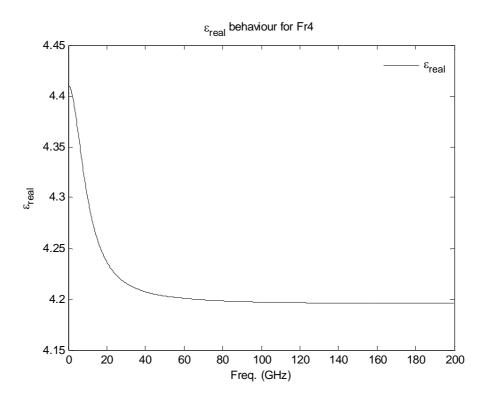

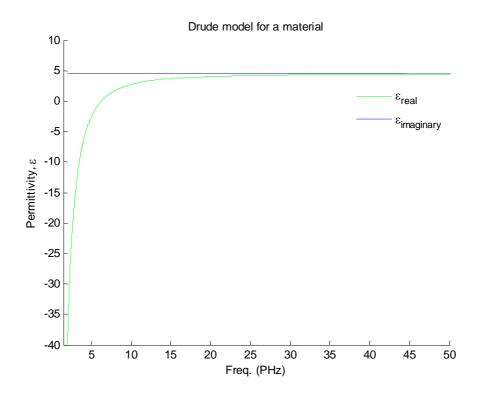

- Fig. 4.18 Tangent loss of dielectric behaviour for Fr4 using Debye model

- Fig. 4.19 Real part of dielectric behaviour for Fr4 using Debye model

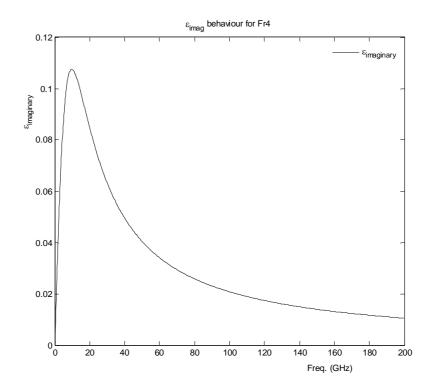

- Fig. 4.20 Imaginary part of dielectric behaviour for Fr4 using Debye model

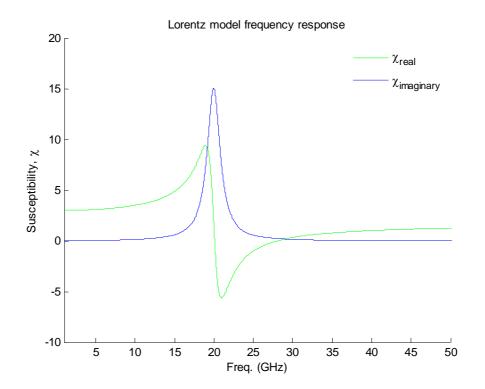

Fig. 4.21 Susceptibility behaviour of a Lorentz model

Fig. 4.22 Drude model of a material with  $\varepsilon_{\infty} = 4.5$

#### **Chapter 5**

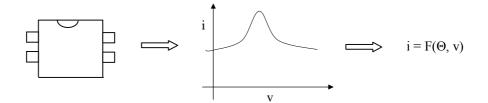

- Fig. 5.1 Modelling of a device

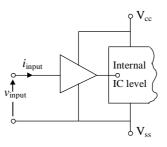

- Fig. 5.2 Macromodel for a generic input buffer

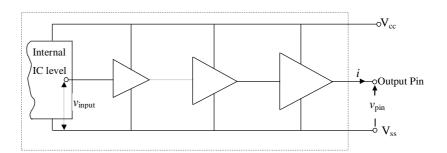

- Fig. 5.3 Macromodel for a generic output buffer

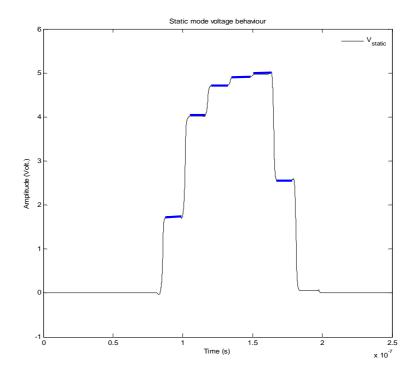

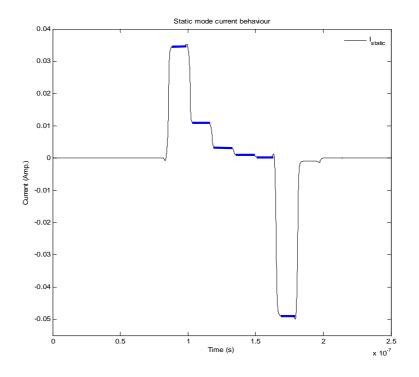

- Fig. 5.4 Buffer's voltage response for extracting the static characteristics  $i_{sH}$  and  $i_{sL}$

- Fig. 5.5 Buffer's current response for extracting the static characteristics  $i_{sH}$  and  $i_{sL}$

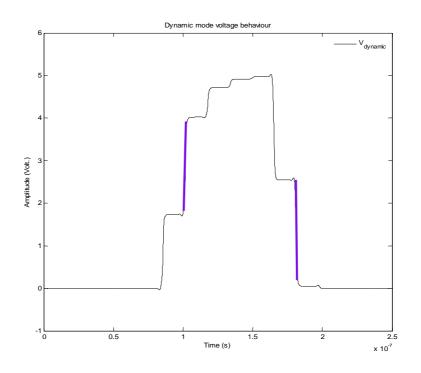

- Fig. 5.6 Buffer's voltage response for extracting the dynamic characteristic  $i_{dH}$  and  $i_{dL}$

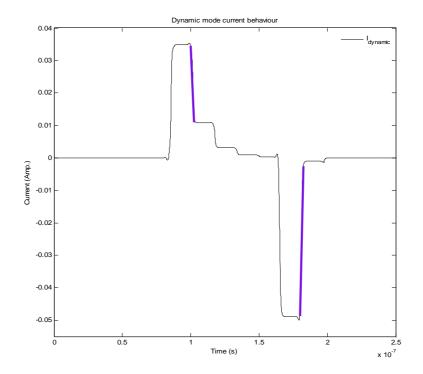

- Fig. 5.7 Buffer's current response for extracting the dynamic characteristics  $i_{dH}$  and  $i_{dL}$

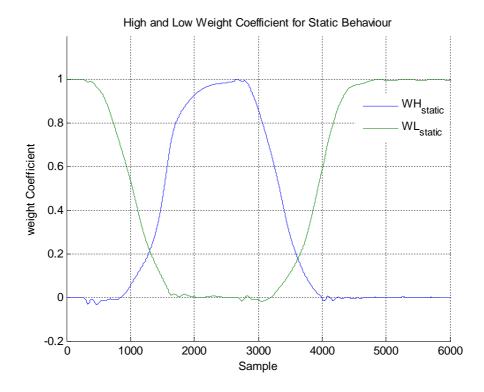

- Fig. 5.8 Driving a buffer for obtaining weight coefficients for static condition

- Fig. 5.9 Driving a buffer for obtaining weight coefficients for dynamic condition

Fig. 5.10 Equivalent circuit of an input buffer in an IBIS model

Fig. 5.11 Equivalent circuit of an output buffer in an IBIS model

Fig. 5.12 Ground clamp characteristic for a typical input buffer

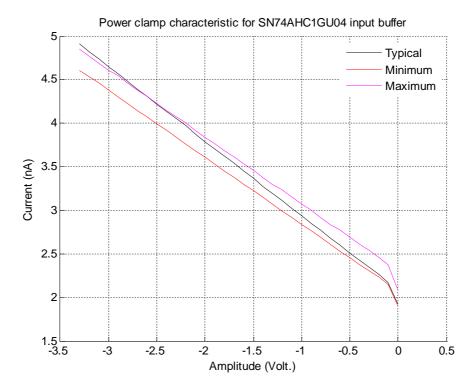

Fig. 5.13 Power clamp characteristic for a typical input buffer

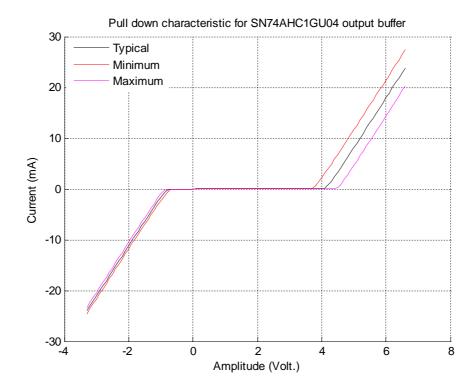

Fig. 5.14 Pull down characteristic for a typical output buffer

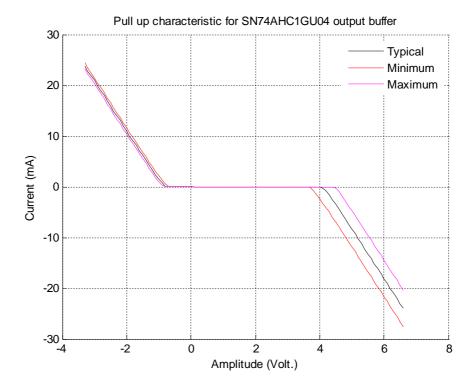

Fig. 5.15 Pull up characteristic for a typical output buffer

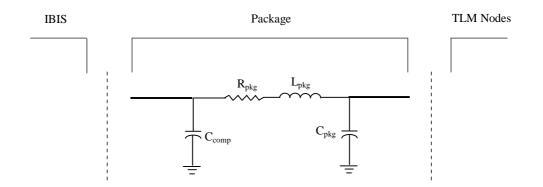

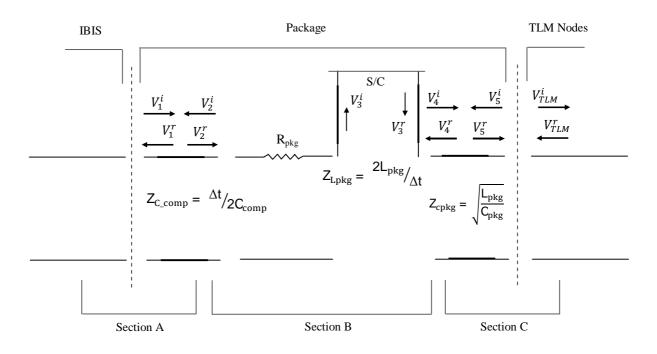

Fig. 5.16 Interface between IBIS and TLM for input/output buffer

Fig. 5.17 Electrical equivalent circuit of IBIS and TLM

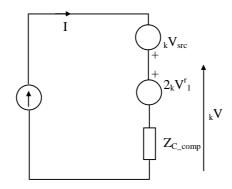

- Fig. 5.18 Electrical equivalent circuit for IBIS output buffer and TLM section A

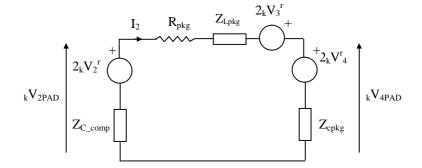

- Fig. 5.19 Electrical equivalent circuit for IBIS output buffer and TLM section B

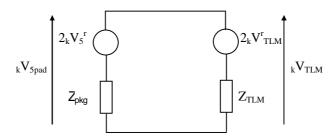

- Fig. 5.20 Electrical equivalent circuit for IBIS output buffer and TLM section C

- Fig. 5.21 Electrical equivalent circuit of IBIS input buffer and TLM section A

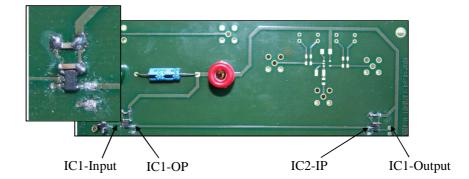

- Fig. 5.22 PCB used for the measurement

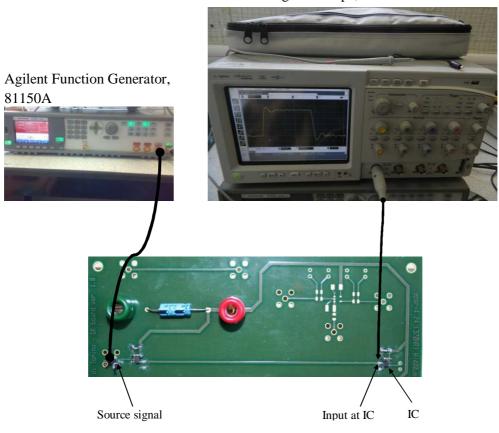

- Fig. 5.23 Setup for experimental measurement

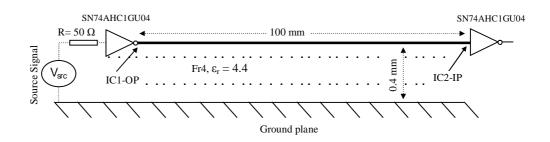

- Fig. 5.24 Simulation setup for transmitter receiver

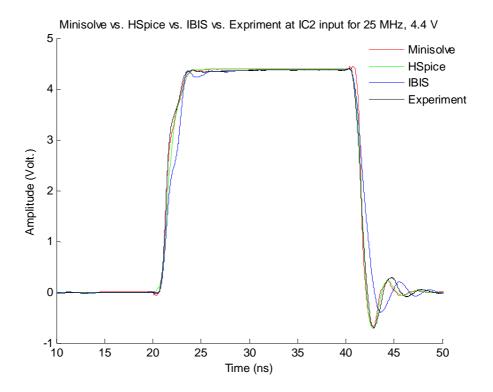

- Fig. 5.25 Comparison at the output of first IC (IC1-OP)

- Fig. 5.26 Comparison at the input of second IC (IC2-IP)

- Fig. 5.27 Comparison at the output of first IC (IC1-OP1)

- Fig. 5.28 Comparison at the input of second IC (IC2-IP1)

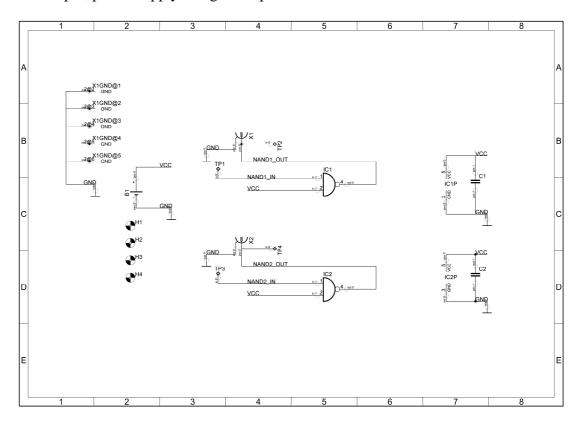

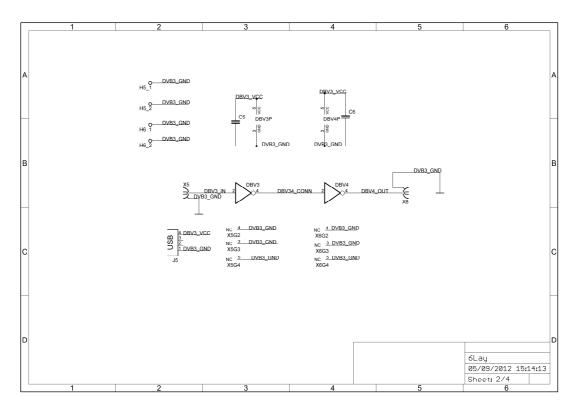

- Fig. 5.29 Eagle schematics for crosstalk configuration

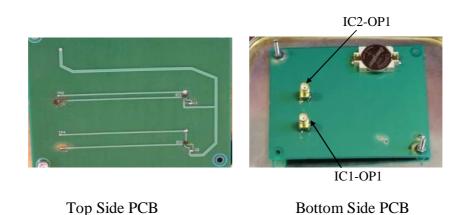

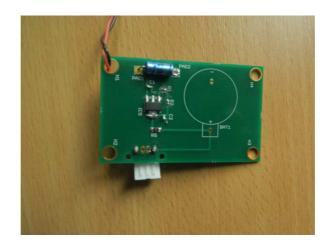

- Fig. 5.30 PCB used for the measurement

- Fig. 5.31 PCB attached to the box for the measurement

- Fig. 5.32 Side view of the PCB

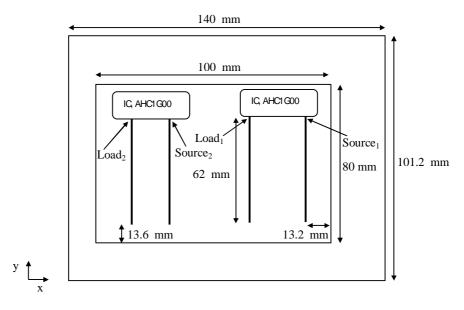

- Fig. 5.33 Top view of the PCB

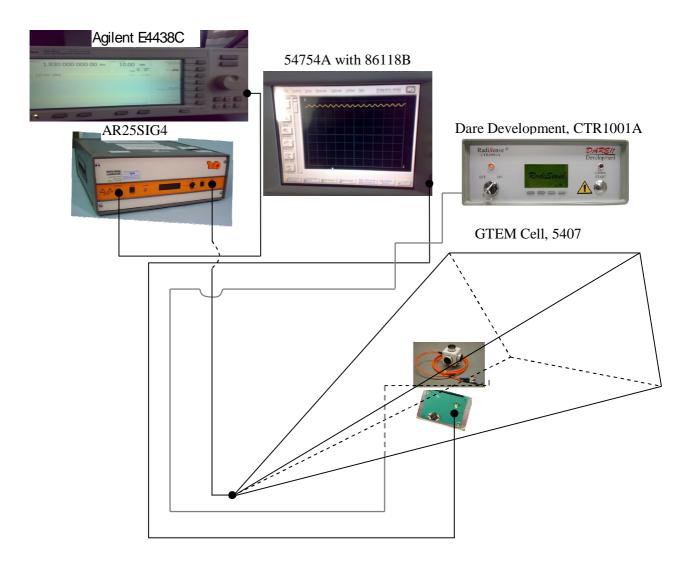

- Fig. 5.34 Experimental setup for the circuit exposed to RF Signal at 1 GHz /1.83 GHz

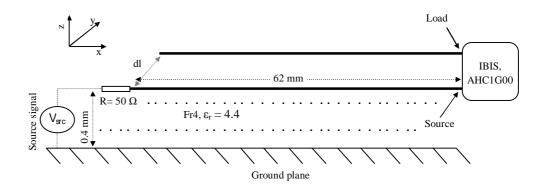

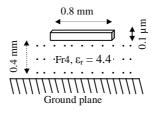

- Fig. 5.35 Lateral/side view of the crosstalk configuration

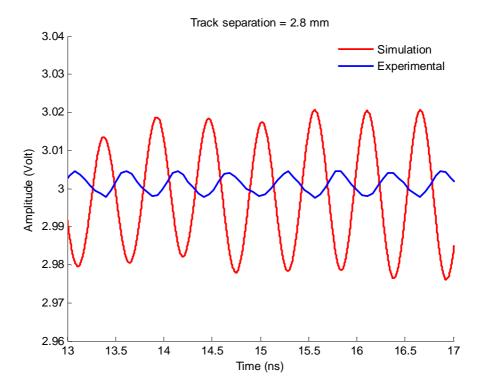

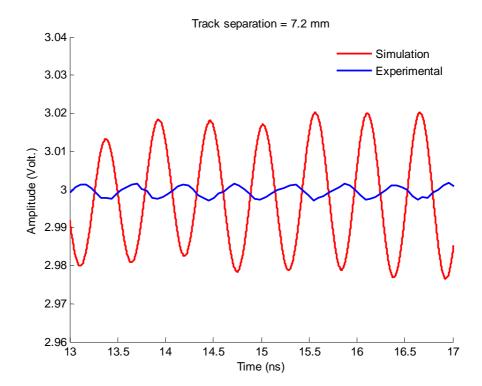

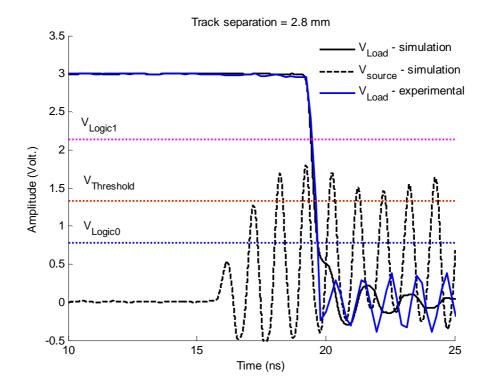

- Fig. 5.36 Switching behaviour for dl = 2.8 mm with 1.83 GHz, 70 V/m field

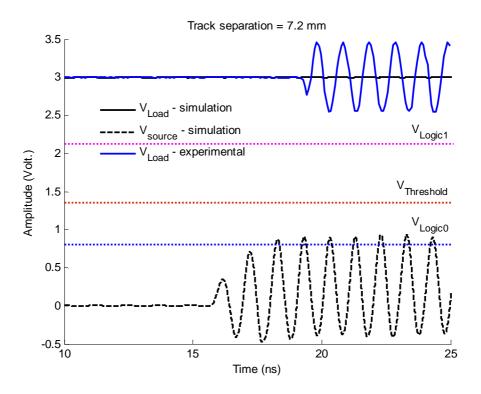

- Fig. 5.37 Switching behaviour for dl = 7.2 mm with 1.83 GHz, 70 V/m field

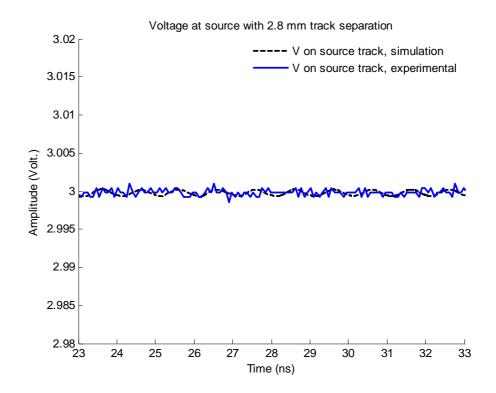

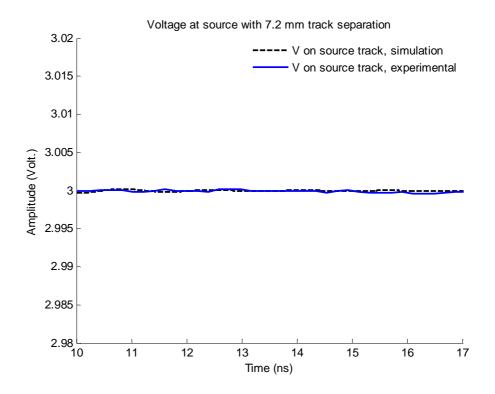

- Fig. 5.38 Output response for dl = 2.8 mm with no external source

- Fig. 5.39 Output response for dl = 7.2 mm with no external source

- Fig. 5.40 Switching behaviour for dl = 7.2 mm with thin wire at input

- Fig. 5.41 Switching behaviour for dl = 2.8 mm with thin wire at input

#### **Chapter 6**

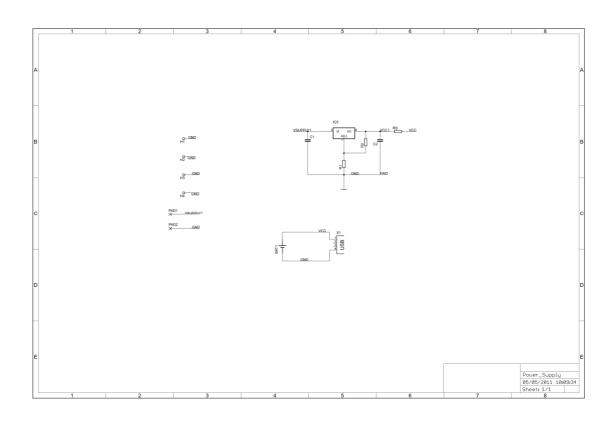

- Fig. 6.1 Eagle schematics for power supply board

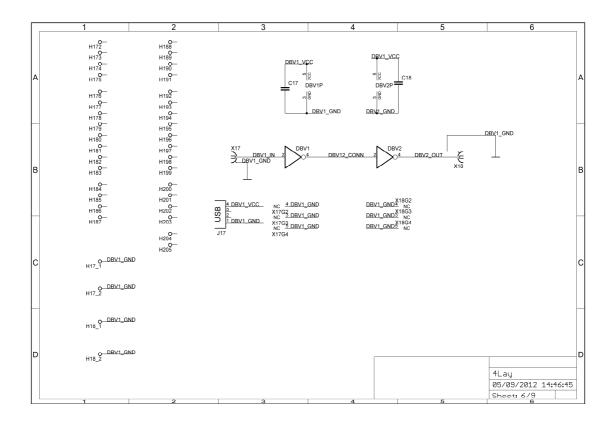

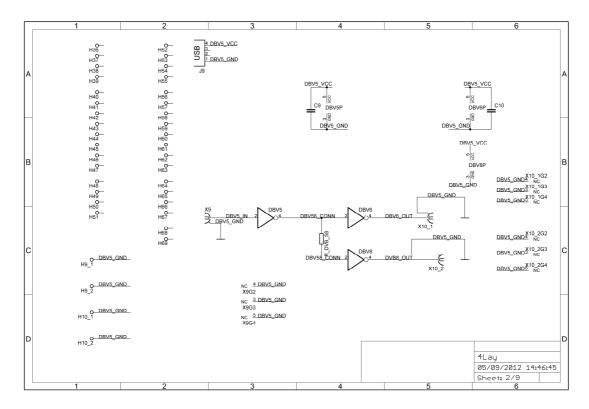

- Fig. 6.2 Eagle schematics for DBV package with straight line configuration

- Fig. 6.3 Eagle schematics for DBV package with fan-out configuration

- Fig. 6.4 Eagle schematics for DBV package with via configuration

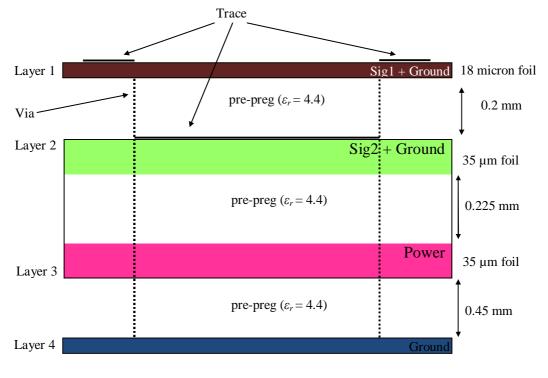

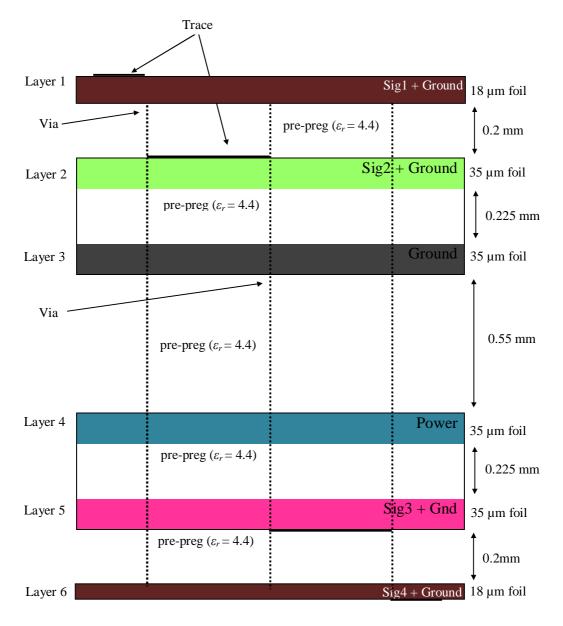

- Fig. 6.5 Four layer stack-up

- Fig. 6.6 Six layer stack-up

- Fig. 6.7 Power supply board to power all the PCB configurations

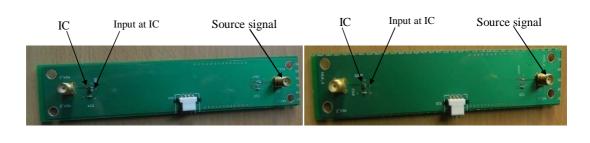

- Fig. 6.8 DBV package, Straight line PCB

- Fig. 6.9 DCK package, Straight line PCB

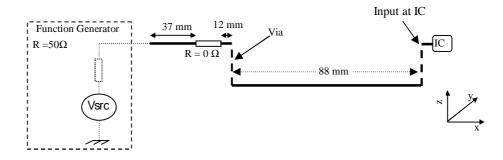

- Fig. 6.10 Straight-line configuration equivalent model

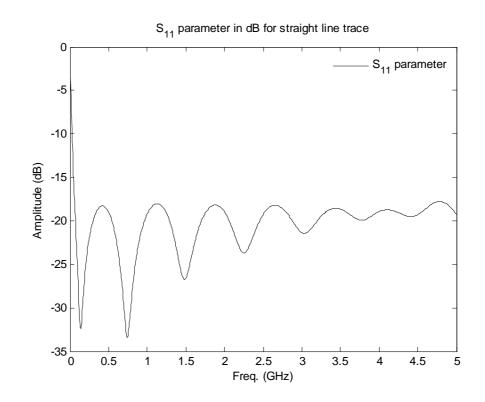

- Fig. 6.11 S<sub>11</sub> parameter of a straight line configuration

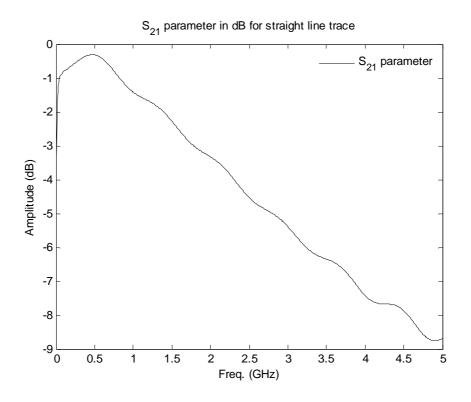

- Fig. 6.12 S<sub>21</sub> parameter of a straight line configuration

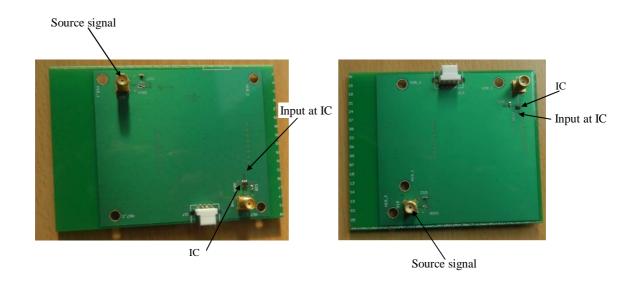

- Fig. 6.13 DBV package, Right Angle PCB

- Fig. 6.14 DCK package, Right Angle PCB

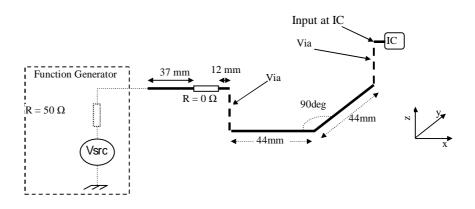

- Fig. 6.15 Right Angle configuration equivalent model

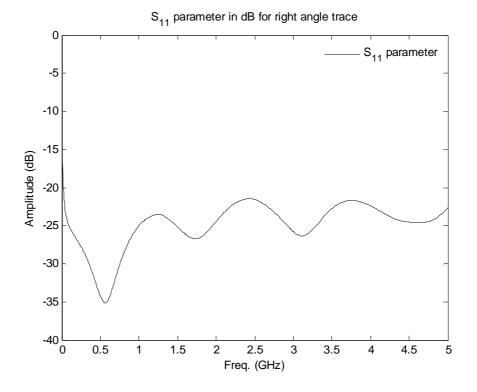

- Fig. 6.16  $S_{11}$  parameter of a right angle configuration

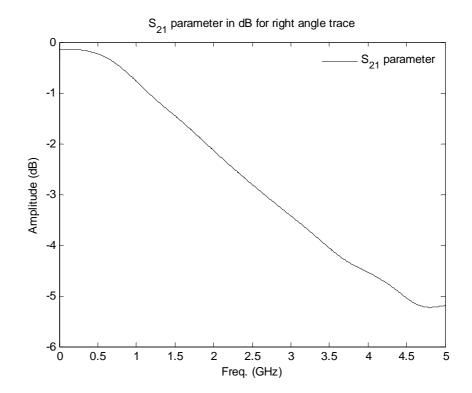

- Fig. 6.17  $S_{21}$  parameter of a right angle configuration

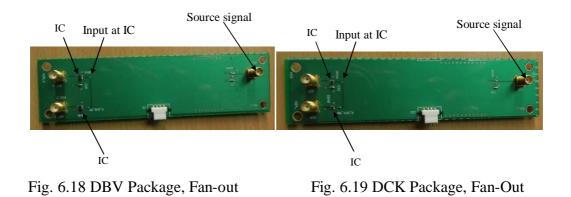

- Fig. 6.18 DBV package, Fan-out PCB

- Fig. 6.19 DCK package, Fan-out PCB

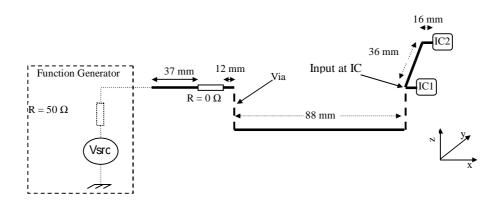

- Fig. 6.20 Fan-out configuration equivalent model

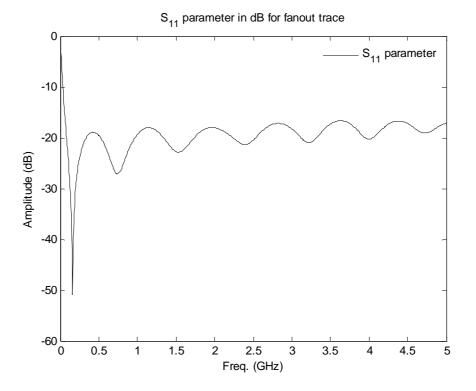

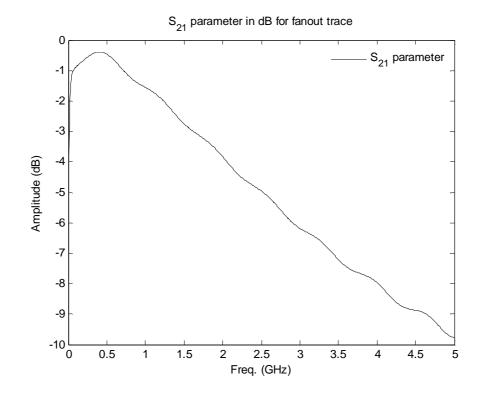

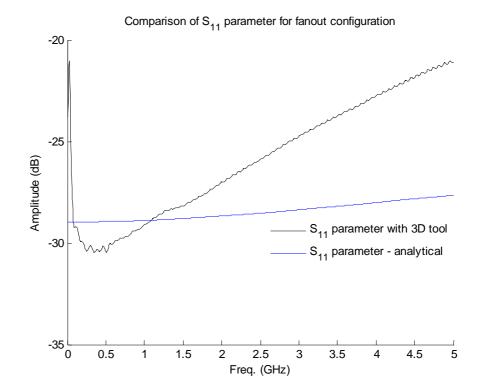

- Fig. 6.21 S<sub>11</sub> parameter of a fan-out configuration

- Fig. 6.22  $S_{21}$  parameter of a fan-out configuration

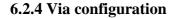

- Fig. 6.23 DBV package, Via PCB

- Fig. 6.24 DCK package, Via PCB

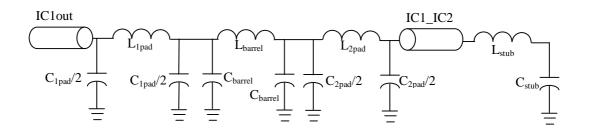

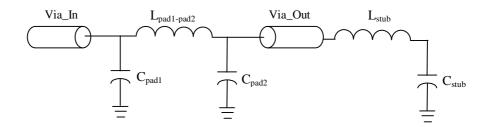

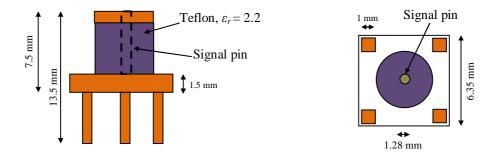

- Fig. 6.25 Via configuration equivalent model

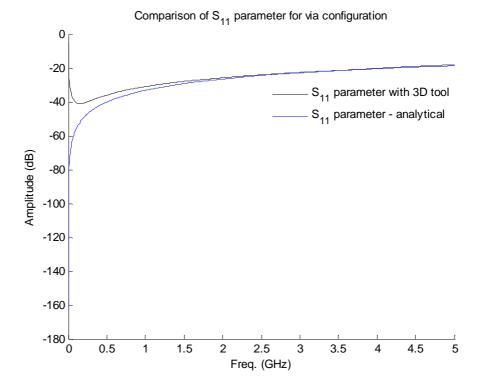

- Fig. 6.26  $S_{11}$  parameter for via configuration

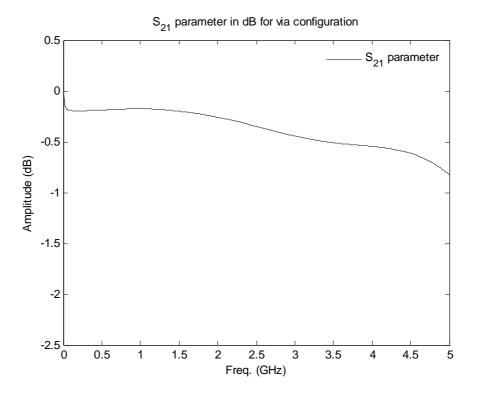

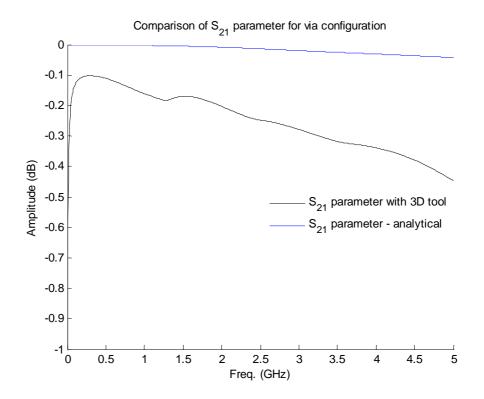

- Fig. 6.27  $S_{21}$  parameter for via configuration

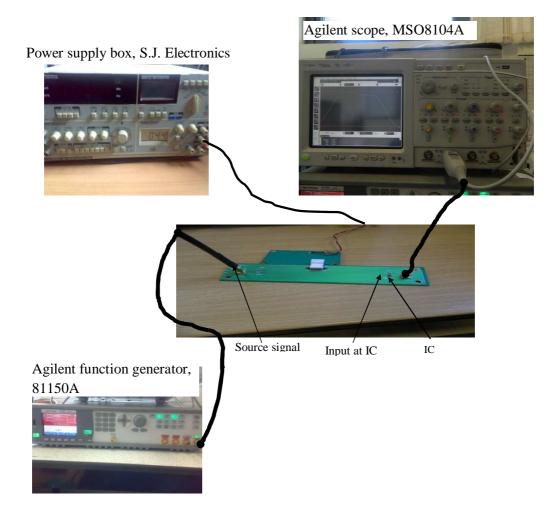

- Fig. 6.28 Measurement setup for PCBs

- Fig. 6.29 Physical via representation in a four layer PCB

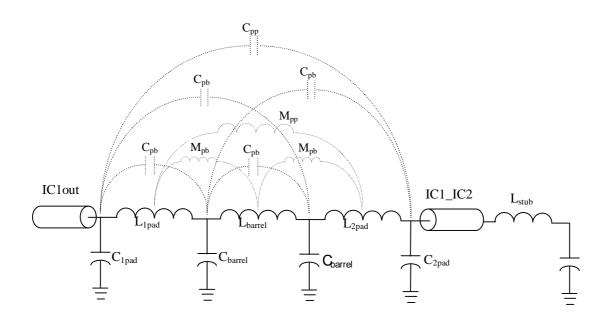

- Fig. 6.30 Coupled equivalent circuit representation of via

- Fig. 6.31 Distributed equivalent circuit representation of via

- Fig. 6.32 Simplified equivalent circuit of via

- Fig. 6.33 S<sub>11</sub> parameter for via using 3D tool and analytical expression

- Fig. 6.34 S<sub>21</sub> parameter for via using 3D tool and analytical expression

- Fig. 6.35 Right Angle bend representation

- Fig. 6.36 Equivalent circuit for a right angle bend

- Fig. 6.37  $S_{11}$  parameter for right angle bends using 3D tool and analytical expression

- Fig. 6.38 S<sub>21</sub> parameter for right angle bends using 3D tool and analytical expression

- Fig. 6.39 Fan-out representation

- Fig. 6.40 S<sub>11</sub> parameter for fan-out using 3D tool and analytical expression

- Fig. 6.41 S<sub>21</sub> parameter for fan-out using 3D tool and analytical expression

- Fig. 6.42 SMA connector representation

- Fig. 6.43 Equivalent circuit for SMA connector

- Fig. 6.44 71 MHz source signal for all the PCBs with 50  $\Omega$  source resistance

- Fig. 6.45 100 MHz source signal for all the PCBs with 5  $\Omega$  source resistance

- Fig. 6.46 Schematic representation of the experimental setup in CST design studio

- Fig. 6.47 Lateral view of the straight line configuration in Minisolve

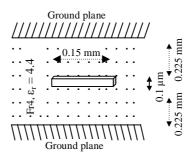

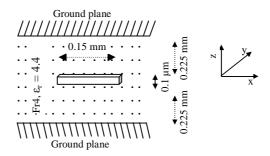

- Fig. 6.48 Cross-sectional view of the straight line configuration in Minisolve

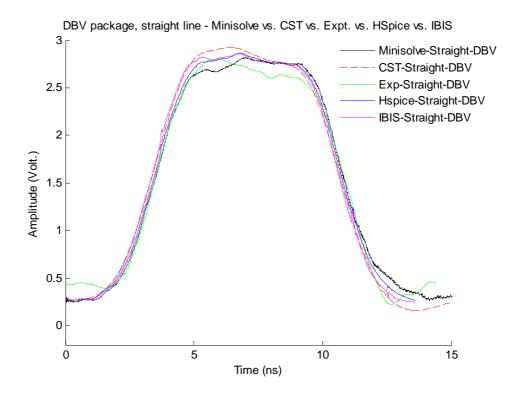

- Fig. 6.49 Straight line configuration, DBV package with 50  $\Omega$  source resistance

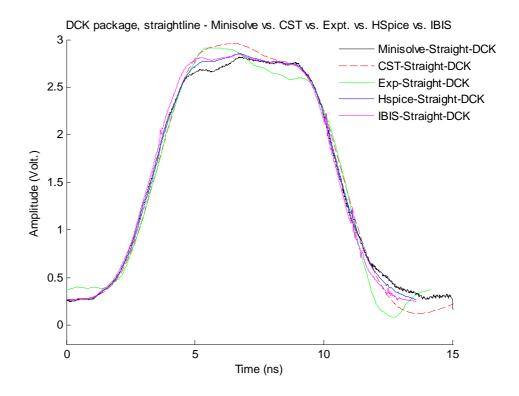

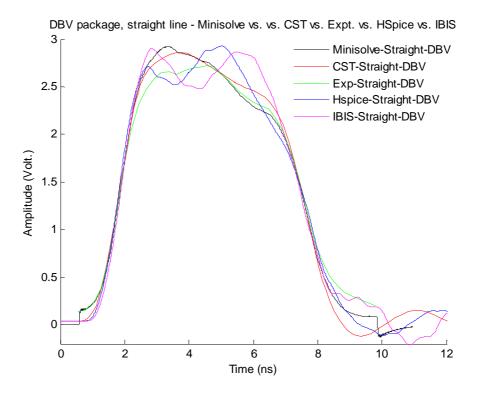

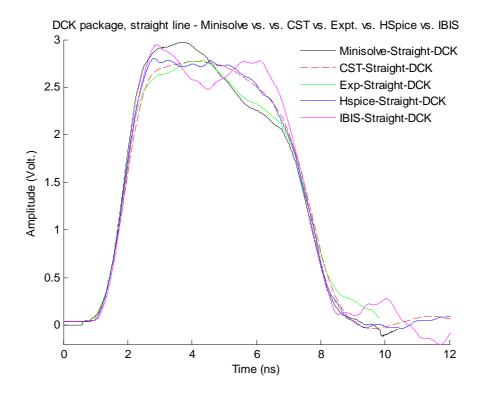

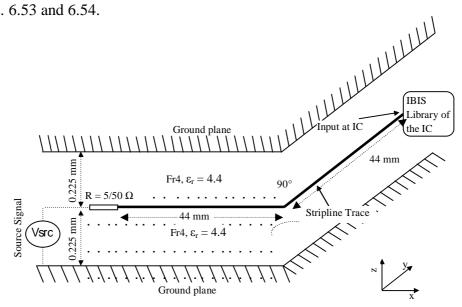

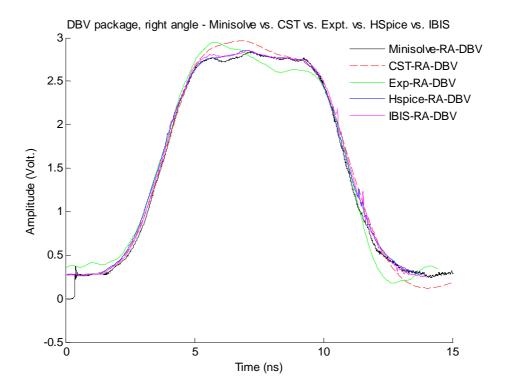

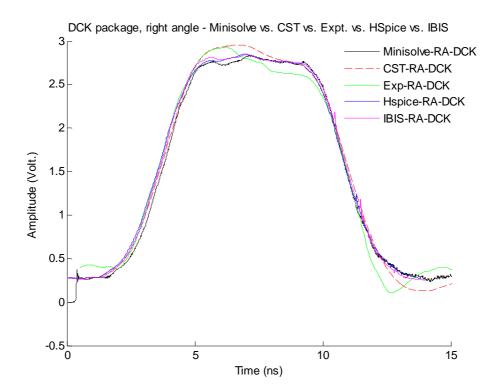

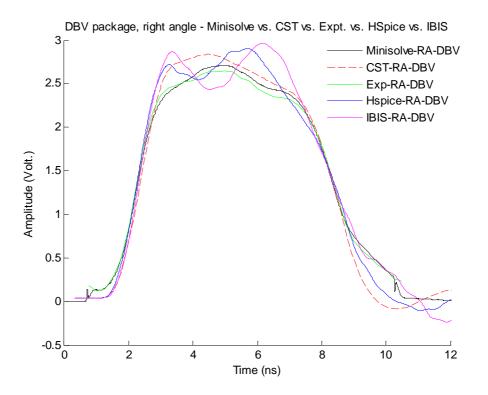

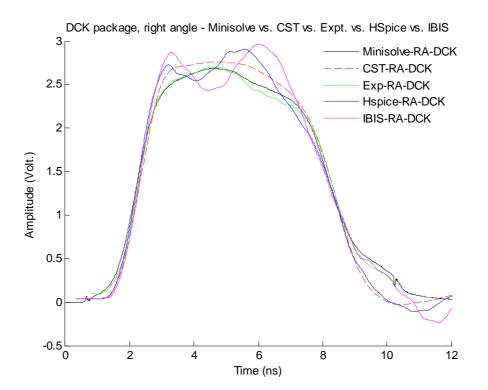

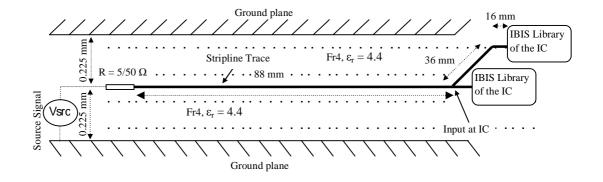

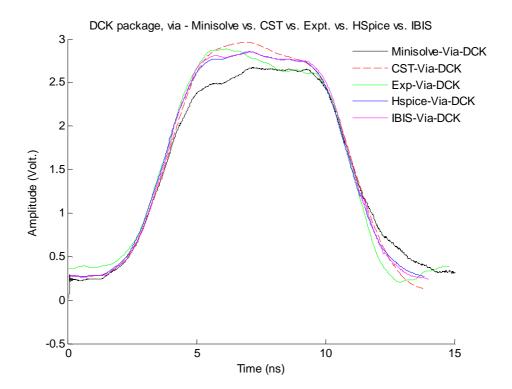

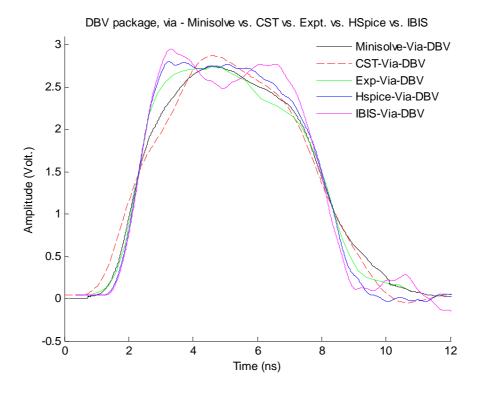

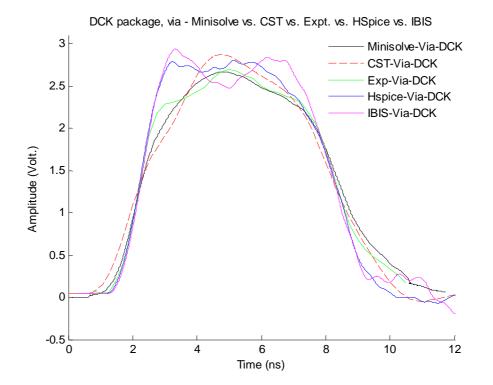

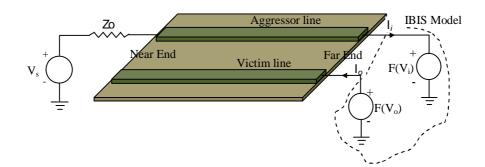

Fig. 6.50 Straight line configuration, DCK package with 50  $\Omega$  source resistance Fig. 6.51 Straight line configuration, DBV package with 5  $\Omega$  source resistance Fig. 6.52 Straight line configuration, DCK package with 5  $\Omega$  source resistance Fig. 6.53 Lateral view of the right angle configuration in Minisolve Fig. 6.54 Cross-sectional view of the right angle configuration in Minisolve Fig. 6.55 Right Angle configuration, DBV package with 50  $\Omega$  source resistance Fig. 6.56 Right Angle configuration, DCK package with 50  $\Omega$  source resistance Fig. 6.57 Right Angle configuration, DBV package with 5  $\Omega$  source resistance Fig. 6.58 Right Angle configuration, DCK package with 5  $\Omega$  source resistance Fig. 6.59 Lateral view of the fan-out configuration in Minisolve Fig. 6.60 Cross-sectional view of the fan out configuration in Minisolve Fig. 6.61 Fan-out configuration, DBV package with 50  $\Omega$  source resistance Fig. 6.62 Fan-out configuration, DCK package with 50  $\Omega$  source resistance Fig. 6.63 Fan-out configuration, DBV package with 5  $\Omega$  source resistance Fig. 6.64 Fan-out configuration, DCK package with 5  $\Omega$  source resistance Fig. 6.65 Lateral view of the via configuration in Minisolve Fig. 6.66 Cross-sectional view of the via configuration in Minisolve Fig. 6.67 Via configuration, DBV package with 50  $\Omega$  source resistance Fig. 6.68 Via configuration, DCK package with 50  $\Omega$  source resistance Fig. 6.69 Via configuration, DBV package with 5  $\Omega$  source resistance Fig. 6.70 Via configuration, DCK package with 5  $\Omega$  source resistance

#### Appendix A

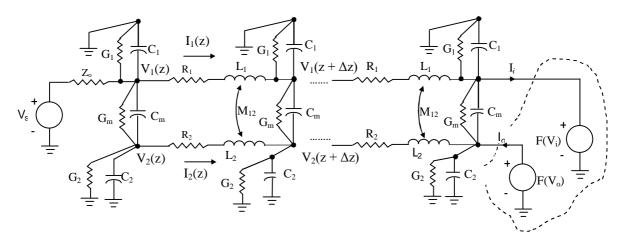

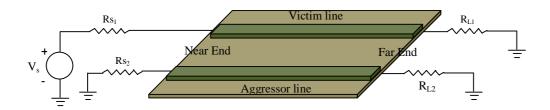

Fig. 1 Crosstalk in two parallel traces

Fig. 2 Electrical circuit representation of a crosstalk

- Fig. 3 Crosstalk structure

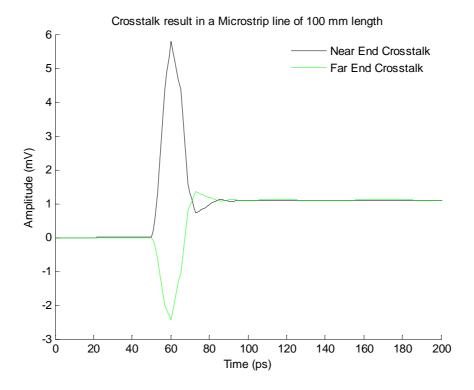

- Fig. 4 Crosstalk response in multi-conductor lines

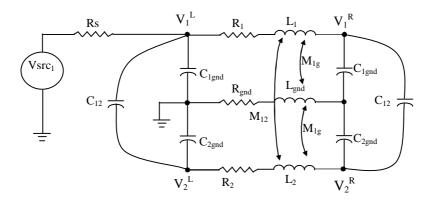

- Fig. 5 Equivalent circuit of a coplanar Microstrip line

# **List of Tables**

- Table 6.1 RLC value for package

- Table 6.2 RLC value for input pin

- Table 6.3 RLC value for output pin

- Table 6.4 Minisolve throughput

- Table 6.5 Other software tools throughput

# Acronyms

| ABC   | Absorbing Boundary Condition                       |

|-------|----------------------------------------------------|

| AC    | Alternate Current                                  |

| ASCII | American Standard Code for Information Interchange |

| BEM   | Boundary Element Method                            |

| BGA   | Ball Grid Array                                    |

| BNC   | Bayonet Neill-Concelman                            |

| CEM   | Computational Electromagnetic                      |

| СМ    | Common Mode                                        |

| CPU   | Central Processing Unit                            |

| CST   | Computer Simulation Tool                           |

| dB    | Decibel                                            |

| DC    | Direct Current                                     |

| DCR   | DC Resistance                                      |

| DDR   | Dynamic Data Rate                                  |

| DM    | Differential Mode                                  |

| EDA   | Electronic Design Automation                       |

| EFIE  | Electric Field Integral Equation                   |

| EM    | Electromagnetic                                    |

| EMC   | Electromagnetic Compatibility                      |

| EMI   | Electromagnetic Interference                       |

| ESR   | Equivalent Series Resistance                       |

| ESL   | Equivalent Series Inductance                       |

| EU    | European Union                                     |

| Exp   | Experiment                                         |

| FCC   | Federal Commission Committee                       |

| FDTD   | Finite Difference Time Domain                              |

|--------|------------------------------------------------------------|

| FEA    | Finite Element Analysis                                    |

|        |                                                            |

| FEM    | Finite Element Method                                      |

| FEXT   | Far End Crosstalk                                          |

| Fr4    | Flame Retardant 4                                          |

| GSCN   | General Symmetrical Condensed Node                         |

| GTEM   | Gigahertz Transverse Electromagnetic                       |

| HFSS   | High Frequency Structure Simulator                         |

| HSCN   | Hybrid Symmetrical Condensed Node                          |

| HSPICE | Hailey Simulation Program with Integrated Circuit Emphasis |

| IBIS   | Input Output Buffer Information Specification              |

| IC     | Integrated Circuit                                         |

| I/O    | Input/Output                                               |

| IPC    | Institute for Printed Circuits                             |

| IWC    | Inter-Winding Capacitance                                  |

| LGA    | Land Grid Array                                            |

| Li-Ion | Lithium-Ion                                                |

| MPIE   | Mixed Potential Integral Equation                          |

| PCB    | Printed Circuit Board                                      |

| PCIE   | Peripheral Component Interface Express                     |

| PD     | Propagation Delay                                          |

| PDE    | Partial Differential Equation                              |

| PEC    | Perfect Electric Conductor                                 |

| РМС    | Perfect Magnetic Conductor                                 |

| MoM    | Method of Moment                                           |

| MSO    | Mixed Signal Oscilloscope                                  |

| NEXT   | Near End Crosstalk                                         |

| RBF    | Radial Basis Function                                      |

|        |                                                            |

| RG58  | Radio Guide 58                                      |

|-------|-----------------------------------------------------|

| RF    | Radio Frequency                                     |

| RLC   | Resistor Inductor Capacitor                         |

| RNN   | Recurrent Neural Network                            |

| RWG   | Rao Wilton Glisson                                  |

| SATA  | Serial Advanced Technology Attachment               |

| SCN   | Symmetrical Condensed Node                          |

| SI    | Signal Integrity                                    |

| SMA   | Sub Miniature Version A                             |

| SMOBC | Solder Mask Over Bare Copper                        |

| SPICE | Simulation Program with Integrated Circuit Emphasis |

| TDK   | Tokyo Denkikagaku Kogyo                             |

| TDR   | Time Domain Reflectometer                           |

| TE    | Transverse Electric                                 |

| TEM   | Transverse Electro Magnetic                         |

| TL    | Transmission Line                                   |

| TLM   | Transmission Line Matrix modelling                  |

| ТМ    | Transverse Magnetic                                 |

| USB   | Universal Serial Bus                                |

|       |                                                     |

# **List of Symbols**

- Ω Ohm

- F Farad

- H Henry

- k Kilo

- m milli

| μ               | Micro                           |

|-----------------|---------------------------------|

| n               | Nano                            |

| р               | Pico                            |

| f               | Femto                           |

| Oz              | Ounce                           |

| ρ               | Resistivity                     |

| ω               | Angular Frequency               |

| S               | Second                          |

| π               | PI                              |

| μ               | Permeability                    |

| 3               | Permittivity                    |

| η               | Intrinsic Impedance             |

| σ               | Conductivity                    |

| γ               | Propagation constant            |

| с               | Speed of light in air           |

| t <sub>pd</sub> | Propagation Delay               |

| t <sub>r</sub>  | Rise time                       |

| t <sub>f</sub>  | Fall time                       |

| Zo              | Characteristic Impedance        |

| Γ               | Reflection Coefficient          |

| $\infty$        | Infinity                        |

| Ħ               | Magnetic flux vector            |

| B               | Magnetic field vector           |

| Ē               | Electric field vector           |

| D               | Flux density vector             |

| J               | Electric current density vector |

| ₩               | Magnetic current density vector |

| P               | Electric polarisation vector    |

| χ               | Susceptibility                  |

| ζ               | Laplace operator                |

| [C]             | Connection matrix               |

| [S]             | Scattering matrix               |

| [I]             | Identity Matrix                 |

| C <sub>l</sub>  | Damping Coefficient             |

| GHz             | GigaHertz                       |

| THz             | TeraHertz                       |

| Θ               | Parametric vectors              |

# **CHAPTER 1**

### **INTRODUCTION**

In the year 1965 Gordon Moore, the founder of Intel first proposed the idea about doubling the Integrated Circuit (IC) complexity every two years [1]. His ideology has been followed till now with a slight correction where the functional density seems to reach a saturation point. Driven by the need for improved cost and performance, the recent advancement of the microprocessor technology as shown in Fig. 1.1 has created newer types of products with ever complex ICs such as System on Chip (SoC), System in Package (SiP) with cheaper production cost and extended Moore's law. The smaller ICs with improved performance means a higher Input/Output (I/O) density at the periphery of the chip and it creates an increased demand in the complex routing constraint where a significant space of the Printed Circuit Board (PCB) is confined by interconnects for connecting these various ICs. Although there has been a dramatic shift over the last decade from its old parallel bus towards serial single ended and differential bus such as PCIE, HDMI, SATA, USB, Fibre Channel 16G, XFI etc. for interconnecting ICs, it has created a new set of issues for its routing constraint and signal quality in its transmission. The severely stressed PCB design - process can provide a poor yield and an increase in the PCB manufacturing cost.

At the same time the consumer electronics market of present years is driven by ever decreasing small, portable, flexible and cost effective consumer electronics products such as smart watch and it is likely to continue for the next few decades till the complete integration of many of the functionality such as internet browsing, networking, memory application, display, audio, various type of sensing applications and power - on time is successfully achieved. The sizing of the IC and PCB board can create tremendous pressure on the functionality and reliability of product.

#### Fig. 1.1 Microprocessor architecture trends

(Source: http://royal.pingdom.com/2012/02/29/the-single-atom-transistor-is-here-the-amazing-evolution-of-microprocessors-infographic/)

In addition, an increased competition in the consumer electronics market has made it necessary to design the product first time right and manufacturable within a very short design cycle time. A typical product design cycle consists of specification preparation as per the intended function of the product, schematics capture, pre-layout simulation, component placement and routing, post layout simulation, prototyping and testing, manufacturing, and finally system integration. Because of the tighter constraint of the board space, the most critical path is the pre-layout simulation, component placement and routing and post layout simulation. Although an analytical or Spice models in some instances may be used to model these interconnects and packages but a poor mathematical representation of these interconnects over a wide range of frequencies can create an inaccurate result and thus can lead to an incorrect simulation output. These all issues have heightened to model and simulate the design in a full field solver before releasing the PCB for fabrication so as to minimise the market lead time, commercial loss and resource wastage.

With the edge rate or signal switching well beyond GHz range and higher IC density in the portable devices within a limited design cycle, these high performance designs require a high quality and critical point – to – point connections between various ICs within its design cycle time frame. While a digital signal is based on low and high voltage thresholds but with increased switching rate and timing issue these same digital domain signal can behave as analogue signal. The analogue signal is much more susceptible to signal quality issue creating Signal Integrity (SI) issues during signal transmission. Poor signal quality such as Inter Symbol Interference (ISI), crosstalk, non-monotonic behaviour, noise coupling, overshoot, undershoot, ringing effect and timing issues such as timing delay, jitter, skew and change in slew rate

-3-

can sometimes produce an incorrect logic state resulting in unintended functionality. The Electromagnetic Compatibility (EMC) is defined where a product does not cause any external interference or get affected by any external interference. Since SI deals with the unintended signal behaviour, this can be one of the sources for EMC arising in PCBs. Hence SI and EMC are all interconnected and a concurrent methodology to address these issues needs to be applied. If the approach for solving the interaction of SI and EMC is applied at the earlier stage, it becomes simpler and cost effective in alleviating the issue arising out of SI and EMC. However as the design stage progresses and gets advanced, the SI and EMC issues become more complex and costly wherein it requires a crisis management approach and might not have any solution except for the revision of the board. Simulation is required to assist a designer in making a right decision, optimising the board space for its various design rules and constraints, innovating new design rules and verifying existing interconnects at the earliest possible stage in the process.

With increased complexity of PCBs, modelling and simulating the ICs and interconnects is becoming more and more important. The simulation of these components can only be achieved if a numerical model could be developed so as to integrate and run it in computer environment. The history of macromodel generation goes about three decades back. In 1980s, macromodel was proposed by T. G. K. Chen and James J. Whalen for speeding up the simulation and handling the complex integrated circuits within reasonable accuracy [2]. In the year 1991, S. Graffi from Univ. of Bologna published a study on 741 Operational amplifiers for 50 MHz signal [3] and the correlation between simulation based on macromodel and experimental result was used to integrate the macromodel in a simulation environment for its accuracy. Based on these contributions, an Input Output Buffer Information

-4-

Specification (IBIS) format was developed by Intel Corporation in early 1990s with an IBIS open forum group. The first behavioural model as an IBIS specification [4] was published as IBIS version 1.1 under the acronym ANSI/EIA-656. The IBIS specification has subsequently been ratified with several modifications including the high frequency noise on power supply pins, package and pin's [RLC]. An alternative to IBIS, the macromodel technique was proposed by Canavero et al. in the year 2001 [5].

In 1985 the effect of the EMC on a microprocessor 8085 was published by J. G. Tront [6]. Subsequently lots of journal papers for EMC and SI effects on ICs and its packages between 1990 and 1995 were published. While working in Nanyang Technological University, Singapore in 1990s H. K. Tang showed that Electromagnetic Interference (EMI) could cause counting inaccuracies and byte swap issues [7]. In the early 1990s many books were also published describing effects of SI and EMC in a PCB. Martin Robinson et al. modelled the effect of EMC on the propagation delay of an IC for the first time at a higher frequency of more than 200 MHz [8].

Transmission Line Matrix modelling (TLM) is a numerical technique, primarily developed for solving electromagnetic field wave propagation in the time domain [9], but some work has also been accomplished for solving the TLM in frequency domain [10]. The TLM method has been implemented and used for solving complex electromagnetic behaviours over the last few decades. Today a vast set of literature apart from many books exist for solving variety of problems such as analysis of microstrip structures [11, 12], analysis of microwave structures for its EMC [13-15]. Johns and Beurle from University of Nottingham first suggested the idea of solving two dimensional scattering parameters in a computer environment using the TLM in

-5-

1971 [16]. A review of TLM in 1985 was given by Hoefer [17]. Although TLM was developed for solving electromagnetic field propagation, there has been little work in solving the PCB domain interconnects and IC packages in a full field environment using this technique. On the other hand, the simulation of PCB domain components can be achieved by 1D, 2D or hybrid tools but the accuracy of the result is often jeopardised in comparison to a 3D tool. 3D tool can take into account of its surrounding effect while representing the complete geometry which can help in an accurate analysis of complex interacting signals similar to a physical model. However a major limitation with a 3D toolset lies in its computational resource requirements and timescale of the simulation for a complete system or subsystem. With a due recognition to the requirement where higher risk is concerned, 3D tool can be used to simulate a subsystem by subdividing the system into active circuits such as ICs and passive circuits such as IC packages, interconnects, via and connectors. A 3D full field solver tool can also help in modelling via, sockets, connectors and various package dies, post-layout verification with a very high accuracy.

#### **1.1 Organisation of the thesis**

The research focus of the thesis as described in Chapters 5 and 6 is the TLM method for the simulation and verification of various interconnect traces and different IC packages of the PCB along with the development of macro-model as an alternative to IBIS. The generated simulation data is verified with the experimental measurement data and other commercial software packages. A typical end-to-end transceiver link can be accurately designed if the PCB materials such as dielectric and conductor behaviour and their intrinsic properties and channel design such as IC breakout region, interconnect topologies, via, discrete components and interface connectors' behaviour could be completely described at a range of frequency. As a background of the original work presented in chapters 5 and 6, chapter 2 describes about frequency behaviour of various individual components used in a typical PCB such as discrete components [RLC], dielectric and conductor, the PCB manufacturing technique, the underlying principle of transmission line, various effects such as skin depth, Maxwell's equation, various boundary conditions for terminating the signal, Bewley lattice diagram and description of various discontinuities in PCB interconnects and extraction of their S-parameters. Chapter 3 briefly talks about the need of numerical solution and different electromagnetic numerical methods such as Finite Difference Time Domain (FDTD), Method of Moment (MoM), Finite Element Method (FEM) and Boundary Element Method (BEM) and development. A short comparison of these methods is also described.

Chapter 4 discusses TLM principles in 1D and 3D domains which is the basis of the research work as developed in chapter 5 and 6. It also discusses about modelling techniques of inhomogeneous media while applying different boundary conditions. This chapter concludes with different PCB dielectric materials and its behaviour over a range of frequencies. A novel 3D time domain modelling tool for I/O ports and interconnects in the PCB, PCB fabrication and experimental setup along with equivalent circuits for the discontinuity has been described in chapter 5 and 6. Chapter 5 talks about the I/O port macromodelling technique and the simulation result of the time domain technique has been compared against the experimental result and other available software while chapter 6 discusses about the result, its S-parameters for different IC packaging, trace configurations using time domain

modelling technique. Finally the conclusions and future scope have been described

in chapter 7.

#### References

- [1] Moore, G. E. 1998. Cramming more components onto integrated circuits. *Proceedings of the IEEE*, 86(1), 82-85.

- [2] Whalen, J.J. (Guest Editorial) 1979. Predicting RFI effects in semiconductor devices at frequencies above 100MHz, *Electromagnetic Compat.*, *IEEE Trans. on*, 21(4), 281-282.

- [3] Graffi, S., Masetti & Golzio, D. 1991. New macromodels and measurements for the analysis of EMI in 741 op-amp circuits, *Electromagnetic Compat.*, *IEEE Trans. on*, 33(1), 25-34.

- [4] IBIS Open Forum. 2008. IBIS Version 5.0 [online]. Available at: http://www.eda.org/ibis/cookbook/cookbook-v5.pdf [Accessed: 10 April 2013].

- [5] Canavero, F. G., Maio, I. A. & Stievano, I. S. 2001. Black-box models of digital IC ports for EMC simulations, *IEEE International Zurich Symposium one electromagnetic Compatibility*, Zurich, February 20-22, 2001, 679-684.

- [6] Tront, J. G. 1985. Predicting URF upset of MOSFET digital IC's. *Electromagnetic Compatibility, IEEE transactions on*, 27(2), 64-69.

- [7] Tang, H. K. & Er, M. H. 1993. EMI induced failure in microprocessor based counting, *Microprocessors and Microsystems*, 17(4), 248-252.

- [8] Robinson, M. P., Fischer, K., Flintoft, I. D. & Marvin, A. C. 2003. A simple model of EMI-induced timing jitter in digital circuits, its statistical distribution and its effect on circuit performance. *Electromagnetic Compatibility, IEEE transactions on*, 45(3), 513-519.

- [9] Akhtarzad, S. & Johns, P. B. 1975. The solution of Maxwell's equations in three space dimensions and time by the TLM method of numerical analysis, *Proc. IEE*, 122(12), 1344-1348.

- [10] Jin, H. & Vahldieck, R. 1992. The Frequency domain Transmission Line Matrix method a new approach. *Microwave Theory and Techniques, IEEE transactions on*, 40(12), 2207-2218.

- [11] Akhtarzad, S. & Johns, P. B. 1975. Three-dimensional Transmission-Line Matrix computer analysis of microstrip resonators. *Micro. Theo. Tech., IEEE Trans. on*, 23(12), 990-997.

- [12] Mariki, G. E. & Yeh, C. 1985. Dynamic three-dimensional TLM analysis of microstrip lines on anisotropic substrate. *Microwave Theory and Techniques, IEEE Transactions on*, 33(9), 789-799.

- [13] Christopoulos, C. 1995. The Transmission-Line Modeling method, *Oxford University Press*, Oxford.

- [14] Özyalçın, M. O. & Sevgi, L. 1998. Comparisons of FDTD and TLM methods in EMC-shielding effectiveness analysis, *The Eighth Biennial IEEE Conference on Electromagnetic Field Computation CEFC* '98, Tucson-Arizona, USA, June 1-3.

- [15] Christopoulos, C. & Herring, J. L. 1993. The application of transmission-line modeling (TLM) to electromagnetic compatibility problems. *Electromagnetic Compatibility, IEEE Transactions on*, 35(2), 185-191.

- [16] Johns, P. B. & Beurle, R. L. 1971. Numerical solution of 2-dimensional scattering problems using a Transmission-Line Matrix. *Electrical Engineers, Proceedings of the Institution of*, 118(9), 1203-1208.

- [17] Hoefer, W. J. R. 1985. The Transmission-Line Matrix method theory and applications. *Microwave Theory and Techniques, IEEE Transactions on*, 33(10), 882-893.

- [18] Johns, P. B. 1986. New symmetrical condensed node for three-dimensional solution of electromagnetic-wave problems by TLM. *Electronics Letters*, 22(3), 162-164.

- [19] Johns, P. B. 1987. A symmetrical condensed node for the TLM method. *Microwave Theory and Techniques, IEEE Transactions on*, 35(4), 370-377.

- [20] Allen, R., Mallik, A. & Johns, P. 1987. Numerical results for the symmetrical condensed TLM node. *Microwave Theory and Techniques, IEEE Transactions* on, 35(4), 378-382.

- [21] Attia, M., Ney, M. & Aguili, T. 2013. The segmentation concept for frequency-domain TLM method combined to the variable mesh technique. *Journal of Electromagnetic Waves and Applications*, 27(16), 2035-2048.

- [22] Naylor, P. 1986. Coupling between electromagnetic waves and wires using Transmission Line modelling, *PhD Thesis*, University of Nottingham.

# CHAPTER 2

### High Frequency PCB methodology and Analysis

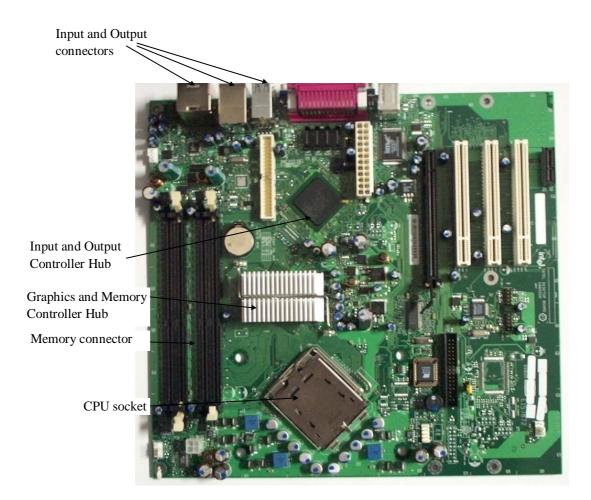

With the increased complexity and higher frequency of operation of various devices inside PCBs, it is not uncommon for any board to go through more than two or three revisions before releasing it into the market. PCB revisions may arise because of the failure to meet the expectation of its functionality due to its incorrect layer stack-up, complex routing over the constrained PCB space, density and placement of its components and IC interconnects, wide frequency behaviour of these components and interconnects, cost target of PCB manufacture. These set of issues can be avoided if there could be some pre-layout simulator which could produce result during its design phase well before the physical translation of its electronics design. A full field solver which can take into account of its surrounding effects along with physical component integration can be a perfect fit for providing the solution. Since the result of a PCB component and IC lies in the time domain, it becomes important for the field solver to present a time domain analysis. This time domain analysis has been part of my research work and has been presented in the subsequent chapters. In order to show the complexity of cad design in the present time, a typical six layer Intel chip based densely routed and complex motherboard has been shown in Fig. 2.1. As shown in this Figure, the motherboard consists of a high density single socket dual core Intel Central Processing Unit (CPU) for processing the instruction/data, an I/O Controller Hub (ICH) for connecting and controlling various

I/O interfaces such as the Peripheral Component Interface (PCI), Peripheral Component Interface Express (PCIE), Universal Serial Bus (USB) and Serial Advanced Technology Attachment (SATA) and a Graphics and Memory Controller Hub (GMCH) for memory and graphics devices. These ICs are available in BGA and LGA package with a pin count of 400 to 700 pins and a pitch of 200  $\mu$ m. With the separation of 200  $\mu$ m, the trace routing in the vicinity of its periphery becomes quite complex, leading to a multi-layered and complex board.

Fig. 2.1 A typical six layered motherboard (source Intel)

The operation of this high density PCB depends on SI between its components, and EMC. SI is often inseparable from the EMC issue and therefore a solution of the SI issue can lead to EMC fulfilment. Hence a good design and its pre-design analysis require an in-depth understanding of the signalling between each of the components lying on the board. The complete PCB system as shown in Fig. 2.1 can be classified by its discrete components (e.g. resistors, capacitors, inductors etc.), transmission lines (various types of single and differential traces) and integrated circuits. For a low operating frequency, the passive components work as expected per the manufacturer provided datasheet, however as the frequency increases these component lose their characteristic. For a PCB designer it becomes important to know the limitation of these passive components.

Further various PCB traces can be designed to create these passive elements and due to space constraints and reliability reasons the latest trend has been to embed these elements in the PCB itself. The EMC of a PCB design is dependent on the behaviour of these PCB elements. Once the behaviour is analysed completely, the SI issue and hence the EMC issue can be solved. The high frequency behaviour of these various elements of the PCB is described in the following sections.

## 2.1 Analysis of Discrete components

#### 2.1.1 Lumped Resistors

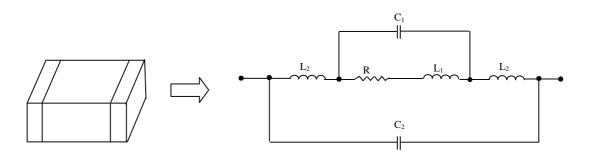

A resistor is often manufactured in three different types: Metal film resistors (these come in different packages, 01005, 0201, 0402, 0603, 0805 etc.), wire wound and carbon resistors (these are inexpensive resistors, made of low conductive carbon). Wire-wound and metal film resistors can carry high current and usually have tighter tolerances and lower temperature coefficients. An equivalent circuit for a metal film

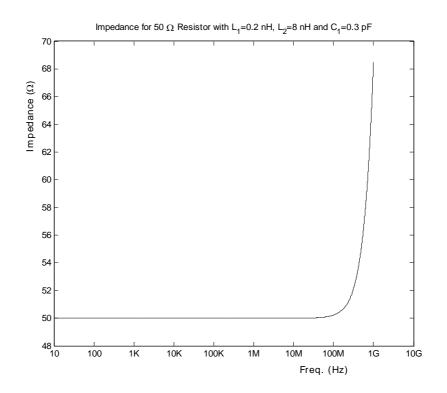

resistor is shown in Fig. 2.2 while its frequency dependant behaviour using Pspice is shown in Fig. 2.3. As seen in Figs. 2.2 and 2.3, the parasitic inductance and capacitance value dominates the resistance value at a higher frequency, increasing the effective impedance. In Fig. 2.2, R is the resistor's value while  $L_1$ ,  $L_2$  and  $C_1$ ,  $C_2$ are the stray capacitances and inductances respectively.

Fig. 2.2 Metal film resistor

Fig. 2.3 Frequency dependent impedance plot for a typical thin film resistor

An equivalent circuit for the resistor model can be defined by Figs. 2.2 and (2.1) [1].

$$Z(\Omega) = (((R + X_{L1}) || X_{C1}) + X_{L2} + X_{L2}) || X_{C2} - (2.1)$$

Here  $X_{L1} = j2\pi fL_1$  and  $X_{L2} = j2\pi fL_{21}$  and  $X_{C1} = \frac{1}{j2\pi fC_1}$  and  $X_{C2} = \frac{1}{j2\pi fC_2}$

Based on the packaging of the resistor,  $C_2$  can be ignored. The impedance plot of a typical metallic film resistor is shown in Fig. 2.3.

A general guideline as described by equation (2.2) can be used for selecting an effective chip resistor [2], here f is the frequency of operation and R is the resistance in ohms.

$$\frac{f}{3 \times 10^{10} \text{ Hz}} \le \frac{R}{50} \le \frac{3 \times 10^{10} \text{ Hz}}{f} - (2.2)$$

The above formula can be applied for the best usage of resistor without a loss of signal quality arising out of a chip resistor.

# 2.1.2 Lumped Capacitors

Capacitors are usually associated with a power supply and are often used for bypassing noise, dc-decoupling or power supply source. However in a signal environment, it can be used for AC-coupling, integrators, filtering as well. These capacitors are not a perfect component but it includes resistive and inductive components and hence it does not show its pure capacitive nature throughout its operating frequency but it can describe its pure capacitive nature only up to a certain frequency range. The extra components affecting its property are defined as the Equivalent Series Resistance (ESR), and the Equivalent Series Inductance (ESL). The ESR value is based on manufacturer, package type and capacitance value. For a 10 nF X7R/X5R package, ESR can vary from 1.7 m $\Omega$  (for 1210 type) to 20 m $\Omega$  (for 0402). Similarly the ESL value is based on the manufacturer, package type and capacitance value. For a 10 nF X7R/X5R package, this can vary from 1070 pH (for 1210 type) to 450 pH (for 0402). Other package types like Y5V, Z5U have significantly higher ESR and ESL. The ESL causes the capacitor to stop behaving like a true capacitor at high frequencies as the impedance starts to increase rather than keep decreasing. The ESL has a more undesirable value when a capacitor has its lead in its package, rather than a surface mount or leadless capacitor. As the lead inductance increases, the high frequency impedance limitation also increases. Hence a higher frequency design should avoid a lead component and instead leadless components should be used in critical designs. When multiple capacitors are placed in parallel, the combinational effect of these capacitors plays a role, and a resonance can cause relatively higher impedance.

A capacitance's equivalent model can be represented by Figs. 2.4 and (2.3) [3]. Here  $R_{hysteresis}$  and  $R_{insulation}$  can be ignored for any reliably manufactured capacitance and hence a capacitor can be represented by its ESR, ESL and its capacitive reactance.

$$Z(\Omega) = X_{ESR} + X_{ESL} + X_C - (2.3)$$

Here the X<sub>ESL</sub> and X<sub>C</sub> can be described using  $X_{ESL} = j2\pi fL$  and  $X_{C} = \frac{1}{j2\pi fC}$

Fig. 2.4 Equivalent capacitance model

Similar to a resistor's behaviour, the capacitor's typical impedance plot for a 10 nF capacitance using Pspice has been shown in Fig. 2.5.

Fig. 2.5 Frequency dependant impedance plot for a capacitor

### 2.1.3 Lumped Inductor

Like a capacitor, inductors also have other parasitic elements. This includes the DC resistance (DCR) and the Inter Winding Capacitance (IWC). Just as the capacitor stops behaving like a capacitor at high frequencies, an inductor also stops behaving like an inductor at high frequencies. The high frequency causes a resonance effect in the circuit and is decided by its inductance and its associated parasitic capacitance. At the resonance point, an inductor will have a substantial rise in its impedance and above the resonance the inductor altogether stops behaving as an inductive element and instead it becomes a capacitive element. This resonance can cause issues in signal transmission and interference in its operation and should not be ignored.

Fig. 2.6 Equivalent inductance model

An inductor's equivalent model can be represented by Figs. 2.6 and (2.4) [4] and can be described by its Inductive value, DCR and IWC, where  $X_L = j2\pi fL$  and  $X_{IWC} = \frac{1}{j2\pi fC_{IWC}}$ ,  $R_{DCR}$  is the DC resistance.

$$Z(\Omega) = (R_{DCR} + X_L) || X_{IWC} - (2.4)$$

The impedance plot of a typical 1.2  $\mu$ H inductor with 20 m $\Omega$  DCR and 20 pH IWC using Pspice is shown in Fig. 2.7.

Fig. 2.7 Frequency dependant impedance plot for an inductor

### 2.2 PCB technology and its high frequency behaviour

### 2.2.1 Overview of a manufactured PCB

On a PCB the components are soldered through interconnect traces which convert an electrical design into a physical form. These traces and components are connected through a multi-layer prepreg with conductors. Normally a typical motherboard for a PC/server has four to twelve layers stack-up, while a telecom board has twelve to twenty-eight layers stack-up. The consumer electronics board is defined in four to eight layers. Interconnects among layers are made using via which is drilled holes and can be plated with copper. There are different types of via in a PCB. These via can be classified as plated through holes, blind and buried. These layers are described by its following manufacturing elements. An example of a six layered PCB is shown in Fig. 2.8.

Fig. 2.8 A six layered PCB overview

1. Core: The core material is a rigid sheet usually made of cured fibreglass resin material that provides isolation between layers. Most commonly used core materials are Fr4 epoxy glass, cyanate ester, polymide glass and Teflon. The dielectric strength, coefficient of thermal expansion and cost of the core play an important role in selecting the core for PCB design.

- 2. Prepreg: The prepreg is made of a material similar to core material but is uncured. It behaves as an adhesive to bond the copper layers. When heated and pressed, the prepreg will cure (harden) holding the copper layers firmly, hence it is used to stick the core layers together.

- 3. Copper foil and traces: Copper foil is a thin sheet of copper that bonds to the prepreg layer. Traces are formed by etching the copper foil. The usual thickness of copper layer is 16.25  $\mu$ m, 32.5  $\mu$ m and 65  $\mu$ m, depending on the impedance, current carrying capacity and thermal effect of the trace. The trace width is a design parameter, depending on the required impedance of the trace.

- Copper plating: Copper plating is primarily used only on the finished board, on the external layer, and provides an additional thickness of copper to the board. The external plating is only done after the board is drilled and etched.

- 5. Drill: This layer defines the location and sizes of drill holes and via on the board.

- 6. Solder flow/paste: This layer is used to apply solder over exposed copper to prevent it from oxidation and also forms the base for surface mount devices. In a related process called Solder Mask over Bare Copper (SMOBC), the board is 'masked' and only exposed copper (usually pads or areas that have surface mount components) can be coated with solder.

- 7. Solder mask: This coating is done on the top and bottom layers of the PCB, which prevents solder from freely flowing on the board. It also insulates the board electrically, and protects the board from the environment. This layer provides the characteristic green, red or other colours in the most PCB boards.

8. Silkscreen: This is the documentation layer containing component references, pin numbers and PCB details like lot number, manufacturer logo etc.

#### 2.2.2 Behaviour of the PCB media at higher frequency

At lower frequency, the wave mode supported by various PCB traces are somewhat straightforward but with the increased operating point of frequency, other conductor and media specific properties play a significant role. Hence the field description on a stripline/microstripline requires some correction based on the conductor behaviour and losses associated with it. These behaviours are described in the following subsections.

### 2.2.2.1 Lossy behaviour of the conductor

At higher operating frequencies there is some resistive loss in the conductor itself and this loss is frequency dependent. Main component of a lossy line can be defined using the series resistance of the trace and dielectric loss of the prepreg. The loss can be represented using two distinguishable parts, DC resistance  $R_{dc}$  as defined in (2.5) and AC resistance  $R_{ac}$  as defined in (2.6). Hence the resistive loss of a conductor at higher frequencies can be defined using (2.7) [5].

$$\mathsf{R}_{\rm dc} = \frac{\rho l}{wt} \tag{2.5}$$

$$\mathsf{R}_{\mathrm{ac}} = \frac{l\sqrt{\rho\pi\mu_{\mathrm{r}}\mu_{\mathrm{0}}\mathsf{f}}}{w} - (2.6)$$

$$R(\omega) = \sqrt{(R_{dc})^2 + (R_{ac})^2} - (2.7)$$

R is a function of the signal frequency and the resistance per metre of 1 oz. (35  $\mu$ m thick) copper (with its resistivity of 1.68e-06) for a 150  $\mu$ m microstrip trace width has been plotted using Matlab and is shown in Fig. 2.9.

Fig. 2.9 Resistive behaviour of copper used in PCB traces

### 2.2.2.2 Skin depth

With an increase in frequency, the current is forced to flow nearer its surface rather than penetrating inside the conductor and flowing uniformly across the cross section of the conductor. As a Matlab plot shown in Fig. 2.10, this skin depth for a copper layer (with its conductivity,  $\sigma = 5.95e05 \text{ Sm}^{-1}$ ) falls exponentially with increasing frequency. The skin depth is an important property because of the copper pouring in the PCB especially in the situation where the current demand is significant. A careful selection of the copper weight can save some PCB cost. The skin depth is analytically derived as in (2.8) [6 - 7] and depends on the conductor's conductivity ' $\sigma$ ' and the frequency 'f' of the signal.

$$\delta = \sqrt{\frac{1}{\pi\mu_0 f\sigma}}$$

(2.8)

Fig. 2.10 Frequency dependant skin depth

The skin effect also causes frequency dependence of the strip line inductance; inductance of the trace is higher at low frequencies and falls noticeably at the transition frequency where skin depth becomes comparable with conductor dimensions. With the increase of operating frequency although the flux density between the microstrip trace and reference conductor remains constant, the magnetic flux of the microstrip trace keeps reducing, hence the inductance at higher frequency becomes low. These effects produce altogether different copper characteristic impedance than originally designed for.

#### 2.2.2.3 Dielectric loss

Dielectric loss occurs when the propagating field interacts with the dielectric material of the PCB and hence it is an intrinsic property of a dielectric material. The wave propagation in microstrip line and even in strip line is not a pure TEM mode

and the electromagnetic wave can interact with the substrate underneath. The microstrip line trace forms a parallel plate (filled with an insulator) structure with ground plane, hence it can be considered as a capacitor. Because of imperfect medium (air on one side while dielectric on the other side), an out of phase current does exist. Dielectric material can be defined by its two important parameters such as dissipation factor (also known as loss tangent, tan  $\delta_d$ ) and relative dielectric constant ( $\varepsilon_r$ ). The frequency dependant behaviour of these parameters is necessary for characterising a PCB dielectric. The effective relative permittivity can be defined using a combination of real and imaginary terms as defined in (2.9), the relationship between imaginary and real term can be defined using dielectric loss tangent in (2.10) while the propagation constant ' $\gamma$ ' can be defined using (2.11) [8].

$$\varepsilon_{\rm r} = \varepsilon_{\rm r}' - j \varepsilon_{\rm r}'' - (2.9)$$

$$\tan(\delta_d) = \frac{\varepsilon_r^{"}}{\varepsilon_r'} - (2.10)$$

$$\gamma = \omega \sqrt{\left(\mu_0 \varepsilon_0\right) \left(\varepsilon_r' - j \varepsilon_r''\right)} - (2.11)$$

Based on the above equations, the attenuation factor for a homogenous quasi-TEM line as symmetric strip line can be determined using (2.12) under low loss condition [9].

$$\alpha_{\varepsilon}(N) = \pi f \tan(\delta_d) \sqrt{\varepsilon_r} \qquad -(2.12)$$

The amount of the dielectric loss is dependent on generated electric field density of the structure apart from the nonlinearity of the polarisation. While taking into account of this effective dielectric constant and capacitance of the microstrip line (assuming filled with air)  $C_{empty}$ , the effective capacitance  $C_{eff}$  of the microstrip line can be defined by (2.13) and effective dielectric loss by (2.14) [9].

$$C_{eff} = (\varepsilon'_r - j \varepsilon''_r)C_{empty} - (2.13)$$

$$G_{eff} = \omega \varepsilon_r^{"} C_{empty}$$

– (2.14)

Apart from conductor and dielectric characteristics, the conductor is often coated with an anti-oxidant material such as nickel/gold/silver to protect the trace from oxidation and corrosion. This can also affect the performance of the transmission line.

#### 2.2.3 Transmission Line requirement on trace

With higher frequencies of operation, falling power level of these ICs and increased edge rate (rise and fall time) of the signal, the interconnection link between different devices can become a transmission line and as part of its function can produce a reduced noise margin. A transmission line is a conducting medium which can be used to guide energy from one position to another position in the form of an electromagnetic field. The transmission line contains transverse electric and magnetic fields. The voltage difference between the transmission line trace and the surrounding planes is a measure of the strength of the electric field. The magnitude of current flowing in a transmission line is a measure of the strength of the strength of the magnetic fields from one point to another point. Electromagnetic waves travel at the speed of light, 'c' (that is  $3x10^8$  m/s) in free space. However, the dielectric medium has a relative dielectric permittivity,  $\varepsilon_r$ . Hence the speed of electromagnetic wave in the presence of dielectric media is guided by its effective dielectric constant and the speed of

propagation for a strip line trace is represented by  $C/\sqrt{\epsilon_{eff}}$  where  $\epsilon_{eff}$  is the effective permittivity. The effective dielectric constant of effective permittivity is dependent on surrounding media (homogenous or inhomogeneous) and its dielectric constant. Assuming 'w' being the width of the metal plate and 'h' being the height of dielectric slab,  $\epsilon_{eff}$  of a wide microstrip trace (where electric field can be considered to be located at the centre of the strip) can be defined by the (2.15) [10] while  $\epsilon_{eff}$  can be approximated to  $\epsilon_r$  for w >> h.

$$\varepsilon_{\rm eff} = \frac{\varepsilon_{\rm r} + 1}{2} + \frac{\varepsilon_{\rm r} - 1}{2} \frac{1}{\sqrt{1 + \frac{12h}{w}}} \quad \text{for } \frac{w}{h} \ge 1$$

- (2.15)

Similarly for a thin microstrip trace (which have its electric field throughout its metal strip)  $\varepsilon_{eff}$  can be defined by the (2.16) [11] while  $\varepsilon_{eff}$  can be approximated to  $0.5(\varepsilon_r + 1)$  for h >> w.

$$\varepsilon_{\rm eff} = \frac{\varepsilon_{\rm r} + 1}{2} + \frac{\varepsilon_{\rm r} - 1}{2} \left[ \frac{1}{\sqrt{1 + \frac{12h}{w}}} + 0.004 \left(1 - \frac{w}{d}\right)^2 \right] \quad \text{for } \frac{w}{h} \le 1 - (2.16)$$

Hence the effective dielectric constant of a Microstrip line can have a range of  $0.5(\varepsilon_r + 1) \le \varepsilon_{eff} \le \varepsilon_r$ . However the effective dielectric constant for Fr4 dielectric with its dielectric constant of 4.4 becomes 3.25 and varies with frequency. The frequency dependent plot can be plotted using Matlab and is shown in Fig. 2.11.

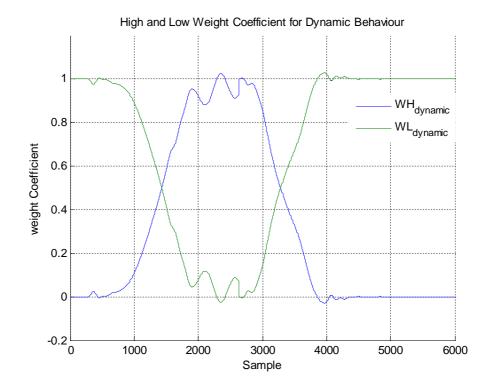

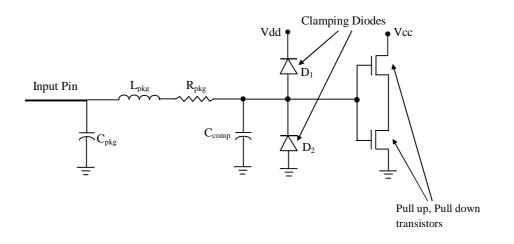

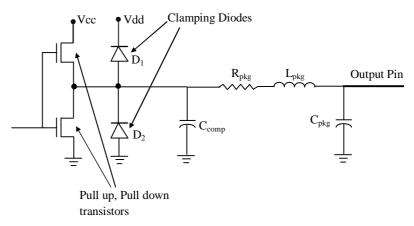

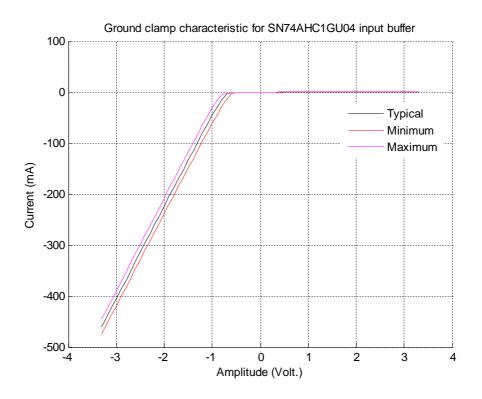

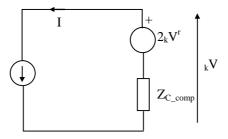

Fig. 2.11 Effective dielectric constant for a microstrip line