Rohouma, Wesam M.M. (2013) Design control and implementation of a four-leg matrix converter for ground power supply application. PhD thesis, University of Nottingham.

## Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/13260/1/Wesam\_Rohouma\_Thesis.pdf

## Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

UNITED KINGDOM · CHINA · MALAYSIA

# Design control and implementation of a four-leg Matrix Converter for ground power supply application

Wesam M. M Rohouma

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

Feb, 2013

## **Abstract:**

The technology of direct AC/AC power conversion (Matrix Converters) is gaining increasing interest in the scientific community, particularly for aerospace applications.

The aim of this research project is to investigate the use of direct AC/AC three phase four-leg Matrix Converter as ground power unit to supply aircraft with power during stopover or maintenance in airports. The converter fourth leg is used to provide a path for the zero sequence components when feeding unbalanced or non-linear loads. A high bandwidth controller is required to regulate the output voltage of Matrix Converter with a 400Hz output frequency. However, the controller bandwidth is limited due to the reduced ratio between the converter switching frequency and the fundamental frequency. In this case undesirable, periodic errors and distortion will exist in the output voltage above all in the presence of a non-linear or unbalanced load.

Digital repetitive control system is proposed to regulate the output voltage of a fourleg Matrix Converter in an ABC reference frame. The proposed control structure introduces a high gain at the fundamental and its integer multiple frequencies. Using the proposed repetitive controller will reduce the tracking error between the output and the reference voltage, as well as increasing the stability of the converter under balanced and unbalanced load conditions.

Simulation studies using SABER and MATLAB software packages show that the proposed controller is able to regulate the output voltage during balanced and unbalanced load conditions and during the presence of non-linear load. In order to validate the effectiveness of the proposed controller, an experimental prototype of a 7.5KW has been implemented in PEMC laboratory using DSP/FPGA platform to control the converter prototype. The steady state and the dynamic performance of the proposed control strategy are investigated in details, and extensive experimental tests have showed that the proposed controller was able to offer high tracking accuracy, fast transient response and able to regulate the output voltage during balanced, unbalanced and non-linear loading.

Acknowledgement

All praise and thanks to Allah the Almighty, for giving me strength and ability to

complete this study.

I express my profound gratitude and sincere thanks to my supervisors Prof Patrick

Wheeler and Dr Pericle Zanchatta for their valuable suggestions and consistent

encouragement through the whole course of my research. I would like to thank all the

staff of the PEMC group at the University of Nottingham and all of the technicians of

the ground floor workshop, for providing the necessary help, to carry out this

research. All of you, who have contributed, all of you who encouraged me and

supported these pages, thank you.

Also, my deepest gratitude and thanks always go to my beloved parents, brothers,

sisters, all of my relatives and friends who have always been enriching my life with

their continuous support and love.

And last but not least, I would like to express my deepest gratitude, love and respect

to my wife and children. Without their support and patience, there would never be

any chance for this work to happen.

Nottingham, 2012

Wesam Rohouma

ii

## **Table of Contents**

| Abstract:i                                  |

|---------------------------------------------|

| Acknowledgementii                           |

| Table of Contentsiii                        |

| List of symbolsviii                         |

| List of figuresix                           |

| List of tablesxvii                          |

| Chapter 1 Introduction:                     |

| 1.1 Introduction                            |

| 1.2 Power supply aircraft standards         |

| 1.3 Matrix Converters:                      |

| 1.3.1 Matrix Converter control6             |

| 1.4 Repetitive control6                     |

| 1.5 Objectives                              |

| 1.6 Thesis outlines                         |

| Chapter 2 Fundamentals of Matrix Converters |

| 2.1 Introduction: 9                         |

| 2.2 Matrix Converter structure              |

| 2.2.1 Input filter                          |

| 2.2.2 Output filter                         |

| 2.2.3 Ridirectional switches                |

| 2.3 Matrix Converter Current Commutation                                            |

|-------------------------------------------------------------------------------------|

| 2.3.1 Simple Commutation Methods                                                    |

| 2.3.2 Soft switching techniques                                                     |

| 2.3.3 Advanced commutation methods16                                                |

| 2.3.4 Output current direction based commutation method                             |

| 2.4 Matrix Converter modulation strategies                                          |

| 2.4.1 Space Vector Modulation for 3x3 Matrix Converter                              |

| 2.4.2 Space Vector Modulation for 3x4 Matrix Converter                              |

| 2.4.3 Principles of the Venturini modulation method                                 |

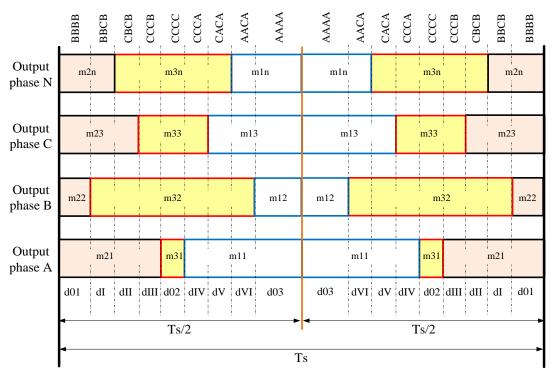

| 2.4.4 Switching Sequence of the Four-Leg Matrix Converter                           |

| 2.5 Summary                                                                         |

| Chapter 3 Control design for the four-leg Matrix Converter power supply             |

| 3.1 Introduction                                                                    |

| 3.2 Modeling and control of four-leg Matrix Converter system                        |

| 3.2.1 Averaged model of the four-leg Matrix Converter                               |

| 3.2.2 GPU based four-leg Matrix Converter control in ABC reference frame 40         |

| 3.2.3 Linear second order control design example for the four-leg Matrix  Converter |

| 3.3 Repetitive Control                                                              |

| 3.3.1 Repetitive control classification                                             |

| 3.3.2 Fundamentals of repetitive control 48                                         |

| 3.3.3 Plug-in Discrete Repetitive Controller                                                                             |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| 3.3.4 Stability Analysis                                                                                                 |  |

| 3.3.5 Design of the robustness filter Q(z)55                                                                             |  |

| 3.3.6 Time advance unit (Z <sup>L</sup> ) design                                                                         |  |

| 3.3.7 Design example of four-leg Matrix Converter using second order linear controller and plug-in repetitive controller |  |

| 3.4 Summary63                                                                                                            |  |

| Chapter 4 Power converter simulation                                                                                     |  |

| 4.1 Introduction64                                                                                                       |  |

| 4.2 Power converter modeling and simulation                                                                              |  |

| 4.3 GPU simulation                                                                                                       |  |

| 5.1.1. Saber simulation of four-leg Matrix Converter                                                                     |  |

| 4.3.1 Simulation flowchart69                                                                                             |  |

| 4.3.2 System parameters71                                                                                                |  |

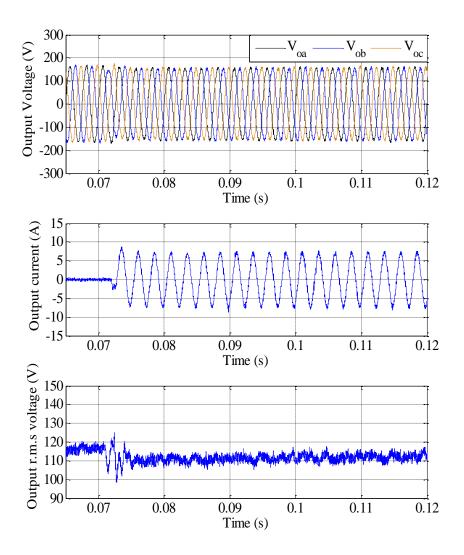

| 4.3.3 Matrix Converter operation under balanced load71                                                                   |  |

| 4.3.4 Unbalanced load conditions                                                                                         |  |

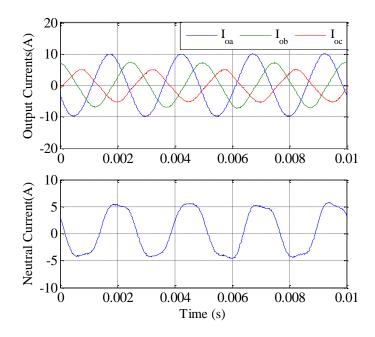

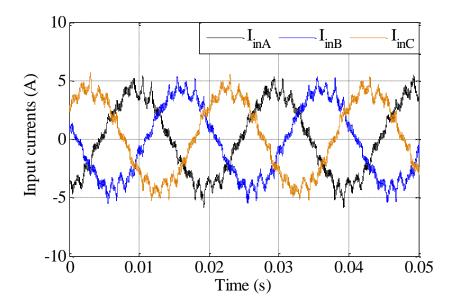

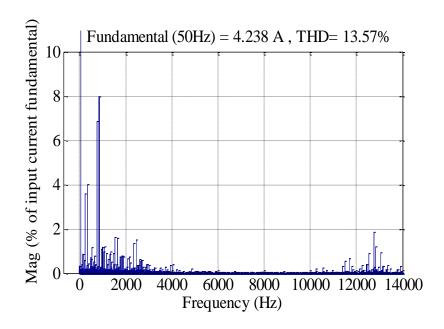

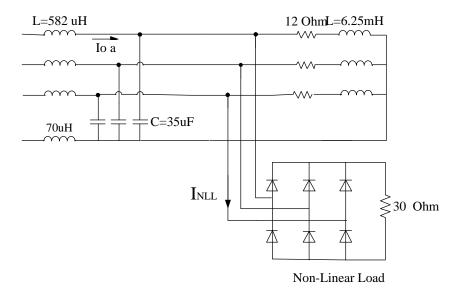

| 4.3.5 Non Linear Load85                                                                                                  |  |

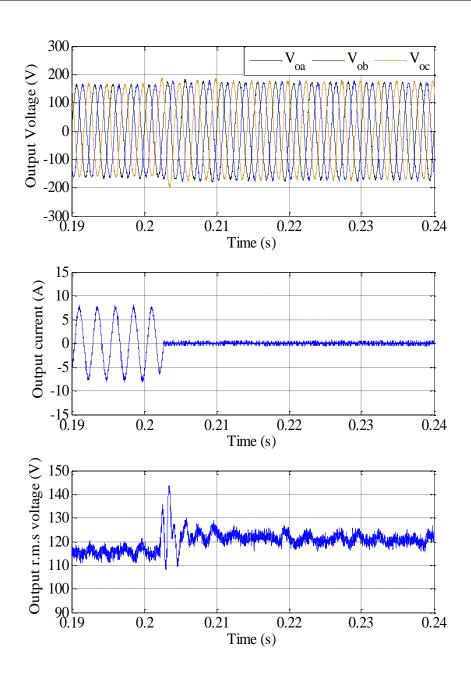

| 4.3.6 Load disconnection and connection                                                                                  |  |

| 4.4 Switching frequency effect on power converter performance                                                            |  |

| 4.4.1 Simulation results using 8kHz switching frequency96                                                                |  |

| 4.4.2 Simulation results using 12.8kHz switching frequency                                                               |  |

| 4.4.3 Simulation results using 25.6kHz switching frequency | 104 |

|------------------------------------------------------------|-----|

| 4.5 Summery                                                | 108 |

| Chapter 5 Hardware Implementation                          | 110 |

| 5.1 Introduction                                           | 110 |

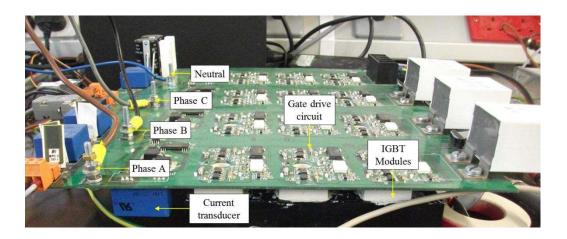

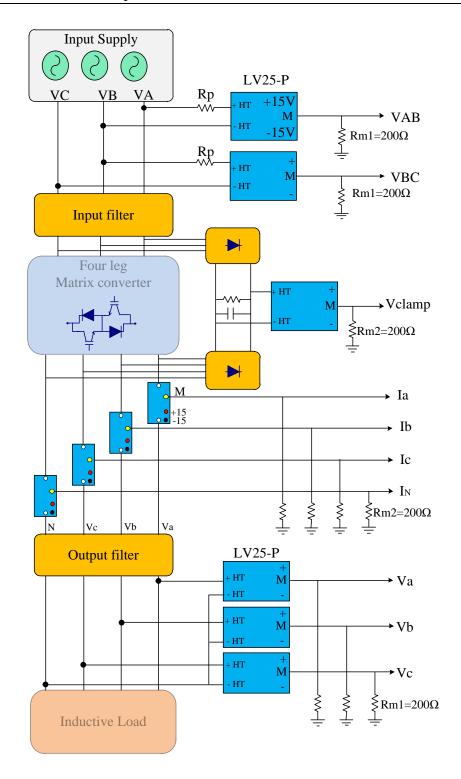

| 5.2 Experimental rig                                       | 111 |

| 5.3 Input filter                                           | 112 |

| 5.4 Power modules (Bidirectional switches)                 | 114 |

| 5.5 Gate drive circuit                                     | 115 |

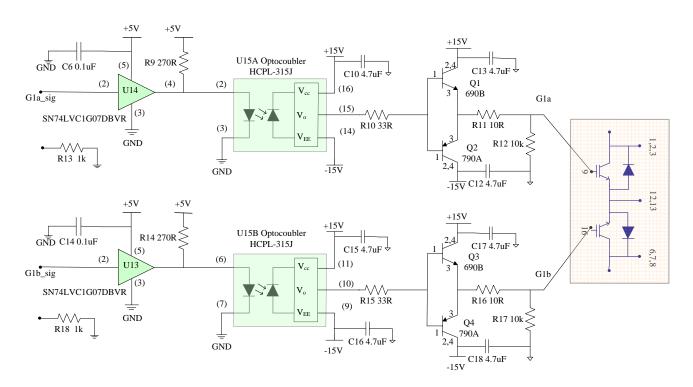

| 5.6 Current direction circuit                              | 117 |

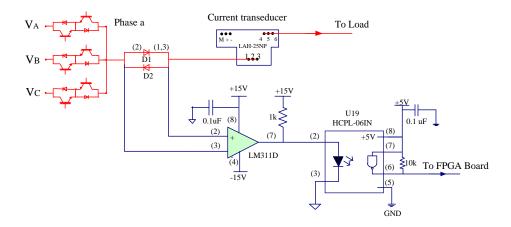

| 5.7 Voltage clamp circuit                                  | 119 |

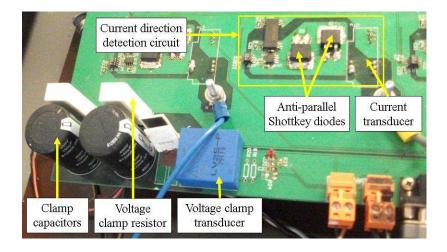

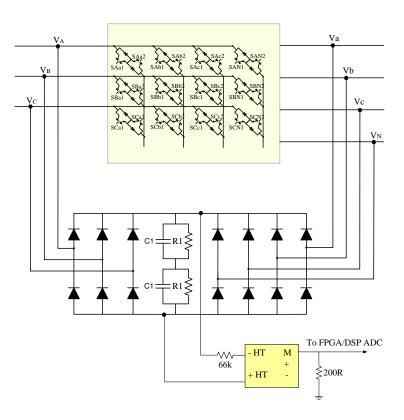

| 5.8 Measurement circuit                                    | 121 |

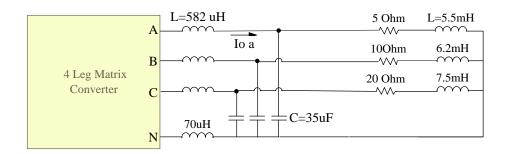

| 5.9 Output filter                                          | 123 |

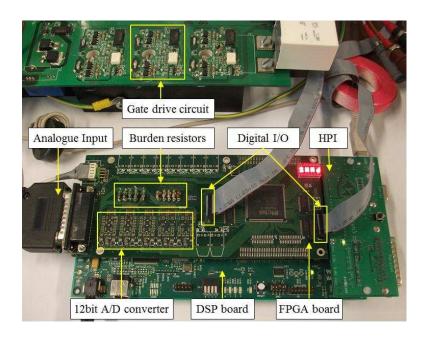

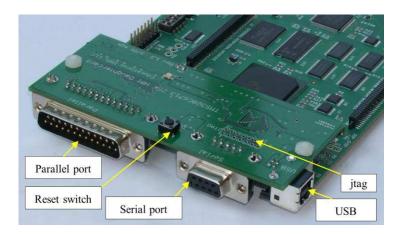

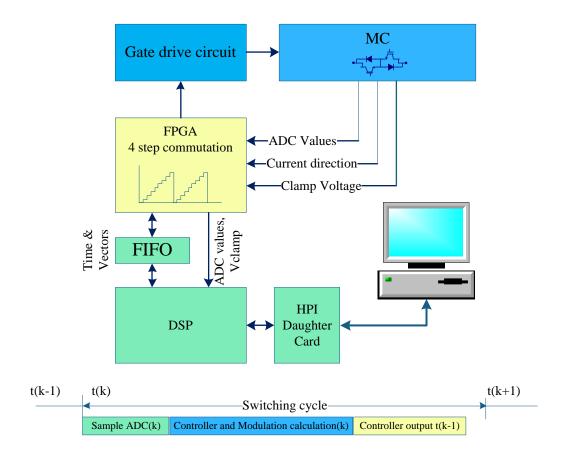

| 5.10 Control platform                                      | 125 |

| 5.10.1 Digital signal processor DSP                        | 126 |

| 5.10.2 Field Programmable Gate Array (FPGA) board          | 126 |

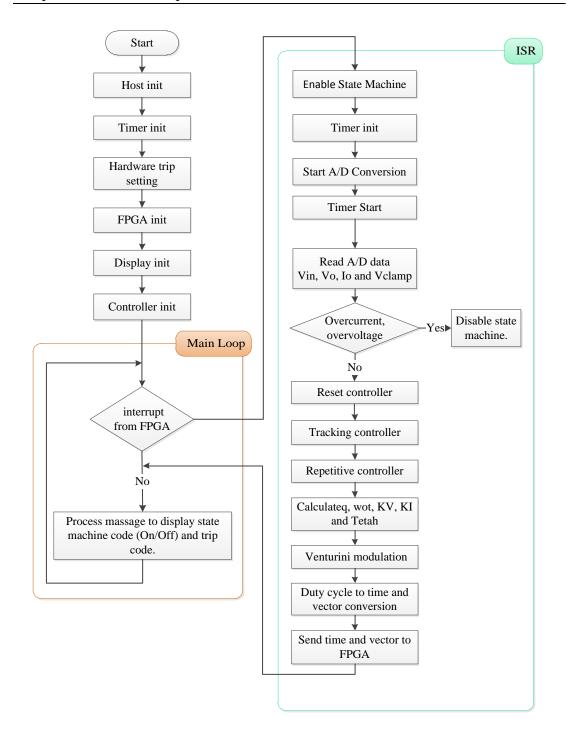

| 5.10.3 DSP software overview                               | 128 |

| 5.11 Summery                                               | 131 |

| Chapter 6 Experimental Results                             | 132 |

| 6.1 Introduction                                           | 132 |

| 6.2 System parameters                                      | 133 |

| 6.3 Matrix Converter operation for a balanced load         | 134 |

| 6.4 Unbalanced load conditions                         | 139 |

|--------------------------------------------------------|-----|

| 6.5 Non Linear Load                                    | 146 |

| 6.6 Load connection and disconnection                  | 153 |

| 6.7 Summery                                            | 155 |

| Chapter 7 Conclusion                                   | 158 |

| 7.1 Conclusion                                         | 158 |

| 7.2 Future work                                        | 161 |

| References                                             | 162 |

| Appendices                                             | 171 |

| Appendix A : Published Papers                          | 171 |

| Under revision jpurnal paper:                          | 171 |

| Appendix B :Duty cycles to space vector transformation | 172 |

## List of symbols

R<sub>s</sub> Input damping resistor.

L<sub>s</sub> Input filter inductance.

C<sub>s</sub> Input filter capacitance.

L<sub>o</sub> Output filter inductance.

C<sub>o</sub> Output filter capacitance.

$V_a, V_b, V_c, V_n$  Output phase voltages.

$V_A$ ,  $V_B$ ,  $V_C$  Input phase voltages.

R<sub>L</sub> Value of load resistance.

L<sub>L</sub> Value of load inductance.

$K_{v}$  Sector number that contains the output voltage vector.

K<sub>i</sub> Sector number that contains the input current vector.

V<sub>im</sub> Peak input voltage.

q Voltage transfer ratio.

U<sub>RC</sub> Repetitive control output.

Q(z) Low pass filter.

Z<sup>-N</sup> Delay element

Z<sup>-L</sup> Delay element.

$G_c(z)$  Controller transfer function.

$G_p(z)$  Plant transfer function.

# List of figures

| Figure 1-1 GPU possible topologies.                                                                  | 2       |

|------------------------------------------------------------------------------------------------------|---------|

| Figure 1-2 Envelope of normal 400 Hz and variable frequency AC voltage trans                         | sient.3 |

| Figure 1-3 Matrix Converter with ABC reference control                                               | 4       |

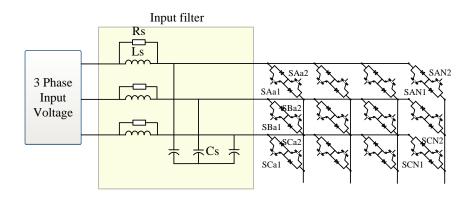

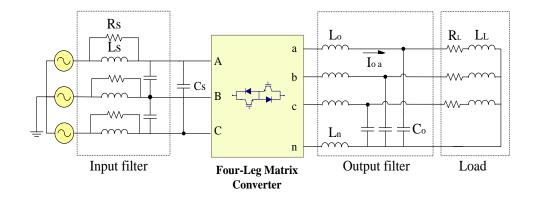

| Figure 2-1 Four-leg Matrix Converter system                                                          | 10      |

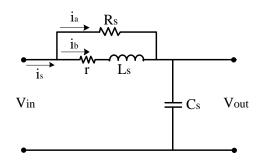

| Figure 2-2 Input filter circuit.                                                                     | 11      |

| Figure 2-3 Input filter Single phase equivalent circuit                                              | 12      |

| Figure 2-4 Three phase matrix converter circuit.                                                     | 13      |

| Figure 2-5 Output filter single phase equivalent circuit                                             | 13      |

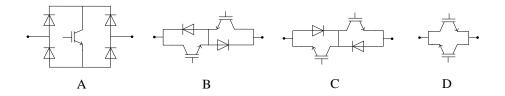

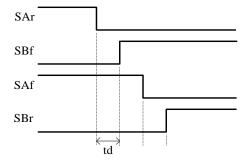

| Figure 2-6 Bidirectional switches configuration                                                      | 14      |

| Figure 2-7 Current direction based commutation.                                                      | 17      |

| Figure 2-8 Four step current commutation.                                                            | 17      |

| Figure 2-9 Four step current commutation                                                             | 18      |

| Figure 2-10 SVM Vectors for a Balanced 3-Phase                                                       | 20      |

| Figure 2-11 Output voltage and input current space vectors                                           | 20      |

| Figure 2-12 Input voltage space.                                                                     | 24      |

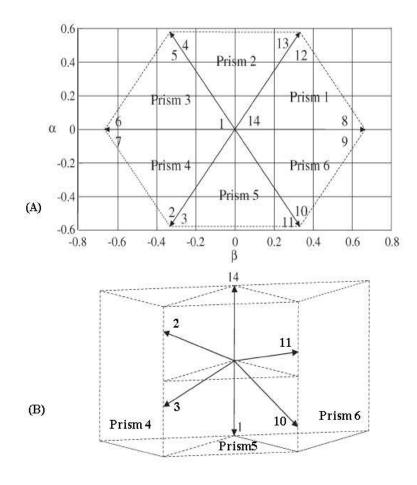

| Figure 2-13 α,β,γ space vector for four-leg Matrix Converter                                         | 28      |

| Figure 2-14 (A) Three dimensional view of the vectors in $\alpha,\beta$ plane, (B) dimensional plan. |         |

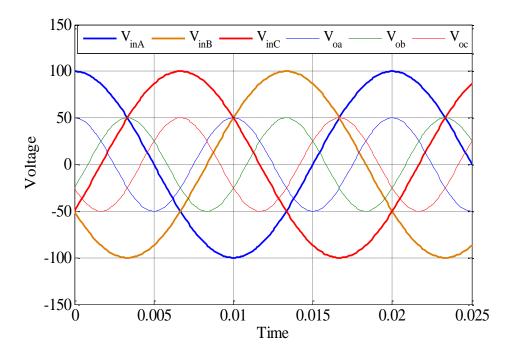

| Figure 2-15 Target output and input voltage                                                          | 32      |

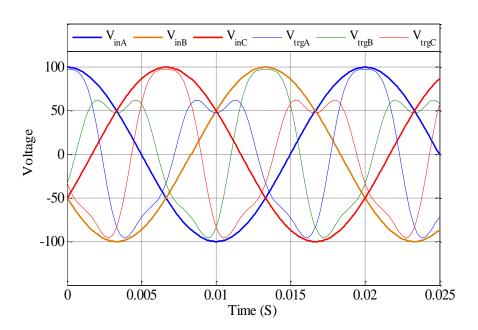

| Figure 2-16 Target output voltage using optimized Venturini modulation                               | 33      |

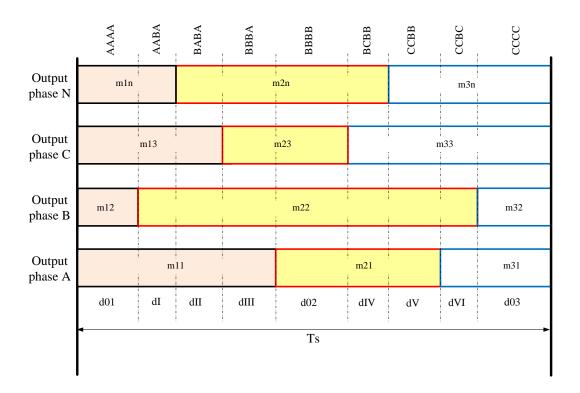

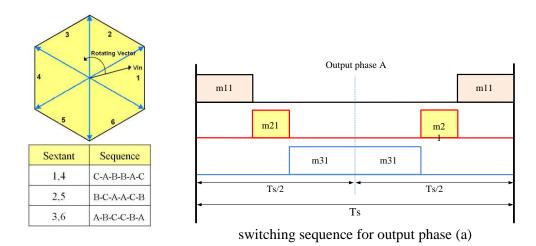

| Figure 2-17 Switching sequence for output phase a.                                 | 35 |

|------------------------------------------------------------------------------------|----|

| Figure 2-18 Output phase voltage (a) using basic Venturini modulation              | 35 |

| Figure 2-19 Output line voltage V <sub>ab</sub> using basic Venturini modulation   | 36 |

| Figure 2-20 Switching sequence according to input voltage vector position          | 37 |

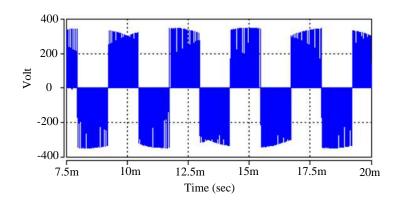

| Figure 2-21 Line to line output voltage using cyclic Venturini                     | 37 |

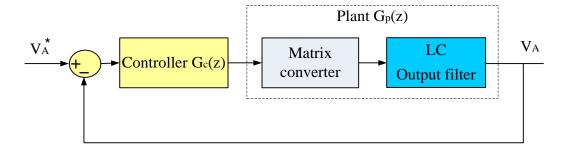

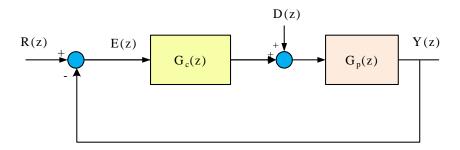

| Figure 3-1 Simplified single phase close loop system of the converter              | 40 |

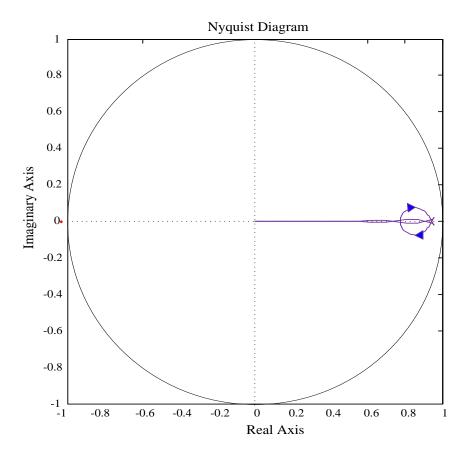

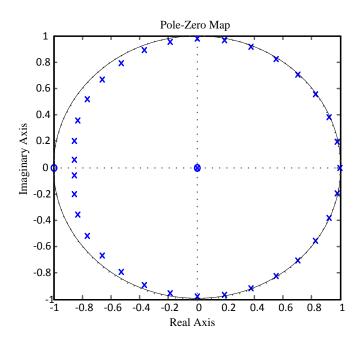

| Figure 3-2 Root locus of Gp(z)*Gc(z)                                               | 44 |

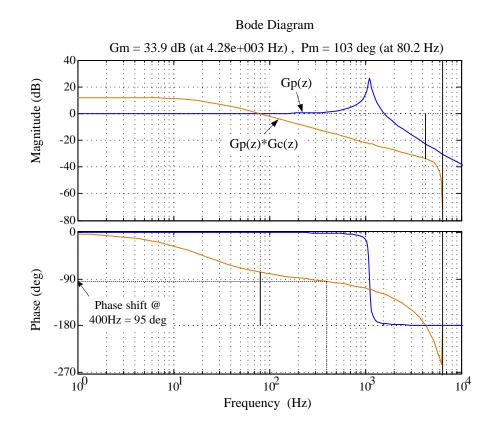

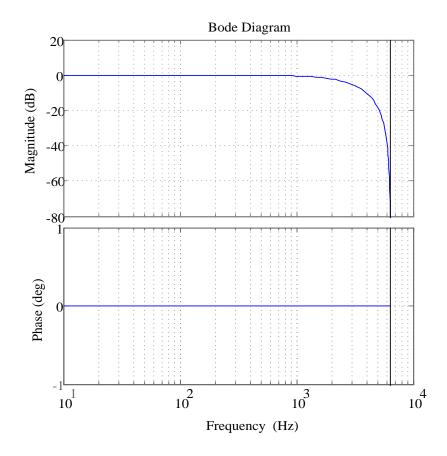

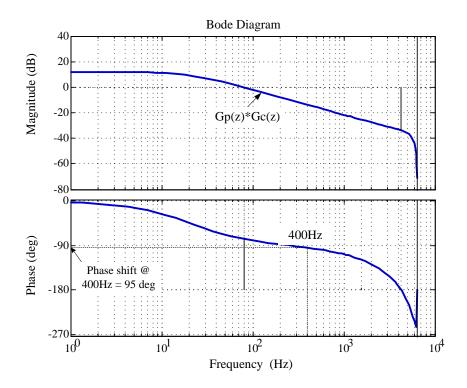

| Figure 3-3 Bode plot of the Gp(z) and Gp(z)*Gc(z)                                  | 45 |

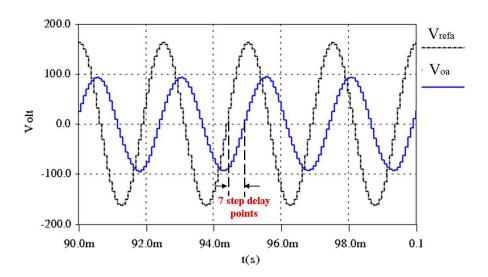

| Figure 3-4 Output voltage response of the converter using second order controller. |    |

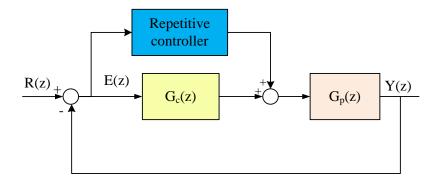

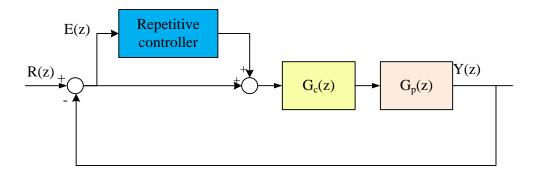

| Figure 3-5 Direct structure repetitive control                                     | 47 |

| Figure 3-6 Parallel structure repetitive control.                                  | 47 |

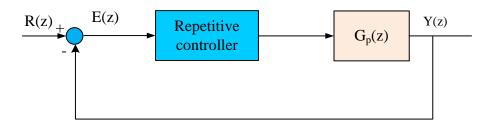

| Figure 3-7 plug-in type repetitive control.                                        | 48 |

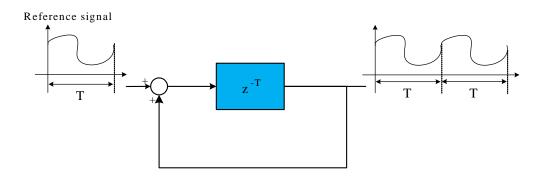

| Figure 3-8 Periodic signal generator                                               | 49 |

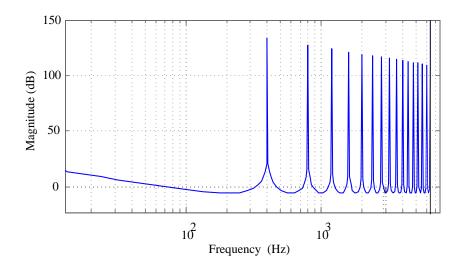

| Figure 3-9 Bode plot of periodic generator.                                        | 49 |

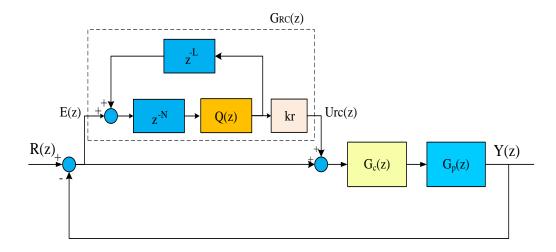

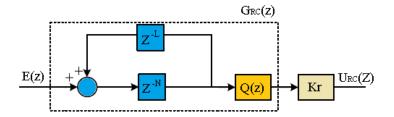

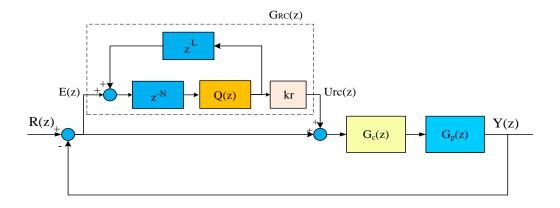

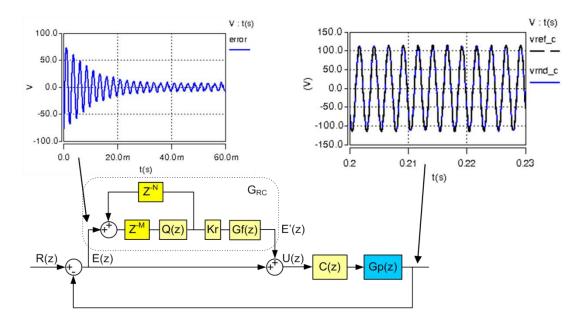

| Figure 3-10 Block diagram of the overall system.                                   | 50 |

| Figure 3-11 Different repetitive controller structure[76]                          | 51 |

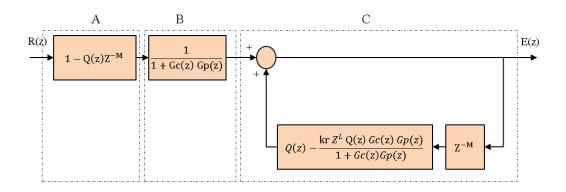

| Figure 3-12 Equivalent system block diagram of equation 3-16                       | 52 |

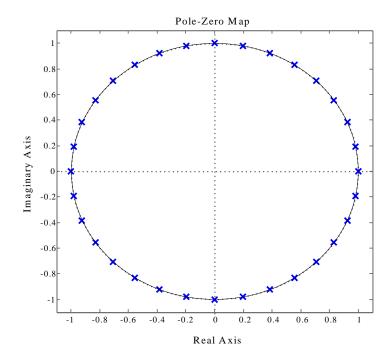

| Figure 3-13 Pole zero map of the system in Figure 3-8                              | 53 |

| Figure 3-14 Negative feedback system                                               | 53 |

| Figure 3-15 The Nyquist diagram of S(z).                                           | 55 |

| Figure 3-16 Bode plot of Q(z)                                                               |

|---------------------------------------------------------------------------------------------|

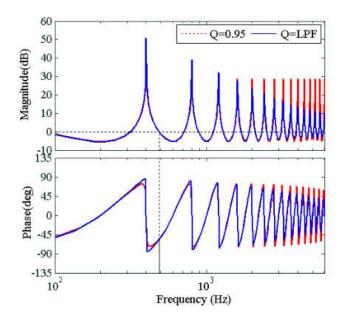

| Figure 3-17 Bode plot of Grc(z) using Q(z) as a constant and as a low pass filter 57        |

| Figure 3-18 Pole zero map of $Grc(z)$ using $Q(z)$ as a low pass filter, $(z+2+z^{-1})/457$ |

| Figure 3-19 Bode plot of Gc(z) Gp(z)59                                                      |

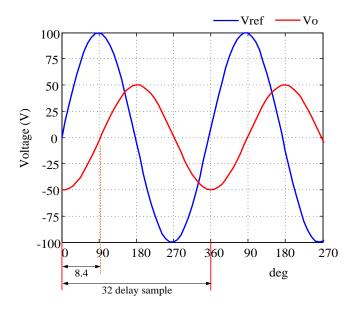

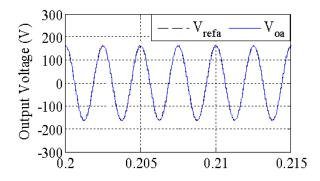

| Figure 3-20 Reference and output voltage using second order linear controller only          |

|                                                                                             |

| Figure 3-21 Proposed plug-in repetitive controller                                          |

| Figure 3-22 Output voltage compared with the reference using plug-in repetitive             |

| controller. 62                                                                              |

| Figure 3-23 proposed repetitive controller                                                  |

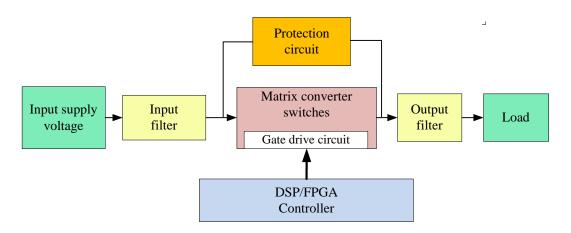

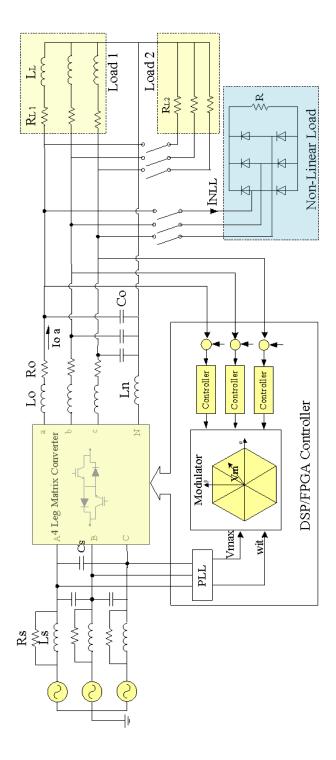

| Figure 4-1 GPU structure 65                                                                 |

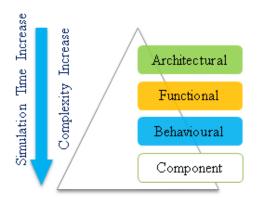

| Figure 4-2 Modelling levels.                                                                |

| Figure 4-3 Matrix Converter system. 68                                                      |

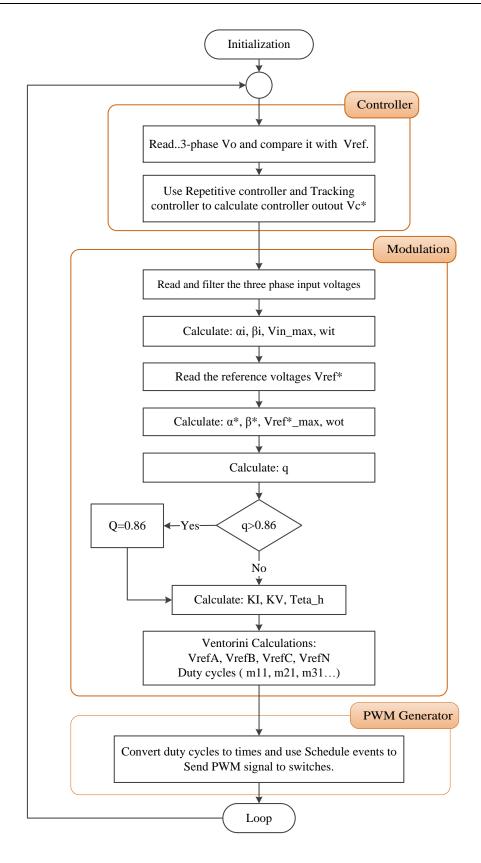

| Figure 4-4 Modulation and control simulation flow chart                                     |

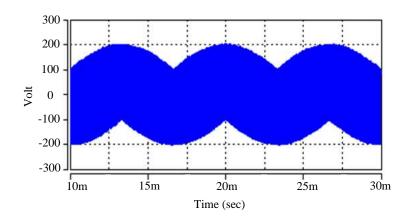

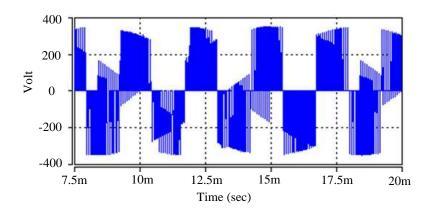

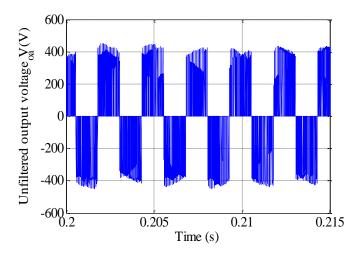

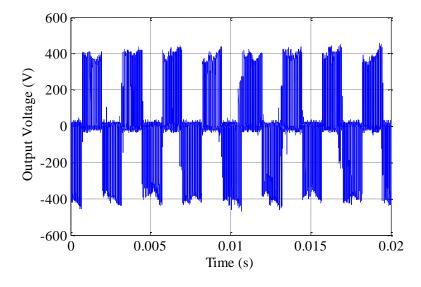

| Figure 4-5 Phase A unfiltered output voltage72                                              |

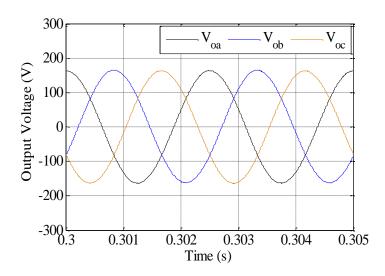

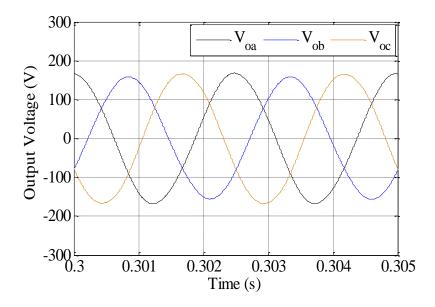

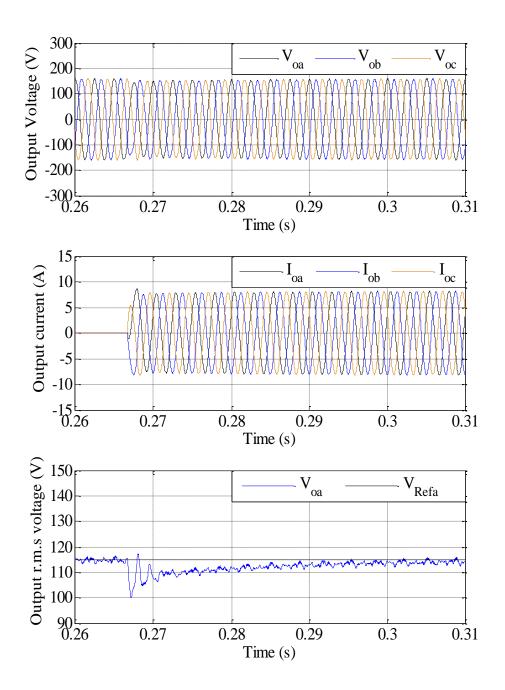

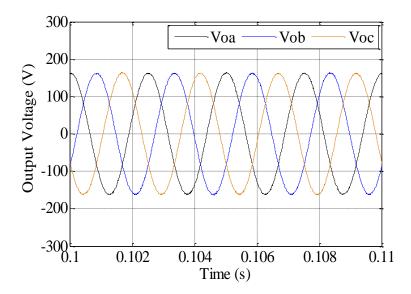

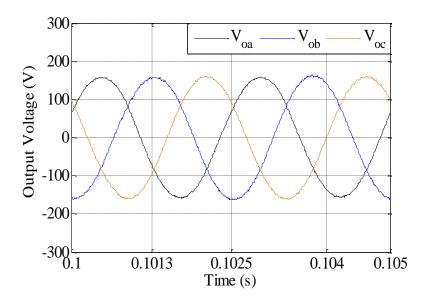

| Figure 4-6 Three-phase output voltage for a balanced load                                   |

| Figure 4-7 Filtered output voltage spectra for a balanced load                              |

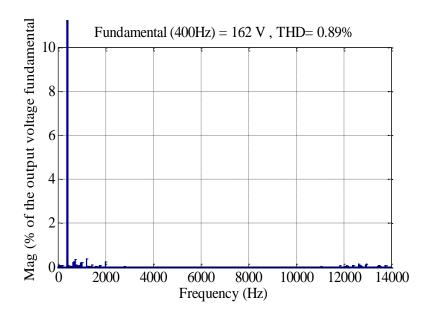

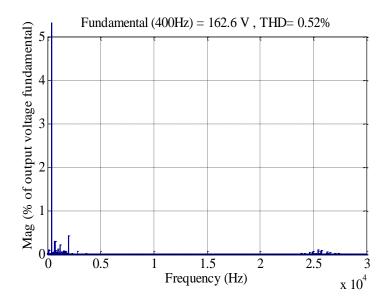

| Figure 4-8 R.M.S output voltage for a balanced load phase A                                 |

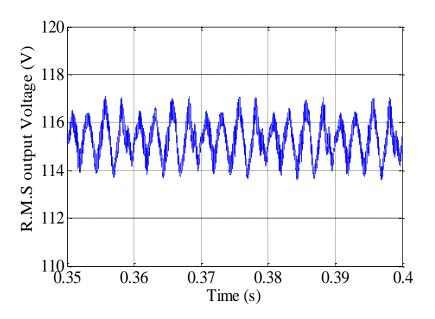

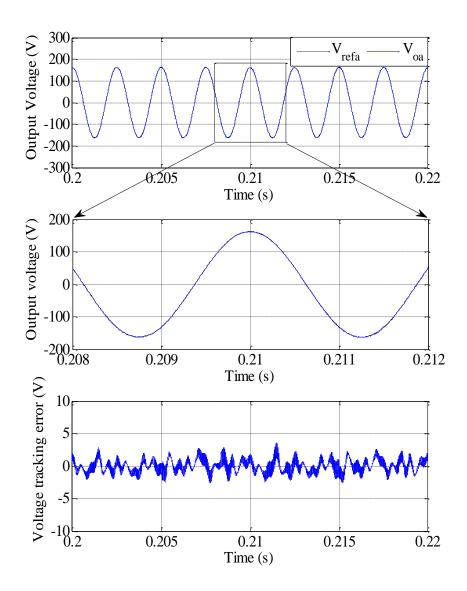

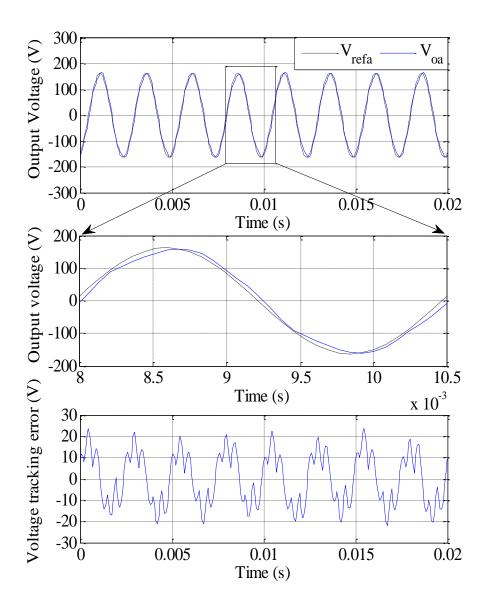

| Figure 4-9 Output voltage tracking for a balanced load phase A                              |

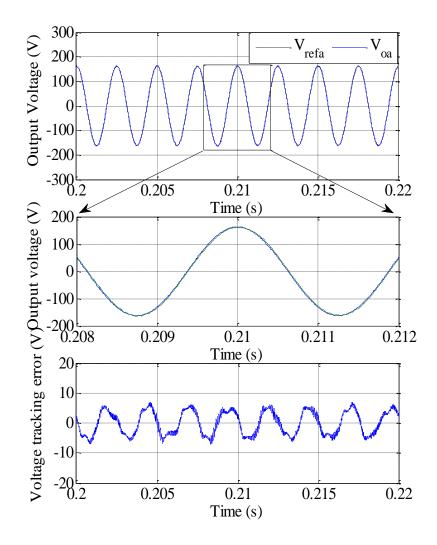

| Figure 4-10 Three phase output currents for a balanced load                                 |

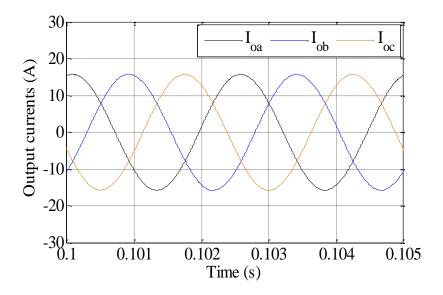

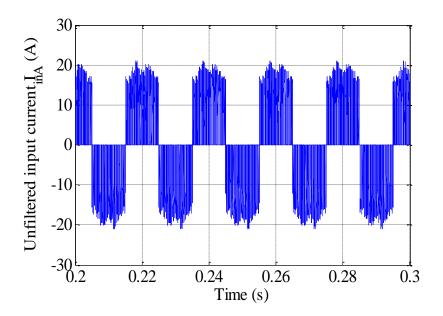

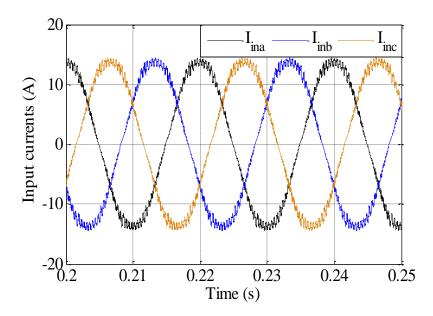

| Figure 4-11 Unfiltered input current in phase A                                             |

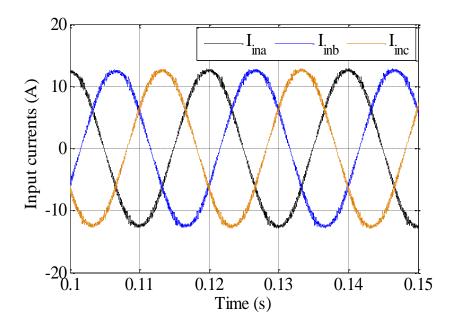

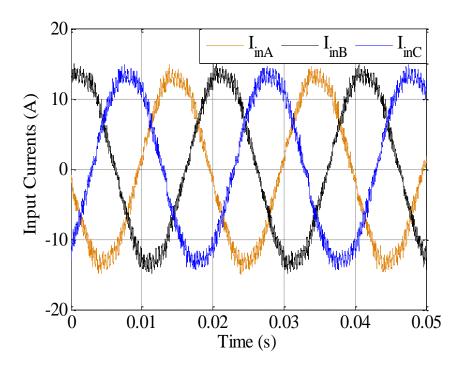

| Figure 4-12 Filtered three phase input currents for a balanced load                         |

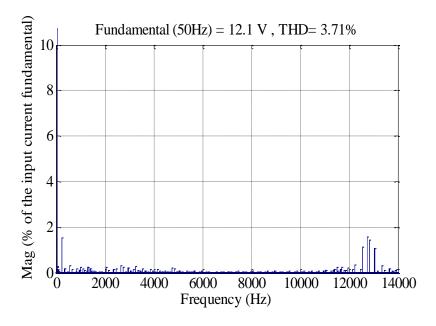

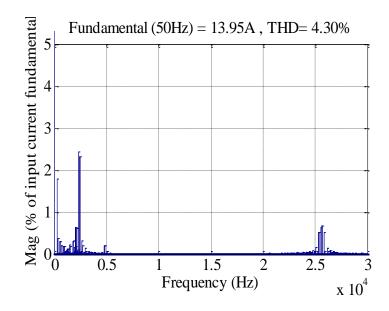

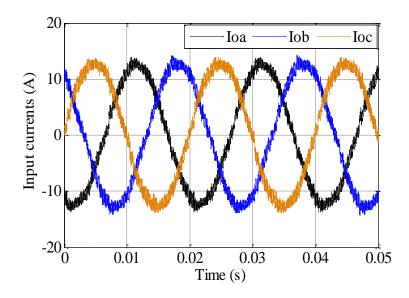

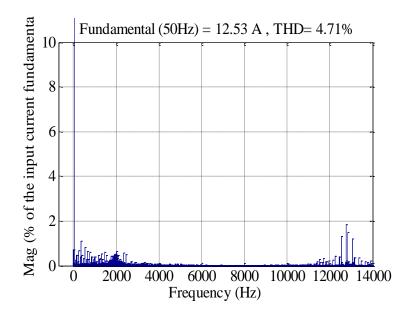

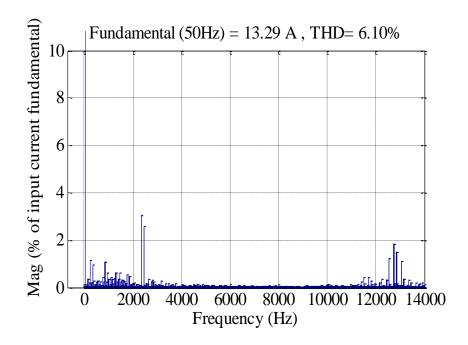

| Figure 4-13 Filtered input current spectra of phase A, for a balanced load |

|----------------------------------------------------------------------------|

| Figure 4-14 The three phase output voltages for an unbalanced load         |

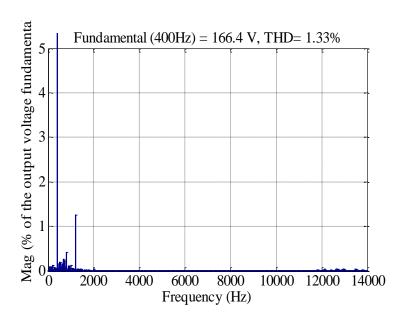

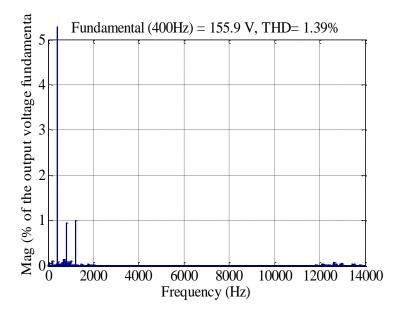

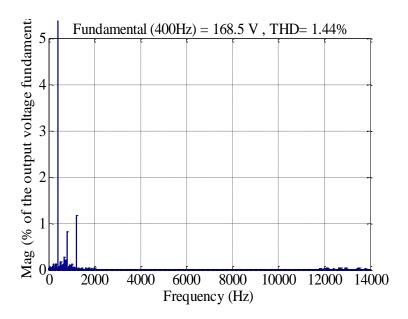

| Figure 4-15 FFT of output phase voltage A for an unbalanced load           |

| Figure 4-16 FFT of output phase voltage B for an unbalanced load           |

| Figure 4-17 FFT of output phase voltage C for an unbalanced load           |

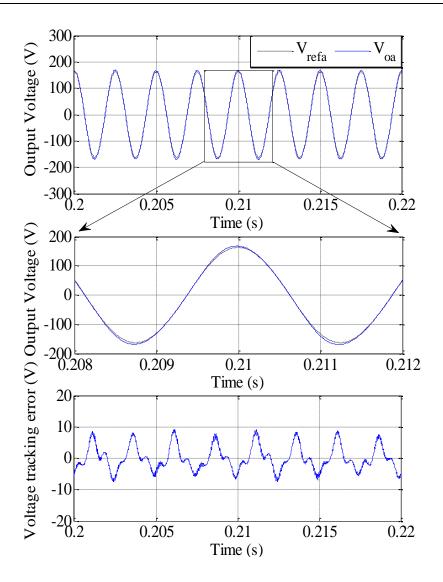

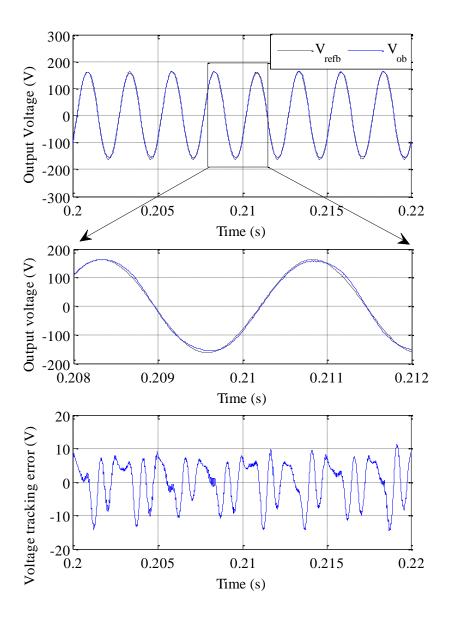

| Figure 4-18 Output voltage tracking of phase (a) for an unbalanced load 80 |

| Figure 4-19 Output voltage tracking of phase (b) for an unbalanced load    |

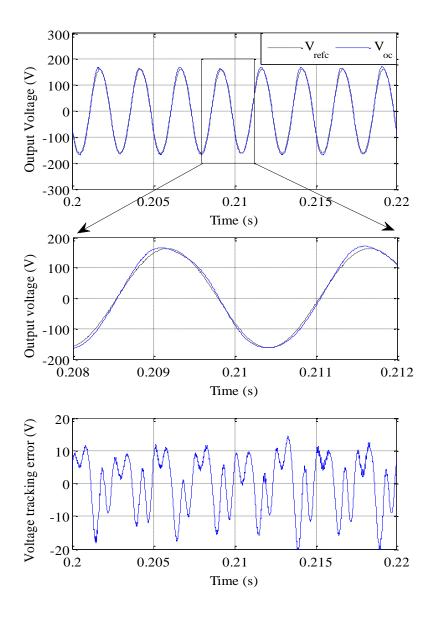

| Figure 4-20 Output voltage tracking of phase (c) for an unbalanced load 82 |

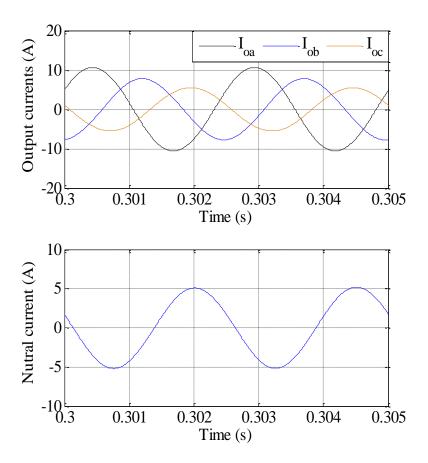

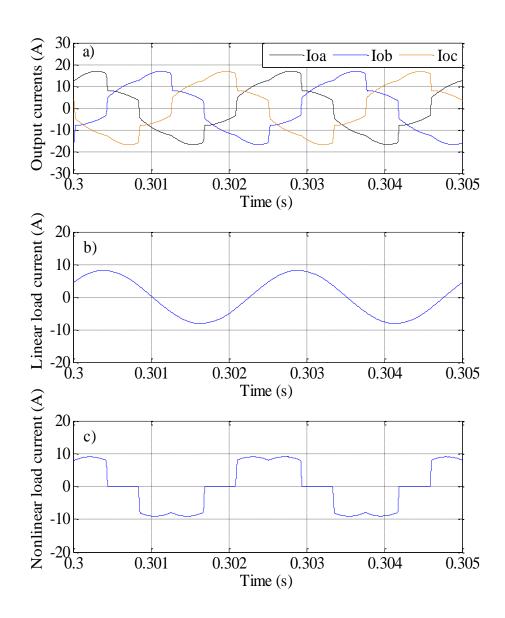

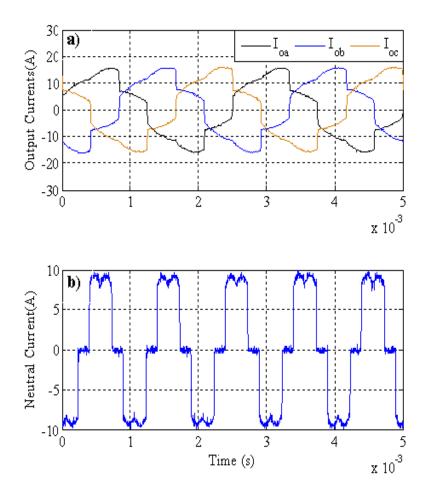

| Figure 4-21 Output currents for the unbalance load condition               |

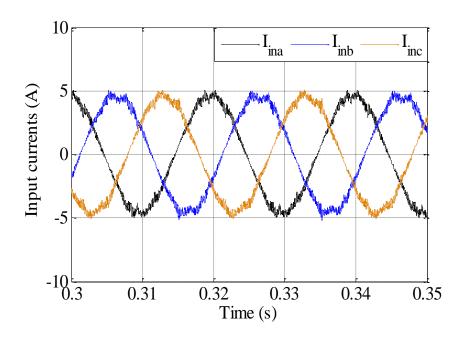

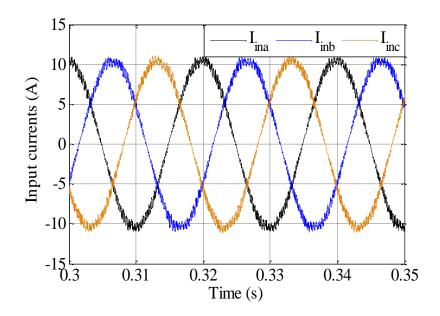

| Figure 4-22 Three phase input currents for an unbalanced load              |

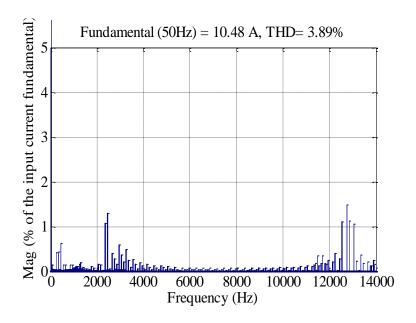

| Figure 4-23 Input current spectra of phase A, for an unbalanced load       |

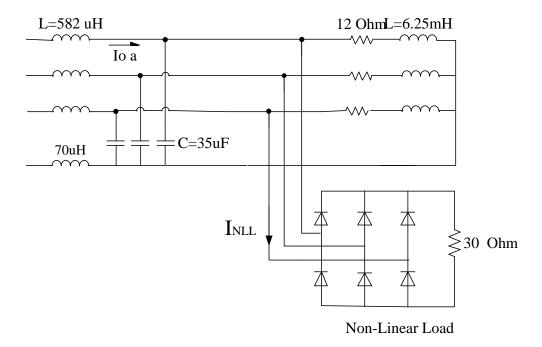

| Figure 4-24 Three phase non-linear load circuit.                           |

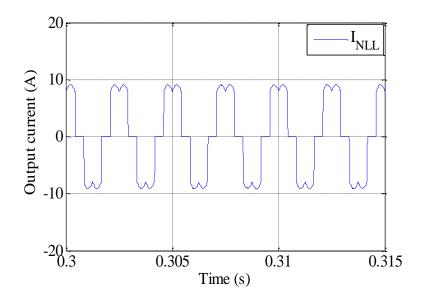

| Figure 4-25 Non-linear load current                                        |

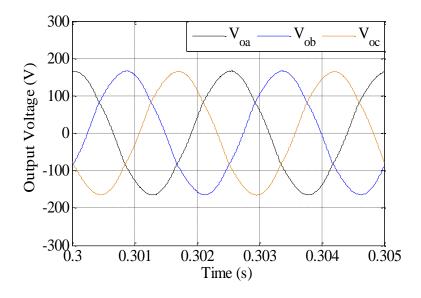

| Figure 4-26 Three phase output voltages for a non-linear load              |

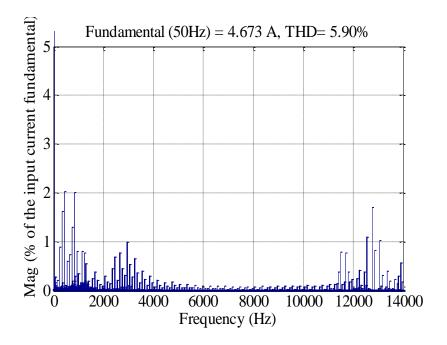

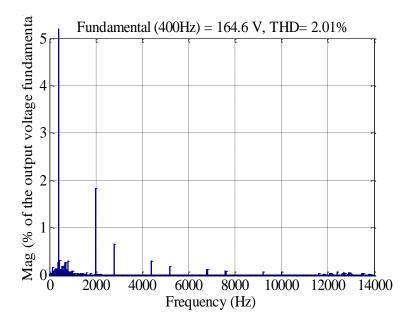

| Figure 4-27 Output voltage spectrum with non-linear load (phase A)         |

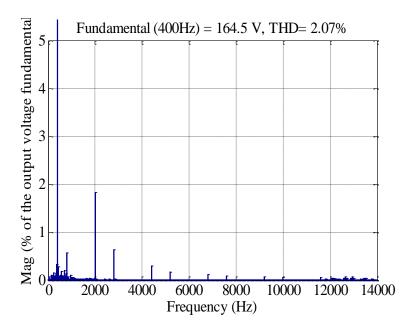

| Figure 4-28 Output voltage spectrum with non-linear load (phase B)         |

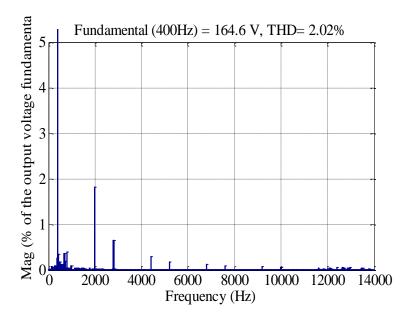

| Figure 4-29 Output voltage spectrum with non-linear load (phase C)         |

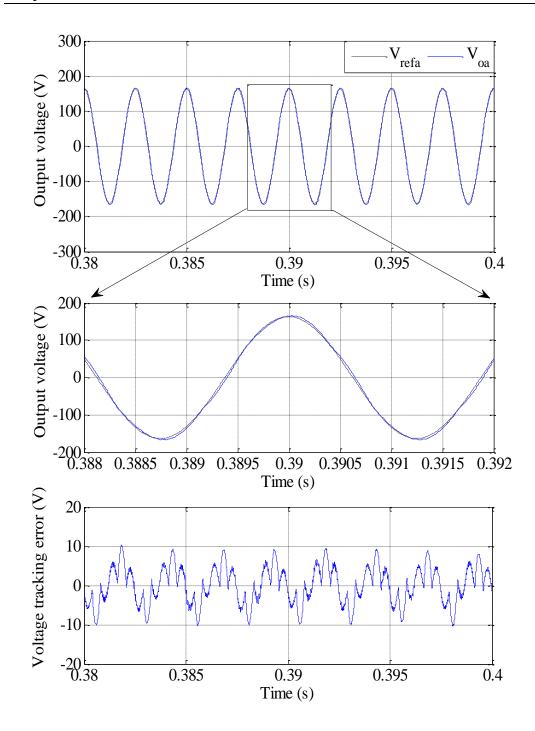

| Figure 4-30 Output voltage tracking for a Non-linear load                  |

| Figure 4-31 Three phase output currents with non-linear load               |

| Figure 4-32 Three phase input currents with non-linear load                |

| Figure 4-33 Input current spectra of phase A, for a non-linear load        |

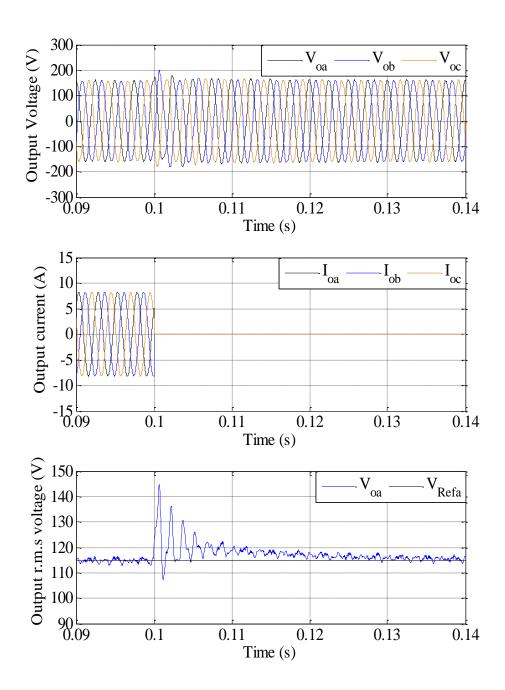

| Figure 4-34 Output voltage response due to a three phase load disconnection 93           |

|------------------------------------------------------------------------------------------|

| Figure 4-35 Output voltage response due to a three phase load connection94               |

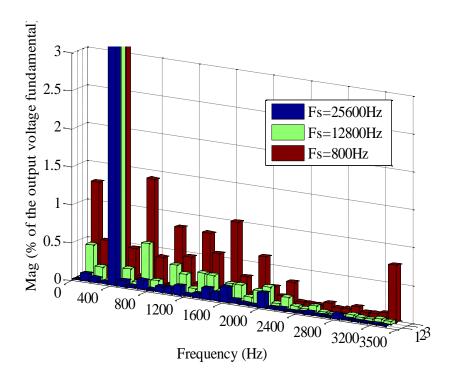

| Figure 4-36 The effect of increasing the switching frequency on output voltage's quality |

| Figure 4-37 Three phase output voltage waveforms using an 8kHz switching frequency       |

| Figure 4-38 Output voltage spectra using an 8kHz switching frequency                     |

| Figure 4-39 Output voltage tracking of phase A for an 8kHz switching frequency98         |

| Figure 4-40 Three phase input current waveforms using an 8kHz switching frequency.       |

| Figure 4-41 Filtered input current spectra for an 8kHz switching frequency99             |

| Figure 4-42 Three phase output voltage waveforms using a 12.8kHz switching frequency     |

| Figure 4-43 Output voltage spectra using a 12.8 kHz switching frequency 101              |

| Figure 4-44 Output voltage tracking of phase A for a 12.8kHz switching frequency.  102   |

| Figure 4-45 Three phase input current waveforms using a 12.8kHz switching frequency      |

| Figure 4-46 Input current spectra for a 12.8kHz switching frequency                      |

| Figure 4-47 Three phase output voltage waveforms using a 25.6kHz switching frequency     |

| Figure 4-48 Output voltage spectra using a 25.6 kHz switching frequency 105              |

| Figure 4-49 Output voltage tracking of phase A for a 25.6kHz switching frequency.        |

| Figure 4-50 Three phase input current waveforms using a 25.6kHz switching frequency |

|-------------------------------------------------------------------------------------|

| Figure 4-51 Input current spectra for a 25.6kHz switching frequency                 |

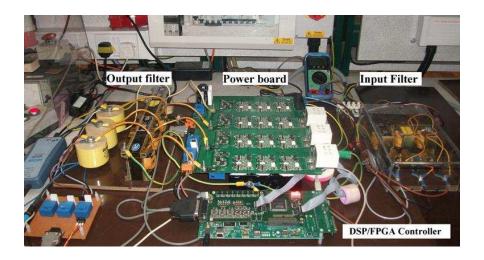

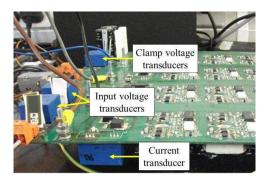

| Figure 5-1- Laboratory prototype of the four-leg Matrix Converter                   |

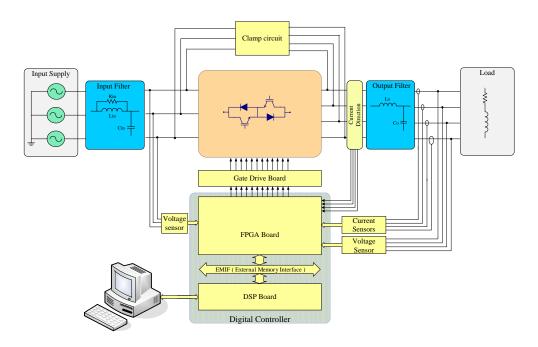

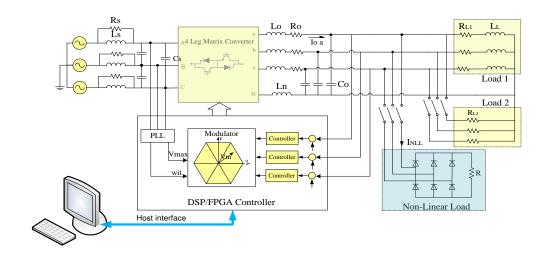

| Figure 5-2 Overall layout of the experimental prototype                             |

| Figure 5-3 Input filter circuit                                                     |

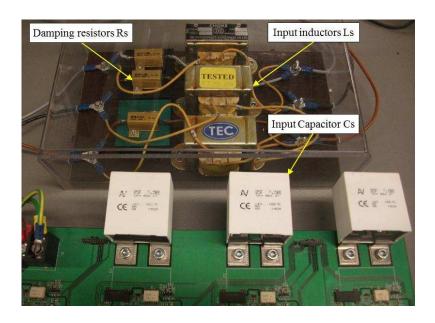

| Figure 5-4 Input filter photograph                                                  |

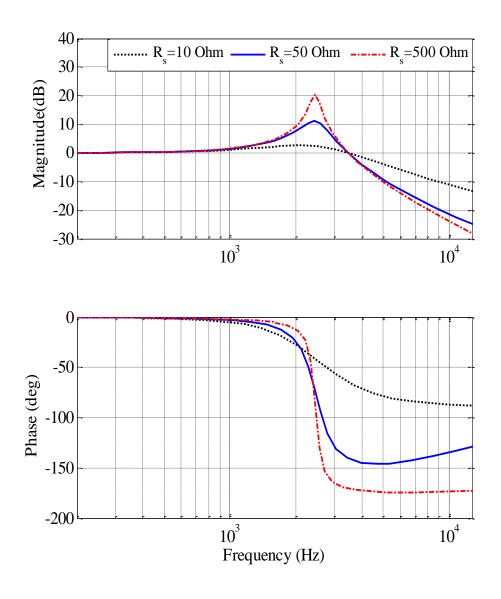

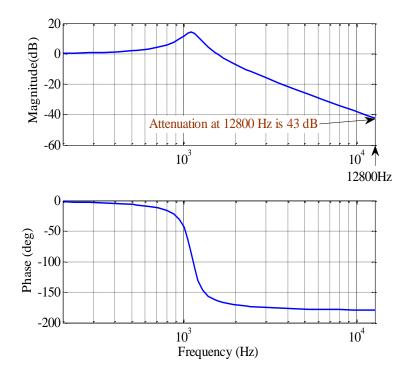

| Figure 5-5 Input filter bode plot                                                   |

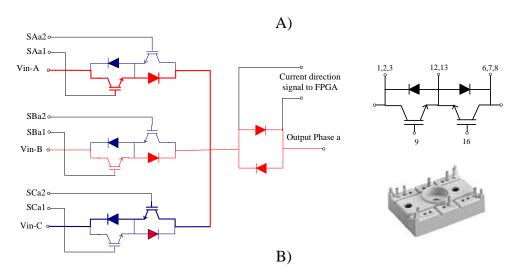

| Figure 5-6 IGBT power circuit                                                       |

| Figure 5-7 Gate drive circuit for one bi-directional switch module                  |

| Figure 5-8 Current direction detection circuit                                      |

| Figure 5-9 Photograph of the current direction circuit                              |

| Figure 5-10 Voltage clamp circuit                                                   |

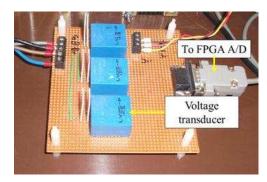

| Figure 5-11 The voltage and current transducers                                     |

| Figure 5-12 Circuit diagram of the measurement circuit                              |

| Figure 5-13 three phase matrix converter showing the input and output filters 123   |

| Figure 5-14 Output filter Bode plot                                                 |

| Figure 5-15 DSP/FPGA control platform. 126                                          |

| Figure 5-16 HPI daughter board                                                      |

| Figure 5-17 FPGA simple block diagram                                               |

| Figure 5-18 DSP controller flow chart                                               |

| Figure 6-1 Experimental prototype of four-leg Matrix Converter                   |

|----------------------------------------------------------------------------------|

| Figure 6-2 Output phase to neutral voltage measured before the output filter 134 |

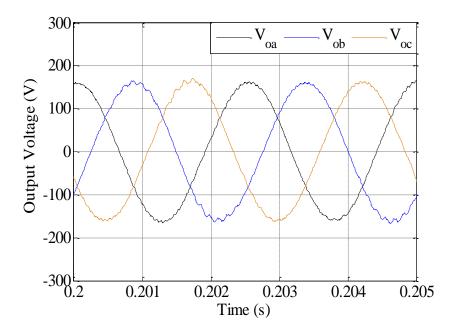

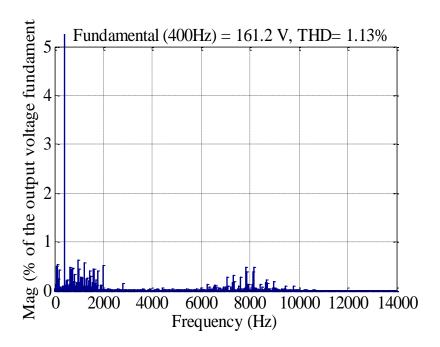

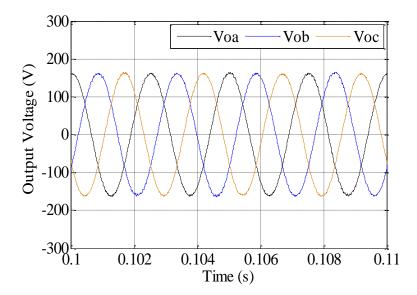

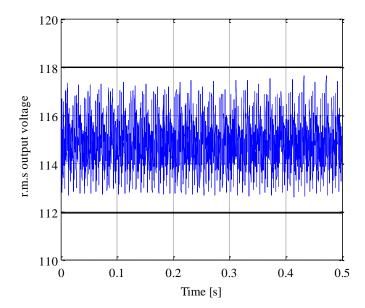

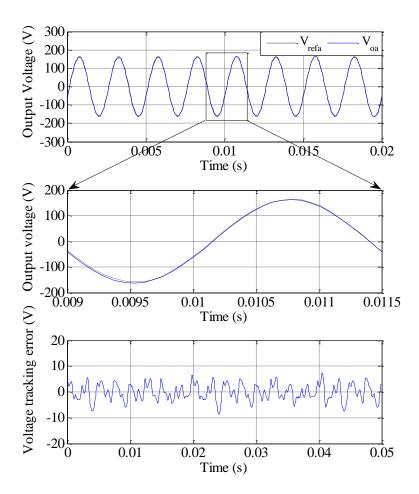

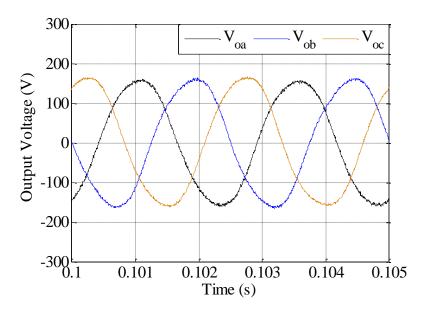

| Figure 6-3 Output voltage for a balanced load                                    |

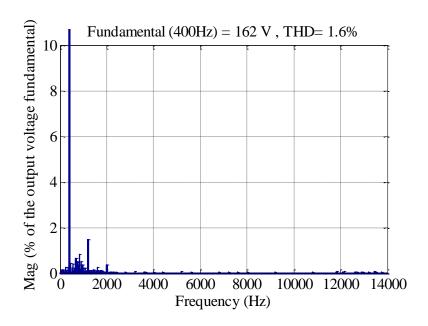

| Figure 6-4 FFT of output phase a balanced load                                   |

| Figure 6-5 R.M.S output voltage for a balanced load                              |

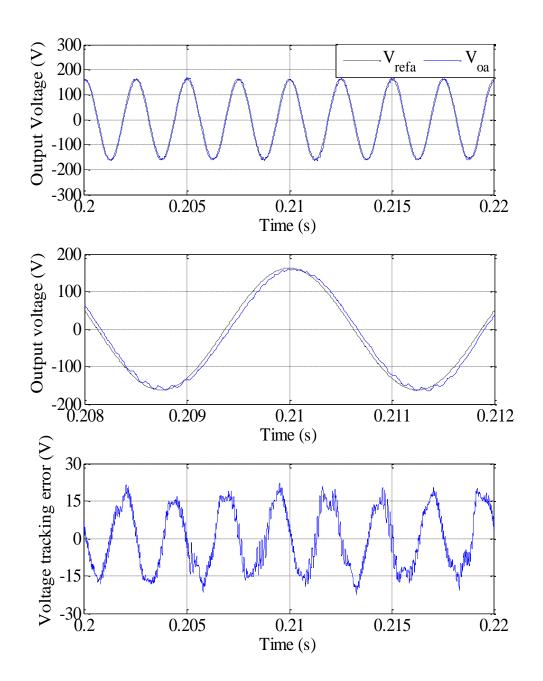

| Figure 6-6 Output voltage tracking for a balanced load                           |

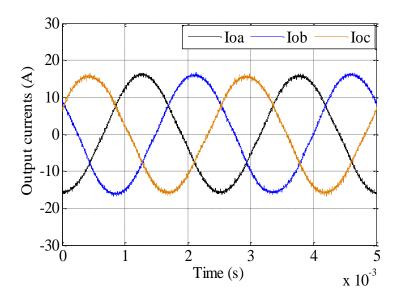

| Figure 6-7 Output currents balanced load. Add captions                           |

| Figure 6-8 Three phase input currents balanced load                              |

| Figure 6-9 Input current spectra of phase A, for a balanced load condition 139   |

| Figure 6-10 Three phase unbalanced load circuit                                  |

| Figure 6-11 Three phase output voltages for an unbalanced load                   |

| Figure 6-12 FFT of output phase (a) for an unbalanced load                       |

| Figure 6-13 FFT of output phase b for an unbalanced load                         |

| Figure 6-14 FFT of output phase c for an unbalanced load                         |

| Figure 6-15 Output voltage tracking for an unbalanced load                       |

| Figure 6-16 Output currents for an unbalance conditions                          |

| Figure 6-17 Three phase input currents for an unbalanced load                    |

| Figure 6-18 Input current spectra of phase A, for unbalanced load condition 145  |

| Figure 6-19 Three phase non-linear load circuit                                  |

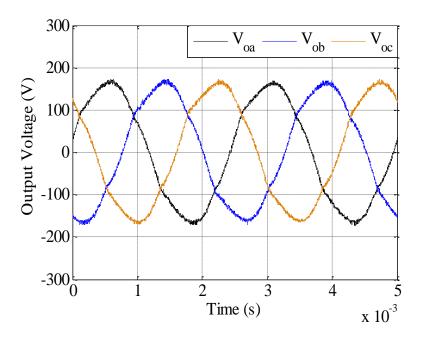

| Figure 6-20 Three phase output voltages for a non-linear load                    |

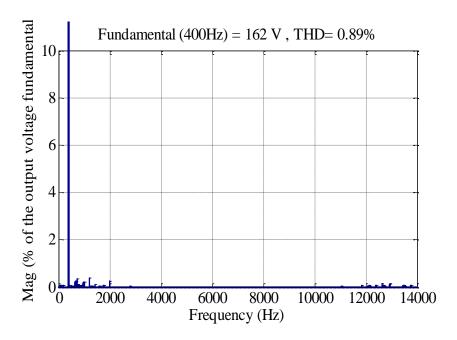

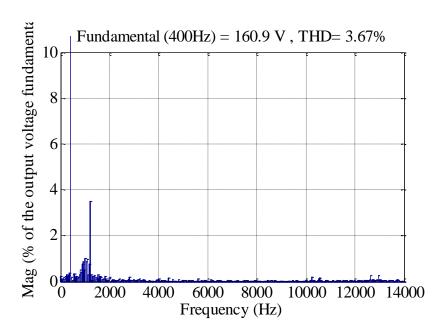

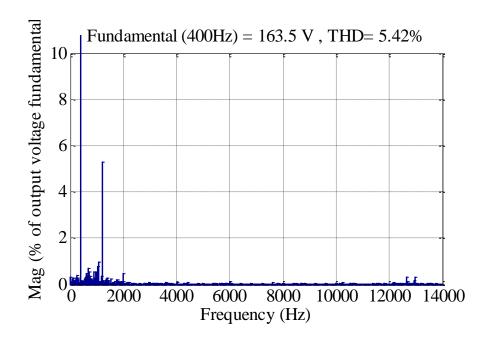

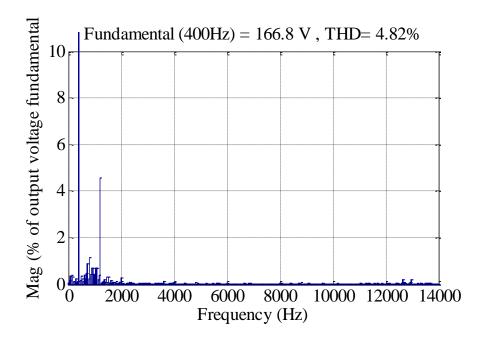

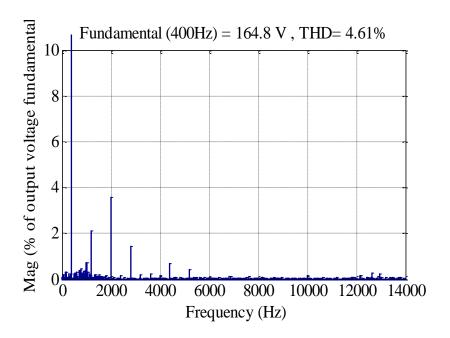

| Figure 6-21 Output voltage spectrum with non-linear load (phase A)               |

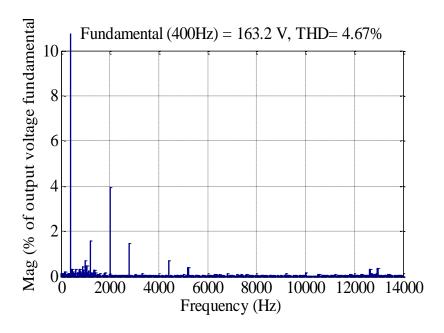

| Figure 6-22 Output voltage spectrum with non-linear load (phase B)                |

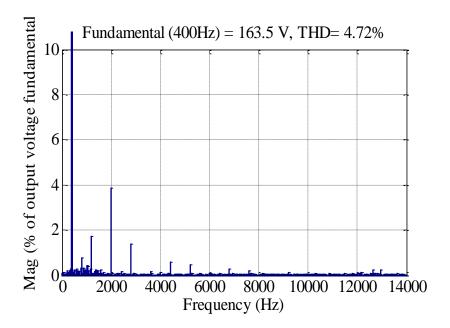

|-----------------------------------------------------------------------------------|

| Figure 6-23 Output voltage spectrum with non-linear load (phase C)                |

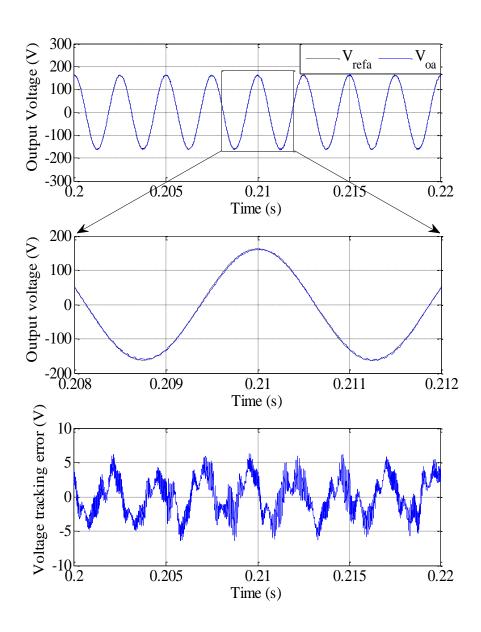

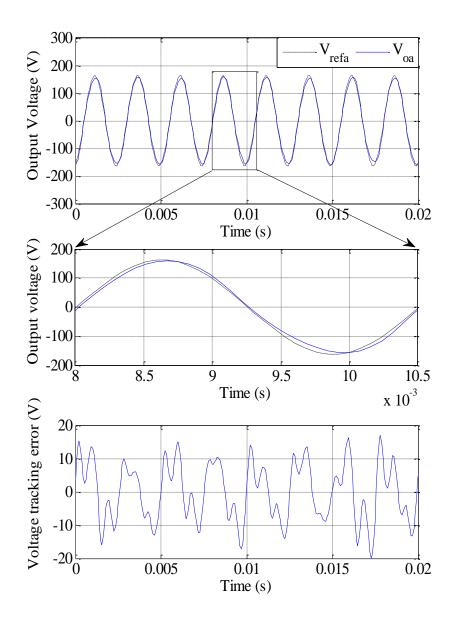

| Figure 6-24 The output voltage tracking for a Non-linear load                     |

| Figure 6-25 Three phase output currents with non-linear load                      |

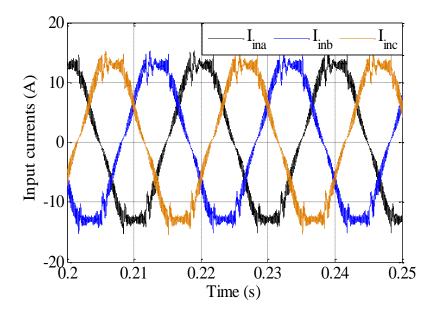

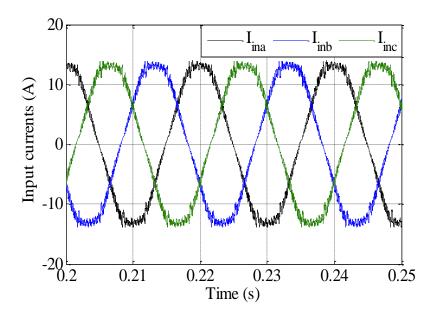

| Figure 6-26 Three phase input currents with non-linear load                       |

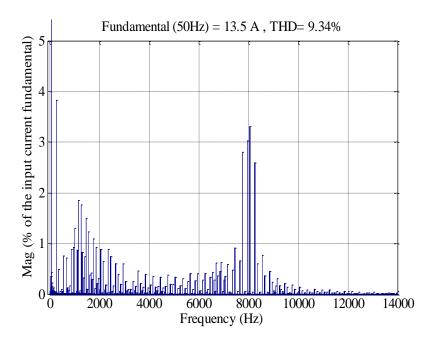

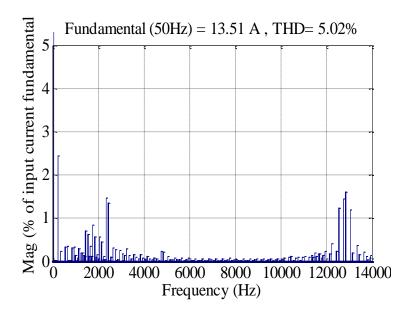

| Figure 6-27 Input current spectra of phase A, for a non-linear load condition 152 |

| Figure 6-28 Output voltage response due to load connection                        |

| Figure 6-29 Output voltage response due to load disconnection                     |

| Figure B1: Cyclic Venturini switching sequence where kv=1, ki=1, Tetrahedron=2.   |

| 173                                                                               |

## List of tables

| Table 1-1 Military standards for aircraft electrical power systems [5]                                    |

|-----------------------------------------------------------------------------------------------------------|

| Table 2-1 Switching states of three phase Matrix Converter[57]                                            |

| Table 2-2 Selection of switching configuration according to output voltage and input current sectors [13] |

| Table 2-3 Rotating vector states for four-leg Matrix Converter                                            |

| Table 2-4 zero vectors and stationary states for four-leg Matrix Converter27                              |

| Table 4-1 Summary of the simulation results for four-leg Matrix Converter system.  108                    |

| Table 4-2 The effect of increasing the switching frequency on Matrix Converter performance                |

| Table 6-1 Matrix Converter parameters                                                                     |

| Table 6-2 Summary of the simulation and experemintal results for four-leg Matrix Converter system         |

| Table B-2: Ki = 1 , Tetrahedron = 2                                                                       |

| Table B-3: Ki = 1, Tetrahedron = 3                                                                        |

| Table B-4: Ki = 2, Tetrahedron = 2                                                                        |

| Table B-5: Ki = 2, Tetrahedron = 3                                                                        |

| Table B-6: Ki = 3, Tetrahedron = 2                                                                        |

| Table B-7: Ki = 3, Tetrahedron = 3                                                                        |

| Table B-8: Ki = 4, Tetrahedron = 2                                                                        |

| Table B-9: Ki = 4, Tetrahedron = 3                                                                        |

| Table B-10: $Ki = 5$ , Tetrahedron = 2 | 175 |

|----------------------------------------|-----|

| Table B-11: Ki = 5, Tetrahedron = 3    | 175 |

| Table B-12: Ki = 6, Tetrahedron = 2.   | 176 |

| Table B-13: Ki = 6 . Tetrahedron = 3   | 176 |

# **Chapter 1 Introduction:**

## 1.1 Introduction

There is a growing interest in the use of static power conversion techniques to provide high-performance AC power supplies applications such as uninterruptible power supplies, automatic voltage regulators, programmable AC sources and ground power units (GPUs) for aircraft. In the past static rotating motor-generator systems were used in these applications. But, more recently static power frequency converters have been considered [1]. The power converter topology used in these applications could be an indirect power converter (AC-DC-AC converter), where a standard 3-phase rectifier/inverter is used or a direct power converter (AC-AC Matrix Converter), where the AC input converted directly. A Matrix Converter (MC) is a direct power converter which can be used to convert AC supply voltages into variable magnitude and frequency output voltages, as shown in Figure 1-3 [2]. The advantages of the MC over rectifier/inverter systems are the sinusoidal input current waveforms, the controllable input displacement factor and the fact that there is no energy storage element or DC link.

For power supply applications, where different loads needs to be supplied ranging from balanced, unbalanced and non-linear loads. In such application, 3x3 power converters will be unable to provide a regulated output voltage. This is because; the converter needs to be able to deal with zero sequence current in the system.

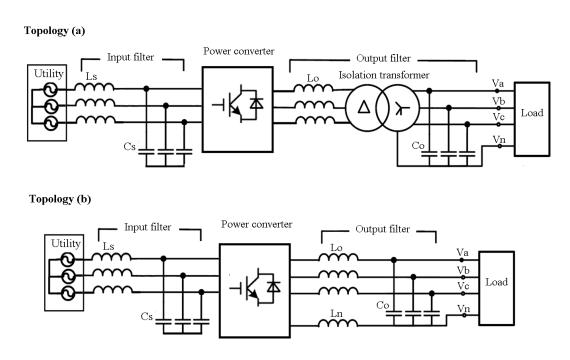

Ground power units (GPU) are designed to provide a high quality power to aircraft at airports at 400Hz, 115V. Static power converters are environmentally friendly and require low maintenance compared to motor generator systems, and the typical rating are up to 90 kVA per unit [3],[4]. Two possible topologies of a three-phase GPU are shown in Fig 1-1. Topology (a) has a three-leg converter supplying a four leg Delta-Star connected transformer while topology (b) has a three phase four leg converter.

Figure 1-1 GPU possible topologies.

The first topology has the advantage of isolation, but the transformer increases the size and the weight of the system. On the other hand, the second topology is more compact and has less weight due to the absence of the transformer.

## 1.2 Power supply aircraft standards

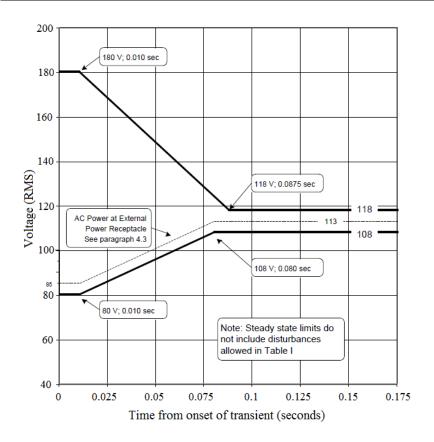

In order to ensure reliable and safe operation of power supply systems, military authorities have established guidelines on power quality for aircraft applications. Table 1-1 details the requirements for these systems which are normally 400Hz, three phase four wire systems. Figure 1-2 shows the allowable output voltage transient envelope.

Table 1-1 Military standards for aircraft electrical power systems [5].

| Steady state voltage     | 108 to 118 Vrms |

|--------------------------|-----------------|

| Peak transient voltage   | 271.8 Vrms      |

| Voltage unbalance        | 3 Vrms          |

| Voltage phase difference | 116o to 124o    |

| Voltage distortion       | 5%              |

| Steady state frequency   | 393Hz to 407 Hz |

Figure 1-2 Envelope of normal 400 Hz and variable frequency AC voltage transient.

A 400 Hz system is used in applications where space and weight are important factors. Due to the higher fundamental frequency, passive components in 400Hz systems are much smaller (compared to 50Hz, for example); this means that the system will be lighter and occupy less volume. However, in the design of a converter with a 400Hz output frequency a high bandwidth controller is required. The reduced ratio between the converter switching frequency and the fundamental frequency limits the maximum controller bandwidth. In this case periodic errors and distortion will exist. A repetitive control (RC) provides a possible solution to minimize these periodic errors [6], [7].

Under unbalanced loading, negative and zero sequence components can cause unbalance output voltages and unequal phase shift between the phases. The neutral wire in the four-leg Matrix Converter is used to provide a path for the zero sequence components and allow independent control for each output phase voltage.

Figure 1-3 Matrix Converter with ABC reference control

## 1.3 Matrix Converters:

A Matrix Converter is an array of bidirectional switches that can directly connect any input phase to any output phase to create a variable voltage and frequency at the output. There are several advantages of Matrix Converters such as:

- o No DC-link, leading to reduced converter weight and size.

- o Simple and compact power circuit.

- The ability to control the output voltages and input currents which results in a nearly sinusoidal input current with a unity power factor.

- o 4 quadrant operations.

The development of Matrix Converters started in early 1980's after Alesina and Venturini introduced their basic operation principles [8]. They presented a converter with an array of bidirectional switches and they introduced the name of Matrix Converter. The main contribution of Alesina and Venturini was the development of mathematical analysis that describes the low frequency behaviour of Matrix Converter. In their basic modulation method the voltage transfer ratio was limited to 0.5, but by the introducing the third harmonics technique the voltage transfer ratio increased the ratio to 0.86 [9]. The concept of the indirect transfer function technique was introduced in 1983 by Rodriguez [10]. This method was based on switch arrangement to switch between the most positive and negative input line using the same PWM technique as used in standard Voltage source inverters (VSI).

The use of space vectors in the modulation of Matrix Converters was introduced by Braun in 1983 [11] and Kastner and Rodriguez in 1985 [12]. Then, this was then extended with Casadei at all paper in 2002 [13], by giving a full Space Vector modulation strategy that controlled the output voltage and the input power factor [14]. However instantaneous commutation of the bidirectional switches used in MC's was difficult to achieve without overvoltage and current spikes that might destroy the switches, and this effected the practical implementation of the converters. Fortunately, the commutation problem was solved by the development of commutation techniques such as the semisoft current commutation technique [15]. Other advanced commutation strategies were introduced later to allow safe and

reliable operation of the switches [16], [17]. Today research activity is mainly dedicated to studying advanced technological and applications issues such as the reliable implementation of commutation strategies [18, 19], overvoltage protection [20, 21], packaging [22], operation under abnormal conditions [4, 23, 24], controller designs such as dead beat control [25, 26], predictive control [27], Genetic Algorithms [1] and sliding mode control [28].

#### 1.3.1 Matrix Converter control

The application of digital controller in the field of switch mode power supplies attracts increased attention due to several advantages. First of all, is the possibility to implement complex and sophisticated control structure and modify or sometimes to reprogram the controller, which is not an easy task using analogue controllers. Secondly, Signal manipulation and taking care of nonlinearities and parameter variation is very attractive feature of digital controllers. In addition, thermal drifts and ageing effect do no longer exist in the digital controller. Finally, the rapid increase in the digital circuit computational power and the continuous reduction of cost is a great advantage of digital controllers.

## 1.4 Repetitive control

The concept of repetitive control was originally developed by Inoue et al. in 1980 for a SISO plants in continuous time domain [29] to track a periodic repetitive signal with defined period T and was applied successfully to control proton synchrotron magnet power supply in 1981 [29]. Based on Internal Model Principle proposed by Francis and Wonham in 1976 [6], any periodic signal with known period T can be generated by including its generator in the stable close-loop [6]. A repetitive control system generates a high gain at the periodic signal fundamental frequency and its integer multiple, therefore a periodic signal can be tracked provided the close loop system is stable. Repetitive controllers have been widely used in applications including PWM inverters [30, 31],[32],[33], PWM rectifiers [34-36], Matrix Converter [4, 37, 38], robotic manipulators [39], disk drive systems [40-42].

## 1.5 Objectives

For a converter with a 400Hz output frequency, a high bandwidth controller is required. The reduced ratio between the converter switching frequency and the fundamental frequency limits the controller bandwidth. In this case periodic errors and distortion can exist.

The main objectives of this project are to:

- 1. Investigate the use of Venturini modulation to enable the control of a 4-Leg Matrix Converter.

- 2. Simulate the 4-leg Matrix Converter using the Saber simulation package.

- 3. Propose control methods that are able to control the output voltages of the converter with balanced, unbalanced and non-linear loads.

- 4. Build a 7.5KW experimental rig to verify the validity of the modulation and the proposed control systems.

## 1.6 Thesis outlines

The thesis is organized into 6 chapters. Chapter II presents the fundamentals of Matrix Converters. This chapter starts by introducing the Matrix Converter structure including the input and output filters and the bidirectional switches that form the heart of the power circuit. The chapter also presents Matrix Converter commutation methods followed by modeling. Finally the chapter presents modulation strategies including the space vector and Venturini modulation methods.

In chapter III, the control design for the four-leg Matrix Converter is presented. Modeling of the four-leg Matrix Converter system is shown and both second order and repetitive control design methods are presented.

In chapter IV, the power converter modeling and simulation methods are shown. Simulation results for the power converter during balanced, unbalanced and non-linear loads are presented. Finally, the switching frequency effect on the converter waveforms is given.

Chapter V presents the hardware implementation of a 7.5KW converter prototype. This chapter describes the overall structure of the prototype converter and explains the design of each circuit such as the input and output filters, power modules, gate drive circuit, current direction circuit, clamp circuit measuring circuit and control platform.

Chapter VI presents the experimental results of prototype converter to demonstrate the effectiveness of the proposed controller. Experimental results are presented in this chapter for different load conditions such as balanced, unbalanced and non-linear loads.

Finally, Chapter VII presents the conclusion of the thesis. This chapter summarizes the PhD research work findings and introduces future work.

# **Chapter 2 Fundamentals of Matrix Converters**

## 2.1 Introduction:

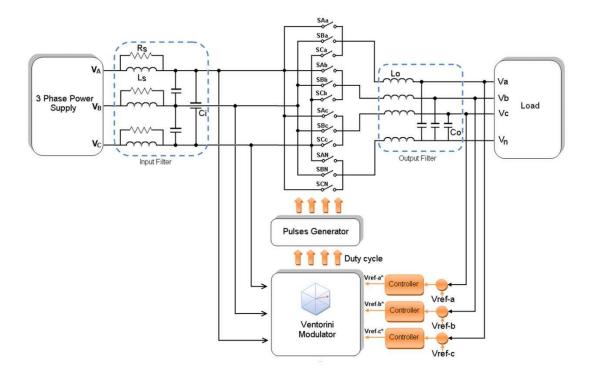

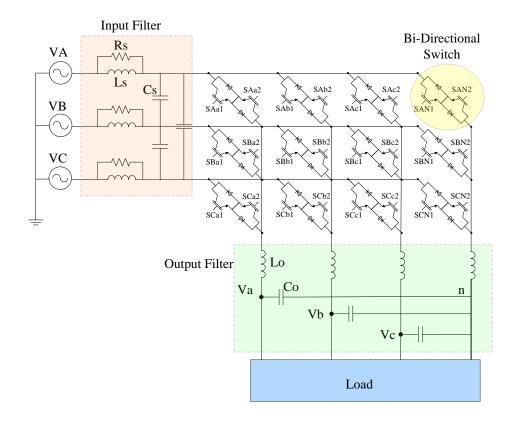

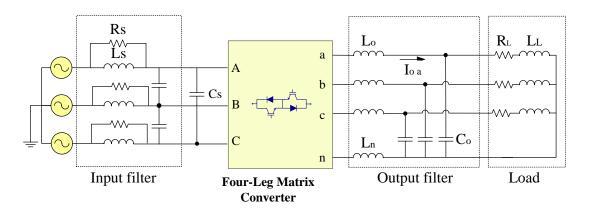

A Matrix Converter is a direct power converter used to convert AC supply voltages into variable magnitude and frequency output voltages. As shown in Figure 2-1 a three phase Matrix Converter consists of array of bi-directional switches that are switched on and off in order to provide variable sinusoidal voltage and frequency to the load. In this type of converter there is no need to the intermediate DC link power circuit and this means no large energy storing capacitors. This will increase the system reliability and reduce the weight and volume for such converters.

Figure 2-1 Four-leg Matrix Converter system

## 2.2 Matrix Converter structure

In this section, the main components of the Matrix Converter will be described. First, the input filter structure and design is investigated. After that the bidirectional power switches are presented. Then the output filter design is discussed. Finally, the clamp circuit that is used to ensure safe operation of the Matrix Converter is also described.

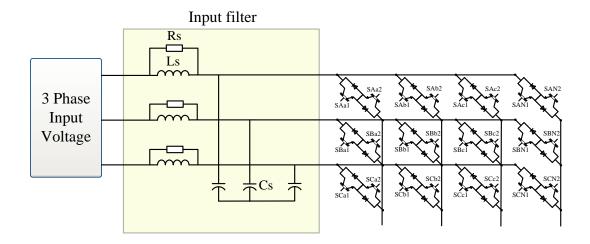

## 2.2.1 Input filter

In power converters input filters are used in order to improve the input current quality and to reduce the input voltage distortion. It acts as an interface between the input power supply and the converter. There are several important features for using the input filter such as [43, 44]:

- it helps to avoid the significant changes of the input supply voltage during each PWM cycle.

- it helps to prevent the unwanted harmonics from flowing into the input power supply.

- it helps to satisfy the electromagnetic interference requirements.

- it helps to protect the converter from transients that appear in the input supply side.

The design of the input filter has to accomplish the following [45]:

- the cut-off frequency of the input filter should be at least one decade above the supply frequency and one decade bellow the switching frequency.

- minimize the voltage drop on the filter inductance at the rated current in order to provide the highest converter voltage transfer ratio.

- minimization of the displacement factor between the supply voltage and the voltages applied to the matrix converter.

- minimization of the ripples in the supply current and the capacitors voltage.

- control the power losses in the damping resistor.

There are a number of different filter topologies can be used for the MC [46]. Among these is the second order LC filter shown in Figure 2-2; it is a common practice to use this topology in many MC applications in view of the low number of components and the satisfactory frequency response that can be achieved [45-50]. Figure 2-2 shows the single phase LCR filter used in this work.

Figure 2-2 Input filter circuit.

The transfer function of the single phase diagram shown in Figure 2-3 of the input filter can be described by [51]:

$$TF = \frac{V_{out}}{V_{in}} = \frac{\left(\frac{1}{R_s.C_s}\right)S + \left(\frac{r}{R_s.L_s.C_s} + \frac{1}{L_s.C_s}\right)}{S^2 + \left(\frac{r}{L_s} + \frac{1}{R_s.C_s}\right)S + \left(\frac{r}{L_s.C_s.R_s} + \frac{1}{L_s.C_s}\right)}$$

The resonant frequency of the output filter can be calculated as:

$$f(Hz) = \frac{1}{2\pi\sqrt{L.C}}$$

Figure 2-3 Input filter Single phase equivalent circuit.

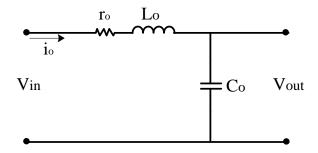

## 2.2.2 Output filter

AC power supplies require a low pass filter (LC filter) at the output side of the converter. The main purpose of the output filter is attenuating voltage ripple from the converter switching. For power supply design, the output impedance of the converter must be close to zero to enable operating as an ideal voltage source. To achieve this, the inductor value is minimized to almost zero and the value of the capacitor should be maximized to keep the same cut-off frequency. However, a high capacitor value is not recommended since the system may face a high inrush current. Also, the power rating of the converter will increase as the capacitor value is increased due to the increment in the filter reactive power. Therefore the inductor value should be chosen as a compromise between these two conditions [52, 53].

Figure 2-4 shows the three phase circuit of the Matrix Converter. The equivalent circuit of the LC output filter is shown in Figure 2-5. In this figure  $r_o$  represents the internal resistance of the output inductor, Lo and Co are the output inductor and

capacitor values. The transfer function of the output filter is important in the design of the control system of the converter and can be calculated from Figure 2-5. The neutral inductor Ln is small compared with the value of filter inductors L<sub>o</sub>, it is used to reduce switching frequency ripples [54].

Figure 2-4 Three phase matrix converter circuit.

Figure 2-5 Output filter single phase equivalent circuit.

The transfer function of the output filter is given by [51]:

$$TF = \frac{\frac{1}{L_o.C_o}}{S^2 + \frac{r_o}{L_o}S + \frac{1}{L_o.C_o}}$$

## 2.2.3 Bidirectional switches

The construction of Matrix Converter requires bidirectional switches that are able to block voltage and conduct current in both directions. However, till now a true single bidirectional switch is still not available [55]. Realization of bidirectional switches

are therefore based on a combination of discrete devices as shown in Figure 2-6. Different bidirectional switch arrangements have been proposed in the literature [15, 56].

## 2.2.3.1 Diode bridge arrangement

It is possible to build a bidirectional switch using one switching device such as an IGBT, MCT or IGCT, as shown in Figure 2-6 (A). The main advantages of this configuration are that only one gate drive circuit is required to switch the device on and off. However, because there are three devices conducting at the same time conduction losses will be large.

Figure 2-6 Bidirectional switches configuration

## 2.2.3.2 Common emitter configuration

The common emitter configuration is shown in Figure 2-6 (B). This arrangement consists of two diodes and two IGBT's connected in anti-parallel configuration. One diode and one IGBT are conducting at any time. These diodes are included to provide reverse blocking capabilities. The advantages of this configuration are lower conduction losses and independent control of positive and negative currents.

## 2.2.3.3 Common collector configuration

The common collector configuration is shown in Figure 2-6 (C). The conduction losses are similar to the common emitter configuration. However, this configuration is not feasible in very large practical systems since the inductance between commutation cells causes a problem [55]

## 2.2.3.4 Anti-parallel reverse blocking IGBTs

It is possible to build a bidirectional switch by simply connecting two reverse blocking devices in anti-parallel as shown in Figure 2-6 (D). In this configuration the efficiency may be improved and a compact converter size is possible to build. However, to date IGBTs showed poor reverse blocking capabilities and this prevented wide spread use of this configuration.

The common emitter configuration is the preferred solution as it is possible to control the direction of the current and conduction losses are lower since only two devices carry the current at any one time. One disadvantage of this configuration is that each bidirectional switch requires an isolated power supply for the gate drive unit [55].

### 2.3 Matrix Converter Current Commutation

Current transfer from one phase into another is difficult to achieve in Matrix Converters due to the fact that there is no a natural freewheeling path for the current. Therefore, controlling the current commutation between bidirectional switches is an important task. Two important rules need to be considered in the commutation:

- For each output phase, do not switch two switches at the same time. Because this will result in a high short circuit that will destroy the converter.

- Do not switch off two switches in the output phase at the same time, this will cause an over-voltage. Always allow a path for the inductive load current to flow.

There is several commutation techniques proposed in the literature such as simple and advanced commutation methods [55, 57].

## 2.3.1 Simple Commutation Methods

Simple commutation methods such as overlap, dead time and semi soft commutation are discussed below. In the overlap current commutation method the incoming switch is turned on before the outgoing switch is turned off. This will result in a short circuit between the supply phases. Extra supply inductance must be used to limit the

current but, this method is rarely used [16]. In the dead time current commutation method the outgoing switch is turned off before the incoming switch is turned on. This method will introduce a dead time in which there is no a path for the inductive load current. Therefore a snubber circuit is required to provide a path for the current. This method is poor due to the wasted energy in the snubber circuit.

## 2.3.2 Soft switching techniques

Soft switching technique such as resonant switch circuits [58, 59] and auxiliary resonant circuits [60], have been introduced in order to reduce switching losses and improve efficiency in power converters. However, in Matrix Converters resonant techniques have extra benefit of solving commutation problem. All these circuits increase the number of components being used in Matrix Converter and this also leads to additional conduction losses.

#### 2.3.3 Advanced commutation methods

For a reliable safe commutation a specific sequence must be adopted without short circuiting the input voltages or breaking the inductive load current. The first current commutation method that does not break the previous rules was proposed in [15] and named semi-soft commutation method or four-step commutation method. These advanced commutation methods are based on the measurement of the load current direction or on the input voltage magnitude or both [57]. In this project current commutation based on the output current direction was adopted.

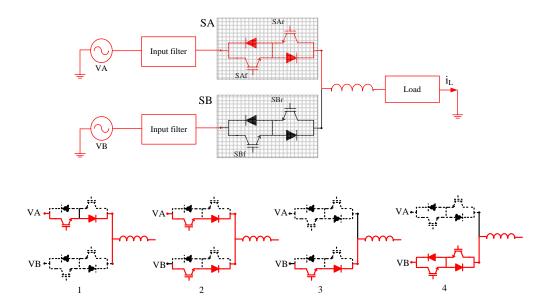

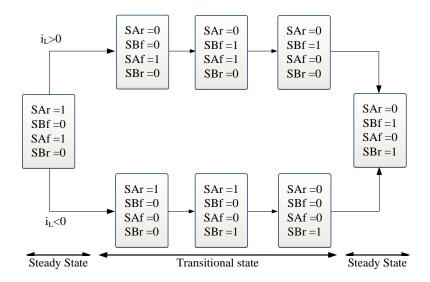

## 2.3.4 Output current direction based commutation method.

This commutation method is based on the load current direction. The load current direction is assumed to be in the direction shown in Figure 2-7, switch SA is assumed to be switched on.

Figure 2-7 Current direction based commutation.

If commutation from switch  $S_A$  to switch  $S_B$  is required then:

- 1. The current direction signal used to determine which device in the active switch is not conducting,  $S_{Ar}(S_{Ar} \rightarrow OFF)$ .

- 2. The device that is going to conduct in the incoming switch  $S_B$  is  $S_{Bf}$ , (  $S_{Bf} \rightarrow ON$  ). Load current transfers to the incoming switch  $S_B$  either at this point or when the  $S_A$  is switched off completely, depending on the polarity of the input voltages.

- 3. The device of  $S_{Br}$  in the incoming switch  $S_B$  is switched ON to allow the current to reverse. This process is shown in Figure 2-7 and Figure 2-8.

Figure 2-8 Four step current commutation.

Figure 2-9 shows the state diagram of the current commutation according to the load current direction.

Figure 2-9 Four step current commutation

# 2.4 Matrix Converter modulation strategies

There are a number of possible modulation techniques that can be used for Matrix Converter control. The optimal modulation strategy should minimise the input current and output voltage harmonic distortion and device power losses [61].

The most relevant control and modulation methods developed for the MCs are the Venturini method, the scalar method developed by Roy and the space-vector modulation (SVM) [9, 11, 12]. In the Venturini method the output voltage is obtained by the product of the input voltage and the transfer matrix. While in the Roy scalar modulation the instantaneous voltage ratio of specific input phase voltages is used to generate the active and zero states of the converter's switches. Comparisons between the SVM and the Venturini modulation methods show that switching losses are lower for the SVM method; however the Venturini modulation method shows better performance in terms of input current and output voltage harmonics. In this work the Venturini method is preferred because it deals with scalar quantities rather than vectors, and this is important when controlling unbalanced or non-linear loads [62, 63].

# 2.4.1 Space Vector Modulation for 3x3 Matrix Converter

Space Vector Modulation had previously been used for inverter control. In 1989 Huber and Borojevic proposed the use of Space Vector Modulation methods for Matrix Converters. In 2002 Casadei at al [13] propose a full Space Vector Modulation strategy that controlled both the output voltage and input power factor. Space Vector Modulation for Matrix Converters is based on the space vector representation of the input currents and output voltages at any time. These vectors are a result of the set of switching states that the Matrix Converter produced. For example, to create the switching state labelled "+1" in Table 2-1, output phase "a" has to be connected to input phase "A", and output phases "b, c, and n" have to be connected to input "B". For the standard  $3 \times 3$  MC, there are 27 ( $3^3$ ) switching states [13]. However in a four-leg MC, due to the addition of the forth leg, the total number of switching states is 81 ( $3^4$ ) [48]. For a set of three phase line to neutral voltages can be represented by:

$$V_o(t) = \frac{2}{3} (V_{oa} + aV_{ob} + a^2 V_{oc})$$

2-4

$$i_i(t) = \frac{2}{3} (i_{1i} + ai_{2i} + a^2 i_{3i})$$

2-5

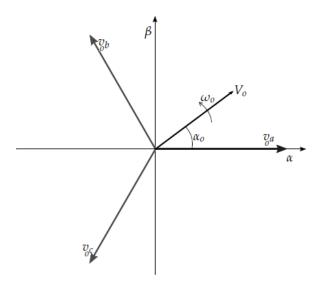

Where  $a=e^{j\frac{2\pi}{3}}$ ,  $V_{oa}$ ,  $V_{ob}$ ,  $V_{oc}$  are the output phase voltages,  $i_{1i}$ ,  $i_{2i}$ ,  $i_{3i}$  are the input currents. Using an Argand diagram the three vectors can be plotted as shown in Figure 2-10. This diagram shows a set of three vectors spaced by  $120^{\circ}$  with  $V_{o}(t)$  on the same diagram produce a vector of constant length and angle  $\alpha_{o}$  rotating at frequency of  $\omega_{o}$ . The output voltage  $V_{o}(t)$ , which is expressed in equation 2-4, can be generated by switching between the adjacent space vectors and producing a time averaged value over a switching period that is equal to the required output space vector.

Figure 2-10 SVM Vectors for a Balanced 3-Phase

# 2.4.1.1 Matrix Converter switching states

For Matrix Converters not all of the switching states have to be used to implement SVM, only the switching states that produce a vector with a constant direction within the output space are normally used and these are called "stationary vectors" and are listed in Table 2-1.

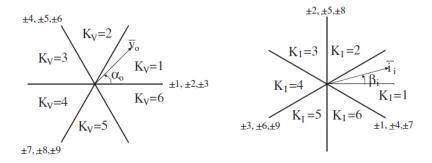

Figure 2-11 Output voltage and input current space vectors

According to Table 2-1  $\alpha_0$  is the angle of the output voltage vector and  $\beta_i$  is the angle of the input current vector. The operation of the Matrix Converter requires one and only one switch in each output phase must be conducting. This leads to twenty seven possible switching states. By applying equation 2-4 and 2-5 to determine the output

voltage and the input current vectors, the magnitude and the phase of these vectors for all possible combinations are given in Table 2-1

Table 2-1 Switching states of three phase Matrix Converter[57] .

| Switching     | Converter        | $v_o$                 | $\alpha_o$                                                                   | $i_i$                                                                                                                     | $\beta_i$                                                                           |

|---------------|------------------|-----------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Configuration | State            |                       |                                                                              |                                                                                                                           |                                                                                     |

| +1            | $S_{122}$        | $\frac{2}{3}v_{12i}$  | 0                                                                            | $\frac{2}{\sqrt{2}}i_{1o}$                                                                                                | $-\frac{\pi}{6}$                                                                    |

| -1            | $S_{211}$        | $-\frac{2}{3}v_{12i}$ | 0                                                                            | $-\frac{\frac{2}{\sqrt{3}}i_{1o}}{-\frac{2}{\sqrt{3}}i_{1o}}$                                                             | $-\frac{\pi}{6}$                                                                    |

| +2            | $S_{233}$        | $\frac{2}{3}v_{23i}$  | 0                                                                            | $\frac{\sqrt{3}}{\sqrt{3}}i_{1o}$                                                                                         |                                                                                     |

| -2            | $S_{322}$        | $-\frac{2}{3}v_{23i}$ | 0                                                                            | $-\frac{2}{\sqrt{3}}i_{1o}$                                                                                               | $\frac{\frac{\pi}{2}}{\frac{\pi}{2}}$ $\frac{7\pi}{6}$                              |

| +3            | $S_{311}$        | $\frac{2}{3}v_{31i}$  | 0                                                                            | $\frac{\frac{2}{\sqrt{3}}i_{1o}}{\frac{2}{\sqrt{3}}}$                                                                     | $\frac{7\pi}{6}$                                                                    |

| -3            | $S_{133}$        | $-\frac{2}{3}v_{31i}$ | 0                                                                            | $-\frac{\sqrt{3}}{\sqrt{3}}i_{1o}$                                                                                        | $ \frac{7\pi}{6} $ $ -\frac{\pi}{6} $ $ -\frac{\pi}{6} $                            |

| +4            | $S_{212}$        | $\frac{2}{3}v_{12i}$  | $\frac{2\pi}{3}$                                                             | - 1                                                                                                                       | $-\frac{\pi}{6}$                                                                    |

| -4            | $S_{121}$        | $-\frac{2}{3}v_{12i}$ | $\frac{2\pi}{3}$                                                             | $\frac{\frac{2}{\sqrt{3}}i_{2o}}{-\frac{2}{\sqrt{3}}i_{2o}}$ $\frac{-\frac{2}{\sqrt{3}}i_{2o}}{\frac{2}{\sqrt{5}}i_{2o}}$ | $-\frac{\pi}{6}$                                                                    |

| +5            | $S_{323}$        | $\frac{2}{3}v_{23i}$  | $\frac{2\pi}{3}$                                                             | $\frac{2}{\sqrt{3}}i_{2o}$                                                                                                | $\frac{\pi}{2}$                                                                     |

| -5            | $S_{232}$        | $-\frac{2}{3}v_{23i}$ | $\frac{2\pi}{3}$                                                             | $-\frac{\sqrt{3}}{\sqrt{3}}i_{2o}$                                                                                        | $\frac{\pi}{2}$ $\frac{\pi}{2}$ $\frac{7\pi}{6}$                                    |

| +6            | $S_{131}$        | $\frac{2}{3}v_{31i}$  | $\frac{2\pi}{3}$                                                             | $\frac{\sqrt{3}}{\sqrt{3}}i_{2o}$                                                                                         | $\frac{7\pi}{6}$                                                                    |

| -6            | $S_{313}$        | $-\frac{2}{3}v_{31i}$ | $ \begin{array}{r} 2\pi \\ 3 \\ 2\pi \\ 3 \\ 2\pi \\ 3 \\ 4\pi \end{array} $ | $-\frac{\sqrt{3}}{\sqrt{3}}i_{2o}$                                                                                        | $ \begin{array}{r} 6 \\ 7\pi \\ 6 \\ -\frac{\pi}{6} \\ -\frac{\pi}{6} \end{array} $ |

| +7            | $S_{221}$        | $\frac{2}{3}v_{12i}$  | $\frac{4\pi}{3}$                                                             | $\frac{2}{\sqrt{3}}i_{3o}$                                                                                                | $-\frac{\pi}{6}$                                                                    |

| -7            | $S_{112}$        | $-\frac{2}{3}v_{12i}$ | $\frac{4\pi}{3}$                                                             | $-\frac{2}{100}$                                                                                                          | $-\frac{\pi}{6}$                                                                    |

| +8            | $S_{332}$        | $\frac{2}{3}v_{23i}$  | $\frac{4\pi}{3}$                                                             | $\frac{2}{\sqrt{5}}i_{3o}$                                                                                                | $\frac{\pi}{2}$                                                                     |

| -8            | $S_{223}$        | $-\frac{2}{3}v_{23i}$ | $\frac{4\pi}{3}$                                                             | $\frac{\sqrt{3}}{\sqrt{3}}i_{3o}$ $\frac{2}{\sqrt{3}}i_{3o}$ $-\frac{2}{\sqrt{3}}i_{3o}$                                  | $\frac{\pi}{2}$                                                                     |

| +9            | $S_{113}$        | $\frac{2}{3}v_{31i}$  | $4\pi$                                                                       | 2 i30                                                                                                                     | $\frac{7\pi}{6}$                                                                    |

| -9            | $S_{331}$        | $-\frac{2}{3}v_{31i}$ | $\frac{3}{4\pi}$                                                             | $-\frac{\frac{2}{\sqrt{3}}i_{3o}}{-\frac{2}{\sqrt{3}}i_{3o}}$                                                             | $ \frac{\frac{\pi}{2}}{\frac{\pi}{2}} $ $ \frac{7\pi}{6} $ $ \frac{7\pi}{6} $       |

| $0_{1}$       | S <sub>111</sub> | 0                     |                                                                              | 0                                                                                                                         | 0                                                                                   |

| $0_{2}$       | $S_{222}$        | 0                     | ===                                                                          | 0                                                                                                                         | 0                                                                                   |

| $0_{3}$       | $S_{333}$        | 0                     | -                                                                            | 0                                                                                                                         | 0                                                                                   |

| FR1           | $S_{123}$        | variable              | variable                                                                     | variable                                                                                                                  | variable                                                                            |

| FR2           | $S_{231}$        | variable              | variable                                                                     | variable                                                                                                                  | variable                                                                            |

| FR3           | $S_{312}$        | variable              | variable                                                                     | variable                                                                                                                  | variable                                                                            |

| BR1           | $S_{132}$        | variable              | variable                                                                     | variable                                                                                                                  | variable                                                                            |

| BR2           | $S_{213}$        | variable              | variable                                                                     | variable                                                                                                                  | variable                                                                            |

| BR3           | $S_{321}$        | variable              | variable                                                                     | variable                                                                                                                  | variable                                                                            |

Group 1 vectors are split into three sub-groups as shown in table 2.1. These six states produce a vector in a defined direction. For the three sub-groups the directions are displaced by 120°.

# **2.4.1.2** Switching state selection

Using the eighteen fixed direction and three null vector combinations, it is possible to generate the required output voltage vector and the required input current

direction. Figure 2-11 shows the output line to neutral voltage vector and input current vector direction generated by the fixed eighteen direction configurations [13]. As shown in Figure 2-11, Kv is the sector that contains the output voltage vectors. Ki is the sector that contains the input current vector. Using table 2.2 and 2.3 it can be seen that for any combination of output voltage and input current sectors, four configurations can be identified that produce output voltage vectors and input current vectors laying adjacent to the desired vectors.

Table 2-2 Selection of switching configuration according to output voltage and input current sectors [13].

|    |   |     | Κ <sub>V</sub> |     |    |    |    |     |    |    |    |     |    |    |    |     |    |    |    |     |    |    |    |     |    |

|----|---|-----|----------------|-----|----|----|----|-----|----|----|----|-----|----|----|----|-----|----|----|----|-----|----|----|----|-----|----|

|    |   | 1 2 |                |     |    |    | 3  |     |    | 4  |    |     | 5  |    |    |     | 6  |    |    |     |    |    |    |     |    |

|    | 1 | +9  | -7             | -3  | +1 | -6 | +4 | +9  | -7 | +3 | -1 | -6  | +4 | -9 | +7 | +3  | -1 | +6 | -4 | -9  | +7 | -3 | +1 | +6  | -4 |

|    | 2 | -8  | +9             | +2  | -3 | +5 | -6 | -8  | +9 | +2 | -3 | +5  | -6 | +8 | -9 | -2  | +3 | -5 | +6 | +8  | -9 | -2 | +3 | -5  | +6 |

| Kı | 3 | +7  | -8             | -1  | +2 | -4 | +5 | +7  | -8 | -1 | +2 | -4  | +5 | -7 | +8 | +1  | -2 | +4 | -5 | -7  | +8 | +1 | -2 | +4  | -5 |

| KI | 4 | -9  | +7             | +3  | -1 | +6 | -4 | -9  | +7 | -3 | +1 | +6  | -4 | +9 | -7 | -3  | +1 | -6 | +4 | +9  | -7 | +3 | -1 | -6  | +4 |

|    | 5 | +8  | -9             | -2  | +3 | -5 | +6 | +8  | -9 | -2 | +3 | -5  | +6 | -8 | +9 | +2  | -3 | +5 | -6 | -8  | +9 | +2 | -3 | +5  | -6 |

|    | 6 | -7  | +8             | +1  | -2 | +4 | -5 | -7  | +8 | +1 | -2 | +4  | -5 | +7 | -8 | -1  | +2 | -4 | +5 | +7  | -8 | -1 | +2 | -4  | +5 |

|    |   | I   | II             | III | IV | I  | II | III | IV | Ι  | II | III | IV | Ι  | II | III | IV | I  | II | III | IV | Ι  | II | III | IV |

The required modulation duty cycles for the switching configurations I, II, III and IV are giving by equation 2-6 to 2-10

$$\delta^{I} = \frac{2}{\sqrt{3}} \cdot q \cdot \frac{\cos\left(\tilde{\alpha}_{o} - \frac{\pi}{3}\right) \cos(\tilde{\beta}_{i} - \frac{\pi}{3})}{\cos\phi_{i}}$$

2-6

$$\delta^{II} = \frac{2}{\sqrt{3}} \cdot q \cdot \frac{\cos\left(\tilde{\alpha}_o - \frac{\pi}{3}\right) \cos(\tilde{\beta}_i + \frac{\pi}{3})}{\cos\phi_i}$$

2-7

$$\delta^{III} = \frac{2}{\sqrt{3}} \cdot q \cdot \frac{\cos\left(\tilde{\alpha}_o + \frac{\pi}{3}\right) \cos(\tilde{\beta}_i - \frac{\pi}{3})}{\cos \phi_i}$$

2-8

$$\delta^{IV} = \frac{2}{\sqrt{3}} \cdot q \cdot \frac{\cos\left(\tilde{\alpha}_o + \frac{\pi}{3}\right) \cos(\tilde{\beta}_o + \frac{\pi}{3})}{\cos \phi_i}$$

2-9

Where  $\tilde{\alpha}_o$  and  $\tilde{\beta}_i$  are the angles of the output voltage and input current vectors measured from the bisecting line of the corresponding sectors.  $\emptyset_i$  is the input phase displacement angle.

For unity input power factor operation  $\delta^{I} + \delta^{II} + \delta^{III} + \delta^{IV} \leq 1$

$$\delta_0 = 1 - (\delta^I + \delta^{II} + \delta^{III} + \delta^{IV})$$

2-10

If double sided modulation is used then  $\delta_0$  is distributed in the modulation period by two equal parts [13, 51].

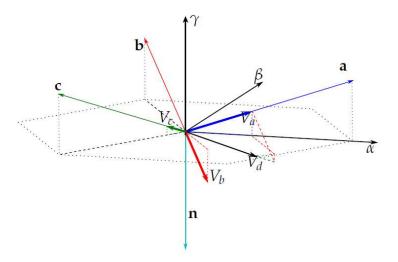

### 2.4.2 Space Vector Modulation for 3x4 Matrix Converter

Matrix Converter modulation is based on the space vector representation of the input and output voltages and currents at any one instant. This section will present a brief summery on the space vector modulation for the three phase four-leg matrix converter.

### 2.4.2.1 Input voltage and current plane

From the basic layout of the four-leg Matrix Converter system shown in Figure , there are three input voltages  $V_A$ ,  $V_B$  and  $V_C$ , these input voltage are defined by:

$$V_A + V_B + V_C = 0$$

2-11

Where each input phase voltage is defined by:

$$V_A = V_{im} \cos(\theta_i)$$

2-12

$$V_{A} = V_{im} \cos \left(\theta_{i} - 2\pi/3\right)$$

2-13

$$V_{A} = V_{im} cos (\theta_{i} - 4\pi/3)$$

2-14

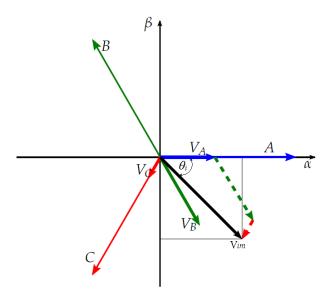

Where  $V_{im}$  is the maximum value of the phase input voltage and  $\theta_i$  is the phase angle. These input voltage quantity can be presented in  $\alpha$ ,  $\beta$  plane as shown below:

$$\begin{bmatrix} V_{\infty,in} \\ V_{\beta,in} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_A \\ V_C \\ V_C \end{bmatrix}$$

2-15

Figure 2-12 Input voltage space.

As shown in Figure 2-12, the input currents  $I_A$ ,  $I_B$ ,  $I_C$ , can be transformed into  $\alpha$ ,  $\beta$  space using the equation.

$$\begin{bmatrix} I_{\alpha} \\ I_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} I_{A} \\ I_{B} \\ I_{C} \end{bmatrix}$$

2-16

The Matrix Converter can be designed to achieve a unity input displacement factor which means that the fundamental input voltage should be in phase with the fundamental input current. In this case the phase angle of the input voltage vector always matches that of the input current vector. Therefore, at any instant of time, the input currents must form balanced 3 phase set such that:

$$I_A + I_B + I_C = 0$$

2-17

# 2.4.2.2 Switching States for the Four-Leg Matrix Converter

The switching states are the states which obey the fundamental rules of the Matrix Converter which are that the input phases cannot be shorted together and no output leg can be open circuit. For the standard 3x3 Matrix Converter there are 27 (3³) possible switching states [4]. However, using the four-leg Matrix Converter the total number of the switching states increases to 81 (3⁴). All of these switching states are shown in Table 2-3 and Table 2-4. As shown in a 3x3 Matrix Converter [13], not all of the switching states are normally used for space vector modulation. So only th states that produce a vector with constant direction within the output space are to be used and these are called the stationary vectors. For the Matrix Converter systems there are 3 switching state categories:

**Rotating vectors states:** in this category all the three input phases are connected to the output. This means that two different line to line voltages are present between the output phases and in this case the resultant vectors change in magnitude and direction. This category is presented in Table 2-3.

**Stationary vectors states:** any two phases of the input voltages are connected to the output legs at any moment in time. This category is the one of interest as the output voltage generated are either zero or the line to line voltage between the two connected phases. This category is shown in Table 2-4

**Zero vector states:** in this category all the four output phases are connected to a single input phase. When the four output phases are connected to one single input phase the voltage between the output phases becomes zero. These vectors are important as they allow a zero state to be applied to the output without disconnecting the output legs from the input phases. This category can be seen at the top of Table 2-4.

Table 2-3 Rotating vector states for four-leg Matrix Converter.

|          | Output Leg Switching Leg a   Leg b   Leg c   Leg n |      |       |       |  | L-N Output Voltage |                  |                  | $I_{vector}$ | Input Current                                                     |                                                                   |                                                                   |  |

|----------|----------------------------------------------------|------|-------|-------|--|--------------------|------------------|------------------|--------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|--|

|          | Leg a                                              | Legb | Leg c | Leg n |  | Van                | $V_{bn}$         | $V_{cn}$         |              | $I_A$                                                             | $I_B$                                                             | $I_C$                                                             |  |

|          | Α                                                  | A    | В     | C     |  | $-V_{CA}$          | $-V_{CA}$        | $V_{BC}$         |              | $I_a+I_b$                                                         | $I_c$                                                             | $-\mathbf{I}_a$ $-\mathbf{I}_b$ $-\mathbf{I}_c$                   |  |

|          | Α                                                  | В    | A     | С     |  | $-V_{CA}$          | $V_{BC}$         | $-V_{CA}$        |              | $I_a+I_c$                                                         | $I_b$                                                             | $-\mathbf{I}_a$ - $\mathbf{I}_b$ - $\mathbf{I}_c$                 |  |