# Butt, David (1999) An investigation of harmonic correction techniques using active filtering. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/12981/1/301660.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# An Investigation of Harmonic Correction Techniques using Active Filtering

David Butt, MEng(Honours)

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, August '99.

### Acknowledgements

I would like to begin by thanking both of my supervisors, Dr M Sumner and Dr JC Clare, for their invaluable guidance and encouragement over the duration of this project. I would also wish to thank the members of the PEMC group who contributed advice and the technicians who were very helpful during the construction of the practical rig.

Gratitude must also be given to those people who, although they have not necessarily assisted me in my work and in certain instances have been downright distracting, have made the last four years very enjoyable: In particular, Gez, Chris H, Nikin, Chris S, Jane, Ben, Ash and the resident meercats in the lab ... who will remain nameless but know who they are.

I would especially like to thank my parents and my brother for their love and continual support.

"I can see the carrot at the end of the tunnel" - Stuart Pearce.

## Contents

| L | Intr | oduction: The problem of power system harmonics   | 2  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Problem overview                                  | 2  |

|   | 1.2  | The effects of system harmonics                   | 6  |

|   | 1.3  | Reduction of the effects of harmonics             | 8  |

|   |      | 1.3.1 1) Dealing with the problem at source       | 8  |

|   |      | 1.3.2 2) Dealing with the problem at system level | 10 |

|   | 1.4  | Regulations pertaining to power quality           | 15 |

|   |      | 1.4.1 BS IEC 61000-3-4:1998                       | 16 |

|   |      | 1.4.2 IEEE 519                                    | 18 |

|   | 1.5  | Aims and objectives of this work                  | 18 |

|   | 1.6  | Structure of this work                            | 20 |

|   | 1.7  | Terminology and definitions of power              | 22 |

|   | 1.8  | Summary                                           | 24 |

| 2 | 2 Alternatives to the standard diode bridge rectifier interface |        |             |                                                                        | 25 |

|---|-----------------------------------------------------------------|--------|-------------|------------------------------------------------------------------------|----|

|   | 2.1                                                             | Introd | uction      |                                                                        | 25 |

|   | 2.2                                                             | The st | andard di   | ode bridge rectifier                                                   | 26 |

|   | 2.3                                                             | The st | andard di   | ode bridge rectifier with added line inductance                        | 30 |

|   |                                                                 | 2.3.1  | Summary     | y                                                                      | 32 |

|   | 2.4                                                             | The 'T | Texas' circ | uit                                                                    | 34 |

|   |                                                                 | 2.4.1  | Circuit o   | peration                                                               | 35 |

|   |                                                                 |        | 2.4.1.1     | Circuit operation with a highly inductive load                         | 35 |

|   |                                                                 |        | 2.4.1.2     | Circuit operation with capacitive smoothing of the d.c. output voltage | 37 |

|   |                                                                 | 2.4.2  | Choice o    | f component values                                                     | 37 |

|   |                                                                 | 2.4.3  | Simulati    | on                                                                     | 38 |

|   |                                                                 | 2.4.4  | The exp     | erimental rig                                                          | 40 |

|   |                                                                 |        | 2.4.4.1     | Performance of the circuit with a resistive load                       | 40 |

|   |                                                                 |        | 2.4.4.2     | Performance at reduced load powers                                     | 49 |

|   |                                                                 |        | 2.4.4.3     | Performance with active load                                           | 51 |

|   |                                                                 | 2.4.5  | Summar      | у                                                                      | 52 |

|   | 2.5                                                             | The 'l | Minnesota   | n' circuit                                                             | 54 |

|   |                                                                 | 2.5.1  | Circuit     | operation                                                              | 55 |

|   |     | 2.5.2 Summary                                                   | 58 |

|---|-----|-----------------------------------------------------------------|----|

|   | 2.6 | The single-switch rectifier                                     | 60 |

|   |     | 2.6.1 Circuit operation                                         | 60 |

|   |     | 2.6.2 Summary                                                   | 61 |

|   | 2.7 | The 'three-switch' rectifier                                    | 63 |

|   |     | 2.7.1 Circuit operation                                         | 63 |

|   |     | 2.7.2 Summary                                                   | 67 |

|   | 2.8 | The six-switch rectifier                                        | 68 |

|   |     | 2.8.1 Circuit operation                                         | 68 |

|   |     | 2.8.2 Summary                                                   | 70 |

|   | 2.9 | Summary                                                         | 71 |

| 3 | An  | introduction to the shunt active filter                         | 76 |

|   | 3.1 | Review of aims and objectives                                   | 76 |

|   | 3.2 | Introduction                                                    | 77 |

|   | 3.3 | Principle of operation                                          | 77 |

|   | 3.4 | Circuit structure of the shunt active filter                    | 78 |

|   | 3.5 | Derivation of the reference current for the shunt active filter | 79 |

|   | 3.6 | Current control of the shunt active filter                      | 80 |

|   |     | 3.6.1  | Linear current controllers                                            | 81  |

|---|-----|--------|-----------------------------------------------------------------------|-----|

|   |     |        | 3.6.1.1 Stationary PI controller                                      | 81  |

|   |     |        | 3.6.1.2 Synchronous PI controller                                     | 82  |

|   |     |        | 3.6.1.3 Deadbeat controller                                           | 84  |

|   |     | 3.6.2  | Nonlinear current controllers                                         | 85  |

|   |     |        | 3.6.2.1 Hysteresis controller                                         | 86  |

|   |     | 3.6.3  | Summary of the various current controllers of the shunt active filter | 88  |

| 4 | The | syncl  | hronous PI controller                                                 | 89  |

|   | 4.1 | Introd | duction                                                               | 89  |

|   | 4.2 | The c  | operation and structure of the synchronous PI controller              | 90  |

|   |     | 4.2.1  | Following the harmonic reference currents - two possible approaches   | 92  |

|   |     | 4.2.2  | Design of the active filter components                                | 94  |

|   |     | 4.2.3  | Design of the current control loop                                    | 97  |

|   |     | 4.2.4  | Design of the dc-link voltage control loop                            | 99  |

|   | 4.3 | Simu   | lation with synchronous PI control                                    | 101 |

|   |     | 4.3.1  | Introduction to the Saber simulation                                  | 101 |

|   |     | 4.3.2  | Synchronous PI control working under realistic conditions             | 102 |

|   |     | 4.3.3  | Synchronous PI control working with ideal conditions                                                                            | 105    |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------------|--------|

|   |     | 4.3.4  | Synchronous PI control working with non-negligible deadtime                                                                     | 107    |

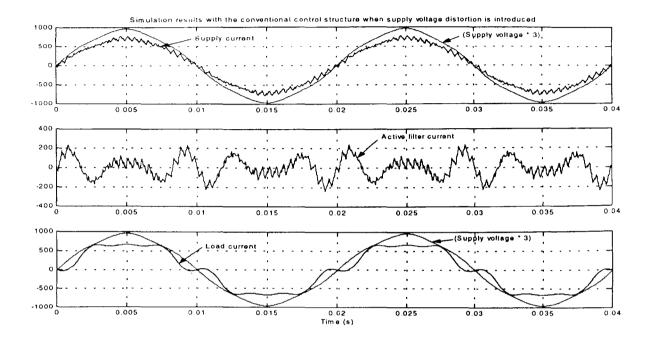

|   |     | 4.3.5  | Synchronous PI control working with supply distortion                                                                           | 109    |

|   | 4.4 | Conclu | usion                                                                                                                           | 111    |

| 5 | An  | improv | ved synchronous PI control structure                                                                                            | 113    |

|   | 5.1 | Introd | uction                                                                                                                          | 113    |

|   | 5.2 | Analys | sis of the synchronous PI control structure                                                                                     | 114    |

|   | 5.3 | Impro  | ving the synchronous PI control structure                                                                                       | 119    |

|   |     | 5.3.1  | Feedforward terms to compensate the effects of deadtime                                                                         | 119    |

|   |     |        | 5.3.1.1 Ideal PWM generation                                                                                                    | 119    |

|   |     |        | 5.3.1.2 Practical PWM generation                                                                                                | 119    |

|   |     | 5.3.2  | Feedforward terms to compensate for the effects of supply distortion                                                            | 127    |

|   | 5.4 |        | ation results demonstrating the performance of the improved syn-<br>ous PI control structure operating as a sinusoidal frontend | 129    |

|   |     | 5.4.1  | Simulation parameters                                                                                                           | 129    |

|   |     | 5.4.2  | Improved synchronous PI control working with non-negligible deadtime                                                            | 129    |

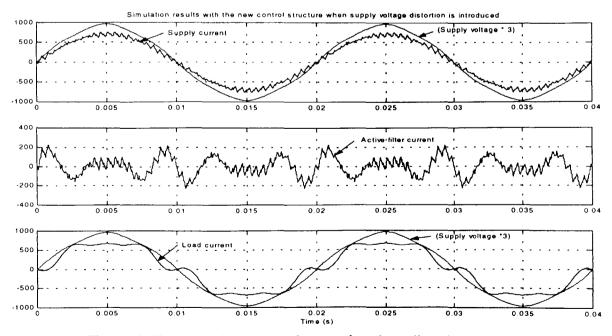

|   |     | 5.4.3  | Improved synchronous PI control working with supply distortion                                                                  | on 132 |

|   |     | 5.4.4                                                                             | Synchronous PI control working under realistic conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 134   |  |  |  |  |

|---|-----|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

|   | 5.5 | Simulation results demonstrating the performance of the improved syn-             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |  |  |

|   |     |                                                                                   | ous PI control structure with sinusoidal frontend operating as a active filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 136   |  |  |  |  |

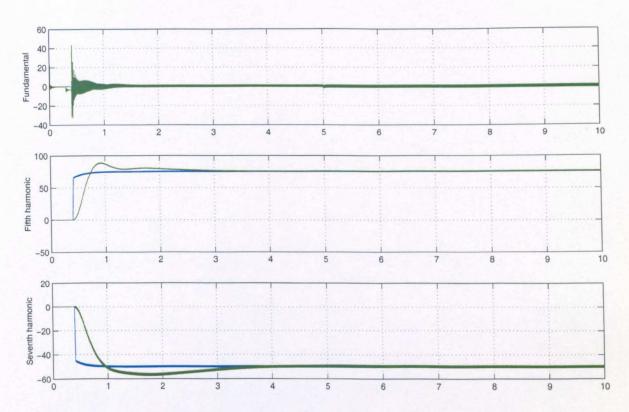

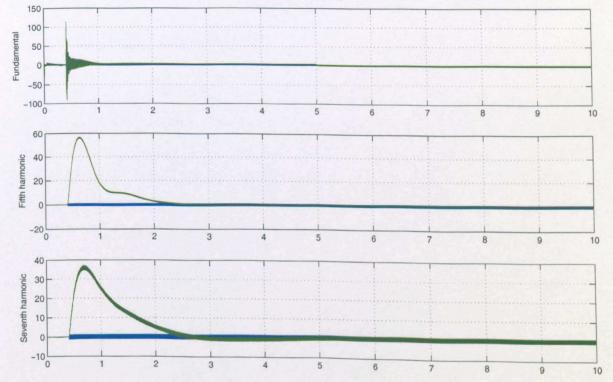

|   |     | 5.5.1                                                                             | Generation of harmonic currents in the dq-frame of reference .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 136   |  |  |  |  |

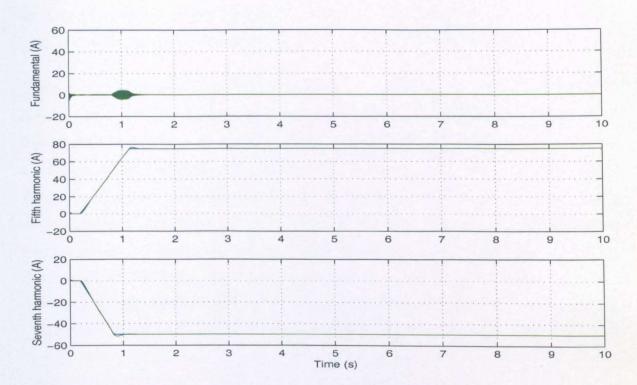

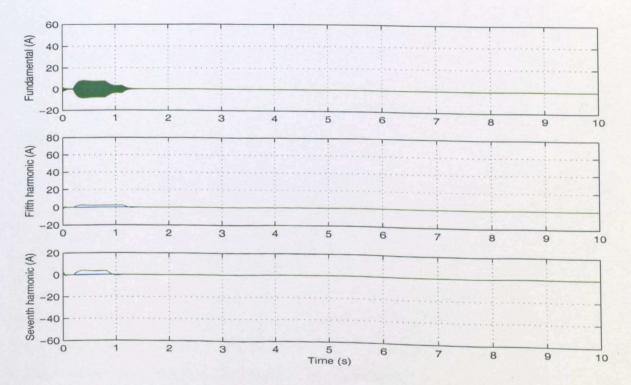

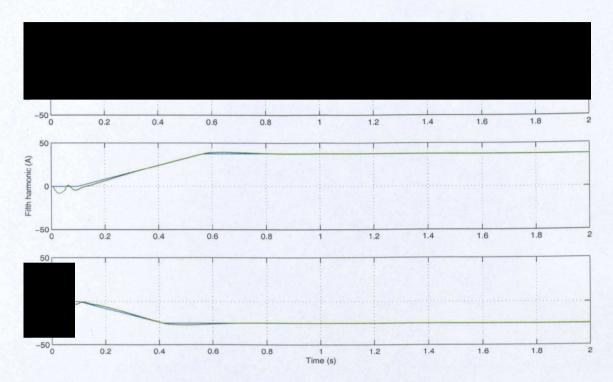

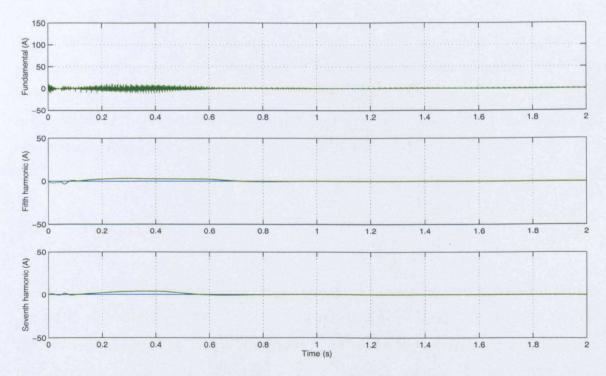

|   |     | 5.5.2                                                                             | Test1: Generation of fifth harmonic current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 137   |  |  |  |  |

|   |     | 5.5.3                                                                             | Test2: Generation of seventh harmonic current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 138   |  |  |  |  |

|   |     | 5.5.4                                                                             | Test3: Generation of fifth and seventh harmonic current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 138   |  |  |  |  |

|   |     | 5.5.5                                                                             | Discussion of results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 139   |  |  |  |  |

|   | 5.6 | Concl                                                                             | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 142   |  |  |  |  |

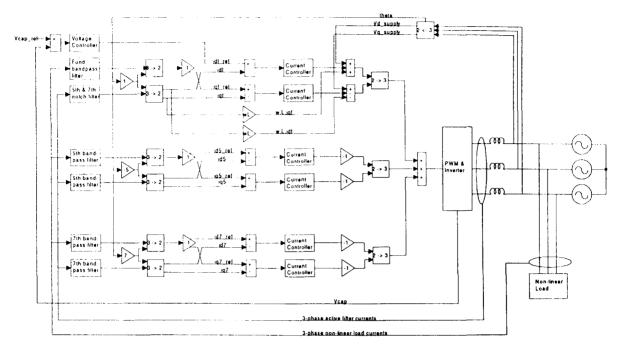

| 6 | An  | advano                                                                            | ced synchronous PI control structure using bandpass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | :s    |  |  |  |  |

|   | (Me | ethod                                                                             | 1) for harmonic signal extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 144   |  |  |  |  |

|   | 6.1 | Introd                                                                            | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 144   |  |  |  |  |

|   | 6.2 | Analy                                                                             | rsis of the advanced synchronous PI control structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 145   |  |  |  |  |

|   | 6.3 | Method 1: Application of a bandpass filter to extract the harmonics from a signal |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |  |  |

|   |     | 6.3.1                                                                             | Introduction to harmonic signal extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 150   |  |  |  |  |

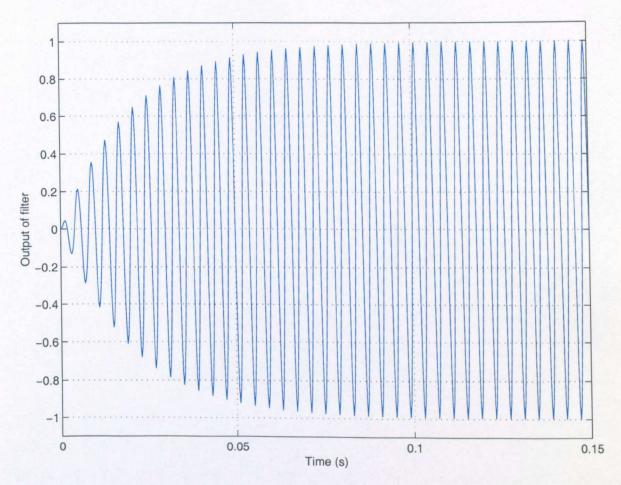

|   |     | 6.3.2                                                                             | Implementation of the hand of the land of | s 150 |  |  |  |  |

|   |     | 0.0.2                                                                             | Implementation of the bandpass filter and design consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 100 |  |  |  |  |

|   |     | 6.3.3                                                                             | Configuring the bandpass filter to be self-tuning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |  |  |  |  |

|   |     | 6.4.1                                 | Introduction to the simulations                                                              | 157                                                                   |

|---|-----|---------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

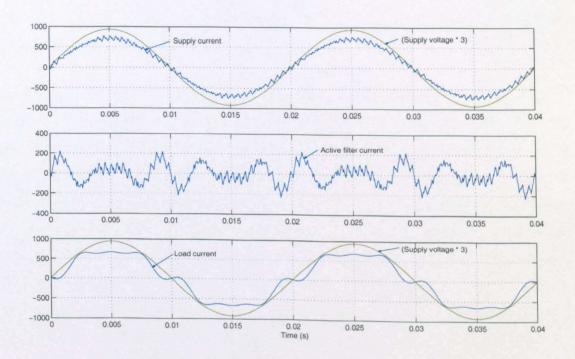

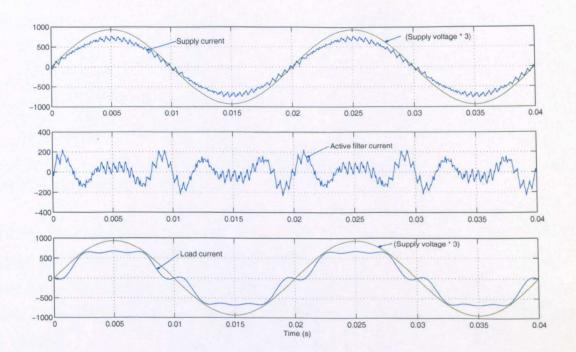

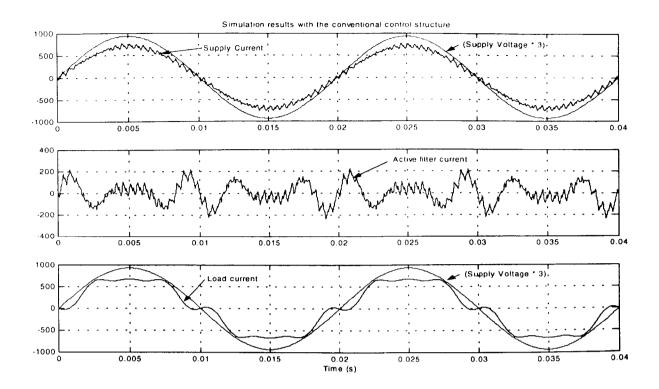

|   |     | 6.4.2                                 | Advanced synchronous PI control working with ideal conditions                                | 158                                                                   |

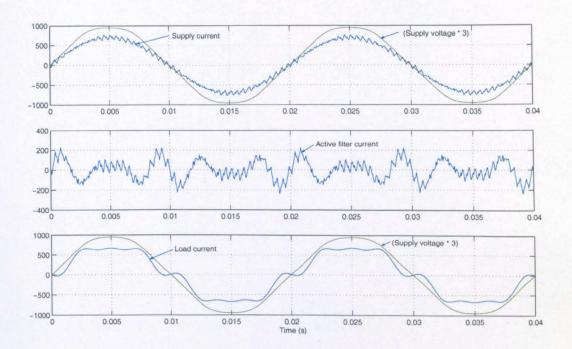

|   |     | 6.4.3                                 | Advanced synchronous PI control working with non-negligible deadtime                         | 161                                                                   |

|   |     | 6.4.4                                 | Advanced synchronous PI control working with supply distortion                               | 162                                                                   |

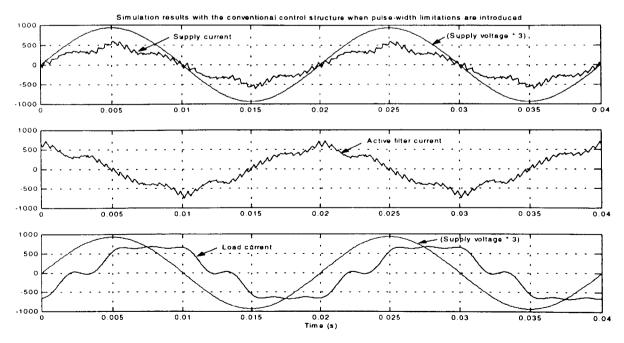

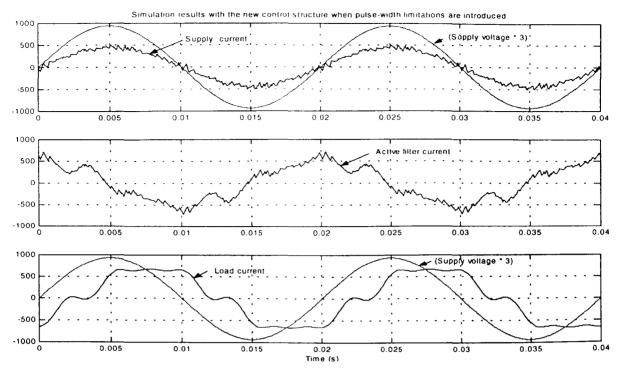

|   |     | 6.4.5                                 | Advanced synchronous PI control working with pulse-width limiting                            | 164                                                                   |

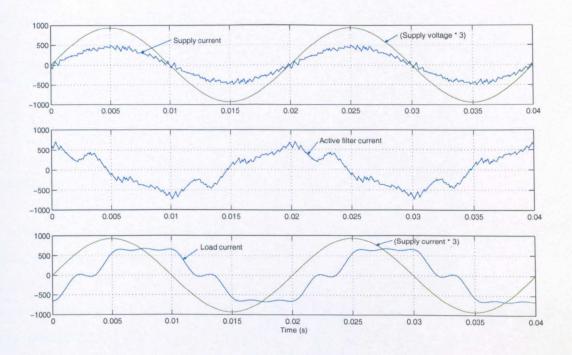

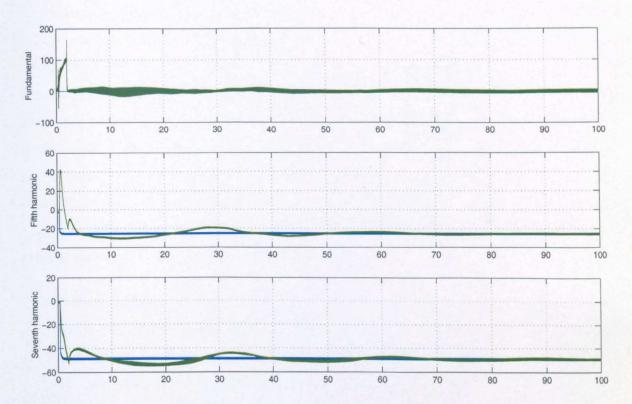

|   |     | 6.4.6                                 | Advanced synchronous PI control working under realistic conditions                           | 167                                                                   |

|   | 6.5 | Conclu                                | ısion                                                                                        | 171                                                                   |

|   |     |                                       |                                                                                              |                                                                       |

| 7 |     |                                       | ced synchronous PI control structure using low pass filter 2) for harmonic signal extraction | s<br>172                                                              |

| 7 |     | ethod 2                               |                                                                                              | 172                                                                   |

| 7 | (Me | ethod 2                               | 2) for harmonic signal extraction                                                            | 172<br>172                                                            |

| 7 | (Me | Introd  Metho                         | 2) for harmonic signal extraction uction                                                     | <ul><li>172</li><li>172</li><li>173</li></ul>                         |

| 7 | (Me | Introd  Metho                         | 2) for harmonic signal extraction uction                                                     | <ul><li>172</li><li>172</li><li>173</li><li>173</li></ul>             |

| 7 | (Me | Introd  Method  7.2.1                 | 2) for harmonic signal extraction  uction                                                    | <ul><li>172</li><li>173</li><li>173</li><li>175</li></ul>             |

| 7 | (Me | Introd Method 7.2.1 7.2.2 7.2.3       | 2) for harmonic signal extraction  uction                                                    | <ul><li>172</li><li>173</li><li>173</li><li>175</li><li>176</li></ul> |

| 7 | (Me | Introd Method 7.2.1 7.2.2 7.2.3 7.2.4 | 2) for harmonic signal extraction  uction                                                    | 172<br>173<br>173<br>175<br>176<br>177                                |

|   | 7.5                 | Perform  | nance und  | er 'realistic' conditions                        | 182 |

|---|---------------------|----------|------------|--------------------------------------------------|-----|

|   | 7.6                 | Perform  | nance whe  | en a step change in load is applied              | 186 |

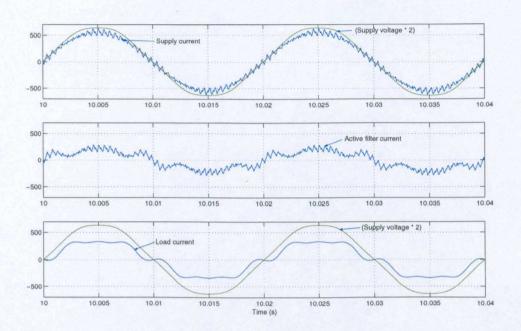

|   | 7.7                 | Perform  | nance as a | a sinusoidal front end and a shunt active filter | 191 |

|   | 7.8                 | Summa    | ary        |                                                  | 194 |

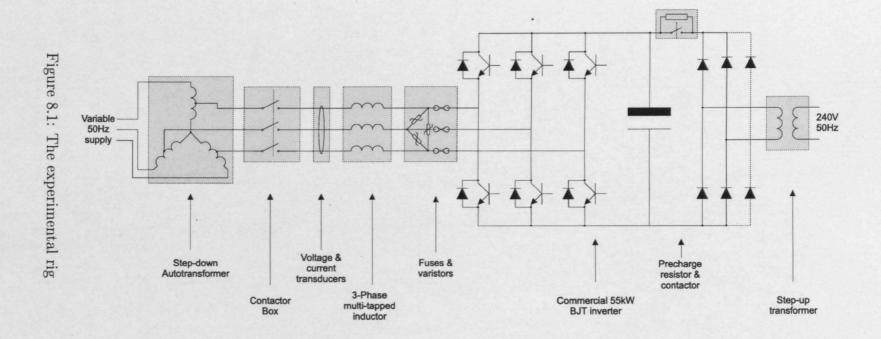

| 8 | $\operatorname{Th}$ | e experi | imental ı  | r <b>i</b> g                                     | 196 |

|   | 8.1                 | Introdu  | uction     |                                                  | 196 |

|   | 8.2                 | The ha   | ardware o  | f the experimental rig                           | 196 |

|   |                     | 8.2.1    | Overviev   | ,                                                | 196 |

|   |                     | 8.2.2    | Design c   | onsiderations                                    | 197 |

|   |                     |          | 8.2.2.1    | Choice of dc-link operating voltage              | 197 |

|   |                     |          | 8.2.2.2    | Choice of supply voltage                         | 197 |

|   |                     |          | 8.2.2.3    | Choice of value of inductors                     | 199 |

|   |                     |          | 8.2.2.4    | Choice of d.clink capacitance                    | 199 |

|   |                     |          | 8.2.2.5    | Choice of switching frequency                    | 199 |

|   |                     |          | 8.2.2.6    | Choice of lockout time                           | 200 |

|   |                     |          | 8.2.2.7    | Actual values on the experimental rig            | 200 |

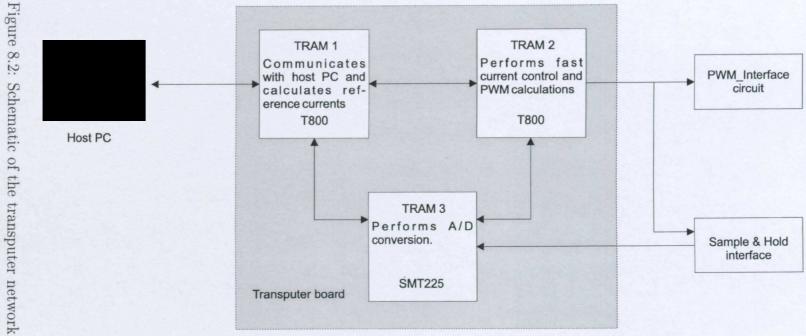

|   | 8.3                 | Trans    | sputer con | trol of the three-phase inverter                 | 202 |

|   |                     | 8.3.1    | Realisa    | tion of control software in OCCAM                | 202 |

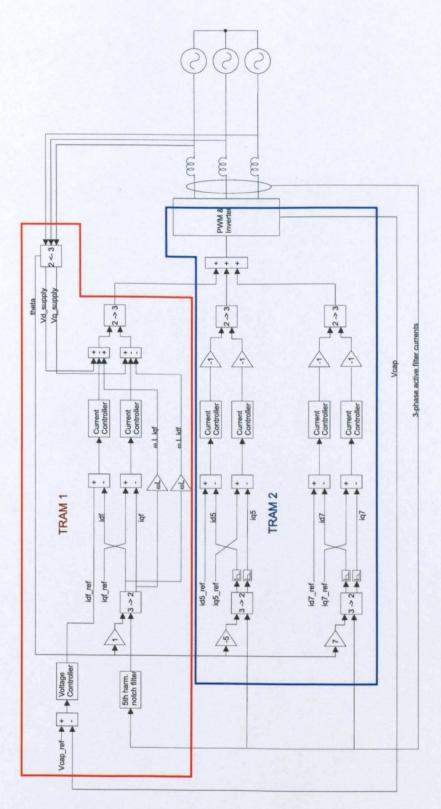

|   |      | 8.3.2    | Tasks performed by the individual TRAMs                                   | 204   |

|---|------|----------|---------------------------------------------------------------------------|-------|

|   | 8.4  | Protec   | tion features incorporated into the experimental rig                      | 208   |

|   | 8.5  | Summ     | ary                                                                       | 209   |

| 9 | Res  | ults fro | om the experimental rig                                                   | 210   |

|   | 9.1  | Introd   | uction                                                                    | 210   |

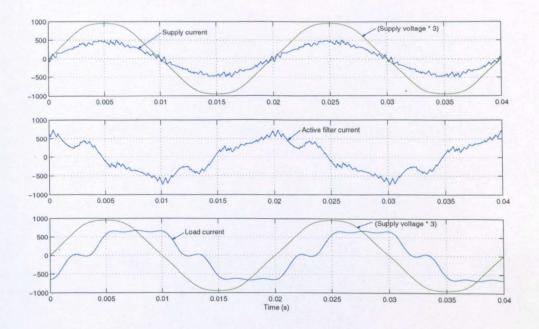

|   | 9.2  |          | xperimental rig operating with the normal synchronous current             | 212   |

|   |      | 9.2.1    | Present 'state of the art' commercial approach                            | 212   |

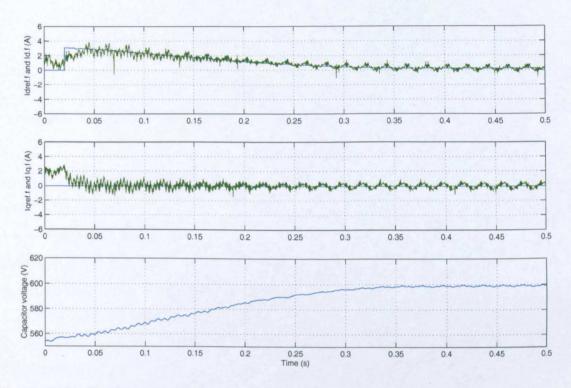

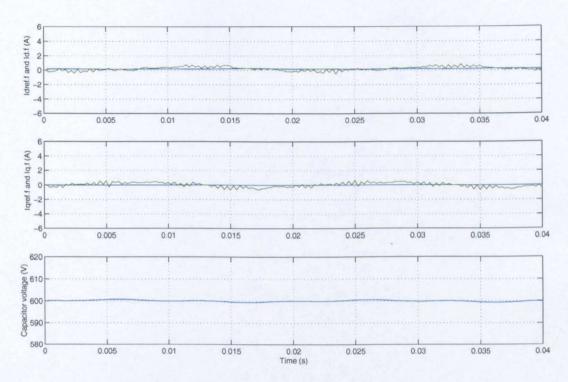

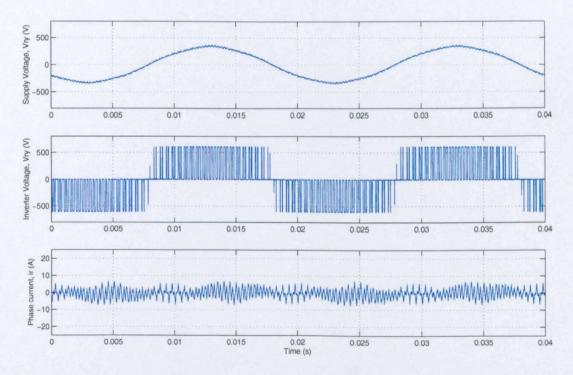

|   |      | 9.2.2    | Operation as a sinusoidal front end                                       | 212   |

|   |      | 9.2.3    | Operation as a harmonic current source                                    | 219   |

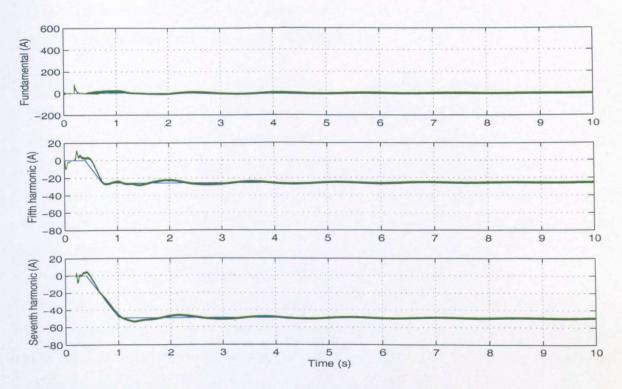

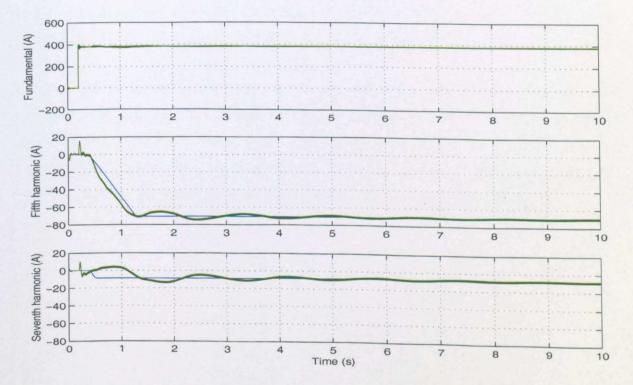

|   | 9.3  | The ex   | xperimental rig operating with the advanced synchronous contro            | 1 225 |

|   |      | 9.3.1    | Software realisation of the control structure                             | 225   |

|   |      | 9.3.2    | Operation as a sinusoidal front end with only fundamental contr           | ol227 |

|   |      | 9.3.3    | Operation as a sinusoidal front end with fundamental and harmonic control |       |

|   |      | 9.3.4    | Operation as a harmonic current source                                    | 233   |

|   | 9.4  | Sumn     | nary                                                                      | 236   |

| 1 | 0 Co | nclusio  | ons and further work                                                      | 239   |

|   | 10.1 | l Overv  | view                                                                      | . 239 |

|   | 10.2 Harmonic distortion                                  | 240 |

|---|-----------------------------------------------------------|-----|

|   | 10.3 Harmonic correction at source                        | 240 |

|   | 10.4 Harmonic compensation at a system level              | 241 |

|   | 10.5 The Advanced Synchronous PI Controller               | 243 |

|   | 10.6 Experimental implementation                          | 244 |

|   | 10.7 Future application                                   | 245 |

|   | 10.8 Further work                                         | 245 |

| A | Transformation to the dq frame of reference               | 259 |

|   | A.1 The basic equations                                   | 259 |

|   | A.2 Conversion of fundamental and fifth harmonic currents | 260 |

| В | 'Texas circuit': PSPICE listing                           | 263 |

| C | 'Minnesota circuit': PSPICE listing                       | 266 |

| D | Typical code for a Saber control block                    | 271 |

| E | Commercial measuring equipment used                       | 279 |

| F | Publications by the author                                | 280 |

# List of Figures

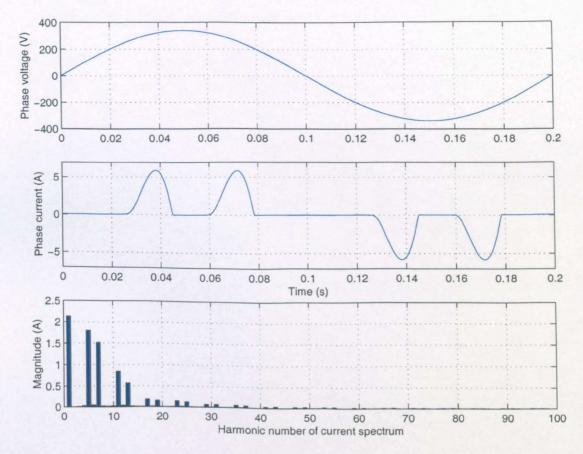

| 1.1 | Typical voltage and current waveforms for a capacitively smoothed rectifier (PSPICE simulation)                                                                                                                                                                                        | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

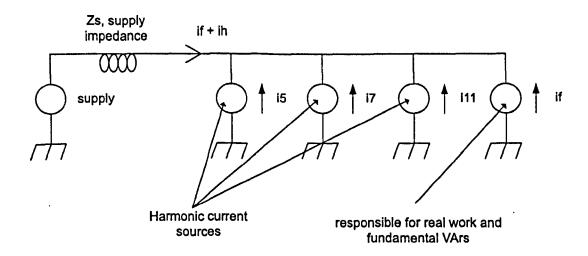

| 1.2 | Equivalent circuit of a power system with a non-linear load: The non-linear load can be seen as a number of harmonic current sources in parallel with a linear load                                                                                                                    | 5  |

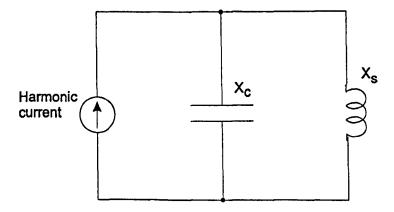

| 1.3 | Equivalent circuit of a VAr compensating capacitor in parallel with system impedance as seen by the harmonic current source [3]                                                                                                                                                        | 7  |

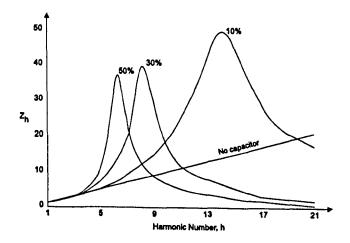

| 1.4 | System frequency response as capacitor size is varied in relation to the transformer [3]                                                                                                                                                                                               | 7  |

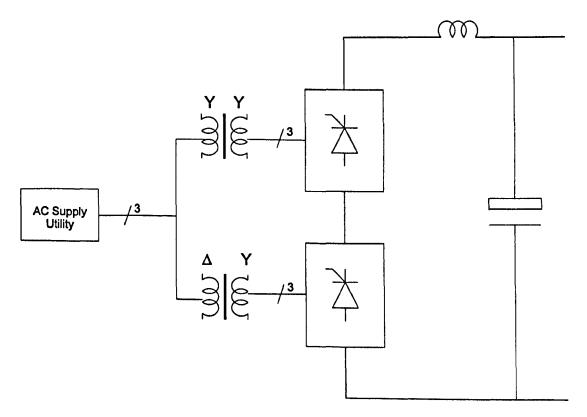

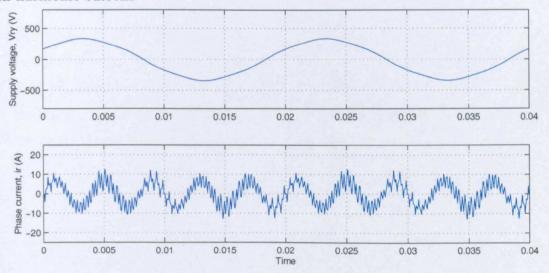

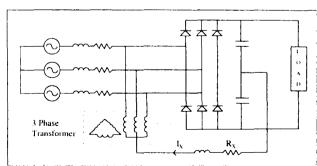

| 1.5 | Example of a multipulse technique to improve line current                                                                                                                                                                                                                              | 9  |

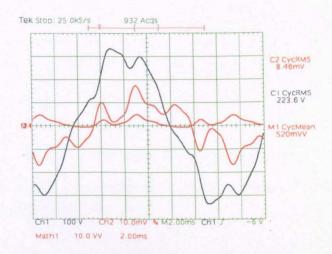

| 1.6 | Phase voltage, line current and instantaneous power in a phase of the transformer's secondary side, Active Power = $52 \text{ kW}$ , Apparent Power = $189.16 \text{ kVA}$ , PF = $0.275 (100 \text{ V/div}. (223.6 \text{ V}_{RMS}))$ and $1000 \text{A/div}. (846 \text{ A}_{RMS}))$ | 11 |

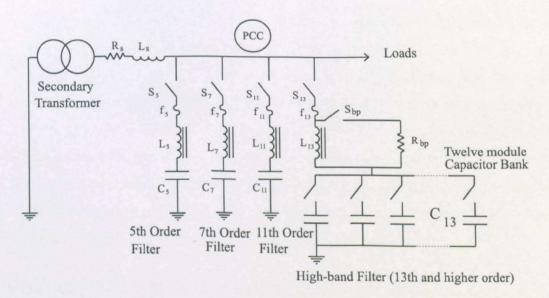

| 1.7 | Single-phase diagram of the plant with passive filters                                                                                                                                                                                                                                 | 11 |

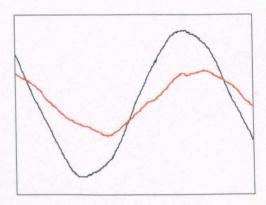

| 1.8 | Phase voltage and line current on the secondary side of the transformer (100V/div, 1000A/div, 2mS/div)                                                                                                                                                                                 | 12 |

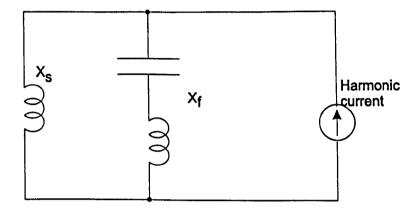

| 1.9  | Equivalent circuit for the combination of supply impedance, $X_s$ , tuned passive filter impedance, $X_f$ , and harmonic current source [3]                                                          | 13 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

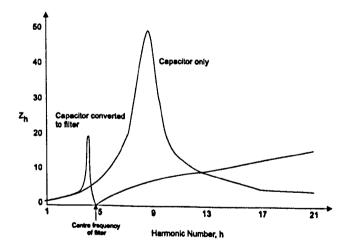

| 1.10 | System frequency response to equivalent circuit of supply impedance with a tuned bandpass filter [3]                                                                                                 | 13 |

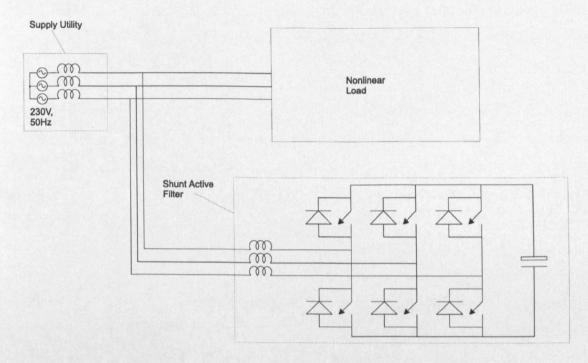

| 1.11 | Configuration of the shunt active filter                                                                                                                                                             | 14 |

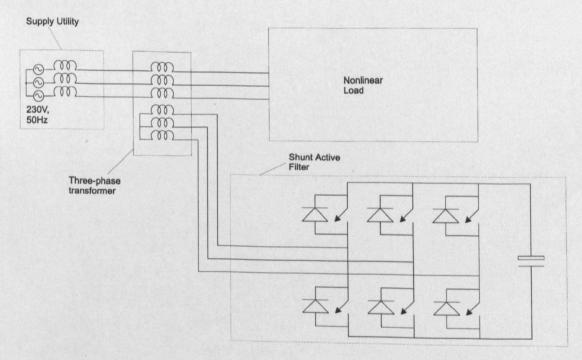

| 1.12 | Configuration of the series active filter                                                                                                                                                            | 14 |

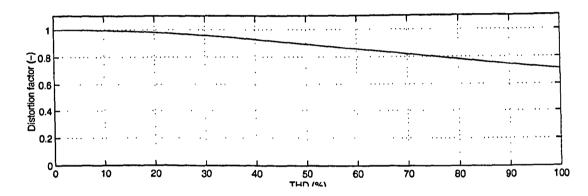

| 1.13 | Relationship between distortion factor and THD                                                                                                                                                       | 24 |

| 2.1  | The capacitively smoothed diode bridge rectifier                                                                                                                                                     | 27 |

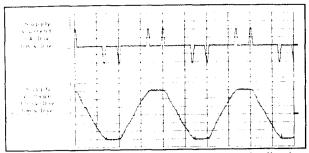

| 2.2  | Typical voltage and current waveforms for a diode bridge rectifier                                                                                                                                   | 28 |

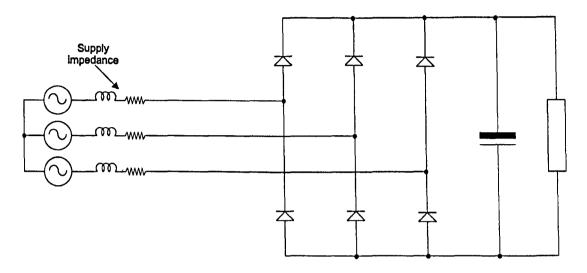

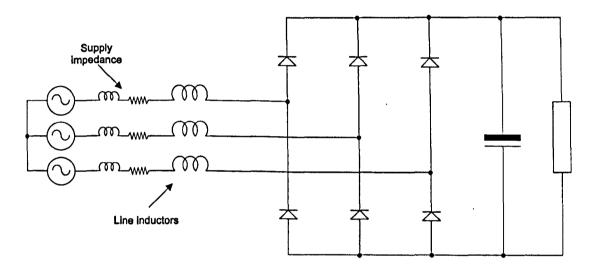

| 2.3  | Diode-bridge rectifier with additional line inductance                                                                                                                                               | 30 |

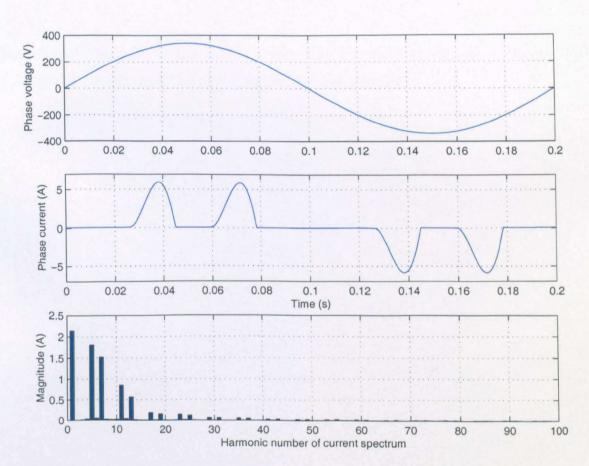

| 2.4  | Voltage and current waveforms for the diode bridge rectifier when 20mH of line inductance are introduced on each phase                                                                               | 31 |

| 2.5  | The 'Texas' circuit                                                                                                                                                                                  | 34 |

| 2.6  | Graph depicting the voltage on the upper and lower limbs of the d.c<br>link, one phase of the supply voltage and the voltage at the capacitor<br>mid-point with respect to the neutral of the supply | 36 |

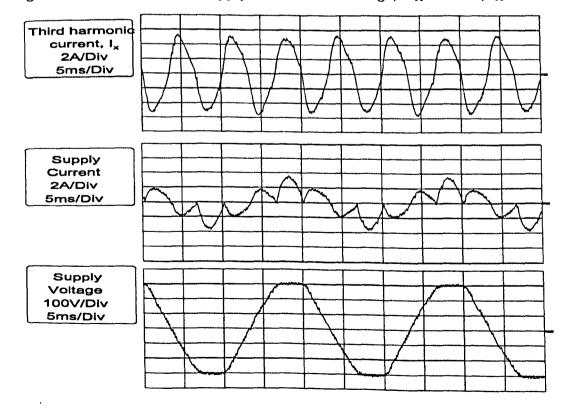

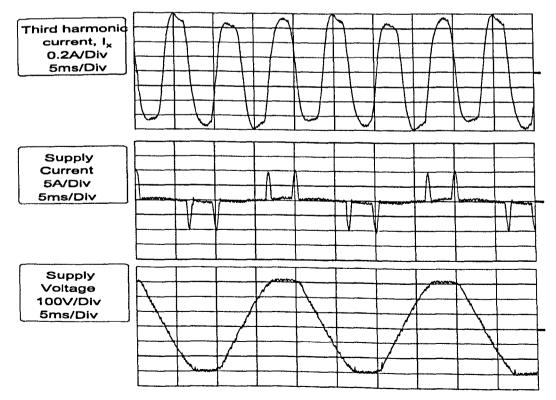

| 2.7  |                                                                                                                                                                                                      | 41 |

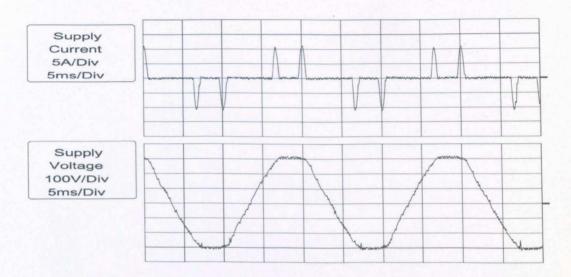

| 2.8  | Experimental: Supply current and voltage, $R_X=1.0\Omega, I_X=3.7A$                                                                                                                                  | 41 |

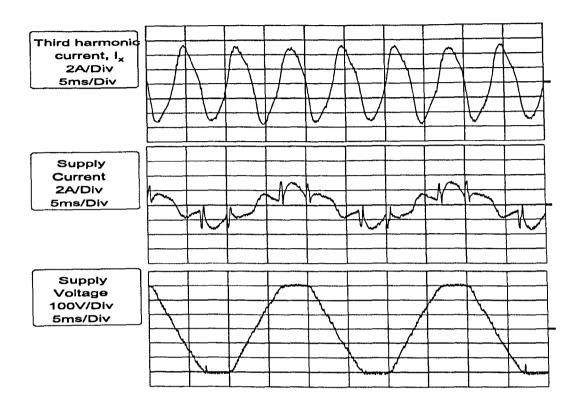

| 2.9  | Experimental: Supply current and voltage, $R_X=1.5\Omega, I_X=3.5A$                                                                                                                                  | 42 |

| 2.10 | Experimental: Supply current and voltage, $R_X=3.6\Omega, I_X=2.1A$                                                                                                                                  | 42 |

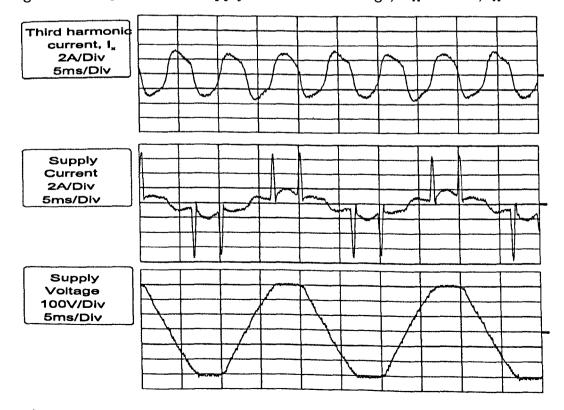

| 2.11 | Experimental: Supply current and voltage, $R_X = 9.0\Omega, I_X = 1.2A$                                                                                                                                                           | 43 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

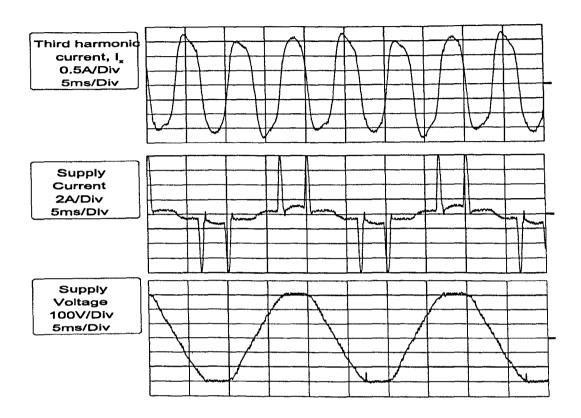

| 2.12 | Experimental: Supply current and voltage, $R_X=19.3\Omega, I_X=0.7A$ .                                                                                                                                                            | 43 |

| 2.13 | Experimental: Supply current and voltage with no feedback loop                                                                                                                                                                    | 44 |

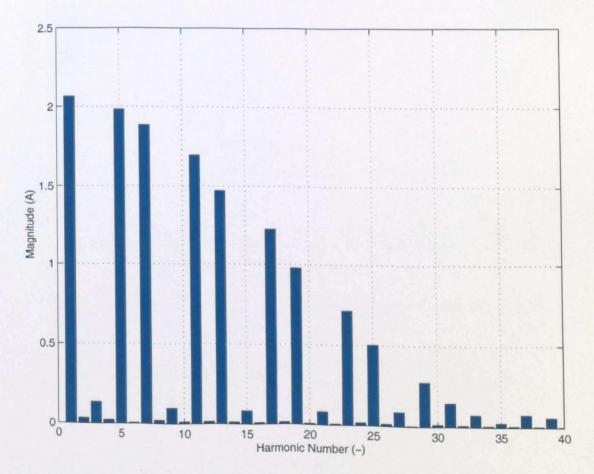

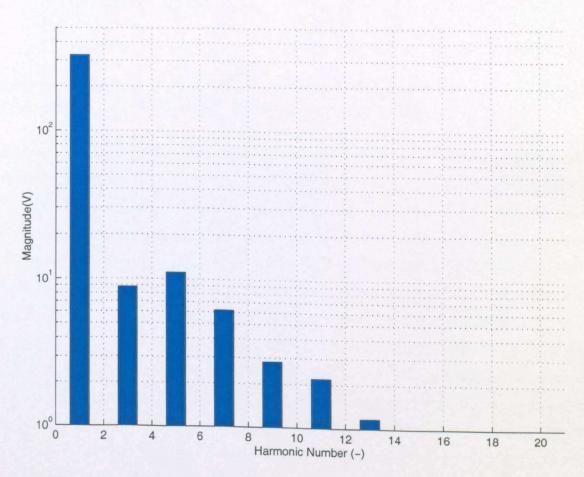

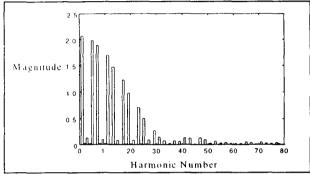

| 2.14 | Experimental: Supply current spectrum with no feedback                                                                                                                                                                            | 44 |

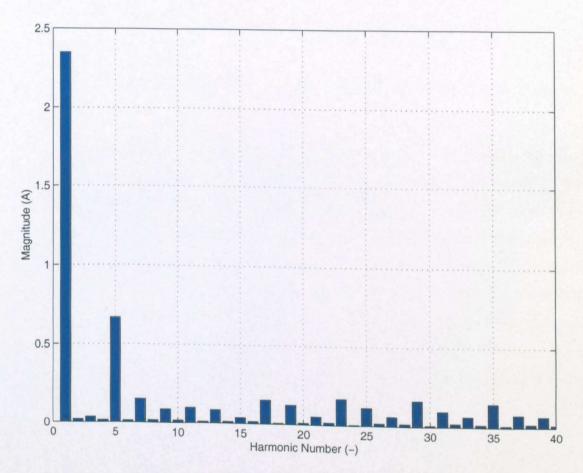

| 2.15 | Experimental: Supply current spectrum when $R_X=1.5\Omega$                                                                                                                                                                        | 45 |

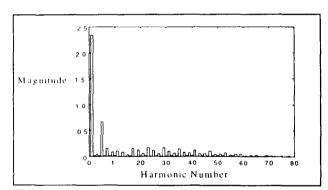

| 2.16 | Experimental: Typical supply phase voltage spectrum                                                                                                                                                                               | 47 |

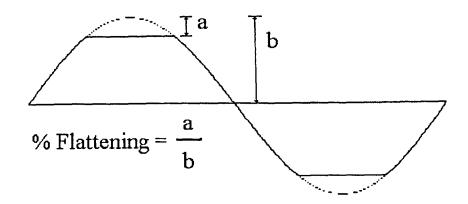

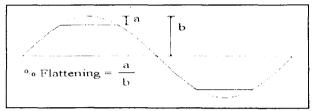

| 2.17 | Simulation: Definition of '% flattening'                                                                                                                                                                                          | 49 |

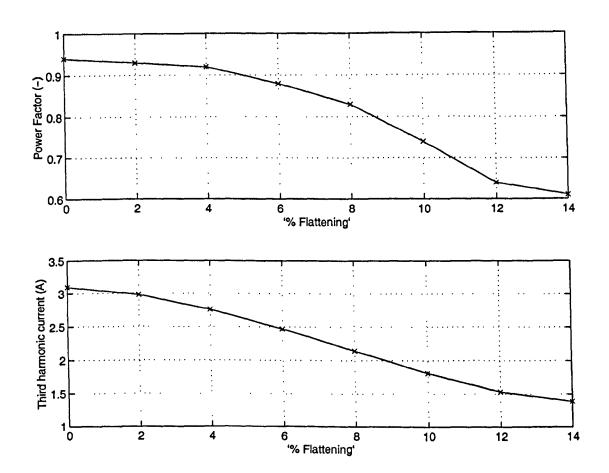

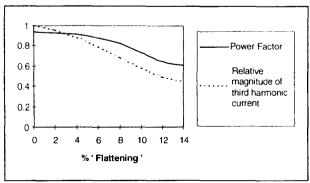

| 2.18 | Simulation: Effect of 'voltage flattening' on power factor and magnitude of circulating third harmonic current                                                                                                                    | 50 |

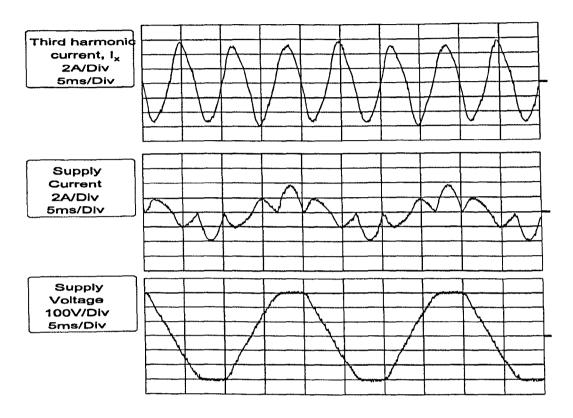

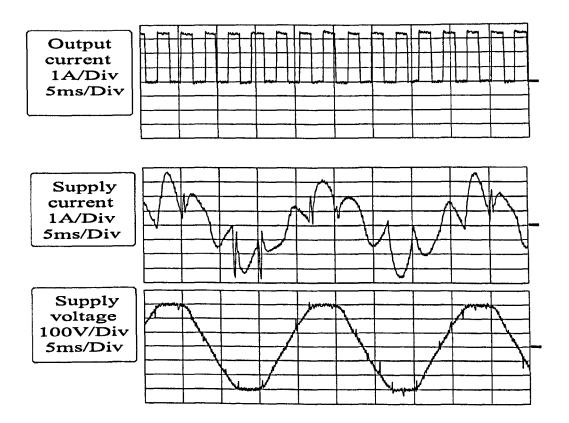

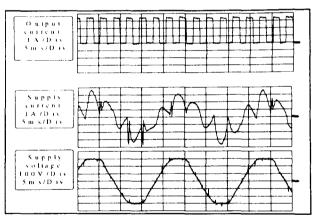

| 2.19 | Experimental: Output current, supply current and voltage with an active load, $R_X = 1.5\Omega \dots \dots \dots \dots \dots$                                                                                                     | 51 |

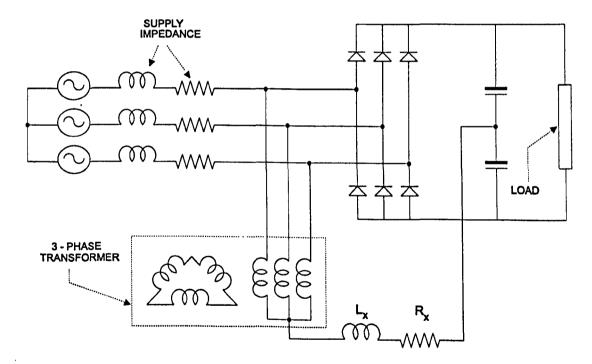

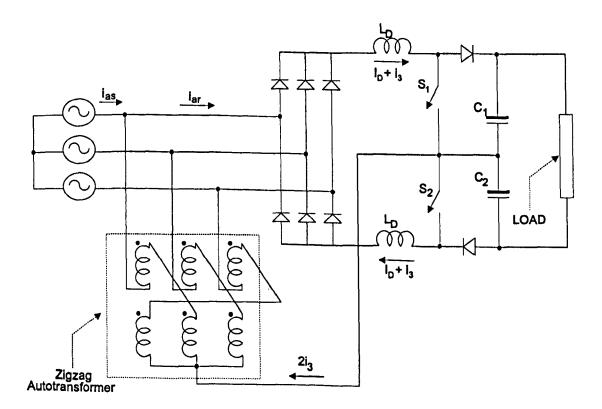

| 2.20 | The 'Minnesota' circuit                                                                                                                                                                                                           | 54 |

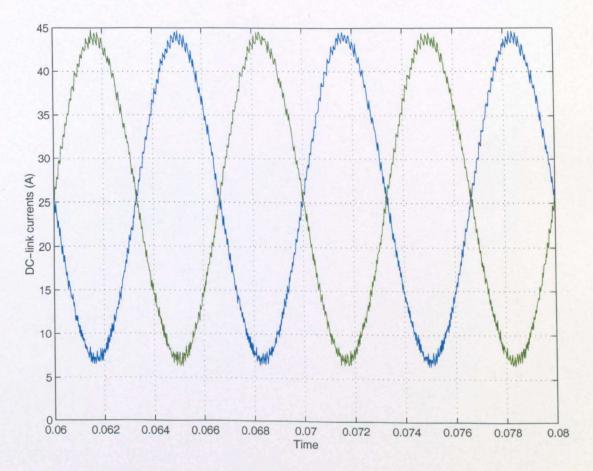

| 2.21 | Simulation: Top and bottom d.clink currents                                                                                                                                                                                       | 56 |

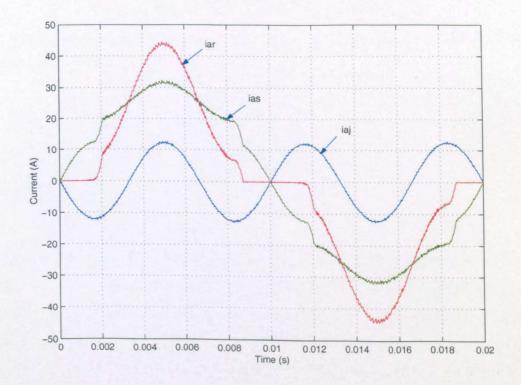

| 2.22 | Simulation: Supply current $(i_{as})$ , current into diode bridge $(i_{ar})$ and circulating third harmonic current $(i_{aj})$                                                                                                    | 57 |

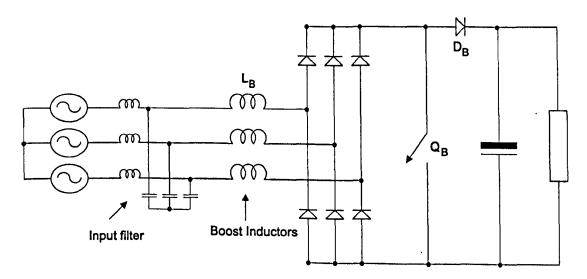

| 2.23 | The single-switch rectifier                                                                                                                                                                                                       | 60 |

| 2.24 | The three switch rectifier                                                                                                                                                                                                        | 63 |

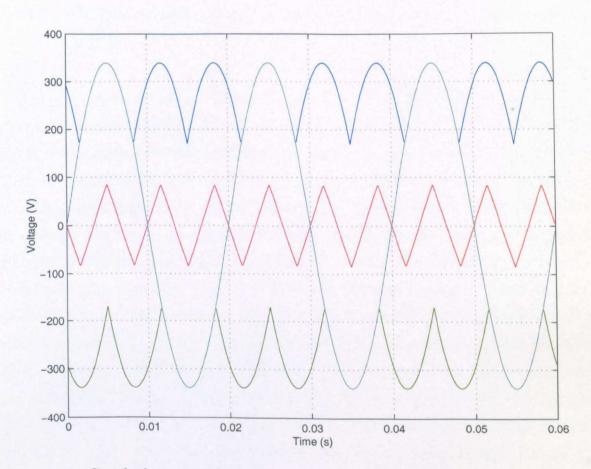

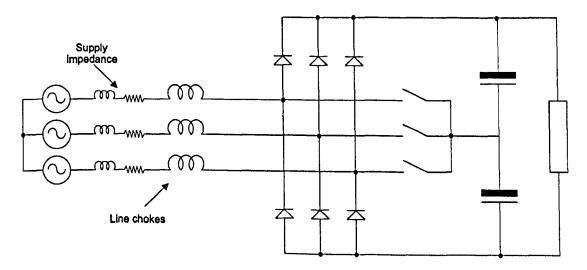

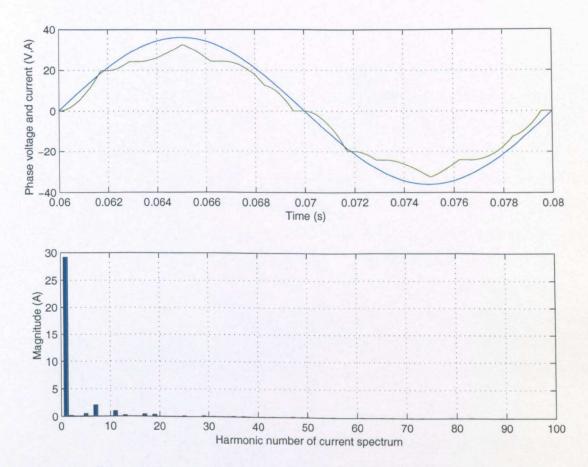

| 2.25 | The three phase currents: In each case the blue line denotes the current flowing into the diode bridge and the green line shows the current through the bidirectional switch. The supply current is the sum of these two currents | 65 |

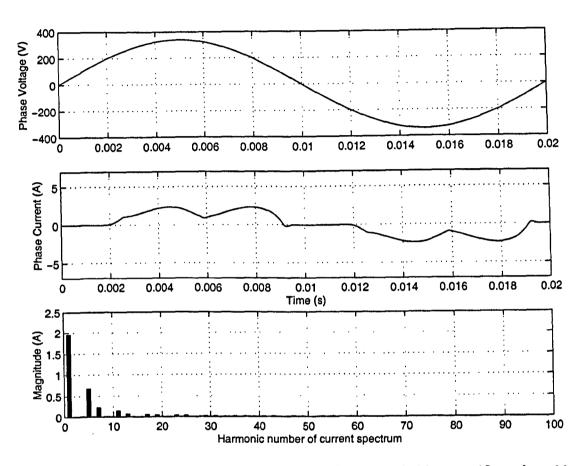

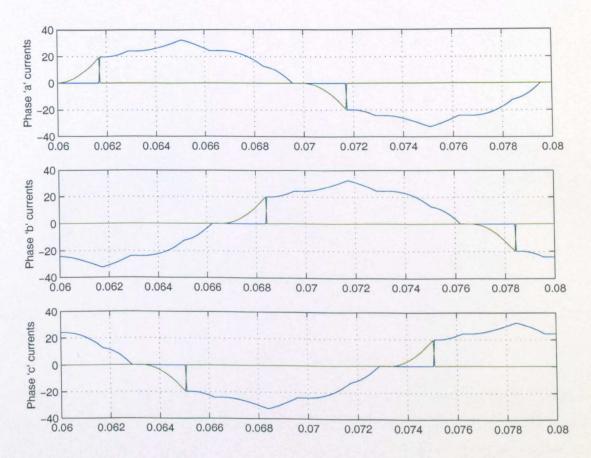

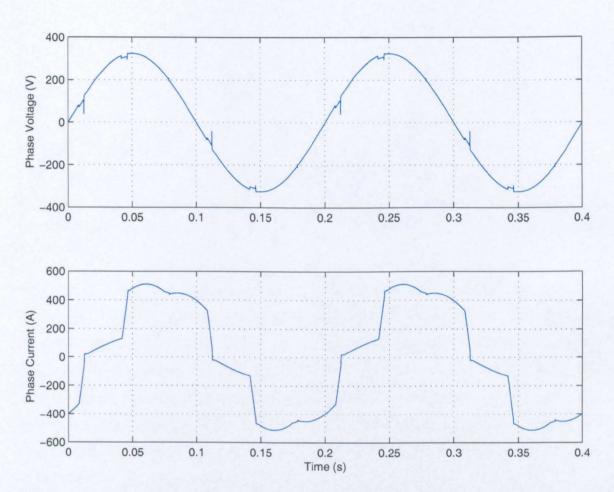

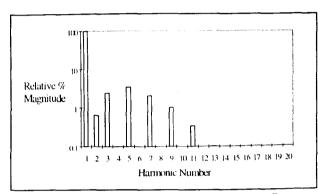

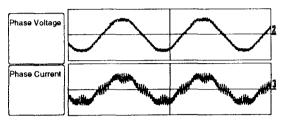

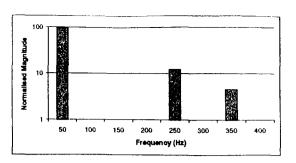

| 2.26 | Phase voltage and current and the harmonic spectrum of the current                                                                                                                                                                         |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | waveform                                                                                                                                                                                                                                   | 66  |

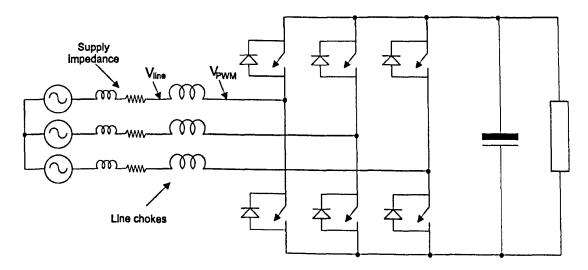

| 2.27 | The six-switch rectifier                                                                                                                                                                                                                   | 68  |

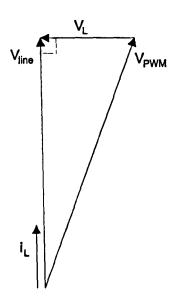

| 2.28 | Phasor diagram depicting the line voltage $(V_{line})$ , the voltage at the output of the inverter $(V_{PWM})$ , the resultant voltage across the line inductor $(V_L)$ and subsequent line current $(i_L)$ , for one phase of the circuit | 69  |

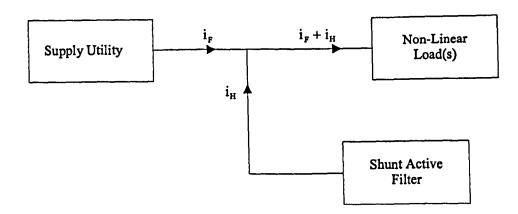

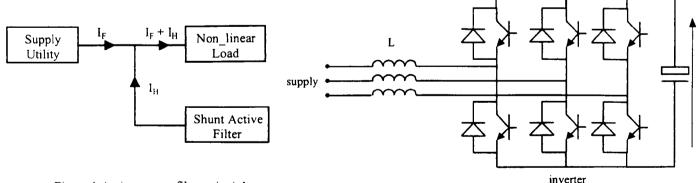

| 3.1  | Principle of operation of the shunt active filter                                                                                                                                                                                          | 77  |

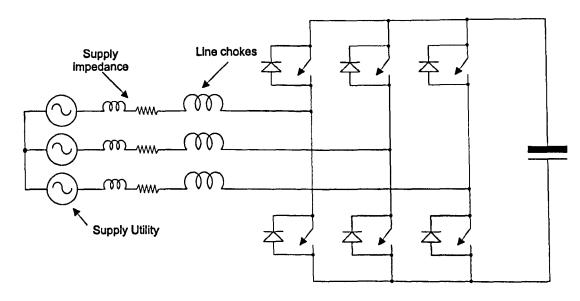

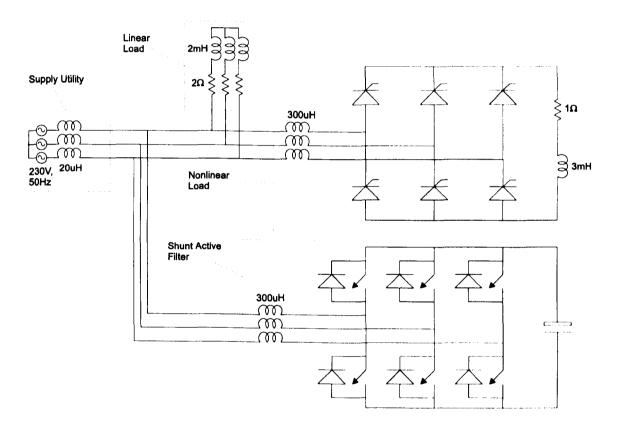

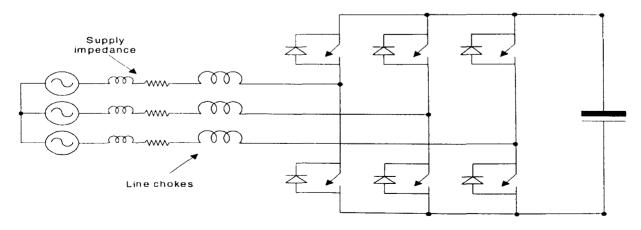

| 3.2  | Topology of the shunt active filter                                                                                                                                                                                                        | 78  |

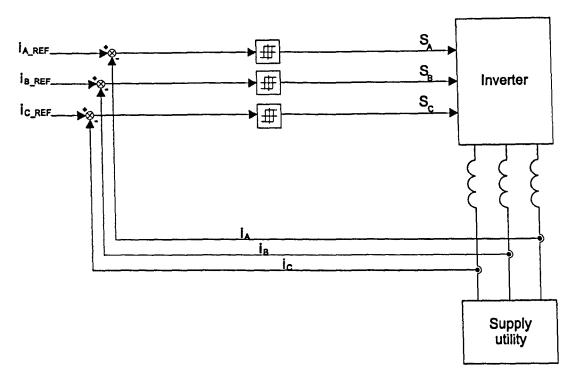

| 3.3  | The stationary PI current controller                                                                                                                                                                                                       | 82  |

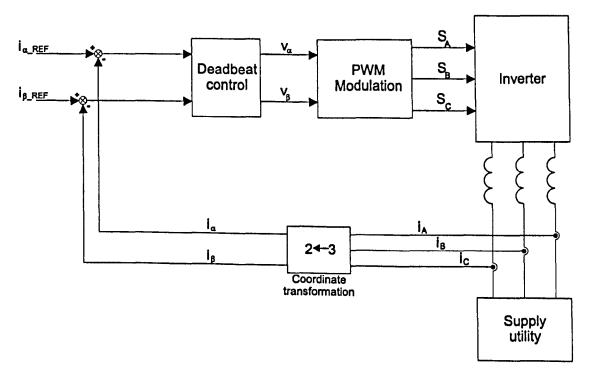

| 3.4  | The synchronous PI current controller                                                                                                                                                                                                      | 84  |

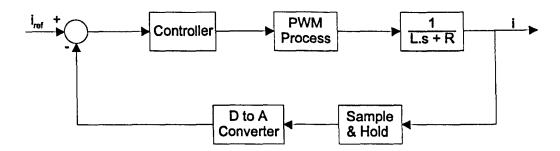

| 3.5  | The deadbeat current controller                                                                                                                                                                                                            | 85  |

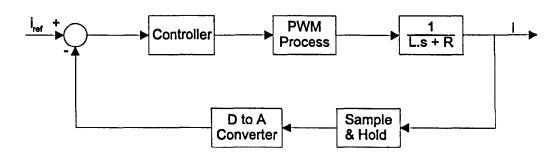

| 3.6  | The hysteresis current controller                                                                                                                                                                                                          | 87  |

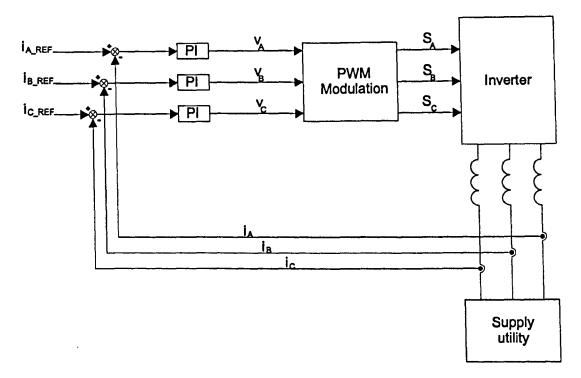

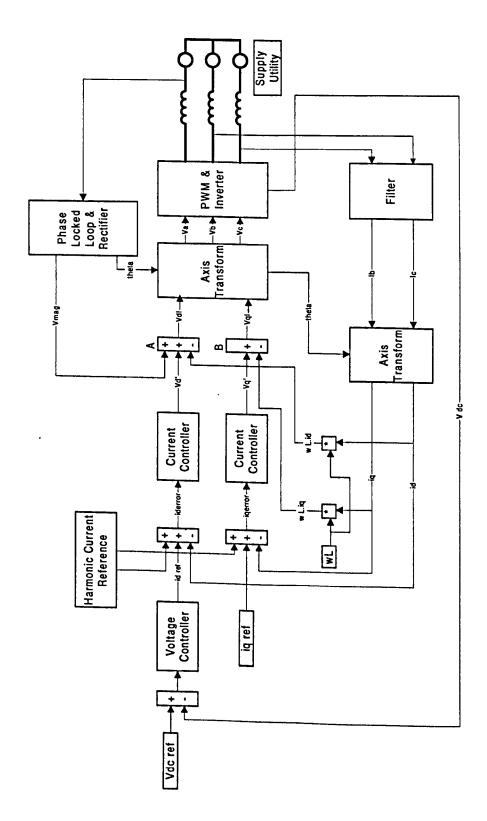

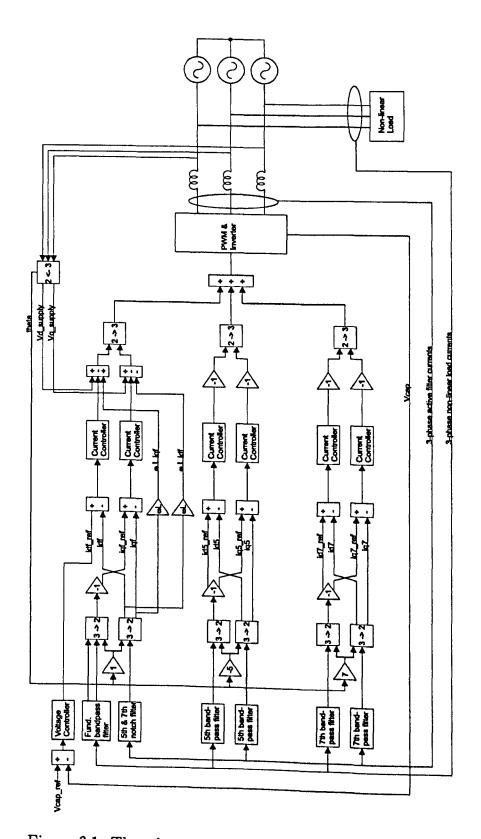

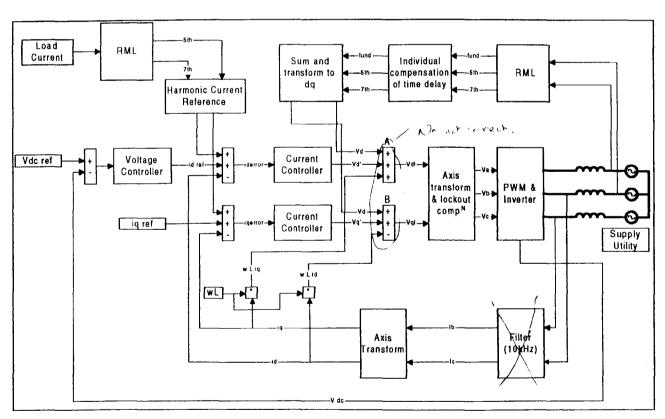

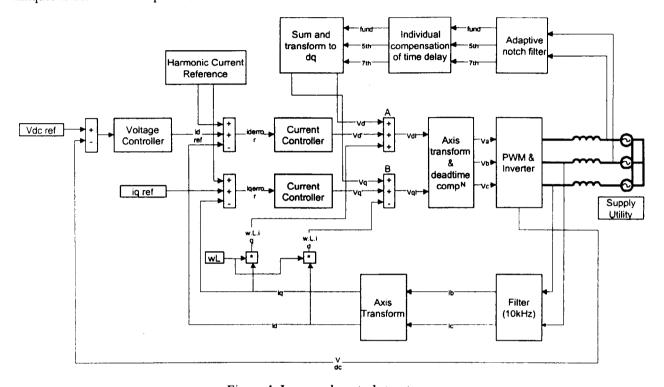

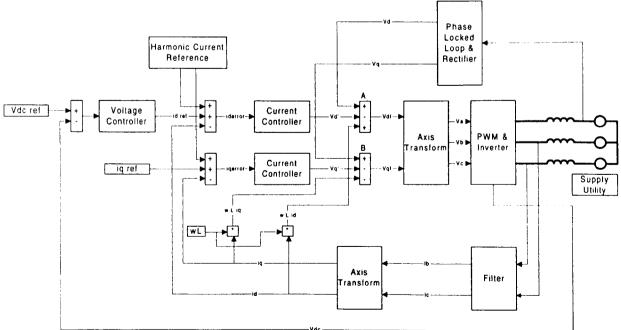

| 4.1  | Synchronous PI control of the shunt active filter                                                                                                                                                                                          | 91  |

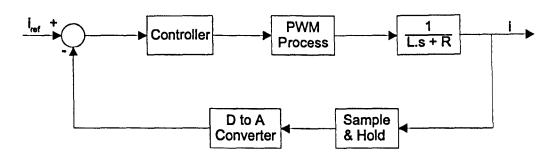

| 4.2  | Closed loop block diagram for the current control on each axis                                                                                                                                                                             | 98  |

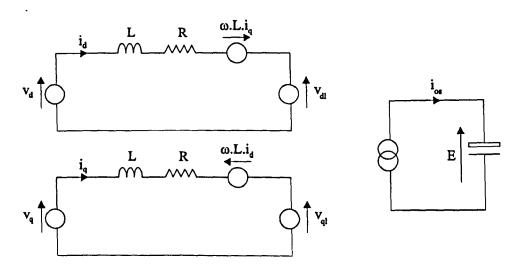

| 4.3  | Equivalent circuit for the shunt active filter in dq-coordinates                                                                                                                                                                           | 100 |

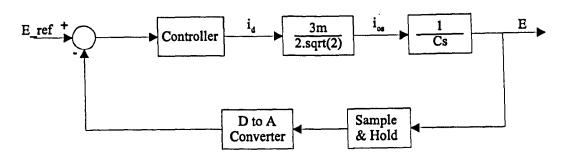

| 4.4  | Closed loop block diagram for the voltage control                                                                                                                                                                                          | 101 |

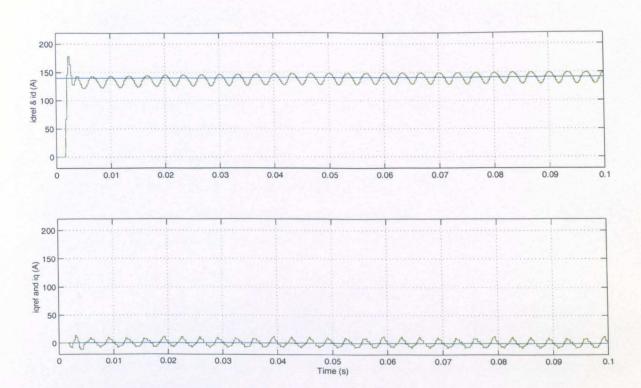

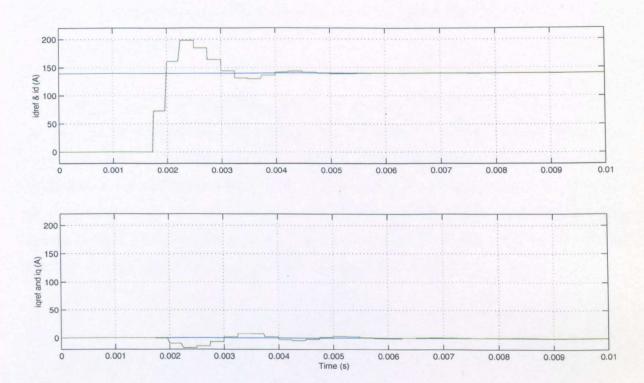

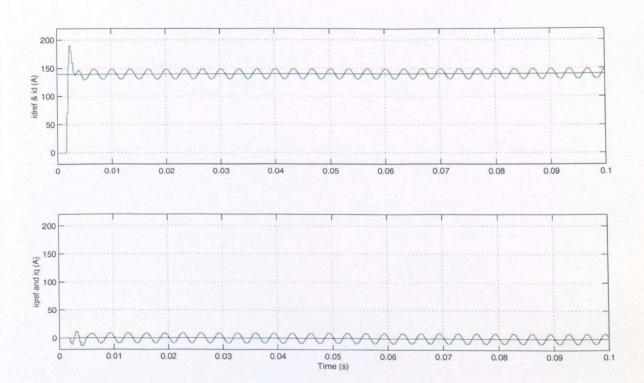

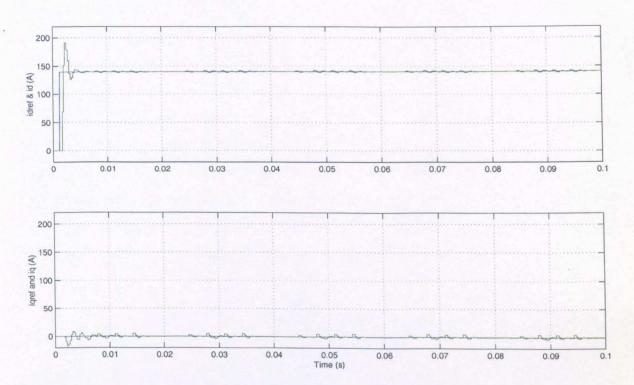

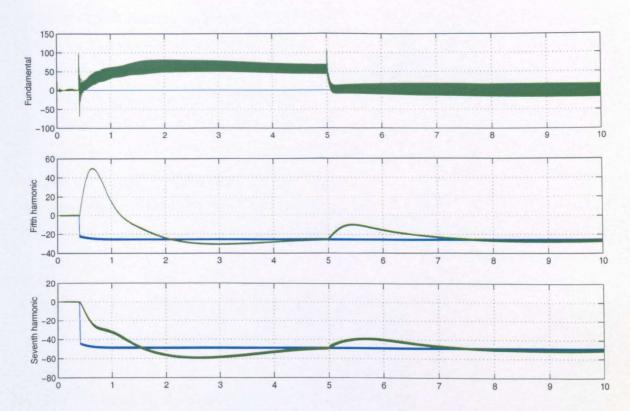

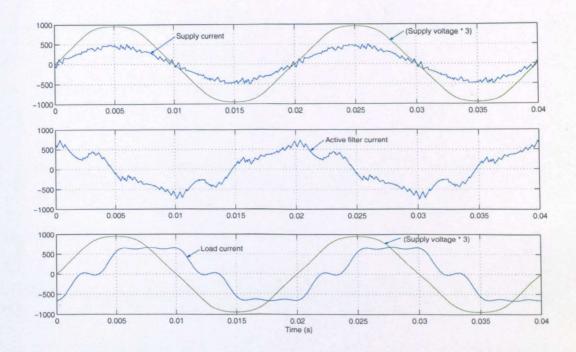

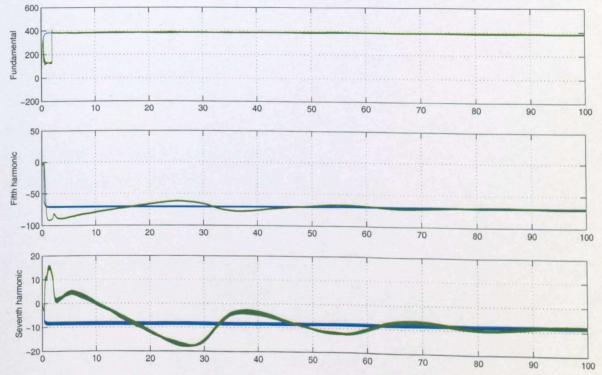

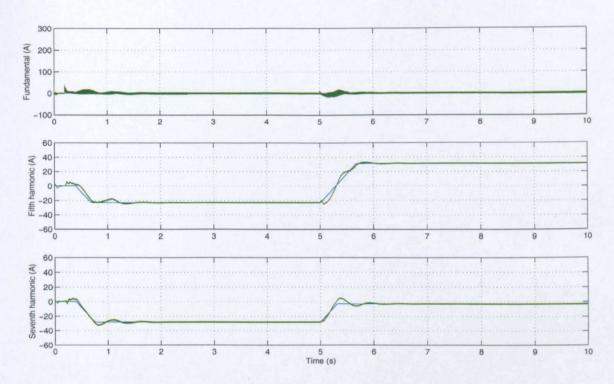

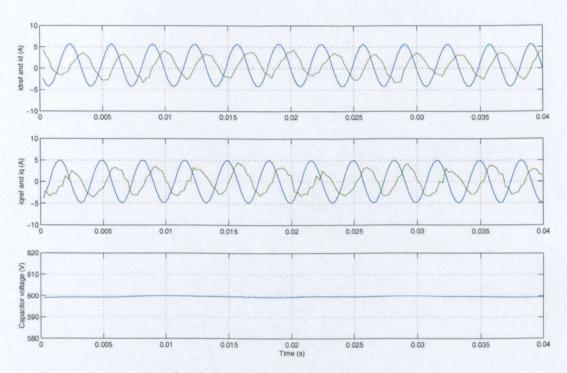

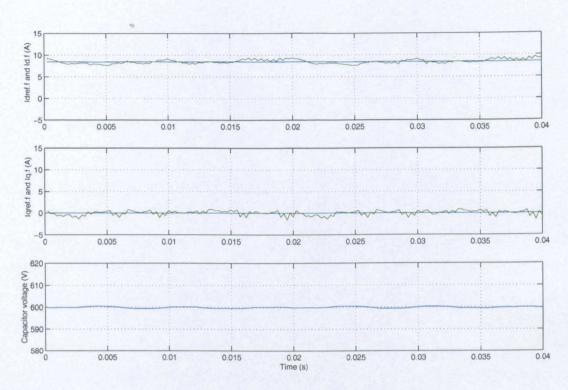

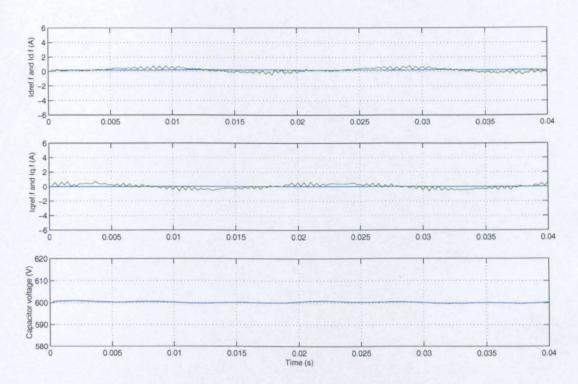

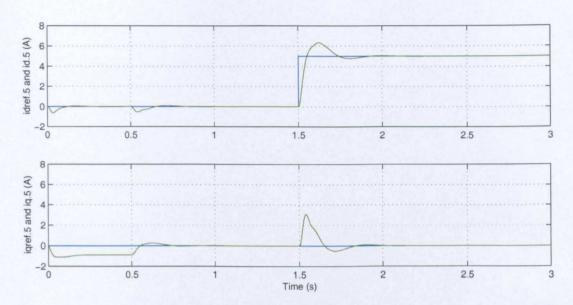

| 4.5  | Synchronous PI control working with realistic conditions: d- and q-axis currents                                                                                                                                                           | 104 |

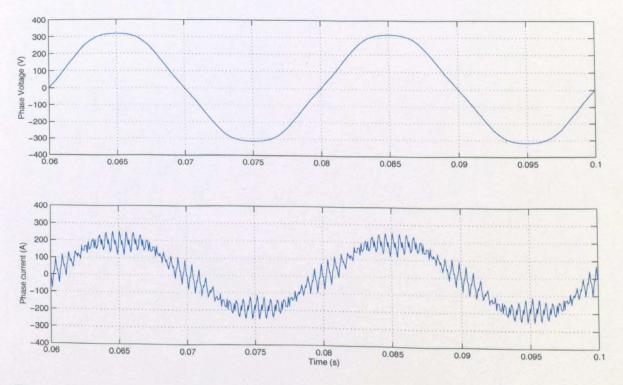

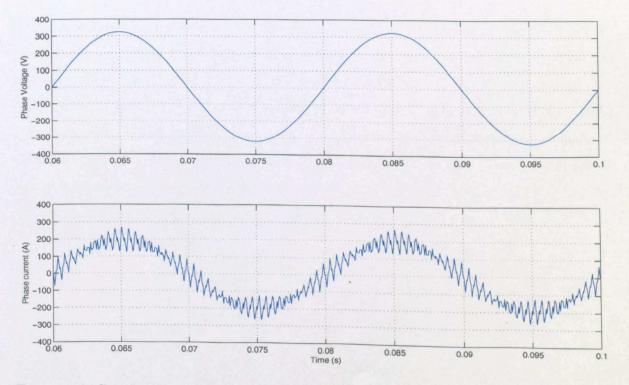

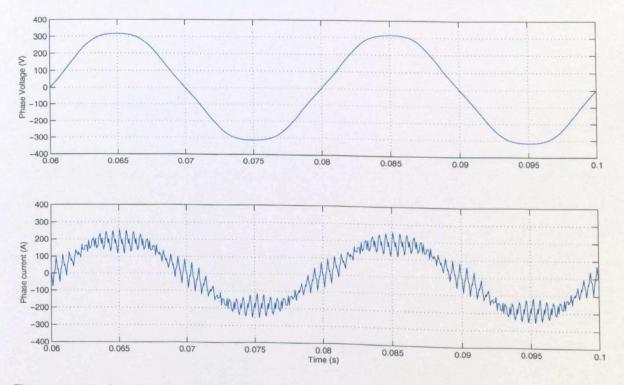

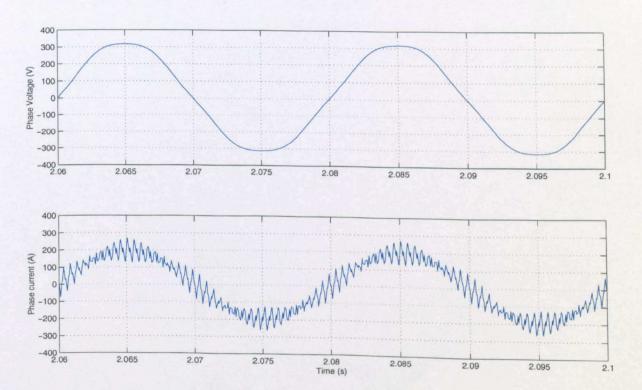

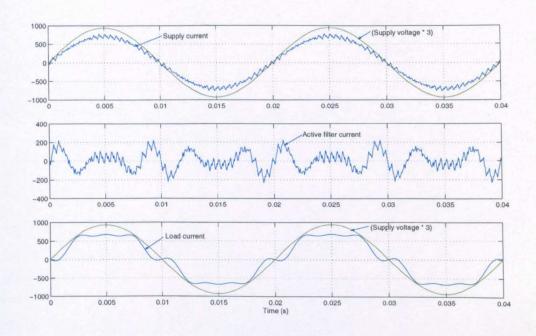

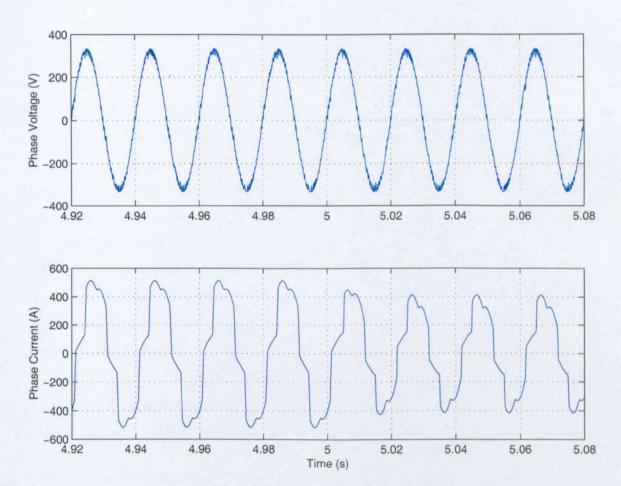

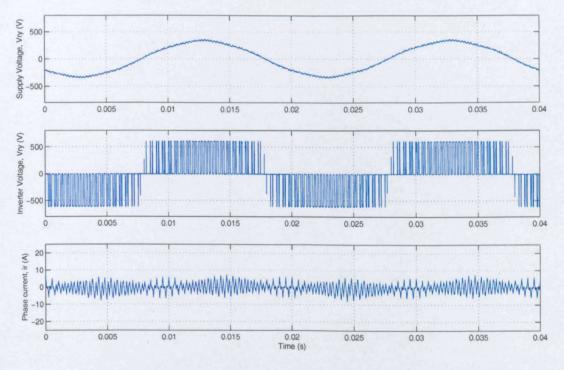

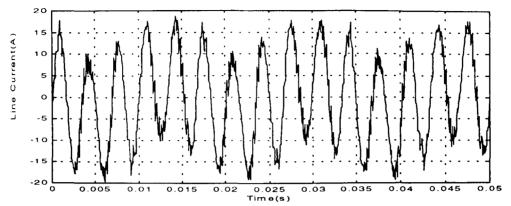

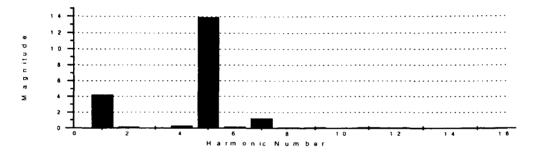

| 4.6  | Synchronous PI control working with realistic conditions: Phase voltage and current                                | 104 |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 4.7  | Synchronous PI control working with ideal conditions: d- and q-axis currents                                       | 106 |

| 4.8  | Synchronous PI control working with ideal conditions: Phase voltage and current                                    | 106 |

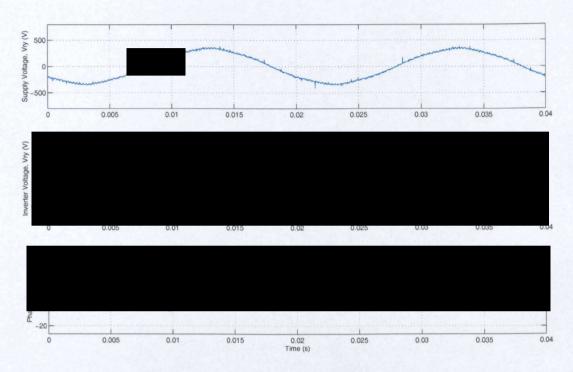

| 4.9  | Synchronous PI control working with deadtime: d- and q-axis currents                                               | 108 |

| 4.10 | Synchronous PI control working with deadtime: Phase voltage and current                                            | 108 |

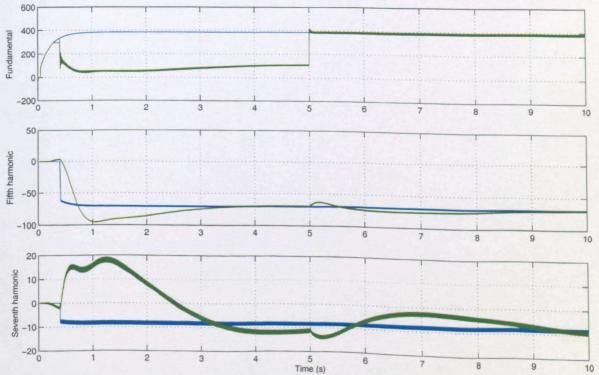

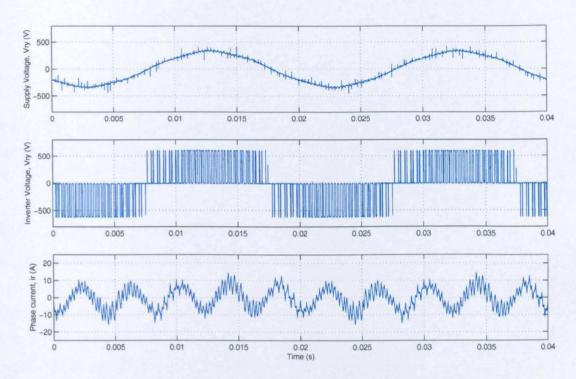

| 4.11 | Synchronous PI control working with supply distortion: d- and q-axis currents                                      | 110 |

| 4.12 | Synchronous PI control working with supply distortion: Phase voltage and current                                   | 110 |

| 5.1  | Current control loop as seen by each axis                                                                          | 114 |

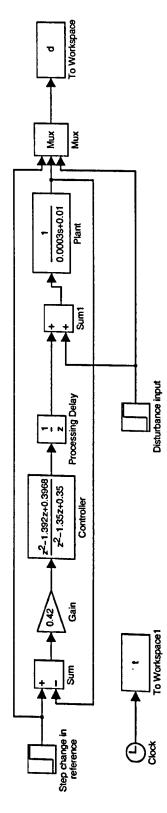

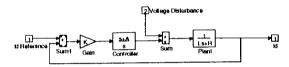

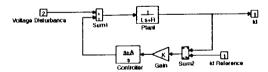

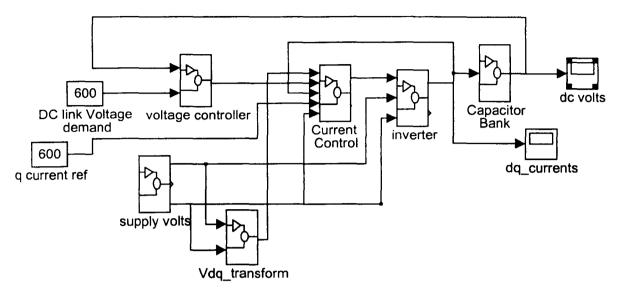

| 5.2  | Simulink model for the above simulation                                                                            | 116 |

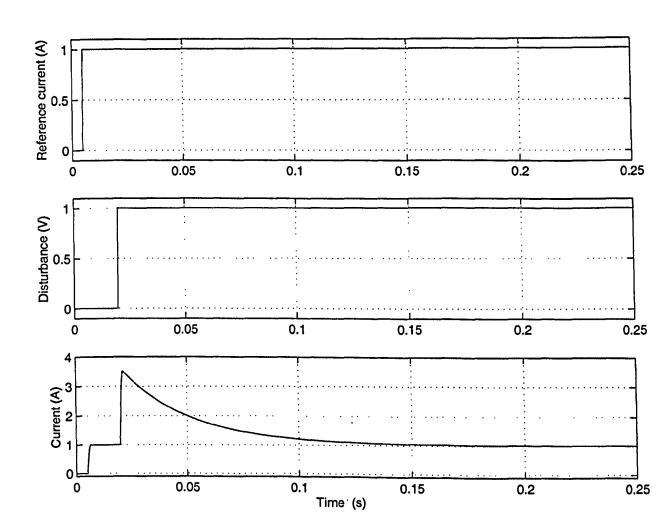

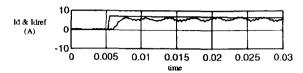

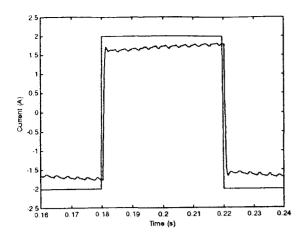

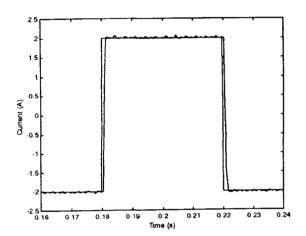

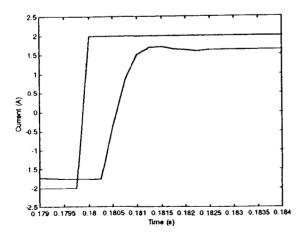

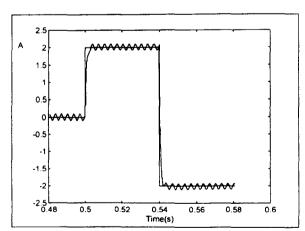

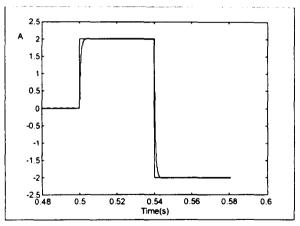

| 5.3  | A step change in current reference and a step disturbance in the current control loop after the current controller | 117 |

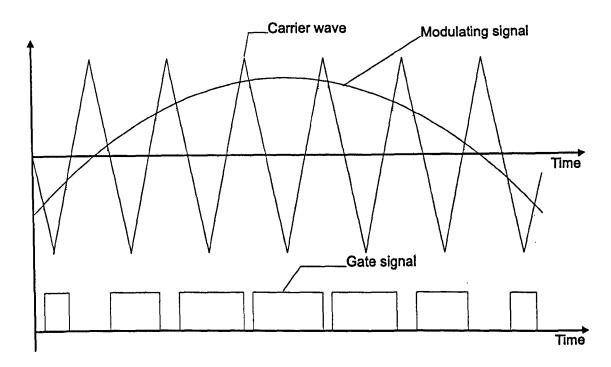

| 5.4  | Generation of the gate signal                                                                                      | 120 |

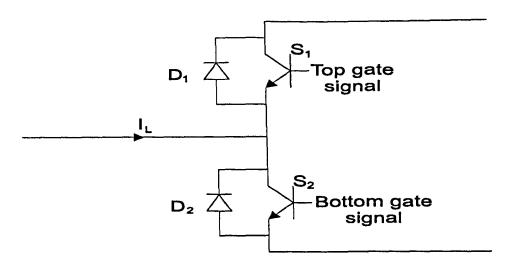

| 5.5  | One inverter leg of the shunt active filter                                                                        | 121 |

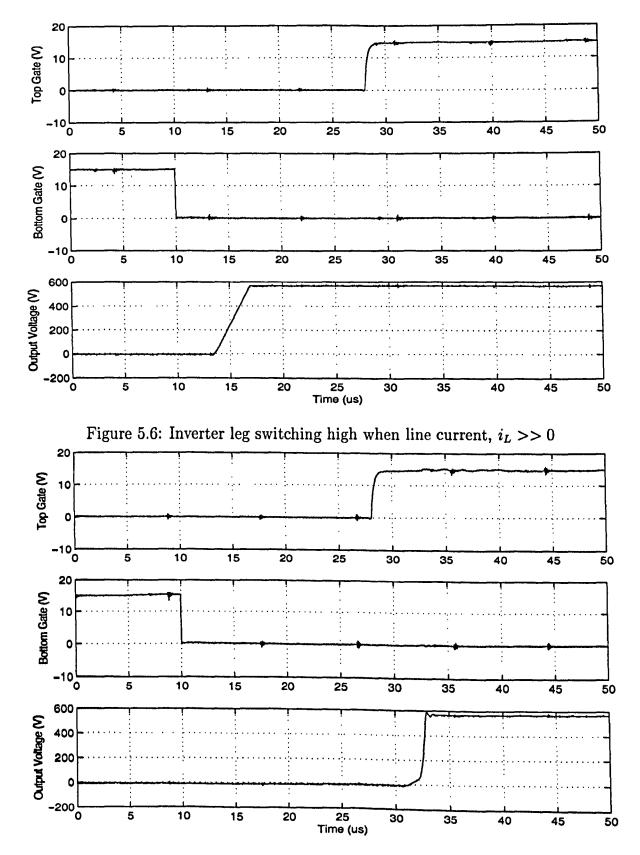

| 5.6  | Inverter leg switching high when line current, $i_L >> 0$                                                          | 122 |

| 5.7  | Inverter leg switching high when line current, $i_L \ll 0 \ldots \ldots$                                           | 122 |

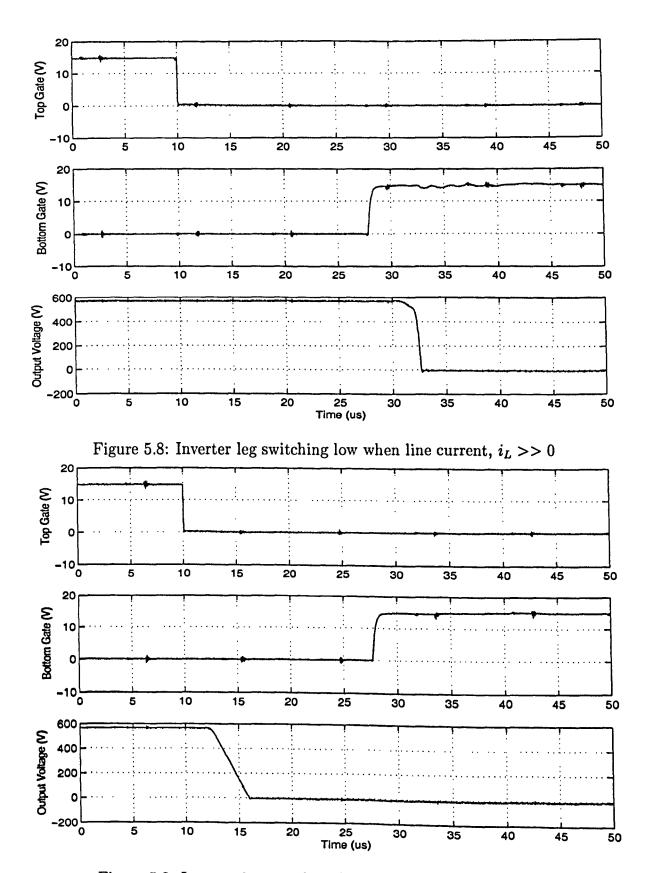

| 5.8  | Inverter leg switching low when line current, $i_L >> 0$                                                                                                          | 123 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | Inverter leg switching low when line current, $i_L << 0 \ldots \ldots$                                                                                            | 123 |

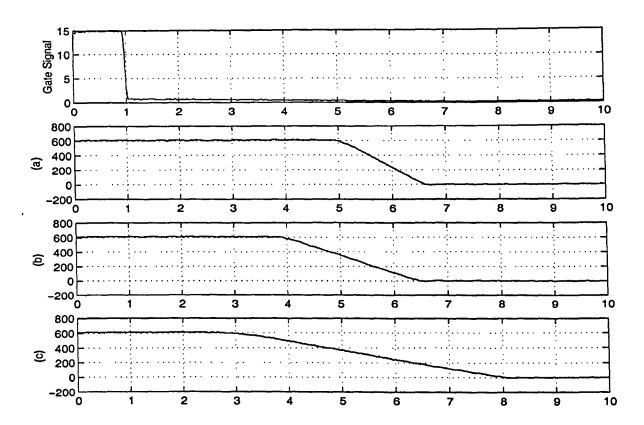

| 5.10 | Switching edge variation with magnitude of the line current: a) Output voltage when $I_L=-20.0A$ , b) $I_L=-12.5A$ , c) $I_L=-6.4A$                               | 125 |

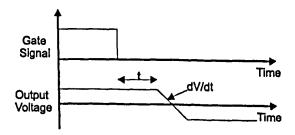

| 5.11 | Trend in output voltage as $I_L$ changes $\ldots \ldots \ldots \ldots$                                                                                            | 125 |

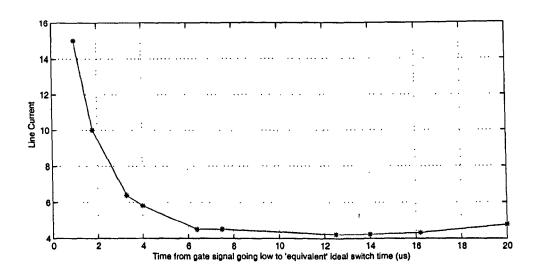

| 5.12 | The relationship between the line current, $i_L$ , and the time delay, $T_D$ , from the gate signal changing to the equivalent ideal switching edge at the output | 126 |

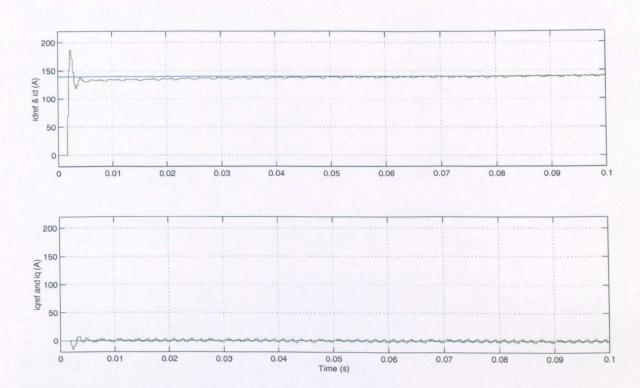

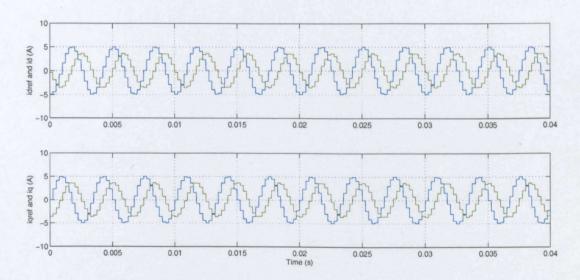

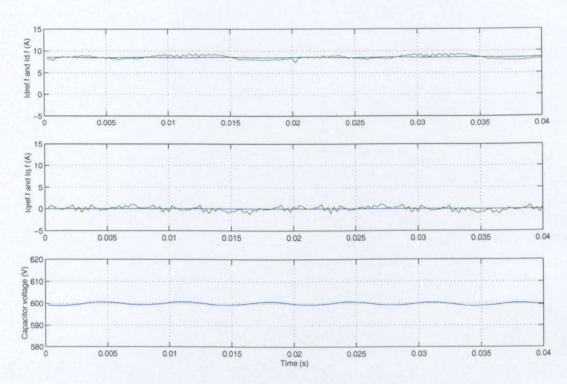

| 5.13 | Improved synchronous PI control working with deadtime: d- and q-axis currents                                                                                     | 130 |

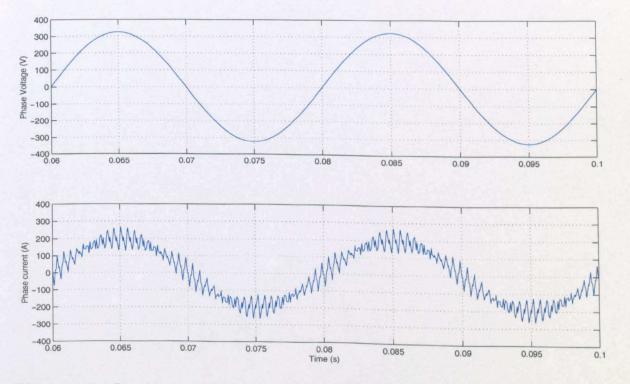

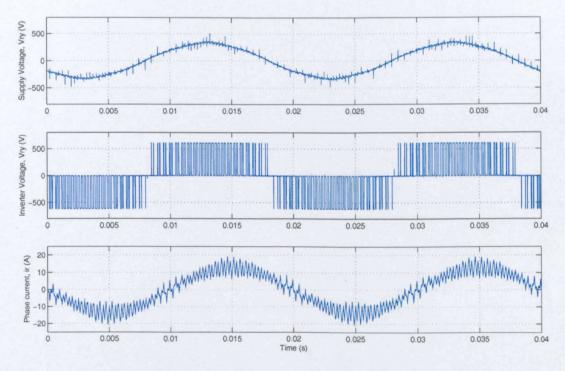

| 5.14 | Improved synchronous PI control working with deadtime: Phase voltage and current                                                                                  | 130 |

| 5.15 | Improved synchronous PI control working with supply distortion: d- and q-axis currents                                                                            | 133 |

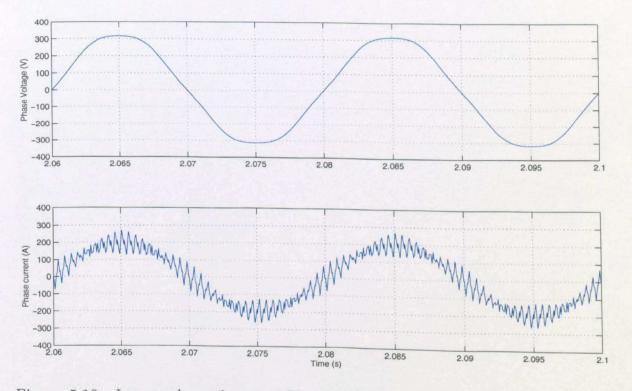

| 5.16 | Improved synchronous PI control working with supply distortion: Phase voltage and current                                                                         |     |

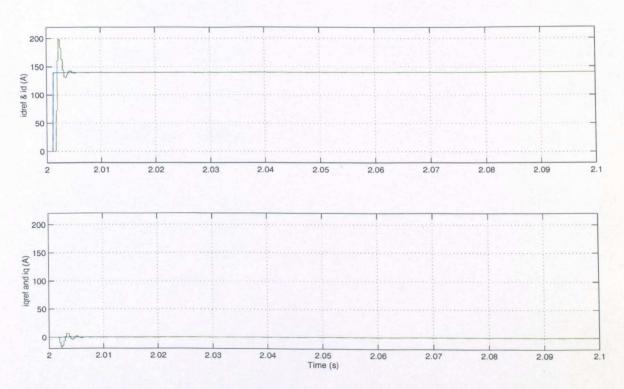

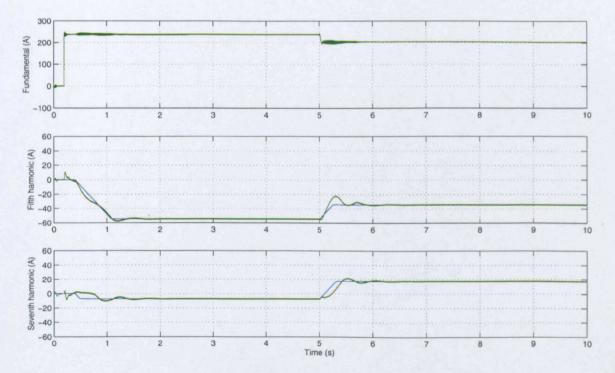

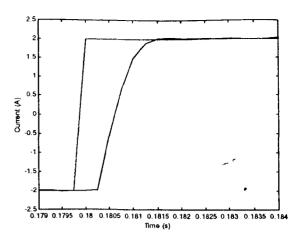

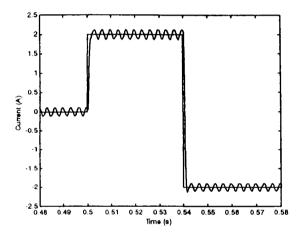

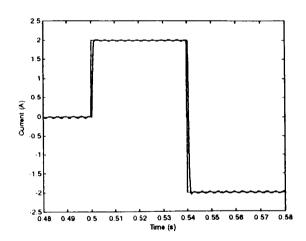

| 5.17 | Improved synchronous PI control working with realistic conditions: d- and q-axis currents                                                                         | 135 |