# Heterogeneous Chip Multiprocessor: Data Representation, Mixed-Signal Processing Tiles, and System Design

by

Kayode A. Sanni

A dissertation submitted to The Johns Hopkins University in conformity with the requirements for the degree of Doctor of Philosophy.

Baltimore, Maryland

January, 2019

© Kayode A. Sanni 2019

All rights reserved

### Abstract

With the emergence of big data, the need for more computationally intensive processors that can handle the increased processing demand has risen. Conventional computing paradigms based on the Von Neumann model that separates computational and memory structures have become outdated and less efficient for this increased demand. As the speed and memory density of processors have increased significantly over the years, these models of computing, which rely on a constant stream of data between the processor and memory, see less gains due to finite bandwidth and latency. Moreover, in the presence of extreme scaling, these conventional systems, implemented in submicron integrated circuits, have become even more susceptible to process variability, static leakage current, and more. In this work, alternative paradigms, predicated on distributive processing with robust data representation and mixed-signal processing tiles, are explored for constructing more efficient and scalable computing systems in application specific integrated circuits (ASICs).

The focus of this dissertation work has been on heterogeneous chip multi-processor (CMP) design and optimization across different levels of abstraction. On the level

#### ABSTRACT

of data representation, a different modality of representation based on random pulse density modulation (RPDM) coding is explored for more efficient processing using stochastic computation. On the level of circuit description, mixed-signal integrated circuits that exploit charge-based computing for energy efficient fixed point arithmetic are designed. Consequently, 8 different chips that test and showcase these circuits were fabricated in submicron CMOS processes. Finally, on the architectural level of description, a compact instruction-set processor and controller that facilitates distributive computing on System-On-Chips (SoCs) is designed. In addition to this, a robust bufferless network architecture is designed with a network simulator, and I/O cells are designed for SoCs.

The culmination of this thesis work has led to the design and fabrication of a heterogeneous chip multi-processor prototype comprised of over 12,000 VVM cores, warp/dewarp processors, cache, and additional processors, which can be applied towards energy efficient large-scale data processing.

Primary Reader: Andreas G. Andreou Secondary Reader: Ralph Etienne-Cummings Committee Member: Philippe O. Pouliquen

### Acknowledgments

This dissertation work would not have been possible without the support of many individuals. Firstly, I would like to express my deepest gratitude to my advisor, Andreas Andreou, who has been an insightful and enduring mentor to me throughout my graduate studies. He has not only challenged me to diligently approach research with an open-mind, but has also been patiently supportive of me throughout the years. I'm grateful for all the candid and unembellished talks we've had that has constructively led to many improvements in my work.

I would like to specially thank my secondary reader, Ralph Etienne-Cummings, for not only his service on my committee, but also for his indispensable support that has always been available to me throughout my studies here at Hopkins. Additionally, I am very grateful to my other committee member, Philippe Pouliquen, who has been an invaluable source of help to me throughout my dissertation work.

I am grateful to other ECE faculty members at Hopkins, who have been instrumental in my research. I thank Pedro Julian for his unwavering support, advice, and insight throughout the years. I thank Charbel Rizk, who I have had the pleasure

#### ACKNOWLEDGMENTS

of collaborating with on projects that has been useful for my research. I thank Jim West, who has been supportive of me, and offered me great advice over the years. I also thank my first PI, Jeffrey Gray, a professor in the Chemical and Biomolecular Engineering Department here at Hopkins. He introduced me to interdisciplinary research during my first research internship, and was a very supportive mentor to me, even before starting graduate school.

A large portion of my dissertation work was supported by the DARPA UPSIDE project HR0011-13-C-0051 through BAE Systems. I am grateful to Mike Graziano, Isidoros Doxas, and Louise Sengupta, who managed the project the first two years while at BAE systems, for their support and encouragement. I would like to acknowledge Tomás Figliolia for his significant contribution to this project. I am appreciative to Christian Mayr from the Technische Universität Dresden, Germany for his support and inspiration in this project that was useful for my dissertation. I am also grateful for the other funding I have received over the year from the NSF grant SCH-INT 1344772, the ONR MURI N000141010278, and the NSF grant INSPIRE SMA 1248056.

I am very thankful to all my fellow colleagues that I have been fortunate to learn from and collaborate with during my tenure in the Andreou Lab including: Joseph Lin, Recep Özgün, Thomas Murray, Tomás Figliolia, Daniel Mendat, Gaspar Tognetti, Guillaume Garreau, Kate Fischl, Martìn Villemur, Christos Sapsanis, Jeff Craley, Alejandro Pasciaroni, Valerie Rennoll, and Jonah Sengupta. I thank Francisco

#### ACKNOWLEDGMENTS

Tejada too for all the help he has provided me. I specially thank Tomás and Martin for teaching me how to use the synthesis and place and route tool, which I was able to use extensively in my thesis. I also specially thank Gaspar for the numerous of insightful discussions we've had that has been instrumental in my dissertation work.

I am grateful to my other colleagues, who have been helpful in one way or another. I thank the members of the Computational Sensory-Motor Systems Laboratory headed by Ralph Etienne-Cumming, especially Jamal Molin, Jack Zhang, and Adebayo Eisape, who I've had the pleasure to collaborate with over the years. I am grateful to Ebuka Arinze, who has been a brother to me and given me invaluable advice and support throughout the years. I would like to acknowledge my friends from JHU BGSA and the ECE GSA for all their support in and outside of school.

I would like to also thank the ECE department and staff including: Janel Johnson, Nicole Aaron, Debbie Race, Cora Mayenschein, Ruth Scally, Sathappan Ramesh, Eileen Miller, Laura Granite, Dana Walter-Shock, Melissa Gibbins, and Barbara Sullivan for all the work they've done in the background, and the timely help they given me over the years. I would also like to thank the Assistant Dean for Graduate and Postdoctoral Academic Affairs, Christine Kavanagh, who has assisted me through my time here at Hopkins.

I am grateful to the Meyerhoff Scholarship Program at UMBC for their financial and academic support throughout my undergraduate career. The Meyerhoff program was instrumental in preparing me for graduate school. Specifically, I would like to

#### ACKNOWLEDGMENTS

thank late LaMont Toliver, Keith Harmon, Mitsue Wiggs, Sharon Johnson, Alicia Halls, and Michael Goodwin for all their support.

Last but not least, I am truly grateful for my family and friends. Right from an early age, my parents, Muibat and Mustapha Sanni, have instilled in me the value and importance of education. They taught me to work hard and to never settle. I am undoubtedly grateful for their untiring sacrifice and support throughout my life. I would like to thank my siblings, Olatunde Sanni, Folashade Sanni, and Adekunle Sanni, who have been very supportive of my academic career. I also extend my gratitude to my church community, including my pastors late Paul Akapo, Taiwo Fagbuyi, and Uwem Ekpo for all their support.

To quote Isaac Newton, "If I have seen further it is by standing on the shoulders of Giants."

## Dedication

This thesis is dedicated to my parents, Muibat and Mustapha, who have inspired and supported me throughout my academic career.

# Contents

| A        | bstra           | ct      |                                             |  |   | ii   |

|----------|-----------------|---------|---------------------------------------------|--|---|------|

| A        | Acknowledgments |         |                                             |  |   |      |

| Li       | st of           | Tables  | 5                                           |  |   | xvi  |

| Li       | st of           | Figure  | es                                          |  | x | viii |

| 1        | Intr            | oducti  | ion                                         |  |   | 1    |

| <b>2</b> | Sto             | chastic | Representation for Computational Efficiency |  |   | 7    |

|          | 2.1             | Data l  | Representation                              |  |   | 8    |

|          |                 | 2.1.1   | Analog vs. Digital                          |  |   | 9    |

|          |                 | 2.1.2   | Unary vs. Binary                            |  |   | 10   |

|          | 2.2             | Stocha  | astic Encoding and Computing                |  |   | 12   |

|          |                 | 2.2.1   | Precision Analysis                          |  |   | 15   |

|          |                 | 2.2.2   | Pseudo-Random Numbers                       |  |   | 18   |

|   | 2.3 | A Dee  | ep Belief Network Using Stochastic Computation        | 20 |

|---|-----|--------|-------------------------------------------------------|----|

|   |     | 2.3.1  | Background and Theory                                 | 21 |

|   |     | 2.3.2  | Architecture and Implementation                       | 25 |

|   |     | 2.3.3  | Results                                               | 28 |

|   | 2.4 | Adapt  | vive Background Modeling Using Stochastic Computation | 31 |

|   |     | 2.4.1  | Parametric Probabilistic Background Model             | 33 |

|   |     | 2.4.2  | Architecture Using Stochastic Computation             | 37 |

|   | 2.5 | Conclu | usion                                                 | 42 |

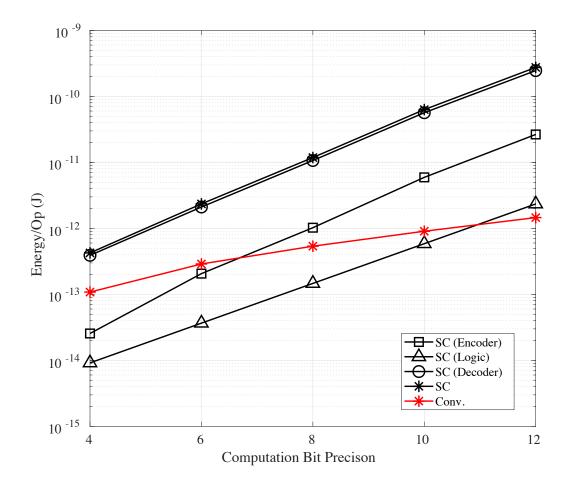

|   |     | 2.5.1  | Comparative Analysis                                  | 43 |

|   |     | 2.5.2  | Exploiting Stochastic Computing for ASIC              | 45 |

| 3 | Mix | ed-Sig | nal Architectures for VVM                             | 48 |

|   | 3.1 | Charg  | e-Based Computing                                     | 50 |

|   |     | 3.1.1  | Energy and Thermal Noise Limit                        | 54 |

|   | 3.2 | Analo  | g-to-Digital Conversion                               | 57 |

|   |     | 3.2.1  | First-Order $\Sigma\Delta$ Modulator                  | 57 |

|   |     | 3.2.2  | Switched-Capacitor Implementation                     | 61 |

|   |     |        | 3.2.2.1 Integrator                                    | 65 |

|   |     |        | 3.2.2.2 Comparator and Latch                          | 70 |

|   | 3.3 | GF1 V  | /VM: A 6-bit MAC Processor in 65nm CMOS               | 72 |

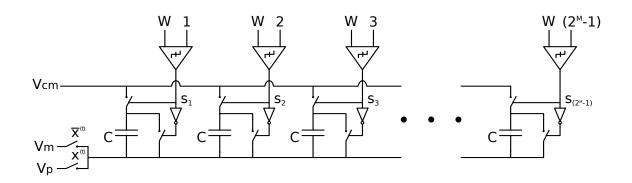

|   |     | 3.3.1  | Unary Weighted Capacitor Array                        | 73 |

|   |     |        | 3.3.1.1 Unit Capacitor                                | 73 |

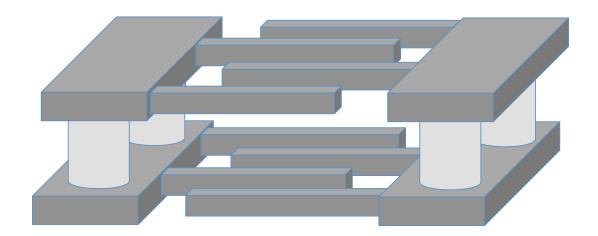

|     |       | 3.3.1.2 2D Capacitor Array                                 | 75  |

|-----|-------|------------------------------------------------------------|-----|

|     | 3.3.2 | VVM Core Architecture                                      | 83  |

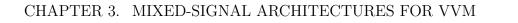

|     | 3.3.3 | Test Chip                                                  | 85  |

| 3.4 | GF2 V | VVM: A 6-bit MAC Processor in 55nm CMOS                    | 90  |

|     | 3.4.1 | Binary Weighted Capacitor Array                            | 91  |

|     | 3.4.2 | VVM Core Architecture                                      | 95  |

|     | 3.4.3 | Test Chip                                                  | 95  |

| 3.5 | GF3 V | VVM: A 4-bit MAC Multicore Processor in 55nm CMOS          | 100 |

|     | 3.5.1 | VVM Core Architecture and Design Improvements              | 101 |

|     | 3.5.2 | Multicore Design and Synthesis                             | 105 |

|     |       | 3.5.2.1 Cell Design                                        | 105 |

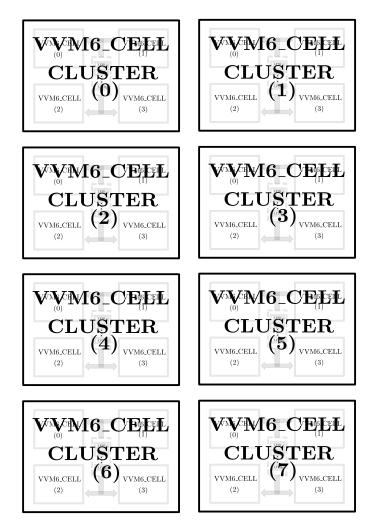

|     |       | 3.5.2.2 VVM Cluster Design                                 | 107 |

|     |       | 3.5.2.3 Top Design                                         | 108 |

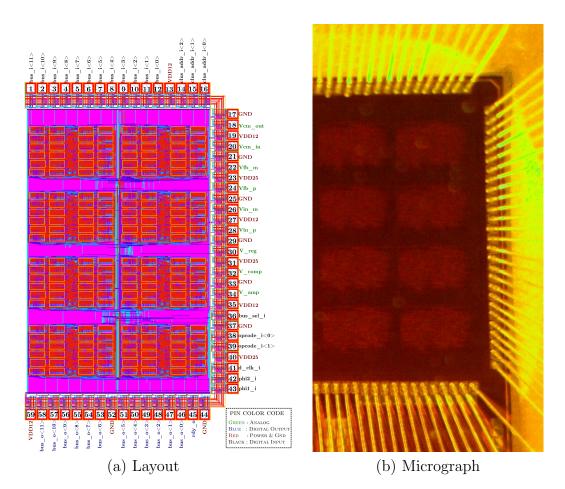

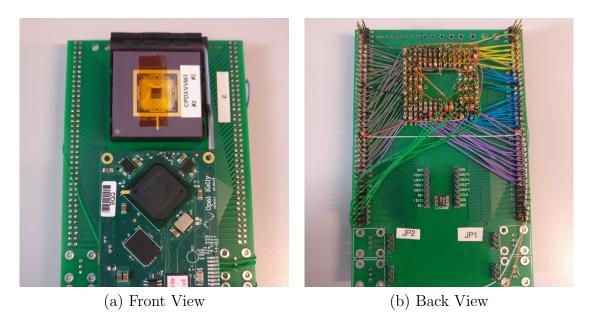

|     | 3.5.3 | Test Chip                                                  | 109 |

|     |       | 3.5.3.1 Chip Interface                                     | 112 |

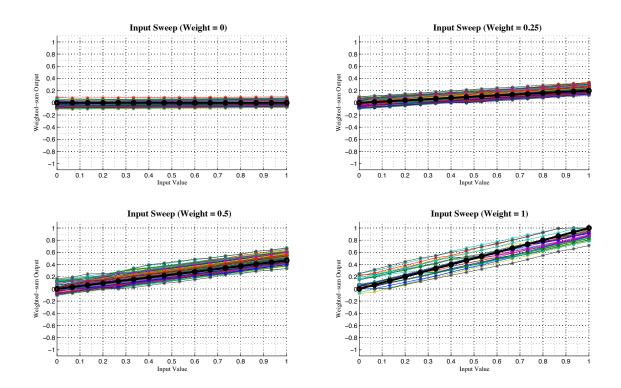

|     |       | 3.5.3.2 Results                                            | 117 |

| 3.6 | GF4 V | VVM: A 4-bit MAC Multicore Processor in 55nm CMOS $\ldots$ | 120 |

|     | 3.6.1 | Series-Parallel Capacitor Array                            | 121 |

|     | 3.6.2 | Core Architecture                                          | 125 |

|     | 3.6.3 | Test Chip                                                  | 128 |

|     |       | 3.6.3.1 Chip Interface                                     | 130 |

|   | 3.7                | GF5 V                                                         | VVM: An 8-bit MAC Multicore Processor in 55nm CMOS $\ .$                                                                                                                              | 136                                                                                      |

|---|--------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

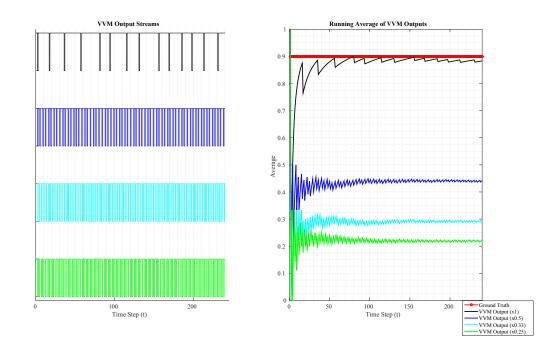

|   |                    | 3.7.1                                                         | Mixed-Signal Stochastic Multiplier                                                                                                                                                    | 137                                                                                      |

|   |                    | 3.7.2                                                         | Core Architecture                                                                                                                                                                     | 140                                                                                      |

|   |                    | 3.7.3                                                         | Test Chip                                                                                                                                                                             | 144                                                                                      |

|   |                    |                                                               | 3.7.3.1 Chip Interface                                                                                                                                                                | 147                                                                                      |

|   |                    |                                                               | 3.7.3.2 Setup                                                                                                                                                                         | 150                                                                                      |

|   |                    |                                                               | 3.7.3.3 Results                                                                                                                                                                       | 151                                                                                      |

|   | 3.8                | Concl                                                         | usion $\ldots$                                                                                       | 157                                                                                      |

|   |                    | 3.8.1                                                         | Design Optimization                                                                                                                                                                   | 158                                                                                      |

|   |                    | 3.8.2                                                         | Comparative Analysis                                                                                                                                                                  | 160                                                                                      |

|   |                    |                                                               |                                                                                                                                                                                       |                                                                                          |

| 4 | A N                | /lixed-                                                       | Signal Successive Approximation Architecture for Energy                                                                                                                               | 7-                                                                                       |

| 4 |                    |                                                               | Signal Successive Approximation Architecture for Energy<br>Fixed Point Arithmetic                                                                                                     | 7-<br>163                                                                                |

| 4 |                    | cient I                                                       |                                                                                                                                                                                       | 163                                                                                      |

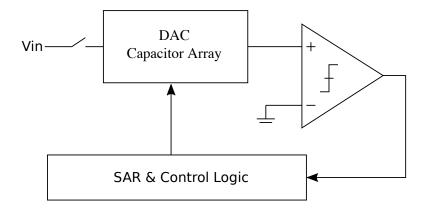

| 4 | Effi               | <b>cient I</b><br>Succe                                       | Fixed Point Arithmetic                                                                                                                                                                | <b>163</b><br>164                                                                        |

| 4 | <b>Effi</b><br>4.1 | <b>cient I</b><br>Succe                                       | Fixed Point Arithmetic                                                                                                                                                                | <b>163</b><br>164<br>167                                                                 |

| 4 | <b>Effi</b><br>4.1 | cient I<br>Succes<br>SA M                                     | Fixed Point Arithmetic<br>ssive Approximation (SA) ADC                                                                                                                                | <b>163</b><br>164<br>167<br>167                                                          |

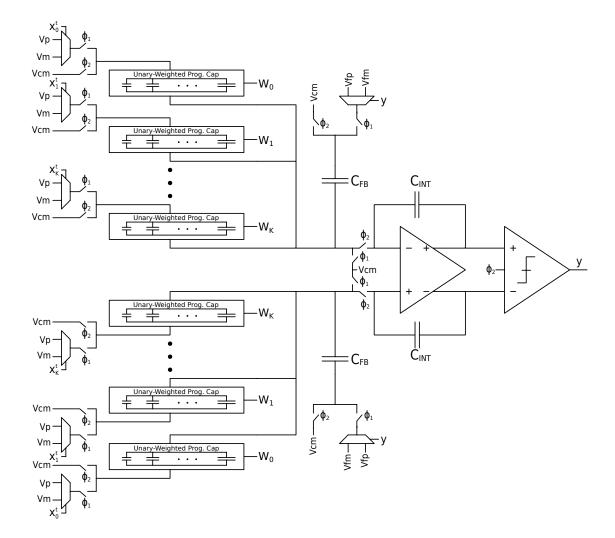

| 4 | <b>Effi</b><br>4.1 | cient I<br>Succes<br>SA M<br>4.2.1                            | Fixed Point Arithmetic         ssive Approximation (SA) ADC         ultiply-Add Architecture         Multiply-Add Operation                                                           | <ul> <li>163</li> <li>164</li> <li>167</li> <li>167</li> <li>168</li> </ul>              |

| 4 | <b>Effi</b><br>4.1 | <b>cient I</b><br>Succes<br>SA M<br>4.2.1<br>4.2.2            | Fixed Point Arithmetic         ssive Approximation (SA) ADC         ultiply-Add Architecture         Multiply-Add Operation         Mixed-Signal Processing Flow                      | <ul> <li>163</li> <li>164</li> <li>167</li> <li>167</li> <li>168</li> <li>171</li> </ul> |

| 4 | <b>Effi</b><br>4.1 | cient I<br>Succes<br>SA M<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | Fixed Point Arithmetic         ssive Approximation (SA) ADC         ultiply-Add Architecture         Multiply-Add Operation         Mixed-Signal Processing Flow         Architecture | <ul> <li>163</li> <li>164</li> <li>167</li> <li>167</li> <li>168</li> <li>171</li> </ul> |

| 5 | Het | erogen | ieous Ch   | ip Multiprocessor Design                               | 186   |

|---|-----|--------|------------|--------------------------------------------------------|-------|

|   | 5.1 | 2.5D I | Nano-Aba   | cus System-on-Chip                                     | 189   |

|   | 5.2 | Proces | ssing Unit | S                                                      | 193   |

|   |     | 5.2.1  | PU VVN     | M: A Mixed-Signal Processor for Fixed-Point Arithmetic | c 193 |

|   |     |        | 5.2.1.1    | Overview                                               | 193   |

|   |     |        | 5.2.1.2    | VVM Core Architecture                                  | 195   |

|   |     |        | 5.2.1.3    | PU VVM Programmability                                 | 197   |

|   |     | 5.2.2  | PU CM      | C: A Computation Memory Controller                     | 199   |

|   |     |        | 5.2.2.1    | Overview                                               | 199   |

|   |     |        | 5.2.2.2    | Processing Flow                                        | 202   |

|   |     | 5.2.3  | PU CAC     | CHE: Auxiliary Memory Unit                             | 204   |

|   |     |        | 5.2.3.1    | Overview                                               | 204   |

|   |     |        | 5.2.3.2    | 2KB Register File Design                               | 206   |

|   |     | 5.2.4  | PU Con     | troller                                                | 211   |

|   |     |        | 5.2.4.1    | Architecture                                           | 212   |

|   |     |        | 5.2.4.2    | PU Core Interface                                      | 219   |

|   |     |        | 5.2.4.3    | L1 Network Interface                                   | 219   |

|   |     |        | 5.2.4.4    | L2 Network Interface                                   | 220   |

|   |     |        | 5.2.4.5    | Configuration                                          | 221   |

|   |     |        | 5.2.4.6    | Applications                                           | 230   |

|   | 5.3 | Netwo  | ork-on-Chi | ip                                                     | 235   |

|       | 5.3.1  | Scalable Bufferless Network                         | 236 |

|-------|--------|-----------------------------------------------------|-----|

|       |        | 5.3.1.1 Router                                      | 238 |

|       |        | 5.3.1.2 Network Protocol                            | 242 |

|       | 5.3.2  | Network Simulator                                   | 244 |

| 5.4   | PAD I  | /O Circuitry                                        | 249 |

|       | 5.4.1  | MHUB I/O Pads                                       | 251 |

|       | 5.4.2  | FPGA I/O Pads                                       | 255 |

|       | 5.4.3  | Power/Analog Pads                                   | 258 |

| 5.5   | The Y  | upana CMP: A Heterogeneous Mixed-Signal Accelerator | 259 |

|       | 5.5.1  | Overview                                            | 259 |

|       | 5.5.2  | Applications                                        | 261 |

|       |        | 5.5.2.1 Wide Area Motion Imagery                    | 262 |

|       |        | 5.5.2.2 Deep Convolutional Neural Networks          | 267 |

| 5.6   | Conclu | usion                                               | 271 |

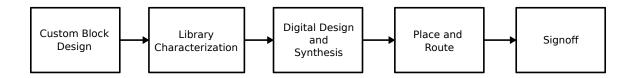

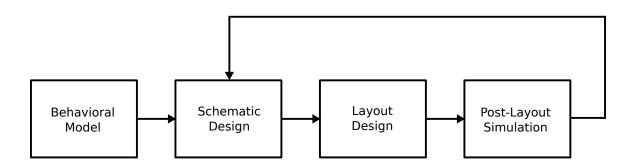

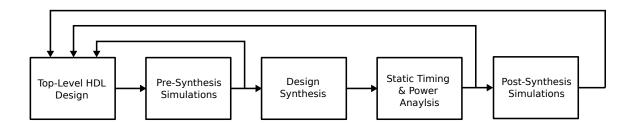

| Appen | dix A  | Mixed-Signal ASIC Design Flow                       | 274 |

| A.1   | Custor | m Block Design                                      | 275 |

| A.2   | Librar | y Characterization                                  | 277 |

|       | A.2.1  | Behavioral Model Description (HDL)                  | 278 |

|       | A.2.2  | Physical Abstract Description (LEF)                 | 278 |

|       | A.2.3  | Timing Description (LIB)                            | 279 |

|       | A.2.4  | Layout Description (GDS)                            | 280 |

|       |        |                                                     |     |

| Bibliography |                              |     |  |  |

|--------------|------------------------------|-----|--|--|

| A.5          | Signoff                      | 284 |  |  |

| A.4          | Place and Route              | 282 |  |  |

| A.3          | Digital Design and Synthesis | 280 |  |  |

Vita

305

# List of Tables

| 2.1  | DBN Experimental Results                                             | 30  |

|------|----------------------------------------------------------------------|-----|

| 2.2  | Parameters for Stauffer et al. Image Segmentation Algorithm          | 34  |

| 2.3  | Image Segmentation Architecture Macro Synthesis                      | 41  |

| 2.4  | Synthesis Results for Stochastic and Deterministic Implementation of |     |

|      | a Image Segmentation Methods                                         | 44  |

| 3.1  | Analog Biases for the VVM Core                                       | 85  |

| 3.2  | Summary of the ADC Characteristics for GF1 VVM                       | 85  |

| 3.3  | Digital I/O Ports for the GF1 VVM Chip                               | 88  |

| 3.4  | Measured Characteristics of the VVM Core                             | 90  |

| 3.5  | Digital I/O Ports for the GF2 VVM Chip                               | 99  |

| 3.6  | Measured Characteristics of the GF2 VVM Core                         | 100 |

| 3.7  | Nominal Bias Values for the GF3 VVM Core                             | 103 |

| 3.8  | Simulated Characteristics of the GF3 VVM Core                        | 104 |

| 3.9  | GF3 VVM Cell Output Table                                            | 107 |

| 3.10 | I/O and Power Ports for the GF3 VVM Chip                             | 111 |

| 3.11 | Nominal Bias Values for the GF4 VVM Core                             | 128 |

| 3.12 | Simulated Characteristics of the GF4 VVM Core                        | 128 |

|      | I/O and Power Ports for the GF4 VVM Chip                             | 130 |

| 3.14 | Instruction Set for GF4 VVM Test Chip                                | 131 |

| 3.15 | Feedback Capacitance Select Mapping for the GF4 VVM Design           | 132 |

|      | Output Precision Select Mapping for the GF4 VVM Design               | 133 |

|      | I/O Ports and Pin Mapping for the GF5 VVM                            | 146 |

|      | Nominal Bias Values for GF5 VVM                                      | 149 |

|      | Instruction Set for GF5 VVM                                          | 149 |

| 3.20 | Measured Characteristics of GF5 VVM                                  | 156 |

| 3.21 | Design Specification and Characteristic of the Synthesized DSP for   |     |

|      | 4-bit MAC and the GF VVM Core                                        | 161 |

| 3.22 | Design Specification and Characteristic of the Synthesized DSP for   |     |

|      | 8-bit MAC and the GF VVM Core                                        | 162 |

### LIST OF TABLES

| 4.1  | Unsigned Binary Multiplication                              | 167 |

|------|-------------------------------------------------------------|-----|

| 4.2  | Simulated Characteristic of the SA Mulitply-Add Single Core | 177 |

| 4.3  | Table of Pins for the 16nm FinFET Test Chip                 | 185 |

| 5.1  |                                                             | 194 |

| 5.2  | Simulated Characteristics of the PU CMC                     | 200 |

| 5.3  | Simulated Characteristics of the PU CACHE                   | 206 |

| 5.4  | Instruction Set for the PU Controller                       | 215 |

| 5.5  | Registers for the PU Controller                             | 216 |

| 5.6  | PU I/O Ports to the PU Controller                           | 219 |

| 5.7  | L1 I/O Ports to the PU Controller                           | 220 |

| 5.8  | L2 I/O Ports to the PU Controller                           | 221 |

| 5.9  | Configuration Packet for the PU Controller                  | 222 |

| 5.10 | Instruction Word for the PU Controller                      | 222 |

| 5.11 | Acknowledge Word for the PU Controller                      | 222 |

| 5.12 | Truth Table for the FPGA I/O Pad Circuit                    | 256 |

|      |                                                             |     |

# List of Figures

| 1.1  | Levels of Abstraction for System Design of a Chip Multiprocessor 3                                               |

|------|------------------------------------------------------------------------------------------------------------------|

| 2.1  | Four Types of Signal Representation                                                                              |

| 2.2  | Examples of Binary and Unary Encoding                                                                            |

| 2.3  | Stochastic Number Encoding                                                                                       |

| 2.4  | Stochastic Operations                                                                                            |

| 2.5  | Stochastic Number Decoding                                                                                       |

| 2.6  | Stochastic Encoder, Logic, and Decoder                                                                           |

| 2.7  | Stochastic Number Precision                                                                                      |

| 2.8  | A 2 Hidden Layer Deep Belief Network                                                                             |

| 2.9  | DBN Activation Function                                                                                          |

| 2.10 | DBN Node Architecture                                                                                            |

| 2.11 | Kintex FPGA board                                                                                                |

| 2.12 | DBN Classification Accuracy Plot                                                                                 |

| 2.13 | DBN Mean Absolute Error Plot                                                                                     |

| 2.14 | Block Diagram of the Unimodal Background Modeling Method 38                                                      |

| 2.15 | Image Segmentation Architecture with Stochastic Logic 40                                                         |

| 2.16 | Background Modeling and Subtraction with 8-bit Stochastic Compu-                                                 |

|      | tation Precision $\ldots \ldots 41$ |

| 2.17 | Background Modeling and Subtraction with 12-bit Stochastic Compu-                                                |

|      | tation Precision $\ldots \ldots 42$ |

| 2.18 | Energy Cost per Operation Comparison between Stochastic and De-                                                  |

|      | terministic Implementation                                                                                       |

| 3.1  | Mixed-Signal 1-bit Multiplier for Unsigned Products                                                              |

| 3.2  | Mixed-Signal Scalar Multiplier                                                                                   |

| 3.3  | Mixed-Signal Vector-Vector Multiplier                                                                            |

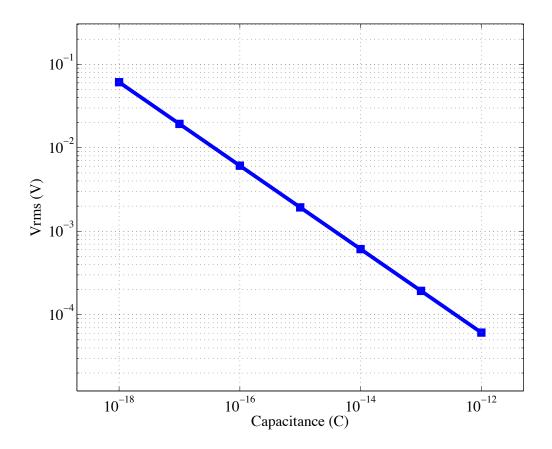

| 3.4  | Root Mean Square Thermal Noise in a Capacitor                                                                    |

| 3.5  | First-Order $\Sigma\Delta$ Modulator Block Diagram                                                               |

| 3.6  | First-Order $\Sigma\Delta$ Modulator Z-Model Block Diagram                                                       |

| 3.7  | Single-Ended Switched-Capacitor $\Sigma\Delta$ Modulator Circuit       | 61  |

|------|------------------------------------------------------------------------|-----|

| 3.8  | Fully-Differential Switched-Capacitor $\Sigma\Delta$ Modulator Circuit | 64  |

| 3.9  | Fully-Differential Operational Amplifier Circuit                       | 68  |

| 3.10 | Switched-Capacitor Common-Mode Feedback Circuit                        | 69  |

| 3.11 | Low-Voltage Comparator Circuit                                         | 71  |

| 3.12 | Low-Voltage Latch Circuit                                              | 72  |

| 3.13 | A Vertical Natural Capacitor (VNCAP)                                   | 74  |

| 3.14 | Row Slice of the Programmable Capacitor Array for GF1 VVM $\ldots$     | 75  |

| 3.15 | Subtractor Circuit for a Magnitude Comparator                          | 76  |

| 3.16 | A Partial Full Adder Circuit for the Magnitude Comparator              | 77  |

| 3.17 | Simplified Carry Out Circuit for the Magnitude Comparator              | 77  |

| 3.18 | Layout of a Generic Row Slice for the Capacitor Array in a 65nm        |     |

|      | CMOS Process                                                           | 79  |

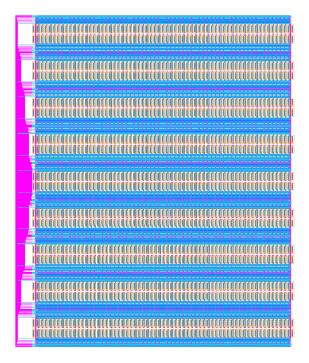

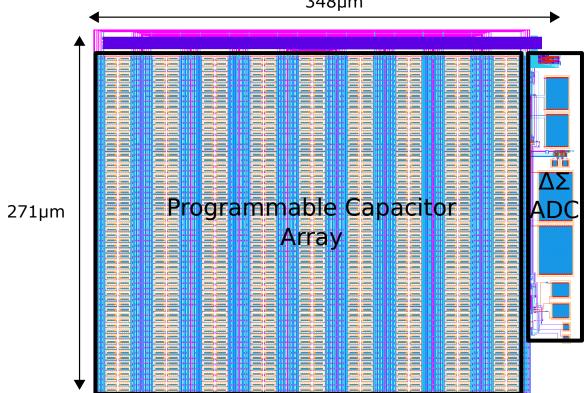

| 3.19 | Layout for the 2D Capacitor Array for GF1 VVM                          | 79  |

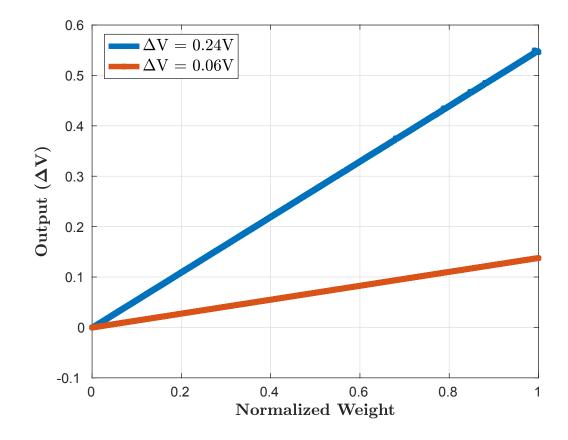

| 3.20 | Transfer Curve Plots of the Weight (Capacitance) to Output (Voltage)   |     |

|      | for the VVM $\ldots$                                                   | 81  |

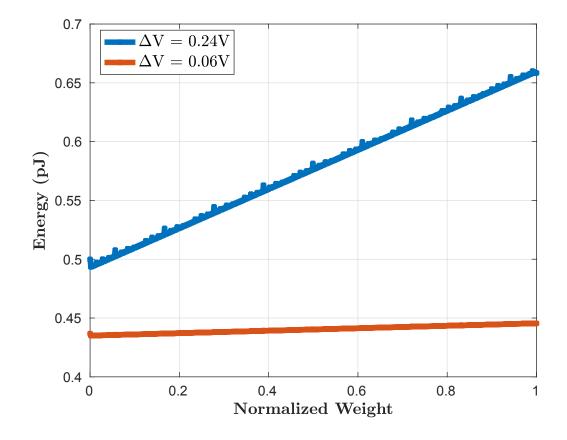

| 3.21 | Plots of Energy Cost for the Capacitor Array with Different Weights    |     |

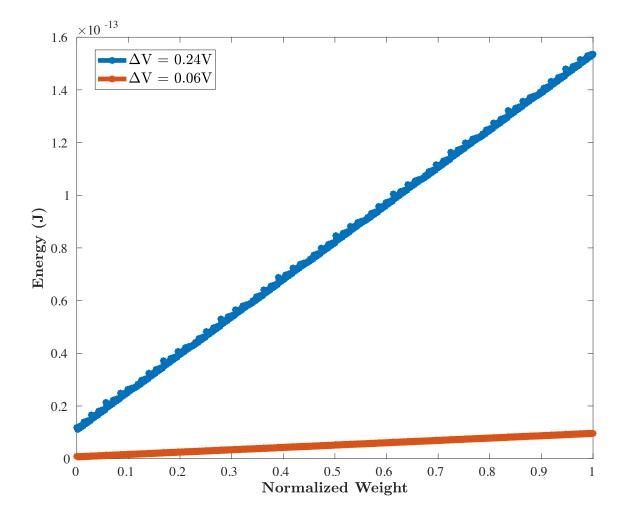

|      | and Input Voltage                                                      | 82  |

| 3.22 | GF1 VVM Core Architecture                                              | 84  |

|      | Layout of the GF1 VVM Core Architecture                                | 86  |

| 3.24 | Layout of the GF1 VVM Chip                                             | 87  |

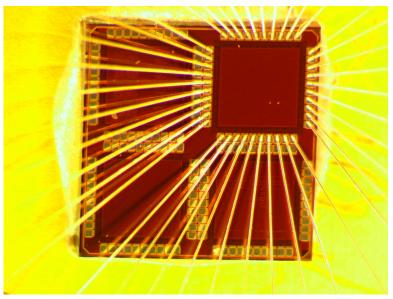

|      | GF1 VVM Chip Micrograph and Test Setup                                 | 89  |

| 3.26 | DeBayering an Image Using the VVM Core                                 | 90  |

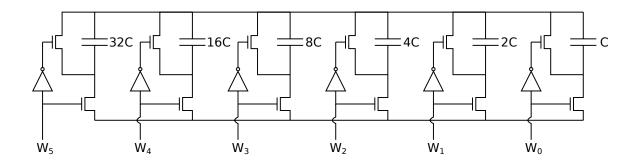

|      | Row Slice of the Programmable Capacitor Array for GF2 VVM $\ldots$     | 91  |

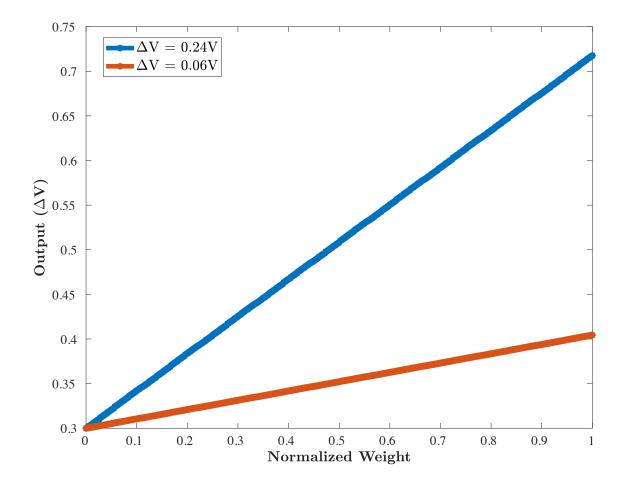

|      | Layout for the Binary-Weighted Capacitor Array for GF2 VVM $\ldots$    | 92  |

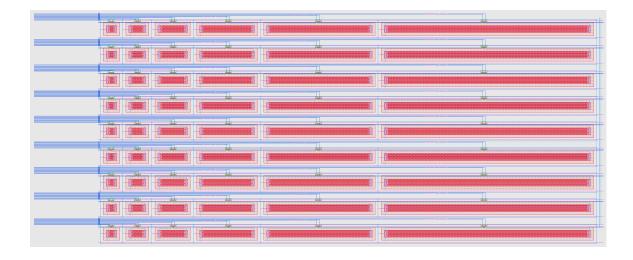

| 3.29 | Transfer Curve Plots of the Weight (Capacitance) to Output (Voltage)   |     |

|      | for the GF2 VVM                                                        | 93  |

| 3.30 | Plots of Energy Cost for the Capacitor Array with Different Weights    |     |

|      | and Input Voltage for the GF2 VVM                                      | 94  |

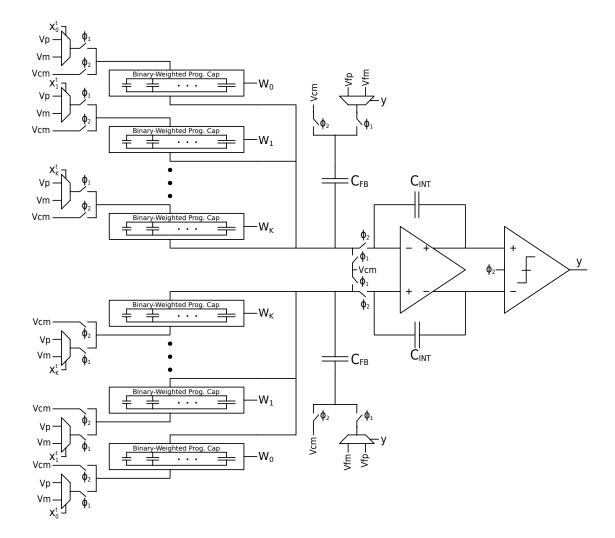

|      | GF2 VVM Core Architecture                                              | 96  |

|      | Layout of the GF2 VVM Core Architecture                                | 97  |

|      | Design Comparison of the GF1 VVM Core and the GF2 VVM Core .           | 97  |

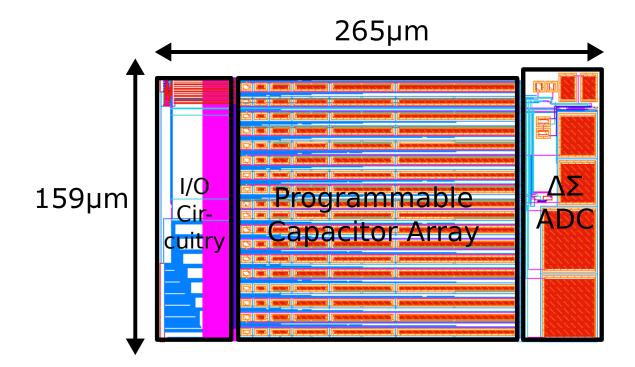

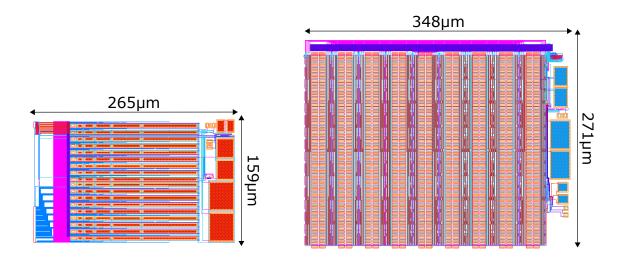

|      | Layout of the GF2 VVM Chip                                             | 98  |

|      | GF2 VVM Chip Micrograph                                                | 98  |

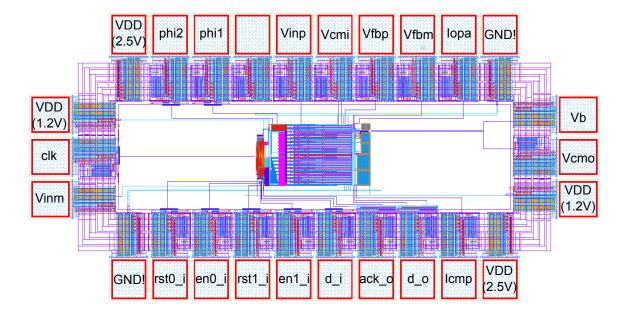

|      | 3D View of a Two-Layered APMOM Capacitor                               | 101 |

|      | Layout of the Unit Capacitor in the GF3 VVM Core                       | 102 |

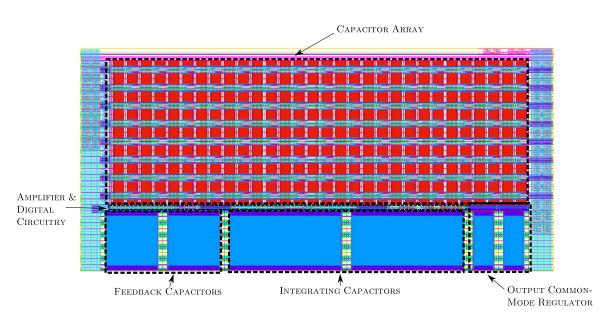

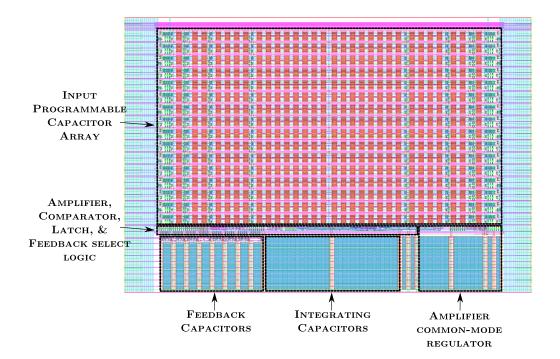

|      | Annotated Layout of the GF3 VVM Core                                   | 102 |

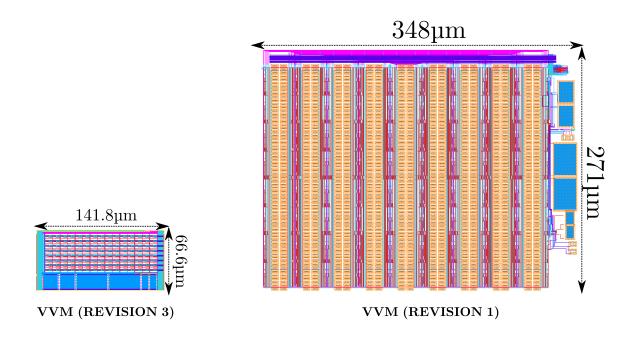

|      | Design Comparison of the GF1 VVM Core and the GF3 VVM Core .           | 103 |

|      | Block Diagram of the GF3 VVM Cell Design                               | 106 |

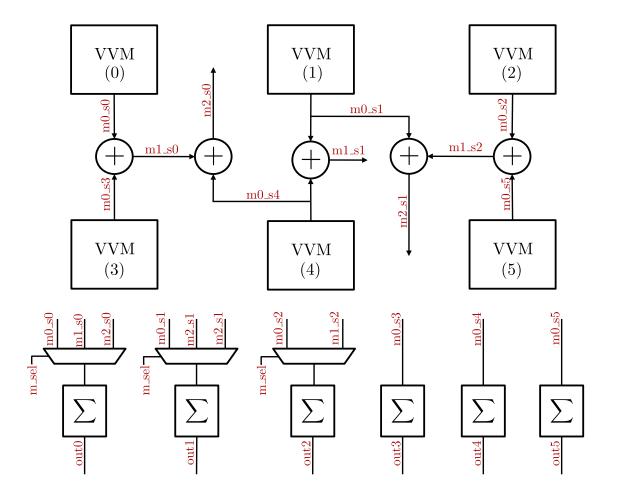

|      | Block Diagram of the GF3 VVM Cluster Design                            | 107 |

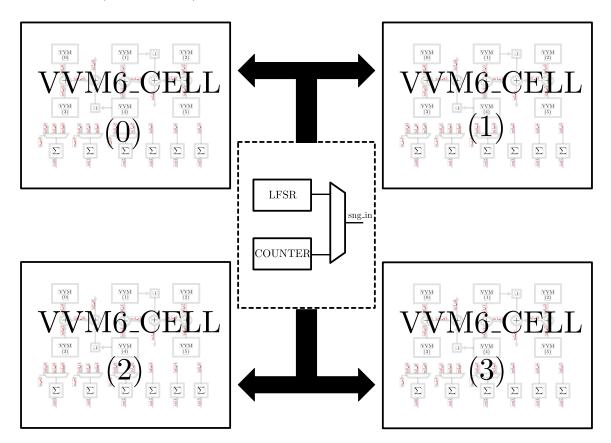

|      | Block Diagram of the GF3 VVM Top Design                                | 109 |

| 3.43 | Annotated Layout and Micrograph of the GF3 VVM Chip                    | 110 |

| 3.44       | GF3 VVM Chip Test Setup                                                  | 112        |

|------------|--------------------------------------------------------------------------|------------|

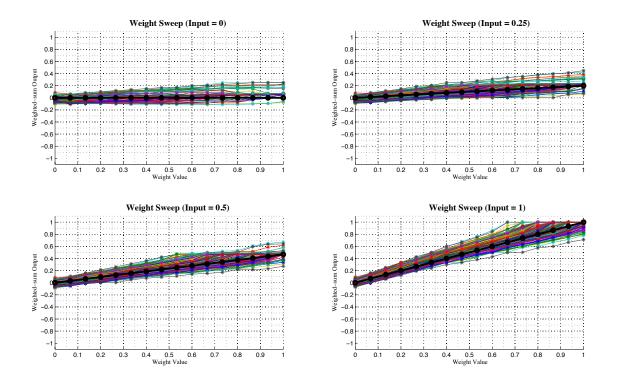

| 3.45       | Input Sweep for Fixed Weights for the 192 GF3 VVM Cores from a           |            |

|            | Test Chip                                                                | 117        |

| 3.46       | Weight Sweep for Fixed Inputs for the 192 GF3 VVM Cores in a Test        |            |

|            | Chip                                                                     | 118        |

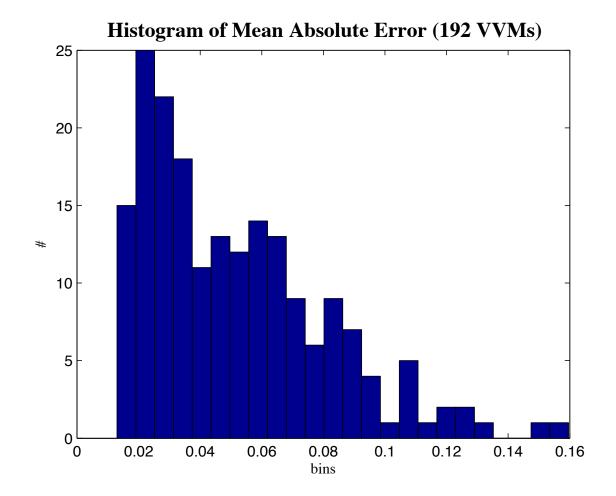

| 3.47       | A Histogram Plot of the Mean Absolute Error from the 192 GF3 VVM         |            |

|            | Cores                                                                    | 119        |

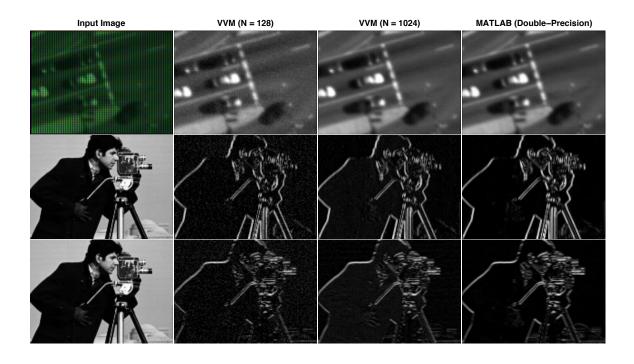

| 3.48       | Image DeBayering through MATLAB and the GF3 VVM Test Chip .              | 120        |

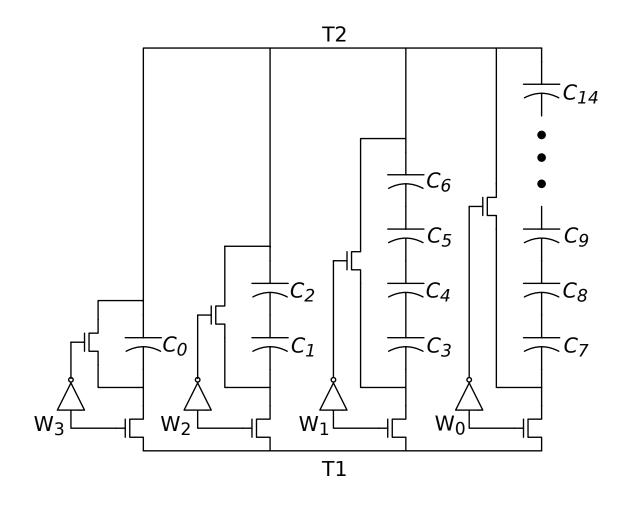

| 3.49       | Circuit of the 4-bit Programmable Capacitor for the GF4 VVM              | 123        |

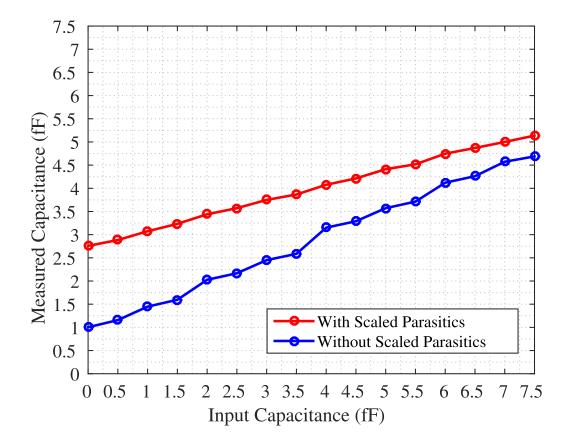

| 3.50       | Transfer Curve of the Programmable Capacitor for GF4 VVM                 | 124        |

| 3.51       | Layout of the 4-bit Programmable Capacitor for the GF4 VVM $\ldots$      | 125        |

| 3.52       | Annotated Layout of the GF4 VVM Core                                     | 126        |

| 3.53       | The GF4 VVM Core Output with Different Output Scaling                    | 127        |

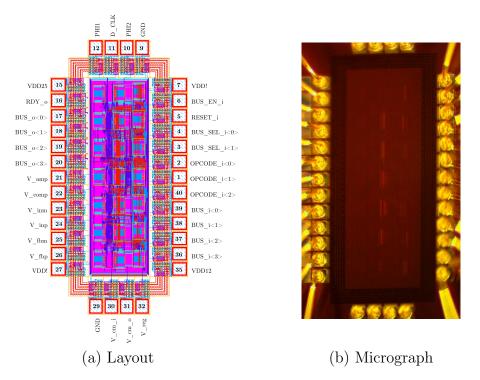

| 3.54       | Layout and Micrograph of the GF4 VVM Test Chip                           | 129        |

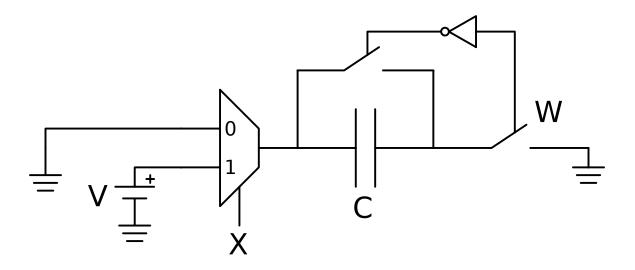

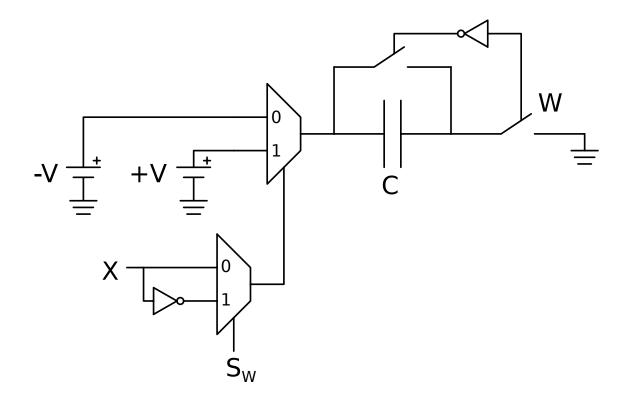

| 3.55       | Mixed-Signal 1-bit Multiplier for Signed Products                        | 138        |

| 3.56       | Layout of the Mixed-Signal 1-bit Multiplier for Signed Products          | 139        |

| 3.57       | Block Diagram of the GF5 VVM Core                                        | 140        |

| 3.58       | GF5 VVM Core Architecture                                                | 142        |

| 3.59       | Layout of the GF5 VVM Core Architecture                                  | 143        |

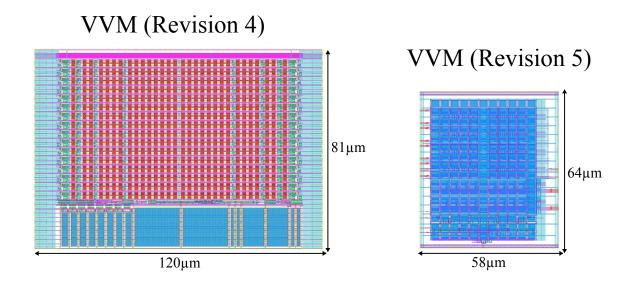

| 3.60       | Layout Comparison of the GF4 VVM Core and the GF5 VVM Core .             | 144        |

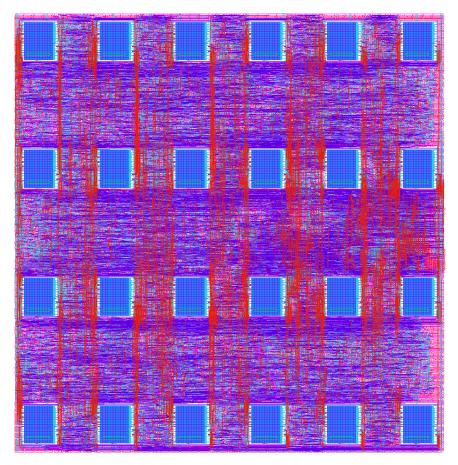

| 3.61       | Layout of the GF5 VVM Multicore Design                                   | 145        |

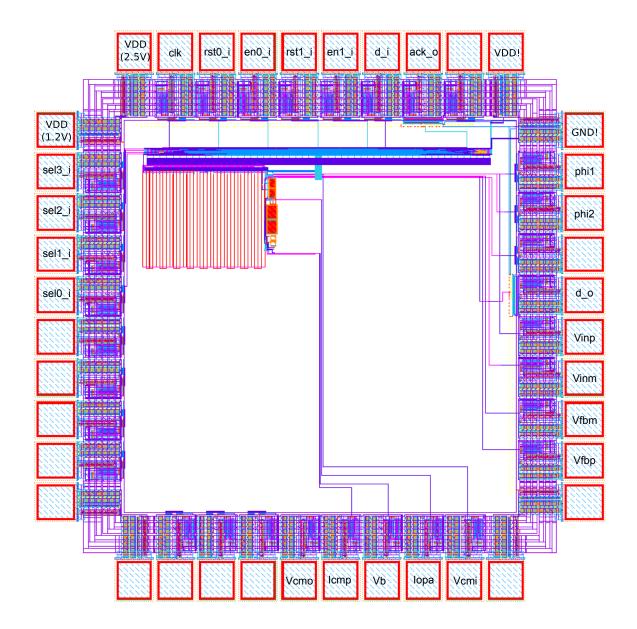

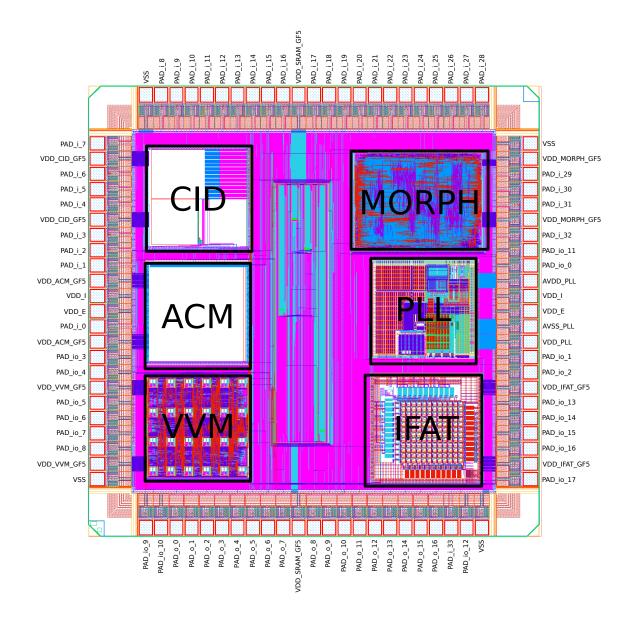

| 3.62       | Annotated Layout of the GF5 Test Chip                                    | 148        |

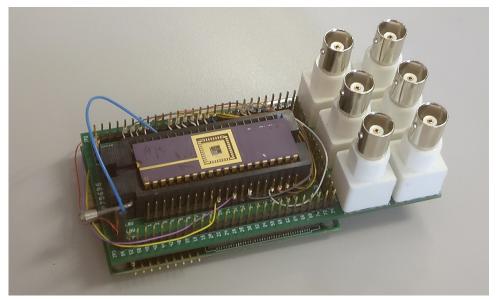

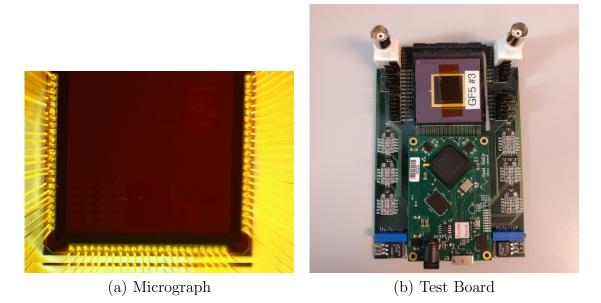

| 3.63       | Chip Micrograph and Test Board for the GF5 Test Chip                     | 151        |

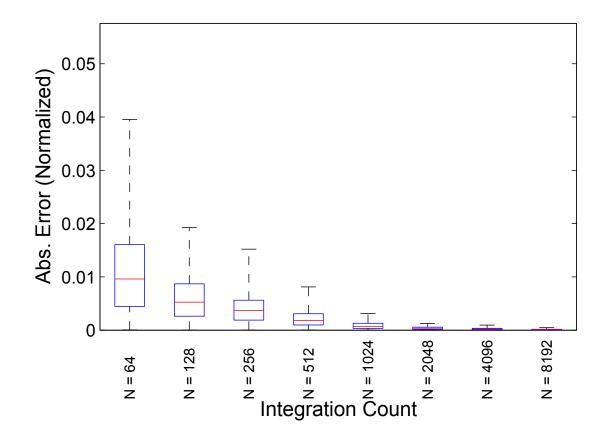

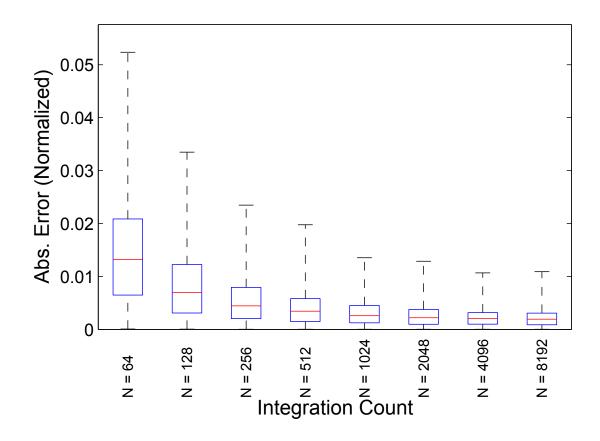

| 3.64       | Absolute Error Box Plot from a GF5 VVM Core Emulated on the FPG.         | A152       |

| 3.65       | Absolute Error Box Plot from a GF5 VVM Core on the Chip                  | 153        |

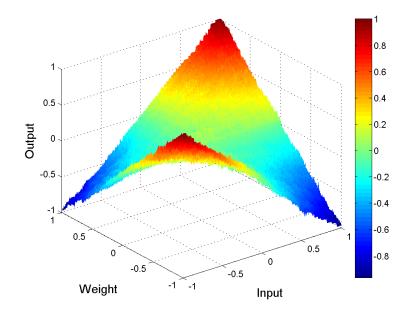

| 3.66       | Surface Plot from a GF5 VVM Core Processing with an Integration          |            |

|            | Count of 64                                                              | 154        |

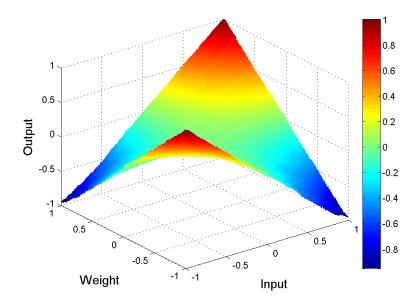

| 3.67       | Surface Plot from a GF5 VVM Core Processing with an Integration          |            |

|            | Count of 256                                                             | 154        |

| 3.68       | Montage of Image Processing Results Using the GF5 VVM Cores at           |            |

|            | Different Precision                                                      | 155        |

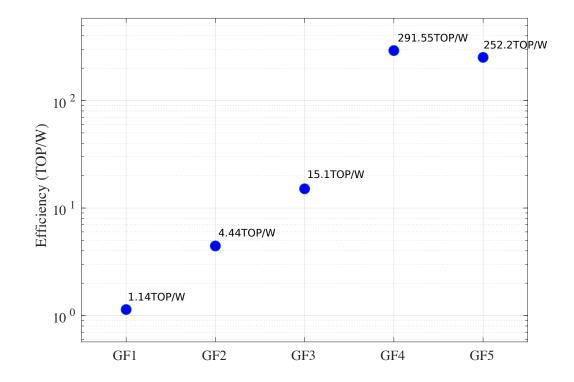

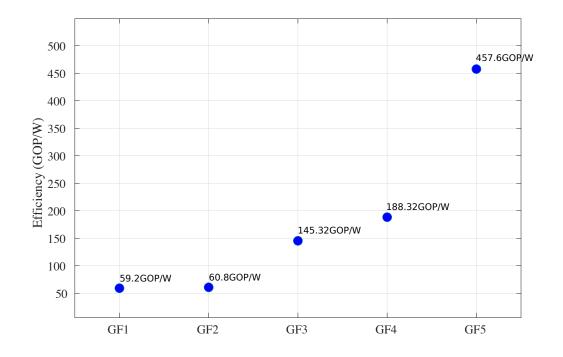

| 3.69       | Computation Efficiency in the Analog Domain Across VVM Designs .         | 159        |

| 3.70       | Computation Efficiency Across VVM Designs                                | 160        |

| 11         | Successive Approximation ADC Black Diamon                                | 165        |

| 4.1        | Successive Approximation ADC Block Diagram                               | 165        |

| 4.2        | Processing flow for SA Architecture                                      | 168<br>172 |

| 4.3        | SA Architecture for Multiply-Add Operations                              | 172        |

| 4.4<br>4.5 | Programmable Capacitor Array for SA Architecture                         | 173<br>172 |

| 4.5<br>4.6 | Dynamic Comparator and Latch for the SA Architecture                     | 173        |

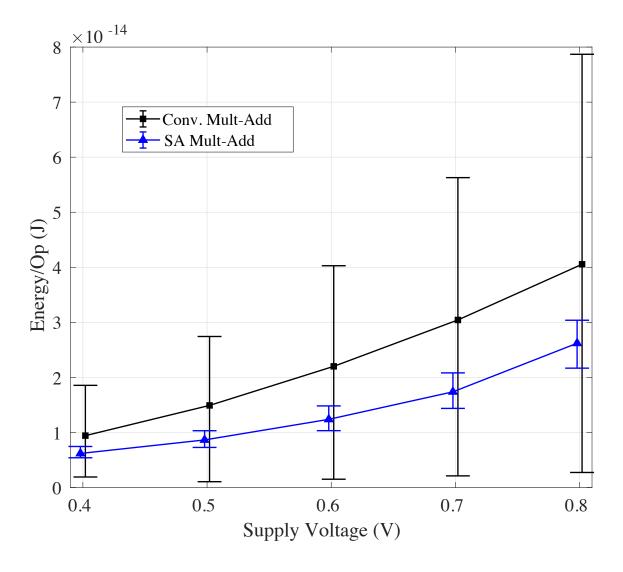

| 4.6        | Energy Plot across Different Supply Voltages for the Different Multiply- | 175        |

|            | Add Designs                                                              | 175        |

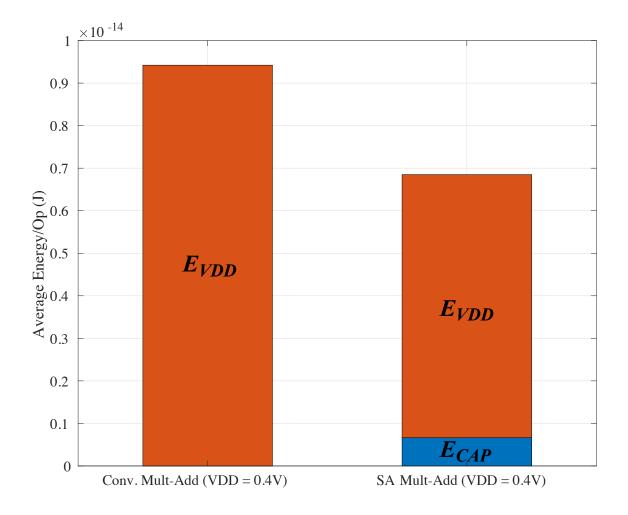

| 4.7  | Energy Comparison for the Different Multiply-Add Designs at 0.4V       |     |

|------|------------------------------------------------------------------------|-----|

|      | Supply Voltage                                                         | 176 |

| 4.8  | Layout of the Unit Cell of the DAC for the SA Multiply-Add Core        | 178 |

| 4.9  | Layout of the Dynamic Comparator and Latch for the SA Multiply-        |     |

|      | Add Core                                                               | 179 |

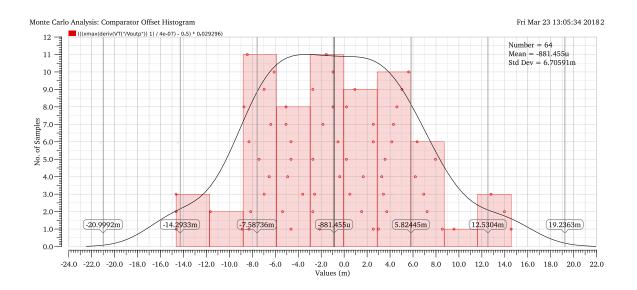

| 4.10 | Histogram Plot of the Comparator Offset with Fabrication Variation .   | 180 |

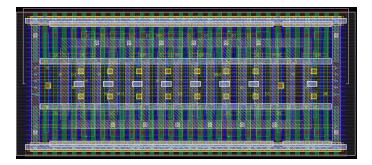

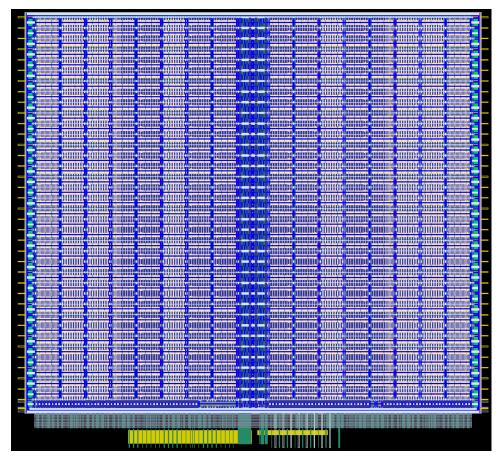

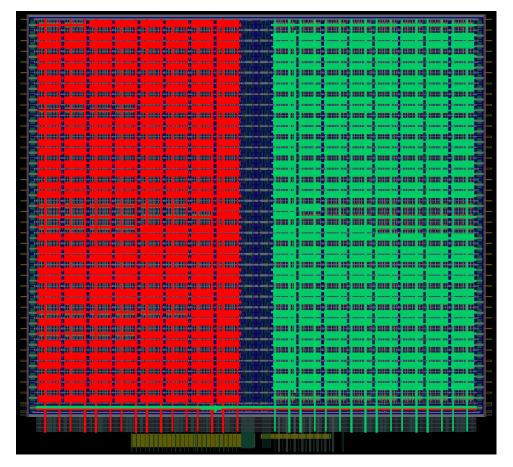

| 4.11 | Layout of the SA Multiply-Add Core without SAR Decoding Logic .        | 181 |

| 4.12 | Layout View of the SA Multiply-Add Core with the Active Capacitors     |     |

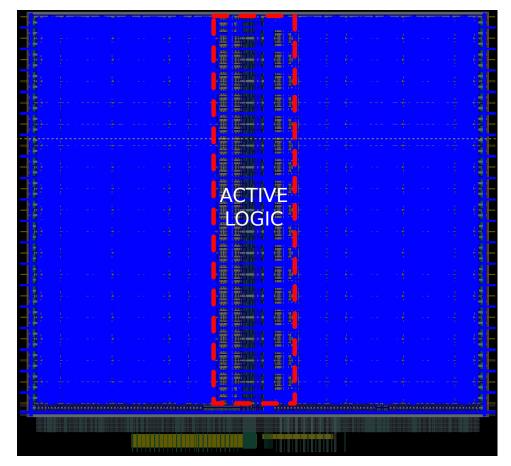

|      | Highlighted                                                            | 182 |

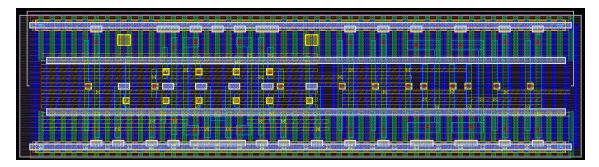

| 4.13 | Layout View of the SA Multiply-Add Core with the Inactive Logic        |     |

|      | Highlighted                                                            | 183 |

| 4.14 | Annotated Layout of the 16nm FinFET Test Chip                          | 184 |

|      |                                                                        | 100 |

| 5.1  | 3D View of the 2.5D Nano-Abacus System-on-Chip Design                  | 190 |

| 5.2  | Top View of the 2.5D System-on-Chip Design                             | 191 |

| 5.3  | Modular Framework for the CMP Design                                   | 192 |

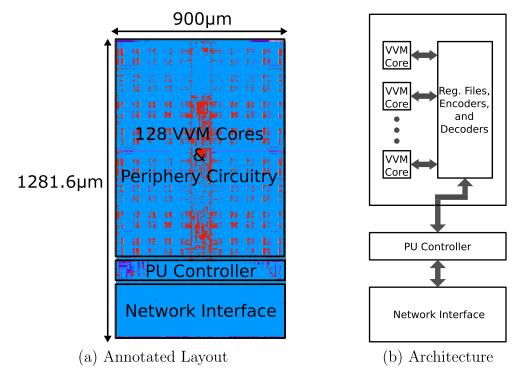

| 5.4  | Annotated Layout and Architecture of the PU VVM                        | 195 |

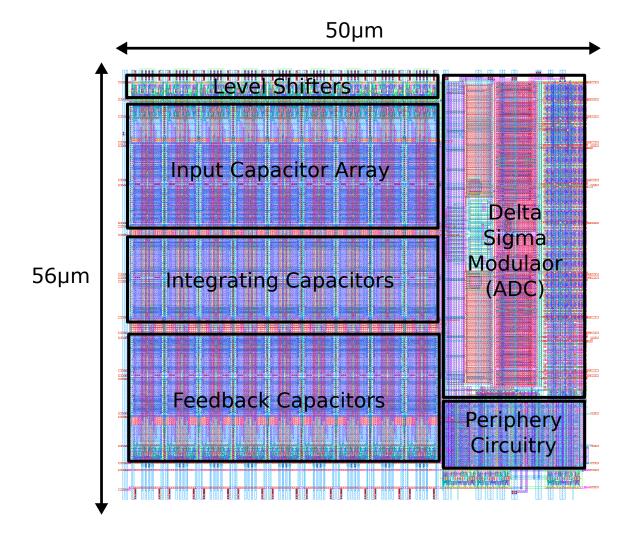

| 5.5  | Annotated Layout of the PU VVM Core Design                             | 196 |

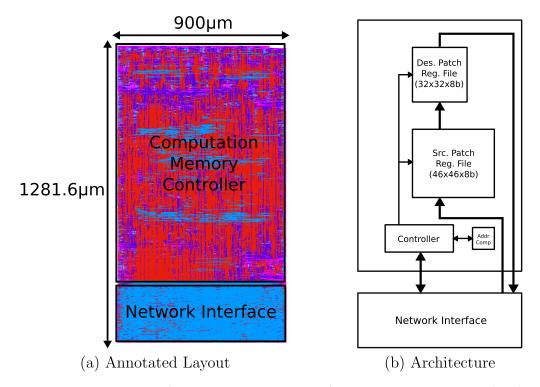

| 5.6  | Annotated Layout and Architecture of the PU CMC                        | 200 |

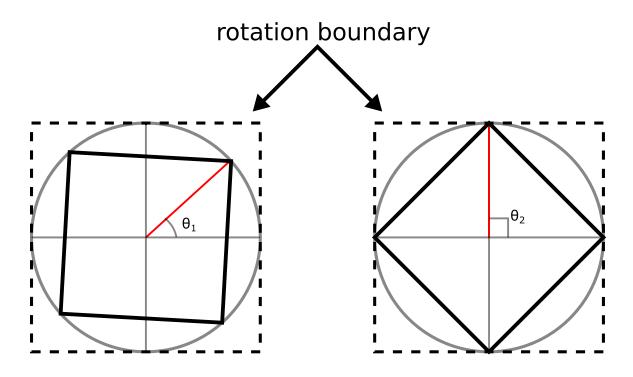

| 5.7  | Rotational Boundary for Points Enclosed in the Unit Circle             | 201 |

| 5.8  | Image DeWarping Using the PU CMC                                       | 201 |

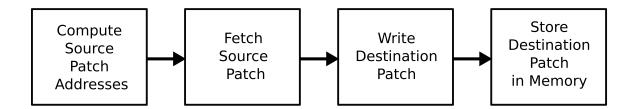

| 5.9  | Processing Flow for the PU CMC                                         | 202 |

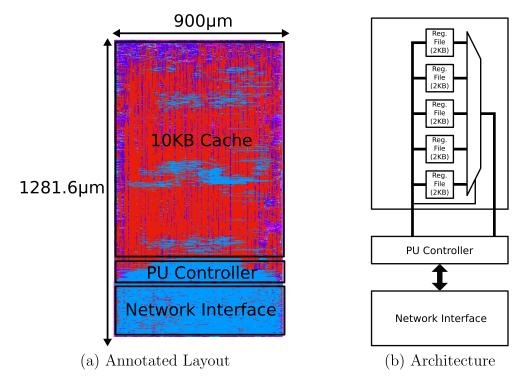

| 5.10 | Annotated Layout and Architecture of the PU CACHE                      | 205 |

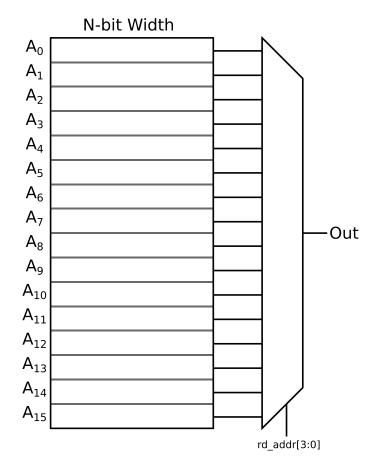

|      | Output Decoder for a 16 Row N-bit Width Register File                  | 207 |

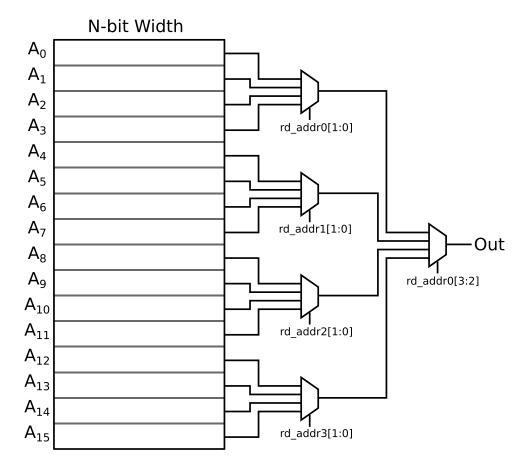

| 5.12 | Output Decoder for a 16 Row N-bit Width Register File with Read        |     |

|      | Address Duplication                                                    | 208 |

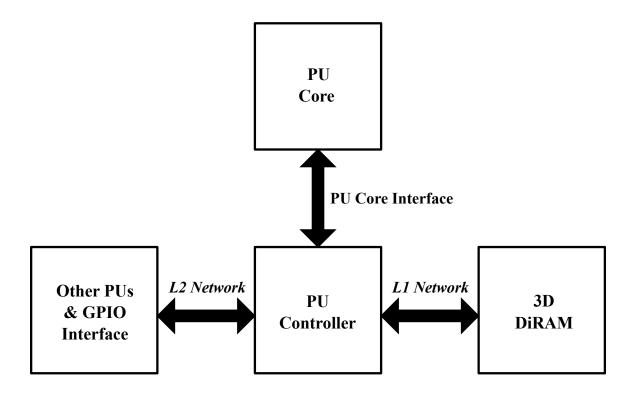

|      | Block diagram of the PU Controller Interface                           | 212 |

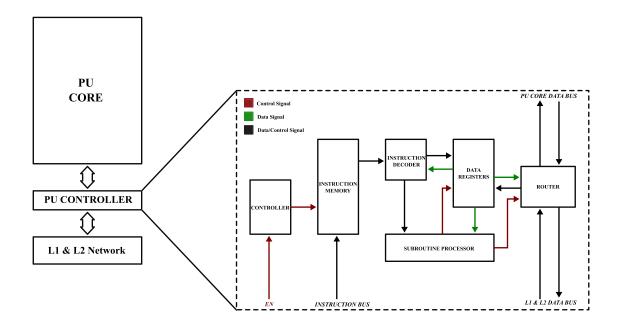

|      | PU Controller Architecture                                             | 213 |

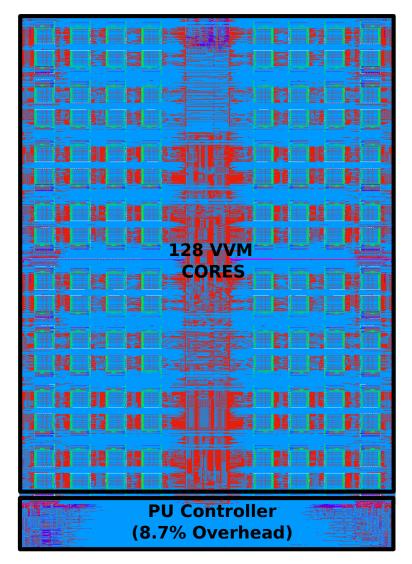

|      | Layout of the PU VVM with the PU Controller                            | 214 |

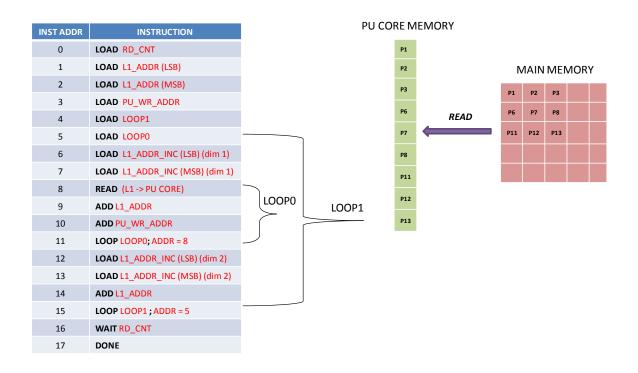

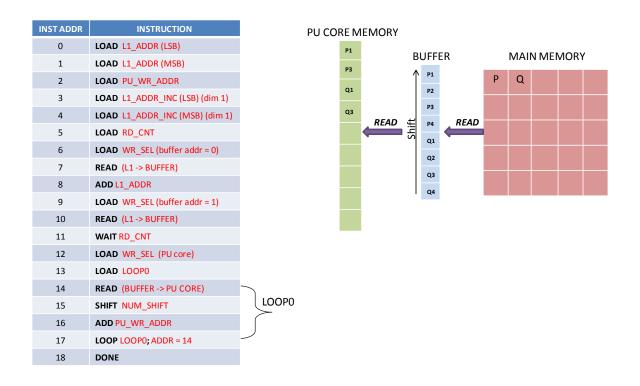

|      | 2D Read From Main Memory to the PU Core                                | 231 |

|      | 1D Read with Byte Shifts From Main Memory to the PU Core               | 232 |

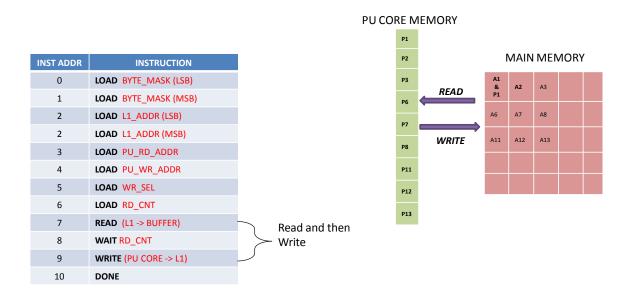

| 5.18 | Read Modify Write From the PU Core to the Main Memory                  | 233 |

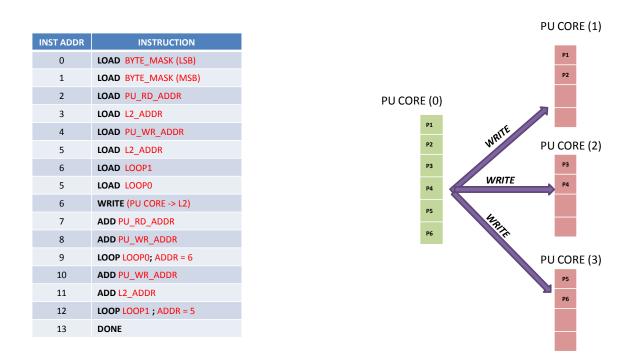

|      | 1D Write From the PU Core to 3 Other PU                                | 234 |

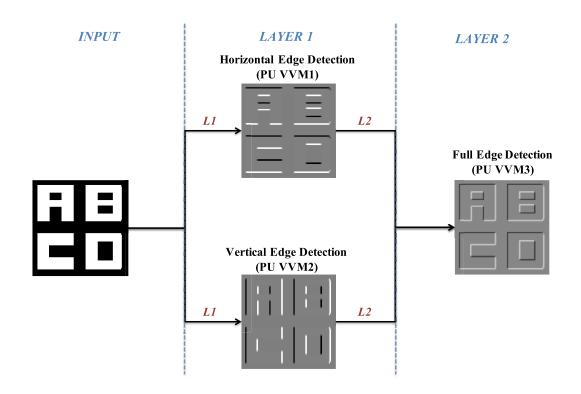

| 5.20 | Processing Flow for Image Edge Detection with 3 PU VVMs                | 235 |

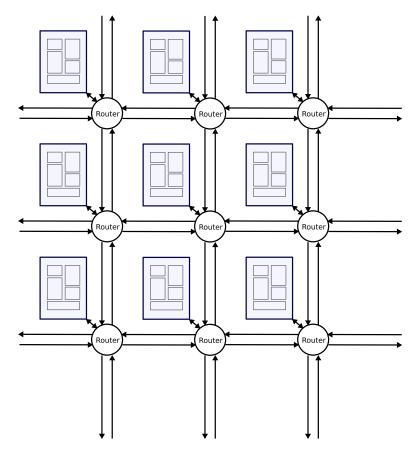

| 5.21 | A 3 by 3 Mesh Network Comprised of Homogeneous Nodes                   | 237 |

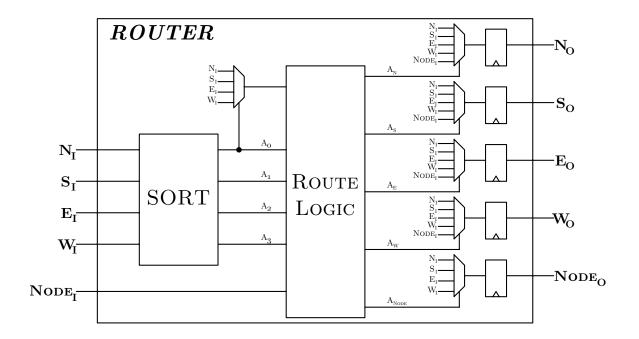

| 5.22 | Architecture of the Bufferless Router in the Mesh Network              | 239 |

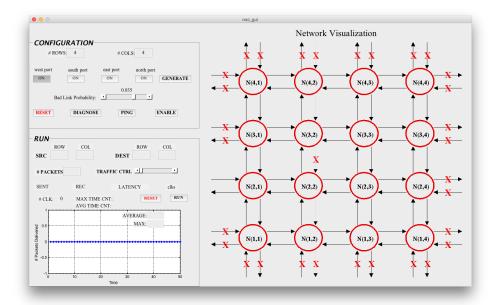

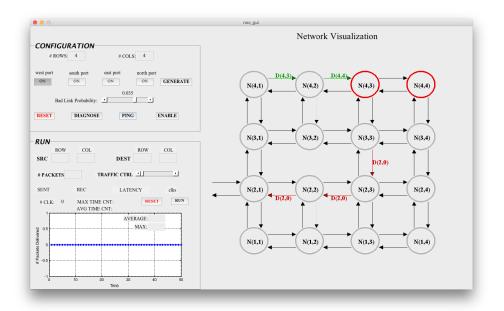

| 5.23 | Visualization of a 4 by 4 Mesh Network During the RESET Phase          | 245 |

| 5.24 | Visualization of a 4 by 4 Mesh Network During the DIAGNOSE Phase       | 245 |

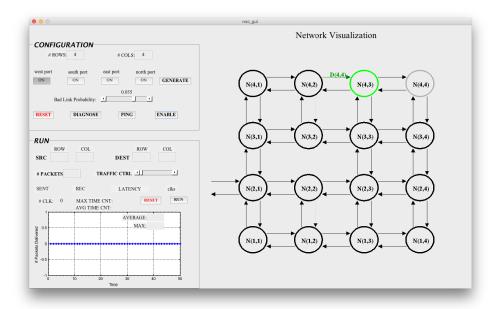

| 5.25 | Visualization of a 4 by 4 Mesh Network During the PING Phase           | 246 |

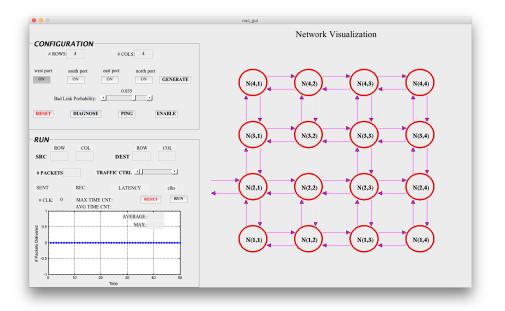

| 5.26 | Visualization of a 4 by 4 Mesh Network During the ENABLE Phase .       | 247 |

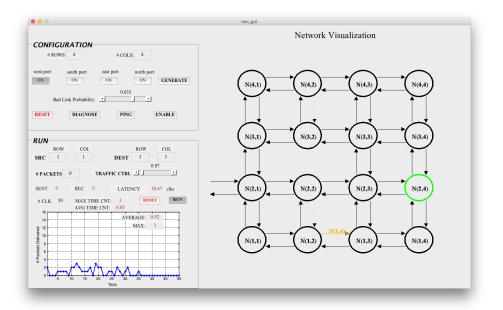

| 5.27 | Visualization of a 4 by 4 Mesh Network Running with Light Data Traffic | 248 |

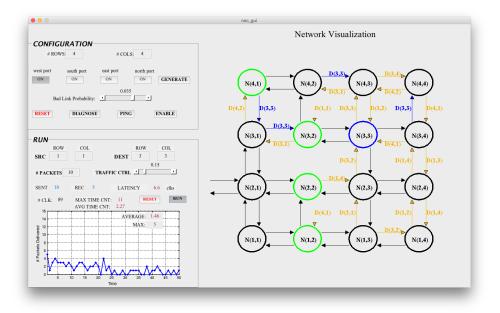

|      | Visualization of a 4 by 4 Mesh Network Running with Heavy Data Traffic |     |

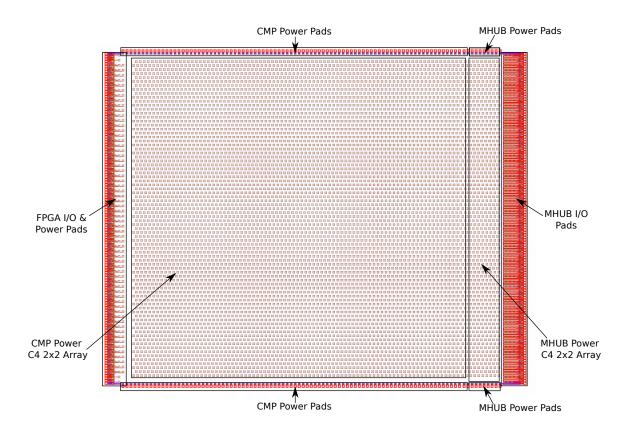

| 5.29 | Annotated Layout of the CMP Pad Frame                                | 250  |

|------|----------------------------------------------------------------------|------|

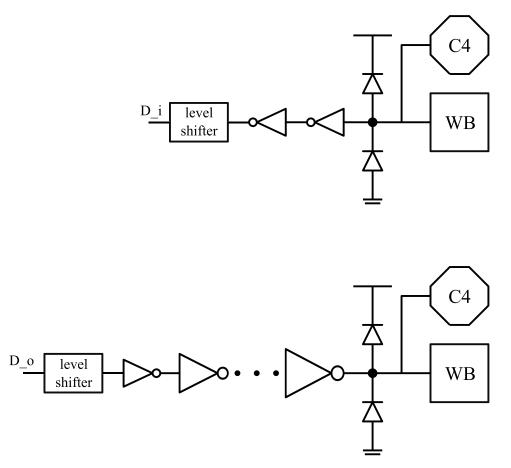

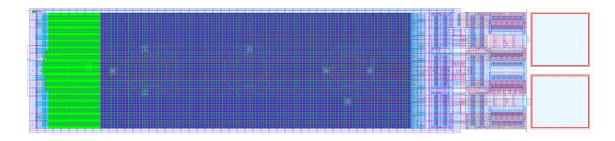

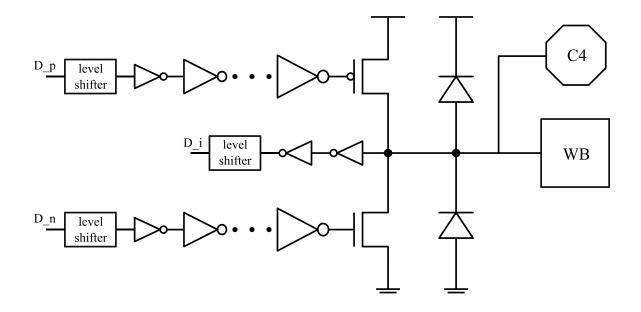

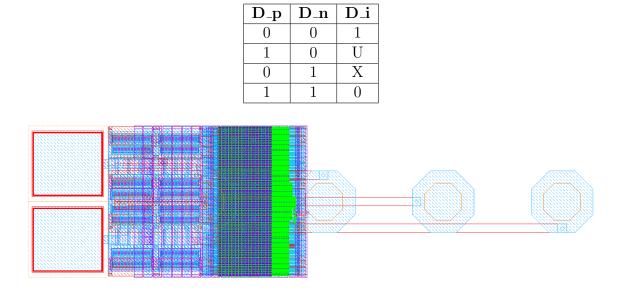

| 5.30 | MHUB Input and Output Pad Circuitry                                  | 252  |

| 5.31 | Layout of the MHUB Input and Output Pads                             | 252  |

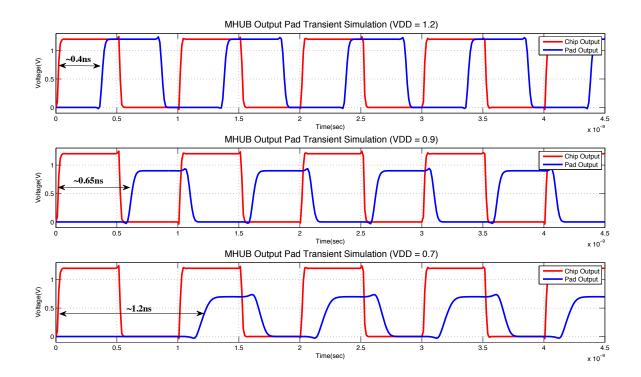

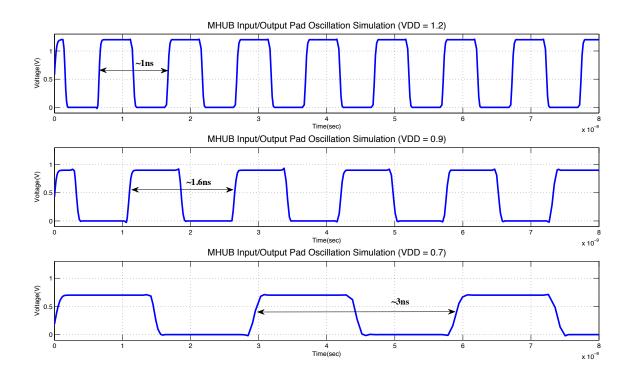

| 5.32 | Transient Simulation Results of the MHUB Output Pad                  | 253  |

| 5.33 | Transient Simulation of a Oscillator Configuration of the MHUB Input |      |

|      | and Output Pads                                                      | 254  |

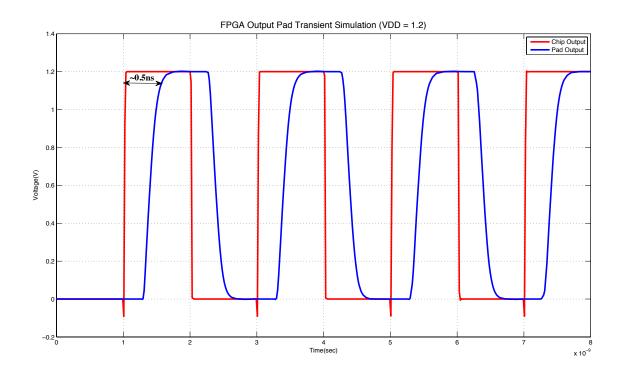

| 5.34 | FPGA Bi-directional I/O Pad Circuitry                                | 255  |

| 5.35 | Layout of the FPGA I/O Pad                                           | 256  |

| 5.36 | Transient Simulation Result of the FPGA I/O Pad Configured as Output | t257 |

| 5.37 | Frequency Plot of the FPGA I/O Pad Configured as an Oscillator For   |      |

|      | Different Supply Voltages                                            | 258  |

| 5.38 | Layout of the Power/Analog Pad                                       | 259  |

| 5.39 | Layout of the Yupana CMP                                             | 260  |

|      | Wide Area Motion Imagery Processing Pipeline                         | 263  |

|      | Wide Area Motion Imagery Preprocessing                               | 265  |

| 5.42 | Images from the CIFAR-10 Dataset                                     | 268  |

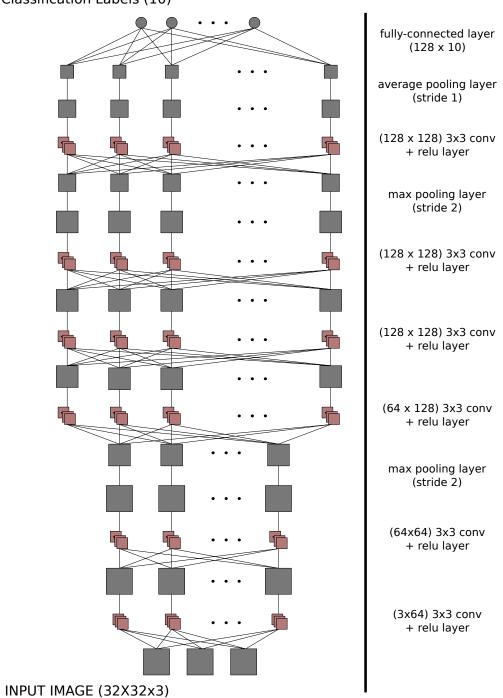

| 5.43 | A Deep Convolutional Neural Network for the CIFAR-10 Dataset         | 269  |

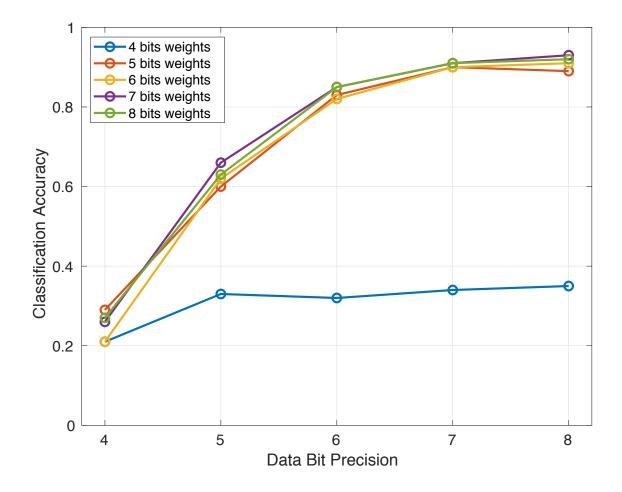

| 5.44 | Classification Accuracy of the DCNN for Different Data and Weight    |      |

|      | Precision on the CIFAR-10 Dataset                                    | 270  |

| A.1  | Mixed-Signal Design Flow                                             | 275  |

| A.2  | Custom Block Design Flow                                             | 276  |

| A.3  | Digital Design and Synthesis Flow                                    | 281  |

| A.4  | Place and Route Flow                                                 | 282  |

### Chapter 1

### Introduction

Envisaged through Moore's law decades ago,<sup>1</sup> transistors have scaled to smaller sizes, which has paved the way for exponential improvements in the functionality and performance of integrated circuits over the years. Conventional computing paradigms, such as Von Neumann architecture, have improved through this scaling with faster processor speed and more functionality through higher circuit density. Nonetheless, the very nature of the Von Neumann architecture with the separation of computational and memory structures requires a constant stream of data between memory and processor, even in the ideal case of infinite bandwidth and zero latency. For realistic implementations with finite bandwidth and latency, designers make recourse to prefetching and caching schemes, which although resolves latency issues, do not however alleviate energy cost issues of constantly streaming data.

Furthermore as emerging technologies are scaling with conventional integrated

circuits, physical limiting factors affecting performance and power consumption has escalated and misaligned what is achievable in principle and in practice. As transistors have scaled to the order of a few nanometers, thinner dielectric has become more susceptible to leakage current; manufacturing variations create a higher disparity and mismatch in the design, and noise has become a bigger factor with supply voltage scaling. Unconventional architectures, such as an analog-array processor,<sup>2</sup> and chargeinjection device (CID) processor,<sup>3–6</sup> have been proposed as energy efficient alternatives to existing paradigms to rectify this scaling issue.

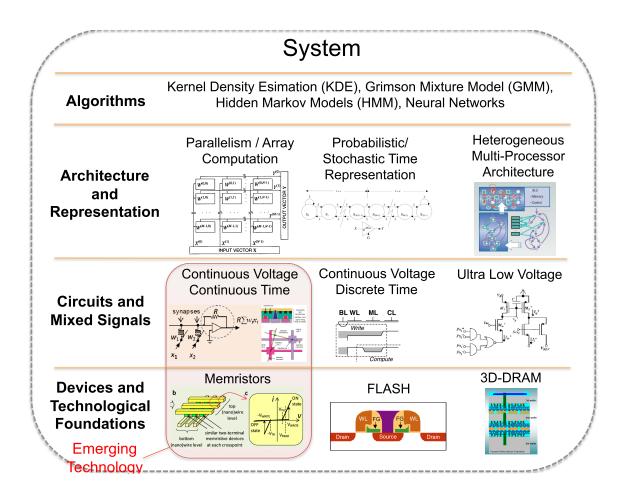

In this work, systems and architectures for chip multiprocessors (CMPs) that exploit bio-inspired data encoding and mixed-signal processing are designed and optimized across different levels of abstraction and description for constructing heterogeneous chip multiprocessor. Conceptually, this hierarchical system design approach is visualized through the diagram shown in Figure 1.1. Generally, system design begins at the algorithmic level of description, where the system's functionality is established. Then, these algorithms or functions are mapped into a coherent architecture, where the the macro system blocks, communication protocols, data representation are defined in the architectural and representation level of description. This coherent architecture is then translated into an integrated circuit, which is implemented with physical devices from a technology process in the circuit and device level of description.

Specifically in this dissertation, work is done on the representation level of descrip-

Figure 1.1: Levels of Abstraction for System Design of a Chip Multiprocessor.

tion that explores a random pulse-density modulation (RPDM) encoding in building computationally-efficient system for implementing machine learning and image processing algorithms. This alternative modality of encoding has been useful in stochastic computation for simplifying complex functions into bit-wise logic operations that can be implemented with much less area and energy costs compared to conventional computing systems.<sup>7,8</sup> Similar to neurobiological systems, such as the human brain that operates on low-dimensional spike trains, data in this modality of computation is implicitly encoded in the statistics of unary samples ergo allowing for a robust en-

coding that trades off precision (variance) for either time or resource. With continued technology trends pushing the brinks of transistor scaling, the need for error-tolerant systems and architecture that are resilient to scaling issues has made alternative computing paradigms, such as stochastic computing, attractive.

Moreover, on the level of circuit description, mixed-signal integrated circuits hinged on charge-based computing have been designed and fabricated in submicron CMOS processes for energy-efficient fixed point arithmetic. In the analog domain, products can be done implicitly and efficiently at the thermal noise limits on a capacitor when one input is encoded as the voltage, and the other as capacitance. Exploiting this principle, vector-vector multipliers were designed in this work that use programmable capacitor arrays for computing inner products and a sigma-delta  $(\Sigma\Delta)$  modulator for decoding these results back to the digital domain.<sup>9</sup> Additionally, a mixed-signal multiply and add processor based on a successive approximation architecture is designed and fabricated in a submicron CMOS process as a competitive alternative to conventional digital signal processor (DSP).

Finally, on the level of architectural description, different system blocks were designed for facilitating distributive computing in CMPs. A compact instruction-set processor that interfaces with both a switch circuit token-ring and packet-switching mesh network-on-chip is designed that works as a direct memory access (DMA) and processing unit (PU) controller on a SoC. This instruction set processor was integrated with a mixed-signal vector-vector multiplication processing unit (PU VVM),

an auxiliary memory unit (PU CACHE), and other PUs such as DSPs and morphological processors. Moreover, a bufferless scalable network architecture is designed and emulated in a network simulator. This network presented in this thesis not only provides a flexible communication solution that efficiently routes based on data traffic, but also prevents network deadlocks and livelocks, and can handle faulty routing channels due to increased fabrication defect with scaling network sizes. Other relating work includes the design of custom I/O cells implemented in a large SoC chip.

The culmination of this dissertation is the multifaceted design of heterogeneous mixed-signal processing units and system modules for a high performance computing and energy efficient 2.5D multiprocessor system-on-chip (MPSoC). Comprised of 12,544 VVM cores, a high bandwidth memory interface with 2 network on chips, ARM Cortex-M0 cores, and additional auxiliary units in 246.8mm<sup>2</sup> silicon area, this chip was designed to be useful for wide area motion imagery with gigabytes of framed images, large scale inference task with deep convolutional neural networks, and more.

This thesis is divided into 5 chapters. Chapter 1, this one, provides an introduction and overview of this work. Chapter 2 discusses a bio-inspired modality of data representation, and how it was used to construct computational efficient architecture predicated on stochastic computation primitives. Chapter 3 presents mixed-signal architectures iteratively designed and optimized for energy-efficient vector-vector multiplication. Moreover, Chapter 4 presents a mixed-signal architecture, inspired from the successive approximation analog-to-digital converter (SA ADC), as a competitive

alternative to conventional DSPs for multiply-add operations. Finally, Chapter 5 details the design of noteworthy units and modules of a heterogeneous CMP prototype implemented in a submicron CMOS process. Also in this chapter, some large-scale applications of this CMP are presented with results from test chips.

### Chapter 2

# Stochastic Representation for Computational Efficiency

The human brain is capable of computing over a quadrillion synaptic operations per second; all while only consuming roughly 12 watts.<sup>10</sup> Even with the exponential improvements in technology from advances in integrated circuits as envisioned through Moore's law,<sup>1</sup> the efficiency that is observed in human brains is still many orders of magnitude superior to current state of the art processors. The computational efficiency of these neurobiological systems can be attributed to clever exploitation of the underlining physics and mediums to efficiently represent and process information.

Generally, computing systems use time, space, and energy as physical resources for processing information. Conventional computing paradigms over the years have leveraged energy, while exploiting space and time for improving performance and

throughput. Nonetheless, now in the age of big data, the increased computation cost for intelligent data exploitation has made these computing systems inadequate and less desirable for efficient computing at a large-scale.<sup>11</sup> In this work, an alternative data representation, inspired from neurobiological systems, is explored for designing and implementing more computational efficient systems and architectures.

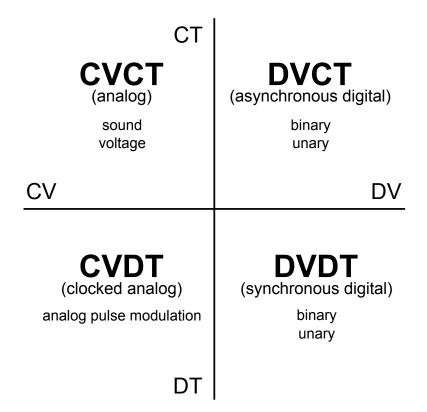

### 2.1 Data Representation

Biological and electronic signals can be categorized based on their representation in time and in value. Four main signal representations are distinguished in prior work.<sup>12,13</sup> Signals that are continuous in value, commonly known as analog signals, can either be represented as continuous-value continuous-time (CVCT) signals, such as sound signals, or as continuous-value discrete-time (CVDT) signals, such as clocked analog signals. On the other hand, signals discretized in value, conventionally known as digital signals, can be represented as discrete-value continuous-time (DVCT) signals, such as anisochronous pulse-time modulated (PTM) signals, or discrete-value discrete-time (DVDT), such as pulse code modulated (PCM) signals. An illustration of these signal representations with example signals is shown in Figure 2.1.

Figure 2.1: Four Types of Signal Representation. The graph is broken up into four quadrant separated by continuity in time and value. In the upper left quadrant are continuous-value continuous-time (CVCT) signals. In the upper right quadrant are the discrete-value continuous-time (DVCT) signals. In the lower left quadrant are the continuous-value discrete-time (CVDT) signals. In the lower right quadrant are the discrete-value discrete-time (DVDT) signals.

### 2.1.1 Analog vs. Digital

Even with the overwhelming popularity and integration of DVDT signal representation as the standard for conventional computing paradigms, there are distinct advantages and disadvantages within each of these analog and digital domains that can be exploited depending on the application. Generally, analog signals need less resources for information encoding as many bits can be encoded in one wire, while digital signals encode 1-bit of information per wire. Nonetheless, analog signals are

more susceptible to inaccuracies in encoding because of mismatches in physical devices and noise from thermal fluctuations or coupling devices, and digital signals are more robust due to less information encoding per resource. Additionally, computation in the analog domain can be done using underlining physic governed by laws such as Kirchoff's current and voltage laws (KCL and KVL), which greatly simplifies system implementation. However, analog signals are not restored after computation stages compared to digital signals, and can thus accumulate noise from cascaded stages. Consequently, complex digital systems with many computing stages are generally easier to design than complex analog systems with many computing stages. These advantages and disadvantages across domains highlight trade-offs that can be exploited for computational efficiency.

### 2.1.2 Unary vs. Binary

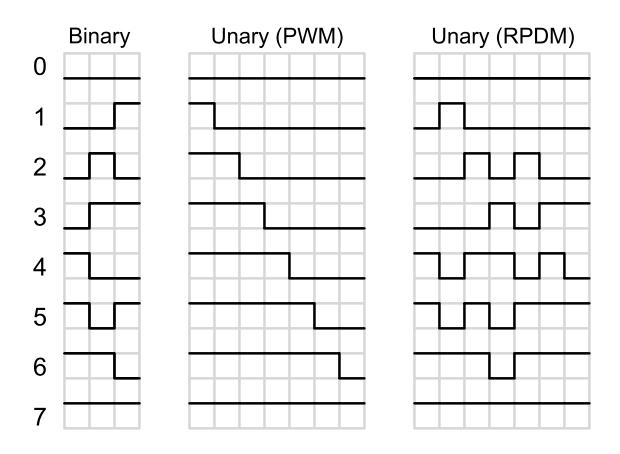

In digital representation, information can be encoded in different schemes based on time and space. Standard digital computers, which are based on a binary numeral system, use positional notation to represent order of magnitudes in a base-2 format, where each bit represents either a '0' or '1' value. This system has been widely adapted for decades because of its straightforward implementation in digital logic gates. Alternatively, a unary coding scheme such as pulse width modulation (PWM) or random pulse density modulation (RPDM) can also be adapted which equally weights all bits in a vector encoding information. Consequently, bit ordering

Figure 2.2: Examples of Binary and Unary Encoding. The numbers 0-7 encoded in 3-bit binary, 7-bit unary PWM, and 7-bit unary RPDM.

is unimportant in these representations as information is encoded as the density of '1's in the vectors. Figure 2.2 shows an example of data encoding in both binary and unary representations. Evidently, digital binary representation is more compact than unary representation as the number of bits in binary scales logarithmically with the number of quantifiable levels as opposed to linearly for unary coding. Nonetheless, unary encoding schemes are more error-tolerant as the error injected per bit flip is constant and fixed at  $1/2^N$  for N-bit resolution in a range of [0, 1], while a bit flip in a binary representation can potentially inject an error equivalent to half

the range (0.5 for a similar range of [0,1]). With transistors scaling to the orders of a few nanometers, parasitic factors from manufacturing variations and noise have become a more significant concern, which has made digital computing systems based on standard binary-radix arithmetic less efficient. In Section 2.2, a bio-inspired unary representation based on stochastic encoding is detailed as an alternative for computing architectures.

### 2.2 Stochastic Encoding and Computing

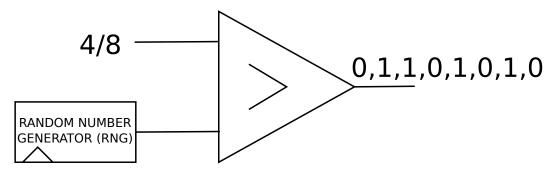

Formally introduced in the 1960s, stochastic computing has been an alternative to traditional digital logic that exploits probabilistic encoding of information to simplify complex computations to simple bitwise logic operations.<sup>7,8</sup> In stochastic computing, a multi-bit value X is encoded temporally or spatially as a random unary stream. A sample of this unary stream is denoted as a Bernoulli-distributed *stochastic number*  $x_k$ , whose mean value  $E[x_k] = p$  encodes X by mapping its range to [0, 1]. Figure 2.3 shows an example of encoding the value 4/8 = 0.5, which can be represented as 4 in a 3-bits unsigned binary representation, as a vector of stochastic numbers.

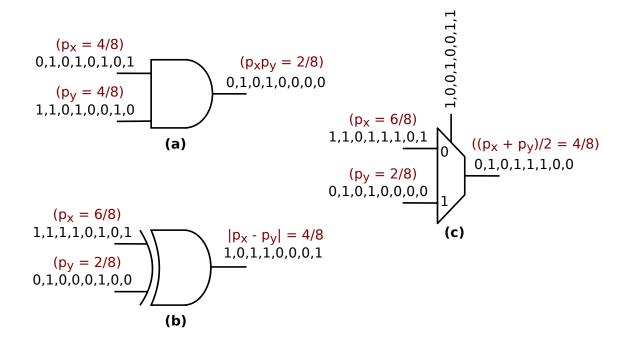

Moreover, in this domain, operations such as multiplication, weighted-sums, absolute differences, and more can be mapped into simple logic functions as seen in Figure 2.4. Multiplications can be done with an AND logic gate, absolute differences can be done using an XOR logic gate, and weighted sums can be done using a

Figure 2.3: Stochastic Number Encoding. Encoding 4/8 into a vector of stochastic numbers using a random number generator (RNG) and a digital comparator.

Figure 2.4: Stochastic Operations. (a) An AND logic gate for multiplication. (b) A XOR logic gate for absolute difference (c) A multiplexer for weighted sum of two inputs.

multiplexer.

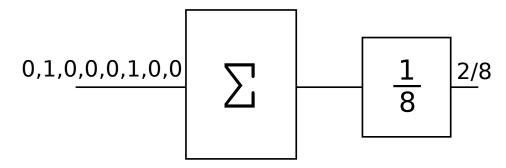

After computing in this domain, the resulting stochastic numbers can be decoded back into a binary number using a counter, and then scaling the count to the appropriate output range. This decoding can be seen in the example illustrated in Fig-

Figure 2.5: Stochastic Number Decoding.

ure 2.5. Similar to neurobiological systems, such as the human brain that operates on low-dimensional spike trains, information in the stochastic domain is implicitly represented in the statistics of the stochastic numbers ergo allowing for a robust encoding with a trade-off of variance for either time or space.

Stochastic computation has been useful for a variety of applications. Specifically, stochastic computation has been exploited for numerous of practical applications in image processing. Peng Li et al. explore stochastic computational elements for implementing digital image processing algorithms.<sup>14, 15</sup> In both works, the authors show how computational intensive functions such as the tanh and exponentiation functions can be implemented with sequential logic in the stochastic domain for doing fault-tolerant image segmentation. A comparison of hardware implementations of kernel density estimation (KDE) image segmentation algorithm with conventional binary radix logic and stochastic logic shows the conventional implementation rapidly degrading with the increased injection of soft errors, while the stochastic implementation is resilient to these errors. Additionally, Weikang Qian shows how any function can be evaluated and approximated using synthesizable Bernstein polynomials, which

can be implemented in a simple reconfigurable stochastic architecture;<sup>16,17</sup> this work has been applied to cutting hardware cost for image processing applications such as gamma correction. Also, an intelligent imaging device that integrates stochastic arithmetic with a digital pixel array for doing local image processing is presented in.<sup>18</sup> Nonetheless, much more work has been done in integrating stochastic computation based architectures for image processing.<sup>19-21</sup>

In addition to image processing, stochastic computation has also been applied to simplifying computational intense arithmetic operations such as division and squareroot,<sup>22</sup> matrix operations such as inverse-matrix transforms,<sup>23</sup> error-correction for digital communication standards,<sup>24</sup> neural networks,<sup>25–27</sup> and more. With continued technology trends pushing the brinks of transistor scaling, the need for robust systems and architecture that are noise-tolerant has made alternative computing paradigms, such as stochastic computing, attractive.

#### 2.2.1 Precision Analysis

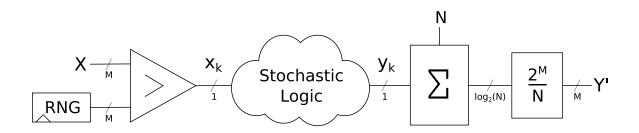

By analyzing the encoding and decoding operation in stochastic computing, an expression of the output precision as a function of the number of stochastic numbers can be derived. As briefly described in Section 2.2 and also shown in Figure 2.6, a stochastic number  $x_k$  encoded from a binary input X, follows a Bernoulli distribution with a probability of 1 given as  $p = X/2^M$ , where M is the bit precision of X. That

Figure 2.6: Stochastic Encoder, Logic, and Decoder. A binary input X is encoded into stochastic numbers, transformed through logic, and then the result is decoded into a binary output Y'.

is,

$$x_k \sim Bern\left(p = \frac{X}{2^M}\right)$$

(2.1)

Moreover, the decoded output Y' from summing and scaling the resulting stochastic number outputs  $y_k$ s, as shown in Figure 2.6, is a Binomially-distributed random variable that approximates the output Y. Assuming that the random numbers  $y_k$  are independent and identically distributed (i.i.d), then by the central limit theorem, Y'can be approximated as

$$Y' \sim B\left(n = N, p = Y\right) \xrightarrow[N \to \infty]{} \mathcal{N}\left(\mu = Y, \sigma^2 = 2^{2M} \left(\frac{\frac{Y}{2^M} (1 - \frac{Y}{2^M})}{N}\right)\right), \qquad (2.2)$$

where N is the integration count, and M is the bit precision of the output Y. Noticeably shown in the Equation 2.2, the variance  $\sigma^2$  of the normal distribution approximating the output Y is inversely proportional to the integration count N. Thus, the variance in the stochastic domain can be tuned based on the integration count, as increasing the count reduces variance and decreasing the count increases the variance.

Moreover, since the decoded output is a random variable, an absolute finite bound can not be derived for the precision of this output. Nonetheless, a probability measuring confidence on an error bound in the decoded output can be deduced, and it can be used as an indication of certainty to attain a particular output precision. The output precision is derived from the number of quantifiable levels across the output range. For an output to attain a certain precision of M-bits, all adjacent output levels must be discernible by 1 least significant bit (LSB) with a value of  $1/2^M$ . Using the LSB value as a bound on the standard deviation  $\sigma$  of the decoded output's distribution, a probability can be derived from the cumulative distribution function (CDF) that expresses a certainty in a confidence interval centered around the mean. In the context of the decoded output, this probability signifies the certainty that a specific output level will have at most a specific standard deviation or error. In the case of an arbitrary bound of  $2\sigma$ , the probability of this confidence interval can be deduced as

$$P(\mu - 2\sigma \le Y' \le \mu + 2\sigma) \approx 0.95. \tag{2.3}$$

For a value of  $2\sigma$  bounded by half of an LSB (half because adjacent codes with this same error will sum to 1 LSB), Equation 2.3 can be modified to

$$2\sigma = 2\sqrt{\frac{p(1-p)}{N}} \le \frac{1}{2}\frac{1}{2^M},$$

(2.4)

where p is the expected output. Equation 2.4 can be simplified to

$$p(1-p) \cdot 2^{2M+4} \le N. \tag{2.5}$$

For the worst case probability p = 0.5, the total N needed to guarantee 95% of samples with M-bit precision is bounded by

$$2^{2M+2} \le N \tag{2.6}$$

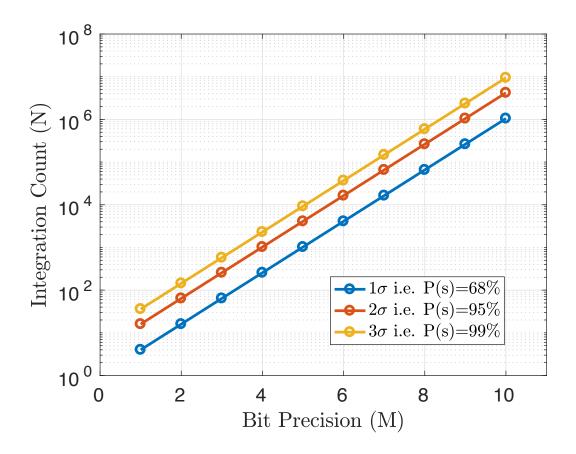

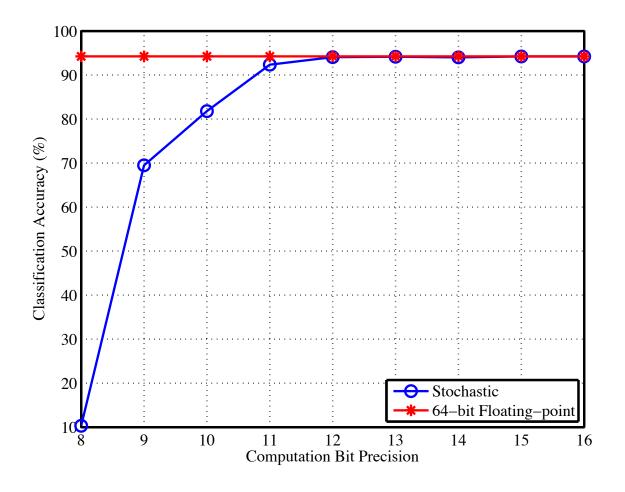

Generalizing for  $1\sigma$ ,  $2\sigma$ , and  $3\sigma$ , the plot in Figure 2.7 shows the necessary integration count N to achieve different bit precision with different certainty on a logarithmic scale, where  $P(s) = P(X - k\sigma \leq Y' \leq Y + k\sigma)$  for  $k\sigma s$ . The integration count scales exponentially with the output bit precision. Although manageable for lower bit precision, the large integration count for high bit precision makes stochastic computation less ideal for applications where accuracy and precision are critical.

#### 2.2.2 Pseudo-Random Numbers

Inaccuracies in stochastic computation may be attributed to three main factors: random fluctuations in the stochastic number representation, correlation across the numbers that are being computed, and physical errors.<sup>19</sup> As described in Section 2.2.1, random fluctuations are accredited to the statistics of the random numbers, which

Figure 2.7: Stochastic Number Precision. The plot shows the necessary integration count to achieve a certain bit precision for a given confidence interval. P(s) represents the probability of samples lying within  $s\sigma$  of the mean.

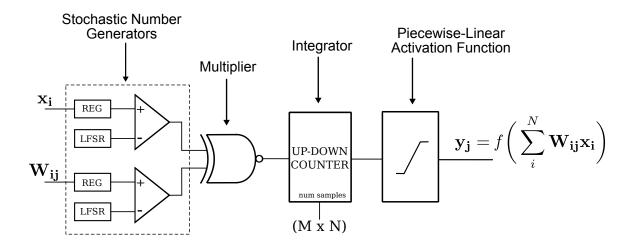

produce erroneous stochastic numbers. Pseudo-random numbers, such as maximumlength sequences from linear feedback shift registers (LFSR), can be used to eliminate random fluctuations induced into the stochastic numbers during encoding. With the appropriate feedback taps, LFSR can generate periodic maximal-length sequences, which although deterministic have good statistical properties, and have proven useful for stochastic computation architectures.<sup>14,19,20,27</sup> Thus, using a M-bit maximallength LFSR for the random number generator in Figure 2.3 and 2.6, guarantees an

exact representation of the input X in the stochastic domain in  $2^{M} - 1$  samples, and hence removing random fluctuations in the stochastic number during encoding. Nonetheless, inaccuracies can still be introduced from correlated stochastic numbers and physical errors.

# 2.3 A Deep Belief Network Using Stochastic Computation

Recently, deep belief networks, a subset of deep neural networks, have shown remarkable performance in a variety of classification and recognition tasks involving vision,<sup>28,29</sup> speech,<sup>30,31</sup> and more. Exemplary at dimensionality reduction,<sup>32</sup> DBNs have excelled at high-dimensional complex classification task, such as image classification, because of their ability to encode high-dimensional data as low-dimensional features over multiple layers. DBNs have also shown a significant advantage of performance scalability with network size. However, due to the computational intensive nature of these networks, DBNs have not been well suited for modern computing implementations for real world tasks. Nonetheless, work has been done to implement more efficient DBNs that optimize for time using Graphical Processing Units (GPUs)<sup>33,34</sup> and that optimize for power implementing spike-based and event-driven system.<sup>35-39</sup> Under this dissertation work, unconventional methodologies based on stochastic computing are explored for designing a computational efficient DBN in an

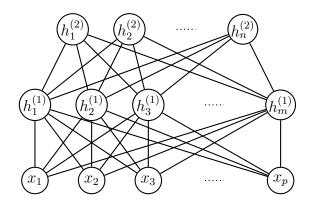

**Figure 2.8:** A 2 Hidden Layer Deep Belief Network. Hidden layer  $h^{(1)}$  encodes features from the input layer x, and hidden layer  $h^{(2)}$ , which is the output layer of this network, encodes more abstract features from the features in hidden layer  $h^{(1)}$ .

attempt to optimize for power, while still maintaining good performance.<sup>27</sup>

#### 2.3.1 Background and Theory

Deep belief networks, which were introduced by Hinton and his collaborators in 2006,<sup>40</sup> are multi-layered generative graphical models that represents layers as Restricted Boltzmann Machines (RBMs),<sup>41</sup> and greedily train them with unsupervised learning algorithms.<sup>42</sup> Figure 2.8 shows the graphical model of a 2-hidden layer DBN. RBMs, which are the building blocks of DBNs, are energy-based models that encode useful properties of the variables in the shape of its energy function. Generalized from exponential family models, a probability distribution can be defined through an energy function as

$$P(x) = \frac{e^{-\mathcal{E}(x)}}{Z},\tag{2.7}$$

where  $\mathcal{E}(x)$  is the energy function, and Z is the normalization factor  $\sum_{x} e^{-\mathcal{E}(x)}$  known as the partition function. Applying gradient descent on the log-likelihood of the observed data, an energy-based model like RBMs can learn features of the data.

Boltzmann machines have the modeling capacity to represent complex distributions through a set of observed visible units  $\mathbf{x}$ , and unobserved hidden units  $\mathbf{h}$ . This modifies the probability distribution defined in Equation 2.7 to

$$P(\mathbf{x}) = \sum_{\mathbf{h}} P(\mathbf{x}, \mathbf{h}) = \sum_{\mathbf{h}} \frac{e^{-\mathcal{E}(\mathbf{x}, \mathbf{h})}}{Z}$$

(2.8)

Moreover, RBMs form bipartite graphs between these layers of visible units  $\mathbf{x}$ , and hidden units  $\mathbf{h}$ , with no intra-layer connections. This creates a conditional independence between the visible and hidden units across the layers, which mathematically can be seen as

$$p(\mathbf{h}|\mathbf{x}) = \prod_{i} p(\mathbf{h}_{i}|\mathbf{x})$$

$$p(\mathbf{x}|\mathbf{h}) = \prod_{j} p(\mathbf{x}_{j}|\mathbf{h})$$

(2.9)

The energy function of an RBM is defined as

$$\mathcal{E}(\mathbf{x}, \mathbf{h}) = -\mathbf{b}^T \mathbf{x} - \mathbf{c}^T \mathbf{h} - \mathbf{h}^T \mathbf{W} \mathbf{x}$$

(2.10)

where  $\mathbf{b}$  and  $\mathbf{c}$  are vectors of offset values associated with the visible units in vector  $\mathbf{x}$

and hidden units in vector  $\mathbf{h}$  respectively, and  $\mathbf{W}$  is a weight matrix associated with visible to hidden unit connections.

In the case that  $\mathbf{h_i}$  and  $\mathbf{x_j}$  are binary units,  $P(\mathbf{h_i}|\mathbf{x})$  and  $P(\mathbf{x_j}|\mathbf{h})$  from Equation 2.9 can be derived as

$$P(\mathbf{h_i} = 1 | \mathbf{x}) = \frac{e^{-(-\mathbf{c_i} - \mathbf{W_i x})}}{1 + e^{-(-\mathbf{c_i} - \mathbf{W_i x})}} = sigm(\mathbf{c_i} + \mathbf{W_i x})$$

$$P(\mathbf{x_j} = 1 | \mathbf{h}) = \frac{e^{-(-\mathbf{b_j} - \mathbf{W_j h})}}{1 + e^{-(-\mathbf{b_j} - \mathbf{W_j h})}} = sigm(\mathbf{b_j} + \mathbf{W_j h})$$

(2.11)

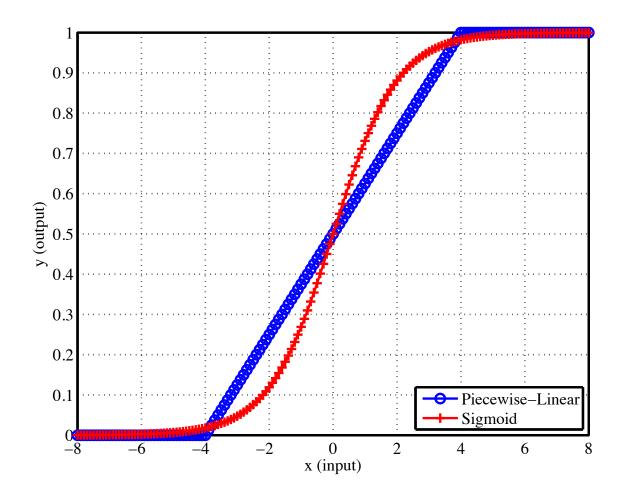

where sigm is the sigmoid function, commonly used as the activation function in artificial neurons.

In training a deep belief network, the log-likelihood gradient is computed on training data for learning parameters associated with the energy function. For the distribution defined in Equation 2.8, this gradient is deduced as

$$\frac{\partial \log p(x)}{\partial \theta} = \frac{\partial \mathcal{F}(x)}{\partial \theta} - \frac{1}{Z} \sum_{\tilde{x}} e^{-\mathcal{F}(x)} \frac{\partial \mathcal{F}(\tilde{x})}{\partial \theta}$$

(2.12)

where x is a single visible unit, h is a single hidden unit, the partition function  $Z = \sum_{x} e^{-\mathcal{F}(x)}$ , and  $\mathcal{F}(x)$  is the free energy function inspired from physic, which is given as

$$\mathcal{F}(x) = -\log \sum_{h} e^{-\mathcal{E}(x,h)}$$

(2.13)

Computing this gradient is intractable because of the second term in Equation 2.12, which requires taking the expectation over all configurations of  $\tilde{x}$  under the distri-

bution of the model. As opposed to deriving an analytical expression for the loglikelihood gradient, a Markov Chain Monte Carlo (MCMC) sampling method, such as Gibbs sampling, is used for estimating this gradient. Because of the conditional independence of intra-layer units in RBMs, block Gibbs sampling can be applied for iteratively sampling hidden and visible units in a Markov chain for training the network. This sampling chain can be visualized as

$$\mathbf{x}^{(0)} \Rightarrow \mathbf{h}^{(0)} \Rightarrow \mathbf{x}^{(1)} \Rightarrow \mathbf{h}^{(1)} \Rightarrow \dots \mathbf{x}^{(t)} \Rightarrow \mathbf{h}^{(t)}$$

As  $t \to \infty$ ,  $\mathbf{x}^{(t)}$  and  $\mathbf{h}^{(t)}$  are guaranteed to be accurate samples from  $p(\mathbf{x}, \mathbf{h})$ . However, since the luxury of sampling till convergence can not be afforded, alternative algorithms have been devised for efficiently sampling for learning.

One in particular, that has gained a lot of popularity, is the Contrastive Divergence  $(CD_k)$  learning algorithm.<sup>43</sup>  $CD_k$  initializes the Markov chain to samples from the training set, and then generates samples from just k-steps of Gibbs sampling. This learning algorithm has been applied for unsupervised training of DBNs with great success, even with only one step of Gibbs sampling (k = 1).

The parameter update equations for training a network with binary units using

the  $CD_k$  algorithm is given as

$$\mathbf{W}^{(t+1)} = \mathbf{W}^{(t)} + \eta(\mathbf{h}^{(t)}\mathbf{x}^{(t)} - sigm(\mathbf{c_i}^{(t)} + \mathbf{W_i}^{(t)}\mathbf{x}^{(t)})\mathbf{x}^{(t+1)})$$

$$\mathbf{b}^{(t+1)} = \mathbf{b}^{(t)} + \eta(\mathbf{x}^{(t)} - \mathbf{x}^{(t+1)})$$

$$(2.14)$$

$$\mathbf{c}^{(t+1)} = \mathbf{c}^{(t)} + \eta(\mathbf{h}^{(t)} - sigm(\mathbf{c_i}^{(t)} + \mathbf{W_i}^{(t)}\mathbf{x}^{(t)}))$$

where  $\eta$  is the learning rate, and  $\mathbf{h}^{(t+1)}$  and  $\mathbf{x}^{(t+1)}$  are samples generated from their conditional probabilities.

Furthermore, with top layer supervised learning, DBNs can also be implemented as deep feedforward neural networks for applications in discriminative tasks, such as classification.

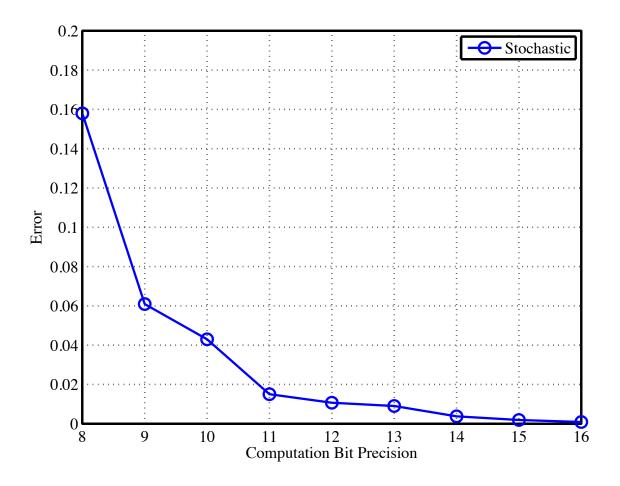

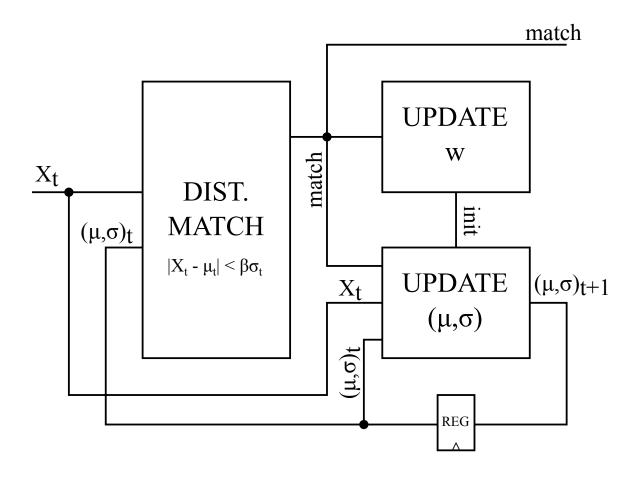

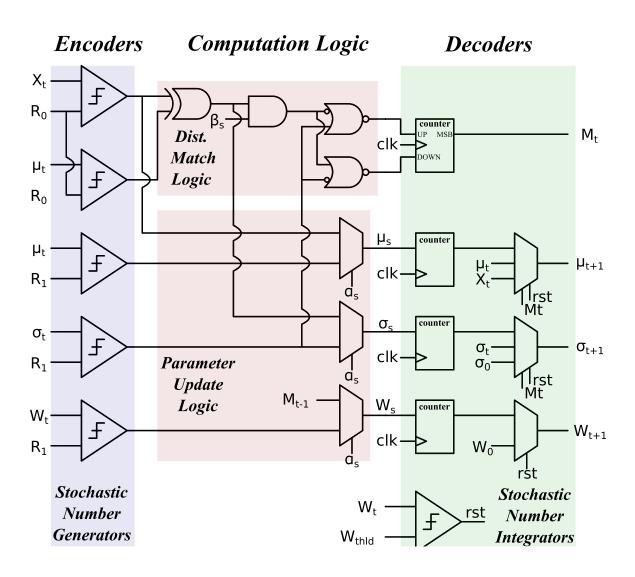

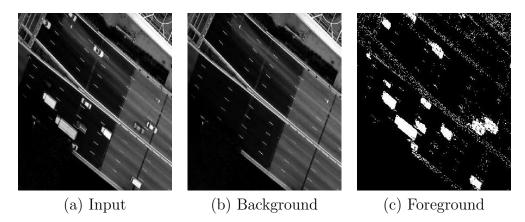

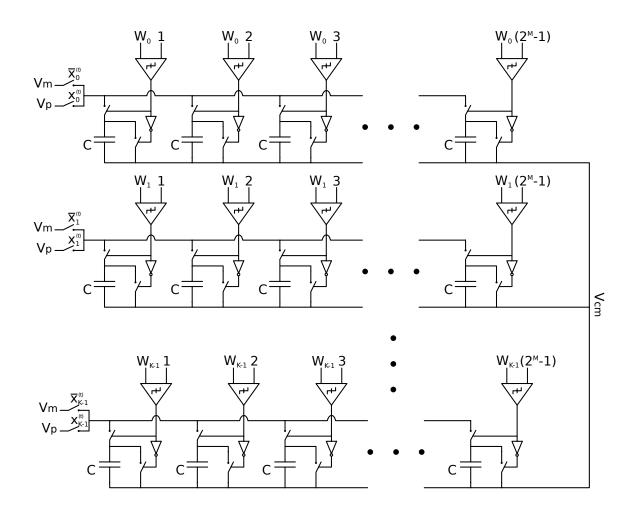

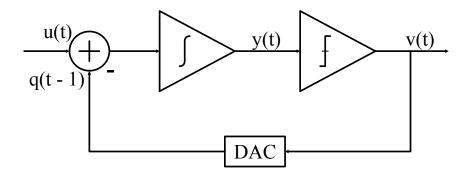

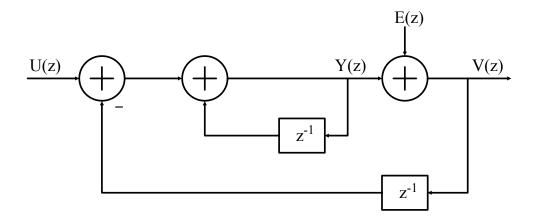

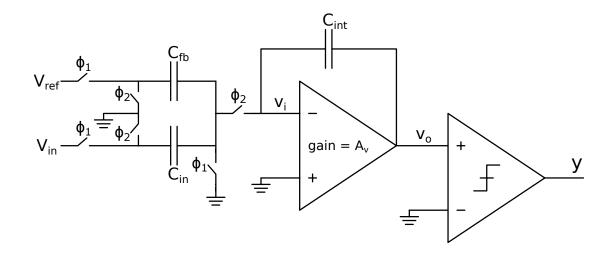

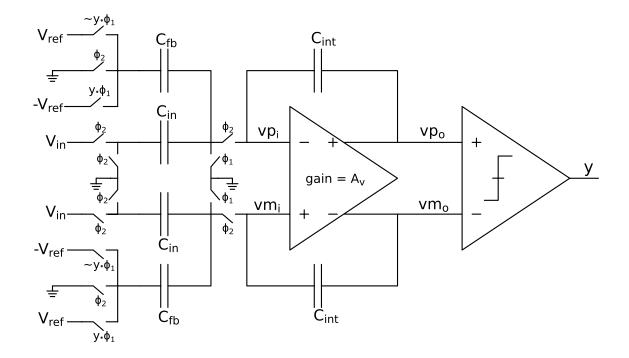

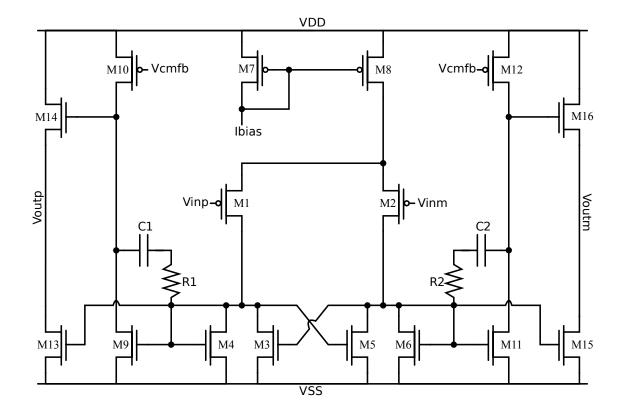

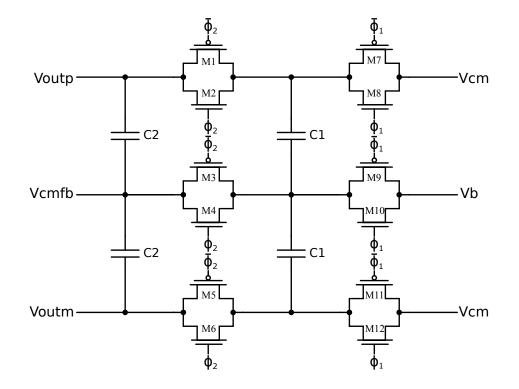

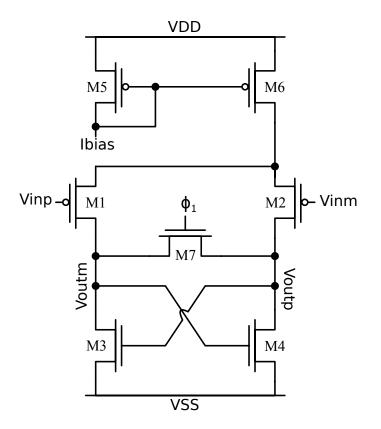

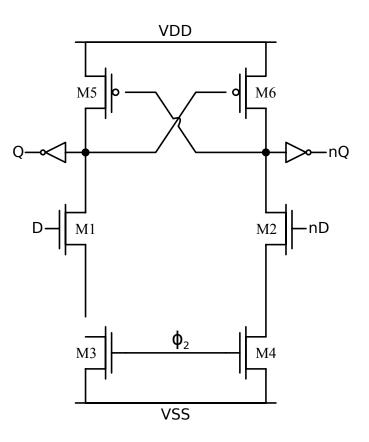

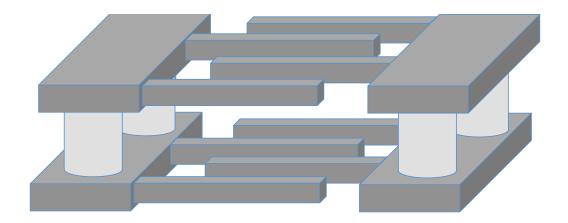

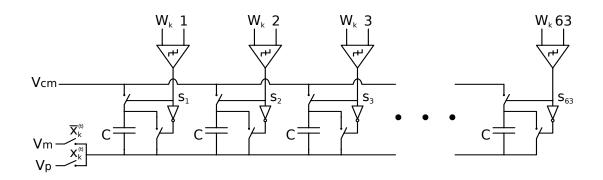

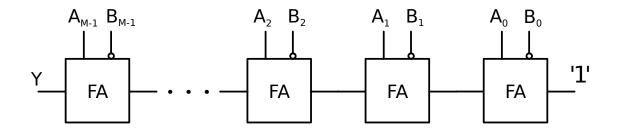

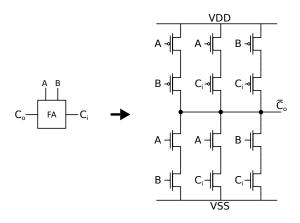

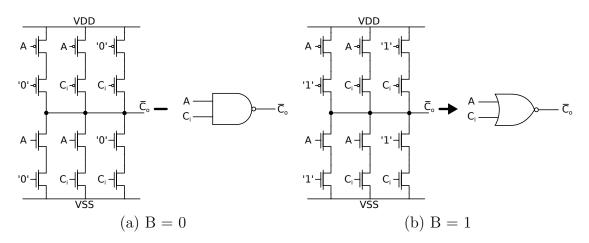

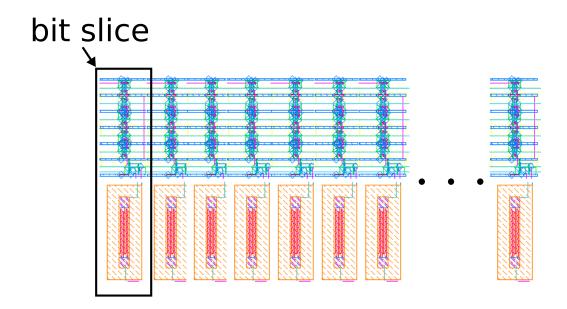

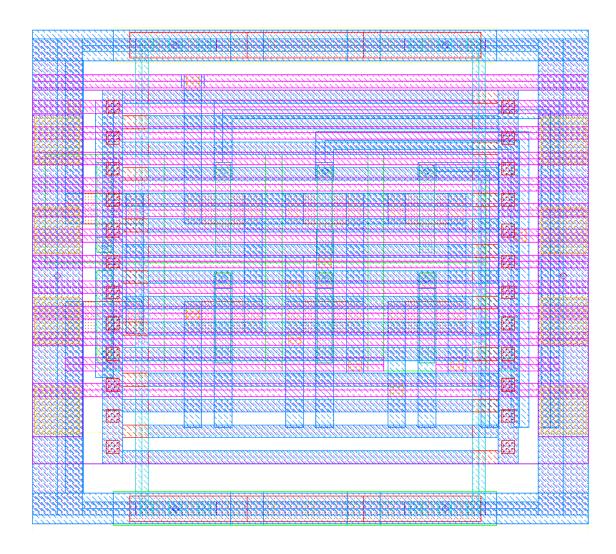

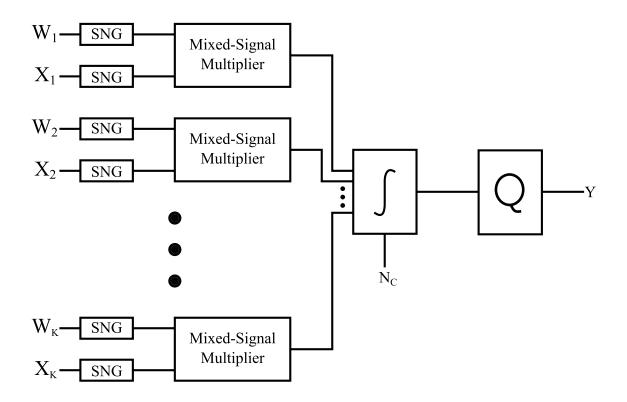

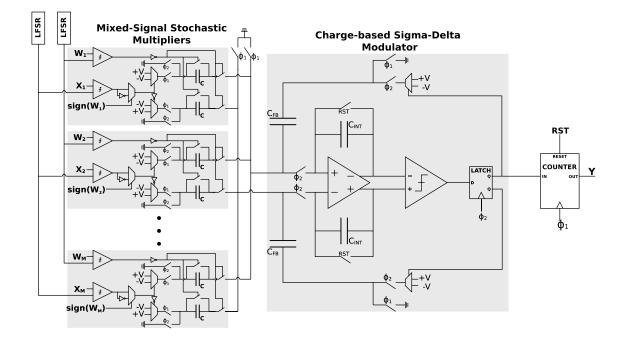

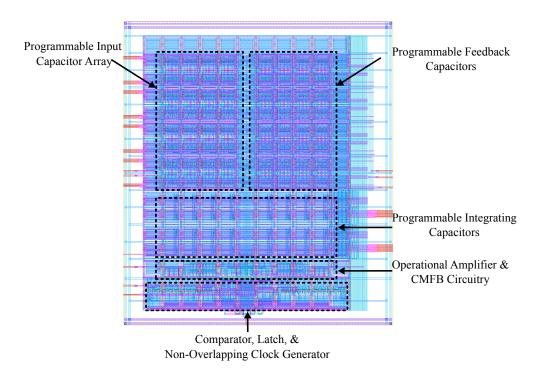

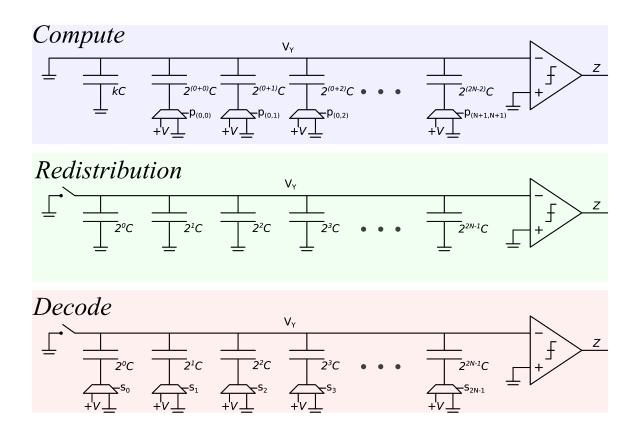

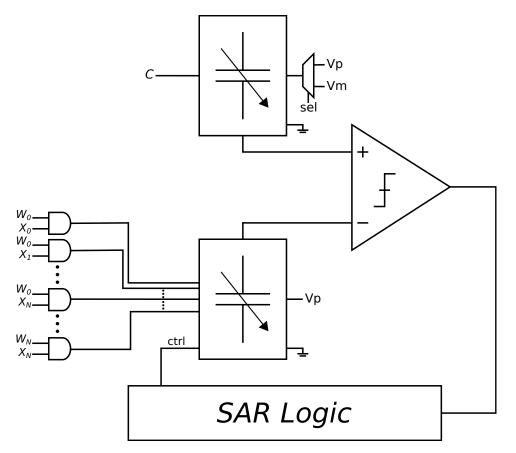

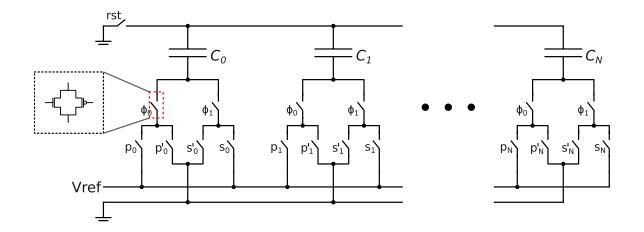

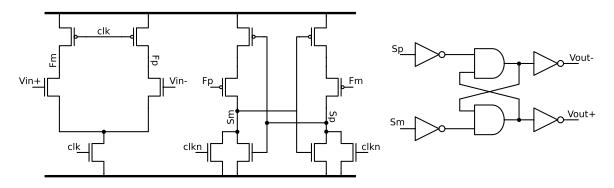

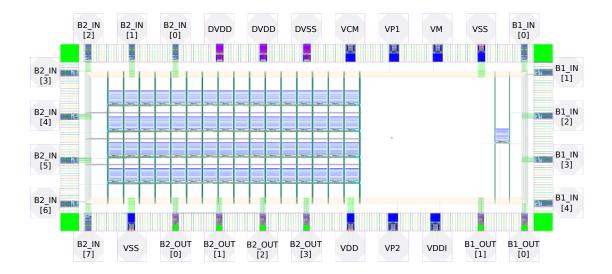

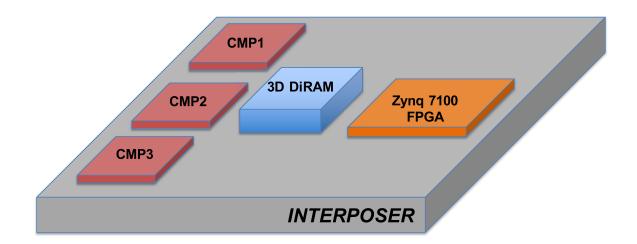

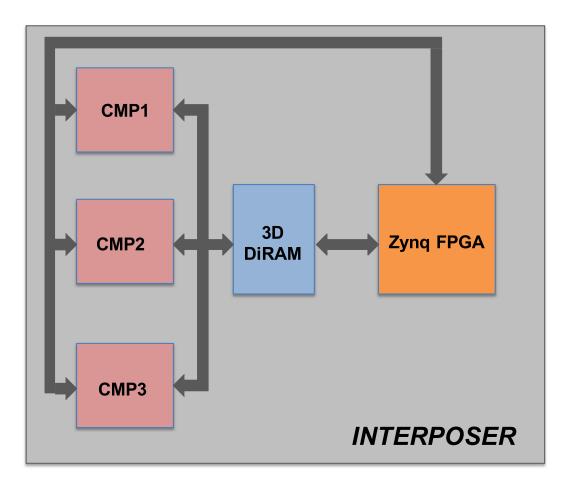

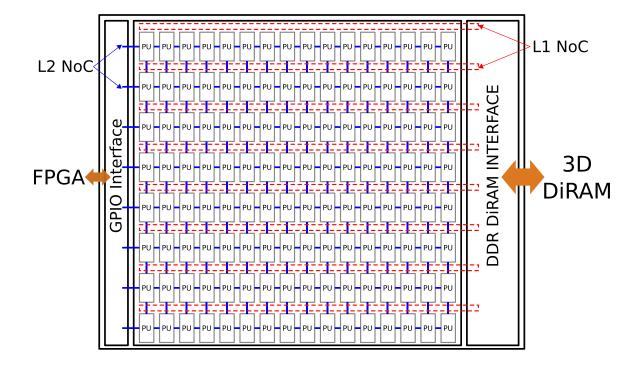

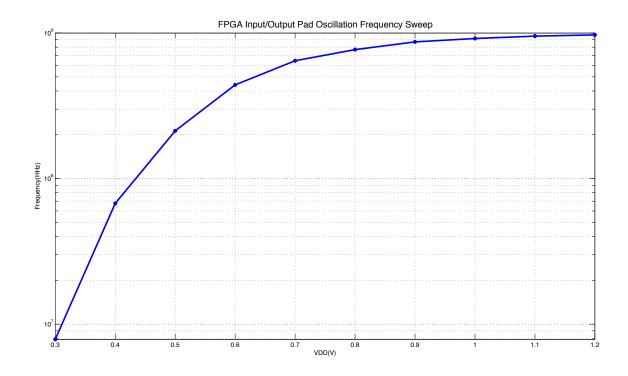

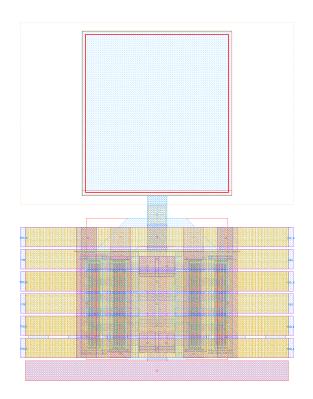

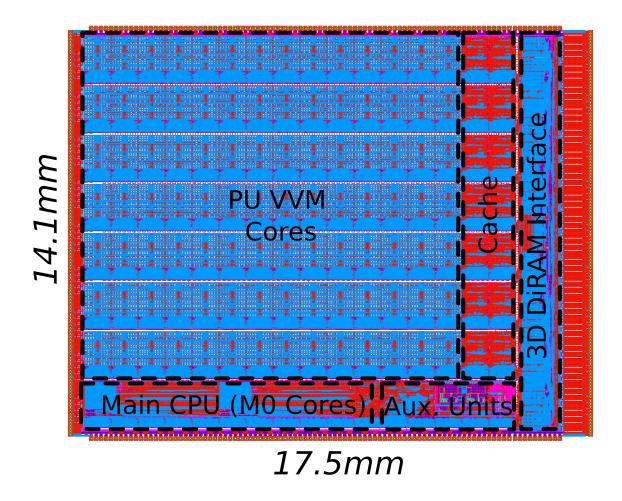

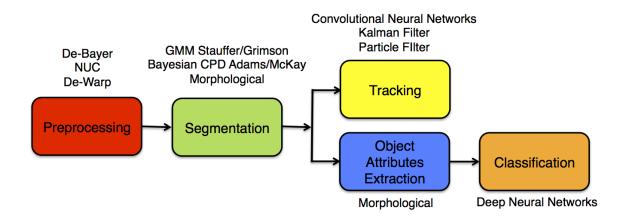

#### 2.3.2 Architecture and Implementation