### LJMU Research Online

Ji, Z, Zhang, JF, Zhang, WD, Gao, R and Zhang, X

An investigation on border traps in III-V MOSFETs with an In0.53Ga0.47As channel

http://researchonline.ljmu.ac.uk/2145/

Article

**Citation** (please note it is advisable to refer to the publisher's version if you intend to cite from this work)

Ji, Z, Zhang, JF, Zhang, WD, Gao, R and Zhang, X (2015) An investigation on border traps in III-V MOSFETs with an In0.53Ga0.47As channel. IEEE Transactions on Electron Devices, 62 (11). pp. 3633-3639. ISSN 0018-9383

LJMU has developed LJMU Research Online for users to access the research output of the University more effectively. Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Users may download and/or print one copy of any article(s) in LJMU Research Online to facilitate their private study or for non-commercial research. You may not engage in further distribution of the material or use it for any profit-making activities or any commercial gain.

The version presented here may differ from the published version or from the version of the record. Please see the repository URL above for details on accessing the published version and note that access may require a subscription.

For more information please contact <a href="mailto:researchonline@ljmu.ac.uk">researchonline@ljmu.ac.uk</a>

http://researchonline.ljmu.ac.uk/

# An investigation on border traps in III-V MOSFETs with an In<sub>0.53</sub>Ga<sub>0.47</sub>As channel

## Z. Ji, Member, IEEE, X. Zhang, J. Franco, R. Gao, M. Duan, J. F. Zhang, W. Zhang, B. Kaczer, A. Alian, D. Linten, D. Zhou, N. Collaert, S. De Gendt, and G. Groeseneken, Fellow, IEEE

Abstract— Continuing CMOS performance scaling requires developing MOSFETs of high-mobility semiconductors and InGaAs is a strong candidate for n-channel. InGaAs MOSFETs, however, suffer from high densities of border traps, and their origin and impact on device characteristic are poorly understood at present. In this work, the border traps in nMOSFETs with an In<sub>0.53</sub>Ga<sub>0.47</sub>As channel and Al<sub>2</sub>O<sub>3</sub> gate oxide are investigated using the discharging-based energy profiling technique. By analyzing the trap energy distributions after charging under different gate biases, two types of border traps together with their energy distributions are identified. Their different dependences on temperature and charging time support that they have different physical origin. The impact of channel thickness on them is also discussed. Identifying and understanding these different types of border traps can assist in future process optimization. Moreover, border trap study can yield crucial information for long-term reliability modelling and device time-to-failure projection.

Index Terms—Border trap, III-V, InGaAs, Quantum well, characterization, mobility, reliability.

#### I. INTRODUCTION

International Technology Roadmap for Semiconductors (ITRS) predicts a power supply of 0.72V will be needed for transistors in high performance logic applications in 2018 [1]. To address this, attention is turning to the use of high mobility channel materials such as InGaAs and Ge for n- and p-MOSFETs, respectively. The development of InGaAs devices has made encouraging progresses in recent years: high intrinsic electron mobility of 3000 cm<sup>2</sup>/V·s has been demonstrated by several groups [2, 3]. With Al<sub>2</sub>O<sub>3</sub> as gate oxide, a low interface state density (e.g. 2x10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> [4]) and a subthreshold swing of 75mV/dec [2] were obtained. However, intolerable number of border traps are found in the oxide, resulting in I-V hysteresis and C-V frequency dispersion [5]. These border traps further cause severe Positive Bias Temperature Instability (PBTI) issue in the long term, shorten the devices' lifetime to an unacceptable level, and therefore impede the practical use of such devices [6] at the current status.

Conventionally, border traps are investigated using Multi-Frequency Charge Pumping (CP) technique [7]. Unlike bulk-Si

Manuscript received MMM DDD, 2014. The review of this paper was arranged by Editor W. WWW.

FETs, devices with InGaAs channel are usually grown on insulating substrate and thus only have three terminals, making the CP impossible to be applied. To overcome this difficulty, a number of drain-current-based methods are proposed, such as those based on noise [8-10] and pulsed Id~Vg measurements [11]. The noise-related techniques, such as TDDS method [10], extract trap information from the steps of drain current due to individual defects' detrapping [8]. The pulsed Id~Vg method investigates the drain current response to gate pulses. The actransconductance (AC-gm) method [12] extracts the traps' energy and spatial location from the frequency dependence of transconductance, which is attributed to charge trapping as modulated by an ac gate voltage. The Trap Spectroscopy by Charge Injection and Sensing (TSCIS) technique [13] has been proposed to extract the energy distribution of border traps based on charging under the assumption that the charging process takes place through elastic tunneling, which does not apply to III-V devices, as we will show in this paper.

In this work, the border traps will be investigated using our recently proposed discharging-based energy profile technique [14]. By analyzing the trap energy distribution after charging at different Vg levels, two different types of border traps are identified. They have dramatic different dependences on the charging time and temperature, strongly supporting that they are of different origins.

The paper is organized as follows: in Section II, the test samples as well as the details of test procedure will be introduced. In Section III, the technique for energy distribution extraction is firstly explained. It is then used to analyze the border traps. Two different types of traps are clearly separated. To further justify their separation, their charging time and temperature dependences are investigated. The channel thickness dependence is also discussed by the end of this Section. Their potential impact on the circuit operation is briefly discussed in Section IV. Finally, Section V concludes this paper.

#### II. DEVICES AND EXPERIMENTAL DETAILS

#### A. Devices

The nMOFETs with n-type channel are used in this work. The devices received a  $(NH_4)_2S$  treatment prior to the gate oxide deposition. The gate oxide is a 10 nm ALD Al<sub>2</sub>O<sub>3</sub> with a TMA initial surface cleaning. ALD Al<sub>2</sub>O<sub>3</sub> on InGaAs using TMA as the precursor have been reported to effectively reduce As and Ga oxides through an interfacial "self-cleaning" reaction

Z. Ji, X. Zhang, R. Gao, M. Duan, J. F. Zhang, W. Zhang are with the School of Engineering, John Moores University, Liverpool L3 3AF, U.K. (e-mail: z.ji@ljmu.ac.uk).

J. Franco, B. Kaczer, A. Alian, D. Linten, D. Zhou, S. De Gendt, and G. Groeseneken are with IMEC, Leuven B3001, Belgium. S. De Gendt, and G. Groeseneken are also with KU Leuven, Leuven, Belgium.

process and can yield a good quality interface [15]. Forming gas anneal at 370 °C was performed on the finished devices. The detailed fabrication process flow, the cross section of the device and the TEM micrograph of the gate stack can be found in [2].

#### B. Experimental procedure

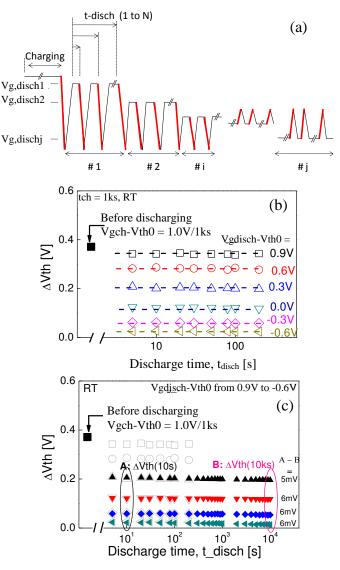

The discharging-based energy profiling technique [14] is used in this work to investigate border traps. The test sequence is shown in **Fig.1**(a).  $V_g$  is firstly raised to a certain charging level  $V_{g,ch}$  for a pre-specified time to fill the traps.  $V_g$  was then lowered to V<sub>g,disch1</sub> and the degradation is monitored against discharge time until its change becomes negligible (e.g. <2mV). Once discharge under Vg,disch1 completed, Vg was further reduced to V<sub>g,disch2</sub> and the same procedure is followed. Full I<sub>d</sub>- $V_g$  measurement is taken at the pulse edge with a speed of  $3\mu s$ , as marked as thick red lines in **Fig.1(a)** [16, 17].  $V_{th}$  is evaluated using constant current method with the level around fresh V<sub>th,0</sub> [18]. When  $V_{g,disch}$  is higher than  $V_{th,0}$ ,  $I_d$ - $V_g$  sweeps negatively from 'on' towards 'off', i.e. from  $V_{g,disch}$  to  $V_{th,0}$  - 0.5V. However, to capture the trap energy location both within and beyond the InGaAs band gap, Vg,disch eventually becomes lower than  $V_{th,0}$  and therefore the direction of pulse needs be reversed and Id-Vg will sweep positively from 'off' towards 'on', i.e. from  $V_{g,disch}$  to Vth0+0.5V.

A typical measurement result is shown in **Fig.1(b)**. After charging under  $V_{g,ch}$  for 1ks, Vg is then lower down to each  $V_{g,disch}$  level for 200s. Under each  $V_{g,disch}$ , the discharging reaches saturation quickly after several seconds and will become almost a flat line up to 200s. In order to check the impact of discharge time, the device was first charged under  $V_{g,ch}$  for 1ks, and then discharged until 10ks under each  $V_{g,disch}$ . **Fig.1(c)** shows that further increasing the discharging time to 10ks will only introduce an extra discharging of 5~6 mV. This indicates that the trap discharging at a given discharge voltage is dominated by its energy level. In the rest of this work, the discharge time of 1s is used for each  $V_{g,disch}$ .

#### III. BORDER TRAPS IN III-V DEVICES

#### A. Energy distribution extraction

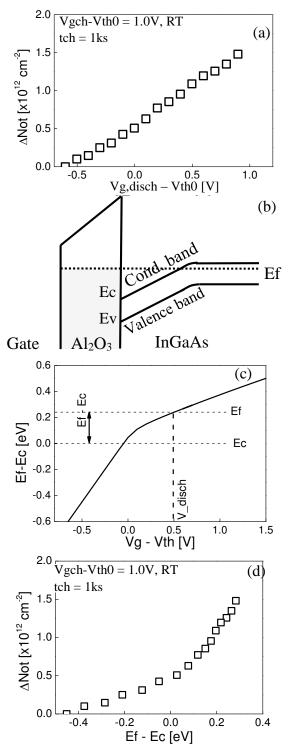

To obtain the trap energy distribution,  $\Delta V$ th after completing discharging under each Vg,disch (the last point of each trace in Fig.1(b)) is firstly converted to the effective charge density,  $\Delta N_{ot}$ , which is the equivalent charge density by assuming all charges being at the interface. It is calculated based on the charge sheet model with the equation:  $\Delta N_{ot} = (C_{ox} * \Delta V_{th})/q$ . Where q is the elementary charge and  $C_{ox}$  is oxide capacitance. The typical  $\Delta N_{ot}$  is plotted against  $V_{g,\text{disch}}$  and shown in Fig.2(a). The next step is to convert  $V_g=V_{g,disch}$  to the corresponding energy level denoted by Ef with respect to Ec of the InGaAs at the surface,  $E_f - E_c$ , as illustrated in Fig.2(b). This requires the relationship between Vg and Ef. This relationship can be obtained by simulating with 1D Schrödinger-Poisson solver [19]. The result is given in Fig.2(c). It should be noted that the horizontal axis of **Fig.2(c)** is  $V_g - V_{th}$  and  $V_{th} = V_{th,0} + V_{th}$ varies during discharging. Fig.2(d) shows the extracted trap energy distribution by plotting the  $\Delta N_{ot}$  against  $E_{f} \cdot E_{c}$ . It is worth

noting that the contribution of the interface states will be the same under all the  $V_{g,disch}$  since the Fermi level at sensing condition is kept constant. Therefore, if new interface states are generated, they would induce only a parallel upshift of the extracted  $N_{ot}$  distribution, as observed in Si devices [14, 20]. However, **Fig.2(d)** shows that complete discharging can be achieved (i.e.,  $\Delta V_{th}=0V$  at the end of the discharging sequences), indicating that interface state generation is negligible during the test and that the extracted energy distribution represents solely the border traps.

**Fig. 1** (a) V<sub>g</sub> waveform used for the test. Full I<sub>d</sub>-V<sub>g</sub> measurement is taken at the edge with a speed of 3µs (marked in thick red lines). (b) Typical results for discharging under different V<sub>g,disch</sub>. The device was charged at V<sub>g,ch</sub> – V<sub>th,0</sub> = 1.0 V under room temperature for 1ks and discharged for 200s under each V<sub>g,disch</sub>. The total threshold voltage shift before discharge is given by the symbol "■". The dash lines are guides to the eye. (c) The discharging traces with discharging time of 10ks after charging at V<sub>g,ch</sub> – V<sub>th,0</sub> = 1.0 V for 1ks. The empty grey points represented the same discharging traces shown in Fig.1(b).

Fig. 2 Energy profiling extraction  $\Delta N_{ot}$  in (a) is the charged electron traps after completing discharging at each  $V_{g,disch}$ . The data is taken from the last point of each trace in Fig.1(b). (b) Illustration of the relationship between  $E_{f'}E_c$  and the energy level of the charged electron traps.  $E_c$  is the conduction band of InGaAs at the interface and the shaded area denotes the charged electron traps. (c) The  $E_r E_v$  against  $V_g - V_{th}$  from 1D Poisson simulator [19] for converting each  $V_{g,disch}$  to an  $E_r E_v$ . (d) The extracted energy distribution of the charged electron traps after charging under  $V_{g,ch} - V_{th,0} = 1.0V$  for 1ks.

#### B. Separation of two types of border traps

Following the procedure described in Fig.2, the trap energy distributions are extracted under different  $V_{g,ch}$ . The result is

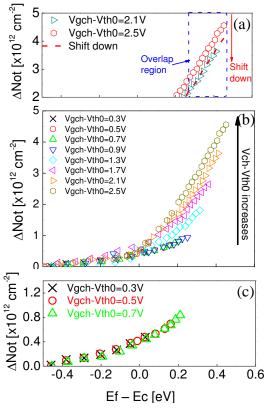

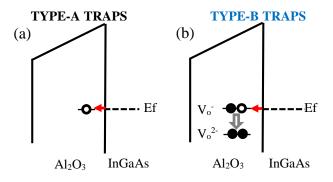

shown in **Fig.3(b)** and the distributions for several high and low  $V_{g,ch}$  levels are zoomed-in in **Figs.3(a)** and (c), respectively. For filling the Type-A under relatively low  $V_{g,ch}$ ,  $\Delta N_{ot}$  is found to increase with surface potential and their relation is independent of  $V_{g,ch}$ , as shown in **Fig.3(c)**. There are two possible explanations: 1) More traps at higher energy become accessible under higher surface potential; and/or 2) more traps deeper into the dielectric become accessible [21]. These traps have the same energy level for their ground and charged states, as illustrated in **Fig.4(a)**. In the rest of the work, this type of trap will be referred to as the **Type-A traps**.

However, as shown in **Fig.3(b)**, when  $V_{g,ch}$  further increases, it is found that the trap distribution starts to deviate. With higher  $V_{g,ch}$ , more charged traps can be observed under the same  $E_{f}$ - $E_{c}$ . As enlarged in **Fig.3(a)**, this difference is a constant when  $E_{f}$ - $E_{c}$  is close to the charging level and then gradually diminishes when Ef approaches to  $E_{c}$ . This cannot be explained by the Type-A traps which predict the same  $\Delta N_{ot}$  under the same  $E_{f}$ - $E_{c}$ regardless of  $V_{g,ch}$ . Therefore, there must exist another type of trap.

It is known that there exists traps which can change their energy level after capturing an electron due to the change of their orbital configurations [22]. In the rest of the work, these traps are called as the **Type-B traps**. The schematic energy diagram is shown in **Fig.4(b)**. Once these traps are charged, their energy levels will be shifted downwards and therefore they become too low to be discharged when E<sub>f</sub> is close to the charging level. These traps start to discharge when  $E_{f}$  further lowers down. Once they are fully discharged, the discharging traps overlap each other, as shown in Fig.3(b). According to abinitio calculations [22], Oxygen vacancies with various configurations can exist in Al<sub>2</sub>O<sub>3</sub> wherein the V<sub>o</sub><sup>-</sup> configuration has an energy level above the InGaAs conduction band and therefore it could be potentially act as an electron trap. For capturing an electron, the defect will reconfigure to its charged state  $V_0^{2-}$  which has an energy level lower than  $V_0^{-}$ , i.e. the trap becomes deeper, after trapping. This behavior expected from theoretical calculations is in line with our experimental observations for Type-B traps: we therefore conclude that oxygen vacancies in Al<sub>2</sub>O<sub>3</sub> are a possible candidate for the Type-B defects. We note that since Al<sub>2</sub>O<sub>3</sub> is amorphous, it is reasonable to assume that the energy levels of each individual oxide defect in the V<sub>0</sub><sup>-</sup> and V<sub>0</sub><sup>2-</sup> configurations are distributed around the theoretically predicted levels. Notably, however, the ab-initio calculations predict an energy gap between  $V_0^-$  and  $V_0^{2}$  [22]. As a result, it is expected that all the charged Type-B traps will not discharge when  $E_f$  is close to their charging levels. This explains the parallel shift of two consecutive discharging trace as observed in Fig.3(a) and therefore the observed discharging in this region is to be ascribed to Type-A traps only.

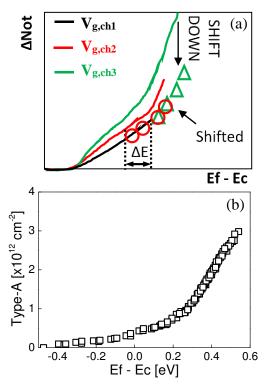

One simple method can be applied to separate these two types of traps by exploiting the parallel region of the distributions extracted for two consecutive  $V_{g,ch}$  levels, as illustrated in **Fig. 5(a)**: starting with the distribution trace at the lowest  $V_{g,ch}$  in which only Type-A traps are involved, the discharging trace under the next charging level,  $V_{g,ch} + \Delta V_{g,ch}$ , is shifted down to align these two curves within the region of 0.1eV from the charging level. Following this procedure up to the highest  $V_{g,ch}$ , the distribution of Type-A traps can be extracted. Type-B traps can be extracted by subtracting TypeA traps from the total. The extracted Type-A and Type-B traps are shown in **Fig.5(b)** and **Fig.6**.

**Fig. 3** Trap energy distribution after charging under different levels,  $V_{g,ch}$  for 1000sec at room temperature. The distribution traces under all  $V_{g,ch}$  are shown in (b). The distribution traces under two highest  $V_{g,disch}$  and three lowest  $V_{g,disch}$  are enlarged and shown in (a) and (c) respectively.

**Fig. 4** Illustration of charging Type-A (a) and Type-B (b) traps. After charging at Ef, Type-A traps will not change the energy level while Type-B traps drop from the ground states to the charged states at lower energy level. Simulation results [22] show that the oxygen vacancy may be the candidate for Type-B traps in which  $V_0^{-2}$  and  $V_0^{-2}$  for the ground states and the charged states respectively. For  $V_0^{-2}$  configuration ( $\bullet \circ$ ), it can act as an electron trap to capture one electron from the substrate and change to  $V_0^{-2}$  configuration ( $\bullet \bullet$ ).

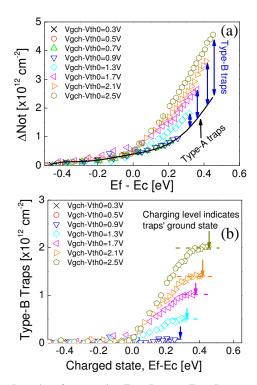

It is worth noting that the extracted distribution of Type-B traps shown in **Fig.6(b)** represents the charged state of such type of traps (i.e., switching traps) because the discharging traces used for the extraction are recorded after charging under certain  $V_{g,ch}$  (as illustrated in **Fig.6(a)**). More traps are switched when higher  $V_{g,ch}$  is applied and these switched traps are mainly above the Ec of InGaAs. Although the ground state of the Type-

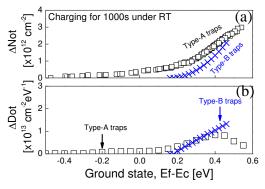

B traps are electrically neutral, their energy distribution can also be obtained. Under each  $V_{g,ch}$ , Type-B traps with their ground states below  $E(V_{g,ch})$  can be charged: i.e.  $E(V_{g,ch})$  is the energy level for the ground state. The total Type-B traps,  $\Delta N_{ot}$ , charged under this  $E(V_{g,ch})$  can be estimated from the flat region of the relevant discharging trace shown in **Fig.6(b)**. By plotting  $\Delta N_{ot}$ against  $E(V_{g,ch})$ , the energy distribution for the ground state of the Type-B traps is obtained, as shown in **Fig.7(a)**. Type-A traps are also shown for comparison. The result shows that Type-A traps spread within and beyond the band gap of InGaAs, while Type-B traps are mainly beyond the band gap. By differentiating  $\Delta N_{ot}$  against  $E_{f}$ - $E_{c}$ , the trap density per eV,  $\Delta D_{ot}$ , is obtained in **Fig.7(b)**. Type-A traps have a peak around 0.4 eV above Ec of InGaAs, while Type-B traps increase monotonically with higher ground levels.

**Fig. 5** (a) Illustration for Type-A traps extraction. The Solid lines denote the total trap distribution under different Vg\_ch level. Aligning two distributions between  $V_{g,ch1}$  and  $V_{g,ch2}$  to assure the region within  $\Delta E$  away from  $V_{g,ch1}$  overlap each other ('**O**'), Type-A traps in the energy range between  $V_{g,ch1}$  and  $V_{g,ch2}$  can be extracted. By following the procedure, the entire Type-A traps distribution can be obtained. (b) The Type-A traps extracted from the real measured data shown in Fig.3(b).

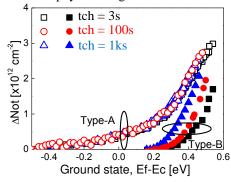

#### C. Impact of charging time

The charging time dependence of Type-A and Type–B traps are shown in **Fig. 8**. The number of charged Type-A traps does not increase for longer charging time, indicating that all the preexisting Type-A traps can be quickly filled to saturation. On the contrary, the number of charged Type-B traps increases with charging time. Compared with higher  $E_{f}$ - $E_{c}$ , the Type-B traps under low  $E_{f}$ - $E_{c}$  increases relatively slow. One speculation is because the channel electrons closer to Ec of the InGaAs are relatively less and therefore Type-B traps in this region take longer time to get charged.

**Fig. 6** (a) Procedure for extracting Type-B traps. Type-B traps can be extracted by subtracting Type-A traps from the total traps for each  $V_{g,ch}$  (b) Type-B defects extracted from the same set of data shown in Fig.3(b).

**Fig. 7** (a) Energy distribution of Type-A traps and the ground states of the Type-B traps. For Type-B traps, each point is taken from the highest trapping level of distribution trace for each  $V_{g,ch}$ .  $\Delta D_{ot}$  in (b) is the trap density by differentiating the data in (a). 5nm channel thickness are used.

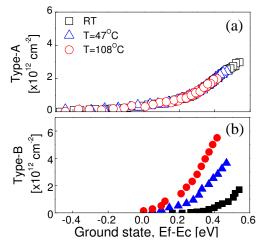

#### D.Impact of Temperature

The impact of temperature is also checked in this section. The Type-A traps will not switch their energy levels after charging and it is expected that their charging should be independent of the temperature [23]. On the contrary, Type-B traps can switch their energy levels after charging. If their trapping process can be described by the lattice relaxation multi-phonon emission (LRME) model, it is expected that their capture times reduce with higher temperature and therefore a strong temperature dependence in trapping can be observed [24]. Following the same extraction method, the energy distribution for the Type-A and Type-B traps are obtained under three temperatures in **Fig. 9(a) and (b)** respectively. As expected, the energy distribution for Type-A traps is independent of temperature in **Fig.9(a)**. The distributions of the Type-B traps in **Fig.9(b)** have a strong temperature dependence: for a fixed charging time, more traps

are charged at higher temperatures due to the phonon-assisted charging process. The different dependence on temperature and charging time supports that there exists two different types of traps with different physical origin.

Fig. 8 Charging time dependence of the Type-A and Type-B traps at room temperature. Devices with channel thickness of 5nm are used.

Fig. 9 Temperature dependence of the Type-A (a) and Type-B (b) traps after charging for 3s. Devices with channel thickness of 5nm are used.

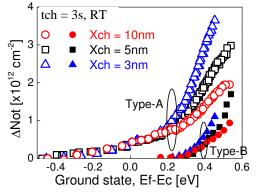

#### E. Impact of Channel thickness

The impact of channel thickness on these two types of traps is given in Fig.10. Both traps are sensitive to the InGaAs channel thickness. More charged traps are observed for thinner channel layer. This is unlikely caused by a poor interface for a thinner channel device, since similar sub-threshold swing values are found [2] for different channel thicknesses. The following reasons are likely to cause this thickness dependence: 1) the channel carriers get closer to the interface for thinner channels and the local electrical field can increase leading to higher trapping. 2) The quantization effect can be enhanced in the thinner channels, as corroborated by device simulations [2]. Enhanced quantization can populate higher energy levels, making the channel electrons energetically favorable for charging traps. This leads to larger PBTI in thinner channel [25] and might jeopardize the use of thin channels, although thinner channels could yield improved subthreshold swing [26] and reduced off-current for better LG-scalability [27]. III-V material has the potential to meet the high driving current/low Vdd requirement in future. For successful introduction of InGaAs devices in real production, a stable high-k gate stacks is equally important as optimizing transport properties of III-V channels, warranting further research and development.

Both Type-A and Type-B traps must be suppressed. One potential solution is to reduce defect density through process optimization [28]. For example, it has been reported that the border traps can be supressed through various passivation methods, such as (NH<sub>4</sub>)<sub>2</sub>S passivation and forming gas annealing [29]. Another possible solution is to use a different high-k layer which have a much narrower energy distribution of defect levels centred at shallower energy level in order to provide sufficient carrier-defect energy decoupling [25].

Fig. 10 Channel thickness dependence of Type-A and Type-B traps after charging for 3s under room temperature.

#### IV. CONCLUSIONS

We investigated the border traps in InGaAs nMOSFETs with Al<sub>2</sub>O<sub>3</sub> gate oxide and different channel thicknesses by using the discharging-based energy profiling technique. By analyzing the extracted trap energy distribution, two different types of border traps are identified. The Type-A traps do not change their energy level after charging, while Type-B traps will switch to a lower energy level after charging. Their different dependences on charging time and temperature strongly suggests that they have different physical origins. The number of charged traps of both types is found to increase when InGaAs channel becomes thinner. This is due to the enhanced quantization effect increasing the channel Fermi level and therefore making more defect levels thermodynamically favorable for trapping channel electrons. This effect jeopardizes the use of thin channels for improved L<sub>G</sub> scalability. Distinguishing these two different types of border traps is useful for process optimization.

#### V.REFERENCES

[1]ITRS, "International Technology Roadmap for semiconductors [online] Available: <u>http://www.itrs.net</u>," 2012.

[2]A. Alian, M. A. Pourghaderi, Y. Mols, M. Cantoro, T. Ivanov, N. Collaert, et al., "Impact of the channel thickness on the performance of ultrathin InGaAs channel MOSFET devices," in IEDM Tech. Dig., 2013, pp. 16.6.1-16.6.4.

[3]S. Takagi and M. Takenaka, "High mobility CMOS technologies using III-V/Ge channels on Si platform," in ULIS, 2012, pp. 1-4.

[4]T. Hoshii, S. Lee, R. Suzuki, N. Taoka, M. Yokoyama, H. Yamada, et al., "Reduction in interface state density of Al2O3/InGaAs metal-oxidesemiconductor interfaces by InGaAs surface nitridation," J. Appl. Phys., vol. 112, pp. -, 2012.

[5]H.-P. Chen, J. Ahn, P. C. McIntyre, and Y. Taur, "Effects of oxide thickness and temperature on dispersions in InGaAs MOS C-V characteristics," JVSTB, 2014.

[6]S. Deora, G. Bersuker, W. Y. Loh, D. Veksler, K. Matthews, T. W. Kim, "Positive Bias Instability and Recovery in InGaAs Channel nMOSFETs," IEEE Trans. Device Mater. Rel., vol. 13, pp. 507-514, 2013.

[7]S. Younghwan, P. Sunyoung, K. Taewook, O. Byoungchan, and S. Hyungcheol, "Characterization of Border Trap Density With the Multifrequency Charge Pumping Technique in Dual-Layer Gate Oxide," IEEE Trans. Electron Devices, vol. 58, pp. 2752-2758, 2011.

[9]M. J. Uren, D. J. Day, and M. J. Kirton, "1/f and random telegraph noise in silicon metal - oxide - semiconductor field - effect transistors," Appl. Phys. Lett., vol. 47, pp. 1195-1197, 1985.

[10] T. Grasser, H. Reisinger, P. J. Wagner, F. Schanovsky, W. Goes, and B. Kaczer, "The time dependent defect spectroscopy (TDDS) for the characterization of the bias temperature instability," in Reliability Physics Symposium (IRPS), pp. 16-25, 2010.

[11] B. H. Lee, C. D. Young, R. Choi, J. H. Sim, G. Bersuker, C. Y. Kang, et al., "Intrinsic characteristics of high-k devices and implications of fast transient charging effects (FTCE)," in IEDM Tech. Dig., 2004, pp. 859-862.

[12] X. Sun, S. Cui, A. Alian, G. Brammertz, C. Merckling, D. Lin, et al., "AC Transconductance Dispersion (ACGD): A Method to Profile Oxide Traps in MOSFETs Without Body Contact," IEEE Electron Device Lett., vol. 33, pp. 438-440, 2012.

[13] R. Degraeve, M. Cho, B. Govoreanu, B. Kaczer, M. B. Zahid, J. Van Houdt, et al., "Trap Spectroscopy by Charge Injection and Sensing (TSCIS): A quantitative electrical technique for studying defects in dielectric stacks," in IEDM Tech. Dig., 2008, pp. 1-4.

[14] S. W. M. Hatta, Z. Ji, J. F. Zhang, M. Duan, W. D. Zhang, N. Soin, et al., "Energy Distribution of Positive Charges in Gate Dielectric: Probing Technique and Impacts of Different Defects," IEEE Trans. Electron Devices, vol. 60, pp. 1745-1753, 2013.

[15] R. M. Wallace, P. C. Mcintyre, J. Kim, and Y. Nishi, "Atomic layer deposition of dielectrics on Ge and III-V materials for ultrahigh performance transistors," MRS Bull., vol. 34, p. 493, 2009.

[16] J. F. Zhang, Z. Ji, M. H. Chang, B. Kaczer, and G. Groeseneken, "Real Vth instability of pMOSFETs under practical operation conditions," in IEDM Tech. Dig., 2007, pp. 817-820.

[17] Z. Ji, J. F. Zhang, W. Zhang, G. Groeseneken, L. Pantisano, S. De Gendt, et al., "An assessment of the mobility degradation induced by remote charge scattering," Applied Physics Letters, vol. 95, pp. 263502-263502-3, 2009.

[18] B. Kaczer, T. Grasser, P. J. Roussel, J. Martin-Martinez, R. O'Connor, B. J. O'Sullivan, et al., "Ubiquitous relaxation in BTI stressing -- New evaluation and insights," in Proc. IRPS, 2008, pp. 20-27.

[19] I. H. Tan, G. L. Snider, L. D. Chang, and E. L. Hu, "A self - consistent solution of Schrödinger - Poisson equations using a nonuniform mesh," J. Appl. Phys., vol. 68, pp. 4071-4076, 1990.

[20] Z. Ji, S. F. W. M. Hatta, J. F. Zhang, J. G. Ma, W. Zhang, N. Soin, et al., "Negative bias temperature instability lifetime prediction: Problems and solutions," in IEDM Tech. Dig., 2013, pp. 15.6.1-15.6.4.

[21] F. P. Heiman and G. Warfield, "The effects of oxide traps on the MOS capacitance," IEEE Trans. Electron Devices, vol. 12, pp. 167-178, 1965.

[22] D. Liu and J. Robertson, "Oxygen vacancy levels and interfaces of Al2O3," Mirco. Eng., pp.1668, 2009.

[23] T. L. Tewksbury III, "Relaxation Effects in MOS Devices due to Tunnel Exchange with Near-Interface Oxide Traps," MIT, 1992.

[24] M. J. Kirton and M. J. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise," Adv. in Phy., vol. 38, pp. 367, 1989.

[25] J. Franco, A. Alian, B. Kaczer, D. Lin, T. Ivanov, A. Pourghaderi, et al., "Suitability of high-k gate oxides for III-V devices: A PBTI study in In0.53Ga0.47As devices with Al2O3," in Proc. IRPS, 2014, pp. 6A.2.1-6A.2.6.

[26] K. Tae-Woo, K. Dae-Hyun, and J. A. del Alamo, "Logic characteristics of 40 nm thin-channel InAs HEMTs," in Indium Phosphide & Related Materials (IPRM), 2010 International Conference on, 2010, pp. 1-4.

[27] K. Suzuki, T. Tanaka, Y. Tosaka and H. Horie, "Scaling theory for double-gate SOI MOSFET's," IEEE Trans. Electron Devices, pp. 2326, 1993.

[28] J. Ahn, T. Kent, E. Chagarov, K. Tang, A. C. Kummel, and P. C. McIntyre, "Arsenic decapping and pre-atomic layer deposition trimethylaluminum passivation of Al2O3/InGaAs(100) interfaces," Applied Physics Letters, vol. 103, p. 071602, 2013.

[29] B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. V. d. Walle, and P. C. McIntyre, "Origin and passivation of fixed charge in atomic layer deposited aluminum oxide gate insulators on chemically treated InGaAs substrates," Appl. Phys. Lett., p. 152908, 2010.