### **Coventry University**

### **DOCTOR OF PHILOSOPHY**

VLSI design and implementation of adaptive two-dimensional multilayer neural network architecture for image compression and decompression

Raj, P. Cyril Prasanna

Award date: 2010

Awarding institution: Coventry University M S Ramaiah University of Applied Sciences

Link to publication

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of this thesis for personal non-commercial research or study

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission from the copyright holder(s)

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 11. Dec. 2021

# VLSI DESIGN AND IMPLEMENTATION OF ADAPTIVE TWO-DIMENSIONAL MULTILAYER NEURAL NETWORK ARCHITECTURE FOR IMAGE COMPRESSION AND DECOMPRESSION

# P. Cyril Prasanna Raj

A thesis submitted in partial fulfillment of the University's requirements for the Degree of Doctor of Philosophy

**APRIL 2010**

# **Coventry University**

Research work carried out at M. S. RAMAIAH SCHOOL OF ADVANCED STUDIES, BANGALORE

# **COVENTRY UNIVERSITY**

**Doctoral Programme**

# Certificate

This is to certify that the PhD dissertation titled "VLSI Design and Implementation of Adaptive Two-Dimensional Multilayer Neural Network Architecture for Image Compression and Decompression" is a bonafied record of the work carried out by P. Cyril Prasanna Raj in partial fulfillment of requirements for the award of Degree of Doctor of Philosophy, Coventry University.

April - 2010

### **Declaration**

### VLSI Design and Implementation of Adaptive Two-Dimensional Multilayer Neural Network Architecture for Image Compression and Decompression

The thesis dissertation is submitted in partial fulfillment of academic requirements for Doctor of Philosophy Degree of Coventry University in Electronics and Computer Engineering. This dissertation is a result of my own investigation. All sections of the text and results, which have been obtained from other sources, are fully referenced. I understand that cheating and plagiarism constitute a breach of University regulations and will be dealt with accordingly.

Signature :

Name of the Student : P. Cyril Prasanna Raj

Date : April, 2010

### **Acknowledgement**

The successful completion of any task will be incomplete without complementing those who made it possible and whose guidance and encouragement made my efforts successful. The right way to express my gratitude is this section of my research work. I take immense pleasure and am overwhelmed at this point of time to express my sincere and heartfelt gratitude to all who were involved with me in successful completion of my research work.

With deep sense of gratitude I acknowledge the help and encouragement rendered by my President, **Dr. S. R. Shankapal**, Director, MSRSAS, Bangalore, for his valuable suggestions, support, encouragement and guidance. His advice has been my inspiration throughout my work at MSRSAS. I am grateful for his valuable feedback and suggestions throughout my career at MSRSAS and also successful completion of this work. I am and will always be indebted to him.

This research work has benefited from the help of many individuals. The discussion sessions and guidance of **Dr. S. L. Pinjare**, was key in realizing and improving this research work. I would like to thank him for his advice, guidance and support during the course of research. His timely support and motivation has been one of the most important aspects towards successful completion of this research work.

I am thankful to **Dr. Y. A. Vershinin**, Professor, Coventry University, U.K, for accepting to be my CU supervisor, his thought provoking suggestions and also key inputs provided during my thesis writing have helped me in successfully completing this work.

I would like to thank **Dr. M. D. Deshpande**, Head Research, MSRSAS, and Dr. **Govind R. Kadambi**, Dean (Academics), MSRSAS, Bangalore for providing necessary resources, facilities and excellent environment necessary for successful completion of this research. Their politeness in conduction of research reviews has really benefited me to complete the research work successfully.

I take this opportunity to express my gratitude to **Dr. Peter White**, Professor - Coventry University. During the review meetings his suggestions and directions have

helped me a lot in understanding the purpose of research. I am ever grateful to him for his kindness and patience listening during review meetings.

I also take great pleasure in expressing my thanks to **Dr. A. G. Ananth**, Respond Office, ISRO, Bangalore, **Shri. E. Devadoss**, Deputy Director, Respond Office, VSSC, and **Prof. Krishna Prasad** and his team, Bangalore for their support throughout the research work.

I take this opportunity to thank my colleagues at **EEE department faculty** members and students who have assisted me in carrying out this research and helped me in validating the results.

I would like to thank the following distinguished members who have constantly supported and helped me in completing the research work:

- 1. Ms. Sarojini, Head DSD, VSSC, Trivandrum

- 2. Shri. B. G. Suresh, Director, VSSC Trivandrum

- 3. Dr. T. V. Ananthapadmanabhan, MSRSAS

I wish to express my warm and sincere thanks to all my teaching staff, non-teaching staff at MSRSAS who directly or indirectly have been of great help for the successful completion of the thesis.

I would also thank my parents (my mother Mrs. G. Shanthy) for their unconditional love and support without which nothing would have been possible.

I take this opportunity to express my deepest and unconditional love to my wife Sujatha Cyril and my daughters Advika C. Sana and Arshia C. Sana without their support my research work would have not been able to see the light. I am always indebted to them and very sincerely acknowledge their patience exhibited during this period. Their support has motivated me in successful completion of my research work.

Above all I thank the almighty, for giving me strength and an opportunity to pursue my research work. It is his blessings that have guided and encouraged me all through my difficulties in successfully completing this work.

### **Abstract**

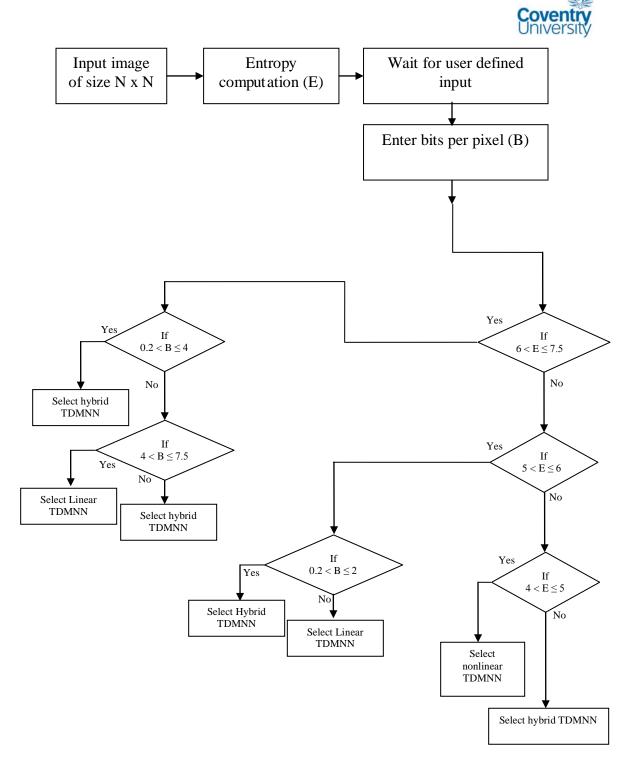

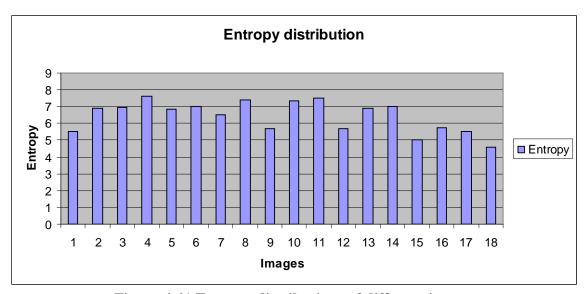

In this research, adaptive Two-Dimensional Multilayer Neural Network (TDMNN) architecture is proposed, designed and implemented for image compression and decompression. The adaptive TDMNN architecture performs image compression and decompression by automatically choosing one of the three (linear, nonlinear and hybrid) TDMNN architectures based on input image entropy and required compression ratio. The architecture is two-dimensional, 2D to 1D reordering of input image is avoided, as the TDMNN architecture is implemented using hybrid neural network, analog to digital conversion of image input is eliminated. The architecture is trained to reconstruct images in the presence of noise as well as channel errors.

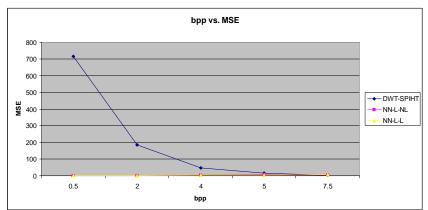

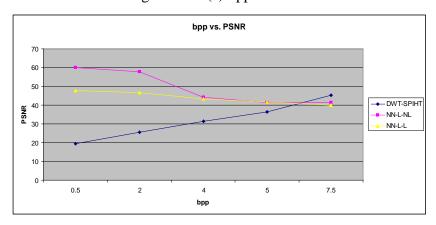

Software reference model for Adaptive TDMNN architecture is designed and modeled using Matlab. Modified backpropagation algorithm that can train two-dimensional network is proposed and is used to train the TDMNN architecture. Performance metrics such as Mean Square Error (MSE) and Peak Signal to Noise Ratio (PSNR) are computed and compared with well established DWT-SPIHT technique. There is 10% to 25% improvement in reconstructed image quality measured in terms of MSE and PSNR compared to DWT-SPIHT technique. Software reference model results show that the compression and decompression time for TDMNN architecture is less than 25 ms for image of size 256 x 256, which is 60 times faster than DWT-SPIHT technique.

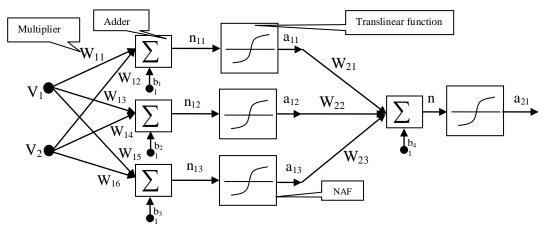

Based on weights and biases of the network obtained from the software reference model VLSI implementation of adaptive TDMNN architecture is carried out. A new hybrid multiplying DAC is designed that multiplies current intensities (analog input) with digital weights. The hybrid multiplier is integrated with adder and network function to realize a hybrid neuron cell. The hybrid neuron cell designed using 1420 transistors works at 200 MHz, consuming less than 232 mW of power, with full scale current of 65.535  $\mu$ A. Multiple hybrid neurons are integrated together to realize the 2-D adaptive multilayer neural network architecture.

### Contents

| 1.1 Preamble                                                             | 22 |

|--------------------------------------------------------------------------|----|

| 1.2 NEED FOR MULTIDIMENSIONAL NEURAL NETWORK ARCHITECTURE                | 24 |

| 1.3 NEED FOR NEURAL NETWORKS FOR IMAGE COMPRESSION                       | 28 |

| 1.4 MOTIVATION TO THIS WORK                                              | 34 |

| 1.5 NEED FOR ANALOG VLSI                                                 | 36 |

| 1.6 Thesis Contributions                                                 | 36 |

| 1.7 ASSUMPTIONS AND TERMINOLOGIES                                        | 38 |

| 1.8 HYPOTHESIS                                                           | 39 |

| 1.9 Thesis Overview4                                                     | 40 |

| CHAPTER 2 - NEURAL NETWORKS FOR IMAGE COMPRESSION: LITERATURE            |    |

| REVIEW                                                                   | 41 |

| 2.1 IMAGE COMPRESSION USING NEURAL NETWORKS 4                            | 41 |

| 2.2 LITERATURE REVIEW ON NEURAL NETWORKS FOR IMAGE COMPRESSION           | 46 |

| 2.3 ARTIFICIAL NEURAL NETWORK                                            | 55 |

| 2.4 NEURAL NETWORK ARCHITECTURES                                         | 57 |

| 2.4.1 Single Layer Neuron5                                               | 57 |

| 2.4.2 Multiple Layer of Neurons5                                         | 58 |

| 2.5 BACKPROPAGATION ALGORITHM                                            | 59 |

| 2.6 NEURAL NETWORKS IN ANALOG VLSI                                       | 50 |

| 2.6.1 Modular T-Mode Design6                                             | 51 |

| 2.7 DIGITAL IMPLEMENTATION OF NEURAL NETWORK ARCHITECTURES               | 67 |

| 2.8 FPGA IMPLEMENTATION OF NEURAL NETWORK ARCHITECTURE                   | 58 |

| 2.9 LITERATURE REVIEW SUMMARY ON VLSI IMPLEMENTATION OF NEURAL NETWORK 7 | 70 |

| CHAPTER 3 - PROBLEM DEFINITION                                           | 72 |

| 3.1 AIM                                                                  | 72 |

| 3.2 Objectives                                                           | 73 |

| 3.3 METHODS AND METHODOLOGIES TO CARRY OUT THE OBJECTIVES                | 73 |

## CHAPTER-4 2-D MULTILAYERED NEURAL NETWORK: DESIGN AND IMPLEMENTATION.......77 4.3 NEURAL NETWORK TRAINING 87 4.7 RESULTS AND ANALYSIS 100 4.10 ADAPTIVE TDMNN ARCHITECTURE FOR IMAGE COMPRESSION AND DECOMPRESSION 144 CHAPTER 5 – VLSI IMPLEMENTATION OF ADAPTIVE TDMNN ARCHITECTURE

| 5.4.1 Multiplier Design                                                      | 158 |

|------------------------------------------------------------------------------|-----|

| 5.4.2 Design of Multiplier Block                                             | 160 |

| 5.4.3 Adders                                                                 | 162 |

| 5.4.4 Neuron Activation Function (NAF)                                       | 162 |

| 5.4.5 Differential Amplifier Design as a Neuron Activation Function          | 162 |

| 5.5 REALIZATION OF NEURAL ARCHITECTURE USING ANALOG COMPONENTS               | 166 |

| 5.5.1 Backpropagation Algorithm                                              | 166 |

| 5.5.2 Validation for Digital Operation                                       | 168 |

| 5.6 IMAGE COMPRESSION AND DECOMPRESSION USING NN ARCHITECTURE                | 169 |

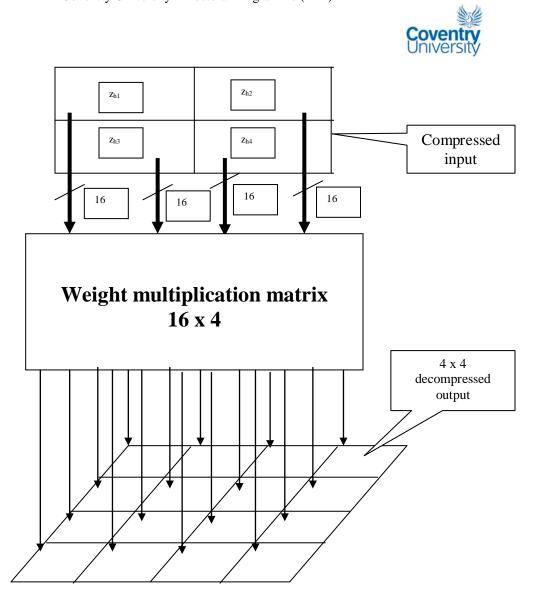

| 5.6.1 2-D multilayered Neural Network Architecture Design and Implementation | 172 |

| 5.6.2 Hybrid Neural Network Architecture                                     | 177 |

| 5.7 CURRENT STEERING DAC                                                     | 179 |

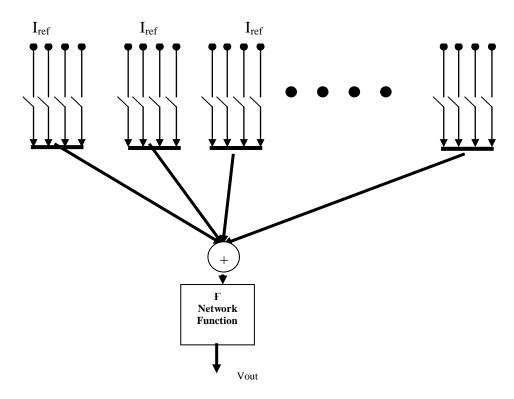

| 5.7.1 Novel Hybrid Current Steering DAC Multiplier                           | 181 |

| 5.7.2 Proposed MDAC Architecture                                             | 181 |

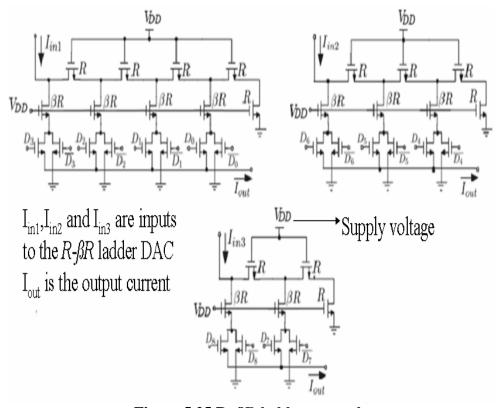

| 5.7.3 MDAC Architecture - R-\(\beta\)R Ladder Network                        | 183 |

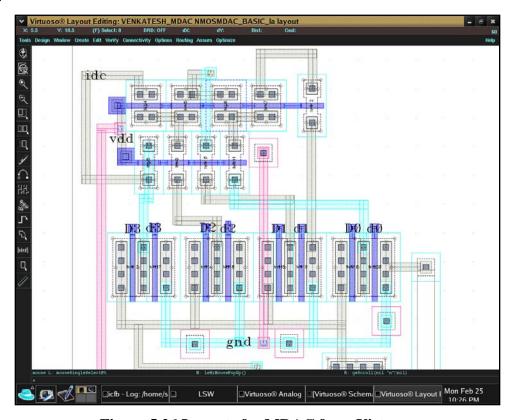

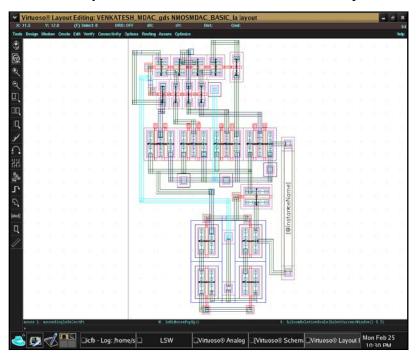

| 5.8 LAYOUTS OF PROPOSED MDAC                                                 | 187 |

| 5.9 TOP-LEVEL BLOCK DIAGRAM OF SINGLE NEURON USING HYBRID MULTIPLIER         | 193 |

| 5.10 TEST SETUP TO EVALUATE PERFORMANCE OF 2-D NETWORK ARCHITECTURE          | 195 |

| CHAPTER 6 – CONCLUSION                                                       | 200 |

| 6.1 CONCLUSION AND RECOMMENDATIONS FOR FUTURE WORK                           | 200 |

| LIST OF PUBLICATIONS                                                         | 204 |

| NATIONAL CONFERENCES:                                                        | 204 |

| International Conferences:                                                   | 204 |

| JOURNAL PUBLICATION:                                                         | 204 |

| REFERENCES                                                                   | 206 |

| APPENDIX-A BACKPROPAGATION ALGORITHM                                         | 220 |

| A.1 Introduction                                                             | 220 |

| A.2 SOFTWARE REFERENCE MODEL FOR NETWORK TRAINING:                           | 223 |

|                                                                              |     |

| APPENDIX-B                                                | 227 |

|-----------------------------------------------------------|-----|

| B.1 DIGITAL IMPLEMENTATION OF NEURAL NETWORK ARCHITECTURE | 227 |

| APPENDIX – C ENTROPY                                      | 240 |

| APPENDIX _ D SPICE CODE MODEL FOR ANALOG NEURAL NETWORK   | 241 |

# **List of Figures**

| 25 |

|----|

| 26 |

| 26 |

| 28 |

| 29 |

|    |

| 29 |

| 30 |

| 31 |

| S  |

| 31 |

|    |

| 32 |

|    |

| 32 |

|    |

| 32 |

|    |

| 3  |

| 36 |

| 12 |

| 13 |

| 14 |

| 16 |

| 19 |

| 52 |

| 55 |

|    |

| Figure 2.8 Different types of neural network architectures (Bose and Liang 2006)  | . 57 |

|-----------------------------------------------------------------------------------|------|

| Figure 2.9 Single neuron (Bose and Liang 2006)                                    | . 58 |

| Figure 2.10 Single layer of neuron (Bose and Liang 2006)                          | . 59 |

| Figure 2.11 Multiple layers neural network (Bose and Liang 2006)                  | . 59 |

| Figure 2.12 Neuron interconnections using transconductance devices (Bernabe 1992) | . 61 |

| Figure 2.13 Building blocks of analog neural network (Bernabe and Barranco 1992)  | . 62 |

| Figure 2.14 Neuron in the output layer (Hussein 1997)                             | . 63 |

| Figure 2.15 Analog neuron circuit diagram (Hussein 1997)                          | . 64 |

| Figure 2.16 Amplifier and adder circuit (Roy 1994)                                | . 65 |

| Figure 2.17 Neuron circuit (Chun, Bing-xue and Lu 2002)                           | . 66 |

| Figure 2.18 Analog accumulator (Chun, Bing-xue and Lu 2002)                       | . 66 |

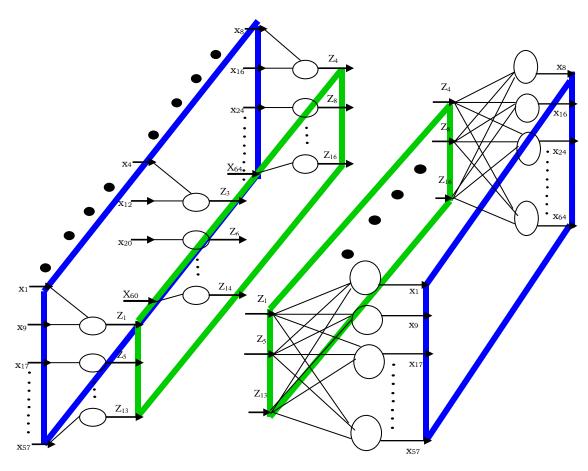

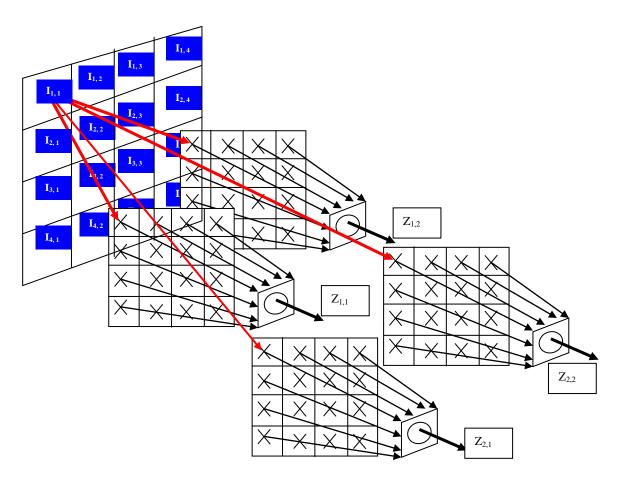

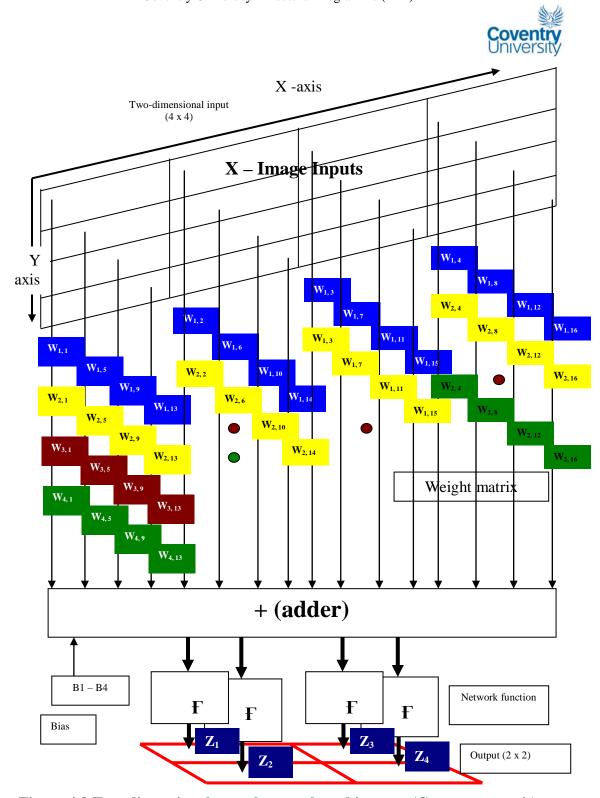

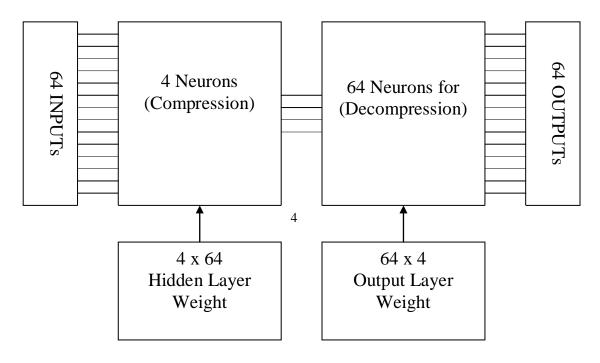

| Figure 4.1 2-D Architecture for image compression and decompression               | . 78 |

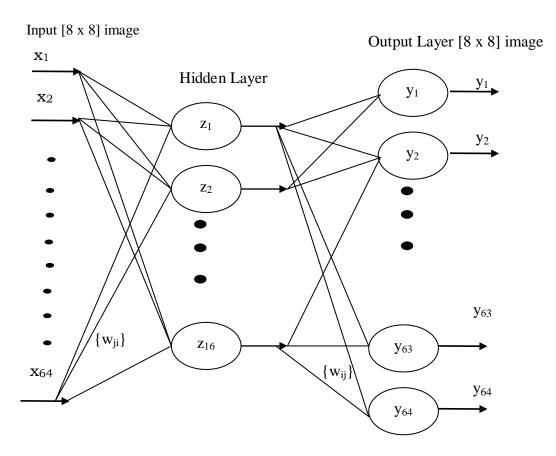

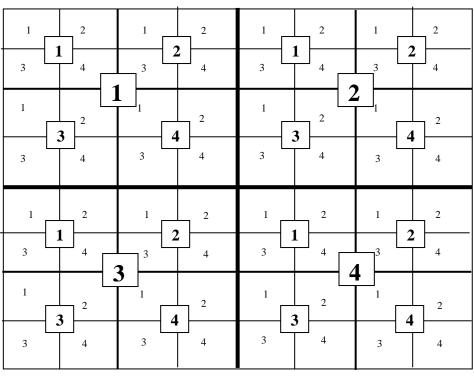

| Figure 4.2 2-Dimensional multilayer neural network                                | . 79 |

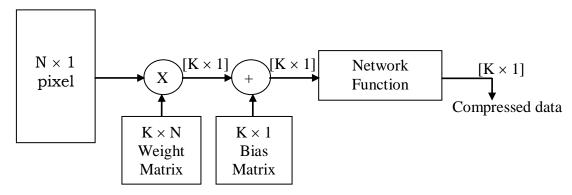

| Figure 4.3 2-D neural network architecture                                        | . 85 |

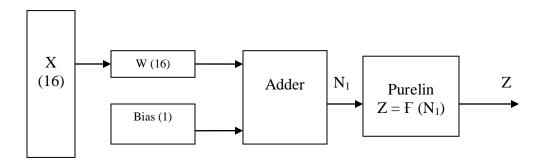

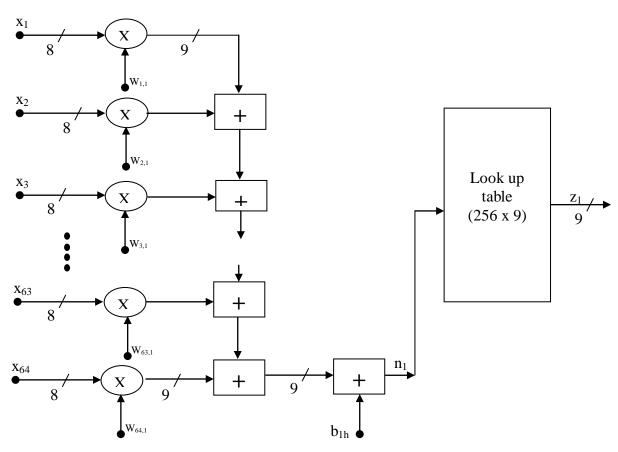

| Figure 4.4 Single neuron structure                                                | . 87 |

| Figure 4.5 Image data sets selected for training the neural network               | . 88 |

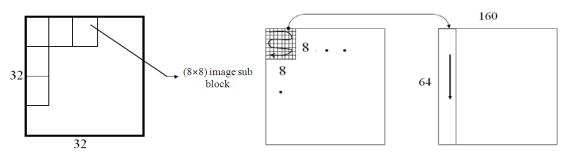

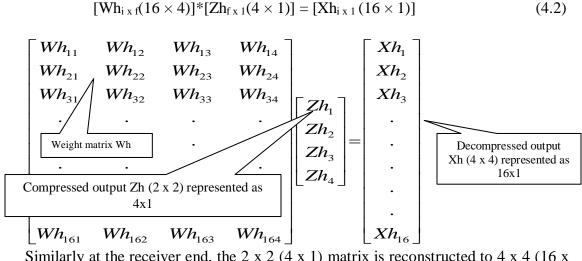

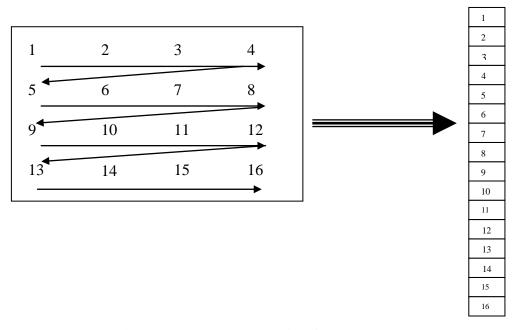

| Figure 4.6 Image reordering from 2-D to 1-D                                       | . 90 |

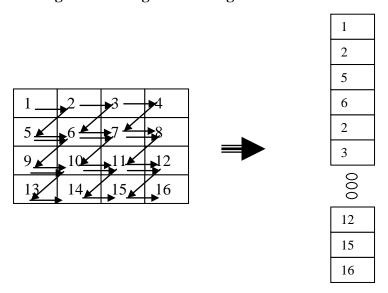

| Figure 4.7 Modified reordering scheme to improve correlation between pixels       | . 90 |

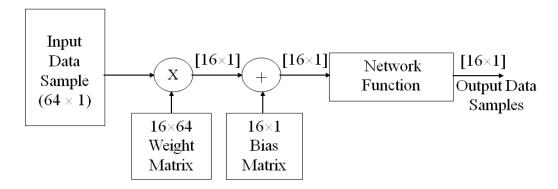

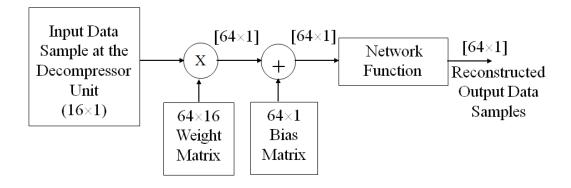

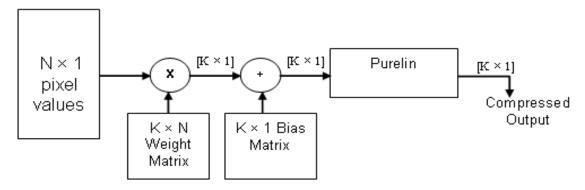

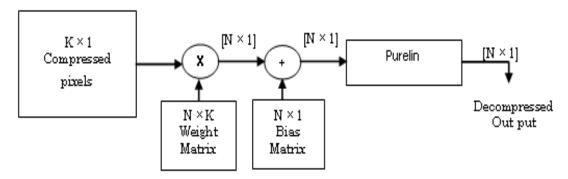

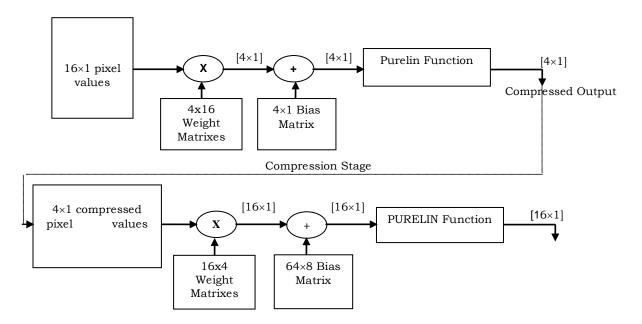

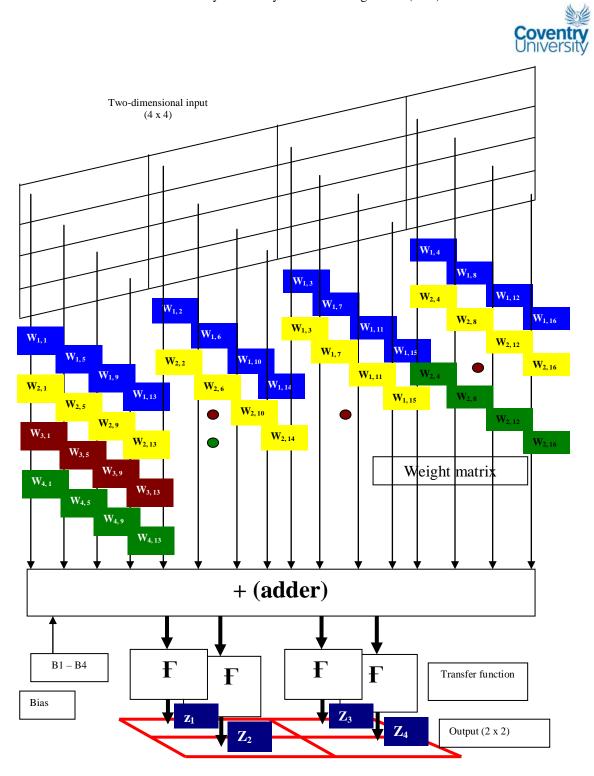

| Figure 4.8 Two-dimensional neural network architecture (Compressor unit)          | . 92 |

| Figure 4.9 level block diagram of neural network architecture for software model  | . 94 |

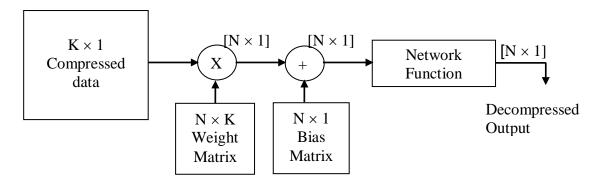

| Figure 4.10 Network functions Tansig, Pure linear and Logsig                      | . 95 |

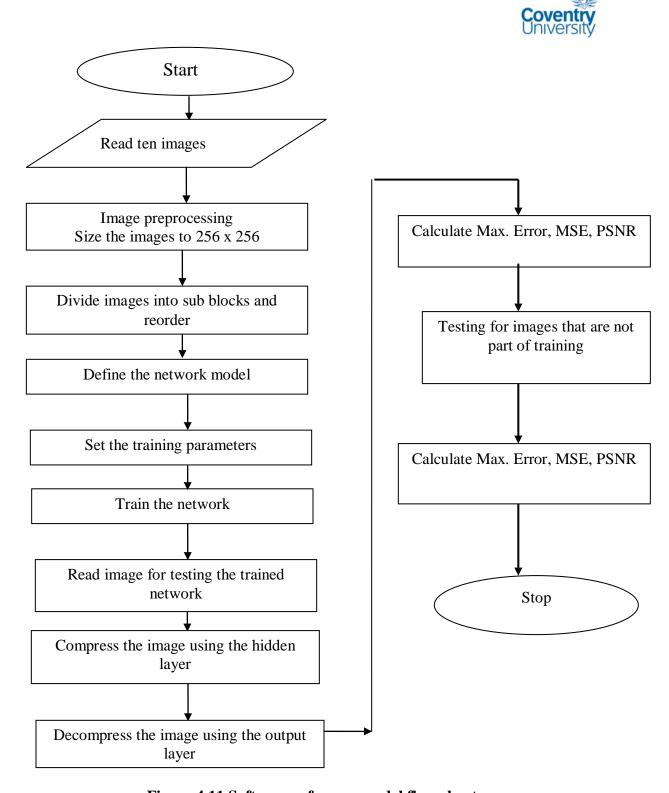

| Figure 4.11 Software reference model flow chart                                   | . 99 |

| Figure 4.12 Linear neural network for compression and decompression               | 102  |

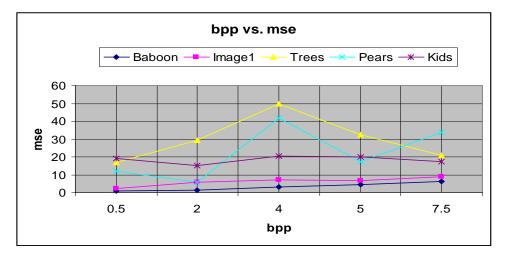

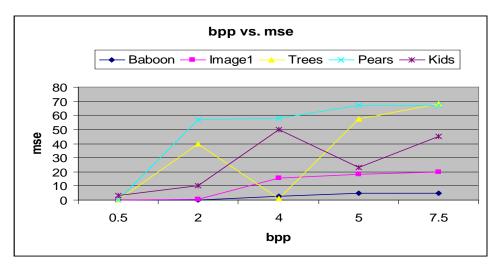

| Figure 4.13 Bpp vs. quality metrics for linear network for selected images        | 104  |

| Figure 4.14 Neural network for compression and decompression                      | 105  |

| Figure 4.15 Bpp vs. Quality metrics for hybrid network for selected images        | 107  |

| Figure 4.16 Decompressed output using linear network                              | 111  |

| Figure 4.17 Decompressed output using nonlinear network (a) baboon (b) Peppers 1  | 112  |

| Figure 4.18 Decompressed output using hybrid network (a) baboon (b) peppers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

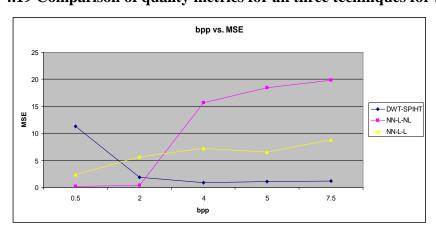

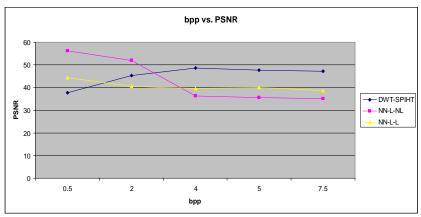

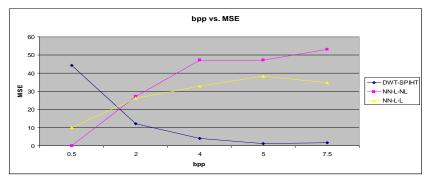

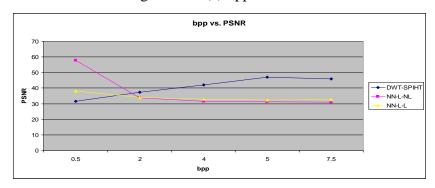

| Figure 4.19 Comparison of quality metrics for all three techniques for baboon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 117                                                         |

| Figure 4.20 Comparison of quality metrics for all three networks for Image1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 118                                                         |

| Figure 4.21 Comparison of quality metrics for all three networks for peppers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 119                                                         |

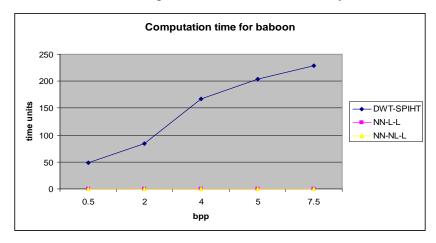

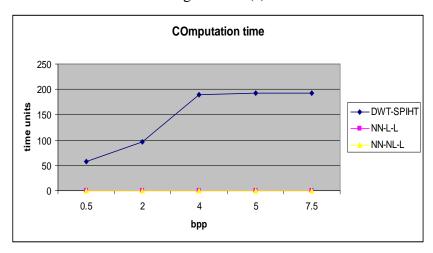

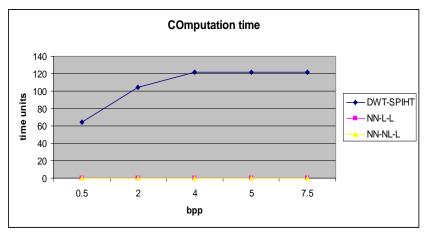

| Figure 4.22 Computation time vs. bpp (a) baboon (b) testim (c) image1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122                                                         |

| Figure 4.23 Results of 2-D multilayered neural network architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123                                                         |

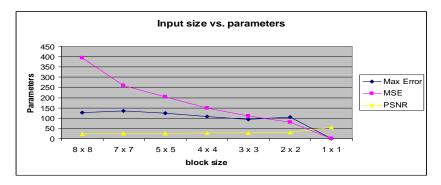

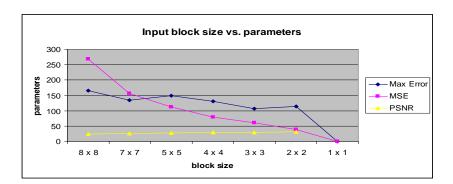

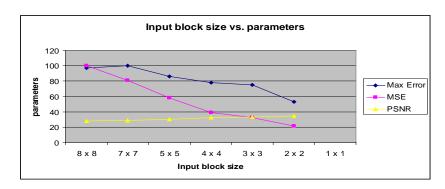

| Figure 4.24 Input block size vs. performance parameters for trees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 125                                                         |

| Figure 4.25 Input block size vs. performance parameters for pears                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 125                                                         |

| Figure 4.26 Input block size vs. performance parameters for peppers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 125                                                         |

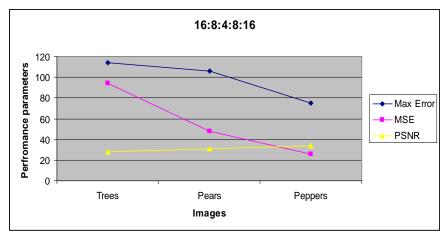

| Figure 4.27 Performance metrics for multiple hidden layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127                                                         |

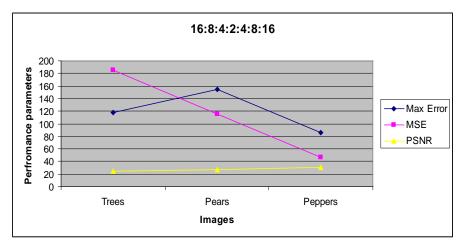

| Figure 4.28 Performance metrics for multiple hidden layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127                                                         |

| Figure 4.29 Error analysis for Baboon image with 0.5 bpp, and error at 60th bit position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                           |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 132                                                         |

| Figure 4.30 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 133                                                         |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134                                                         |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134<br>134                                                  |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position                                                                                                                                                                                                                                                                                                                                                                                                                    | 134<br>134<br>136                                           |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position  Figure 4.33 Compressed output                                                                                                                                                                                                                                                                                                                                                                                     | 134<br>134<br>136<br>137                                    |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position  Figure 4.33 Compressed output  Figure 4.34 Reconstructed output at 1bpp using linear network                                                                                                                                                                                                                                                                                                                      | 134<br>134<br>136<br>137                                    |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position  Figure 4.33 Compressed output  Figure 4.34 Reconstructed output at 1bpp using linear network  Figure 4.35 Reconstructed output at 0.5 bpp using linear network                                                                                                                                                                                                                                                    | 134<br>134<br>136<br>137<br>138                             |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position.  Figure 4.33 Compressed output  Figure 4.34 Reconstructed output at 1bpp using linear network  Figure 4.35 Reconstructed output at 0.5 bpp using linear network  Figure 4.36 Reconstructed output at 1 bpp using hybrid network                                                                                                                                                                                   | 134<br>134<br>136<br>137<br>138<br>138                      |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position  Figure 4.33 Compressed output  Figure 4.34 Reconstructed output at 1bpp using linear network  Figure 4.35 Reconstructed output at 0.5 bpp using linear network  Figure 4.36 Reconstructed output at 1 bpp using hybrid network  Figure 4.37 Reconstructed output at 0.5 bpp using hybrid network                                                                                                                  | 134<br>134<br>136<br>137<br>138<br>139                      |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position.  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position.  Figure 4.33 Compressed output  Figure 4.34 Reconstructed output at 1bpp using linear network.  Figure 4.35 Reconstructed output at 0.5 bpp using linear network.  Figure 4.36 Reconstructed output at 1 bpp using hybrid network.  Figure 4.37 Reconstructed output at 0.5 bpp using hybrid network.  Figure 4.38 Linear correlations between adjacent image pixels.                                            | 134<br>136<br>137<br>138<br>138<br>139<br>146               |

| Figure 4.31 Error analysis for Testim image with 0.5 bpp, and error at 60th bit position.  Figure 4.32 Error analysis for Test image with 0.5 bpp, and error at 60th bit position.  Figure 4.33 Compressed output.  Figure 4.34 Reconstructed output at 1bpp using linear network.  Figure 4.35 Reconstructed output at 0.5 bpp using linear network.  Figure 4.36 Reconstructed output at 1 bpp using hybrid network.  Figure 4.37 Reconstructed output at 0.5 bpp using hybrid network.  Figure 4.38 Linear correlations between adjacent image pixels.  Figure 4.39 Adaptive TDMNN architecture. | 134<br>134<br>136<br>137<br>138<br>138<br>139<br>146<br>148 |

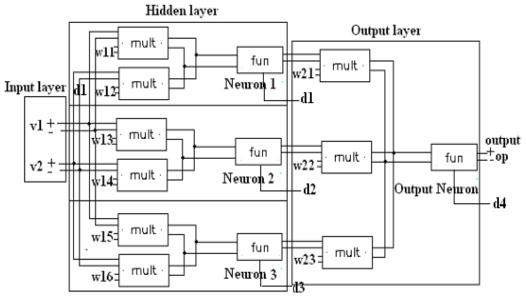

| Figure 5.2 Block diagram for 2:3:1 neuron                                      | 157 |

|--------------------------------------------------------------------------------|-----|

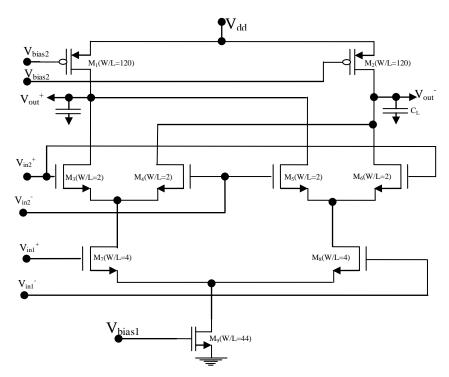

| Figure 5.3 Gilbert cell multiplier                                             | 158 |

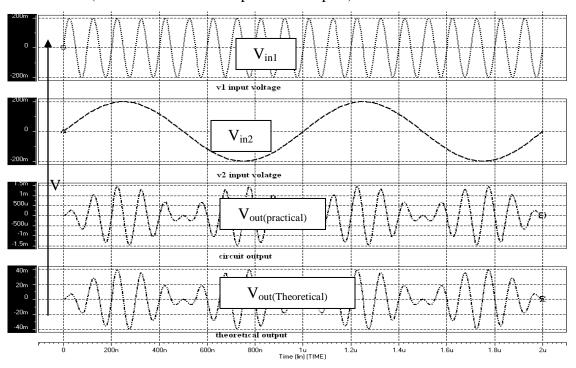

| Figure 5.4 Gilbert cell multiplier results                                     | 161 |

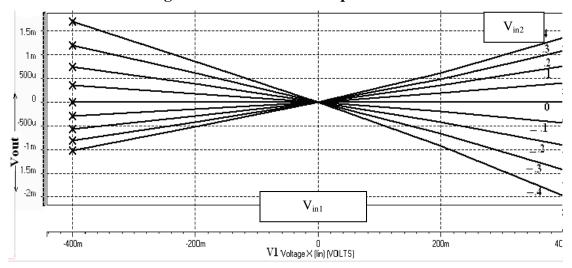

| Figure 5.5 DC characteristics of Gilbert cell multiplier                       | 161 |

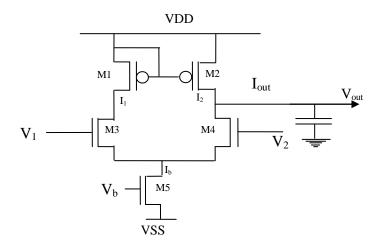

| Figure 5.6 Simple differential amplifier                                       | 163 |

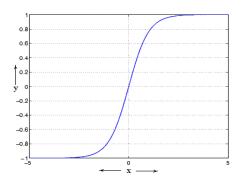

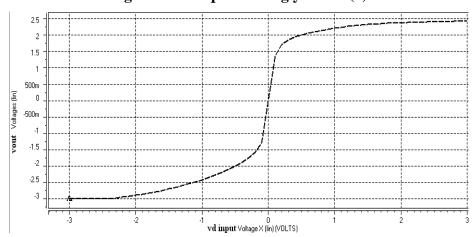

| Figure 5.7 Graph showing $y = tanh(x)$                                         | 165 |

| Figure 5.8 Circuit output for neuron activation function block (tan)           | 165 |

| Figure 5.9 Implementation of the neural architecture using analog blocks       | 166 |

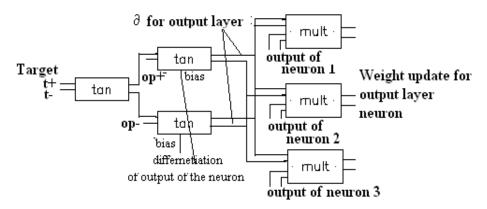

| Figure 5.10 Block diagram for weight update scheme for the output neuron       | 167 |

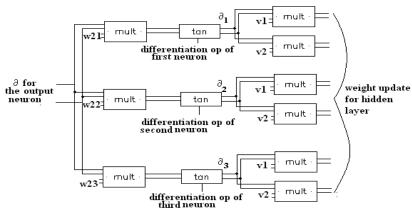

| Figure 5.11 Block diagram for weight update scheme for hidden layer neuron     | 168 |

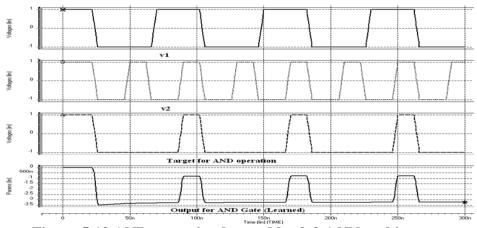

| Figure 5.12 AND operation learned by 2:3:1 NN architecture                     | 168 |

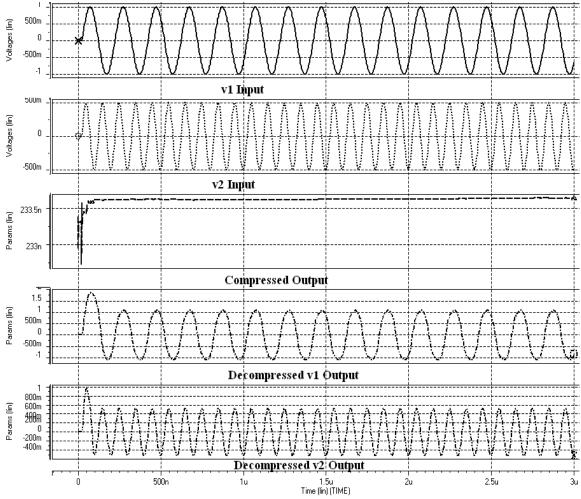

| Figure 5.13 Image compression and decompression simulation                     | 169 |

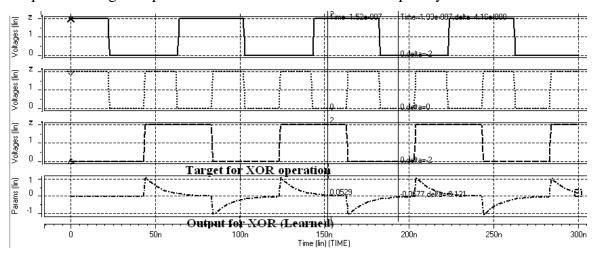

| Figure 5.14 Limitation of 2:3:1 neuron for XOR operation                       | 170 |

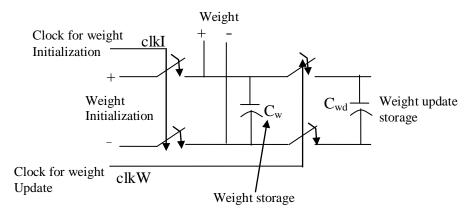

| Figure 5.15 Weight update and initialization scheme                            | 171 |

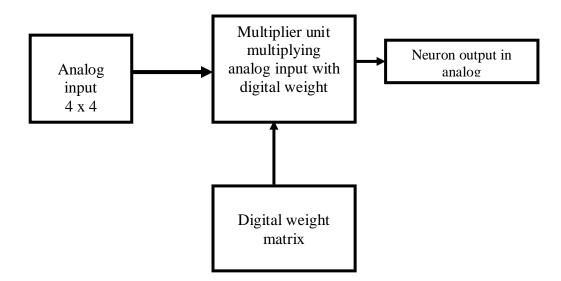

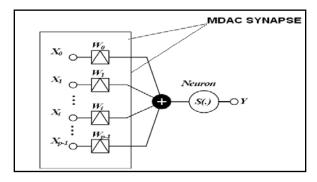

| Figure 5.16 Hybrid neuron model for image compression                          | 173 |

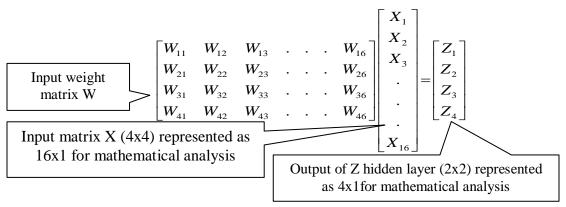

| Figure 5.17 2-D architecture of neural network (Hidden Layer)                  | 175 |

| Figure 5.18 Block diagram of single neuron with input and hidden layer         | 176 |

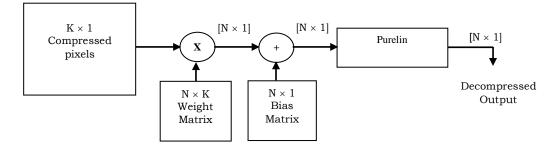

| Figure 5.19 Mathematical operation performed by the neural network             | 176 |

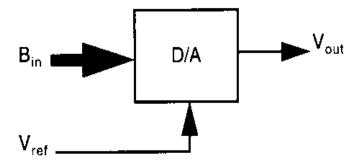

| Figure 5.20 DAC ports                                                          | 177 |

| Figure 5.21 Input-output transfer curve for ideal 2-bit DAC (Tiilikainen 2001) | 178 |

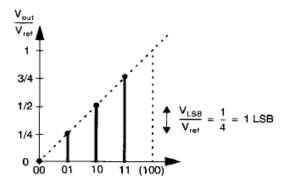

| Figure 5.22 Binary weighted current string DAC                                 | 179 |

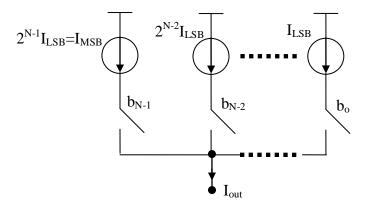

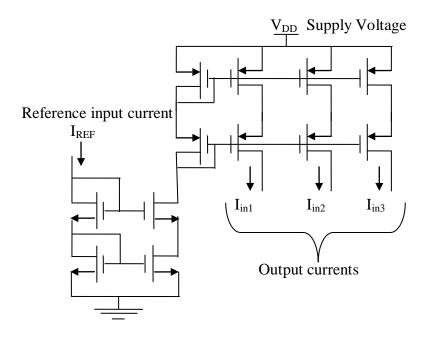

| Figure 5.23 Weighted current steering circuit                                  | 182 |

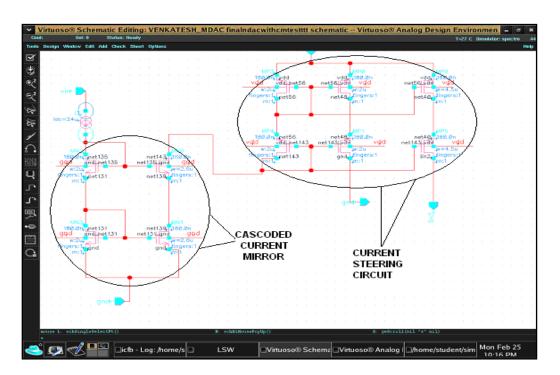

| Figure 5.24 Weighted current steering circuit schematic from Virtuoso          | 183 |

| Figure 5.25 R- βR ladder network                                               | 184 |

| Figure 5.26 Layouts for MDAC from Virtuoso                                     | 187 |

| Figure 5.27 GDSII Extracted view of proposed MDAC architecture                 | 188 |

| Figure 5.28 2D-multilayered architecture (hidden layer)                        | 191 |

| Figure 5.29 2D-multilayered architecture (output layer)                        | 192 |

|                                                                                |     |

| Figure 5.30 Neuron Cell                                                      | 193 |

|------------------------------------------------------------------------------|-----|

| Figure 5.31 Single neuron using hybrid cell multiplier (hidden layer)        | 194 |

| Figure 5.32 Hidden layer test setup.                                         | 195 |

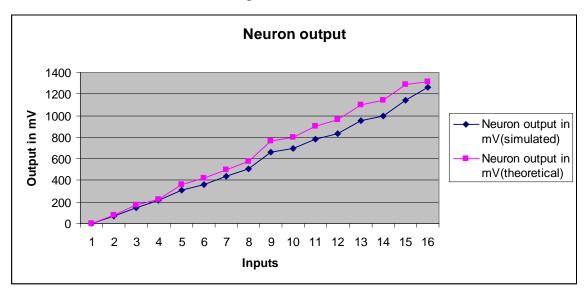

| Figure 5.33 Simulated results of single neuron cell                          | 197 |

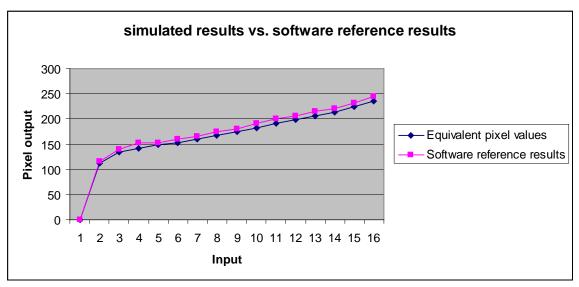

| Figure 5.34 Comparison of simulated results with software reference results  | 198 |

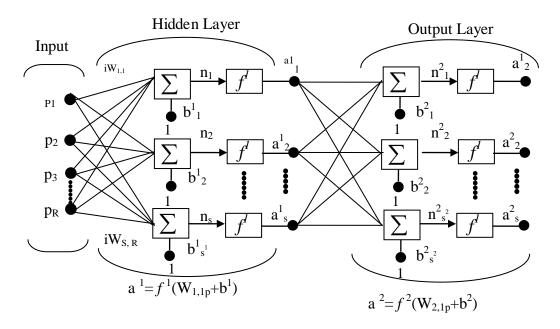

| Figure A.1 Multilayer neural network architecture                            | 220 |

| Figure B.1 NN architecture for image compression                             | 227 |

| Figure B.2 Single neuron architecture of hidden layer                        | 229 |

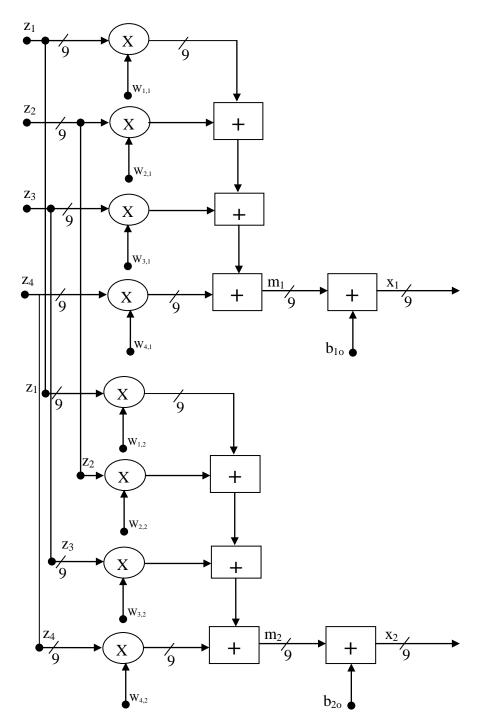

| Figure B.3 Output Layer neural network architecture (2 neurons)              | 230 |

| Figure B.4 Images for training and testing neural network architecture       | 232 |

| Figure B.5 Matlab and ModelSim results of decompressed image                 | 233 |

| Figure B.6 Results of image reconstruction using neural network architecture | 236 |

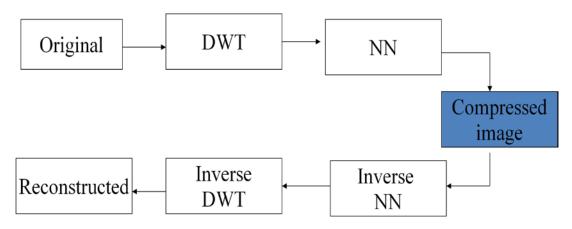

| Figure B.7 Hybrid architecture for image compression and decompression       | 237 |

| Figure B.8 Modified reordering scheme of sub-bands for NN training           | 238 |

| Figure B.9 Simulation results of hybrid architecture                         | 239 |

|                                                                              |     |

# **List of Tables**

| Table 1.1 Data rate of communication channels                                      | 22       |

|------------------------------------------------------------------------------------|----------|

| Table 4.1 TDMNN design parameters                                                  | 81       |

| Table 4.2 Neural network classification based on transfer function                 | 95       |

| Table 4.3 Compression ratio vs. Quality metrics for linear network                 | 102      |

| Table 4.4 Compression ratio vs. Quality metrics for hybrid network                 | 106      |

| Table 4.5 Comparison of Hybrid and Linear Network                                  | 109      |

| Table 4.6 Quality metric for all three networks                                    | 110      |

| Table 4.7 Comparison of quality metrics for linear, hybrid and DWT-SPIHT te        | chniques |

|                                                                                    | 114      |

| Table 4.8 Computation time with variation in bpp                                   | 120      |

| Table 4.9 Input block size vs. Performance parameters for tree image               | 124      |

| Table 4.10 Performance parameters for 16:8:4:8:16 network                          | 126      |

| Table 4.11 Performance parameters for 16:8:4:2:8:16 network                        | 126      |

| Table 4.12 Results of noise analysis (Salt and Pepper)                             | 129      |

| Table 4.13 Results of noise analysis (Poisson)                                     | 130      |

| Table 4.14 Results of noise analysis (Gaussian)                                    | 131      |

| Table 4.15 Error analysis for DWT-SPIHT technique                                  | 133      |

| Table 4.16 Error analysis for linear network                                       | 139      |

| Table 4.17 Error analysis for hybrid network                                       | 140      |

| Table 4.18 Adaptive TDMNN selection guide                                          | 152      |

| Table 4.19 Comparison of adaptive TDMNN with TDMNN                                 | 152      |

| Table 4.20 Comparison of adaptive TDMNN with TDMNN                                 | 153      |

| Table 4.21 Adaptive TDMNN architecture comparison                                  | 153      |

| Table 5.1 Binary equivalents of weight matrix                                      | 172      |

| Table 5.2 Theoretical, practical outputs with the error of the reference architect | ture 180 |

| Table 5.3 MDAC Transistors widths Tabulation for Proposed Architecture             | 185      |

|                                                                                    |          |

| Table 5.4 Comparisons of theoretical, simulation outputs for proposed architecture | . 186 |

|------------------------------------------------------------------------------------|-------|

| Table 5.5 Comparisons of various multiplier cells designed                         | . 189 |

| Table 5.6 Simulation results of single neuron cell                                 | 196   |

| Table 5.7 Image size and performance parameters                                    | 198   |

| Table 5.8 Compression ratio and MSE                                                | 199   |

| Table B.1 Complexity of neural network architecture                                | 233   |

| Table B.2 Comparison of multiplier architectures                                   | 234   |

| Table B.3 Synthesis results of 64-4-64 neural network architecture                 | . 235 |

| Table B.4 Single neuron comparison                                                 | . 235 |

|                                                                                    |       |

### **Nomenclature**

Bias current, A  $I_{bias}$  $I_{ds}$ Drain current MOSFET (Ampere), A  $I_{s}$ Static Current (Ampere), A Inductance, H L  $L_{\text{channel}} \\$ Channel length, m P Power gain in dB, output power, dBm **Quality Factor** Q R Resistance,  $\Omega$  $V_{bias}$ Bias voltage, V Gate-to-source voltage, V  $V_{gs}$ Threshold voltage, V  $V_{t}$

Capacitance, F

W Channel width, m

X Reactance,  $\Omega$ Z Impedance,  $\Omega$ α Closed Loop Gain

Angular frequency

C

$\begin{array}{lll} \omega & & \text{Angular frequency, rad/s} \\ \phi_n & & \text{Phase noise, dBc/Hz} \\ f & & \text{Frequency, Hz} \end{array}$

$g_m$  Transconductance,  $\Omega^{-1}$

$r_{ds}$  Drain-to-source resistance,  $\Omega$

$\begin{array}{lll} \mu A & \text{microampere} \\ \mu s & \text{micro} \ (10^{\text{-6}}) \text{ sec} \\ \text{ns} & \text{nano} \ (10^{\text{-9}}) \text{ sec} \\ \text{mm} & \text{millimeter} \end{array}$

MHz Mega Hertz (Frequency)

mW milli (10<sup>-3</sup>) Watt

W Watts

$p_i, v_i$  Input to NN (Volt)  $t_i$  Target input (Volt)

$v_g$  Gate voltage with respect to bulk (Volt), V

Source voltage with respect to bulk (Volt), V

### **Abbreviations**

1-D One-dimensional2-D Two-Dimensional

ADC Analog to Digital Converter

AI Artificial Intelligence ANN Artificial Neural Network

ASIC Application Specific Integrated Circuit

BP Backpropagation

BPNN Backpropagation Neural Network

CCD Charge Coupled Device CMOS Complementary MOS CR Compression Ratio

DAC Digital to Analog Converter DWT Discrete Wavelet Transform

DRC Design Rule Check

EDA Electronic Design Automation

EP Error Propagation FFN Feed Forward Network

FPGA Field Programmable Gate Array

GB Giga Byte

GDSII Graphical Data Source Interchange IDWT Inverse Discrete Wavelet Transform

JPEG Joint Pictures Experts Group

LAN Local Area Network

LVQ Learning Vector Quantization LVS Layout versus Schematic

MATLAB Matrix Lab

MaxError Maximum Error

Mbps Mega bits per second

ML Multilayer

MLP Multilayer Perceptron

MPEG Motion Pictures Experts Group

MSE Mean Square Error

MOS Metal Oxide Semiconductor

MOSFET MOS Field Effect Transistor

MVBP Modified Vogl Back Propagation

NA Neural Architecture NN Neural Network Op Output of NN

PCA Principal Component Analysis

PSNR Peak Signal to Noise Ratio

RRANN Reconfigurable Neural Network

SNR Signal to Noise Ratio

SPIHT Set Partitioned Integer Hierarchical Tree

SOM Self Organizing Map T Target for Learning

TDMNN Two-Dimensional Multilayer Neural Network

TSMC Taiwan Semiconductor Manufacturing Company

TV Television

VBP Vogl Back Propagation

VLSI Very Large Scale Integration

VSSC Vikram Sarabhai Space Centre

W/L Width / Length

### **Chapter 1 - Introduction**

Today's technological development has intruded into human lifestyle to such an extent that we feel uncomfortable without the use of electronic gadgets, information systems, household electronic equipments and display systems. We have started adopting and have got used to the latest electronic gadgets without which we feel isolated from rest of the world. The main reason to this is that, new products developed are sophisticated and addresses the needs of common man and these products are user-friendly and reliable. The electronic equipment available interacts with us and assists us in our day to day activities. Most of the commercially available electronics equipments have graphical display interfaces. Data in the form of images, motion pictures, icons and text displays on graphical displays assist humans and hence language or speech does not pose a barrier for the use of these gadgets worldwide. Visual representation tends to be perceived as being more efficient than the spoken or written word. As the demand for user-friendly equipment keeps increasing, image processing finds utmost importance. New applications based on image processing are being invented. Image processing of biomedical signal assist doctors and technicians to diagnose and treat patients, similarly processing of satellite images assist scientists to monitor and predict climate changes. In a time critical application such as launching of satellites, image processing assists in monitoring the launch of satellite using the launch vehicle from the base station. Controlling of launch vehicle is monitored based on image signal received at the base station. One of the major challenges working with image data is the size of image, or the number of bits required to represent visual information. A typical color image of size 512 x 512 consists of 6.5 Mega bits. Real time processing of image data, storage and transmission of image signals always pose a challenge for designers. Image enhancement, image restoration, image segmentation and image compression are the major image processing operations. In this work, compression of images based on neural network architectures for launch vehicle applications are addressed.

### 1.1 Preamble

Images that we see with our visual system are captured using image sensors in digital form and stored in memory banks. As the storage space for these digital samples consumes large space, cost increases. For example, a natural image captured from a sensor when digitized is converted to a 2-D matrix of size 256 x 256 pixels, each pixel representing intensity level of the natural image. Image sensors capture pixel intensities. Each pixel can be represented by 1 bit, 8 bit or 24 bit for black and white, gray scale and color image respectively. A color image of size 256 x 256 represented using 24 bit requires a storage space of 1.5 mega bits (256\*256\*24 = 1.5 Mb). A motion picture captured at 30 frames per second requires a storage space of 45 Mbps (1.5 Mb\*30 = 45 Mbps). The storage space for a three hour movie requires 486 Giga bits (4.5 Mb\*60\*60\*3 = 486 Giga bits). Table 1.1 present's bandwidth, transmission delay of three major communication links and transmission delay of uncompressed video signal.

Table 1.1 Data rate of communication channels

| Communication            | Data Rate  | Round Trip    | Transmission delay |

|--------------------------|------------|---------------|--------------------|

| Channel                  |            | Time (RTT) or | for uncompressed   |

|                          |            | Transmission  | video = Data Size  |

|                          |            | Delay         | (486 Gb)/Data Rate |

| DSL/ADSL                 | 256 Kbps   | 50 ms         | 202 minutes        |

| (William Stallings 2010) | to 40 Mbps |               |                    |

| Mobile broad band -      | 1.2 Mbps   | 100 ms        | 96 minutes         |

| HSDPA (Martin Sauter     | to 84 Mbps |               |                    |

| 2006)                    |            |               |                    |

| High-speed terrestrial   | 1 Gbps     | 1 ms          | 8 minutes          |

| network (Kai Chen et al. |            |               |                    |

| 2003)                    |            |               |                    |

Compression of raw video data thus makes it possible for transmission of data through existing communication links with minimum delay. Compressed images are transmitted through communication channels and are decompressed on the receiver side, without affecting the quality of picture. However, an image or video data being transmitted in real time have a minimum amount of delay of few milli seconds (Stuart

Cheshire 1996). This delay is mainly due to three factors. Firstly, huge data need to be compressed to the available channel bandwidth. This compression is accomplished using sophisticated software's and hardware's executing complex algorithms on high speed architectures, and this constitutes the maximum delay (Schaphorst and Richard 1999). Secondly, the compressed data is further encoded with security bits and parity bits for security and to avoid noise as they travel through the channel. In order to ensure that the data reaches the destination, they are also padded with specific bits to guide the encoded information through the channel and reach the destination. This processing of the compressed data using software and hardware devices introduces delay (Stuart Cheshire 1996). Thirdly, the transmitted data traveling through the channel also introduces delay and is called as the channel delay (Stuart Cheshire 1996). Delay in a communication system of few micro seconds to few milliseconds (Umashankar 2003) is negligible and usually not observed and is accepted. On the other hand, in crucial applications such as satellite launching where necessary control actions needs to taken based on visual information, a small amount of delay causes a major impact on the system and decision making. For example, if the trajectory path of the launch vehicle carrying a satellite is being monitored using visual information being captured and down linked in real time by onboard video processing systems, guiding the launch vehicle and launching of the satellite to appropriate destination requires critical and time bound control system. Based on the received visual information at the base station if suitable control actions have to take place, the delay in decompressing the compressed data has its impact, as the entire application is time critical. In this case the delay in signal reception has a major impact. Channel noise affecting the decompressed image is another major challenge. In a personal interview conducted by the author, Ms. Sarojini, Head, Digital Signal Design, Avionics Group, VSSC, Trivandrum, mentioned about the draw backs of the system that they had which was used to monitor the launch vehicle. In the discussion she emphasized on the need for a system that can work at 40 frames per second and also is immune to channel noise (Sarojini 2004). Information in an image when compressed, any error due

to noise in the channel affecting the compressed bits significantly affects the decompressed images. This research work carried out is an approach to firstly, minimize the system delay in compression and decompression of image applicable to time critical applications with novel architectures being proposed, designed, implemented and validated for image compression. Secondly, with the compressed data traveling through noisy channel, noise interference on the compressed data impacts the decompressed output, hence it is required to improve image quality at the receiver even in the presence of channel noise or error.

### 1.2 Need for Multidimensional Neural Network Architecture

Many practical solutions have been designed by eminent scientists and researchers adopting conventional techniques for compression and decompression of still and motion pictures. These systems are interoperable worldwide as they support uniform standards such as JPEG and MPEG (Chrysafis and Ortega 1998, Frescura, F., Giorni, M., Feci, C. and Cacopardi, S. 2003, Lian *et al.* 2003 and Mitchell and Pennebaker 1993, Signoroni, Lazzaroni and Leonardi 2003). JPEG and MPEG standards recommend guidelines for compressing and encoding the image signals, frame formats for transmission of compressed data and hardware requirements. These standards assume that the input image is digitized raw data represented in bmp, png or tiff formats (William and Joan 2004, *JPEG 2000 image coding system 2000*).

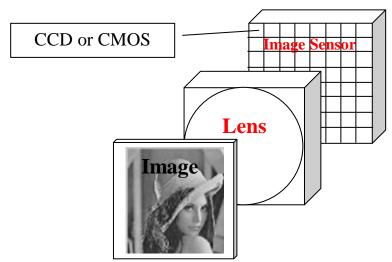

Natural images are captured using either Charged Coupled Devices (CCD) sensors (Tompsett, M. F. Amelio, G. F. Bertram, W. J., Jr. Buckley, R. R. McNamara, W. J. Mikkelsen, J. C. and Jr. Sealer, D.A. 1971) or Complementary Metal Oxide Semiconductor (CMOS) sensors (D. Renshaw, P. B. Denyer, G. Wang, and M. Lu 1990). Light intensity that is reflected from the object(s) is focused through the lens and strikes array of image sensors as shown in Fig. 1.1. Photo detectors that form the sensor array capture the light intensities and convert into voltage levels. Both type of sensors capture light intensities and convert into electrical signals. Interfacing circuit reads the electrical

signals from sensor arrays and processes the captured light intensities. Interfacing circuits for CCDs and CMOS sensor have different configuration (Dave Litwiller 2001). In a CCD sensor, light intensity reflected from the object(s) is focused through the lens that energizes the CCD that is arranged in 2-D array (Spatial). CCD sensors capture the light intensity of the image being focused. The image data captured is read out of the CCD array in the form of voltage or current equivalents.

Figure 1.1 Image sensor

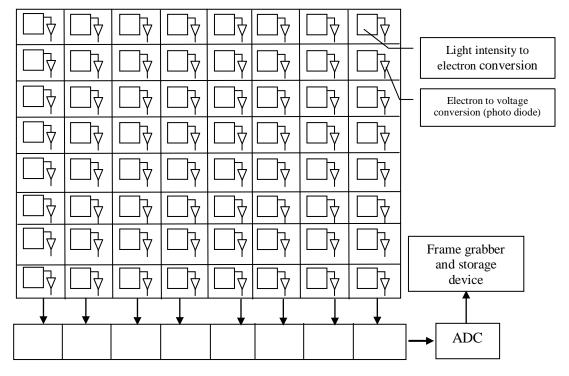

Fig. 1.2 demonstrates the read out operation of these intensities stored on the CCD devices (Karim Nice, Tracy V. Wilson and Gerald Gurevich 2004). Energized CCD array elements that accumulate charge corresponding to light intensity is read out serially and amplified by a gain factor (e.g.  $10~\mu\text{A/e}$ ). This way of serially reading out the data from the array reduces the complexity of drawing multiple wires from the array elements and also ensures the serialization of the data samples. The analog intensities read out from the matrix are further digitized to equivalent binary values in the Analog to Digital Converter (ADC) and stored in memory.

In a CMOS imaging sensor, arrays of active pixel sensors (Dickinson Alexander G., Eid El-Sayedi and Inglis Davida 1997) are placed at every pixel location that consists of a photo diode and active amplifier. Photo sensor captures light intensity and converts to voltage levels, which is converted to digital samples using ADC as shown in Fig. 1.3.

CMOS sensors have advantages compared to CCD sensors in terms of speed, responsivity, windowing, anti-blooming and reliability (Dave Litwiller 2001).

Figure 1.2 CCD based image sensor with analog readout

Figure 1.3 CMOS sensor based imaging unit

CCDs are superior to CMOS in terms of image quality and flexibility (Dave Litwiller 2001). Both technologies for imaging offer unique advantage, one common limitation is that, the voltage samples are read out serially to avoid number of wires from each sensor and additional electronic circuitry is required to convert analog to digital samples. Digital data read out of imaging unit which is in uncompressed form is stored in a digital memory.

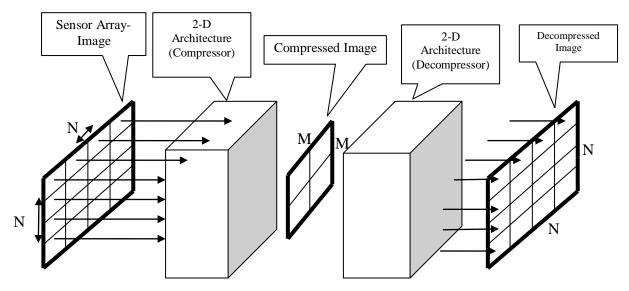

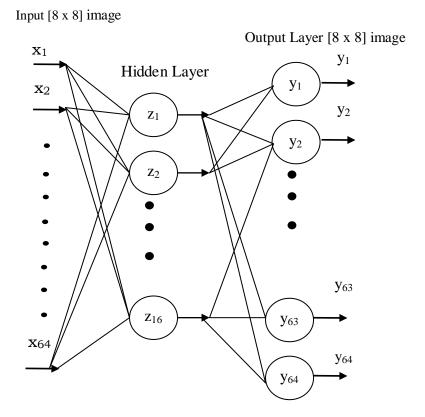

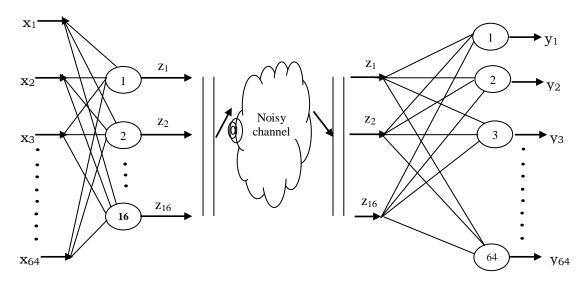

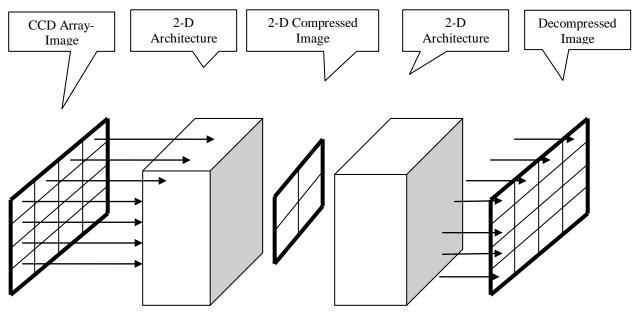

Digital samples are in uncompressed form and occupy more space. Compression of these samples is performed using the classical techniques as per the guidelines recommended by JPEG or MPEG. Two observations are made at this point, which leads to the scope of this research work. First, the time involved in reading out the 2-D array elements into 1-D elements can be avoided if a 2-D architecture that can accept the 2-D samples and can process the 2-D signals and perform compression. Second, instead of processing the 1-D data in digital domain, what if we process the 2-D analog data directly read from CCD devices or CMOS sensors using 2-D architectures. In a CMOS sensor array, the output of photo diodes which is current (I) can be processed using the 2-D architecture proposed in this work. In case of CCD sensor array, it is required to add additional circuits at every pixel location to convert charge to voltage samples, these voltage samples can be directly interfaced to the 2-D architecture. These two observations are the motivating factors to carry out this work.

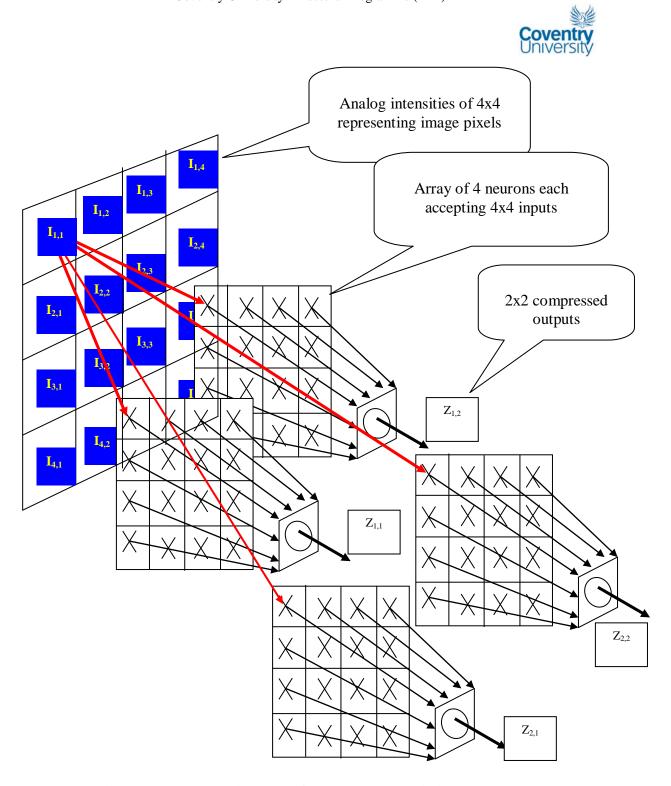

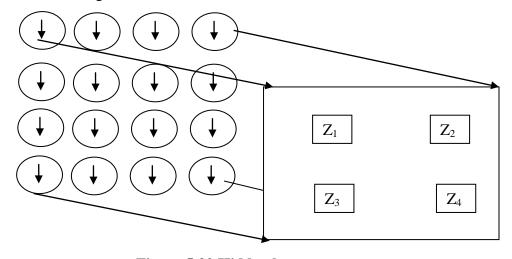

The 2-D architecture shown in Fig. 1.4 consists of image sensor array capturing brightness or intensity levels of image. These intensities are amplified and converted to equivalent current or voltage values. These N x N arrays of electrical samples are directly fed into a two dimensional architecture that processes the analog values and reduce the array dimension to M x M array elements. Since M < N, the number of pixel elements representing the image is compressed from N<sup>2</sup> to M<sup>2</sup> elements, which can be further encoded using 2-D techniques for storage and transmission. The advantage of 2-D architecture is that as the analog samples or pixel intensities are captured in the analog domain and processed using 2-D architecture, this avoids use of Analog to Digital

Converter (ADC) at the input side hence reduction in hardware complexity and also further reduces the delay.

Figure 1.4 2-D architecture for image capture and process

### 1.3 Need for Neural Networks for Image Compression

Classical techniques for image compression based on the recommendations from JPEG standards have been implemented on hardware and software, and these techniques have been used in electronic products and applications (Andra, Chakrabati and Acharya 2003, Chiang, J. S., Lin, Y. S and Hsieh, C. Y. 2002, Fang *et al.* 2003, Iain 2002 and Ong *et al.* 2002). Fig. 1.5 shows the basic block diagram of image compression and decompression unit.

The major blocks for image compression are transform coding, quantization and entropy coding (David and Michael 2001). Input to the system is image data with  $N_1$  bits per pixel, encoded data is the compressed out with  $N_2$  bits per pixel. As  $N_2$  is less than  $N_1$ , only  $N_2$  bits are required to represent  $N_1$  bits achieving compression. The compressed data  $N_2$  that consists of the entire information of  $N_1$  packed using  $N_2$  bits is transmitted through the channel. On the receiver side,  $N_2$  bits received is decompressed to  $N_1$  bits. However, during the transmission, if the compressed data gets corrupted due to noise in

This image has been removed

### Figure 1.5 Block diagram of image compression unit (David and Michael 2001)

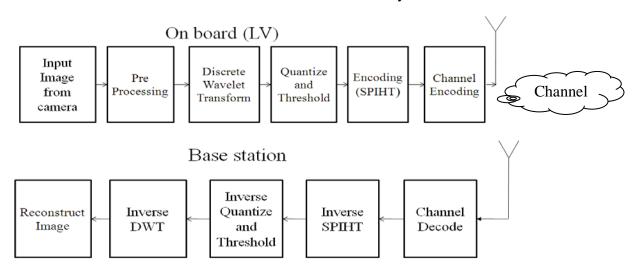

Fig. 1.6 shows the block diagram of JPEG 2000 standard based image compression and decompression unit, the transmitter is on the launch vehicle and the receiver is at the base station. It is required to capture the image sequences on board and compress the captured data and transmit to the base station, at the base station, the image is decompressed and used to track launch vehicle movement and satellite launch activity from the base station.

Figure 1.6 JPEG based image compression and decompression unit for launch vehicle applications

Launch Vehicle (LV) travels at a speed of 2 – 11 km/sec, launching the satellite into the orbit takes 10 minutes to 30 minutes (Chang IS 2007), thus it is required to monitor the satellite launch and onboard monitoring of launch vehicle trajectory. Camera mounted on the launch vehicle captures images, compresses and transmits to the base station. Based on the received visual information it is required to take corrective feedback from the base station. Due to noise in the channel if compressed data is corrupted, reconstructed image at the base station is distorted. Fig. 1.10 to Fig. 1.14 demonstrates the results for image compression using Discrete Wavelet Transform (DWT) and Set Partitioned Integer Hierarchical Tree (SPIHT) encoding techniques. This work was carried out as part of research work sponsored by Vikram Sarabhai Space Centre (VSSC), Trivandrum, India. The aim of this work was to identify the impact of bit errors due to channel noise on the reconstruction of compressed image. Noise in the channel causes a bit '1' to become '0' or vice versa. If the compressed bit information is corrupted due to channel noise, decompressing the image from the corrupted packets of received information affects the quality of the image.

This image has been removed

### Figure 1.7 Input image (pictorial representation)

Image shown in Fig. 1.7 is of size 512 x 512 is compressed using DWT and SPIHT technique and is used as a test case to illustrate the impact of channel noise on reconstructed image. Fig. 1.8 shows the pixel representation of the input image shown in Fig. 1.7 (only a part of the 512 x 512 image is presented in Fig. 1.8). Every pixel is

represented using 8 bits or expressed as 8 bits per pixel (bpp) or in general N<sub>1</sub> bits per pixel.

| 110 | 82  | 105 | 83  | 93  | 83  | 110 |

|-----|-----|-----|-----|-----|-----|-----|

| 123 | 93  | 83  | 110 | 80  | 93  | 93  |

| 146 | 119 | 105 | 80  | 105 | 71  | 83  |

| 142 | 83  | 119 | 86  | 59  | 93  | 74  |

| 146 | 119 | 119 | 93  | 83  | 59  | 71  |

| 137 | 93  | 105 | 83  | 119 | 80  | 89  |

| 110 | 82  | 83  | 82  | 54  | 93  | 71  |

| 119 | 127 | 119 | 77  | 93  | 54  | 93  |

| 93  | 119 | 93  | 83  | 96  | 93  | 83  |

| 119 | 137 | 110 | 119 | 80  | 93  | 69  |

| 93  | 119 | 146 | 105 | 69  | 83  | 105 |

| 105 | 110 | 93  | 110 | 105 | 59  | 119 |

| 110 | 123 | 137 | 142 | 83  | 105 | 93  |

Figure 1.8 Input image (pixel representation) represented using  $N_1$  bpp

Image of size 512 x 512 represented using 8 bpp (N<sub>1</sub> bpp) consists of 512\*512\*8  $(M_1)$  bits is represented using 512\*512\*0.1  $(M_2)$  bits after compression. Compression of 0.1 bpp (N<sub>2</sub> bits per pixel) implies that every 10 pixels of the input image are represented using 1 The compressed image is binary of data bpp. stream compressed form with N<sub>2</sub> bpp. The compressed M<sub>2</sub> bits that contain the information of M<sub>1</sub> bits, when transmitted may get corrupted in the channel due to channel noise. Fig. 1.9 to Fig. 1.13 presents the reconstructed images with channel noise affecting the compressed data. In this work, channel noise is introduced by complementing the binary values at randomly chosen bit positions in the compressed binary stream (hence forth called as bit errors).

Figure 1.9 Reconstructed image after error being introduced at 1st and 100th bit positions [Max. Error = 167, MSE = 219.13, PSNR = 24.72]

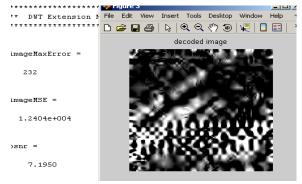

Figure 1.10 Reconstructed image after error being introduced at 10th and 30th bit positions [Max. Error = 232, MSE = 12404, PSNR = 7.19]

Figure 1.11 Reconstructed image after error being introduced at 10th and 50th bit positions [Max. Error = 187, MSE = 230, PSNR = 24.5]

These images have been removed

Figure 1.12 Reconstructed image after error being introduced at 1st and 2000th bit positions [Max. Error = 74, MSE = 120.78, PSNR = 27.31]

Figure 1.13 Reconstructed image after error being introduced at 1st and 10000th bit positions [Max. Error = 61, MSE = 116, PSNR = 27.48]

Observations made based on the simulation results illustrate that MSE and PSNR of the reconstructed image is affected due to bit errors. Bit errors in the initial part of the compressed data (within 30 bits in this example) can have significant effect on the reconstructed image. Fig. 1.10 showing the error in the 10<sup>th</sup> and 30<sup>th</sup> bit position having catastrophic effect on the reconstructed image. This is due to the fact that the DWT decomposes image into high frequency and low frequency components. As low frequency components of the decomposed image having significant information compared to high frequency components, encoding the decomposed image using SPIHT, low frequency components are arranged first in the encoded bit stream (Fang et al. 2003). Bit errors at the first few bits affect the quality of the image, because more information is stored in low frequency (Cyril 2005). Mean Square Error (MSE), Maximum Error and Peak Signal to Noise Ratio (PSNR) is calculated to estimate the quality of image. Poor quality image has higher MSE and lower PSNR.

The solution to this problem is to request for retransmission of the compressed image. MPEG and JPEG standards recommend use of channel encoding and retransmission schemes based on image quality at the receiver (Turner and Peterson 1992).

The technique proposed in this research does not require the need for error coding and retransmission schemes. This is achieved by use of neural network architectures for image compression and decompression. The objectives of this work are:

- 1. To prove the effectiveness of neural network architecture in reconstructing the image from the compressed data with noise in the transmission channel.

- 2. To propose, design, model and implement neural network architectures for image compression and decompression in analog VLSI.

### 1.4 Motivation to this Work

Vikram Sarabhai Space Centre (VSSC), Trivandrum an entity of Indian Space Research Organization (ISRO), under their RESPOND Scheme awarded the research project entitled "High speed DWT architectures for image compression for launch vehicle applications". The objective was to realize image compression algorithms on FPGA working at speed greater than 25 frames per second. This research work finds application in launch vehicles. As the launch vehicle carrying the satellite has to guide the satellite to the corresponding destination along the predefined path traveling at a speed of 11000 meters per second, monitoring this movement is very critical. Once the destination is reached i.e. the required orbit, the launch vehicle should eject satellite and place it into the corresponding orbit. High speed cameras are mounted to capture images to monitor and guide the launch vehicle to follow a trajectory path. This allows real time monitoring. The images are down linked to the base station from the launch vehicle. Since this is in real time and requires feedback from the base station for guidance of launch vehicle and successful launch of the satellite, high speed architectures are required to compress the images captured and down linked to the base station. The system is time critical as suitable action should be invoked observing the images being received at the base station. During transmission of compressed data channel error on the compressed data affects the quality of the decompressed image. One of the objectives was to find out the impact of

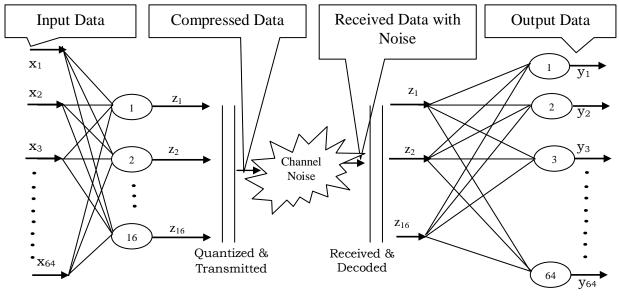

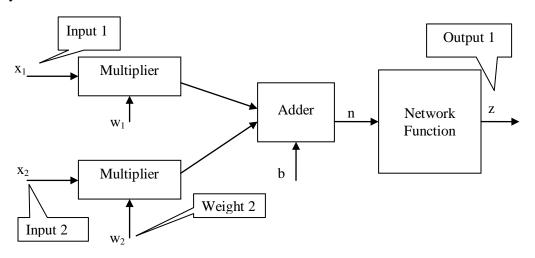

bit error on the decompressed data. During the experimentation, synthetic bit errors (change of '1' to '0' and '0' to '1') were randomly introduced at multiple positions in the compressed stream of data. Corrupted bit stream was decompressed to reproduce the images. It was observed that the bit errors on the first 30 bits of the compressed data had significant impact and reconstruction was impossible with the required information. Schemes recommended by JPEG and MPEG standards adopt retransmission of the frames. Also channel coding schemes are adopted to reduce the impact of error on signal during transmission. For launch vehicle applications as they are time critical retransmission of images may not be a possible solution. Hence, this motivated to investigate use of neural networks for image compression, as neural network techniques have been adopted for signal processing applications (Greenhil and Davies 1994, Guan, Anderson and Sutton 1997, Hanek and Ansari 1996, Lee and Degyvez 1996, Matsumoto, Kobayashi and Togawa 1992, Garris, Wilson and Blue 1998, and Paik and Katsaggelos 1993). Fig. 1.15 depicts simple neural network architecture with input and output neurons. As the network is trained with known set of input and outputs, neural network architectures are immune to noisy environment (Lampinen, J., Laaksonen, J. and Oja, E. 1997). Neural network architectures for image processing are flexible, reconfigurable and can work in noisy environment (Mitra and Yang 1999).

Multiple neurons in multiple layers include weight and bias elements. Weight and bias elements of the neuron decide the functionality of the network. Input image fed into the network, is processed by weight and bias elements of the network. Image processing functions like compression, enhancement, edge detection and segmentation can be executed by the neural network based on the type of weight and bias elements (Koh, Suk and Bhandarkar 1995, Kotropoulos, Magnisalis and Pitas 1994, Le, Thoma and Wechsler 1995, Lin, Tsao and Chen 1992, Manjunath, Simchony and Chellappa 1990, Marshall 1990, Ngan and Hu 1999, Opara and Worgotter 1996 and Ozkan, Dawant and Maciunas 1993). Functionality of neural network architecture depends on number of neurons and

neuron function, interconnection of neurons, and number of layers, weights and bias values.

Figure 1.14 Neural networks for image compression

## 1.5 Need for Analog VLSI

As the input captured from image sensors are analog samples, analog neural network architecture designed using multipliers, adders and network functions are required to process analog samples. The advantage of processing signals in analog domain is that the number of transistors required realizing neural network architecture is much less than digital implementation (Andreou 1992).

#### 1.6 Thesis Contributions

Image sensors capture light intensities of objects with frame rate varying from 30 frames per second to 1000 frames per second, with the time interval between frames are 33 ms and 1 ms respectively. Every frame of image which is in analog form is digitized and compressed using high speed architectures that perform complex digital signal processing algorithms. Hardware implementation of such algorithms consumes power and area, thus increasing the cost of the hardware.

Image conversion from analog to digital, (2-D analog discrete interval to 1-D digital space) introduces delay due to varied reasons. Conventional techniques use powerful transform and efficient encoding techniques for compression and decompression. This research work carried out addresses the issues such as image reordering and image compression together with the proposed architecture eliminating the bottleneck in image acquisition and compression. New techniques for compression and decompression based on neural networks are proposed, realized and validated.

This thesis work investigates the design, modelling, analog VLSI implementation and validation of multidimensional neural network architecture for image compression. The architecture processes image samples stored as current equivalents in 2-D matrix form for testing of the proposed design. Results obtained from this work are compared with digital implementation and software reference models for validation. Techniques and circuits proposed in this thesis are derived based on the references reported in the literature. Validations of the circuits designed and use of them for image compression are carried out based on the results obtained using software and firmware models.

This thesis work demonstrates the need for neural networks for image compression in certain critical application areas like satellite launch applications. The techniques discussed can also be extended to other applications by appropriately choosing network architecture and network functions according to the functionality and the network is trained to realize the functionality. This work uses parameters such as compression ratios, MSE, PSNR and hardware complexities in terms of power, delay and area as a measuring factor to estimate neural network performance. The thesis explores the tradeoff between classical techniques and the neural network techniques for image compression.

VLSI implementation of 2-D architecture for image compression using multilayered neural networks is also discussed in this thesis. This research work proposes two-dimensional multilayered neural network architecture for image compression, thus avoiding rearrangement of 2D image samples to 1D. As the compressed data is in the 2-D

space, two dimensional coding techniques can be adopted to quantize and encode the compressed image. Auto associative neural network uses backpropagation training algorithm for image compression (Sicuranzi, Ramponi, and Marsi 1990, Anthony, D., Taylor, E., D. and Barham, J. (1989), Kohno, Arai, and Imai 1990, Ivan Vilvonic 2006, Omer, M., Farhat, A., Momoh and Salami (2007), Hadi and Mansour 2009). Literature review shows that most of the training algorithm is aimed at training either a single or multilayered neuron. Training a multidimensional network for image compression has not been reported. This thesis work proposes a simplified backpropagation algorithm based training technique for the proposed Two-dimensional Multilayer Neural Network (TDMNN) architecture. Another contribution in this thesis is the design of hybrid architectures for implementation of TDMNN architecture for image compression. The architecture is called as hybrid as it multiplies analog input with digital weights and produces analog outputs. The digital weights (obtained during training) are stored in memory, the hybrid architectures perform multiplication of analog inputs with digital weights. Hybrid architecture is reconfigurable to realize different image processing functionalities by changing the digital weights of the network.

Software reference model for the proposed TDMNN architecture is designed, modeled and simulated using MATLAB. The reference model is trained using image data sets. The weights and biases for the network after training are used to model the compressor and the decompressor. The network is analyzed for its performance using multiple data sets.

## 1.7 Assumptions and Terminologies

This research work has the following assumptions made:

Image sensors are not interfaced to the proposed hardware for image compression, instead input reference model equivalent to the natural image is created using MATLAB for software simulations and Cadence Virtuoso for hardware simulations. Test images provided by the standard software are used for

simulation purpose assuming that the properties of these images are identical to a natural image captured from the camera.