brought to you by 🎛 CORE

Hindawi Publishing Corporation Journal of Nanomaterials Volume 2013, Article ID 127690, 7 pages http://dx.doi.org/10.1155/2013/127690

# Research Article

# Classic and Quantum Capacitances in Bernal Bilayer and Trilayer Graphene Field Effect Transistor

## Hatef Sadeghi, Daniel T. H. Lai, Jean-Michel Redoute, and Aladin Zayegh

- <sup>1</sup> The TEPS Research Group, College of Engineering and Science, Footscray Park Campus, Victoria University, Melbourne, VIC 3011, Australia

- <sup>2</sup> Department of Electrical and Computer Systems Engineering, Monash University, Melbourne, VIC 3800, Australia

Correspondence should be addressed to Hatef Sadeghi; hatef.sadeghi@live.vu.edu.au

Received 9 November 2012; Accepted 26 March 2013

Academic Editor: Nadya Mason

Copyright © 2013 Hatef Sadeghi et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Our focus in this study is on characterizing the capacitance voltage (C-V) behavior of Bernal stacking bilayer graphene (BG) and trilayer graphene (TG) as the channel of FET devices. The analytical models of quantum capacitance (QC) of BG and TG are presented. Although QC is smaller than the classic capacitance in conventional devices, its contribution to the total metal oxide semiconductor capacitor in graphene-based FET devices becomes significant in the nanoscale. Our calculation shows that QC increases with gate voltage in both BG and TG and decreases with temperature with some fluctuations. However, in bilayer graphene the fluctuation is higher due to its tunable band structure with external electric fields. In similar temperature and size, QC in metal oxide BG is higher than metal oxide TG configuration. Moreover, in both BG and TG, total capacitance is more affected by classic capacitance as the distance between gate electrode and channel increases. However, QC is more dominant when the channel becomes thinner into the nanoscale, and therefore we mostly deal with quantum capacitance in top gate in contrast with bottom gate that the classic capacitance is dominant.

#### 1. Introduction

As the fundamental miniaturization limits of integrated metal oxide (MOS) processes are being approached, the conventional path of scaling integrated processes, obeying Moore's law and correspondingly leading to smaller gate lengths and oxide thicknesses, is no longer meeting the performance and power consumption requirements [1]. Robert Dennard's scaling theory, published almost four decades ago, summarized how transistor and corresponding circuit parameter change when these are being scaled under ideal conditions, where *K* is the unitless scaling constant [2, 3]. Amongst these circuit parameters, reducing the thickness of the gate oxide has been a key contributor to scaling improvements. The resulting oxide capacitance between the gate electrode and the inverted channel is given by [4]:  $C_{\text{ox}} = \varepsilon_{\text{ox}} W L / t_{\text{ox}}$ , where W is the effective width, L is the effective length,  $t_{\rm ox}$  is the thickness of the gate oxide, and  $\varepsilon_{ox}$  is the permittivity of the gate insulator. The importance of a high oxide capacitance is illustrated by means of the drain current to gate-source voltage square law

relationship for a MOS transistor biased in saturation, namely, [5];  $I_d = \mu C_{\rm ox} W (V_{\rm gs} - V_t)^2 / 2L$  illustrates that increasing the oxide capacitance increases the transistor drain current for a given overdrive voltage.

Dennard's scaling theory predicted a scaling of *K* in the gate oxide capacitance between each process node, explained by the fact that W, L, and  $t_{ox}$  scale with K. Current integrated technologies use oxide thicknesses which are a few atomic layers thick, and as a result, they do not follow Dennard's theory regarding transistor density, performance, and power consumption. New materials, processes, and device architectures are continuously being researched so as to overcome current technological barriers. As an example, Intel's 65 nm process node transistors use a silicon dioxide with a thickness of 1.2 nm [6]; Intel's 22 nm process features a high-K and metal gate technology and manages to reduce the gate oxide thickness to 0.9 nm [7]. In future semiconductor technology, thinner material with a higher dielectric constant is expected to be used as gate insulators in MOS structures [8]. However, the gate capacitance of a MOS structure with a finite density of

states cannot be described properly by the oxide capacitance alone [9]. In nanoscale devices with strongly coupled gates, the quantum capacitance (QC) as high as hundreds of attofarads could be obtained due to a low density of states in the channel [10]. For these two reasons studying the quantum capacitance in new materials for future electronic devices is very important particularly when it becomes a dominant source of capacitance.

Graphene is a two-dimensional (2D) honeycomb lattice of an atomic layer of carbon. Exciting electronic, thermal, and photoelectronic properties of graphene as a two dimensional electron gas (2DEG) has attracted a huge scientific interest in recent years. After the discovery of graphene [11] the studies on electronic properties of this material are dramatically increased and some studies tuned toward the characterizing the multilayer of this material. Further investigation on bilayer and trilayer graphene shows that each of these materials shows different behavior rather than monolayer graphene [12, 13]. Linear band structure in monolayer graphene changes to quadratic with tunable gap in Bernal bilayer graphene (BG) and tunable band overlap in trilayer graphene (TG). This leads to different electronic structure in mono-, bi- and trilayer graphene.

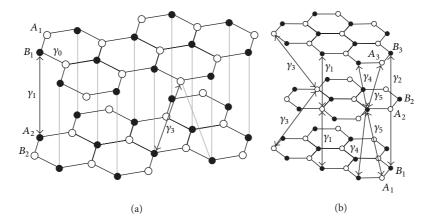

Graphene has an extraordinary mobility (200 times higher than in silicon), amazing current-handling capability (ten times higher than copper), very high thermal conductivity, and a long mean free path [14]. Graphene could be stacked in different forms but the only stable structure of BG is in Bernal or AB stacking structure. In addition, TG could be realized in two different forms: ABA (Bernal) and ABC [15, 16]. The common hexagonal structure found in graphite is Bernal stacking (ABA) [17]. From a geometrical point of view, AB BG and ABA TG have the same stacking configuration. Although the only geometrical difference between those is an additional graphene layer in TG, the effect of this additional layer in quantum capacitance of the system might be interesting point which has not been explored yet. Figure 1 demonstrates the Bernal stacking structure of BG (Figure 1(a)) and TG (Figure 1(b)) which come in to our focus through this paper.

The quantum capacitance of epitaxial and exfoliated single-layer graphene as well as nanoribbon has been investigated from both theoretical and experimental perspectives. Recently, Xu, et al. reported a mathematical description for monolayer graphene QC which is in good agreement with the experiment [18]. A V-shape dependence of QC versus gate voltage in monolayer graphene was observed [8, 10, 19–25]. However, fluctuation in QC of single layer graphene nanoribbon with van Hove singularities has been reported which is due to a gap in its band structure [26–30]. Also experiments show that multilayer graphene nanoribbons exhibit larger capacitance than their few-layer and single-layer graphene [31, 32]. To the best of our knowledge from the body of the literature, theoretical QC in bilayer and trilayer graphene has not been investigated yet.

Here, we present the mathematical model of capacitance where intrinsic AB bilayer graphene or ABA Trilayer graphene is used as channel of FET devices in low energy regime with respect to classical (electrostatic) and quantum aspects. Their behavior under different gate voltage as well as

temperature dependence will be studied. We show that although there is not the experimental evidence reported in the body of literature for C-V characteristic of BG and TG, this model shows good agreement with a reported DFT simulation for BG [33]. In addition, the behavior of quantum capacitance in BG and TG will be compared and discussed, and finally the effect of the distance between the center of the channel and the gate electrodes (top and bottom) on total capacitance will be argued.

#### 2. Band Structure

The starting point for understanding the electronic structure of bilayer and trilayer graphene is obtaining their band structure. The gap between the valence and conduction bands can be varied by external perpendicular electric field in BGs though it varies the overlap between the valence and conduction bands in TGs [34]. The spectra of full tight-binding Hamiltonian of Bernal stacked BGs and TGs [35–38] give their electronic structure. In the absence of an electric field, the band structure of *ABA* TG is a combination of monolayer and bilayer graphene band structures. Using perturbation theory [39], (1) and (2) represent the band structures (*E-k* relation) of the BGs [35] and TGs [36], respectively, in the presence of applied external perpendicular electric field:

$$E_{\mathrm{BG}}^{\pm}(k) = \pm \Delta \mp \alpha_{\mathrm{BG}} |k|^2 \pm \beta_{\mathrm{BG}} |k|^4, \tag{1}$$

$$E_{\rm TG}^{\pm}(k) = \pm \alpha_{\rm TG} |k| \mp \beta_{\rm TG} |k|^3,$$

(2)

where  $\alpha_{\rm BG} = v_g v_F^2/t_{\rm \perp BG}^2$ ,  $\beta_{\rm BG} = v_F^4/v_g t_{\rm \perp BG}^2$ ,  $\alpha_{\rm TG} = \sqrt{2}\Delta v_F/t_{\rm \perp TG}$ , and  $\beta_{\rm TG} = \sqrt{2}v_F/\Delta t_{\rm \perp TG}$  in which the upper layer and lower layers are at potential  $\pm \Delta = q v_g/2$  and the middle layer in TG is at zero potential. The Fermi velocity is  $v_F = \sqrt{3} \gamma_0 a/2\hbar \cong 10^6$  m/s [38], where hopping between  $\pi$  orbitals located at nearest neighbor atoms is  $\gamma_0 (\approx 3.1 \, {\rm eV})$  [40]. In addition, the interlayer hopping energy values for BGs and TGs are  $t_{\rm \perp BG} \approx 0.39 \, {\rm eV}$  and  $t_{\rm \perp TG} \approx 0.44 \, {\rm eV}$ , respectively [41].

### 3. Capacitance Model

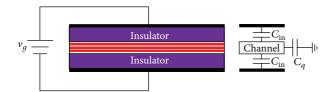

One way to determine device performance is measuring I-V (current-voltage) and C-V (capacitance-voltage) characteristics which would be helpful to understand fundamental electronic properties of the devices such as density of states (DOS), band energy, mobility, and conductance and that is why the capacitance is an important parameter [42]. In conventional MOSFETs, we usually deal with only the classic capacitance. However, device miniaturization to nanoscale has started to make QC comparable with electrostatic capacitance in channel. For instance, in carbon nanotube both classic and quantum capacitances are in the range of 1–10 pF/cm [43, 44]. Figure 1 shows the approximate circuited representation of a MOS capacitor including classic and quantum capacitors.

Electrostatic capacitance ( $C_{\rm ox}$ =  $2C_{\rm in}$ ) per unit area is proportional to the effective dielectric constant ( $\varepsilon$ ) divided by

FIGURE 1: Configuration of (a) AB (Bernal) BG with  $A_1B_1A_2B_2$  unit cell and in plain hopping ( $\gamma_0 = 3.14 \text{ eV}$ ) and interlayer hopping ( $\gamma_1 = 0.35 \text{ eV}$ ); (b) ABA (Bernal) TG with  $A_1B_1A_2B_2A_3B_3$  unit cell and interlayer hopping ( $\gamma_1 = 0.44 \text{ eV}$ ).

distance between two plates (*d*) as  $C_{\rm in} = \varepsilon/d$ . The channel capacitance can be expressed by the series combination of classic and QC (Figure 2) as  $C = C_{\rm ox}C_q(C_{\rm ox} + C_q)^{-1}$  [45]. For a double gate BGFET or TGFET with 285 nm SiO<sub>2</sub> insulator region where  $\varepsilon = 4$  [46], electrostatic capacitance could be easily obtained.

Carrier concentration in a band is achieved by integrating the Fermi-Dirac distribution function over energy band as  $n = \int D(E) f_F(E) dE$ , where D(E) and  $f_F(E) = (1 + \exp((E - E)))$  $(E_F)/(k_BT))^{-1}$  are available energy states (density of states) and Fermi-Dirac distribution function, respectively. Derivatives k over the energy  $D(E) = 2\pi k dk/dE$  with respect to E-k relation of Bernal BG and TG (1) and (2) indicate the density of states as  $D_{\rm BG}(E) = 2\pi (4\beta_{\rm BG}k^2 - 2\alpha_{\rm BG})^{-1}$  for Bernal stacking BG and  $D_{\text{TG}}(E) = 2\pi k (\alpha_{\text{TG}} - 3\beta_{\text{TG}}k^2)^{-1}$  for Bernal stacking TG. Employing the quadratic and Cardano's solutions for quadratic and cubic equations [47], the momentum (k) can be obtained from E-k relations of both Bernal stacking BG and TG. Averaged density of states over a few  $k_BT$  around Fermi level indicates the quantum capacitance  $(C_a(E))$  $q^2 \int dED(E)F_T(E)$ , where  $(F_T(E) = df(E)/dE)$  is a thermal broadening function [45]. Therefore, by substituting  $D_{BG}(E)$ and  $D_{\mathrm{TG}}(E)$  into the QC mathematical expression  $(C_q(E))$ , the quantum capacitance of BGs and TGs could be obtained as follows:

$$C_{qBG} = \frac{WLq^{2}}{4\pi^{2}} \times \int_{0}^{+\infty} \frac{2\pi e^{(E-E_{F})/k_{B}T} dE}{k_{B}T \left(4\beta_{BG} \left(|A\pm B|\right) - 2\alpha_{BG}\right) \left(1 + e^{(E-E_{F})/k_{B}T}\right)},$$

$$C_{qTG} = \frac{WLq^{2}}{4\pi^{2}} \times \int_{0}^{+\infty} \left(2\pi e^{(E-E_{F})/k_{B}T} \left|\sqrt[3]{C+D} + \sqrt[3]{C-D}\right| dE\right)$$

$$\times \left(k_B T \left(\alpha_{\rm TG} - 3\beta_{\rm TG} \left(\left|\sqrt[3]{C+D} + \sqrt[3]{C-D}\right|\right)^2\right) \times \left(1 + e^{(E-E_F)/k_B T}\right)^{-1},\tag{4}$$

where  $A = -\alpha_{\rm BG}/2\beta_{\rm BG}$ ,  $B = 0.5\sqrt{A^2/4 - 4(E-\Delta)/\beta_{\rm BG}}$ ,  $C = -E/2\beta_{\rm TG}$ , and  $D = \sqrt{(-\alpha_{\rm TG}/3\beta_{\rm TG})^3 + (E/2\beta_{\rm TG})^2}$ . By changing the variables as  $x = (E-\Delta)/k_BT$  and  $\eta = (E_F-\Delta)/k_BT$ , (3) and (4) could be readily written as

$$C_{qBG} = \frac{WLq^{2}}{2\pi} \int_{0}^{vg} \frac{e^{x-\eta}dx}{(4\beta_{BG}(|A\pm B'|) - 2\alpha_{BG})(1 + e^{x-\eta})},$$

(5)

$$C_{qTG} = \frac{WLq^{2}}{2\pi} \times \int_{0}^{vg} \left( e^{x-\eta} \left| \sqrt[3]{C' + D'} + \sqrt[3]{C' - D'} \right| dx \right) \times \left( \left( \alpha_{TG} - 3\beta_{TG} \left( \left| \sqrt[3]{C' + D'} + \sqrt[3]{C' - D'} \right| \right)^{2} \right) \times (1 + e^{x-\eta}) \right)^{-1},$$

(6)

where

$$A = -\alpha_{\rm BG}/2\beta_{\rm BG}$$

,  $B' = 0.5\sqrt{A^2/4 - 4(xk_BT)/\beta_{\rm BG}}$ ,  $C' = -(xk_BT + \Delta)/2\beta_{\rm TG}$ , and  $D' = \sqrt{(-\alpha_{\rm TG}/3\beta_{\rm TG})^3 + ((xk_BT + \Delta)/2\beta_{\rm TG})^2}$ . Equations (5) and (6) express QC in  $AB$  BG and  $ABA$  TG where they are used as channels in FET devices.

Recently, experimental work has been done to determine QC in TG-metal Schottky contact [48] as well as a DFT-based simulation to determine QC on Bernal BG [33]. QC is expected to be increased by gate voltage with some fluctuation. Fiori and Iannaccone showed by DFT-based simulation calculation that QC is increased by gate voltage

FIGURE 2: Circuited representation of metal oxide bi-/trilayer graphene capacitor.

([-0.15 0.15] V) around Fermi level in Bernal BGFET which our analytical model shows good agreement with as well. However, they reported in a low range of gate voltage. Here not only we present the analytical model of a BG QC, which not considered yet; to the best of our knowledge, there is no detailed work (theoretical or experimental) reported in the existing body of literature on Bernal TG quantum capacitance. It is apparent that the presented single band approximation model applicable for a proper range of the gate voltages. However, for very high gate voltages, a modified model which takes the multiband effect [37] into account is needed.

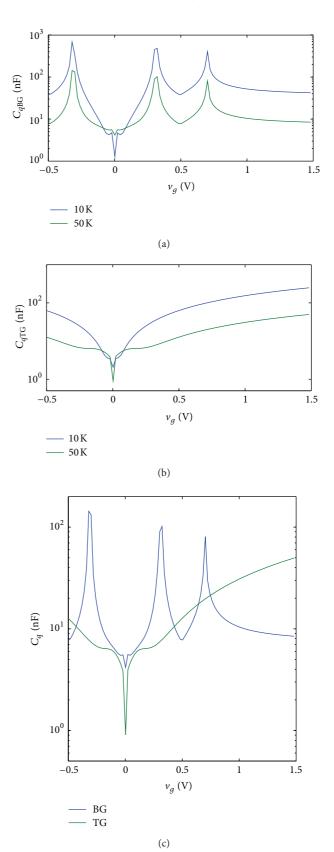

Our calculation result shows that around the neutrality point (Fermi level which is set to zero here) QC is increased for both BG and TG as shown in Figure 3. Figure 3(a) shows QC of BG in different temperatures. Fluctuations in the graph could be explained by the behavior of the density of states versus electric field as quantum capacitance is proportional to density of states. In addition, minimum QC decreases with increasing temperature. However, QC increases with higher rate in lower temperatures and that is why although QC is lower around neutrality point for higher temperature, the graph predicts higher peaks in lower temperature for similar gate voltages as shown in Figure 3(a). As demonstrated in Figure 3(b), QC of TG is increased by gate voltage with smoother fluctuation rather than BG. Here also temperature decreases QC. However, temperature much affects BG rather than TG in neutrality point as shown in Figures 3(a) and 3(b). Figure 3(c) shows QC of BG and TG versus gate voltage in similar temperature (T = 50 K). Comparing QC on BG and TG, it is apparent that QC in BG is higher than TG specifically at the neutrality point which is more dominant in transport. In the case of biased bilayer graphene, a band gap opens and QC similar to the density of states exhibits van Hove singularities. But in TG where it is semimetal, the gap does not exist and then we expect to observe gate voltage QC dependence without fluctuation.

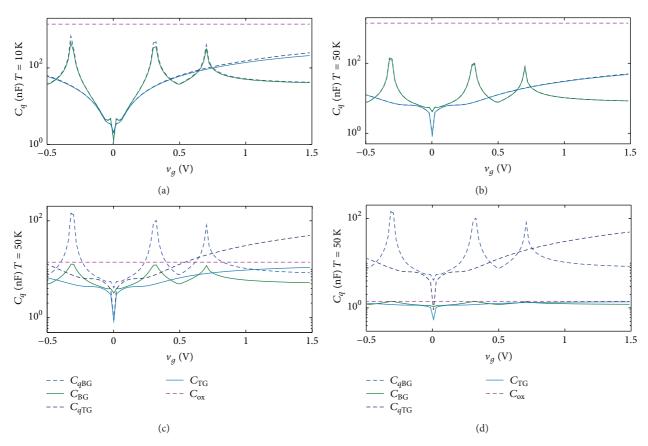

Figure 4 shows the comparison between classic and quantum capacitances in BG and TG as well as effect of the gating region size in total capacitance. Figures 4(a) and 4(b) show the quantum and classic capacitance of BG and TG in two different temperatures ( $T=10,50\,\mathrm{K}$ ) in a device with  $d=285\,\mathrm{nm}$  and  $\mathrm{SiO}_2$  dielectric. With this condition where classic capacitance is higher than QC, the contribution of the QC in total capacitance is higher. Meaning that for a device with similar size, the effect of the QC should be considered. Moreover, comparing Figures 4(a) and 4(b) reveals that although the classic capacitance contribution in total capacitance is very small, the effect of the classic capacitance on total

FIGURE 3: Quantum capacitance versus gate voltage around Fermi energy (a) in AB bilayer graphene in different temperature based on (4), (b) in ABA trilayer graphene in different temperatures based on (5), and (c) comparison between Bernal AB and TG in T=50 K.

FIGURE 4: Total (dark and light green solid lines), quantum (dark and light blue dashed lines), and classic (purple dashed lines) capacitances in BG and TG for (a) T = 10 K and d = 285 nm; (b) T = 50 K and d = 285 nm; (c) T = 50 K and d = 285 um.

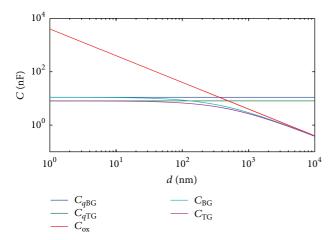

FIGURE 5: Total, quantum, and classic capacitances in BG and TG at room temperature.

capacitance is higher in lower temperature. We generate Figures 4(c) and 4(d) with the same device (SiO<sub>2</sub> dielectric) but with higher d (d = 28.5  $\mu$ m in Figure 4(c) and d = 285  $\mu$ m in Figure 4(d)). It is apparent that the total capacitance is more affected by classic capacitance in Figure 4(c), and its contribution becomes major where we increase d as shown in

Figure 4(d). This is important since we usually have higher dielectric in bottom gate rather than upper gate in double gate devices. Therefore, we could conclude that in upper gate the QC leads the total capacitance rather than bottom gate where classic capacitance is dominant for BGFET and TGFET.

Figure 5 shows total, quantum, and classic capacitances in BG and TG at room temperature. Figure 5 clearly confirms that for the channels with *d* (distance between two plates) less than about 200 nm, classical capacitance does not affect total capacitance in both BG and TG. However, classical capacitance becomes dominant for greater d. Advances in chip fabrication technology which yields capability of fabricating nanoscale devices would reach very small devices, which would induce thinner top gate oxide in FET structures. As shown in Figure 5, device fabrication should be concerned about only quantum capacitance for very thin (less than 100 nm) gate oxide devices. This research could be continued in the different directions such as studying the second stable stacking of TG (ABC) and comparing with current ABA TG QC model, looking at higher energy regime and studying unclean structures such as doped or defected channels.

#### 4. Conclusion

Each of BG and TG when applied as channel in FET devices shows different behavior compared to each other and

monolayer graphene. Rather than a linear band structure as observed in monolayer graphene, the band gap could be tuned in BG and band overlap could be varied in TG. These differences lead us to expect different behavior of these materials. Measuring the QC in the MOS configuration, has been a question for years. Although there is not any experimental result reporting QC in BG and TG, a method has recently been proposed to measure this in monolayer graphene which shows V-shape relation with gate voltage. In this study, our focus was on characterizing the capacitance voltage behavior of Bernal stacking BG and TG from theoretical point of view. Analytical quantum capacitance model of BG and TG was presented in low energy limit. Although the quantum capacitance is not considerable in conventional devices, our result clearly shows that it is dominant in BG- and TG-based devices specifically when the dielectric thickness is in nanometer range. Our calculation shows that quantum capacitances in both BG and TG increase with gate voltage and decrease with temperature with some fluctuation. However, in bilayer graphene the fluctuation is higher due to its band structure. In similar condition, the quantum capacitance in BG metal oxide is higher than TG metal oxide. Moreover, higher distance between gate electrode and channel leads total capacitance in both BG and TG to be more affected by classic capacitance. On the contrary, the quantum capacitance becomes dominant where the dielectric thickness is lower, for example, top gate. However, the experimental observation of the quantum capacitance in BG and TG needs to be addressed.

## Acknowledgment

The authors acknowledge Victoria University Postgraduate Research Office for their support and providing the necessary environment for this research.

#### References

- [1] S. I. Association, International Technology Roadmap for Semiconductors (ITRS), 2011.

- [2] R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," *IEEE Journal of Solid-State Circuits*, vol. 9, no. 5, pp. 256–268, 1974.

- [3] H. Iwai, "CMOS technology—year 2010 and beyond," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 3, pp. 357–366, 1999.

- [4] Y. Tsividis, Mixed Analog-Digital VLSI Devices and Technology, World Scientific Publishing Company Incorporated, 2002.

- [5] W. M. C. Sansen, Analog Design Essentials, vol. 289, Springer, Berlin, Germany, 2006.

- [6] P. Bai, C. Auth, S. Balakrishnan et al., "A 65nm logic technology featuring 35 nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and 0.57  $\mu$ m<sup>2</sup> SRAM cell," in *Proceedings of the Electron Devices Meeting, IEDM Technical Digest. IEEE International*, pp. 657–660, December 2004.

- [7] C. Auth, C. Allen, A. Blattner et al., "A 22 nm high performance and low-power CMOS technology featuring fully-depleted trigate transistors, self-aligned contacts and high density MIM capacitors," in *Symposium on VLSI Technology (VLSIT '12)*, pp. 131–132, 2012.

[8] J. Xia, F. Chen, J. Li, and N. Tao, "Measurement of the quantum capacitance of graphene," *Nature Nanotechnology*, vol. 4, no. 8, pp. 505–509, 2009.

- [9] S. A. Thiele, J. A. Schaefer, and F. Schwierz, "Modeling of graphene metal-oxide-semiconductor field-effect transistors with gapless large-area graphene channels," *Journal of Applied Physics*, vol. 107, no. 9, Article ID 094505, 2010.

- [10] A. Hazeghi, J. A. Sulpizio, G. Diankov, D. Goldhaber-Gordon, and H. S. P. Wong, "An integrated capacitance bridge for highresolution, wide temperature range quantum capacitance measurements," *Review of Scientific Instruments*, vol. 82, no. 5, Article ID 053904, 2011.

- [11] K. S. Novoselov, A. K. Geim, S. V. Morozov et al., "Two-dimensional gas of massless Dirac fermions in graphene," *Nature*, vol. 438, no. 7065, pp. 197–200, 2005.

- [12] Y. B. Zhang, T. T. Tang, C. Girit et al., "Direct observation of a widely tunable bandgap in bilayer graphene," *Nature*, vol. 459, no. 7248, pp. 820–823, 2009.

- [13] M. F. Craciun, S. Russo, M. Yamamoto, J. B. Oostinga, A. F. Morpurgo, and S. Tarucha, "Trilayer graphene is a semimetal with a gate-tunable band overlap," *Nature Nanotechnology*, vol. 4, no. 6, pp. 383–388, 2009.

- [14] H. Sadeghi, J.-M. Redoute, D. T. H. Lai, M. T. Ahmadi, and R. Ismail, "A review on: carbon based materials as on-chip interconnects," in *Proceedings of the SPIE Smart Nano-Micro Materials and Devices*, Melbourne, Australia, December 2011.

- [15] H. Sadeghi, M. T. Ahmadi, S. M. Mousavi, M. H. Ghadiry, and A. R. Ismail, "Channel conductance of ABA stacking trilayer graphene nanoribbon field effect transistor," *Modern Physics Letters B*, vol. 26, no. 8, Article ID 1250047, 10 pages, 2012.

- [16] H. Sadeghi, M. T. Ahmadi, B. I. Ishak, S. M. Mousavi, and A. R. Ismail, "Ballistic conductance model of Bilayer Graphene Nanoribbon (BGN)," *Journal of Computational and Theoretical Nanoscience*, vol. 8, pp. 1993–1998, 2011.

- [17] H. Lipson and A. R. Stokes, "The structure of graphite," *Proceedings of the Royal Society of London A. Mathematical and Physical Sciences*, vol. 181, no. 984, pp. 101–105, 1942.

- [18] H. Xu, Z. Zhang, and L.-M. Peng, "Measurements and microscopic model of quantum capacitance in graphene," Applied Physics Letters, vol. 98, no. 13, Article ID 133122, 2011.

- [19] S. Thiele and F. Schwierz, "Modeling of the steady state characteristics of large-area graphene field-effect transistors," *Journal of Applied Physics*, vol. 110, no. 3, Article ID 034506, 7 pages, 2011.

- [20] M. D. Stoller, C. W. Magnuson, Y. Zhu et al., "Interfacial capacitance of single layer graphene," *Energy & Environmental Science*, vol. 4, pp. 4685–4689, 2011.

- [21] M. Begliarbekov, S. Strauf, and C. P. Search, "Quantum inductance and high frequency oscillators in graphene nanoribbons," Nanotechnology, vol. 22, no. 16, Article ID 165203, 2011.

- [22] J. L. Xia, F. Chen, J. L. Tedesco et al., "The transport and quantum capacitance properties of epitaxial graphene," *Applied Physics Letters*, vol. 96, no. 16, Article ID 162101, 2010.

- [23] L. A. Ponomarenko, R. Yang, R. V. Gorbachev et al., "Density of states and zero landau level probed through capacitance of graphene," *Physical Review Letters*, vol. 105, no. 13, Article ID 136801, 2010.

- [24] S. Sonde, F. Giannazzo, V. Raineri, and E. Rimini, "Dielectric thickness dependence of capacitive behavior in graphene deposited on silicon dioxide," *Journal of Vacuum Science and Technology B*, vol. 27, no. 2, pp. 868–873, 2009.

[25] S. Dröscher, P. Roulleau, F. Molitor et al., "Quantum capacitance and density of states of graphene," *Applied Physics Letters*, vol. 96, no. 15, Article ID 152104, 2010.

- [26] G. S. Kliros, "Modeling of carrier density and quantum capacitance in graphene nanoribbon FETs," in *Proceedings of the International Conference on Microelectronics (ICM '10)*, pp. 236–239, December 2010.

- [27] J. Guo, Y. Yoon, and Y. Ouyang, "Gate electrostatics and quantum capacitance of graphene nanoribbons," *Nano Letters*, vol. 7, no. 7, pp. 1935–1940, 2007.

- [28] A. A. Shylau, J. W. Klos, and I. V. Zozoulenko, "Capacitance of graphene nanoribbons," *Physical Review B*, vol. 80, no. 20, 9 pages, 2009.

- [29] Y. Ouyang, Y. Yoon, and J. Guo, "Edge chemistry engineering of graphene nanoribbon transistors: a computational study," in *Proceedings of the IEEE International Electron Devices Meeting (IEDM '08)*, December 2008.

- [30] T. Fang, A. Konar, H. Xing, and D. Jena, "Carrier statistics and quantum capacitance of graphene sheets and ribbons," *Applied Physics Letters*, vol. 91, no. 9, Article ID 092109, 2007.

- [31] M. S. Goh and M. Pumera, "Multilayer graphene nanoribbons exhibit larger capacitance than their few-layer and single-layer graphene counterparts," *Electrochemistry Communications*, vol. 12, no. 10, pp. 1375–1377, 2010.

- [32] A. Misra, H. Kalita, M. Waikar et al., "Multilayer graphene as charge storage layer in floating gate flash memory," in *Proceedings of the 4th IEEE International Memory Workshop (IMW '12)*, pp. 1–4, 2012.

- [33] G. Fiori and G. Iannaccone, "Ultralow-voltage bilayer graphene tunnel FET," *IEEE Electron Device Letters*, vol. 30, no. 10, pp. 1096–1098, 2009.

- [34] A. A. Avetisyan, B. Partoens, and F. M. Peeters, "Electric-field control of the band gap and Fermi energy in graphene multi-layers by top and back gates," *Physical Review B*, vol. 80, no. 19, Article ID 195401, 2009.

- [35] E. V. Castro, K. S. Novoselov, S. V. Morozov et al., "Electronic properties of a biased graphene bilayer," *Journal of Physics Con*densed Matter, vol. 22, no. 17, Article ID 175503, 2010.

- [36] F. Guinea, A. H. Castro Neto, and N. M. R. Peres, "Electronic states and Landau levels in graphene stacks," *Physical Review B*, vol. 73, no. 24, Article ID 245426, 2006.

- [37] B. Partoens and F. M. Peeters, "From graphene to graphite: electronic structure around the K point," *Physical Review B*, vol. 74, no. 7, Article ID 075404, 2006.

- [38] A. A. Avetisyan, B. Partoens, and F. M. Peeters, "Stacking order dependent electric field tuning of the band gap in graphene multilayers," *Physical Review B*, vol. 81, no. 11, Article ID 115432, 2010.

- [39] T. Kat, Perturbation Theory for Linear Operators, vol. 132, Springer, 1995.

- [40] K. F. Mak, J. Shan, and T. F. Heinz, "Electronic structure of fewlayer graphene: experimental demonstration of strong dependence on stacking sequence," *Physical Review Letters*, vol. 104, no. 17, Article ID 176404, 2010.

- [41] A. Bostwick, J. McChesney, T. Ohta, E. Rotenberg, T. Seyller, and K. Horn, "Experimental studies of the electronic structure of graphene," *Progress in Surface Science*, vol. 84, no. 11-12, pp. 380–413, 2009.

- [42] D. L. John, L. C. Castro, and D. L. Pulfrey, "Quantum capacitance in nanoscale device modeling," *Journal of Applied Physics*, vol. 96, no. 9, pp. 5180–5184, 2004.

[43] S. Ilani, L. A. K. Donev, M. Kindermann, and P. L. McEuen, "Measurement of the quantum capacitance of interacting electrons in carbon nanotubes," *Nature Physics*, vol. 2, no. 10, pp. 687–691, 2006.

- [44] M. T. Ahmadi, J. F. Webb, N. A. Amin et al., "Carbon nanotube capacitance model in the degenerate and the non-degenerate regimes," in *Presented at the 4th Global Conference on Power* Control and Optimization (PCO '10), Sarawak, Malaysia, 2011.

- [45] S. Datta, Quantum Transport: Atom to Transistor, Cambridge University Press, 2005.

- [46] S. Russo, M. F. Craciun, M. Yamamoto, S. Tarucha, and A. F. Morpurgo, "Double-gated graphene-based devices," *New Journal of Physics*, vol. 11, Article ID 095018, 2009.

- [47] G. Cardano and T. R. Witmer, Ars Magna or the Rules of Algebra, Dover, 1993.

- [48] S. Tongay, T. Schumann, X. Miao, B. R. Appleton, and A. F. Hebard, "Tuning Schottky diodes at the many-layer-graphene/semiconductor interface by doping," *Carbon*, vol. 49, no. 6, pp. 2033–2038, 2011.

Submit your manuscripts at http://www.hindawi.com