# Kent Academic Repository Full text document (pdf)

### **Citation for published version**

Chaudhary, Mandeep (2016) Implementation and Applications of Logarithmic Signal Processing on an FPGA. Doctor of Philosophy (PhD) thesis, University of Kent.

### DOI

### Link to record in KAR

http://kar.kent.ac.uk/55184/

### **Document Version**

UNSPECIFIED

#### **Copyright & reuse**

Content in the Kent Academic Repository is made available for research purposes. Unless otherwise stated all content is protected by copyright and in the absence of an open licence (eg Creative Commons), permissions for further reuse of content should be sought from the publisher, author or other copyright holder.

#### Versions of research

The version in the Kent Academic Repository may differ from the final published version. Users are advised to check http://kar.kent.ac.uk for the status of the paper. Users should always cite the published version of record.

#### Enquiries

For any further enquiries regarding the licence status of this document, please contact: **researchsupport@kent.ac.uk**

If you believe this document infringes copyright then please contact the KAR admin team with the take-down information provided at http://kar.kent.ac.uk/contact.html

# Implementation and Applications of Logarithmic Signal Processing on an FPGA

A Thesis submitted to The University of Kent for the degree of Doctor of Philosophy in Electronic Engineering

By

Mandeep Chaudhary February 2016 Dedicated to my family, teachers & friends.

## Acknowledgements

Firstly, I would like to thank my supervisor Dr. Peter Lee for his guidance and support. I thank him for supporting me with my PhD when I was having health problems. My meetings with him have been a source of great encouragement, inspiration and learning. Thank you for believing in me and giving me such a nice opportunity.

My friends and colleagues Dr. Harshal Oza, Gurtac Yemiscioglu, Mark Esdale and Steven J. Moser, thank you for keeping me smiling in difficult times. Thank you to the EDA staff for the opportunities and help you have given me for the years.

Finally I would like to say deepest thanks to my family in India. My father (Randhir Singh Malik) and mother (Kamla Devi) thank you for love and moral support. I would not have made this far without you all.

#### Abstract

This thesis presents two novel algorithms for converting a normalised binary floating point number into a binary logarithmic number with the single-precision of a floating point number. The thesis highlights the importance of logarithmic number systems in real-time DSP applications. A real-time cross-correlation application where logarithmic signal processing is used to simplify the complex computation is presented.

The first algorithm presented in this thesis comprises two stages. A piecewise linear approximation to the original logarithmic curve is performed in the first stage and a scaled-down normalised error curve is stored in the second stage. The algorithm requires less than 20 kbits of ROM and a maximum of three small multipliers. The architecture is implemented on Xilinx's Spartan3 and Spartan6 FPGA family. Synthesis results confirm that the algorithm operates at a frequency of 42.3 MHz on a Spartan3 device and 127.8 MHz on a Spartan6. Both solutions have a pipeline latency of two clocks. The operating speed increases to 71.4 MHz and 160 MHz respectively when the pipeline latencies increase to eight clocks.

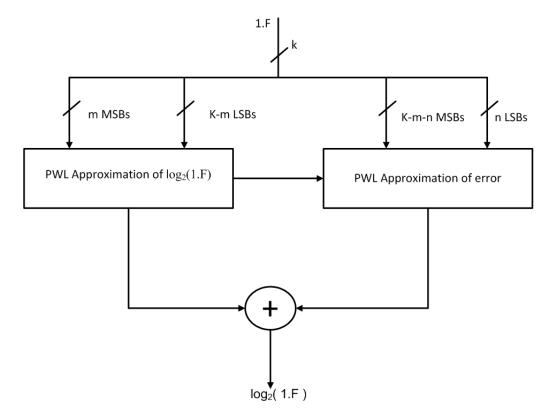

The proposed algorithm is further improved by using a PWL (Piece-Wise Linear) approximation of the transform curve combined with a PWL approximation of a scaled version of the normalized segment error. A hardware approach for reducing the memory with additional XOR gates in the second stage is also presented. The architecture presented uses just one 18k bit Block RAM (BRAM) and synthesis results indicate operating frequencies of 93 and 110 MHz when implemented on the Xilinx Spartan3 and Spartan6 devices respectively.

Finally a novel prototype of an FPGA-based four channel correlation velocimetry system is presented. The system operates at a higher sampling frquency than previous published work and outputs the new result after every new sample it receives. The system works at a sampling frequency of 195.31 kHz and a sample resolution of 12 bits. The prototype system calculates a delay in a range of 0 to 2.6 ms with a resolution of 5.12  $\mu$ s.

## Publications

- Chaudhary, M.; Lee, P, "Two-stage logarithmic converter with reduced memory requirements," *Computers & Digital Techniques, IET*, vol.8, no.1, pp.23,29, January 2014.

- Chaudhary, M.; Lee, P, "An Improved 2-Step Binary Logarithmic Converter for FPGAs," *IEEE transactions on Circuits & Systems II : Express Briefing*, vol.62, no.5, pp.476,480, May 2015.

# Contents

|          | Ack  | nowledgements                          | iii          |

|----------|------|----------------------------------------|--------------|

|          | Abs  | tract                                  | iv           |

|          | Pub  | lications                              | $\mathbf{v}$ |

|          | Abb  | previations x                          | ix           |

| 1        | Intr | oduction                               | 1            |

|          | 1.1  | Motivation, Aims & Objective           | 1            |

|          | 1.2  | Research Contributions                 | 4            |

|          | 1.3  | Thesis Organisation                    | 6            |

| <b>2</b> | FPO  | GA Technology                          | 8            |

|          | 2.1  | Introduction                           | 8            |

|          | 2.2  | DSP system Technologies                | 8            |

|          | 2.3  | FPGA Overview                          | 10           |

|          | 2.4  | FPGA Device Types and Families         | 13           |

|          |      | 2.4.1 Altera Cyclone Family Overview   | 14           |

|          |      | 2.4.2 Xilinx Spartan3 Family Overview  | 15           |

|          |      | 2.4.3 Xilinx Spartan6 Family Overview  | 18           |

|          | 2.5  | Hardware Description Language          | 21           |

|          | 2.6  | Numerical Data Representation on FPGAs | 21           |

|          | 2.7  | Summary                                | 28           |

| 3        | Log | arithmic Conversion Literature Review   | 29  |

|----------|-----|-----------------------------------------|-----|

|          | 3.1 | Introduction                            | 29  |

|          | 3.2 | Normalisation Methods                   | 31  |

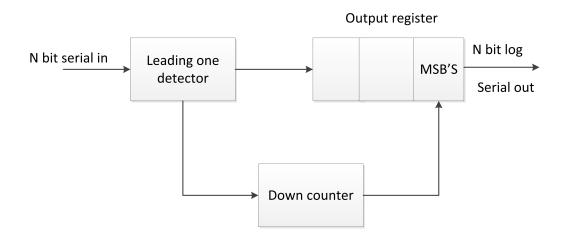

|          |     | 3.2.1 Leading Zero Detector             | 31  |

|          |     | 3.2.2 Leading One Detector              | 32  |

|          | 3.3 | Logarithmic Converter                   | 34  |

|          |     | 3.3.1 Direct PWL Conversion Algorithms  | 35  |

|          |     | 3.3.2 PWL and LUT Algorithms            | 49  |

|          |     | 3.3.3 Polynomial Approximation Methods  | 54  |

|          |     | 3.3.4 CORDIC and Taylor algorithms      | 60  |

|          |     | 3.3.5 Other Methods                     | 64  |

|          | 3.4 | Summary                                 | 74  |

| 4        | Imp | proved Logarithmic Converter            | 76  |

|          | 4.1 | Introduction                            | 76  |

|          | 4.2 | Larson Lin2Log conversion algorithm     | 77  |

|          | 4.3 | Novel Algorithm                         | 84  |

|          | 4.4 | Implementation                          | 89  |

|          | 4.5 | Results                                 | 92  |

|          | 4.6 | Conclusion                              | 94  |

| <b>5</b> | Fur | ther Improved Logarithmic Converter     | 95  |

|          | 5.1 | Introduction                            | 95  |

|          | 5.2 | Novel Algorithm                         | 96  |

|          |     | 5.2.1 Symmetry                          | 98  |

|          |     | 5.2.2 LUT2 size reduction               | 100 |

|          | 5.3 | Implementation                          | 106 |

|          | 5.4 | Results                                 | 110 |

|          | 5.5 | Conclusion                              | 111 |

| 6        | FP  | GA based Correlation Velocimetry System | 113 |

|          | 6.1 | Introduction                            | 113 |

|              | 6.2  | Correl   | ation                              | . 114 |

|--------------|------|----------|------------------------------------|-------|

|              |      | 6.2.1    | Cross-correlation                  | . 114 |

|              |      | 6.2.2    | Fast cross-correlation             | . 115 |

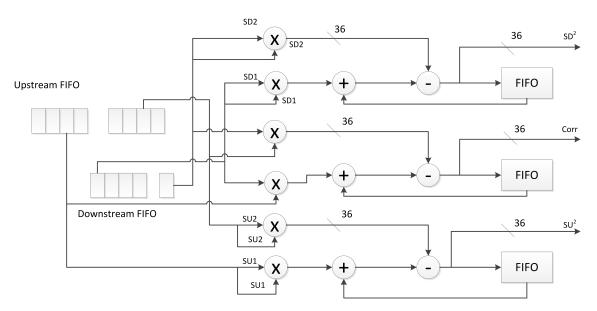

|              |      | 6.2.3    | Incremental cross-correlation      | . 116 |

|              | 6.3  | Veloci   | metry System                       | . 116 |

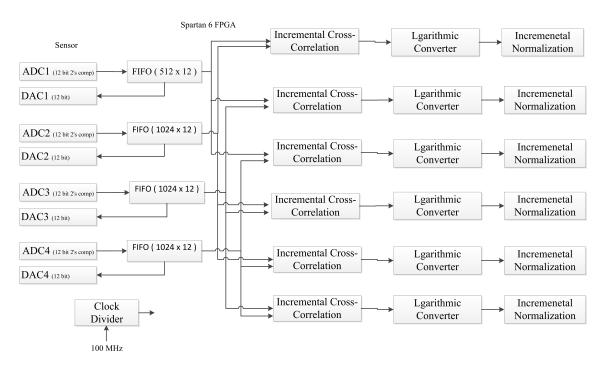

|              | 6.4  | FPGA     | based Velocimetry System           | . 118 |

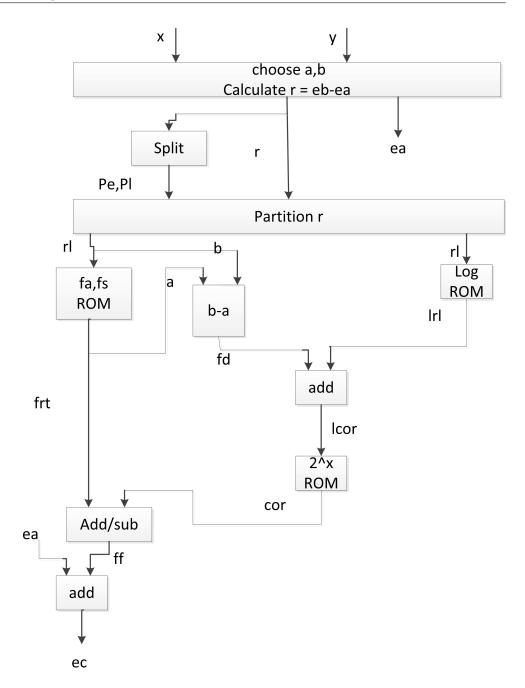

|              | 6.5  | Veloci   | metry System Algorithm             | . 120 |

|              | 6.6  | Hardw    | vare Implementation                | . 122 |

|              | 6.7  | Result   | S                                  | . 127 |

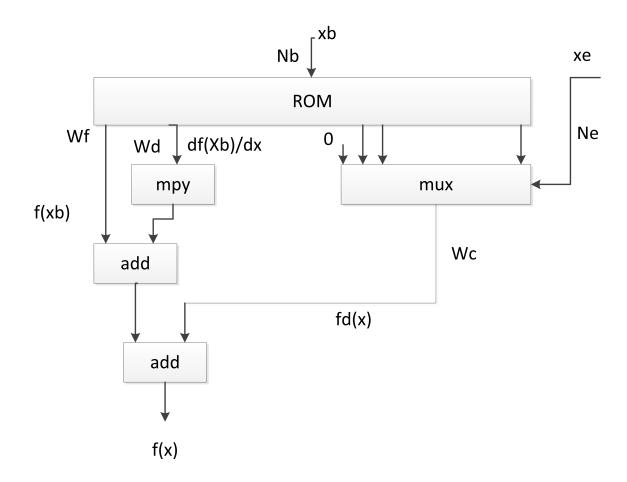

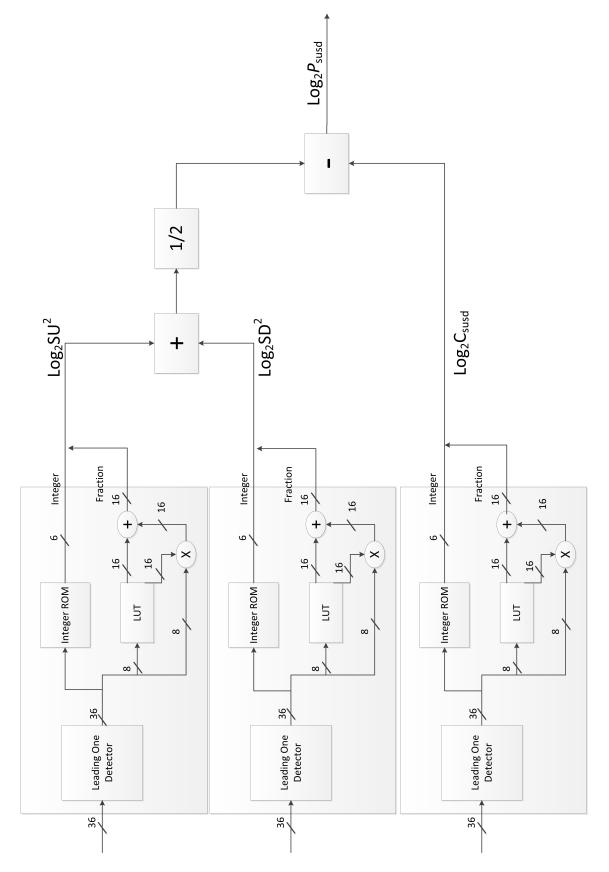

|              |      | 6.7.1    | Log2Lin Domain                     | . 128 |

|              |      | 6.7.2    | FPGA Utilisation                   | . 133 |

|              |      | 6.7.3    | Piecewise Linear Area Optimisation | . 138 |

|              | 6.8  | Conclu   | usion                              | . 141 |

| 7            | Con  | clusio   | ns and Future Work                 | 142   |

|              | 7.1  | Summ     | ary of Research                    | . 142 |

|              | 7.2  | Resear   | cch Novel Claims                   | . 143 |

|              | 7.3  | Future   | e Research Directions              | . 144 |

|              | Bibl | liograp  | ohy                                | 145   |

|              | App  | oendix   |                                    | 164   |

| A            | Tab  | le 4.2   | Matlab Simulations                 | 165   |

| В            | Tab  | le 4.3   | Matlab Simulations                 | 174   |

| С            | Tab  | le 5.2 ] | Matlab Simulations                 | 183   |

| D            | Tab  | le 5.3 ] | Matlab Simulations                 | 192   |

| $\mathbf{E}$ | Log  | arithm   | ic Domain Cross-Correlation Plots  | 201   |

| $\mathbf{F}$ | VH   | DL Sai   | mple Code                          | 210   |

# List of Figures

| 1.1  | Standard logarithmic processor.                                    | 3  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Hybrid logarithmic processor                                       | 4  |

| 2.1  | FPGA Architecture.                                                 | 11 |

| 2.2  | FPGA CLB using 4 input LUT                                         | 12 |

| 2.3  | FPGA CLB using 6 input LUT                                         | 12 |

| 2.4  | Spartan 3 Starter Kit Board                                        | 17 |

| 2.5  | DSP48A1 Slice.                                                     | 18 |

| 2.6  | Nexys3 Board                                                       | 20 |

| 2.7  | IEEE-754 std Single Precision                                      | 22 |

| 2.8  | IEEE-754 std Double Precision.                                     | 22 |

| 2.9  | Three stage 18-bit floating point adder                            | 23 |

| 2.10 | Three stage 18-bit floating point multiplier.                      | 24 |

| 2.11 | Floating point addition algorithm                                  | 25 |

| 2.12 | 32 bit floating point adder                                        | 26 |

| 2.13 | Digit serial multiplier.                                           | 26 |

| 3.1  | Oklobdzija leading zero detector circuit                           | 31 |

| 3.2  | P. Lee's LOD circuit                                               | 32 |

| 3.3  | Fast 4-bit LOD                                                     | 33 |

| 3.4  | Fast 16-bit LOD                                                    | 34 |

| 3.5  | Mitchell's algorithm generating binary logarithm                   | 36 |

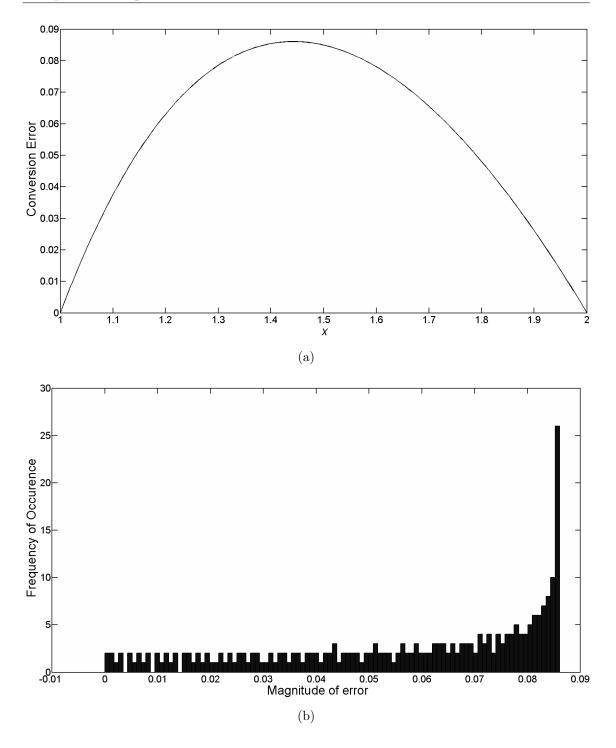

| 3.6  | Mitchell approximation (a) Absolute error (b) Error histogram      | 38 |

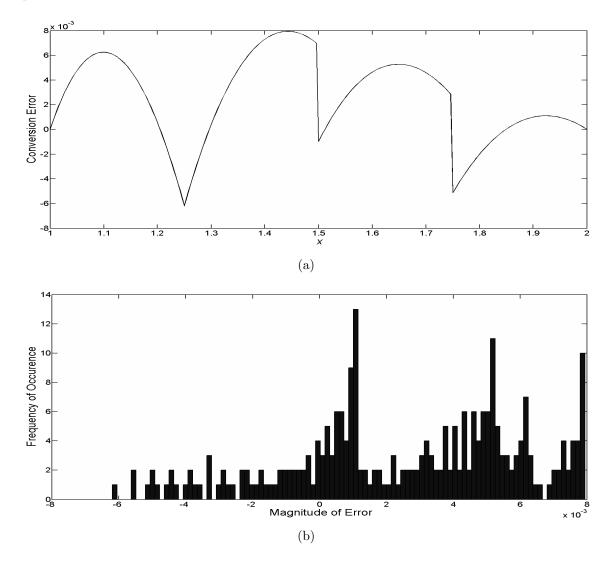

| 3.7  | The Combet et al. Logarithmic approximation (a) Absolute error (b) |    |

|      | Error histogram                                                    | 39 |

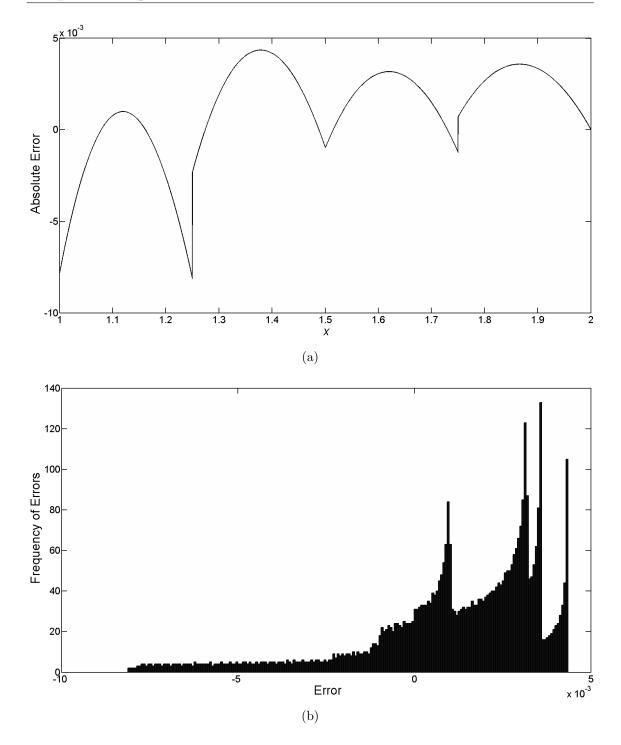

| 3.8  | Hall's Logarithmic approximation (a) Absolute error (b) Error his-       |    |

|------|--------------------------------------------------------------------------|----|

|      | togram                                                                   | 41 |

| 3.9  | Hoefflinger's bit-serial logarithmic encoder                             | 42 |

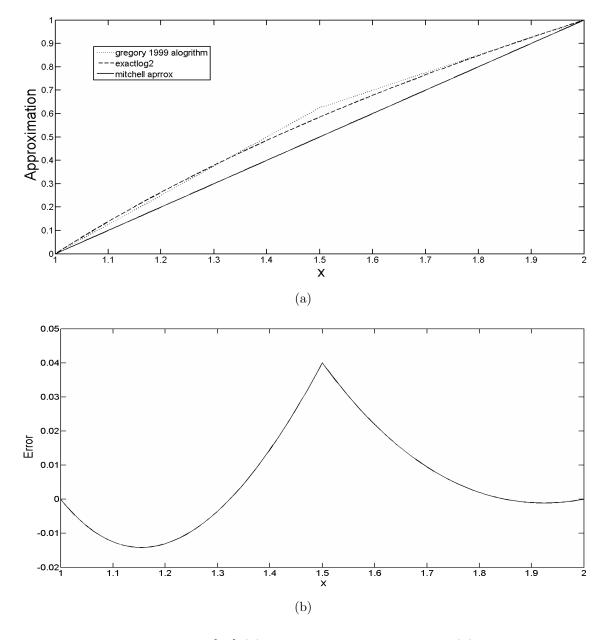

| 3.10 | Gregory 1999 (a) Logarithmic approximation (b) Absolute error            | 43 |

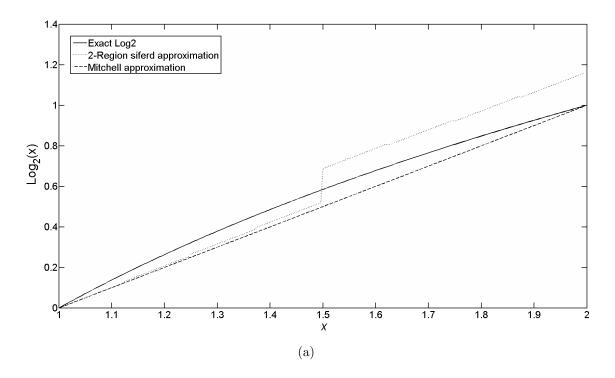

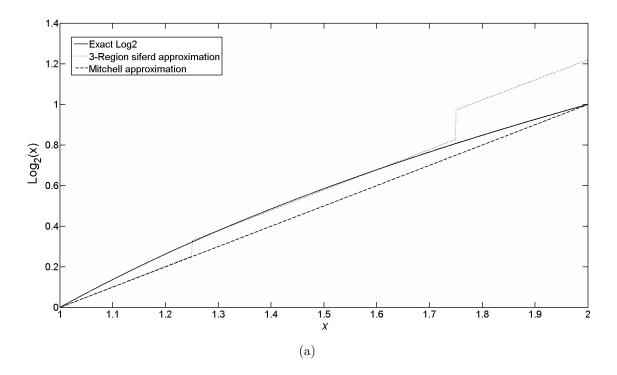

| 3.11 | Siferd 2-region (a) Logarithmic approximation                            | 44 |

| 3.11 | Siferd 2-region (b) Absolute error                                       | 45 |

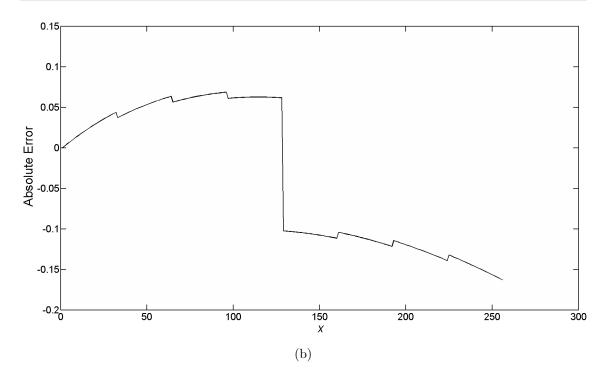

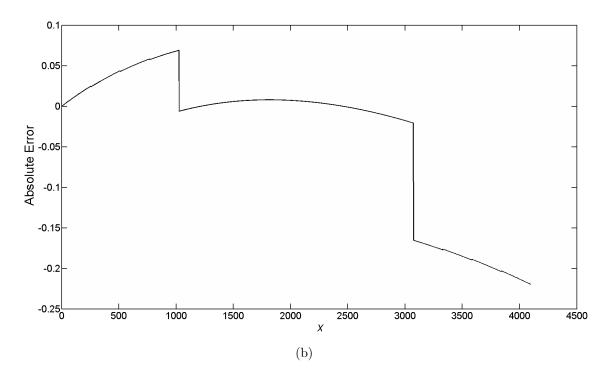

| 3.12 | Siferd 3-region (b) Absolute error                                       | 46 |

| 3.12 | Siferd 3-region (a) Logarithmic approximation                            | 46 |

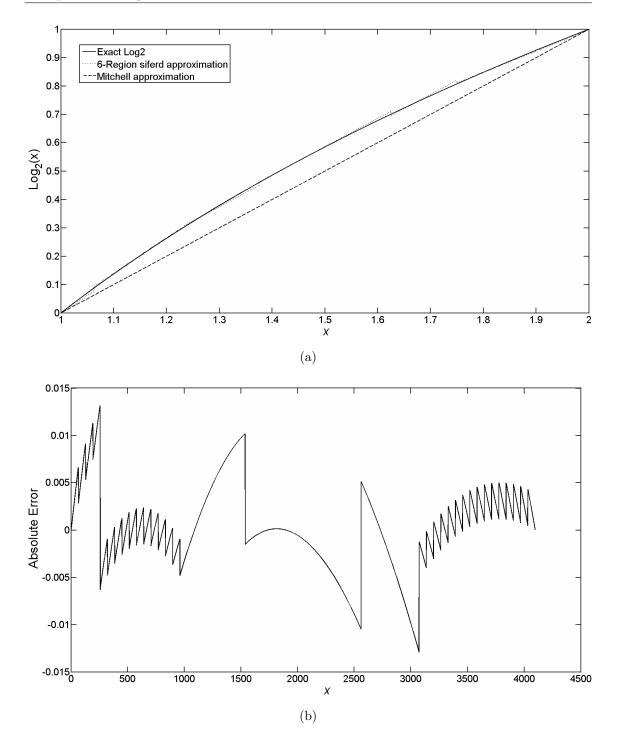

| 3.13 | Siferd 6-region (a) Logarithmic approximation (b) Absolute error         | 48 |

| 3.14 | Kmetz's principal of proposed approximation.                             | 50 |

| 3.15 | Kmetz's (a) Logarithmic approximation (b) Absolute error $\ldots \ldots$ | 51 |

| 3.16 | Maenner principal of proposed approximation                              | 52 |

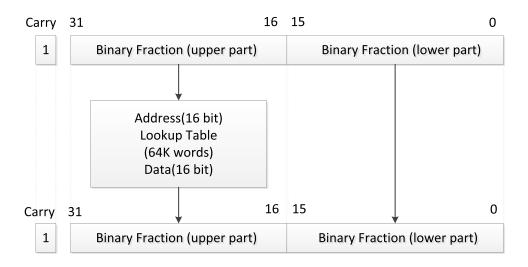

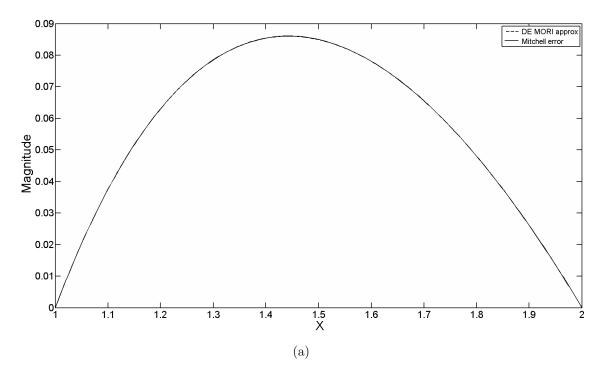

| 3.17 | Maenner (a) Logarithmic approximation (b) Absolute error                 | 53 |

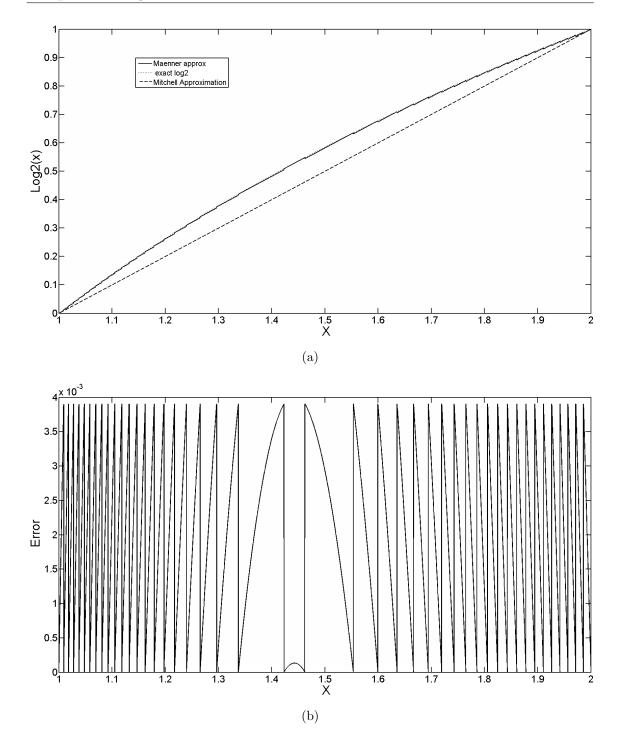

| 3.18 | Marino (a) Logarithmic approximation (b) Absolute error $\ldots \ldots$  | 55 |

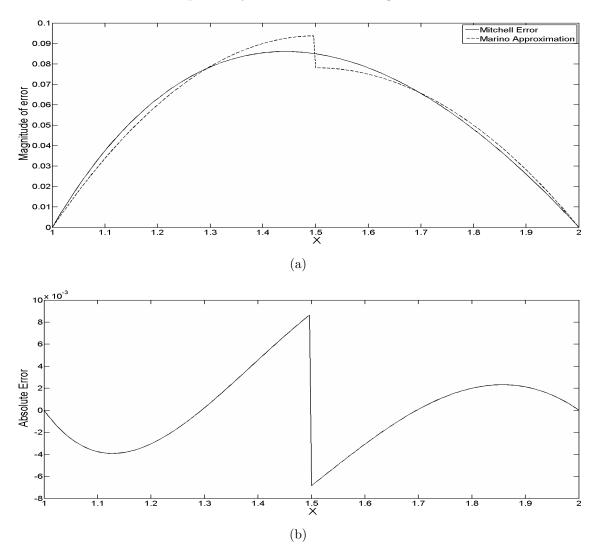

| 3.19 | Mori (a) Logarithmic approximation                                       | 56 |

| 3.19 | Mori (b) Absolute error                                                  | 57 |

| 3.20 | Knittel non uniform log approximation                                    | 59 |

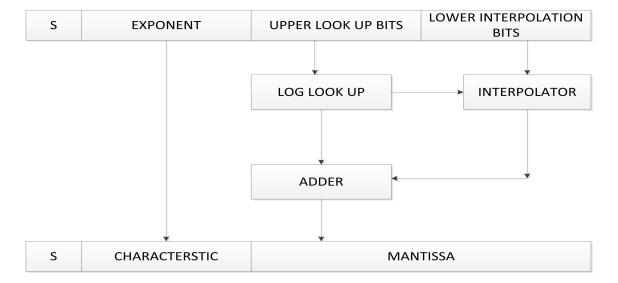

| 3.21 | S.Pan Lin2Log architecture.                                              | 60 |

| 3.22 | Multiplier-based Linear Interpolator                                     | 62 |

| 3.23 | Multiplierless Linear Interpolator                                       | 63 |

| 3.24 | Novel Single Multiplier Quadratic Interpolator                           | 64 |

| 3.25 | Data path for Lewis segmented linear approximation                       | 66 |

| 3.26 | Lewis Nonlinear compression.                                             | 68 |

| 3.27 | Huang et al. Lin2Log architecture.                                       | 69 |

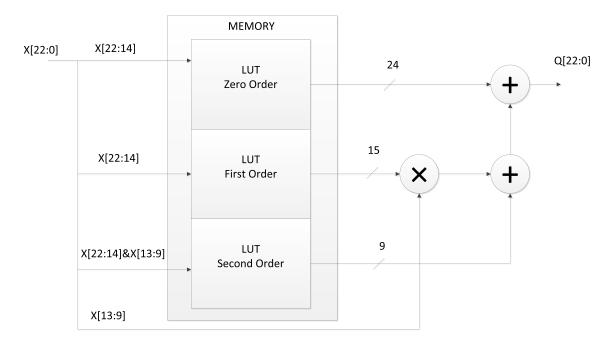

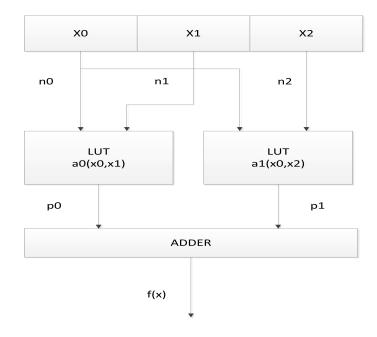

| 3.28 | Stine and Schulte Bipartite table method.                                | 70 |

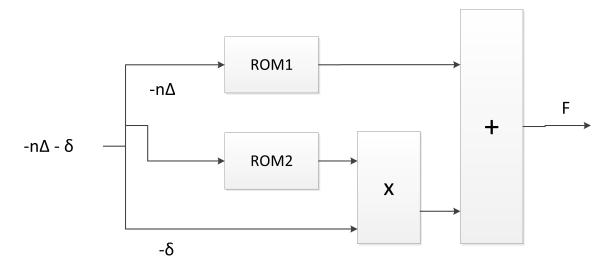

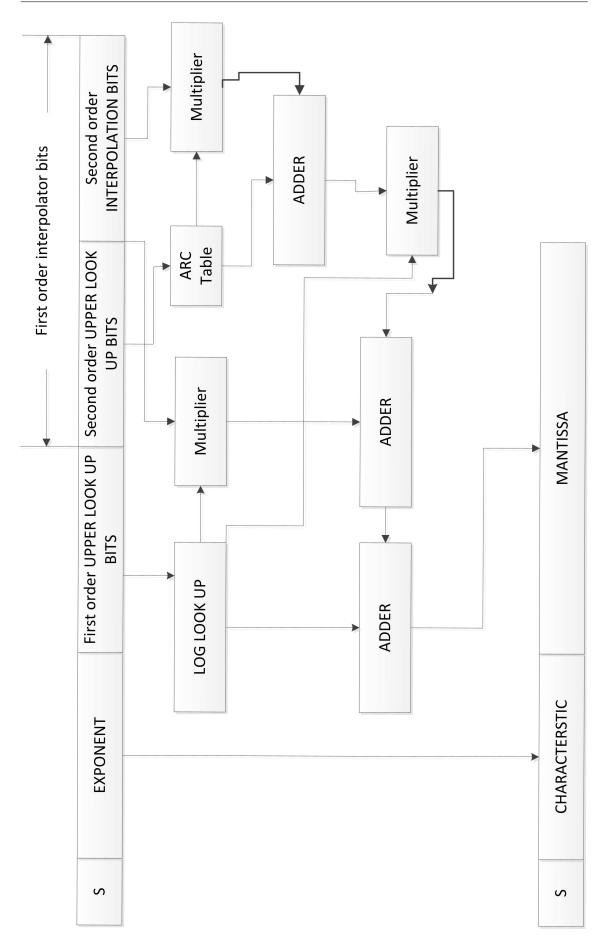

| 3.29 | LARSON first order interpolation                                         | 71 |

| 3.30 | LARSON second order interpolation.                                       | 73 |

| 4.1  | Larson algorithm                                                         | 80 |

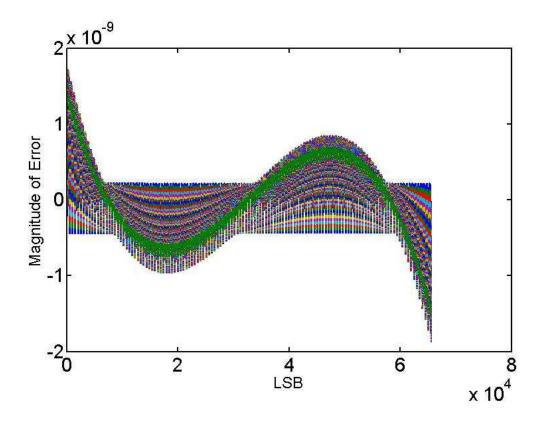

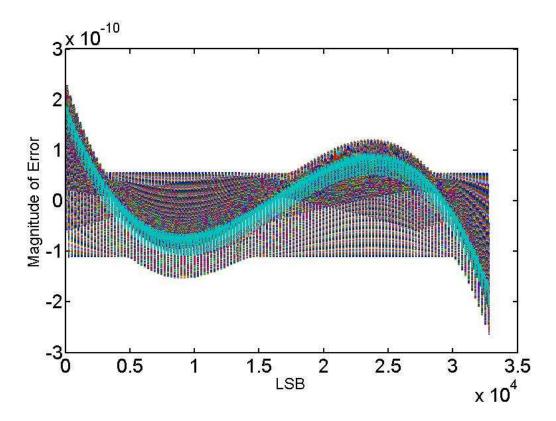

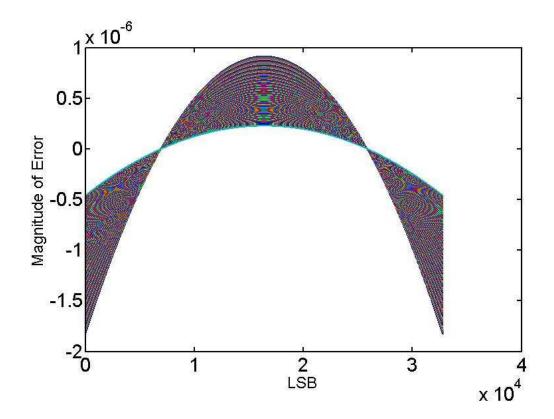

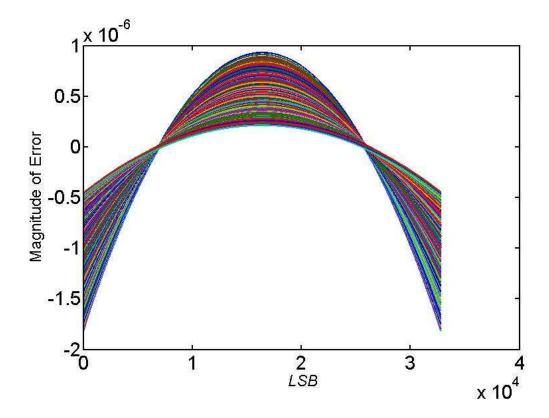

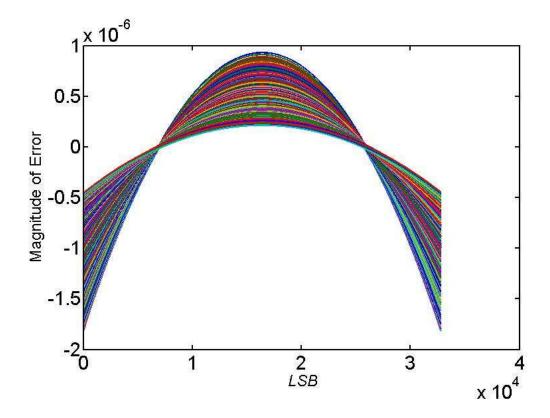

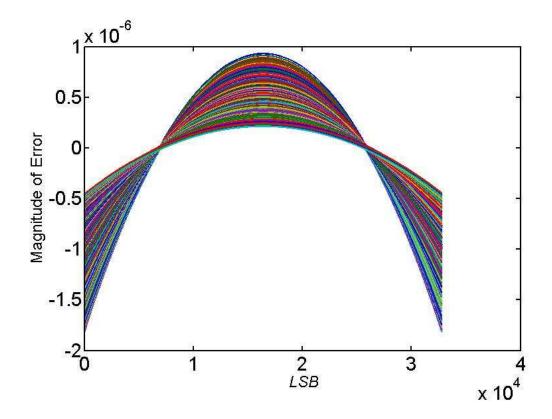

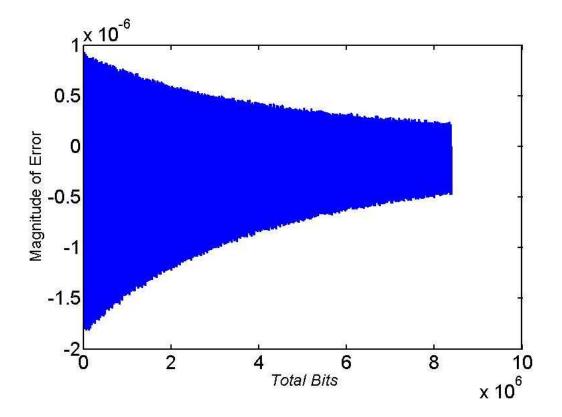

| 4.2  | Larson first stage errors (128 segments, linear Interpolation) (a) Error |    |

|      | for 128 intervals (b) Superimposed error curves for each segment         | 82 |

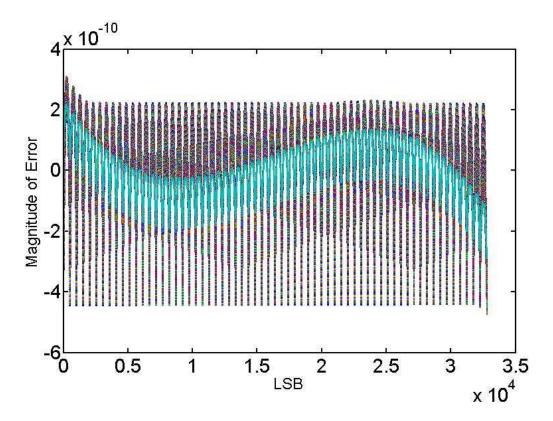

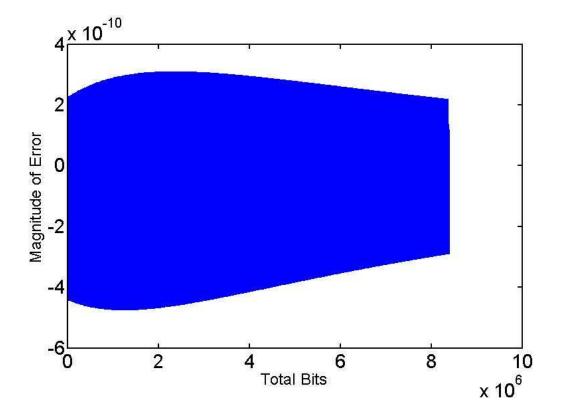

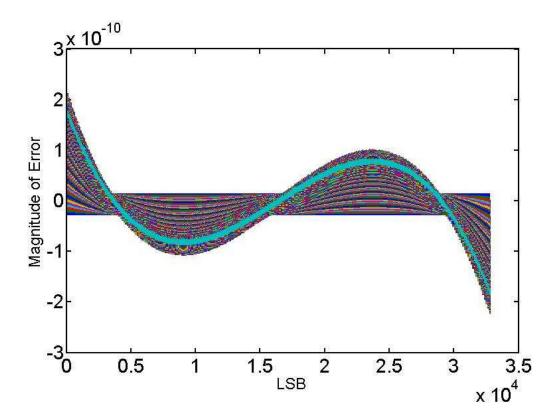

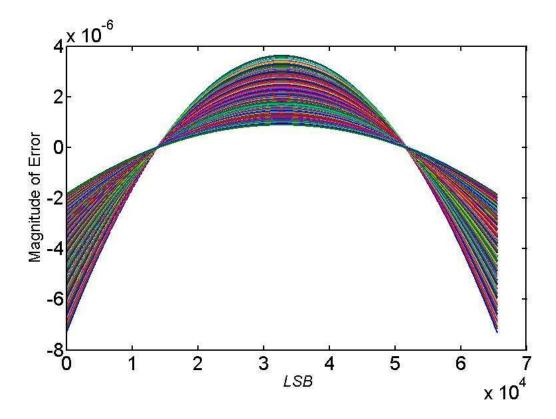

| 4.3  | Larson first stage errors (128 segments, linear Interpolation) (a) Nor-  |     |

|------|--------------------------------------------------------------------------|-----|

|      | malised error curves for each segment (b) mean of normalised curves.     | 83  |

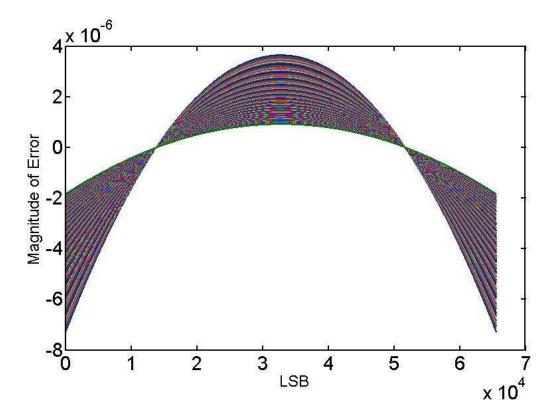

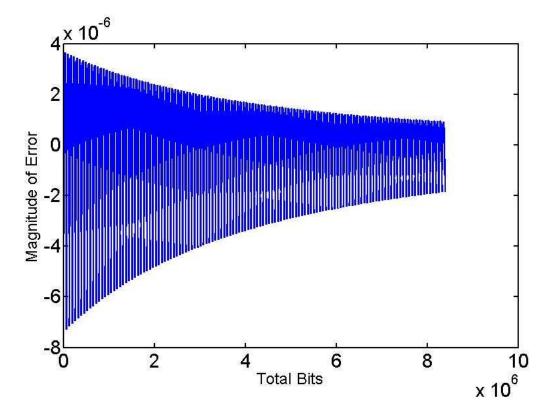

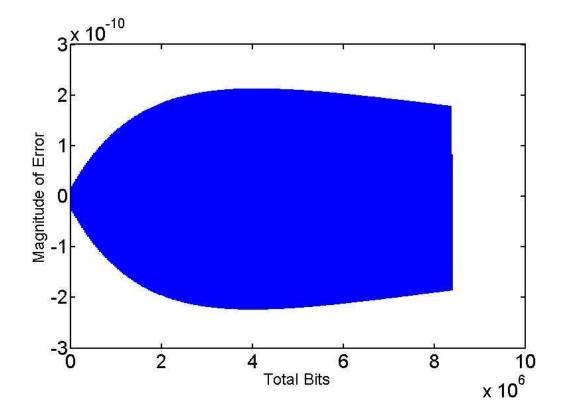

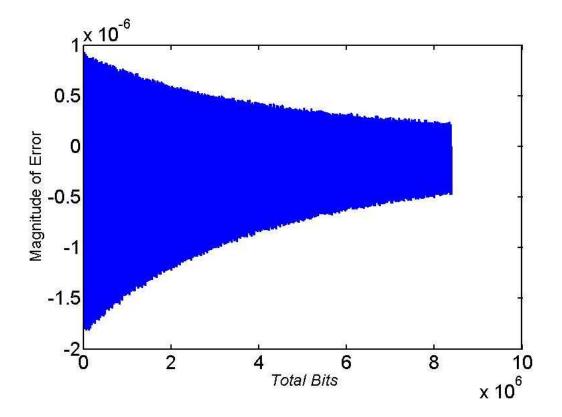

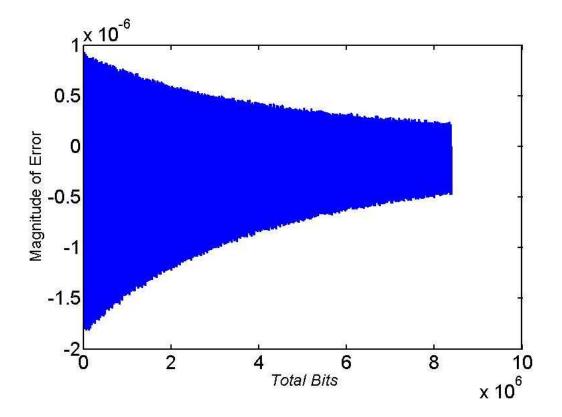

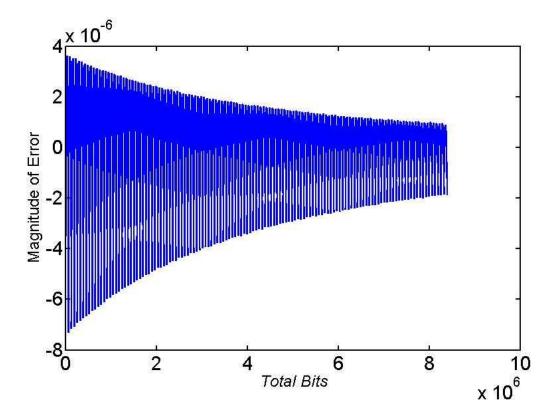

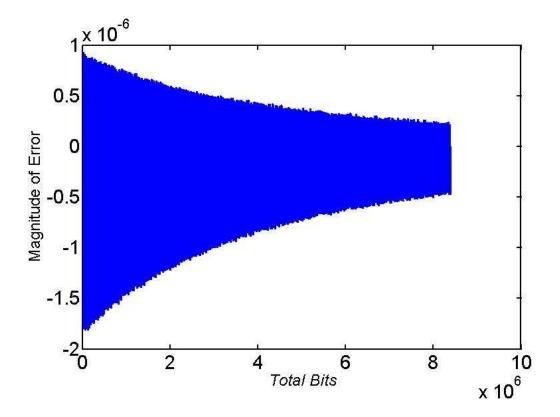

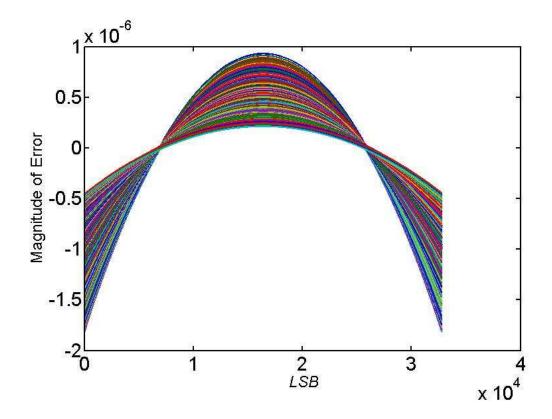

| 4.4  | Larson total error i.e. $(1st + 2nd)$ stage errors (a) Superimposed      |     |

|      | error curves for each segment errors using maximum error curve (i.e.     |     |

|      | 1st error curve) of first stage                                          | 85  |

| 4.4  | Larson total error i.e. $(1st + 2nd)$ stage errors (b) error obtained    |     |

|      | using maximum error curve (i.e. 1st error curve) of first stage          | 85  |

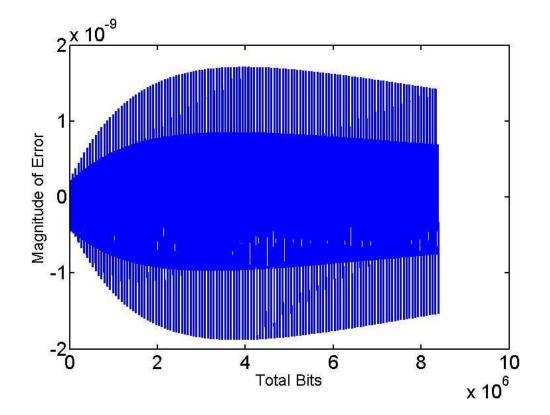

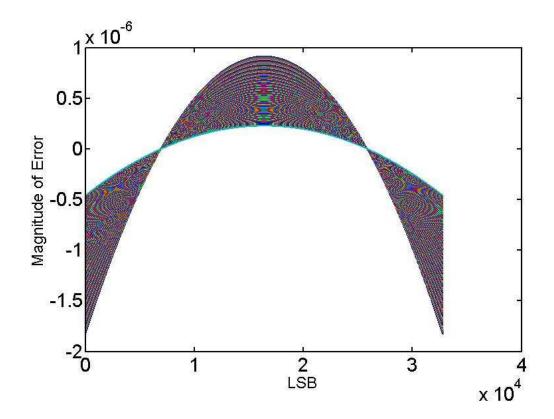

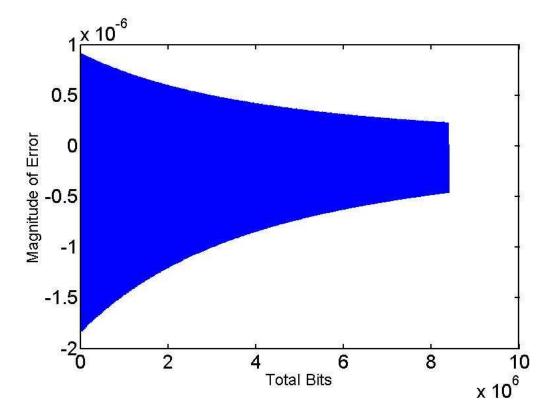

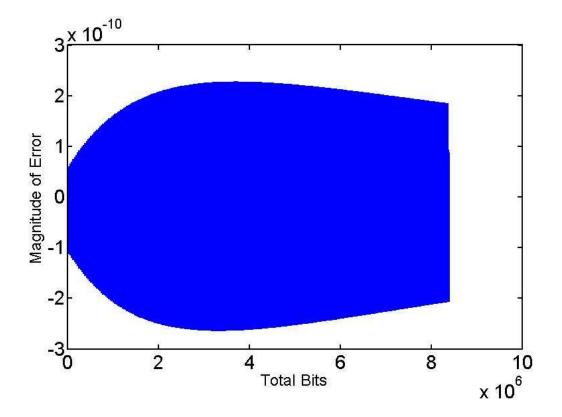

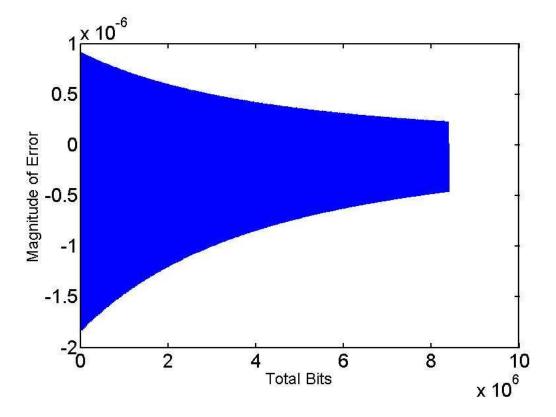

| 4.5  | Larson total error i.e. $(1st + 2nd)$ stage errors (a) error obtained    |     |

|      | using mean (average i.e. $64$ th error curve) error curve of first stage | 86  |

| 4.5  | Larson total error i.e. $(1st + 2nd)$ stage errors (b) error obtained    |     |

|      | using minimum (i.e. 128th error curve) error curve of first stage        | 86  |

| 4.6  | Algorithm using finite coefficients                                      | 88  |

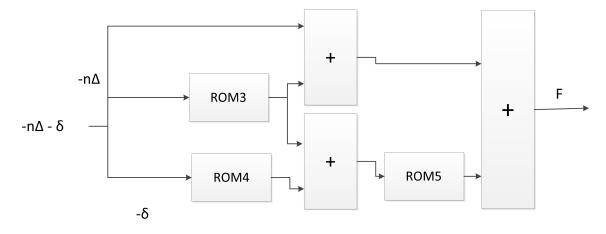

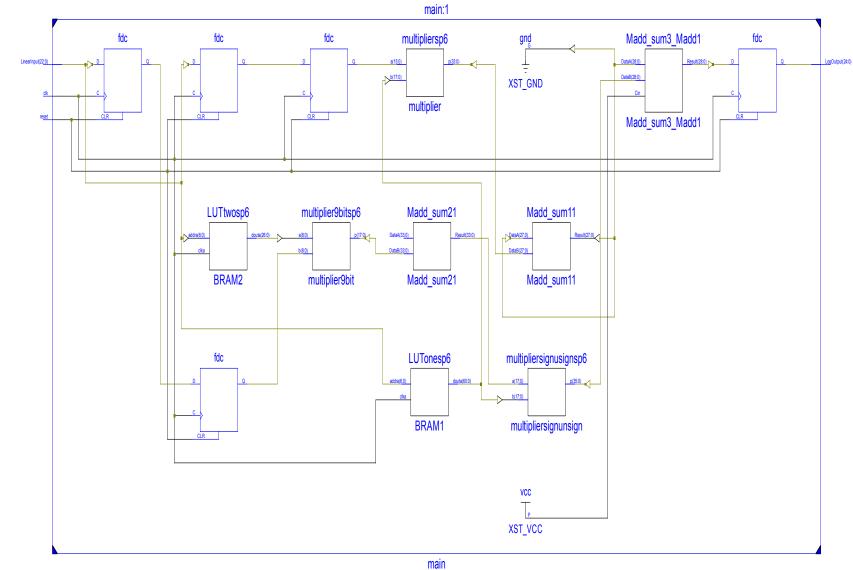

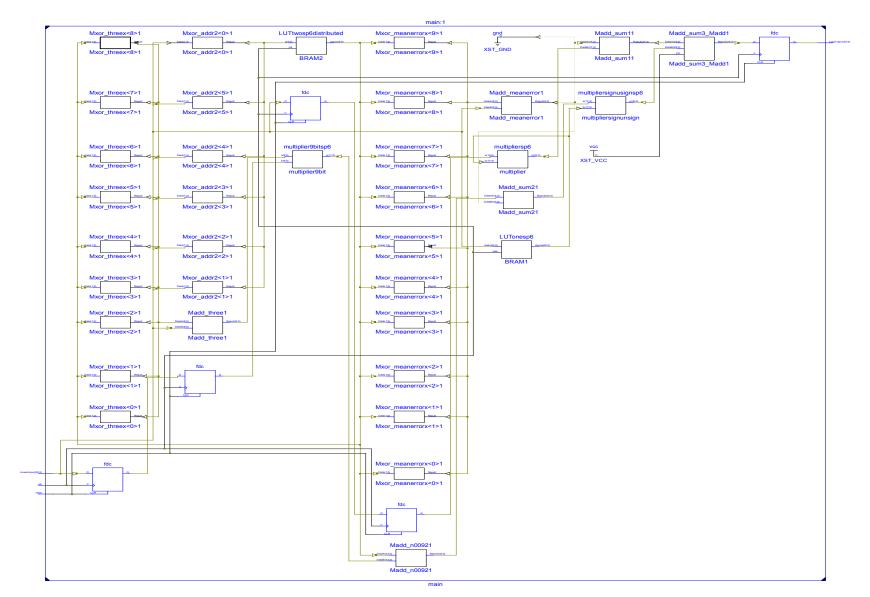

| 4.7  | Spartan 6 based minimum pipelining design of the novel algorithm         | 90  |

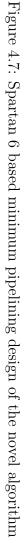

| 4.8  | Spartan 6 based maximum pipelining design of the novel algorithm $$ .    | 91  |

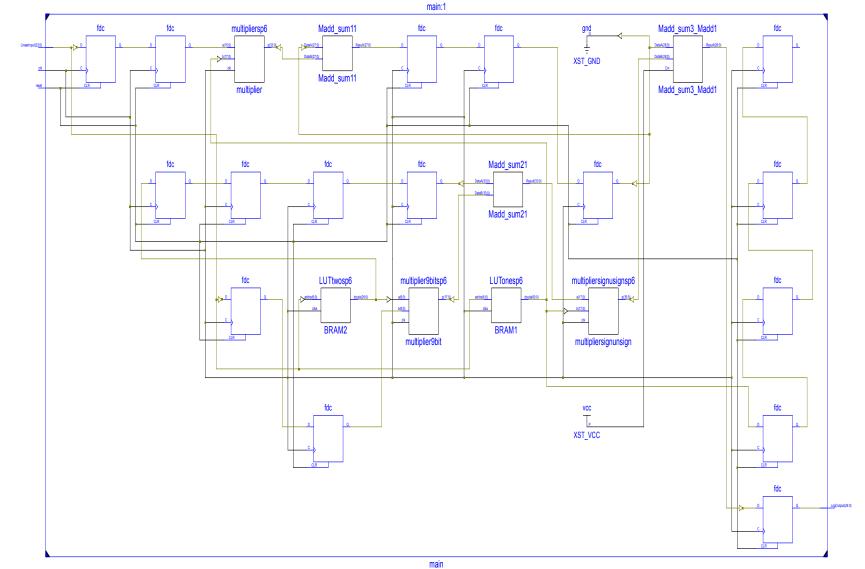

| 5.1  | Right-angled triangle on cartesian coordinates                           | 98  |

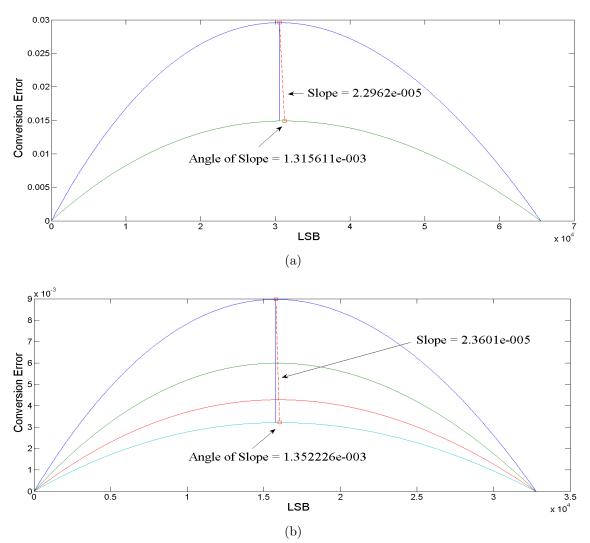

| 5.2  | 1st-stage errors showing magnitude of slope and angle of slope, when     |     |

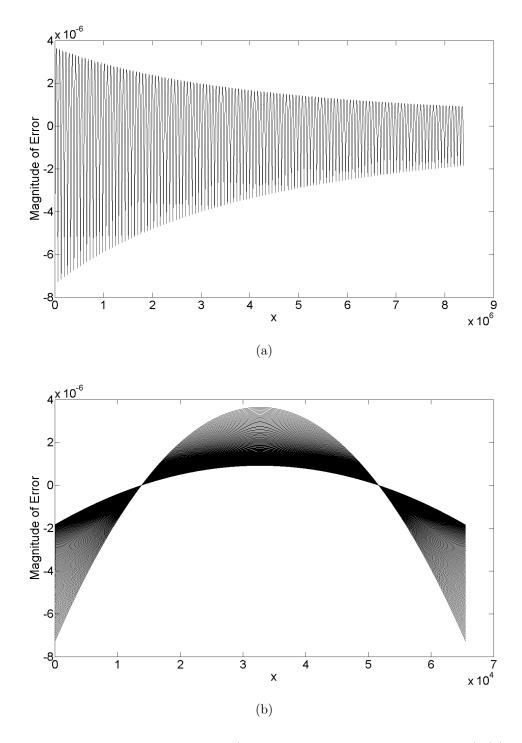

| 0.2  | using (a) 1 MSB and 16 LSB (b) 2 MSB and 15 LSB.                         | 99  |

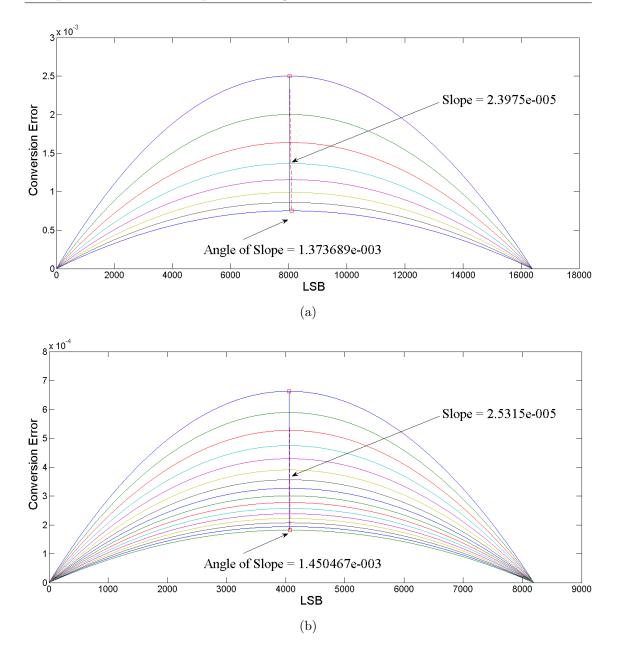

| 5.3  | 1st-stage errors showing magnitude of slope and angle of slope, when     |     |

|      | using (a) 3 MSB and 14 LSB (b) 4 MSB and 13 LSB                          | .00 |

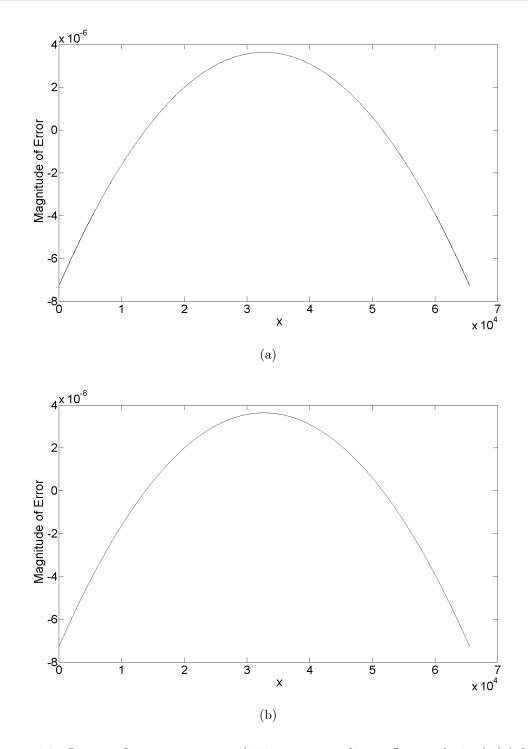

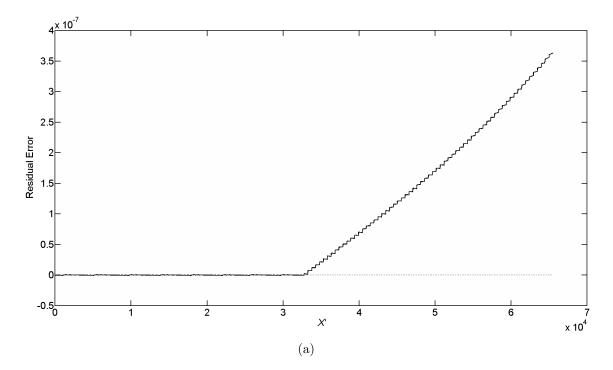

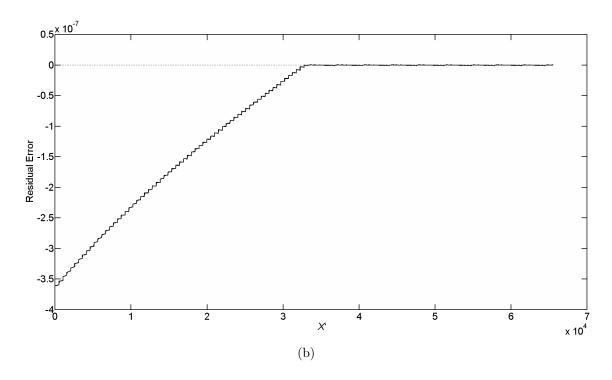

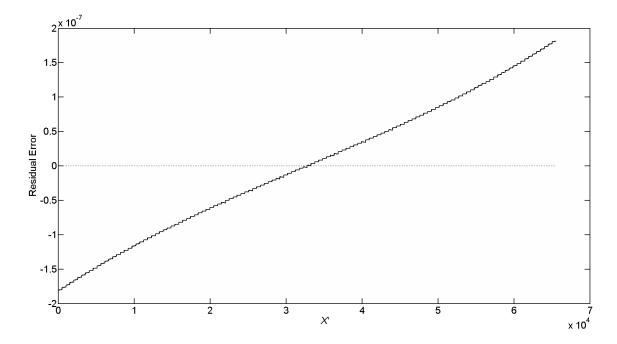

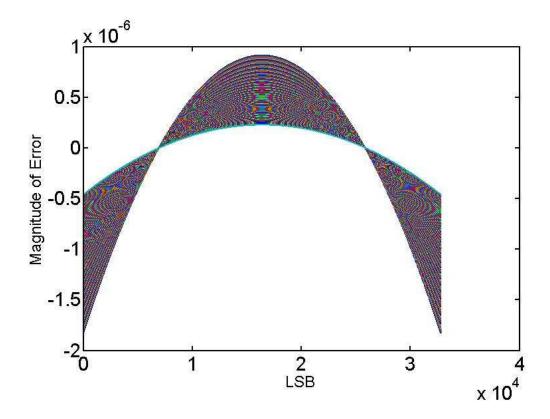

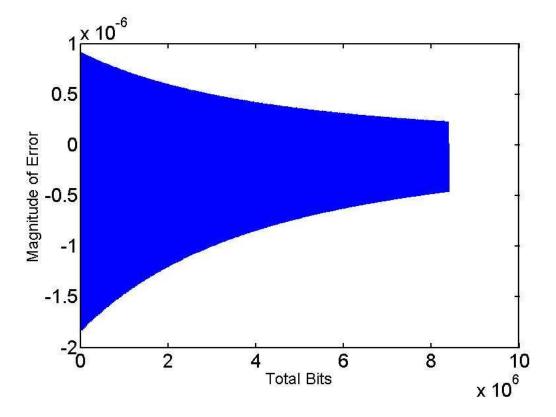

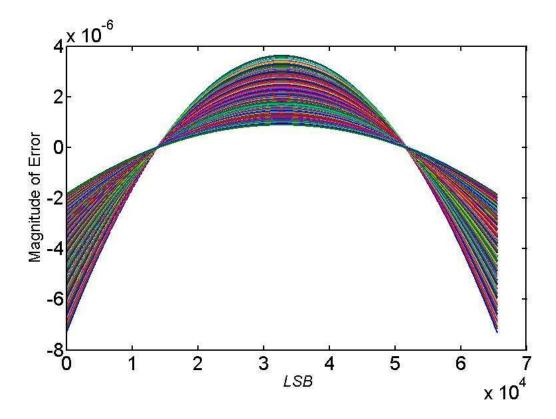

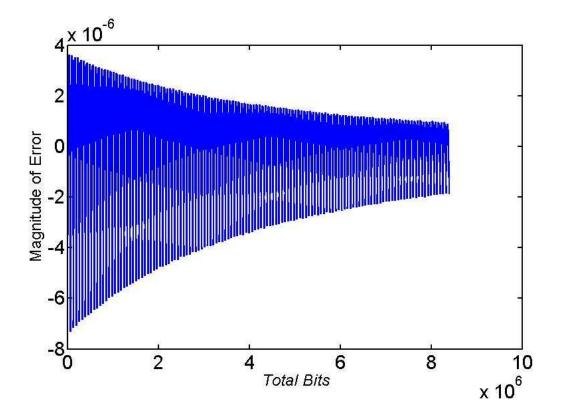

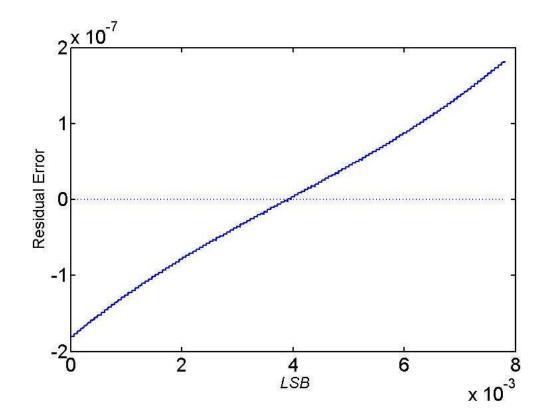

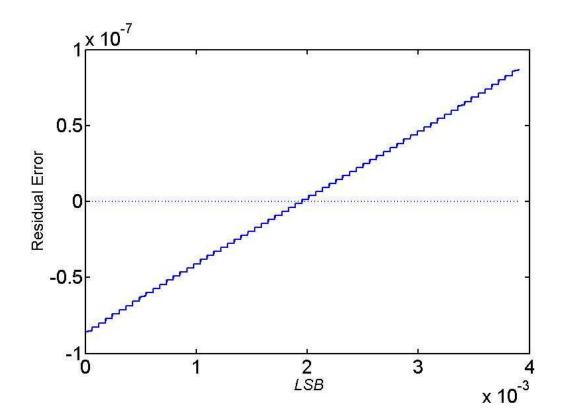

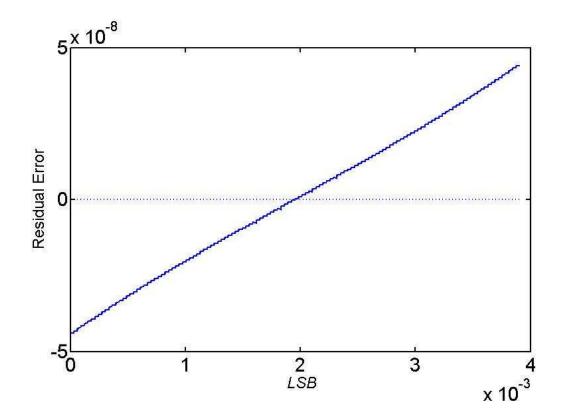

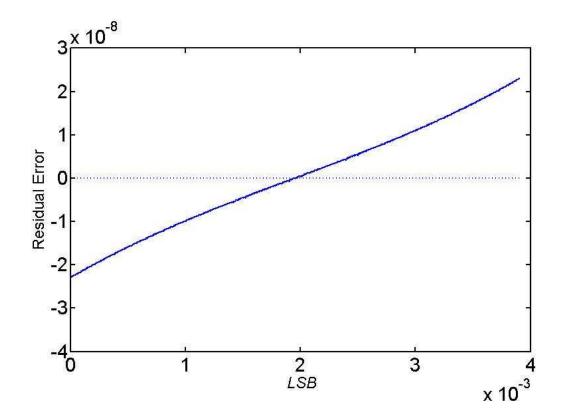

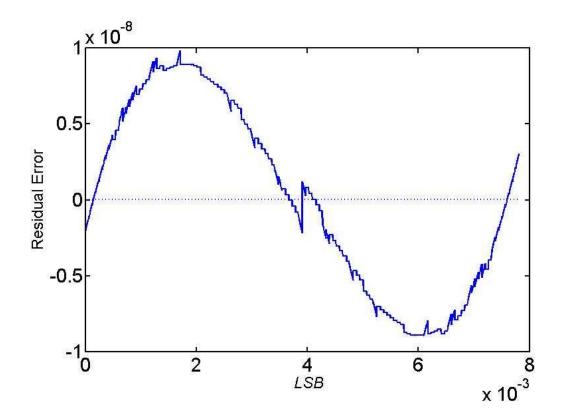

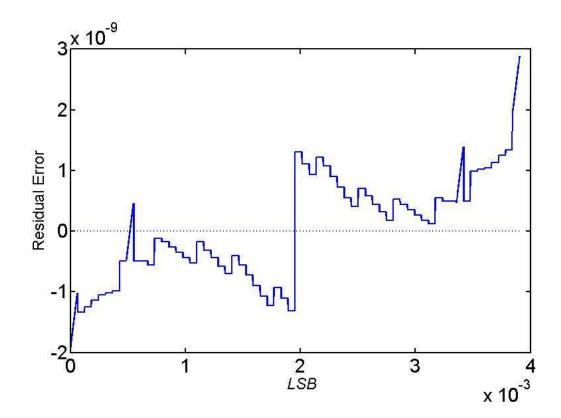

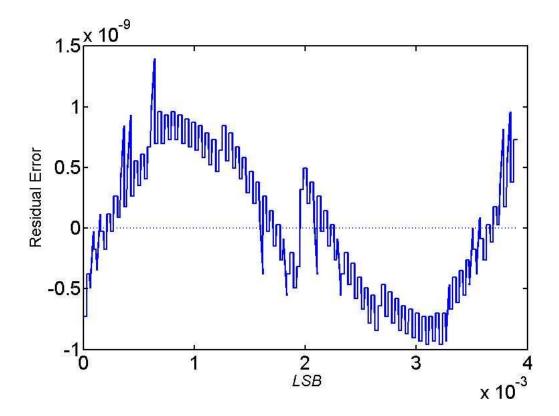

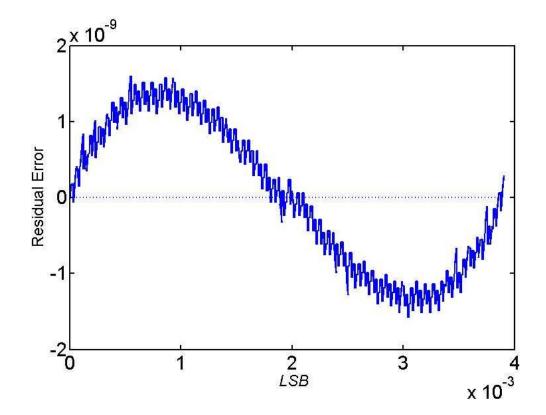

| 5.4  | Residual error produced after superimposing (a) left half of the nor-    |     |

|      | malised curve on the other half                                          | .01 |

| 5.4  | Residual error produced after superimposing (b) right half of the nor-   |     |

|      | malised curve on the other half                                          | .02 |

| 5.5  | Residual error produced after approximating the normalised curve         |     |

|      | using a symmetrical approximation.                                       | .02 |

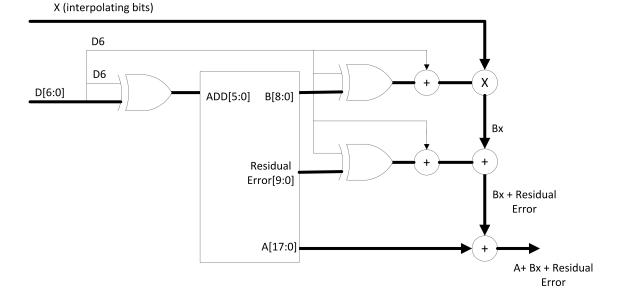

| 5.6  | Improved LUT2 architecture                                               |     |

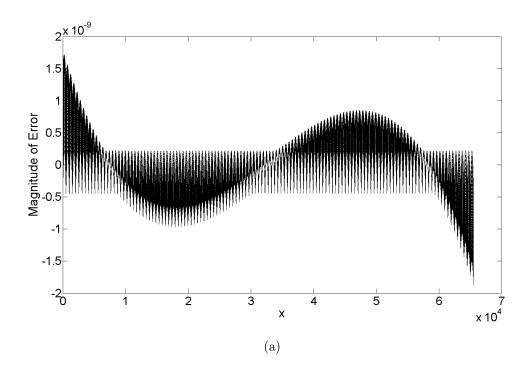

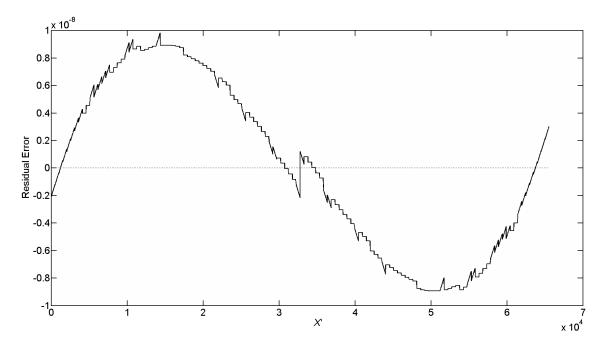

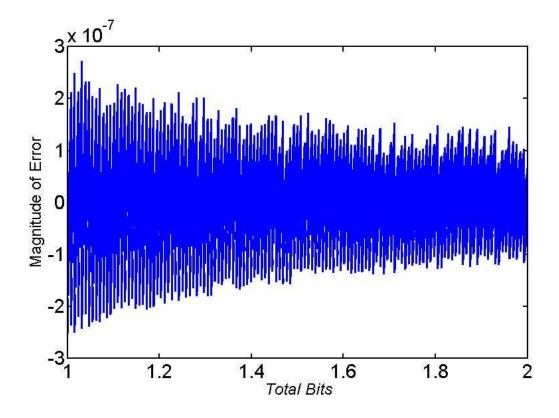

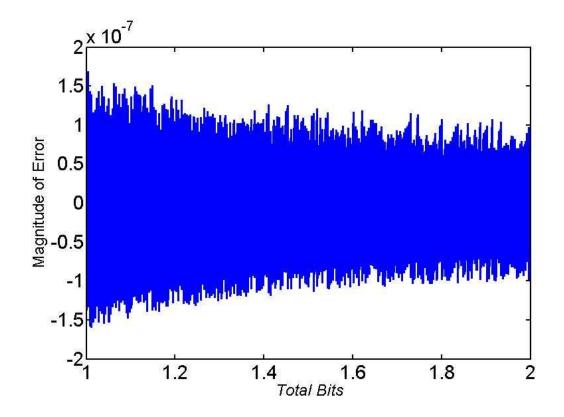

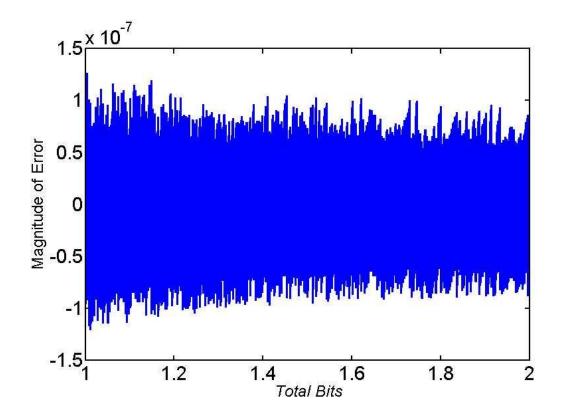

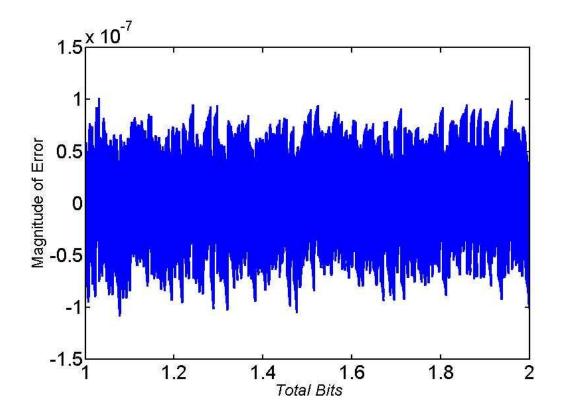

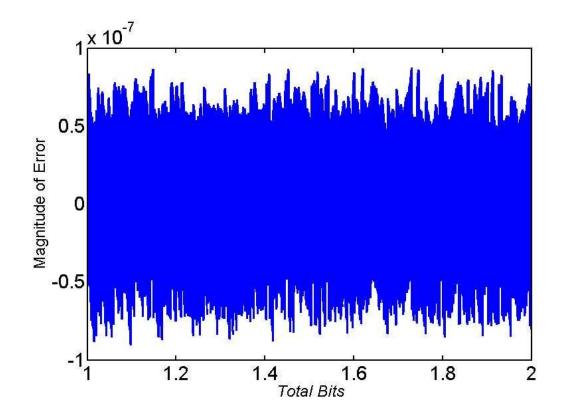

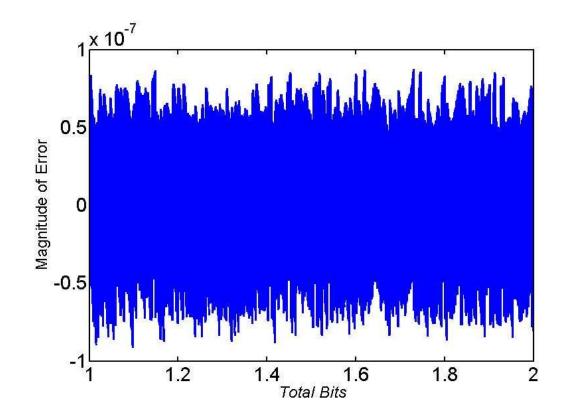

| 5.7  | Residual error in normalised error curve approximation                   |     |

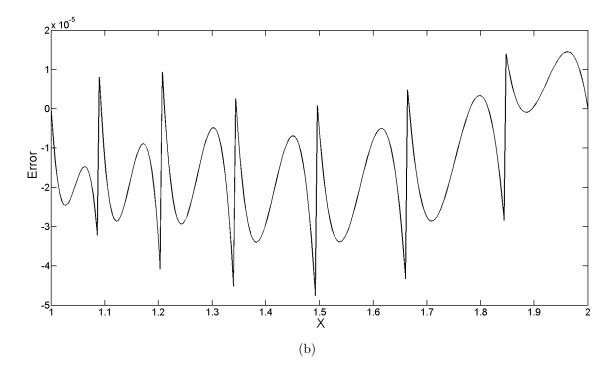

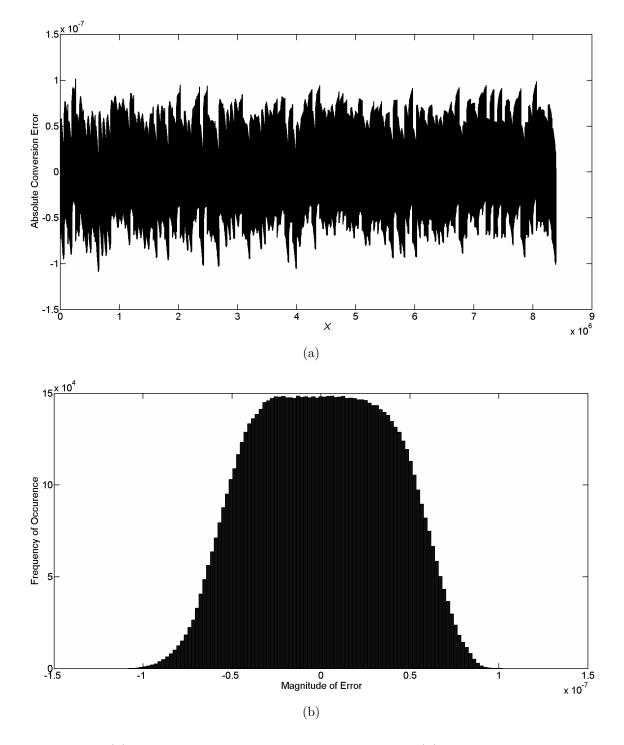

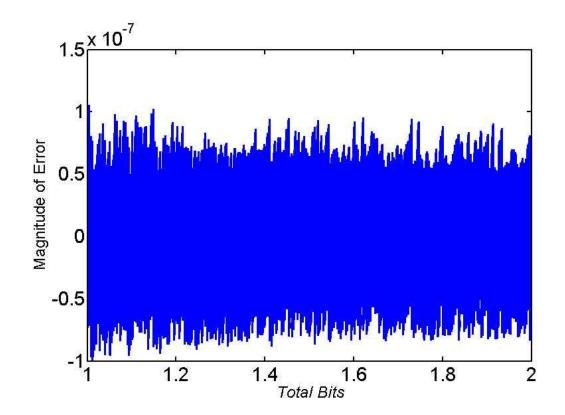

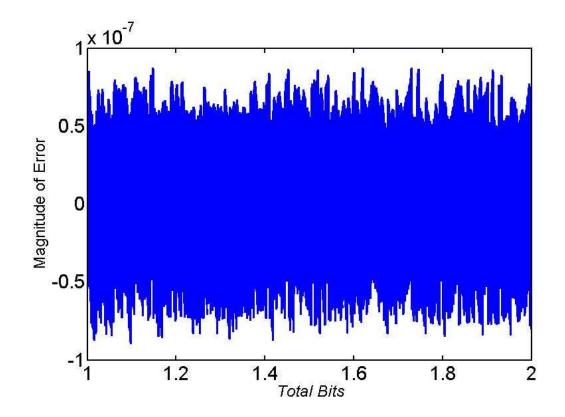

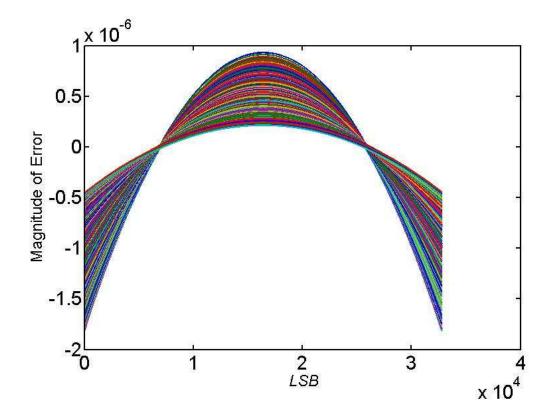

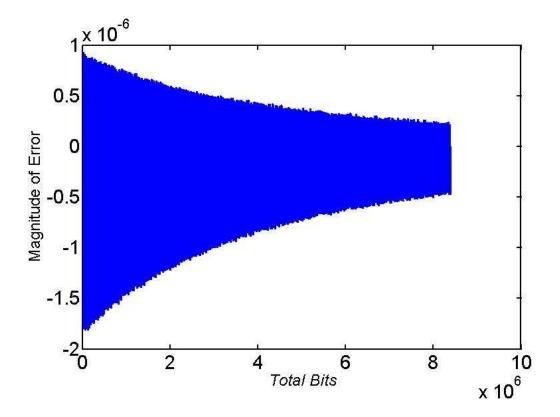

| 5.8  | (a) Overall error obtained in approximation. (b) Histogram of ap-        |     |

|      | proximated error distribution.                                           | .05 |

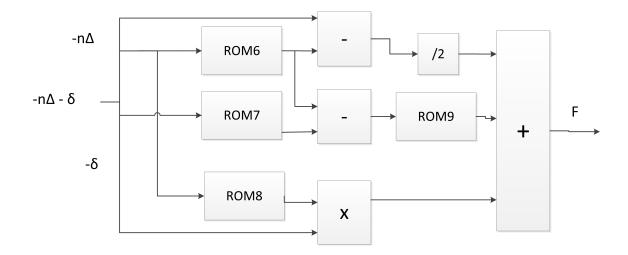

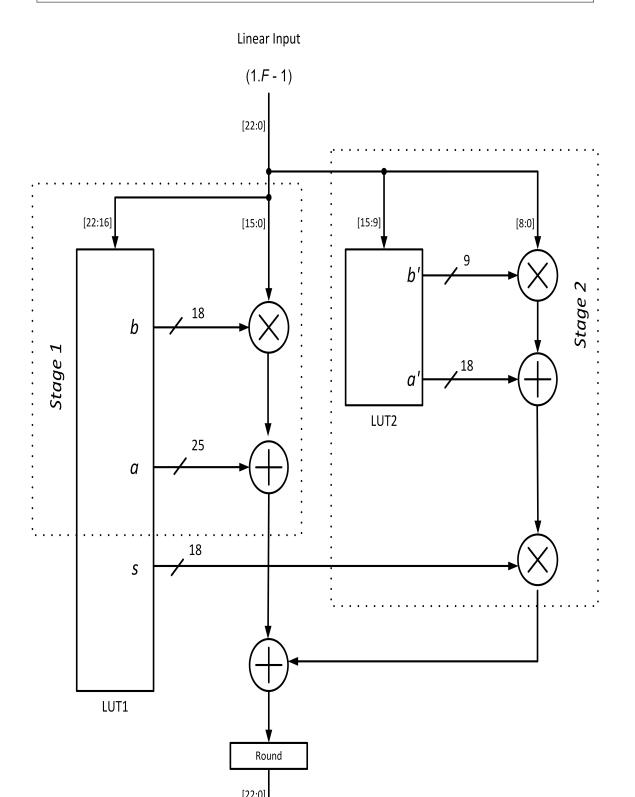

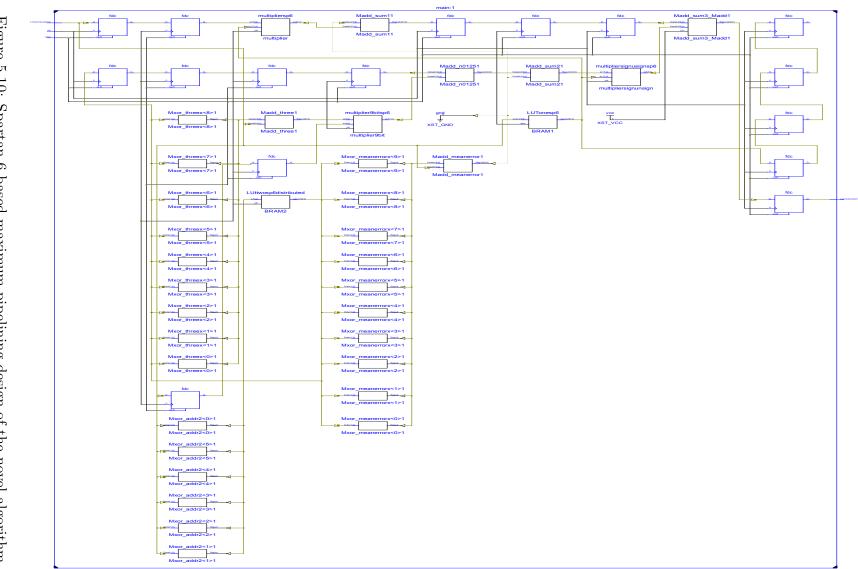

| 5.9  | Spartan 6 based minimum pipelining design of the novel algorithm 1       |     |

| 5.10 |                                                                          |     |

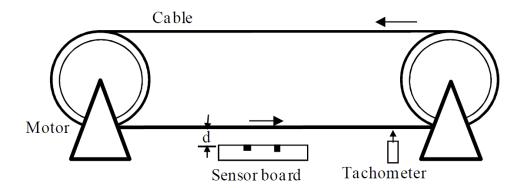

| 6.1  | Cable speed test rig                                                          |

|------|-------------------------------------------------------------------------------|

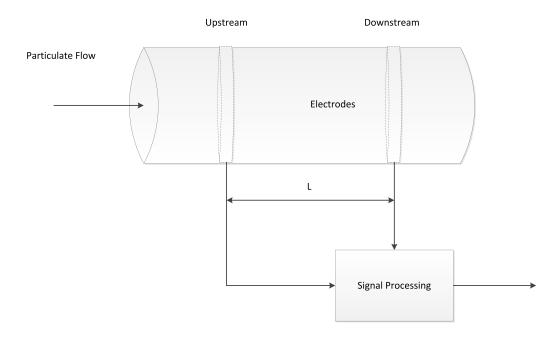

| 6.2  | 2 channel velocimetry system                                                  |

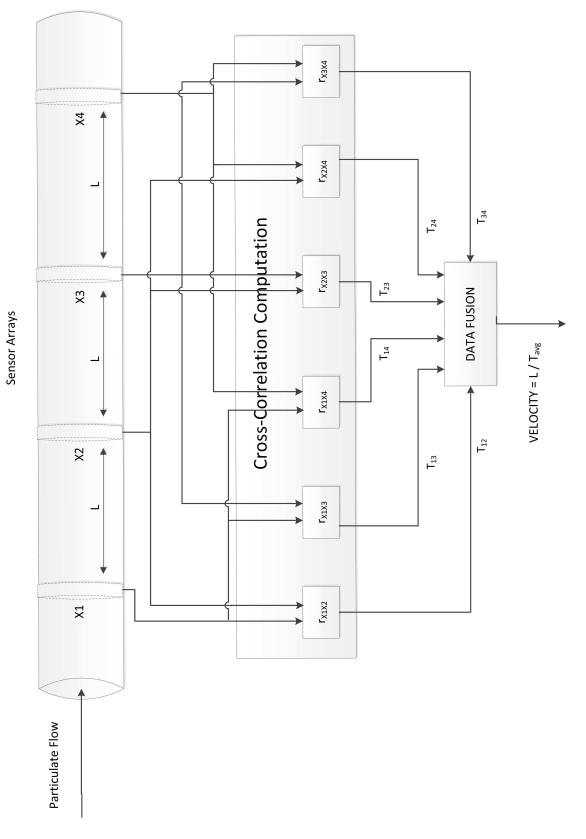

| 6.3  | 4 channel velocimetry system                                                  |

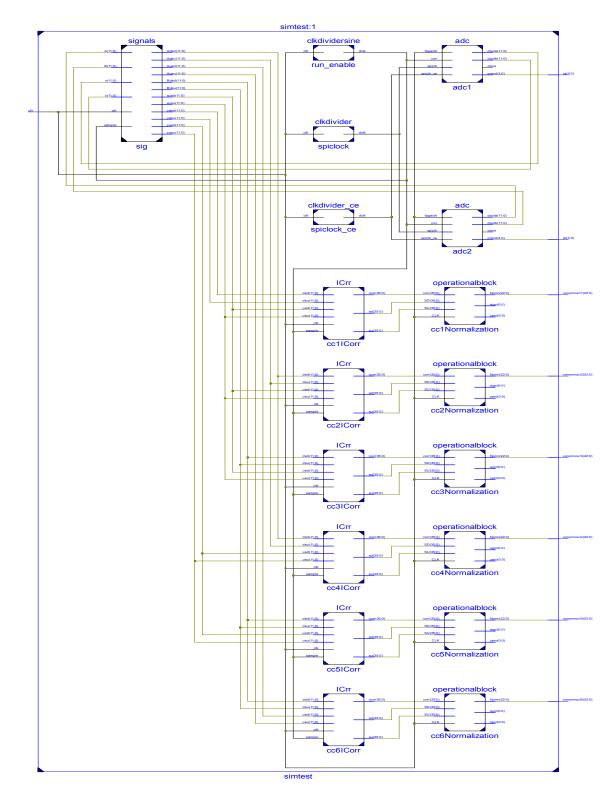

| 6.4  | Architecture for an FPGA-based 4-channel cross-correlation proto-             |

|      | type system                                                                   |

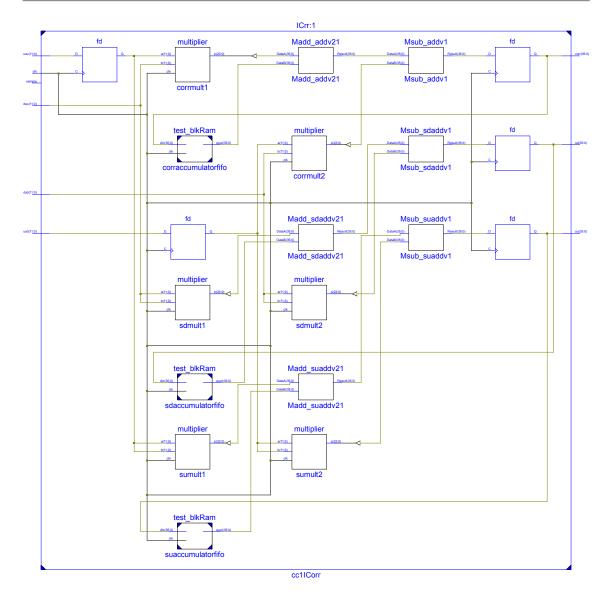

| 6.5  | Incremental calculations arithmetic unit                                      |

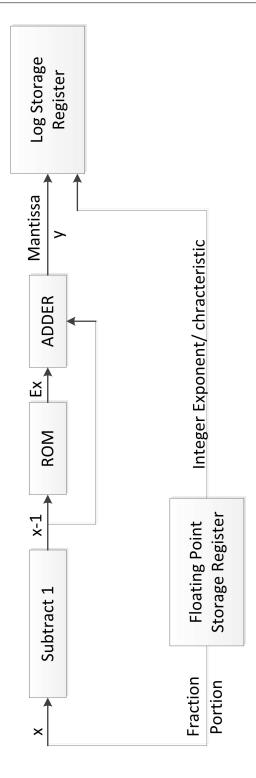

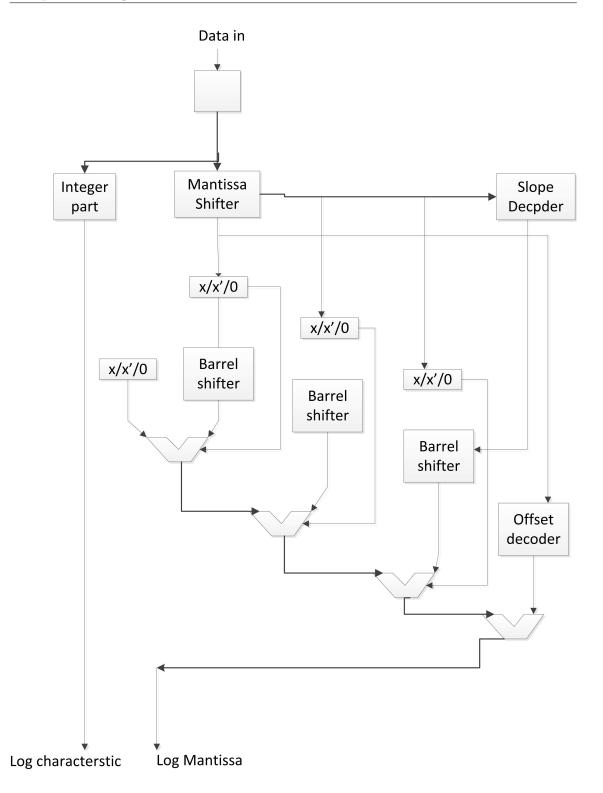

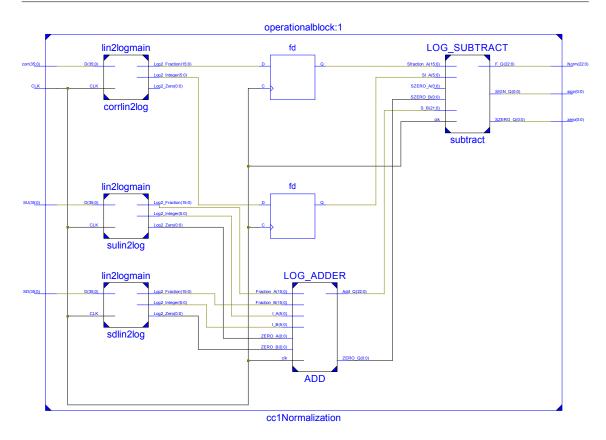

| 6.6  | Lin2Log and normalisation circuit                                             |

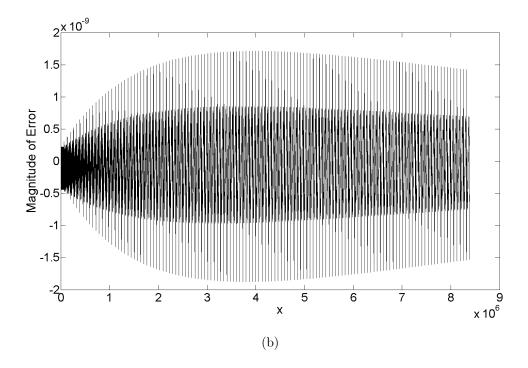

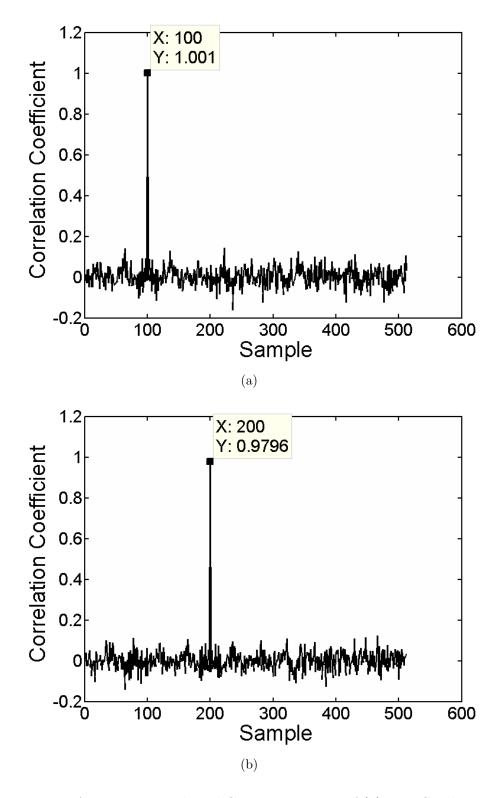

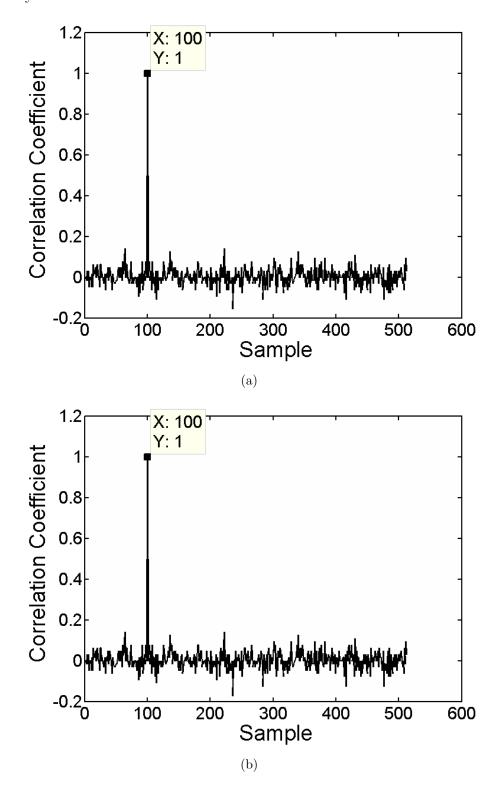

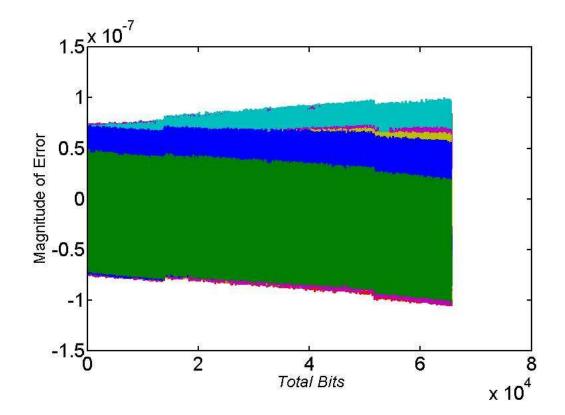

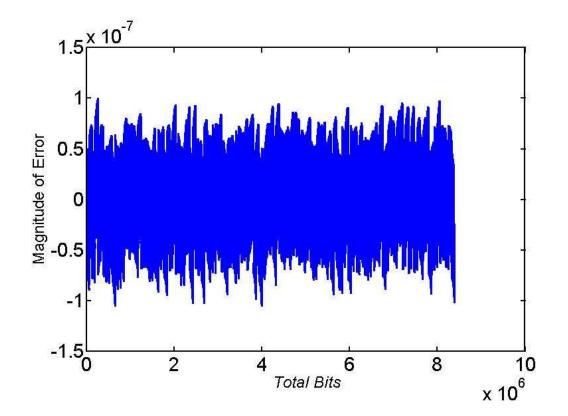

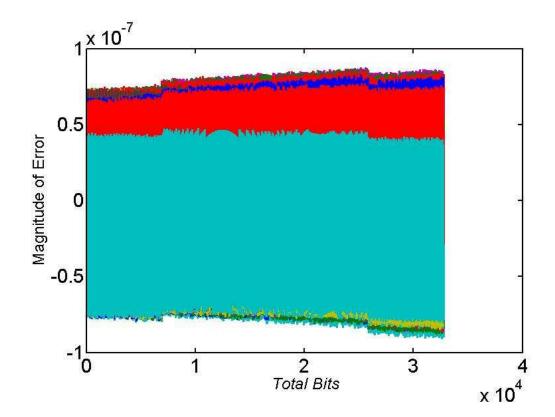

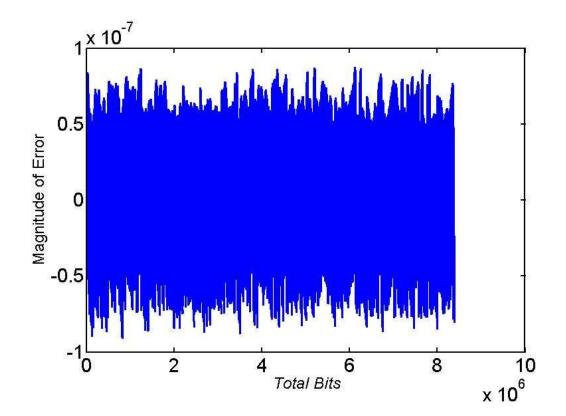

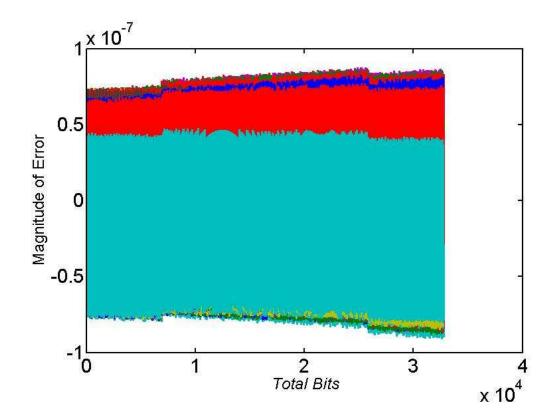

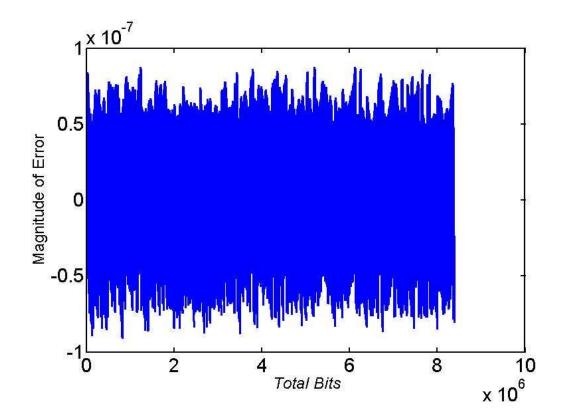

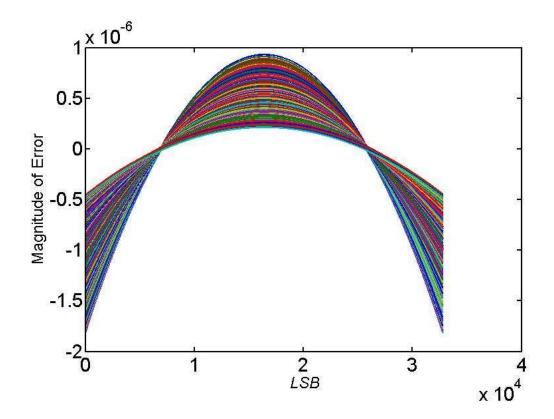

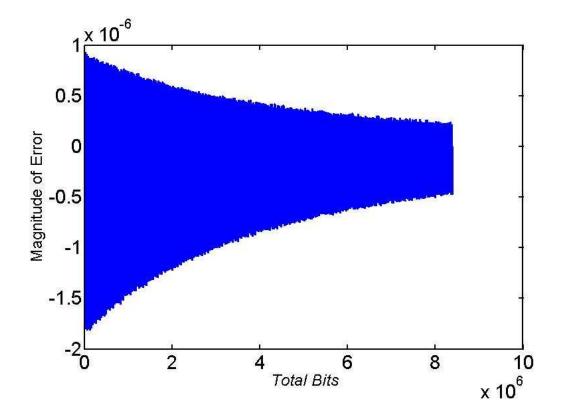

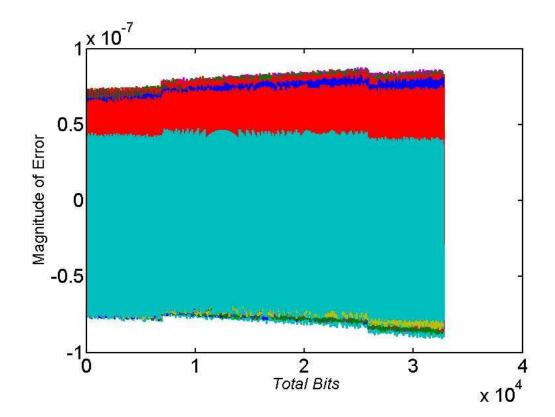

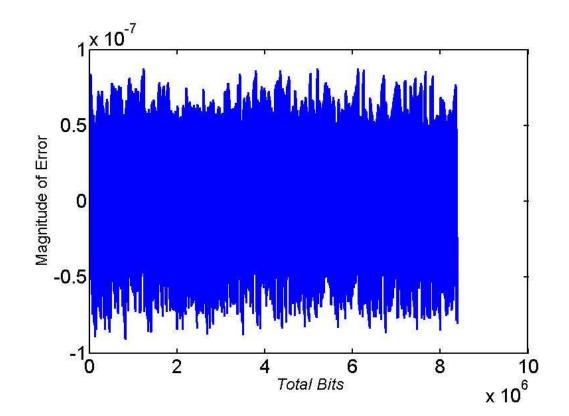

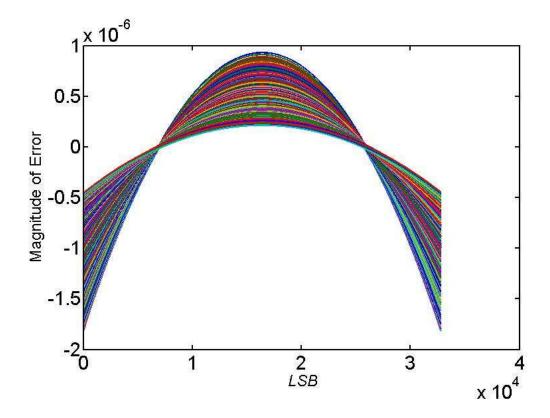

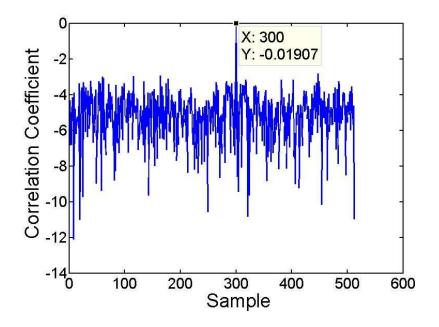

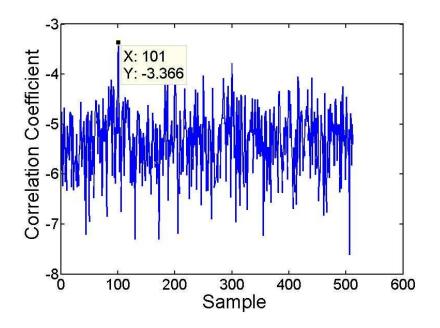

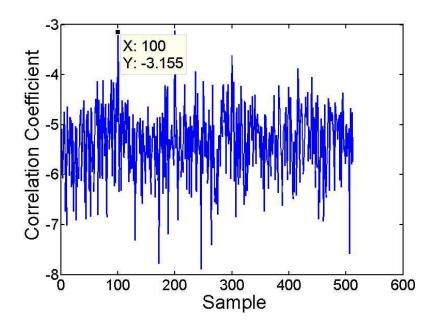

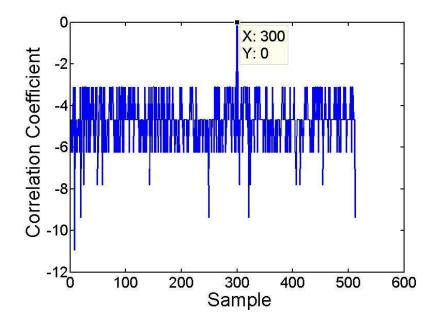

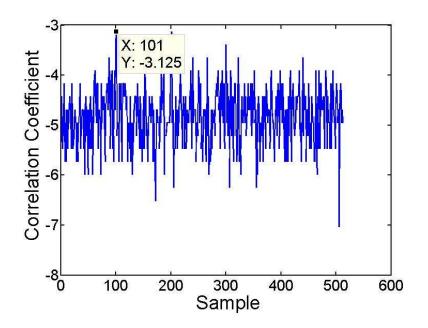

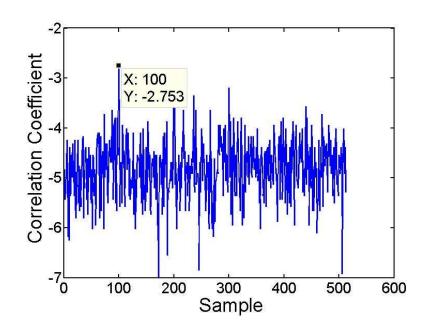

| 6.7  | Log Approximation based Cross-correlation of (a)First Combination             |

|      | (b) Second Combination                                                        |

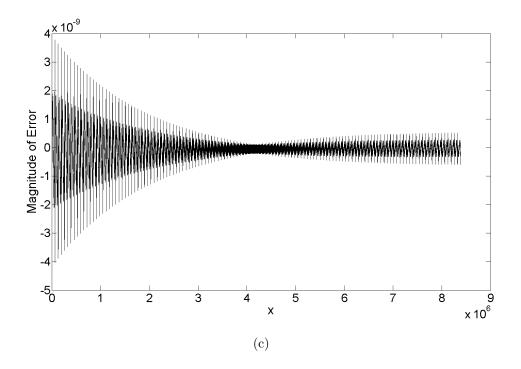

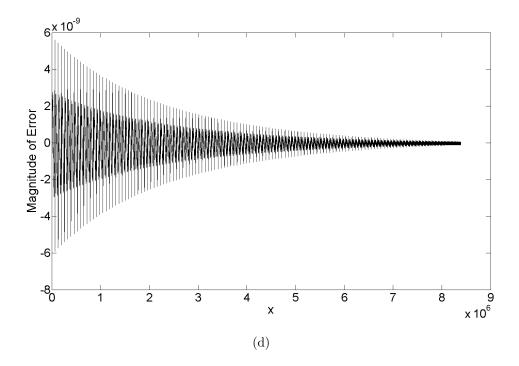

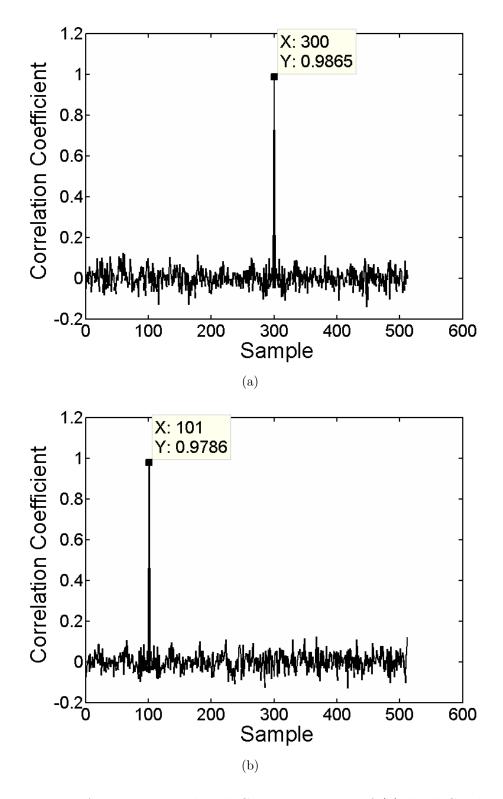

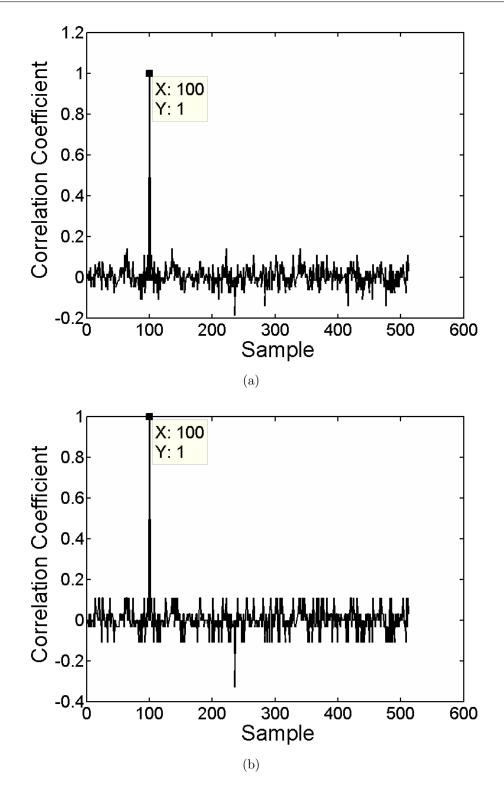

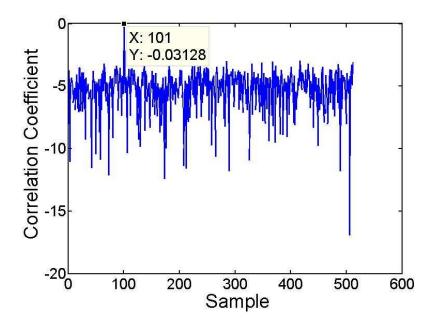

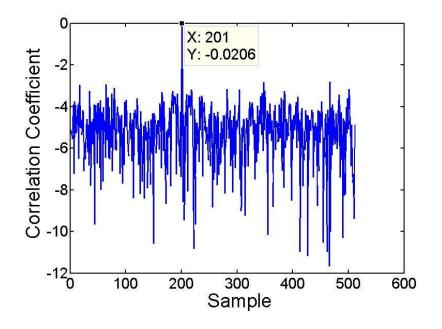

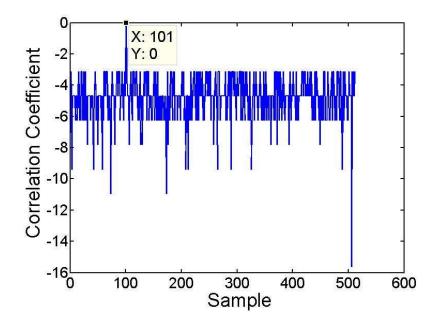

| 6.8  | Log Approximation based Cross-correlation of (a)Third Combination             |

|      | (b) Fourth Combination                                                        |

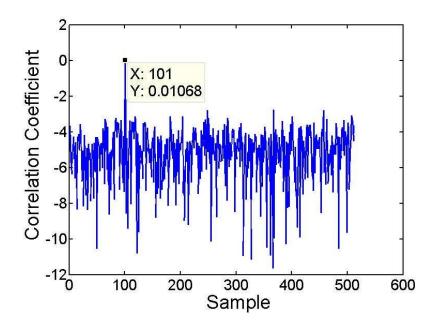

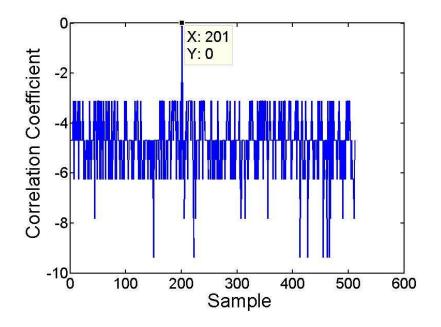

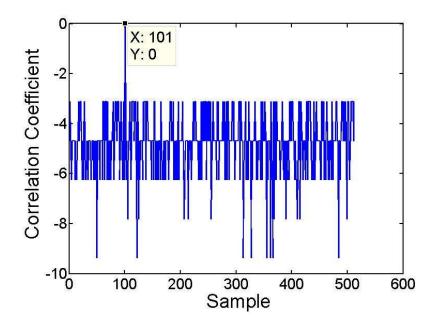

| 6.9  | Log Approximation based Cross-correlation of (a)Fifth Combination             |

|      | (b) Sixth Combination                                                         |

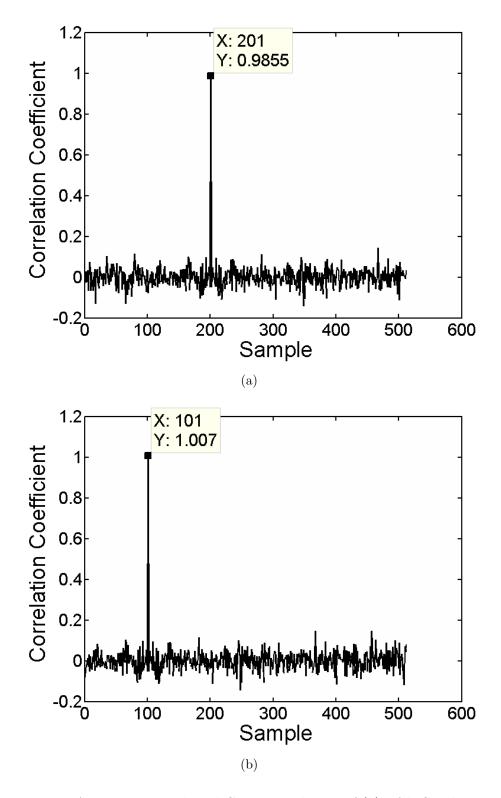

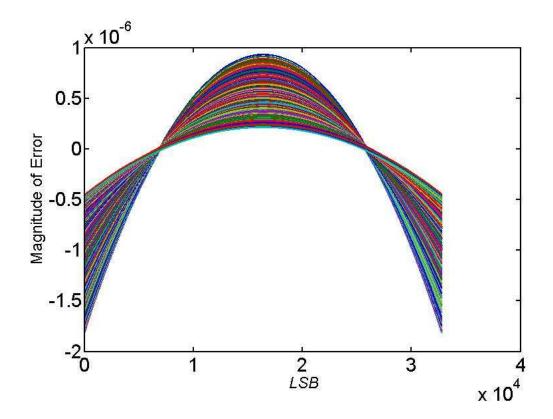

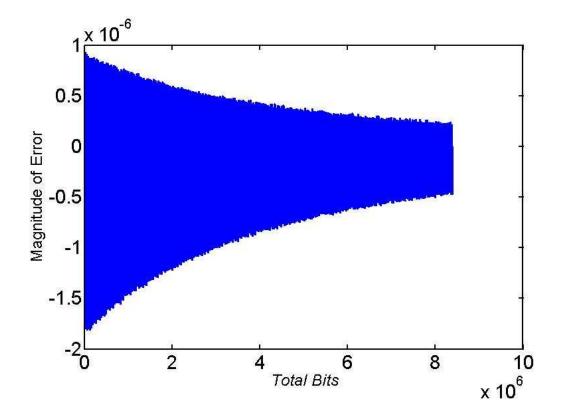

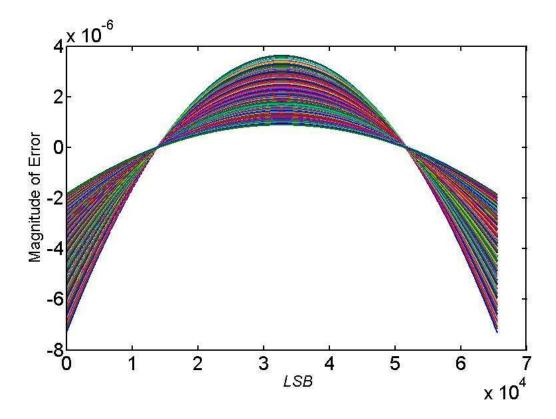

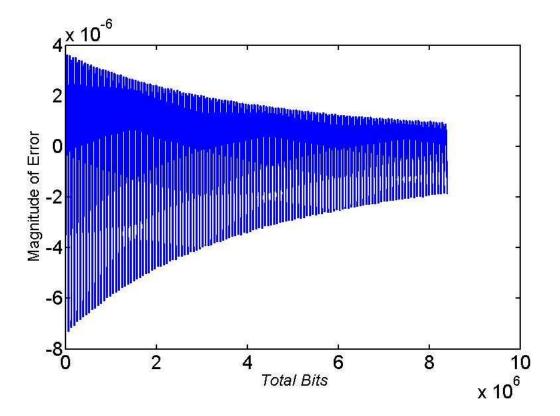

| 6.10 | Log Approximation based (a)Simple moving average (b)Weighted                  |

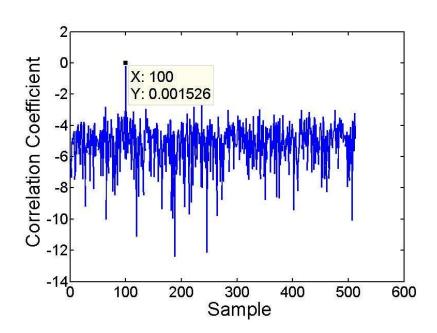

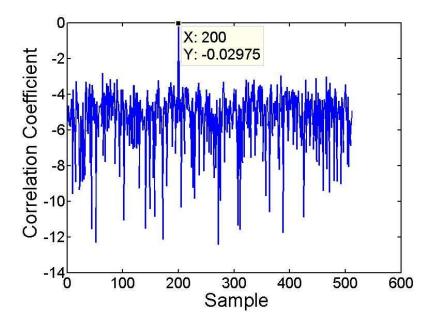

|      | moving average of six combinations                                            |

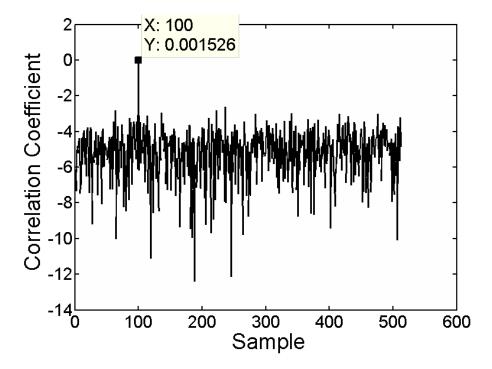

| 6.11 | Logarithmic cross correlation coefficient value of first combination 133      |

| 6.12 | Spartan6 based 4-channel velocimetry system                                   |

| 6.13 | Cross-correlation block of velocimtery system                                 |

| 6.14 | Normalisation block of velocimtery system                                     |

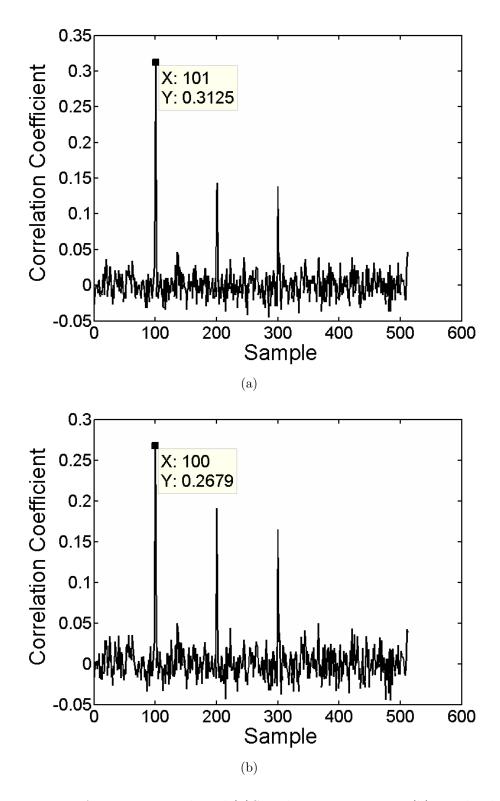

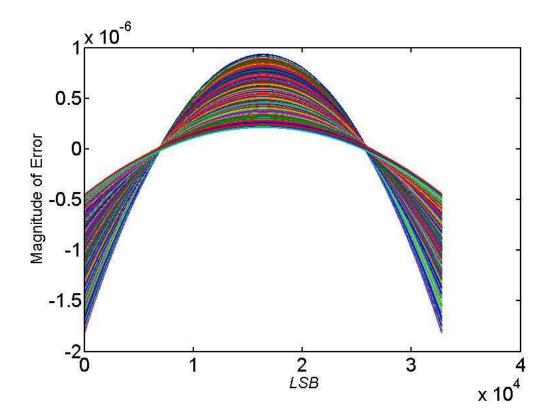

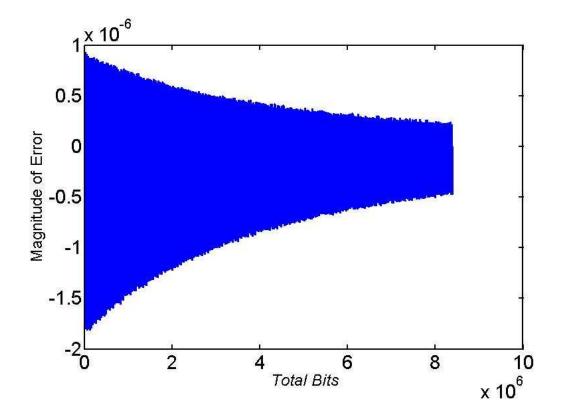

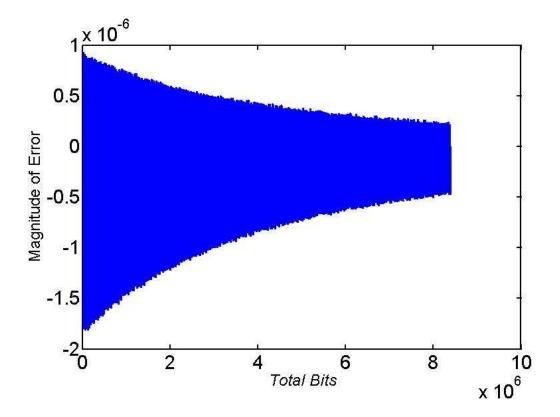

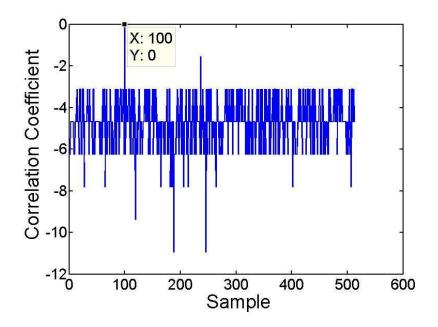

| 6.15 | Approximation of first combination when fraction bits are reduced to          |

|      | (a)12 bits (b)10 bits                                                         |

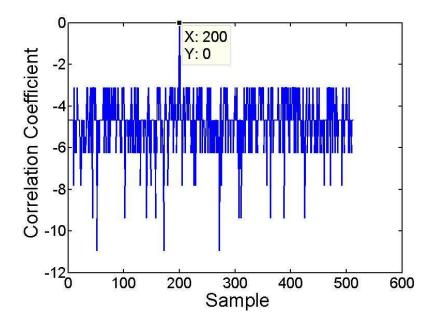

| 6.16 | Approximation of first combination when fraction bits are reduced to          |

|      | (a)8 bits (b)6 bits                                                           |

| A.1  | Configuration 7:16::7:9 - 1st stage errors for each segment 165               |

| A.2  | Configuration 7 : 16 :: 7 : 9 - 1st stage error approximation 166             |

| A.3  | Configuration 7 : 16 :: 7 : 9 - 1st stage + 2nd stage errors for each         |

|      | segment                                                                       |

| A.4  | Configuration 7 : 16 :: 7 : 9 - 1st stage + 2nd stage error approximation.167 |

| A.5  | Configuration $8:15::6:9$ - 1st stage errors for each segment 167             |

| A.6  | Configuration 8 : 15 :: 6 : 9 - 1st stage error approximation                 |

| A.7 Configuration $8:15::6:9$ - 1st stage + 2nd stage errors for each           |     |

|---------------------------------------------------------------------------------|-----|

| segment.                                                                        | 168 |

| A.8 Configuration 8 : 15 :: 6 : 9 - 1st stage + 2nd stage error approximation.  | 169 |

| A.9 Configuration 8:15::7:8 - 1st stage errors for each segment                 | 169 |

| A.10 Configuration 8 : 15 :: 7 : 8 - 1st stage error approximation              | 170 |

| A.11 Configuration 8 : 15 :: 7 : 8 - 1st stage + 2nd stage errors for each      |     |

| segment.                                                                        | 170 |

| A.12 Configuration 8 : 15 :: 7 : 8 - 1st stage + 2nd stage error approximation. | 171 |

| A.13 Configuration 8 : 15 :: 8 : 7 - 1st stage errors for each segment          | 171 |

| A.14 Configuration 8 : 15 :: 8 : 7 - 1st stage error approximation              | 172 |

| A.15 Configuration $8:15::8:7$ - 1st stage + 2nd stage errors for each          |     |

| segment.                                                                        | 172 |

| A.16 Configuration 8 : 15 :: 8 : 7 - 1st stage + 2nd stage error approximation. | 173 |

| B.1 Configuration 7:16::7:9 - 1st stage errors for each segment                 | 174 |

| B.2 Configuration 7:16::7:9 - 1st stage error approximation                     | 175 |

| B.3 Configuration 7 : 16 :: 7 : 9 - Residual error in normalised error curve.   | 175 |

| B.4 Configuration $7: 16:: 7: 9$ - 1st stage + 2nd stage error approximation.   | 176 |

| B.5 Configuration $8:15::6:9$ - 1st stage errors for each segment               | 176 |

| B.6 Configuration 8 : 15 :: 6 : 9 - 1st stage error approximation               | 177 |

| B.7 Configuration 8 : 15 :: 6 : 9 - Residual error in normalised error curve.   | 177 |

| B.8 Configuration 8 : 15 :: 6 : 9 - 1st stage + 2nd stage error approximation.  | 178 |

| B.9 Configuration 8:15::7:8 - 1st stage errors for each segment                 | 178 |

| B.10 Configuration 8 : 15 :: 7 : 8 - 1st stage error approximation              | 179 |

| B.11 Configuration 8 : 15 :: 7 : 8 - Residual error in normalised error curve.  | 179 |

| B.12 Configuration 8 : 15 :: 7 : 8 - 1st stage + 2nd stage error approximation. | 180 |

| B.13 Configuration 8 : 15 :: 8 : 7 - 1st stage errors for each segment          | 180 |

| B.14 Configuration 8 : 15 :: 8 : 7 - 1st stage error approximation              | 181 |

| B.15 Configuration 8 : 15 :: 8 : 7 - Residual error in normalised error curve.  | 181 |

| B.16 Configuration 8 : 15 :: 8 : 7 - 1st stage + 2nd stage error approximation. | 182 |

| C.1 Configuration 7:16::7:9 - 1st stage errors for each segment                 | 183 |

C.2 C.3 Configuration 7:16:7:9 - Residual error in normalised error curve. 184 C.4 Configuration 7:16::7:9 - 1st stage + 2nd stage error approximation.185 C.5Configuration 8:15::6:9 - 1st stage errors for each segment. . . . 185 C.6 Configuration 8:15::6:9 - 1st stage error approximation. . . . . . 186 C.7Configuration 8:15::6:9 - Residual error in normalised error curve. 186 Configuration 8: 15:: 6: 9 - 1st stage + 2nd stage error approximation. 187 C.8 C.9 Configuration 8 : 15 :: 7 : 8 - 1st stage errors for each segment. . . . . 187 C.11 Configuration 8:15:7:8 - Residual error in normalised error curve. 188 C.12 Configuration 8:15::7:8 - 1st stage + 2nd stage error approximation.189 C.13 Configuration 8:15::8:7 - 1st stage errors for each segment. . . . 189 C.14 Configuration 8:15::8:7 - 1st stage error approximation. . . . . . 190 C.15 Configuration 8:15::8:7 - Residual error in normalised error curve. 190 C.16 Configuration 8:15::8:7 - 1st stage + 2nd stage error approximation.191 D.1 Configuration 7: 16:: 7: 9 - 1st stage errors for each segment. . . . . 192 D.2 Configuration 7:16:7:9 - Residual error in normalised error curve. 193 D.3 Configuration 7: 16:: 7: 9 - 1st stage + 2nd stage error approximation. 194 D.4 D.5Configuration 8:15::6:9 - 1st stage errors for each segment. . . . . 194 D.6 Configuration 8:15::6:9 - 1st stage error approximation. . . . . . . . 195 D.7 Configuration 8 : 15 :: 6 : 9 - Residual error in normalised error curve. 195 D.8 Configuration 8:15::6:9 - 1st stage + 2nd stage error approximation.196 Configuration 8 : 15 :: 7 : 8 - 1st stage errors for each segment. . . . . 196 D.9 D.10 Configuration 8:15::7:8 - 1st stage error approximation. . . . . . . 197 D.11 Configuration 8:15::7:8 - Residual error in normalised error curve. 197 D.12 Configuration 8 : 15 :: 7 : 8 - 1st stage + 2nd stage error approximation. 198 D.13 Configuration 8 : 15 :: 8 : 7 - 1st stage errors for each segment. . . . . 198 D.15 Configuration 8:15::8:7 - Residual error in normalised error curve. 199 D.16 Configuration 8:15::8:7 - 1st stage + 2nd stage error approximation.200

| E.1            | Cross correlation coefficient value of first combination - using 16 frac- |

|----------------|---------------------------------------------------------------------------|

|                | tional bits                                                               |

| E.2            | Cross correlation coefficient value of second combination - using 16      |

|                | fractional bits                                                           |

| E.3            | Cross correlation coefficient value of third combination - using $16$     |

|                | fractional bits                                                           |

| E.4            | Cross correlation coefficient value of fourth combination - using $16$    |

|                | fractional bits                                                           |

| E.5            | Cross correlation coefficient value of fifth combination - using 16 frac- |

|                | tional bits                                                               |

| E.6            | Cross correlation coefficient value of sixth combination - using 16       |

|                | fractional bits                                                           |

| $\mathrm{E.7}$ | Log Approximation Based Simple Moving Average of Six combina-             |

|                | tions - using 16 fractional bits                                          |

| E.8            | Log Approximation Based Weighted Moving Average of Six combi-             |

|                | nations - using 16 fractional bits                                        |

| E.9            | Cross correlation coefficient value of first combination - using 4 frac-  |

|                | tional bits                                                               |

| E.10           | Cross correlation coefficient value of second combination - using $6$     |

|                | fractional bits                                                           |

| E.11           | Cross correlation coefficient value of third combination - using 6 frac-  |

|                | tional bits                                                               |

| E.12           | Cross correlation coefficient value of fourth combination - using $6$     |

|                | fractional bits                                                           |

| E.13           | Cross correlation coefficient value of fifth combination - using 6 frac-  |

|                | tional bits                                                               |

| E.14           | Cross correlation coefficient value of sixth combination - using 6 frac-  |

|                | tional bits                                                               |

| E.15           | Log Approximation Based Simple Moving Average of Six combina-             |

|                | tions - using 6 fractional bits                                           |

| E.16 Log Approximation Based Weighted Moving Average of Six combi- |       |

|--------------------------------------------------------------------|-------|

| nations - using 6 fractional bits                                  | . 209 |

# List of Tables

| 2.1 | Cyclone FPGA Family Overview                                             | 15  |

|-----|--------------------------------------------------------------------------|-----|

| 2.2 | Spartan3 FPGA Family Overview                                            | 16  |

| 2.3 | Spartan6 FPGA Family Overview                                            | 19  |

| 2.4 | Hardware usage in multiplication of single and double floating point     |     |

|     | precision                                                                | 27  |

| 2.5 | Hardware usage in division of single and double floating point precision | 27  |

| 4.1 | Larson table of maximum errors using PWL Approximation $\ldots$ .        | 79  |

| 4.2 | Ideal Performance using Scaled Max Error Curve for 23 bit fractional     |     |

|     | input (MATLAB simulation results)                                        | 87  |

| 4.3 | LUT coefficient bits (MATLAB simulation results)                         | 88  |

| 4.4 | Implementation statistics                                                | 89  |

| 4.5 | Comparison of Results with previous work for Single Floating Point       |     |

|     | Precision.                                                               | 92  |

| 5.1 | LUT coefficient bits                                                     | 96  |

| 5.2 | LUT coefficient bits                                                     | 103 |

| 5.3 | LUT coefficient bits                                                     | 104 |

| 5.4 | Device Utilisation Statistics (LUT2 with additional adder and xor        |     |

|     | gates)                                                                   | 106 |

| 5.5 | Device Utilisation Statistics (LUT2 without additional adder and xor     |     |

|     | gates)                                                                   | 109 |

| 5.6 | Device Utilisation Statistics (Reduced LUT2 architecture implemented)    |     |

|     | 110                                                                      |     |

| 5.7 | Utilization Comparison                                                   | 111 |

| 6.1 | FPGA implementation of 2-channel signal                        | 137 |

|-----|----------------------------------------------------------------|-----|

| 6.2 | FPGA implementation of 4-channel signal with exceeded hardware |     |

|     | resources in detail                                            | 138 |

| 6.3 | FPGA implementation of 4-channel signal                        | 138 |

# Abbreviations

| BRAM    | : | Block random access memory                      |  |  |  |

|---------|---|-------------------------------------------------|--|--|--|

| DRAM    | : | Distributed random access memory                |  |  |  |

| DSP     | : | Digital Signal Processing                       |  |  |  |

| DFT     | : | Discrete Fourier Transform                      |  |  |  |

| FPGA    | : | Field Programmable Gate Arrays                  |  |  |  |

| FFT     | : | Fast Fourier Transform                          |  |  |  |

| GPU     | : | Graphical processing unit                       |  |  |  |

| LSP     | : | Logarithmic Signal Processing                   |  |  |  |

| LNS     | : | Logarithmic Number System                       |  |  |  |

| LUT     | : | Look Up Table                                   |  |  |  |

| Log     | : | Logarithm                                       |  |  |  |

| LIN2LOG | : | Linear To Logarithm                             |  |  |  |

| LOG2LIN | : | Logarithm TO Linear                             |  |  |  |

| LOD     | : | Leading One Detector                            |  |  |  |

| LSB     | : | Least Significant Bit                           |  |  |  |

| LZD     | : | Leading Zero Detector                           |  |  |  |

| MSB     | : | Most Significant Bit                            |  |  |  |

| PWL     | : | Piecewise Linear                                |  |  |  |

| PWP     | : | Piecewise Polynomial                            |  |  |  |

| ROM     | : | Read Only Memory                                |  |  |  |

| ULP     |   |                                                 |  |  |  |

| ULP     | : | Unit Last Place                                 |  |  |  |

| VLSI    | : | Unit Last Place<br>Very Large Scale Integration |  |  |  |

## Chapter 1

## Introduction

### 1.1 Motivation, Aims & Objective

In the world today digital electronics are used in almost every other application. Whether, these applications are related to day-to-day activities, defence services or research work, they all perform computations in the digital field. The technologies used in implementing digital electronics in hardware have evolved with time. One of the important parameters for a computation is its precision (i.e. the bit resolution). The precision used in a computation is responsible for the result's accuracy.

There are many number systems used to perform computations in digital electronics. However, the two most common number systems used are the fixed and floating point number systems. These number systems are acceptable for low resolution simple arithmetic computations. The usage of fixed and floating point numbers in real time applications with higher bit resolution requires enormous and complex hardware architecture. This complex hardware architecture and real-time computation of data creates the problem of bottlenecks and inefficient systems for real-time computations. The research in this thesis solves the problem by using logarithm numbers instead of fixed/floating point numbers in computations. The research in this thesis designs a single floating point precision Lin2Log converter which uses less hardware (maintaining similar accuracy) than the recently published Lin2Log converters and uses it in a real-time application.

Logarithms were first introduced by John Napier in 1614. The logarithm of a

number is defined as the exponent by which a number is raised to produce the same number again, for example

$$1000 = 10^3 \tag{1.1}$$

Thus, the number 1000 has a logarithm value of 3 with base 10. The logarithm mathematically can be expressed as

$$\log_{10}(1000) = 3 \tag{1.2}$$

In computers/digital electronics a logarithm with base 2 otherwise known as binary logarithm is used. The binary logarithm is simple and easy to implement in hardware when compared to the implementation of other bases of logarithm in computers/digital electronics.

Logarithms have been used as a tool in mathematics, to simplify complex arithmetic operations. The logarithm properties of the linear operations of multiplication, division, power, addition and subtraction are shown in equations 1.3, 1.4, 1.5, 1.6 and 1.7, where x and y are the numbers in the linear domain. The use of logarithms reduces multiplication, division and power in the linear domain to addition, subtraction and multiplication in the log domain respectively.

$$log_b(x.y) = log_b(x) + log_b(y)$$

(1.3)

$$log_b(\frac{x}{y}) = log_b(x) - log_b(y) \tag{1.4}$$

$$log_b(x^p) = p.log_b(x) \tag{1.5}$$

$$\log_b(x+y) = \log_b|x| + \log_b(1+2^{\log_b|y|-1})$$

(1.6)

$$\log_b(x-y) = \log_b|x| + \log_b(1 - 2^{\log_b|y|-1})$$

(1.7)

The properties of logarithms save time for multiplication and division in a processor on a computer and reduce the area in integrated circuits by replacing hardware multipliers and shifters by adders and subtractors. Logarithmic signal processing has been used in a number of applications and is of increasing interest because of the potential for area and higher resolution architectures [1]. As a consequence, many algorithms and hardware architectures have been proposed over the past 50 years for converting a normalised binary number x into a binary logarithm  $(log_2x)$  or converting the binary exponent  $(2^{log_2x})$  back to a normalised binary number. These algorithms vary widely in terms of their accuracy, efficiency and speed. Over such a long time-span there have also been significant changes in the performance of the implementation technologies, resulting in newer architectures capable of achieving increasing conversion accuracies and making the logarithmic number system (LNS) a viable alternative in a number of modern applications [2–4], speech recognition [5] and digital hearing aids [6].

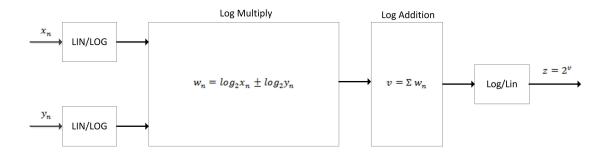

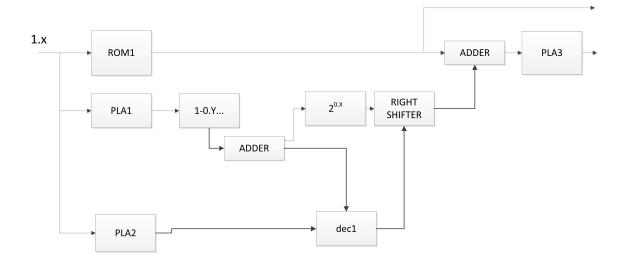

There are two generic architectures for LNS processing. The first architecture consists of all arithmetic operations  $(\times, \div, +, -)$  to be performed in the logarithmic domain (see figure 1.1), whereas in the second architecture, sometimes called hybrid-LNS, the arithmetic operations  $(\times, \div)$  are performed in the log domain while the remaining operations (+, -) are performed in the linear domain (see figure 1.2). The reason for using two different domains in hybrid-LNS is that logarithmic addition and subtraction are non-linear functions requiring further approximation methods (see equations 1.6 and 1.7), frequently based on piecewise linear (PWL) or higherorder piecewise polynomial (PWP) methods, thereby offsetting any advantages of using the LNS (Logarithmic Number System). The hybrid LNS architectures have been used in many applications such as image compression where the forward and inverse discrete cosine transforms (DCT) are performed on digital images [7].

The disadvantage of hybrid LNS is that for some algorithms repeated conversion to and from the log domain is necessary. The choice of architecture, the required

Figure 1.1: Standard logarithmic processor.

Figure 1.2: Hybrid logarithmic processor.

resolution and the complexity of the overall conversion algorithms are strongly application dependent and are only advantageous if the sum of complex arithmetic operations is reduced, resulting in decreased power consumption or reduced circuit area [8].

The recent research has tended to ignore a potential niche where logarithmic signal processing has advantages over both fixed and floating point solutions. Thus, the research work objective was to establish an algorithm for analysing and modelling the performance of a Lin2Log converter with single floating point precision [9]. As most of the LSP-based applications require a high dynamic range with limited accuracy, single floating point precision (i.e. 32 bit) is chosen for the purposes of this research.

Another objective of the research was to map the architecture of a logarithmic converter onto a reconfigurable logic device (i.e. FPGA). Finally in this research a cross-correlation-based application using the LNS instead of a fixed/floating point number system is presented to find the velocity of pneumatic particles flowing through a pipeline.

### **1.2** Research Contributions

The research work in this thesis provides information about the two novel algorithms [10,11] for a Lin2Log converter and an application of cross-correlation using the LNS specifically designed for mapping onto a reconfigurable device. The research work here focuses on the area reduction, usage of minimum hardware and precision achieved when designing a new algorithm or implementing the LNS onto an application. In this thesis reconfigurable devices are chosen for hardware implementation as they can perform parallel computation processing at high frequencies in comparison to microprocessors and microcontrollers.

The thesis presents a novel algorithm [10] to convert a linear (fixed/floating point) number to an equivalent logarithmic number. The proposed algorithm [10] requires less than 20 kbits of ROM and a maximum of three small multipliers. The research shows how a generic error curve is generated in the first stage of the algorithm using max, mean and minimum error curves and then normalised for reproducing in the second stage. The thesis proposes another novel algorithm [11] to reduce the memory elements (in the second stage) used for storing the error curve of the first stage. The memory in the second stage is reduced further by 32% by exploiting the properties of symmetry in the normalised error curve. The algorithm [11] uses additional XOR gates for implementing reduced memory in the second stage.

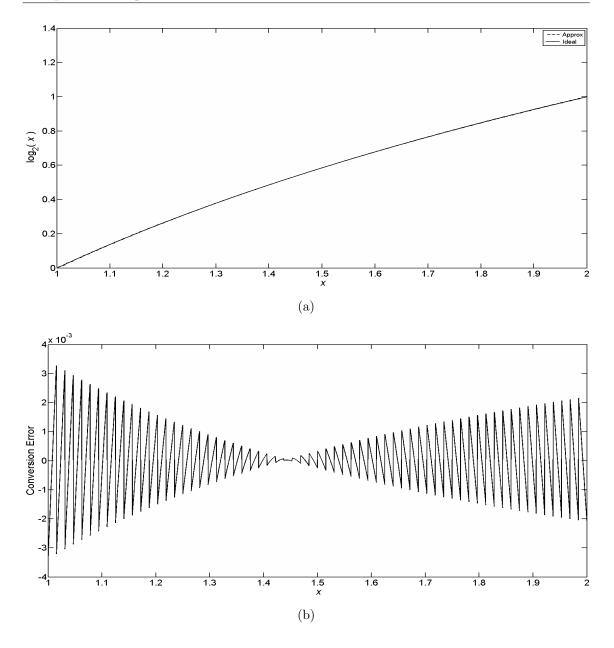

A prototype velocimetry system used for real-time speed measurement of pneumatic particulates flowing through a pipeline using the LNS is presented. The system is developed using incremental cross-correlation in the time domain instead of using FFT (fast fourier transform) techniques in the frequency domain for the calculation of a continuous stream of data from multiple electrostatic sensors located in a pipeline. The system operates at a higher sampling frequency than in previously published work and outputs the new result after every new sample it receives. This thesis provides the results of implementing the circuit on an FPGA device and shows the reduction of bits in fractional bits (used for the linear to logarithmic converter).

The research work presented in this thesis has been submitted to and accepted by IET Computer and Digital Techniques [10] and IEEE Transactions on Circuit and Systems II [11].

### 1.3 Thesis Organisation

All the work presented in this thesis is organised in different chapters. The thesis begins with an overview of FPGA technology in Chapter 2. The generic FPGA architecture and features are compared with other alternative implementation technologies. The number representation using floating point and fixed point number systems are discussed. Published work on the implementation of floating point number systems on FPGA devices, for arithmetic operations is discussed and compared with logarithmic number systems.

Chapter 3 describes in detail the logarithmic number system and provides an overview of algorithms and techniques used for converting Lin2Log and vice versa. The popular algorithms proposed for normalising a binary number, using a leading one or leading zero detector, are explained in section 3.2 and domain conversion algorithms are explained in section 3.3. The algorithms described in Chapter 3 are re-simulated in MATLAB and are plotted with their individual accuracy achieved.

Chapter 4 begins with a description of the Lin2Log conversion algorithm proposed by K.E. Larson in 1994 [12]. The chapter proposes a novel algorithm performing improvements to Larson's algorithm [12]. The proposed novel algorithm is simulated using MATLAB and implemented onto newer and old families of FPGA devices. An analysis of different configurations of data bits, used for addressing and interpolation of the PWL (Piece-wise Linear) approximation and a detailed overview of the resolution of coefficient bits stored in memory to perform PWL approximation is provided in this chapter. The numerical data on precision achieved is compared with recent published papers.

Chapter 5 presents further improvement to the algorithm first proposed in Chapter 4. Chapter 5 describes a further improved algorithm, exploiting symmetrical properties of a normalised error curve. The implementation of a further improved algorithm on an FPGA device, by using dynamic RAM instead of Block RAM, is provided in the chapter. The algorithm is implemented in newer and old families of FPGA devices. An analysis of different configurations of data bits and resolution of coefficient bits stored in memory are provided in this chapter. The chapter compares the results obtained from the further improved algorithm with results obtained from Chapter 4 and recent published papers.

Chapter 6 begins by describing correlation techniques and methods to speed up its computation such as using FFT (Fast Fourier Transform) and incremental correlation algorithms. The recent work used for velocimetry system is described in section 6.3. The velocimetry system implemented on an FPGA device in previous work is presented in section 6.4. A new algorithm for detecting the velocity of pneumatic particles flowing in a pipeline is mentioned in section 6.5. The results obtained from implementing the algorithm on an FPGA device and its utilisation of hardware resources are presented in section 6.7.

A review of all the research presented in this thesis, along with a summary of findings, is presented in Chapter 7 as a conclusion. Directions for further research are also suggested.

## Chapter 2

## FPGA Technology

### 2.1 Introduction

This Chapter contains a brief overview on FPGA (Field Programmable Gate Array) technology. The FPGA is a very flexible and powerful hardware, allowing implementation of large and complex logic designs. The FPGA generally uses a combination of gates and provides dedicated hardware resources to implement a real-time complex application.

The chapter begins with existing DSP system technologies for implementing a digital logic circuit in section 2.2. Section 2.3 starts with a brief history of FPGA technology. An overview on FPGA different programming technologies along with their main vendors are provided in section 2.4. An overview of low-cost families of FPGA devices, are provided in sections 2.4.1, 2.4.2 and 2.4.3. Section 2.5 provides a brief information on programming languages used for designing a digital circuit. Section 2.6 provides a description of a common value representation format implemented on FPGAs and their shortcomings.

### 2.2 DSP system Technologies

For implementing the DSP operations in the hardware a DSP system is required, the discrete signals are easily manipulated in a DSP system. The FPGA, ASIC, DSP, GPU and CPU are the few commonly used technologies for implementing a DSP system in hardware.

ASICs (Application Specific Integrated Circuits) are ICs (integrated circuits) built only for a specific application. ASICs contains predefined/hardwired gates for specific applications because of which they do not offer flexibility of redesigning or reprogramming them. ASICs require a low level logic to design the device. The mask and design cost of ASICs in lower volume are higher than FPGA and DSP devices. However, when ASICs are made in high volume, the cost becomes more economical. It is been proved that for the same level of technology, ASICs are typically three to four times faster than the FPGA devices [13].

ASICs require refabrication if there are any errors found in the design. FPGAs were initially made to avoid the problem of refabrication of ASIC chips. The FPGAs are sea of gates present in hardware. A prototyping of the logic circuits is performed on FPGA. FPGA's reprogrammable feature makes it possible to make changes and run tests in the circuit before the circuit is send for fabrication. FPGA provides the feature of signal processing in parallel rather than sequence because of which multiple operations can be performed at the same time. Unlike ASICs, FPGAs require no layout, masks or other manufacturing steps in designing an integrated circuit. When implementing a system that requires reprogramming, parallel operations and cost effectiveness for lower volume production, FPGA technology is preferred over ASIC technology.

The above mentioned technologies were based on designing hardware circuit performing parallel operations. However, processors (CPU) used for simpler operations in general purpose computers can be used for performing DSP applications. A CPU uses a simple load-store program design. The CPUs have a fixed hardware structure which limits there memory, peripheral structures and connections in hardware. Due to which when performing a DSP application on general purpose processor a slower performance is obtained. To overcome the performance issues, the GPUs and DSPs were introduced. The GPUs are designed to accelerate creation of images for a computer display. A GPU consists of thousands of cores designed for handling multiple tasks simultaneously. The GPUs are designed to perform functions such as texture mapping, image rotation, translation, shading, etc. Modern GPUs are very efficient at manipulating computer graphics and image processing, and their highly parallel structure makes them more effective than general-purpose CPUs for algorithms where the processing of large blocks of visual data is done in parallel.

The DSPs are specialised integrated circuits for processing digital signals. They have better power consumption and are faster than general purpose processors. Fixed and floating point architectures are both present in DSPs. However, for speed efficiency fixed point binary architectures are preferred. The DSP architecture generally contains a program memory, data memory, ALU (arithmetic logic unit) and the input / output ports. The input / output ports connect to analogue signals by using an ADC (analogue to digital converter) and DAC (digital to analogue converter). In the architecture, the data memory stores the data to be processed and the program memory provides the data to ALU. In the ALU, instructions are executed sequentially. An example of fixed point digital signal processor is TMS320C6455. It comes in four packages : TMS320C6455-1000, TMS320C6455-1200, TMS320C6455-720 and TMS320C6455-850, each with 1 GHz, 1.2 GHz, 720 MHz and 850 MHz operating frequency respectively. This DSP comprises eight 32-bit instruction cycles and performs 9600 million instructions per second [14].

### 2.3 FPGA Overview

The FPGA was invented by Ross Freeman in 1984. The basic idea behind FPGA was to have a reprogrammable hardware, on which one or more particular application logic designs can be made. The instructions were executed in parallel on FPGA rather than in sequence, on conventional computers.

In the 1970s, programming logic devices were introduced. These devices were programmed either by fuse or masking logic. In the 1980s, EEPROMs (electrically erasable programmable read only memory) were used to control each programmable connection instead of a fuse. Another alternative method, PAL (programmable array logic), was made by fixing AND gates and making OR gates programmable. The structure resulted in a PROM (programmable read only memory) or LUT (look up table). The problem with PROM was that the circuit size grew exponentially with number of inputs [15]. Larger PROMs, were slower than the dedicated logic, and power consumption was higher, which restricted this technology.

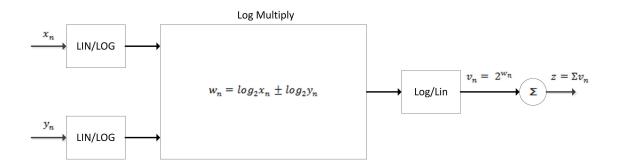

In the mid 1980s programmable logic used several blocks of logic on a single chip to make complex logic functions. This advancement in technology resulted in CPLD (complex programmable logic devices) and FPGA (field programable gate arrays) devices. The CPLDS were based on PAL architecture, making them flash programmable. The FPGAs were based on LUT architecture, where the programme is held in static memory cells, making the configuration of FPGA devices volatile. With the development in technology, interconnection structure and availability of logic resources on FPGA devices increased. This made complex algorithms/architectures implementation easier and on a single device. In an FPGA architecture (shown in figure 2.1), there is a 2-D array layout of identical CLBs (Configurable Logic Blocks), input-output blocks and programmable interconnections.

Figure 2.1: FPGA Architecture.

The input-output blocks connect the internal structure of FPGA to external

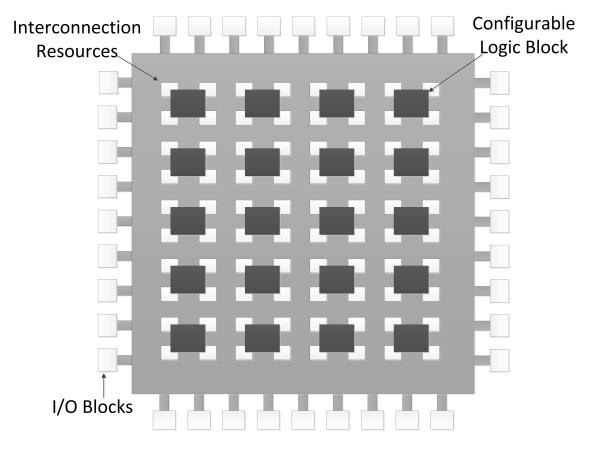

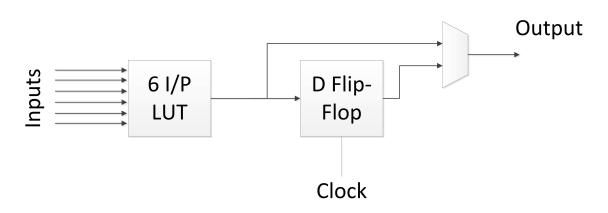

devices. The CLBs are based on a LUT architecture and are interconnected through a programming routing matrix, enabling FPGA to achieve high flexibility in their designs. The CLBs in FPGA are made of 4 input LUT (see figure 2.2) or 6 input LUT (see figure 2.3) in modern FPGA devices, producing a single bit output. The flip-flop attached to the LUT is used to register the output. The complex functions in FPGA are implemented by cascading multiple LUTs.

Figure 2.2: FPGA CLB using 4 input LUT.

Figure 2.3: FPGA CLB using 6 input LUT.

It is not practically possible on the basis of speed and area to provide dedicated connection of every possible output to every possible input of CLBs. The solution of this problem was to have a set of routing lines, which can be shared to create connection between CLBs for a specific application. In an FPGA for grid interconnections a crossbar switch is used to programme connections between horizontal and vertical routing lines. In modern days due to the high input output technology, reconfigurable logic blocks with high flexibility and dedicated hardware resources in FPGAs are being used for implementing complete computer control systems such as the Commodore Amiga 500 in project MiniMig [16]. FPGAs have also been implemented to make a complete computer using linux [17–19].

### 2.4 FPGA Device Types and Families

In the current market, FPGA devices uses anti-fuse, flash and SRAM based programming technology. In the anti-fuse programming technology, the devices are configured by burning a set of fuses. They are one time programmable i.e. once the devices are configured they cannot be altered. Quicklogic is the industrial manufacturer for anti-fuse based FPGA devices. The FPGA devices using the flash programming technology may re-programm the device several thousand times. The devices using flash programming technology are non-volatile i.e. they keep their configuration after the power-off. This technology is expensive and takes several seconds for reconfiguration. The flash based devices are manufactured by the Actel corporation.

The current dominating programming technology for FPGAs is SRAM based technology. It features fast configuration and unlimited times re-programming of the digital circuit. The devices using SRAM programming technology are volatile and may require additional circuitry to load configuration in the device after power is on. Due to the lower system cost, unlimited and fast re-programmable features of programming a device, the FPGA device using SRAM based programming technology is used in this research.

The main vendors for making SRAM based FPGA devices are Xilinx and Altera. The Xilinx, Inc. is an American technology company. It is known for inventing the FPGAs. The Xilinx FPGA product families includes a variety of high performance (Virtex family), mid range (Kintex family) and low cost (Artix / Spartan family) devices. The Altera corporation is also an American manufacturer of FPGA devices. It produces companies high bandwidth devices (stratix series) with 1.1 million logic elements. The Altera corporation also produces low cost and low power FPGA devices known as cyclone series and SoC FPGAs. The Arria series FPGA devices are produced by Altera for balance in power, cost and performance of FPGA devices. The difference between the Altera and Xilinx FPGA devices is of the internal structure. The Xilinx FPGA device uses CLB (complex logic blocks) and Altera FPGA devices uses logic cells. The CLBs are built with LUTs, flip flops and multiplexers whereas the logic cells are made up by multiplexers alone.

There are number of families of FPGA available, offering different levels of complexity in size and logic resources. The research in this thesis requires a lower cost SRAM based FPGA device to re-programm / alter a digital circuit unlimited times. Xilinx Spartan and Altera Cyclone families are both excellent devices featuring the lower cost families of SRAM based FPGA devices. The research in this thesis does not favour any specific family for implementing a digital circuit on FPGA devices. However, due to ease in comparing implementation results with other recent and old published papers, a Xilinx Spartan3 and Spartan6 families are being chosen for implementation of logarithmic converters and logarithmic based correlation applications in this research.

#### 2.4.1 Altera Cyclone Family Overview

The Cyclone SRAM based FPGA family is based on a 1.5V,  $0.13\mu m$ , all-layer copper SRAM process, with densities up to 20,060 logic elements (LEs) and up to 288 kbits of RAM. With features like phaselocked loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements, Cyclone devices are a cost-effective solution for data-path applications. Cyclone devices support various I/O standards, including LVDS at data rates up to 311 megabits per second (Mbps) and 66-MHz, 32-bit peripheral component interconnect (PCI), for interfacing with and supporting ASIC devices. Altera also offers new low-cost serial configuration devices to configure Cyclone devices. A detailed overview of Cyclone family compared to Logic elements, Block RAM, PLLs and I/O pins are shown in table 2.1.

| Device | Logic Elements | Block RAM | Total RAM bits | PLLs | I/O pins |

|--------|----------------|-----------|----------------|------|----------|

| EP1C3  | 2,910          | 13        | 59,904         | 1    | 104      |

| EP1C4  | 4,000          | 17        | 78,336         | 2    | 301      |

| EP1C6  | $5,\!980$      | 20        | 92,160         | 2    | 185      |

| EP1C12 | 12,060         | 52        | 239,616        | 2    | 249      |

| EP1C20 | 20,060         | 64        | 294,912        | 2    | 301      |

Table 2.1: Cyclone FPGA Family Overview [20]

#### 2.4.2 Xilinx Spartan3 Family Overview

The Spartan3 family of FPGA devices was made as a successor of the SpartanIIE family. Spartan3 devices are being widely used for a range of consumer electronic applications because of their low cost on a comparison to the other families of FPGA. The members of this family provide system gates from 50k to 5M (million) in number. The Spartan3 family CLBs are made of RAM based 4 input LUT, shown in figure 2.2. For applications, multipliers used can either be made by using LUT available on the slices of Spartan3 device or by using embedded 18 bit dedicated multipliers. The Spartan3 family provides Block RAM for data storage in the size of 18k bits dual port blocks [21]. A detailed overview of Spartan3 family compared to Logic cells, CLBs, Distribute RAM, Block RAM and Dedicated multipliers are shown in table 2.2.

| Device   | System          | Logic Cells | Total     | Distributed | Block  | Dedicated   |

|----------|-----------------|-------------|-----------|-------------|--------|-------------|

|          | Gates           |             | CLBs      | RAM         | RAM    | Multipliers |

| XC3S50   | 50k             | 1,728       | 192       | 12k         | 72k    | 4           |

| XC3S200  | 200k            | 4,320       | 480       | 30k         | 216k   | 12          |

| XC3S400  | 400k            | 8,064       | 896       | 56k         | 288k   | 16          |

| XC3S1000 | $1\mathrm{M}$   | 17,280      | 1,920     | 120k        | 432k   | 24          |

| XC3S1500 | $1.5\mathrm{M}$ | 29,952      | 3,328     | 208k        | 576k   | 32          |

| XC3S2000 | 2M              | 46,080      | $5,\!120$ | 320k        | 720k   | 40          |

| XC3S4000 | $4\mathrm{M}$   | 62,208      | 6,912     | 432k        | 1,728k | 96          |

| XC3S5000 | $5\mathrm{M}$   | 74,880      | 8,320     | 520k        | 1,872k | 104         |

Table 2.2: Spartan3 FPGA Family Overview [21]

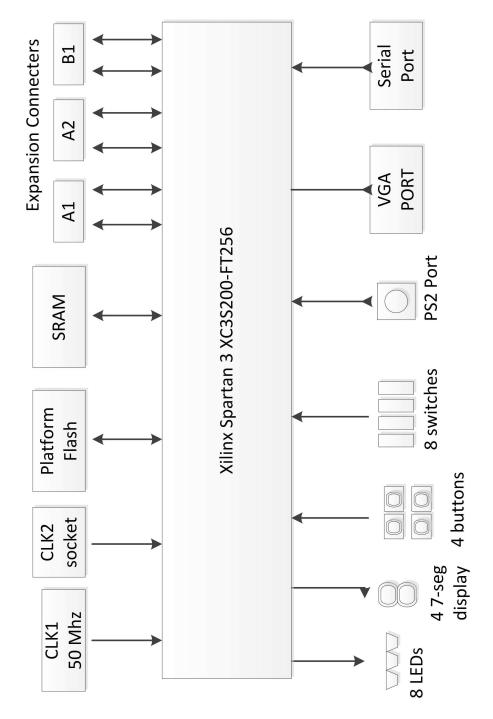

For the purposes of testing in this thesis a Spartan3 Starter Kit board from Digilent Inc. is used. The Starter Kit board [22] provides a 20,000 gate Xilinx Spartan3 XC3S200 device with four digit seven segment LED display, 3-bit 8-colour VGA display port, ps2 port, 9 pin rs232 serial port with slide and push switches (shown in figure 2.4).

Figure 2.4: Spartan 3 Starter Kit Board [22].

#### 2.4.3 Xilinx Spartan6 Family Overview

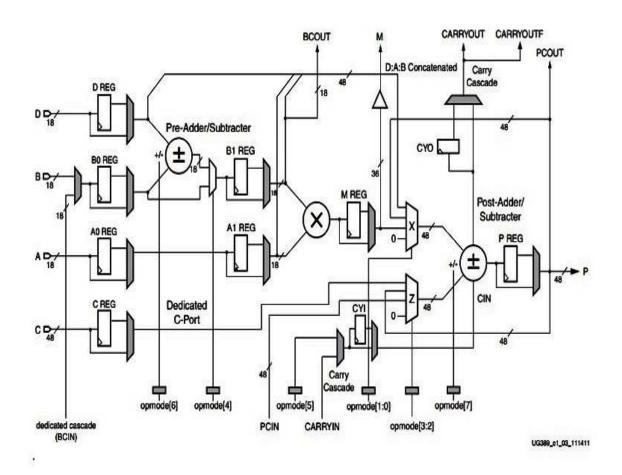

The Spartan6 family consists of 13 members ranging from 3k to 147k logic cells. The Spartan6 device CLBs use dual register 6 input LUT architecture (shown in figure 2.3). The Block RAM available on the device is further reduced to 9k bits blocks in comparison to previous spartan families. Instead of using dedicated 18 bit multipliers, as in the case of previous Spartan3 families, the Spartan6 device uses DSP48A1 slices. DSP48A1 blocks perform operations like multiply, add, multiply add and multiply accumulate, which are essential for DSP applications. The DSP48A1 slice in their architecture consists of two input pre-adder/subtractor, 18 bit two's complement multiplier with a full precision of 36 bit result and two input 48 bit post-adder/subtractor. Figure 2.5 shows a detailed diagram of the DSP48A1 slice [23].

Figure 2.5: DSP48A1 Slice [23].

A detailed overview of the Spartan6 family with a comparison of their Logic cells, CLBs, Distribute RAM, Block RAM and DSP48A1 slices is shown in table 2.3 [24].

| Device     | Logic Cells | CLBs   | Distributed | Block                 | DSP48A1 |

|------------|-------------|--------|-------------|-----------------------|---------|

|            |             | Slices | RAM         | RAM $(18 \text{ kb})$ | Slices  |

| XC6SLX4    | 3,840       | 600    | 75k         | 12                    | 8       |

| XC6SLX9    | 9,152       | 1,430  | 90k         | 32                    | 16      |

| XC6SLX16   | $14,\!579$  | 2,278  | 136k        | 32                    | 32      |

| XC6SLX25   | 24,051      | 3,758  | 229k        | 52                    | 38      |

| XC6SLX45   | 43,661      | 6,822  | 401k        | 116                   | 58      |

| XC6SLX75   | 74,637      | 11,662 | 692k        | 172                   | 132     |

| XC6SLX100  | 101,261     | 15,822 | 976k        | 268                   | 180     |

| XC6SLX150  | 147,443     | 23,038 | $1,\!355k$  | 268                   | 180     |

| XC6SLX25T  | 24,051      | 3,758  | 229k        | 52                    | 38      |

| XC6SLX45T  | 43,661      | 6,822  | 401k        | 116                   | 58      |

| XC6SLX75T  | 74,637      | 11,622 | 692k        | 172                   | 132     |

| XC6SLX100T | 101,261     | 15,822 | 976k        | 268                   | 180     |

| XC6SLX150T | 147,443     | 23,038 | 1,355k      | 268                   | 180     |

Table 2.3: Spartan6 FPGA Family Overview [24]

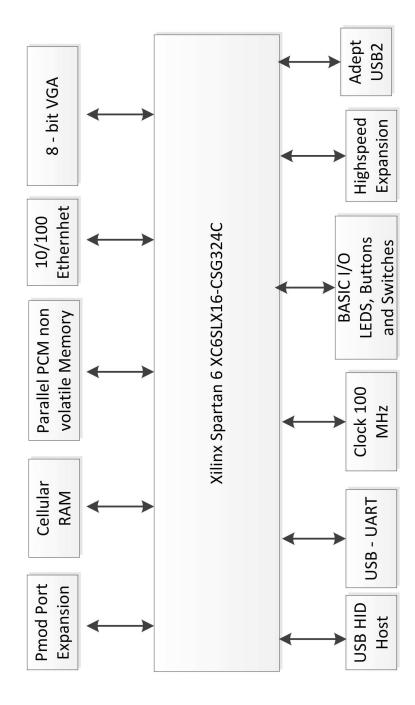

For the testing purposes in this thesis a Nexys3 board from Digilent Inc. is used. The Nexys3 board provides Xilinx Spartan6 XC6SLX16 device with Adept USB2, cellular RAM of 16 Mbyte, parallel PCM nonvolatile of 16Mbyte memory, ethernet port, 8 bit VGA, USB HID Host and UART port, basic input output LEDs, push and switch buttons (shown in figure 2.6).

Figure 2.6: Nexys3 Board [25].

# 2.5 Hardware Description Language

In computer languages, hardware description language is used to program an FPGA device. It describes the behaviour and structural flow of digital logic circuits. The two common form of hardware description languages used in industries are Verilog and VHDL. For the research in this thesis VHDL is used for implementing novel logarithmic converters on FPGAs.

The VHDL stands for very high speed integrated circuit hardware description language. It was first introduced in 1981 by the U.S. department of defence (DoD). The VHDL is used to write and synthesis digital logical circuits. The simulation programs such as Xilinx Vivado and Mentor Graphics ModelSim are used to test the logic design written in VHDL codes. After the successful simulation of digital logic circuits, the circuits are implemented on the hardware FPGA devices by translating synthesis output into a bitstream suited for a specific target device.

The advantage of using VHDL for system design is that it verifies the system through simulation before synthesis tools implements the circuit on hardware. Another benefit of using VHDL over other conventional C, BASIC and assembly languages is that it provides a description of concurrent process rather than sequential process.

# 2.6 Numerical Data Representation on FPGAs

The mathematical operations like addition, subtraction, multiplication and division in hardware uses either fixed point binary number system or floating point binary number system. The fixed point number system is straightforward and does not create any complexity in mathematical operations as numbers of integers and fraction bits are pre-defined.

The floating point on the other hand uses exponent bits and fraction bits covering a large range of numbers with limited precision in comparison to the fixed point number system. There is a trade off between the floating point number system and fixed point number system on the basis of precision achieved and range covered.

The IEEE-754 [9] standard defines binary floating point numbers into single and

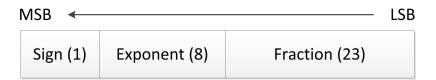

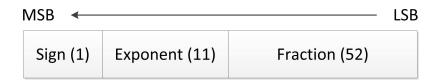

double precision. The single precision uses 32 bits out of which 1 bit is for sign bit, 8 bits for exponent and 23 bits for fractional part (shown in figure 2.7). The double precision (64 bits) in a floating point number are divided as 1 bit for sign bit, 11 bits for exponent and 52 bits for fractional part (shown in figure 2.8).

Figure 2.7: IEEE-754 std Single Precision.

Figure 2.8: IEEE-754 std Double Precision.

The DSP applications are mostly real time based, requiring a large dynamic range. Using the floating point number system on an FPGA hardware has been achieved in [26–29]. However, multiplication and division operations of a floating point number on FPGAs is not trivial as described in [30] and [31]. Multiplication of floating point numbers further requires operations of multiplication of fractional bits and addition of exponent bits. Similarly the division of floating point numbers requires the division of fractional bits and subtraction of exponent bits, making computation slower in comparison to the fixed point number system.

A floating point adder/subtractor algorithm [30] is presented on an FPGA device in order to maximize speed and minimise area. In the algorithm [30] addition and subtraction are performed in three stages. A floating point number is represented as

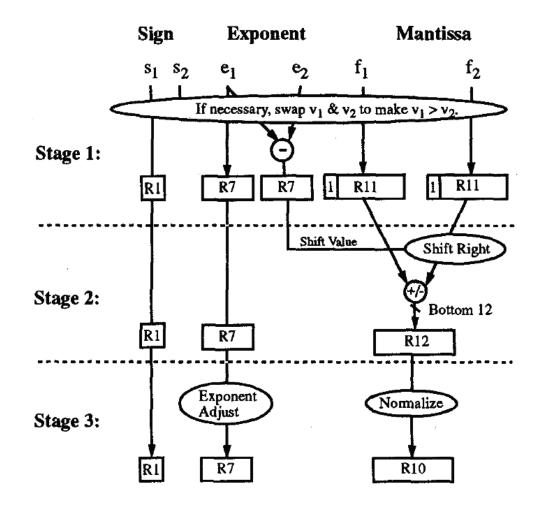

$$v = (-1)^S . 2^E . (1.F) (2.1)$$

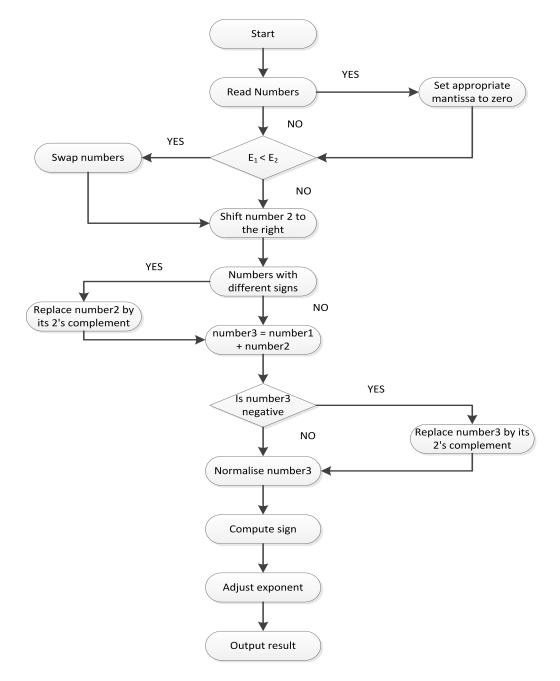

where S, E and F are used to represent sign, exponent and fraction/mantissa fields of the floating point number. Figure 2.9 shows a three-stage 18-bit adder, where addition takes place between  $v_1$  and  $v_2$  floating point numbers. In the first stage, alignment of fraction/mantissa bits is performed by shifting to the right. The number of positions to shift the fraction bit right is decided by subtracting exponent bits. The subtraction of exponent bits is decided by a comparison of absolute values of  $v_1$  and  $v_2$  floating point numbers. The addition/subtraction of fraction bits takes place in the second stage, depending on the sign bit. In stage three, normalisation of the resultant fraction bit is performed, by shifting fraction bits to the left until high order bit is one.

Figure 2.9: Three stage 18-bit floating point adder [30].

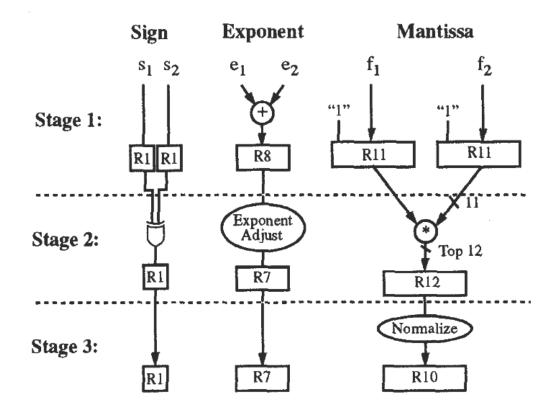

[30] also presents a similar three-stage 18-bit multiplier unit. In stage 1, the addition of exponent bits of floating numbers take place and '1' is concatenated to the left side of fraction bits. The multiplication of two fractional bits is performed in stage 2 by using an integer multiplier. The exponent part of the floating point

number is adjusted depending on the higher bit of the multiplication result. Resultant sign bit is calculated by using a xor gate. Normalisation of the multiplication resultant is performed in stage 3. A three-stage 18-bit floating point multiplier is shown in figure 2.10. The integer multiplier used for fraction bits in multiplication unit suffers the problem of bottleneck. The author uses four different methods to optimise the integer multiplier by using a integer multiplier available in VHDL compiler, array multiplier and by using pipeline in multiplication design to increase the speed of the design.

Figure 2.10: Three stage 18-bit floating point multiplier [30].

In [27], the author describes an addition algorithm of floating point numbers, shown in figure 2.11. The hardware implementation of addition algorithm is shown in figure 2.12. The Initial version of 32-bit adder design took 72% of area on an Altera 81188 device. The author claimed reduction of area by 25% when FLEX 8000 logic elements were used in the circuit. For the multiplication of floating point numbers, the author [27] uses a digit serial multiplier. A digit serial multiplier gives

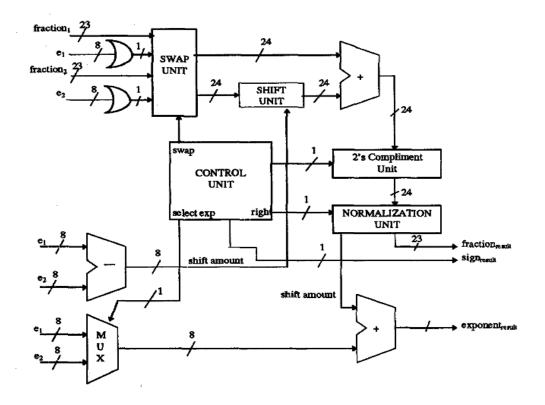

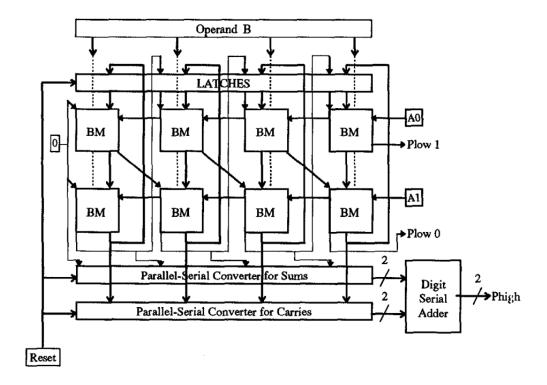

performance in between a bit serial multiplier [32] and a bit parallel multiplier [33]. A digit serial multiplier is implemented on an Altera FLEX 81188 device. Figure 2.13 shows arrays of bit multipliers (BM). In the multiplication, multiplier bits are passed to columns of array and multiplicand bits are passed to rows. The multiplication unit consumes 49% of the Altera flex 81188 device, giving a performance of 2.3 MFlops.

Figure 2.11: Floating point addition algorithm [27].

Figure 2.12: 32 bit floating point adder [27].

Figure 2.13: Digit serial multiplier [27].

Another format of binary number system, LNS (logarithmic number system) not being widely used in hardware, solves the problem of multiplication and division in wide dynamic range [34]. LNS provides a similar range and precision to that of the floating point number system. In 2005, Haselman [31] compared floating point and logarithmic number systems on FPGAs. Tables 2.4 and 2.5 are reproduced from [31], showing a comparison of FPGA hardware (Virtex II 2000) resources used when arithmetic operations of multiplication and division are performed.

Table 2.4: Hardware usage in multiplication of single and double floating point precision [31]

|             | Single FP Precision |     | Double FP Precision |     |

|-------------|---------------------|-----|---------------------|-----|

|             | FP                  | LNS | FP                  | LNS |

| Slices      | 297                 | 20  | 820                 | 36  |

| Multipliers | 4                   | 0   | 9                   | 0   |

| 18k BRAM    | 0                   | 0   | 0                   | 0   |

| Latency(ns) | 65                  | 10  | 83                  | 12  |

Table 2.5: Hardware usage in division of single and double floating point precision

[31]

|             | Single FP Precision |     | Double FP Precision |      |

|-------------|---------------------|-----|---------------------|------|

|             | FP                  | LNS | FP                  | LNS  |

| Slices      | 910                 | 20  | 3376                | 36   |

| Multipliers | 0                   | 0   | 0                   | 0    |

| 18k BRAM    | 0                   | 0   | 0                   | 0    |

| Latency(ns) | 150                 | 10  | 350                 | 12.7 |

#### 2.7 Summary

This chapter has summarised the FPGA technology for designing a digital logic circuit. The FPGAs can implement simple and complex function on a single device. The commonly used functions (adder, multiplier etc.) on modern FPGAs are present in dedicated hardware. The dedicated hardware resources can be combined with other existing logic design on FPGA board.

The number systems for arithemic operations on FPGA devices are discussed and compared. The tables 2.4 and 2.5 shows that multiplication and division linear operations in LNS are very efficient in terms of hardware resources usage in FPGAs. However, before performing the linear operations of multiplication and division, a floating point number must be converted into a logarithmic number and vice versa with the resultant value. The conversion of floating point number to logarithmic number, while maintaining its accuracy the same as single floating point precision is further discussed in Chapters 3, 4 and 5. An example of using a logarithmic number system instead of floating point number in a real time based application is showed in Chapter 6.

# Chapter 3

# Logarithmic Conversion Literature Review

# 3.1 Introduction

This chapter provides an overview of algorithms and techniques used in converting linear to logarithm value with base 2 (Lin2Log) and vice versa (Log2Lin). Logarithmic conversion and logarithmic signal processing have been used in a number of applications and are of increasing interest because of the potential for area and higher resolution architectures [1, 35–37]. As a consequence, many algorithms and hardware architectures have been proposed over the past 50 years for converting a normalised binary number x into a binary logarithm ( $log_2x$ ) or converting the binary exponent ( $2^{log_2x}$ ) back to a normalised binary number. These algorithms vary widely in terms of their accuracy, efficiency and speed. Over such a long time-span there have also been significant changes in the performance of the implementation technologies, resulting in newer architectures capable of achieving increasing conversion accuracies and making the logarithmic number system (LNS) a viable alternative in a number of modern applications [5, 6, 38–43].

As compared to recent algorithms early algorithms have low-precision, limited to 12-bits because of limited technology as integrated digital circuits their have limited memory and/or logic capacities. Recent publications show that algorithms which rely on direct LUT are more accurate, but conversion becomes impractical and large when using for 16-bits or higher because of their LUT size and access time [44]. At this time when higher precision is required curve fitting techniques such as Taylor, CORDIC, Chebyschev etc. are used to approximate the curve, using LUT for their coefficient values. There are algorithms based on curve fitting techniques using first order and second order approximation. Higher order polynomial approximation methods are used in few papers where the precision required is greater than IEEE single-precision floating point format [9].

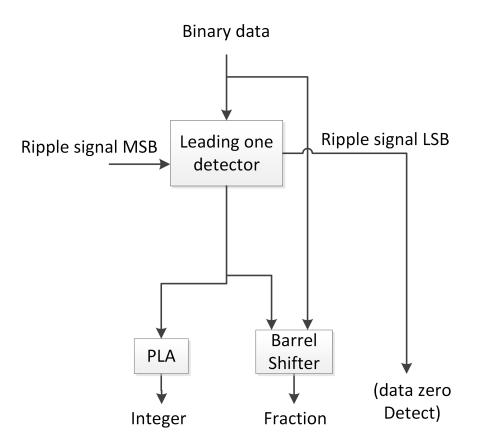

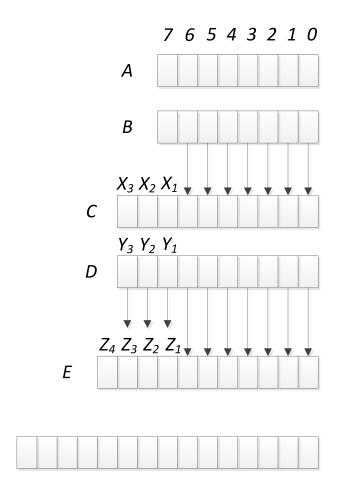

The process of converting a fixed/floating point number into a logarithmic number is divided into two parts. The first part includes calculation of the integer part into a logarithmic characteristic value and the second part calculates the decimal/mantissa part into a logarithmic mantissa/fractional value. The finding of the characteristic/integer value of a logarithmic number from a normalised fixed/floating point number has been reasonably straightforward as there are similarities found in normalised floating point formats and logarithmic formats. In equations 3.1 and 3.2, S denotes the sign bit. The exponent part of the floating point number (E)has the same value as the characteristic value or integer part (I) of the logarithmic value.

Floating Point Format

$$x = (-1)^S . 2^E . (1.M) \tag{3.1}$$

Logarithmic Format

$$x = (-1)^S . 2^I . 2^F (3.2)$$

So the initial step for finding a logarithmic number of a given fixed/floating point number is to normalise the input number. To normalise the input number by using a leading one or leading zero detector is discussed in detail in section 3.2. Once the input number is normalised and the characteristic value of the logarithmic number is obtained, the next step is to perform a Lin2Log conversion on the decimal part (M) of the floating/fixed point number. The different types of algorithms used for converting a normalised floating/fixed point number into a logarithmic number fraction/mantissa (F) are discussed in section 3.3.

## **3.2** Normalisation Methods

The first step in converting a fixed/floating point number to a logarithmic number is to normalise the input number. The normalisation is performed by using leading one detector (LOD) or leading zero detector (LZD) [45–52]. LOD/LZDs are preferred in designing a normalisation circuit as they are trivial to implement in hardware. LOD/LZDs work on simple algorithm of shifting the first one or non zero bit to the left-most bit position. A few popular and recent algorithms for leading one/zero detectors are explained in this section.

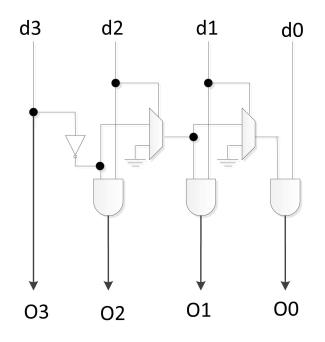

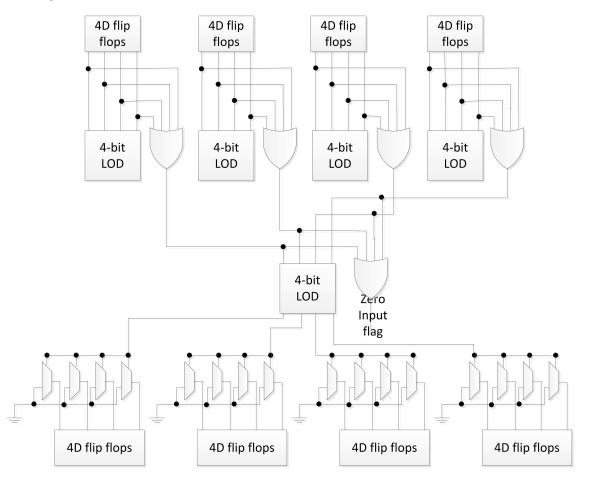

#### 3.2.1 Leading Zero Detector