Amoroso, S. M., Georgiev, V. P., Gerrer, L., Towie, E., Wang, X., Riddet, C., Brown, A. R., and Asenov, A. (2014) Inverse scaling trends for charge-trapping-induced degradation of FinFETs performance. IEEE Transactions on Electron Devices, 61(12), pp. 4014-4018.

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/101340/

Deposited on: 16 February 2016

# Inverse Scaling Trends for Charge-Trapping-Induced Degradation of FinFETs Performance

Salvatore Maria Amoroso, *Member, IEEE*, Vihar P. Georgiev, Louis Gerrer, Ewan Towie, Xingsheng Wang, *Member, IEEE*, Craig Riddet, Andrew Robert Brown, and Asen Asenov, *Fellow, IEEE*

Abstract—In this brief, we investigate the impact of a single discrete charge trapped at the top oxide interface on the performance of scaled nMOS FinFET transistors. The charge-trapping-induced gate voltage shift is simulated as a function of the device scaling and for several regimes of conduction-from subthreshold to ON-state. Contrary to what is expected for planar MOSFETs, we show that the trap impact decreases with scaling down the FinFET size and the applied gate voltage. By comparing drift-diffusion with nonequilibrium Green functions simulations, we show that quantum effects in the charge distribution and transport can reduce or amplify the impact of discrete traps in simulation of reliability resilience of scaled FinFETs.

Index Terms—Charge-trapping, CMOS scaling, FinFET, nonequilibrium Green function (NEGF), quantum transport, reliability.

### I. INTRODUCTION

THE performance improvements of planar bulk MOSFETs has reached saturation at the 20/22-nm CMOS generation, forcing Intel's to shift from planar to trigate architectures to continue on the path of Moore's law. Short channel effects, high leakage current, variability associated with the high channel doping, reliability associated with the high-field effects have been the main driving forces for this technological paradigm shift [1]. While the trigate transistors deliver superior scalability, they also face important challenges, including 3-D process integration, electromigration, electrostatic discharge failure, thermal budget management, layout-dependent effects, and presence of defects along the semiconductor/oxide interface [2]–[4]. In particular, interface traps represent a new and not-negligible source of variability to be addressed in the low-doping realm of FinFET channels and their impact on transistors performance is further aggravated by the generation

Manuscript received July 8, 2014; revised September 4, 2014 and October 9, 2014; accepted October 10, 2014. This work was supported by the European Commission within the FP7 Programme under Grant 261868 through the MORDRED Project. The review of this brief was arranged by Editor E. Rosenbaum.

S. M. Amoroso, V. P. Georgiev, L. Gerrer, and X. Wang are with the Device Modeling Group, School of Engineering, University of Glasgow, Glasgow G12 8QQ, U.K. (e-mail: salvatore.amoroso@glasgow.ac.uk; vihar.georgiev@glasgow.ac.uk; louis.gerrer@glasgow.ac.uk; xingsheng.wang@glasgow.ac.uk).

E. Towie, C. Riddet, A. R. Brown, and A. Asenov are with Gold Standard Simulations Ltd., Glasgow G12 8QQ, U.K., and also with the Device Modeling Group, University of Glasgow, Glasgow G12 8QQ, U.K. (e-mail: ewan.towie@glasgow.ac.uk; craig.riddet@glasgow.ac.uk; a.brown@goldstandardsimulations.com; asen.asenov@glasgow.ac.uk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2014.2363212

of new trap during operation [4]. Understanding the impact of discrete trapped charge in the presence of strongly confined quantum conduction becomes therefore mandatory for unlocking reliability enhancement of FinFET transistors. In this brief, we study the impact of a discrete trapped charge located at the top center of the fin on the transistor performance as a function of the device scaling and for several regimes of conduction-from subthreshold to ON-state. Because of the complex charge distribution in the channel ruled by quantum mechanics, the impact of the oxide trap results to exhibit inverse scaling trends with respect to both fin sizes and applied gate biases.

### II. SIMULATION METHODOLOGY

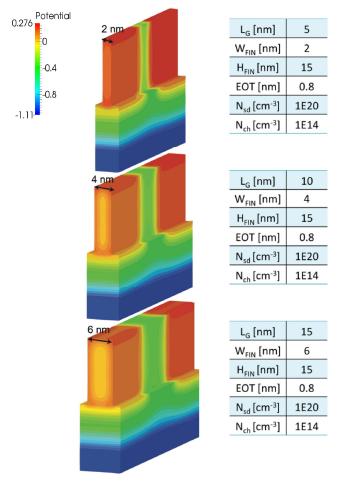

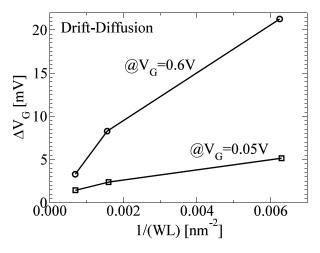

We performed 3-D numerical simulations of FinFETs with features shown in Fig. 1. The ratio between fin width and channel length is keep constant in scaling down the devices to maintain electrostatic integrity. The gate voltage shift  $(\Delta V_G)$ due to a single trapped charge located at the top center of the fin was evaluated from the transistor transfer characteristic in the subthreshold regime ( $V_G = 0.05 \text{ V}$ ) and in the ON-state regime ( $V_G = 0.6 \text{ V}$ ) at low drain biases ( $V_D =$ 0.05 V). Simulations were carried out by means of the driftdiffusion (DD) module (activating density-gradient quantum corrections) and the nonequilibrium Green function (NEGF) module of the GSS atomistic simulator GARAND [5]. A very fine mesh is used in the oxide to resolve the trap impact for the very thin transistors. The NEGF formalism is based on coupled mode space approach [6]. In this case, we assume ballistic transport along the transport direction of the device without any sources of scattering and statistical variability. We consider only four of the six lowest valleys of the Si conduction band as previously done in [6]. The effective masses correspond to their bulk values for (100) crystal orientation in Si: 1)  $m_1 = 0.916m_0$  and 2)  $m_t = 0.19m_0$ . As a caveat, the effective masses do not scale with the device sizes in our simulations. This may be an issue for severe confinement regimes, as shown in [7], and deserve further investigations by means of first-principles simulations. Note that, when referring to the ON-state regime, the DD and the additional contribution of the mobility modulation around the traps is neglected. This contribution can be captured by means of Monte Carlo transport simulations [8] or full-NEGF approaches [6].

# III. RESULTS AND DISCUSSION

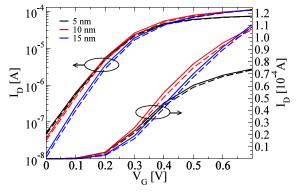

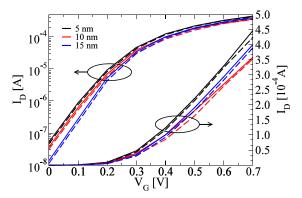

Figs. 2 and 3 show the drain current versus gate voltage  $(I_D-V_G)$  characteristics for the FinFETs described in Fig. 1

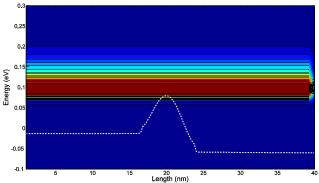

Fig. 1. Electrostatic potential and transistors parameters for the FinFETs studied in this brief. A single discrete trap (empty and neutral state in the picture) is located at the center of the top fin interface.

Fig. 2. DD *I-V* curves for the three FinFET templates in Fig. 1, with (dashed lines) and without (solid lines) trapped charge.

obtained by DD and NEGF simulations, respectively. The ratio between fin width and channel length is kept constant with scaling to retain similar electrostatic integrity. The Equivalent Oxide Thickness is not optimized as in [9], but it is kept constant to avoid additional contribution to the trapping-induced  $\Delta V_G$ . It is worth noting that the curves obtained by NEGF ballistic simulations in Fig. 3 do not show the scattering-related behavior of the DD curves in Fig. 2, where the ON-current decreases with shrinking the fin dimensions due to the perpendicular field dependence

Fig. 3. NEGF I-V curves for the three FinFET templates in Fig. 1, with (dashed lines) and without (solid lines) trapped charge.

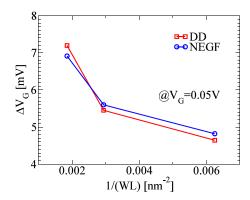

Fig. 4. Gate voltage shift due to a single discrete trapped charge on the top center of the fin as a function of FinFET active area size obtained by DD and NEGF simulations with a reading current criterion in the subthreshold region. Note, here  $W = W_{\rm FIN} + 2 \times H_{\rm FIN}$ .

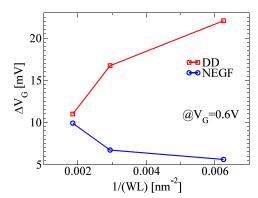

Fig. 5. Gate voltage shift due to a single discrete trapped charge on the top center of the fin as a function of FinFET active area size obtained by DD and NEGF simulations with a reading current criterion in nearly ON-state region.  $W = W_{\text{FIN}} + 2 \times H_{\text{FIN}}$ .

of the mobility. Therefore, to have a consistent comparison between DD and NEGF results in the ON-state region, we have evaluated  $\Delta V_G$  as a function of  $V_G$  (as in [10]) instead of function of the current criterion [11]. Fig. 4 shows the  $\Delta V_G$  obtained in the subthreshold regime, as a function of scaling. Both DD and NEGF simulations show very similar results, with a surprising inverse-scaling behavior. Indeed, the impact of the top-fin located trap increases when we increase the fin size. This behavior is counterintuitive compared with the trends expected for conventional planar MOSFETs [11]. Fig. 5 shows the  $\Delta V_G$  obtained in ON-state regime.

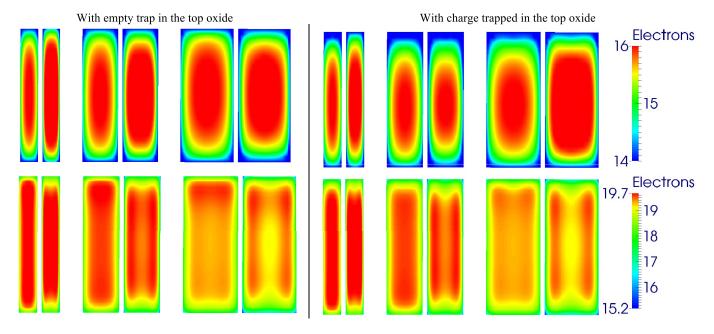

Fig. 6. 2-D cross sections (at the center of the channel) of the simulated electron density at threshold voltage conditions for a current criterion in the subthreshold region (top) and in the ON-state region (bottom). The left(right) of each couple of FinFET cross sections represents DD(NEGF) results. The FinFETs features are summarized in Fig. 1.

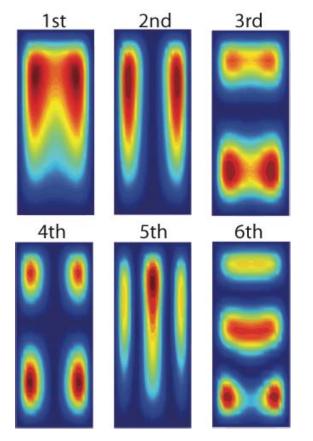

In this case, DD simulations yield results in accordance with the expected scaling trends. However, NEGF simulations result in a lower  $\Delta V_G$ , with a trend similar to the trend in the subthreshold regime. It is very important to note that both DD and NEGF results confirm a positive trend between the  $\Delta V_G$  value and the gate drive voltage  $V_G$ . The  $\Delta V_G$  increases moving from subthreshold to ON-state region, in contrast to what showed by conventional planar MOSFETs [11]. This trend is confirmed for intermediate  $V_G$  values (not shown for brevity). To understand these trends observed in the trigate architecture, we report in Fig. 6 the simulated charge density at  $V_G = 0.05$  V and  $V_G = 0.6$  V. First, it is evident that the channel inversion occurs deeply inside the bulk in the subthreshold regime, while it moves closer to the oxide interface in the ON-state regime: this explains why the trap impact increases with increasing  $V_G$  (common feature to DD and NEGF simulations). Please note that this behavior cannot be observed in a conventional planar MOSFET, where the inversion charge centroid is always close to the oxide interface and barely modulated by the gate voltage conditions. Second, Fig. 6 shows very small differences between DD and NEGF results in the subthreshold regime: this explains the similar  $\Delta V_G$  values shown in Fig. 4 for the two simulations approaches. On the other hand, DD and NEGF charge distributions markedly differ in the ON-state regime: while DD charge moves uniformly toward the fin top interface, the NEGF charge follows a similar trend but maintaining two distinct peaks close to the lateral fin sidewalls. The latter distribution is dictated by the quantum eigenvectors obtained by the Poisson-Schrodinger solution, as shown in Fig. 7, where we report the first six wave functions for the 15-nm FinFET. Given this charge distribution, the electrostatic impact of a trap located on the fin top will be reduced in NEGF simulations with

Fig. 7. First six wave functions in the channel cross section of the FinFET with 15-nm channel length in ON-state regime.

respect to DD ones, as shown in Fig. 5. Please note that NEGF intrinsically considers also the possible charge tunneling in the channel through the potential barrier created by the trap.

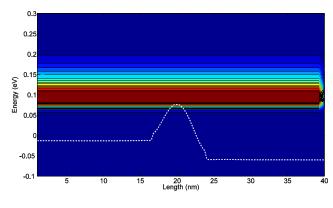

Fig. 8. Energy-position-resolved current spectrum along the 5-nm FinFET without (top) and with (bottom) trap, in ON-state. White dashed lines: first lowest subband.

This impact is, however, negligible in comparison with the large differences in the charge distributions. We have also confirmed the minor importance of tunneling by the plotting in Fig. 8, the current density spectrum obtained from NEGF simulation for the 5-nm FinFET. It is worth noting that NEGF simulations including scattering predict, however, larger contribution of tunneling current component, as shown in [12]. A final insight to the charge distributions in Fig. 6 can help to understand the inverse-scaling behavior of  $\Delta V_G$  observed in Fig. 4. In subthreshold conditions, the charge inversion occurs in the middle of the fin body and is practically controlled by the two lateral gates, especially in the very narrow FinFET (W = 2 nm). The top gate has very low control; therefore, a trap located at its interface will have very low impact on the device drain current. Increasing the FinFET dimensions accordingly to the scaling in Fig. 1, the ratio between the size of the top gate and the lateral gates increases.

As a consequence, the lateral gates lose control on the body charge in favor of a higher control by the top gate. This explains the increasing  $\Delta V_G$  with the larger fin dimensions. In the ON-state, a normal  $\Delta V_G$  scaling behavior is observed for the DD simulations (Fig. 5) as the charge inversion occurs at the channel interface, whereas the NEGF simulations preserve the inverse behavior due to the higher charge inversion at the sidewalls. To corroborate these results, we have repeated DD simulations changing the scaling criterion and keeping the ratio between top gate size and lateral gate size constant, as reported in Table I. In this case, the simulation results in Fig. 9 show a normal  $\Delta V_G$  scaling behavior in

TABLE I FINFETs FEATURES FOR THE SET OF SIMULATIONS IN WHICH THE RATIO BETWEEN FIN HEIGHT (H) AND FIN WIDTH (W) IS KEPT CONSTANT

| L <sub>G</sub> [nm]                 | 5    | 10   | 15   |

|-------------------------------------|------|------|------|

| W <sub>FIN</sub> [nm]               | 2    | 4    | 6    |

| H <sub>FIN</sub> [nm]               | 15   | 30   | 45   |

| EOT [nm]                            | 0.8  | 0.8  | 0.8  |

| N <sub>sd</sub> [cm <sup>-3</sup> ] | 1E20 | 1E20 | 1E20 |

| N <sub>ch</sub> [cm <sup>-3</sup> ] | 1E14 | 1E14 | 1E14 |

Fig. 9. Gate voltage shift due to a single discrete trapped charge on the top center of the fin as a function of FinFET active area size obtained by DD simulations with a reading current criterion in the subthreshold and nearly ON-state regions, for the FinFETs reported in Table I.  $W = W_{\text{FIN}} + 2 \times H_{\text{FIN}}$ .

both subthreshold and ON-state regimes, confirming the above-mentioned explanation.

# IV. CONCLUSION

By means of 3-D DD and NEGF simulations, we have investigated the impact of a single discrete-trapped charge on the performance of scaled nMOS FinFET transistors. The gate voltage shift has been evaluated for several device sizes and for several regimes of conduction-from subthreshold to ON-state.

We have shown that, due to the FinFET volume inversion in subthreshold region, a top-fin located trap can show inverse-scaling behavior compared with what is expected in conventional planar MOSFETs. Moreover, the quantum effects in charge distribution and transport, captured by NEGF simulations, can reduce or amplify the impact of discrete traps on FinFETs drain current.

# REFERENCES

- [1] D. A. Antoniadis and A. Khakifirooz, "MOSFET performance scaling: Limitations and future options," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [2] D. Linten, G. Hellings, S.-H. Chen, and G. Groeseneken, "ESD in FinFET technologies: Past learning and emerging challenges," in *Proc. IRPS*, Apr. 2013, pp. 2B.5.1–2B.5.8.

- [3] H. Kawasaki et al., "Challenges and solutions of FinFET integration in an SRAM cell and a logic circuit for 22 nm node and beyond," in *IEDM Tech. Dig.*, Dec. 2009, pp. 1–4.

- [4] M. Toledano-Luque et al., "Degradation of time dependent variability due to interface state generation," in Proc. Symp. VLSI Technol., Jun. 2013, pp. T190–T191.

- [5] GARAND Version 2014.2. [Online]. Available: http://www.goldstandardsimulations.com

- [6] A. Martinez, M. Aldegunde, N. Seoane, A. R. Brown, J. R. Barker, and A. Asenov, "Quantum-transport study on the impact of channel length and cross sections on variability induced by random discrete dopants in narrow gate-all-around silicon nanowire transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2209–2217, Aug. 2011.

- [7] K. Nehari, N. Cavassilas, J. L. Autran, M. Bescond, D. Munteanu, and M. Lannoo, "Influence of band structure on electron ballistic transport in silicon nanowire MOSFET's: An atomistic study," *Solid-State Electron.*, vol. 50, no. 4, pp. 716–721, Apr. 2006.

- [8] S. M. Amoroso, L. Gerrer, M. Nedjalkov, R. Hussin, C. Alexander, and A. Asenov, "Modeling carrier mobility in nano-MOSFETs in the presence of discrete trapped charges: Accuracy and issues," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp. 1292–1298, May 2014.

- [9] X. Wang, A. R. Brown, B. Cheng, and A. Asenov, "Statistical variability and reliability in nanoscale FinFETs," in *Proc. IEDM*, Dec. 2011, pp. 5.4.1–5.4.4.

- [10] B. Kaczer et al., "The relevance of deeply-scaled FET threshold voltage shifts for operation lifetimes," in *Proc. IRPS*, Apr. 2012, pp. 5A.2.1–5A.2.6.

- [11] S. M. Amoroso *et al.*, "Investigation of the RTN distribution of nanoscale MOS devices from subthreshold to on-state," *IEEE Electron Device Lett.*, vol. 34, no. 5, pp. 683–685, May 2013.

- [12] M. Aldegunde, A. Martinez, and A. Asenov, "Non-equilibrium Green's function analysis of cross section and channel length dependence of phonon scattering and its impact on the performance of Si nanowire field effect transistors," *J. Appl. Phys.*, vol. 110, no. 9, pp. 094518-1–094518-9, 2011.

**Vihar P. Georgiev** received the Ph.D. degree from the University of Oxford, Oxford, U.K., in 2011.

He joined the Device Modelling Group with the School of Engineering, University of Glasgow, Glasgow, in 2011, where he is currently a Post-Doctoral Research Assistant.

**Louis Gerrer** was born in Amiens, France, in 1983. He received the M.Sc. degree in engineering in Strasbourg and the Ph.D. degree from Minatec, Grenoble, France.

He is currently involved in developing a reliability simulator with the Device Modelling Group, University of Glasgow, Glasgow, U.K.

Craig Riddet, photograph and biography not available at the time of publication.

$\boldsymbol{Andrew}\ \boldsymbol{R}.\ \boldsymbol{Brown},$  photograph and biography not available at the time of publication.

**Salvatore Maria Amoroso** (S'10–M'12) received the Ph.D. degree in electronics engineering from the Politecnico di Milano, Milan, Italy, in 2012.

He has been an Associate Researcher with the Department of Electronics, University of Glasgow, Glasgow, U.K., since 2012.

**Asen Asenov** (M'96–SM'05–F'11) received the Ph.D. degree in physics from the Bulgarian Academy of Science, Sofia, Bulgaria, in 1989.

He is currently the James Watt Chair in Electrical engineering with the University of Glasgow, Glasgow, U.K. He is also a Co-Founder, CEO, and the Director of Gold Standard Simulations Ltd., Glasgow.