## Demonstration of the Feasibility of Large Port Count Optical Switching Using a Hybrid MZI-SOA Switch Module in a Recirculating Loop

Q. Cheng<sup>\*</sup>, A. Wonfor, J. L. Wei, R. V. Penty, and I. H. White

Centre for Photonic Systems, Electrical Engineering Division, Department of Engineering, University of Cambridge, 9 JJ Thomson Avenue, Cambridge CB3 0FA, UK \*Corresponding author: <u>gc223@cam.ac.uk</u>

Received Month X, XXXX; revised Month X, XXXX; accepted Month X, XXXX; posted Month X, XXXX (Doc. ID XXXXX); published Month X, XXXX

For the first time, the feasibility of large port count nanosecond reconfiguration time optical switches is demonstrated using a novel hybrid approach, where Mach-Zehnder interferometric (MZI) switches provide low loss high speed routing with short semiconductor optical amplifiers (SOAs) being integrated to enhance extinction. By repeatedly passing signals through a monolithic hybrid dilated  $2\times 2$  switch module in a recirculating loop, the potential performance of high port count switches using the hybrid approach is demonstrated. Experimentally, a single pass switch penalty of only 0.1 dB is demonstrated for the  $2\times 2$  module, while even after 7 passes through the switch, equivalent to a 128x128 router, a penalty of only 2.4dB is recorded at a data rate of 10Gb/s. © 2014 Optical Society of America

OCIS Codes: (130.0250) Optoelectronics, (130.4815) Optical switching devices

In recent years, a surge has occurred in the demand for network traffic due to popular internet applications, such as cloud storage and video downloading. This is causing increased demands on network switching capacity, both in the internet core and also within datacenters [1]. High speed optical switching circuits are regarded as potential key components in next generation high-capacity systems but as port-counts increase, they will rely increasingly on photonic integration, given their predicted complexity, and will also have to demonstrate low latency, low energyconsumption and low cost [2]. As a result, a considerable number of potential integrated optical switch fabrics have been studied [3-12].

Large port count optical switches have been realized based on Micro-electro-mechanical systems (MEMS) [13] and thermo-optic technologies [3, 4] for example. These are low loss but exhibit relatively slow switching times, making them suitable for provisioning and restoration. Research on high speed integrated switches has included integrated MZI circuits [5-8] and SOA gate arrays [9-11]. Recent progress has resulted in up to eight-port MZI switch arrays being fabricated based on carrier-injection broadband switching elements [5-7]. These devices have nanosecond reconfiguration times and so can switch on packet timescales. However, the fabrication variability and design constraints limit the crosstalk of a single MZI element to worse than -20dB when integrated to form large port count routers [5-8]. To overcome this, a dilated scheme has been applied to improve the crosstalk ratio to -30dB at the expense of introducing a larger number of switching elements and greater on-chip loss [8, 9]. Additional attenuators have been introduced at the outputs of the MZIs for increased crosstalk suppression, again resulting in higher loss [9].

In addition to providing nanosecond switching times and broadband operation, SOA-based switches offer gain and high ON/OFF extinction ratios, both of which are important for large port count switches. However, the ultimate size of such a switch is limited by the accumulation of amplified spontaneous emission (ASE) noise and saturation-induced distortion. This limitation can be mitigated through the use of a Clos architecture to optimize the number of cascaded SOAs, thus minimizing ASE, loss and complexity [10]. Using this approach, switches with up to 16 ports have been demonstrated [11, 12]. However, this is unlikely to improve further the scalability, since the broadcast-and-select scheme suffers inherent losses both due to the signal being splitted/combined at various points in the switch and excess losses from optical components. This increases substantially the SOA gain required to compensate for the losses and hence degrades performance.

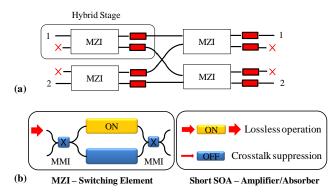

Therefore in our work it has been recognized that a large-scale high speed switch requires high-crosstalk suppression in addition to low loss and low noise figure. A modified MZI-SOA hybrid switch approach has thus been proposed, in which the high extinction ratio and gain of SOAs complement the main advantages of the MZI switches [14]. A schematic of the 2×2 switch block is shown in Fig. 1(a). Here the short SOAs are switched in tandem with the MZIs to pass wanted signals and strongly absorb leakage signals [Fig. 1(b)]; hence enabling both improved crosstalk and mitigated loss. Detailed physical layer simulations have been done to investigate the viability of large-scale optical switches using the hybrid approach and to compare it with conventional SOA switches in terms of power-efficiency and optical performance [14]. Recently, a monolithically integrated 2×2 MZI-SOA hybrid switch module has been fabricated with up to -40 dB extinction/crosstalk ratio, 3 ns switching time (10-90%) and moderate on-chip loss of 3 dB (under 14 mA bias to the SOAs) [15]. The switch penalties are significantly lower than those obtained from conventional all-SOA architectures.

The performance of up to 8×8 port count hybrid switch has previously been investigated by using three cascades of 2×2 switching building blocks with shuffle network losses [15]. However, it is not feasible to emulate larger size hybrid switches using this approach because of the number of devices required [14]. A different approach is therefore required to evaluate the performance of larger port count switches. In this letter therefore, for the first time, we evaluate the cascaded performance of the  $2 \times 2$ hybrid switch module in a re-circulating loop to assess the likely performance of switches with up to 128×128 port count. In this letter, we for the first time evaluate the cascaded performance of the 2×2 hybrid switch module in a recirculating loop to assess the likely performance of switches with up to 128×128 port count. The detailed BER performance of various switch sizes is presented, demonstrating the feasibility of building such large port count devices based on the hybrid MZI-SOA approach.

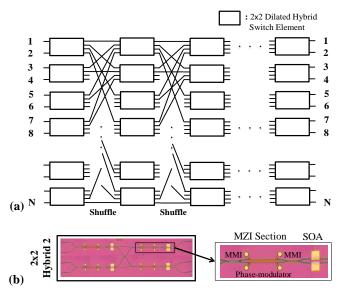

The 2×2 hybrid switch module is constructed, in a 2 mm × 6 mm photonic integrated circuit (PIC) with fixed 500  $\mu$ m spaced input/output ports, using a combination of pre-defined elements, such as SOA sections, electro-optic phase modulators, MMI couplers and waveguides to enable reliable design and fabrication [16]. The 2×2 module comprises four MZI elements with 800  $\mu$ m long phase modulators, as shown in the photograph in Fig. 2(b). Two 170  $\mu$ m long SOA gates are introduced at the outputs of each MZI. The passive waveguides are formed using deep-etched straight waveguides, S-bends, and perpendicular waveguide crossings. Transition elements are used between the shallow-etched SOAs and the other deep-etched structures.

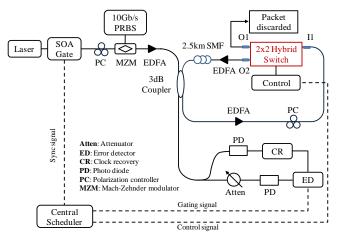

Using this hybrid MZI-SOA 2×2 switch building block, large port count hybrid switches can be constructed using a dilated Benes architecture, as indicated in Fig. 2(a). An N×N size hybrid switch fabric requires log<sub>2</sub>N cascades of the 2×2 switch module to offer rearrangeablely nonblocking connections [14]. A recirculating loop is therefore built to emulate large-scale hybrid switches and a schematic of it along with its control plane is presented in Fig. 3. A Stanford Research Systems delay generator is used as a central scheduler, primarily for conditioning gating signals to the error detector for loop-dependent BER measurement and also for generating switch control signals. Synchronized electrical sources are used to drive the SOAs and phase-modulators separately without using matched impedances. A tunable laser is operated at a wavelength of 1546.7 nm. The laser output is gated by a commercial CIP SOA device, generating periodic packets for use in the recirculating loop experiment. 10Gb/s NRZ data is imposed on the optical signal by a Mach-Zehnder modulator. A 3dB coupler is used to load and monitor the loop.

The loop is constructed from a coupler, the switch, optical amplifiers and 2.5 km of single mode fibre (SMF). It is chosen to be long enough to contain a 12 µs long packet comprising repeated 10 Gb/s pseudo-random data with a  $2^{15}$ -1 pattern length (limited by the packet period). When the switch is configured in the cross state, packets are recirculated from input port I1 to output port O2 and the loop is emptied by directing the discarded packets to output port O1 (as shown in Fig. 3). One packet circulates

around the loop zero up to eight times, equivalent to backto-back and a  $2\times2$ ,  $4\times4$ ,  $8\times8$ ,  $16\times16$ ,  $32\times32$ ,  $64\times64$ ,  $128\times128$  and  $256\times256$  port count switches, respectively. The overall loop sequence is repeated periodically every  $125 \,\mu$ s, each circulation taking 100  $\mu$ s followed by a 25  $\mu$ s period while the loop is emptied. The unamplified contents of the loop are monitored by a dc-coupled lightwave converter (HP11982A), which is not a burst mode receiver and which therefore does lead to compromised detection.

In order to emulate the performance of a large-scale hybrid switch and ensure there is sufficient optical power after several loops, the coupling loss of each facet of the switch block (8 dB) has to be compensated. A booster EDFA is therefore placed in the loop before the switch to enable a reasonable on-chip input power (0 dBm), while a post EDFA is placed at the output end, providing enough gain for compensating excess losses of the loop. It is worth noting that no filter is placed either within the loop or at the receiver. Slight degradation in performance is indeed observed with a 1 nm bandwidth optical filter due to the reduced power margin. The hybrid switch is biased using a current of 20 mA and voltage of -3.7 V for each of the SOAs and phase-modulators, to enable a modest on-chip loss of less than 1.5 dB. This operating condition also enables a static optical signal to noise ratio (OSNR) of up to 42 dB in a 0.1 nm bandwidth, the noise contribution being dominated by the post EDFA whose OSNR is 38 dB in a 0.1 nm bandwidth, causing a 4 dB OSNR penalty.

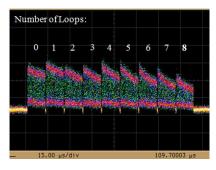

A temporal trace for packets undergoing 0-8 loops is shown in Fig. 4, where a 0.5 µs guard band is followed by each payload. It can be seen that in addition to ASE noise the looped packets suffer from saturation induced distortion of the EDFAs due to the high optical input power required for high OSNR.

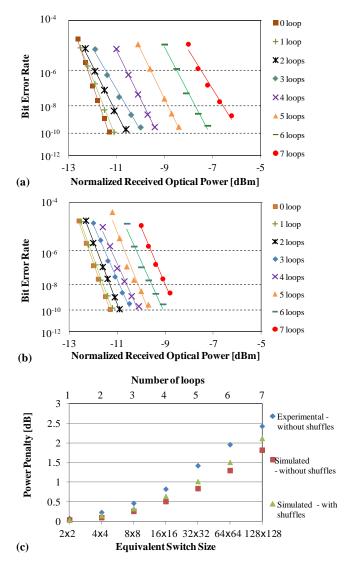

A loop-number dependent BER measurement is performed by sweeping the gating signal from the first packet to the 9<sup>th</sup>, allowing assessment for switch sizes up to 256×256. The detailed BER measurement is presented in Fig. 5(a) as a function of normalized received optical power. It can be seen that for up to 7 loops, which is equivalent to a 128×128 port switch, the signal is errorfree (<10<sup>-9</sup>), with a power penalty at BER of 10<sup>-9</sup> of 0.2 dB for 1 circulation and 5.1 dB after 7 circulations. However, much of the overall signal degradation can be attributed to the EDFAs, the switch equipment, fibre chromatic dispersion and the non-ideal burst mode receiver. The system performance without the switch is therefore subsequently assessed so as to reveal the switch subsystem penalties. A passive modulator is used to replace the switch and a variable optical attenuator is attached in order that the loop power budget remains unchanged. Results for the loop penalty with the switch thus bypassed are presented in Fig. 5(b), where up to 2.7 dB penalty is observed for the 7<sup>th</sup> looped packet. The switch sub-system performance equivalent to the different port counts is therefore estimated by subtracting the bypass switch penalties, and is shown in Fig. 5(c). Penalties of 0.1 dB, 0.2 dB, 0.5 dB, 0.8 dB, 1.4 dB, 1.9 dB and 2.4 dB, are observed for equivalent port sizes for 2×2, 4×4, 8×8, 16×16, 32×32, 64×64 and 128×128 respectively.

This excellent performance can be attributed to the nature of the hybrid design. Broadcast-and-select SOA arrays lose half their optical power at each waveguide junction and thus longer SOA gates or a larger number of cascades are required to build large-scale optical switches, inevitably inducing significant signal impairments. MZI switching elements avoid these inherent optical losses, and thus shorter overall SOA lengths can be used, this enabling a significant improvement in noise performance. As stated above, in addition to providing extinction enhancement, the distributed short SOAs enable low-loss performance within each 2×2 building block, avoiding the loss penalties which would otherwise accumulate.

However, it should be noted that the shuffle network losses have not been included in this work when considering the recirculating operation. Fully integrated shuffle networks may require hundreds of waveguide crossings and straight sections. Nevertheless, studies have shown that in InP materials, each waveguide crossing contributes a loss of the order of 0.01 dB while less than 1 dB/cm propagation loss can be achieved for the straight waveguides [17]. In the hybrid design, the longest path of the shuffle network in a 128×128 size switch consists of up to 160 waveguide crossings and 50 mm long passive waveguides, resulting in about 9 dB excess loss. Since the rearrangeablely non-blocking switch can always optimize routes among different connections, we consider the path from the first input port to the last output port as a representative case, where each of the six shuffle stages only imposes 1.5 dB loss. The low excess interstage losses could readily therefore be compensated by small increases in the length of the SOA components. Simulations using the validated PICwave physical layer simulator are subsequently performed to reveal the impact of shuffle networks on the switch overall performance. The results are included in Figure 5(c). It can be seen that increased SOA lengths (up to 230µm), for full-size switches, do lead to signal degradation but excellent performance is still achieved, with 128×128 port switch simulations exhibiting a power penalty of 2.1 dB. For emulated switches, experimental trends agree well with the simulated penalties to within 0.6 dB, with the additional power penalties observed in this experiment arising from beat noise between the switches and EDFAs.

Future larger switches will not be limited by the current constraints of the multi project wafer design rules, thus benefiting from a more compact design, and therefore lossless performance can be expected. A large-scale hybrid switch can readily be built from identical 2×2 building blocks, reducing the complexity of design and fabrication. Other techniques could be used to further reduce signal degradation such as multi-wavelength coding [18] and constant-intensity modulation formatting [19] to suppress cross gain modulation. Control systems previously reported are also expected to minimize additional system penalties [20]. On this basis therefore, it can be concluded that the hybrid approach provides enhanced performance at large port counts.

In conclusion, for the first time this letter demonstrates the feasibility of building large-scale optical switches by using a novel hybrid MZI-SOA design approach. Cascaded performance of a fabricated 2×2 hybrid switch module has been assessed in a re-circulating loop. Penalties of only 2.4 dB are observed for recycling of the signal 7 times through a 2×2 switch module, equivalent to a 128×128 port count router.

The research leading to these results has received funding from the UK EPSRC through the INTERNET, STAR and COPOS II grants and the switch module was fabricated by Oclaro under the European Commission under FP7 grant agreement ICT 257210 PARADIGM.

## References

- [1] R. Tucker, IEEE J. Sel. Top. Quantum Electron. **17**, 261, (2011).

- [2] I. O'Connor, in Proc. Int. Workshop Syst. Level Interconnect Prediction, 79, (2004).

- [3] S. Sohma, T. Watanabe, N. Ooba, M. Itoh, T. Shibata, and H. Takahashi, 2006 European Conference on Optical Communications, 1, (2006).

- [4] F. L. W. Rabbering, J. F. P. van Nunen, and L. Eldada, in Proceedings of ECOC (2001), Vol. 27, paper PD-78.

- [5] B. Lee and A. Rylyakov, in Optical Fiber Communication Conference (2013), paper PDP5C.3.

- [6] A.V. Rylyakov, C.L. Schow, B.G. Lee, W. M J Green, S. Assefa, F.E. Doany, M. Yang, J. Van Campenhout, Christopher V. Jahnes, J.A. Kash, and Y.A. Vlasov, IEEE J. Solid-State Circuits, 47, 345, (2012).

- [7] H. Kouketsu, S. Kawasaki, N. Koyama, Y. Matsushima, and K. Utaka, Optical Fiber Communication Conference (2014), paper M2K.3.

- [8] J. J. Xing, Z. Li, Y. D. Yu, and J. Z. Yu, Opt. Lett., 38, 4774, (2013).

- [9] D. H. P. Maat, Y. C. Zhu, F. H. Groen, H. Van Brug, H. J. Frankena, and X. J. M. Leijtens, IEEE Photon. Technol. Lett. 12, 284 (2000).

- [10] I. White, E. T. Aw, K. Williams, H. Wang, A. Wonfor, and R. Penty, J. Opt. Netw., 8, 215, (2009).

- [11] A. Wonfor, H. Wang, R. V. Penty, and I. H. White, J. Opt. Commun. Netw., 3, A32 (2011).

- [12] R. Stabile, A. Albores-Mejia, and K. A. Williams, Opt. Lett. 37, 4666 (2012).

- [13] V. Aksyuk and S. Arney, IEEE Photon. Technol. Lett., 15, 587, (2003).

- [14] Q. Cheng, A. Wonfor, R. V. Penty, and I. H. White, J. Lightwave Technol. 31, 3077 (2013).

- [15] Q. Cheng, A. Wonfor, J. L. Wei, R. V. Penty, and I. H. White, Opt. Lett., **39**, 1449, (2014).

- [16] M. K. Smit, X. Leijtens, E. Bente, J. Van der Tol, H. Ambrosius, D. Robbins, M. J. Wale, N. Grote, and M. Schell, in Optic Fiber Communication Conference (2012), paper OM3E.3.

- [17] H. Bukkems and C. Herben, IEEE Photon. Technol. Lett., **11**, 1420, (1999).

- [18] G. Roberts, R. V. Penty, I. H. White, A. West, and S. Moore, in The 18th Annual Meeting of the IEEE Lasers and Electro-Optics Society (IEEE, 2005), pp. 739–740.

- [19] P. S. Cho and J. B. Khurgin, IEEE Photon. Technol. Lett. 15, 162, (2003).

- [20] I. H. White, K. A. Williams, R. V. Penty, T. Lin, A. Wonfor, E. T. Aw, M. Glick, M. Dales, and D. McAuley, J. Opt. Netw. 6, 180, (2007).

Fig. 1: (a) Schematic of a hybrid dilated 2×2 switch. (b) Operating principle of a hybrid MZI-SOA switch element.

Fig. 2: (a) Schematic of the large-scale hybrid switch in building block approach. (b) Photograph of the fabricated  $2\times 2$  hybrid switch.

Fig. 3: Schematic of the control plane for re-circulating loop experiment.

Fig. 4: Temporal trace for packets undergoing increasing passes though the 2x2 switch.

Fig. 5: (a) BER measurement as a function of normalized received optical power with the presence of the switch. (b) BER measurement as a function of normalized received optical power by pass the switch. (c) Experimental and simulated sub-system power penalties of different port count switches. Simulated results of switches with shuffles are also included.

## REFERENCES

- R. Tucker, "Green optical communications—Part II: Energy limitations in networks," IEEE J. Sel. Top. Quantum Electron., VOL. 17, NO. 2, pp. 261–274, 2011.

- [2] I. O'Connor, "Optical solutions for system-level interconnect," in Proc. Int. Workshop Syst. Level Interconnect Prediction, 2004, pp. 79–88.

- [3] S. Sohma, T. Watanabe, N. Ooba, M. Itoh, T. Shibata, and H. Takahashi, "Silica-based PLC Type 32 x 32 Optical Matrix Switch," 2006 European Conference on Optical Communications, pp. 1–2, Sep. 2006.

- [4] F. L. W. Rabbering, J. F. P. van Nunen, and L. Eldada, "Polymeric 16x16 Digital Optical Switch Matrix", in Proceedings of ECOC (2001), Vol. 27, paper PD-78.

- [5] B. Lee and A. Rylyakov, "Four-and eight-port photonic switches monolithically integrated with digital CMOS logic and driver circuits," presented at the Opt. Fiber Commun. Conf. Expo. Nat. Fiber Opt. Eng. Conf., Anaheim, CA, USA, 2013, Paper PDP5C.3.

- [6] A.V. Rylyakov, C.L. Schow, B.G. Lee, W. M J Green, S. Assefa, F.E. Doany, M. Yang, J. Van Campenhout, Christopher V. Jahnes, J.A. Kash, and Y.A. Vlasov, "Silicon Photonic Switches Hybrid-Integrated With CMOS Drivers," Solid-State Circuits, IEEE Journal of, vol.47, no.1, pp.345-354, Jan. 2012

- [7] H. Kouketsu, S. Kawasaki, N. Koyama, Y. Matsushima, and K. Utaka, "High-speed and Compact Non-blocking 8×8 InAlGaAs/InAlAs Mach-Zehnder-Type Optical Switch Fabric", presented at the Opt. Fiber Commun. Conf., San Francisco, CA, USA, 2014, Paper M2K.3.

- [8] J. J. Xing, Z. Li, Y. D. Yu, and J. Z. Yu, "Low cross-talk 2 × 2 silicon electro-optic switch matrix with a doublegate configuration", Opt. Lett., Vol. 38, pp. 4774-4776, (2013).

- [9] D. H. P. Maat, Y. C. Zhu, F. H. Groen, H. Van Brug, H. J. Frankena, and X. J. M. Leijtens, "Polarizationindependent dilated InP-based space switch with low crosstalk," IEEE Photon. Technol. Lett., vol. 12, no. 3, pp. 284–286, Mar. 2000.

- [10] I. White, E. T. Aw, K. Williams, H. Wang, A. Wonfor, and R. Penty, "Scalable optical switches for computing applications [Invited]," J. Opt. Netw., vol. 8, no. 2, pp. 215–224, Jan. 2009.

- [11] A. Wonfor, H. Wang, R. V. Penty, and I. H. White, "Large Port Count High-Speed Optical Switch Fabric for Use Within Datacenters [Invited]," J. Opt. Commun. Netw., vol. 3, no. 8, p. A32, Jul. 2011.

- [12] R. Stabile, A. Albores-Mejia, and K. A. Williams, "Monolithic active-passive 16 × 16 optoelectronic switch", Opt. Lett. 37, pp. 4666-4668, 2012.

- [13] V. Aksyuk and S. Arney, "238×238 micromechanical optical cross connect," IEEE Photon. Technol. Lett., vol. 15, no. 4, pp. 587–589, Apr. 2003.

- [14] Q. Cheng, A. Wonfor, R. V. Penty, and I. H. White, "Scalable, Low-Energy Hybrid Photonic Space Switch", J. Lightwave Technol. Vol. 31, pp. 3077-3084, 2013.

- [15] Q. Cheng, A. Wonfor, J. L. Wei, R. V. Penty, and I. H. White, "Monolithic MZI-SOA hybrid switch for lowpower and low-penalty operation", Optics Letters, Vol. 39, pp. 1449-1452, 2014.

- [16] M. K. Smit, X. Leijtens, E. Bente, J. Van der Tol, H. Ambrosius, D. Robbins, M. J. Wale, N. Grote, and M.

Schell, "A generic foundry model for InP-based photonic ICs," presented at the Opt. Fiber Commun. Conf., Los Angeles, CA, USA, 2012, Paper OM3E.3.

- [17] H. Bukkems and C. Herben, "Minimization of the loss of intersecting waveguides in InP-based photonic integrated circuits," IEEE Photon. Technol. Lett., vol. 11, no. 11, pp. 1420–1422, Nov. 1999.

- [18] G. Roberts, R. V. Penty, I. H. White, A. West, and S. Moore, "Multi-wavelength data encoding for improved input power dynamic range in semiconductor optical amplifier switches," in The 18th Annual Meeting of the IEEE Lasers and Electro-Optics Society (IEEE, 2005), pp. 739–740.

- [19] P. S. Cho and J. B. Khurgin, "Suppression of crossgain modulation in SOA using RZ-DPSK modulation format," IEEE Photon. Technol. Lett., Vol. 15, pp. 162– 164, 2003.

- [20] I. H. White, K. A. Williams, R. V. Penty, T. Lin, A. Wonfor, E. T. Aw, M. Glick, M. Dales, and D. McAuley, "Control architecture for high capacity multistage photonic switch circuits," J. Opt. Netw. 6, pp. 180–188, 2007.