# Device and Circuit-level Models for Carbon Nanotube and Graphene Nanoribbon Transistors

Michael Loong Peng Tan Queens' College University of Cambridge

A dissertation submitted for the degree of Doctor of Philosophy January 2011

# Declaration

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except where specifically indicated in the text. This thesis has not been submitted in whole or in part as consideration for any other degree or qualification at the University of Cambridge or any other University or similar institution. In compliance with regulations, this thesis does not exceed 65,000 words, and contains 109 figures.

Michael Loong Peng Tan January 2011 To my wonderful parents and sister, for their guidance, support, love and enthusiasm. I would not have made it this far without your motivation and dedication to my success. Thank you, Mama and Daddy, I love you both.

## Acknowledgement

First of all, I am thankful to my supervisor, Prof. Gehan Amaratunga for his valuable insight, guidance, advice and time. I would like to take this opportunity to record my sincere gratitude for his supports and dedication throughout the years.

My thankfulness also goes to Prof. Vijay K. Arora, my mentor from Wilkes University. His immense support and encouragement gave me the strength to go forward. I wish to express my heartfelt thanks to Prof. Razali Ismail for the advice and supports.

I could not complete my study without the help and discussions with Chin Shin Liang, Desmond Chek, David Chuah and Caston Urayai. Their contributions in quantum physics and circuit simulation in the aspect of this dissertation are greatly appreciated. I would also like to acknowledge John Norcott for his computing assistance.

Also, thank you to my friends namely Tee Boon Tuan, Chong Cheng Tung and Javier Wong and Lim Kian Min. I cherish the ideas they have given me, their supports and warmhearted friendships.

I would also like to thank Malaysia Ministry of Higher Education and Universiti Teknologi Malaysia for the award of advanced study fellowship.

On a personal note, I would like to thank my family who has always supported me and the encouragement they have given me.

# List of Publications

Michael L. P. Tan and Gehan A. J. Amaratunga, "Performance Prediction of Graphene-Nanoribbon and Carbon Nanotube Transistor", Eleventh International Conference on the Science and Application of Nanotubes, (NT10), 27 June – 2 July 2010, Montreal, Quebec, Canada.

Michael L. P. Tan and Gehan A. J. Amaratunga, "Performance Prediction of Graphene-Nanoribbon and Carbon Nanotube Transistor", *Proceedings of the IEEE on International Conference on Enabling Science and Nanotechnology*, (Nanotech Malaysia 2010), 1-3 December 2010, KLCC, Malaysia.

### Abstract

### Device and Circuit-level Models for Carbon Nanotube and Graphene Nanoribbon Transistors

Michael Loong Peng Tan

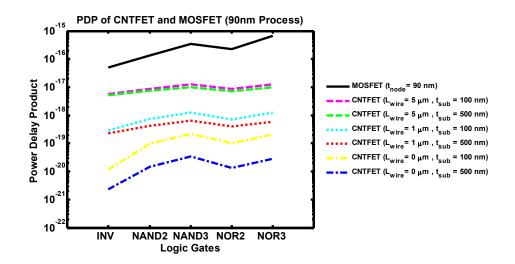

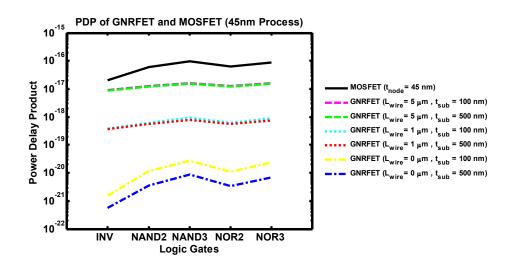

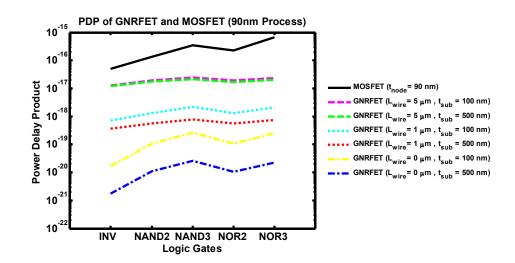

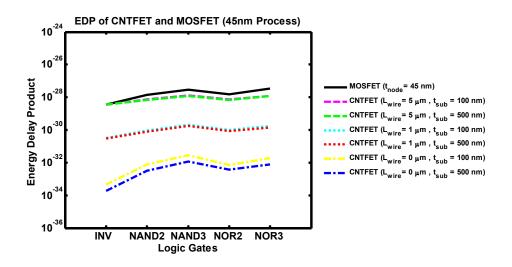

Metal-oxide semiconductor field-effect transistor (MOSFET) scaling throughout the years has enabled us to pack million of MOS transistors on a single chip to keep in pace with Moore's Law. After forty years of advances in integrated circuit (IC) technology, the scaling of silicon (Si) MOSFET has entered the nanometer dimension with the introduction of 90 nm high volume manufacturing in 2004. The latest technological advancement has led to a low power, high-density and high-speed generation of processor. Nevertheless, the scaling of the Si MOSFET below 22 nm may soon meet its' fundamental physical limitations. This threshold makes the possible use of novel devices and structures such as carbon nanotube field-effect transistors (CNTFETs) and graphene nanoribbon field-effect transistors (GNRFETs) for future nanoelectronics. The investigation explores the potential of these amazing carbon structures that exceed MOSFET capabilities in term of speed, scalability and power consumption. The research findings demonstrate the potential integration of carbon based technology into existing ICs. In particular, a simulation program with integrated circuit emphasis (SPICE) model for CNTFET and GNRFET in digital logic applications is presented. The device performance of these circuit models and their design layout are then compared to 45 nm and 90 nm MOSFET for benchmarking. It is revealed through the investigation that CNT and GNR channels can overcome the limitations imposed by Si channel length scaling and associated short channel effects while consuming smaller channel area at higher current density.

# Contents

# 1 Introduction

| 1.1 | Background          | 1 |

|-----|---------------------|---|

| 1.2 | Problem Statements  | 3 |

| 1.3 | Objectives          | 4 |

| 1.4 | Contributions       | 4 |

| 1.5 | Thesis Organization | 5 |

| 1.6 | References          | 7 |

### 2 Overview of Carbon and Silicon-Based Technology

| 2.1 | Carbon Nanotubes                         |    |  |  |  |

|-----|------------------------------------------|----|--|--|--|

|     | 2.1.1 Energy-Momentum Relation           | 12 |  |  |  |

|     | 2.1.2 Bandstructure of a Zigzag Nanotube | 13 |  |  |  |

|     | 2.1.3 Schottky Barrier CNTFET            | 14 |  |  |  |

|     | 2.1.4 Synthesis                          | 17 |  |  |  |

| 2.2 | Graphene                                 | 18 |  |  |  |

|     | 2.2.1 Synthesis                          | 22 |  |  |  |

| 2.3 | Carbon-based Nanoelectronics             | 23 |  |  |  |

| 2.4 | Current Transport Models                 | 24 |  |  |  |

| 2.5 | Device Modeling                          | 28 |  |  |  |

| 2.6 | Conclusion                               | 33 |  |  |  |

| 2.7 | References                               | 35 |  |  |  |

#### 3 Device Model

| 3.1  | Introduction                            | 44 |

|------|-----------------------------------------|----|

| 3.2  | Modeling Approaches                     | 45 |

| 3.3  | Low Dimensional Structure Modeling      | 46 |

| 3.4  | Electrostatic Capacitance               | 54 |

| 3.5  | Quantum Capacitance                     | 55 |

| 3.6  | Channel, Quantum and Contact Resistance | 57 |

| 3.7  | Source and Drain Resistance             | 59 |

| 3.8  | Energy Dispersion in GNR and CNT        | 60 |

| 3.9  | Model Verification                      | 63 |

| 3.10 | MATLAB Implementation                   | 66 |

| 3.11 | Analog Behavior Modeling in PSPICE      | 69 |

| 3.12 | Comparison with MOSFET model            | 73 |

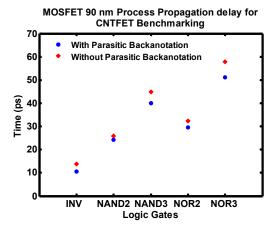

| 3.13 | RC and Propagation Delay                | 75 |

| 3.14 | Conclusion                              | 82 |

| 3.15 | References                              | 83 |

#### 4 Performance Prediction of the CNTFET and the GNRFET

| 4.1 | Introduction             | 87  |

|-----|--------------------------|-----|

| 4.2 | Performance Metric       | 88  |

| 4.3 | Performance Benchmarking | 94  |

| 4.4 | Conclusion               | 108 |

| 4.5 | References               | 110 |

### 5 Layout and Circuit Analysis

| 5.1 | Introd | uction             |         |       |        |        |        | <br>111 |

|-----|--------|--------------------|---------|-------|--------|--------|--------|---------|

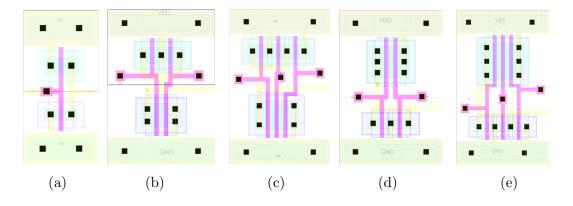

| 5.2 | Gener  | ic $45 \text{ nm}$ | PDK     |       |        |        |        | <br>112 |

|     | 5.2.1  | MOSFE              | T Layou | t for | CNTFET | Benchm | arking | <br>113 |

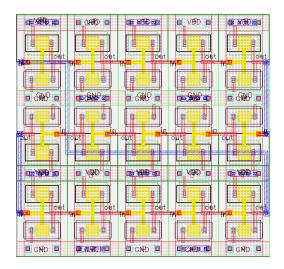

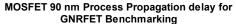

|     | 5.2.2  | MOSFE              | T Layou | t for | GNRFET | Benchm | arking | <br>115 |

#### Contents

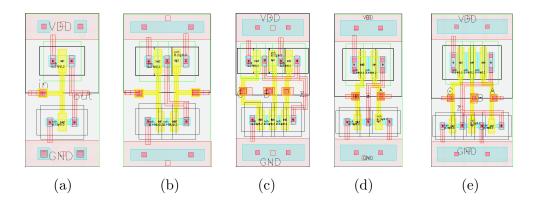

| 5.3 | Generic 90 nm PDK                           |     |  |  |  |

|-----|---------------------------------------------|-----|--|--|--|

|     | 5.3.1 MOSFET Layout for CNTFET Benchmarking | 118 |  |  |  |

|     | 5.3.2 MOSFET Layout for GNRFET Benchmarking | 120 |  |  |  |

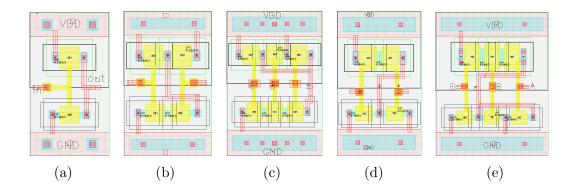

| 5.4 | Digital Logic Circuit for CNTFET and GNRFET | 122 |  |  |  |

| 5.5 | Conclusion                                  | 138 |  |  |  |

| 5.6 | References                                  | 139 |  |  |  |

#### 6 Conclusions and Future Work

| 6.1 | Summary     | <br>140 |

|-----|-------------|---------|

| 6.2 | Future Work | <br>142 |

| 6.3 | References  | <br>145 |

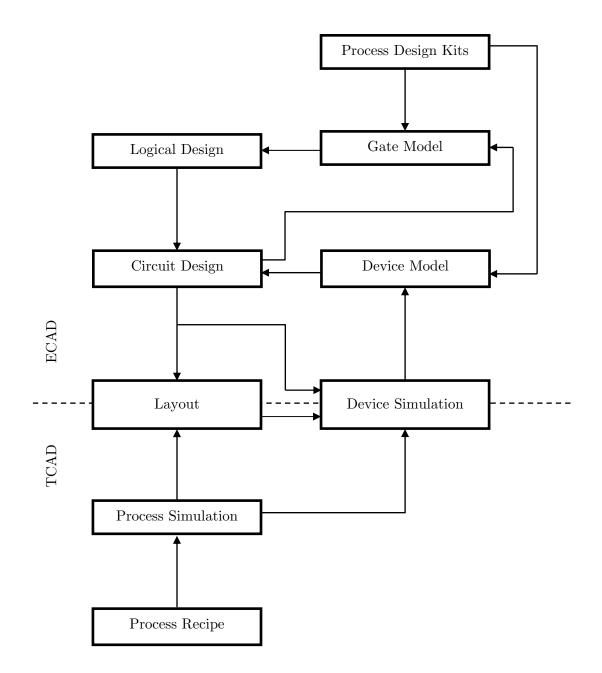

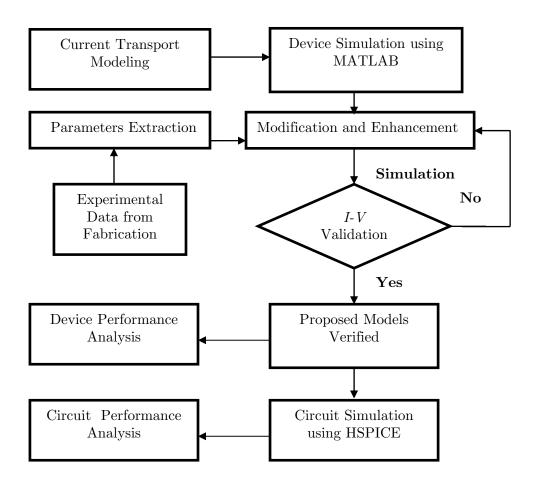

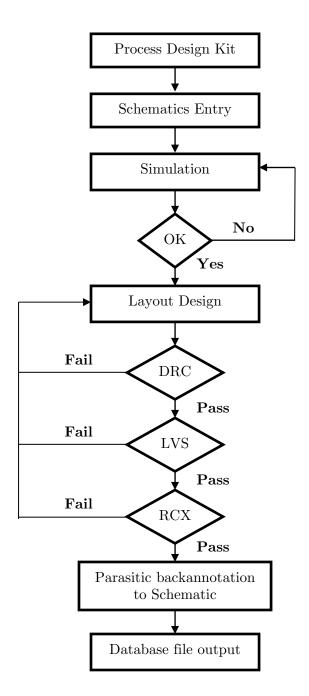

### Appendix A Research Methodology

| A.1 | Introd  | luction1      |  |     |  |  |  |

|-----|---------|---------------|--|-----|--|--|--|

| A.2 | Electri | ical Modeling |  | 148 |  |  |  |

|     | A.2.1   | MATLAB        |  | 150 |  |  |  |

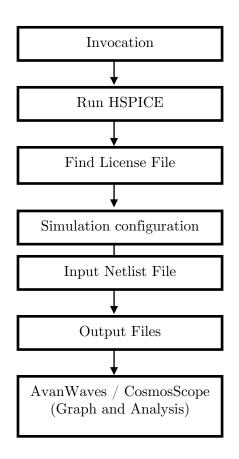

|     | A.2.2   | HSPICE        |  | 151 |  |  |  |

|     | A.2.3   | PSPICE        |  | 153 |  |  |  |

|     | A.2.4   | CADENCE       |  | 154 |  |  |  |

| A.3 | Conclu  | usion         |  | 157 |  |  |  |

| A.4 | Refere  | nces          |  | 158 |  |  |  |

#### Appendix B Low Dimensional Modeling

| B.1 | Quasi- | Quasi-Two Dimensional Model              |     |  |  |  |  |

|-----|--------|------------------------------------------|-----|--|--|--|--|

|     | B.1.1  | Density of States for Q2D Structure      | 161 |  |  |  |  |

|     | B.1.2  | Electron Concentration for Q2D Structure | 161 |  |  |  |  |

|     | B.1.3  | Instrinsic Velocity for Q2D Structure    | 162 |  |  |  |  |

## Contents

| B.2 | Quasi-One Dimensional Model |                                          |     |  |  |  |

|-----|-----------------------------|------------------------------------------|-----|--|--|--|

|     | B.2.1                       | Density of States for Q1D Structure      | 163 |  |  |  |

|     | B.2.2                       | Electron Concentration for Q1D Structure | 164 |  |  |  |

|     | B.2.3                       | Instrinsic Velocity for Q1D Structure    | 165 |  |  |  |

| B.3 | Summ                        | ary of Relative Formulas                 | 166 |  |  |  |

| B.4 | Gamm                        | a Function                               | 167 |  |  |  |

# List of Abbreviations

| ABM    | - | Analog Behaviour Model                  |

|--------|---|-----------------------------------------|

| ALD    | - | Atomic Layer Deposition                 |

| AMS    | - | Analog Mixed Signal                     |

| BSIM   | - | Berkeley Short-Channel IGFET Model      |

| CAD    | - | Computer Aided Design                   |

| CDF    | - | Component Description Format            |

| CMC    | - | Compact Modeling Council                |

| CMOS   | - | Complementary Metal-Oxide-Semiconductor |

| CNTFET | - | Carbon Nanotube Field-Effect Transistor |

| DC     | - | Direct Current                          |

| DG     | - | Double Gate                             |

| DIBL   | - | Drain-Induced Barrier Lowering          |

| DOS    | - | Density of States                       |

| DRC    | - | Design Rules Check                      |

| ECAD   | - | Electronic Computer-Aided Design        |

| EDA    | - | Electronic Design Automation            |

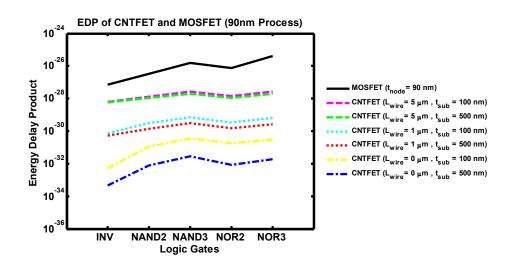

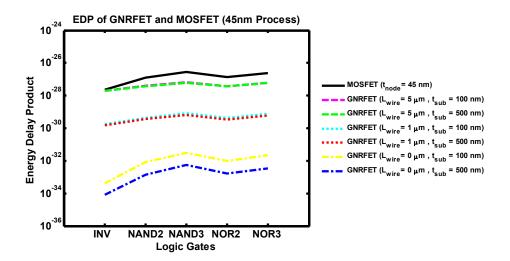

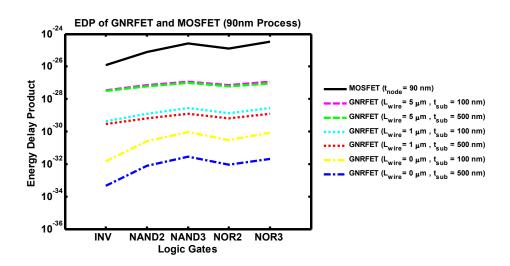

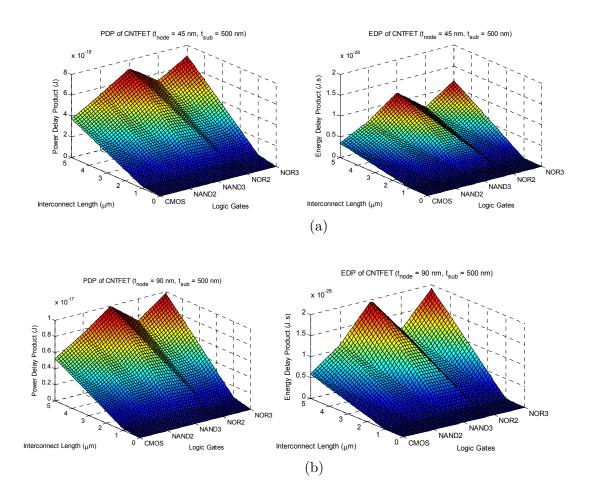

| EDP    | - | Energy Delay Product                    |

| FDSOI  | - | Fully-Depleted Silicon on Insulator     |

| FET    | - | Field Effect Transistor                 |

| GaAr   | - | Galium Arsenide                         |

| GCA    | - | Gradual Channel Approximation           |

| GDSII  | - | Graphic Database System II              |

| GHz    | - | Giga Hertz                              |

|        |   |                                         |

| GNR                 | - | Graphene Nanoribbon Field-Effect Transistor         |

|---------------------|---|-----------------------------------------------------|

| GUI                 | - | Graphical User Interface                            |

| IBM                 | - | International Business Machines                     |

| IC                  | - | Integrated Circuit                                  |

| IGFET               | - | Insulated Gate Field-Effect Transistor              |

| InP                 | - | Indium Phosphide                                    |

| LVS                 | - | Layout versus Schematic                             |

| MFP                 | - | Mean Free Path                                      |

| MMSIM               | - | Multi-mode Simulation                               |

| MOS                 | - | Metal Oxide Semiconductor                           |

| MOSFET              | - | Metal Oxide Semiconductor Field Effect Transistor   |

| NEGF                | - | Non-equilibrium Green's Function                    |

| NMOS                | - | n-channel MOSFET                                    |

| OA                  | - | Open Access                                         |

| PDP                 | - | Power-delay product                                 |

| PDK                 | - | Process Design Kit                                  |

| PMOS                | - | p-channel MOSFET                                    |

| Q1D                 | - | Quasi-one dimensional                               |

| Q2D                 | - | Quasi-two dimensional                               |

| RC                  | - | Resistive-Capacitive                                |

| RCX                 | - | Parasitic Extraction                                |

| RF                  | - | Radio Frequency                                     |

| S/D                 | - | Source and Drain                                    |

| Si                  | - | Silicon                                             |

| Si2                 | - | Silicon Integration Initiative                      |

| SiGe                | - | Silicon Germanium                                   |

| SOE                 | - | Second Order Effects                                |

| $\operatorname{SP}$ | - | Surface Potential based Models                      |

| SPE                 | - | Surface Potential Equation                          |

| SPICE               | - | Simulation Program with Integrated Circuit Emphasis |

| $\mathbf{SS}$       | - | Subthreshold Swing                                  |

| TCAD | - | Technology Computer-Aided Design           |

|------|---|--------------------------------------------|

| TSMC | - | Taiwan Semiconductor Manufacturing Company |

| UTB  | - | Ultra-thin Body                            |

| VLSI | - | Very Large Scale Device                    |

| VSR  | - | Velocity Saturation Region                 |

| VHDL | - | Very High Density Logic                    |

| 2DEG | - | 2D Electron Gas                            |

# List of Figures

| 2.1  | Buckyball C60                                                   | 9  |

|------|-----------------------------------------------------------------|----|

| 2.2  | Multi-walled carbon nanotube                                    | 9  |

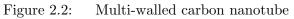

| 2.3  | Single-walled carbon nanotube                                   | 9  |

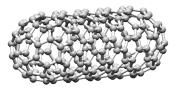

| 2.4  | Map of chiral vectors (n, m) of carbon nanotube                 | 10 |

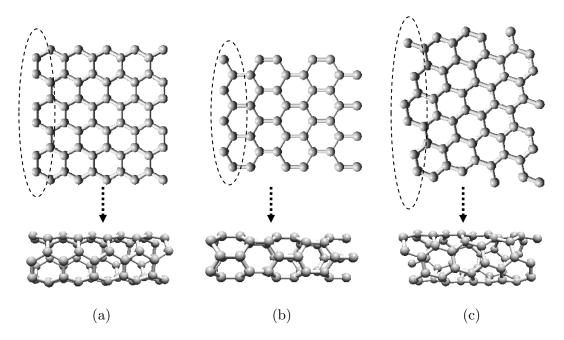

| 2.5  | The creation of (a) (3,3) armchair nanotube                     | 11 |

|      | (b) $(4, 0)$ zigzag nanotube (c) $(4,2)$ chiral nanotube        |    |

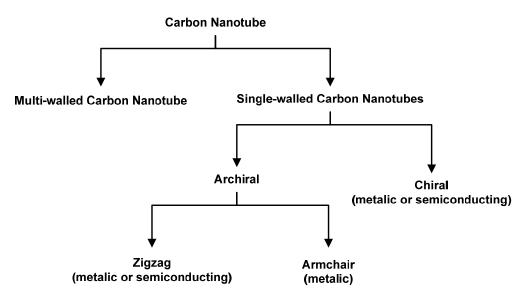

| 2.6  | Classification of nanotubes                                     | 11 |

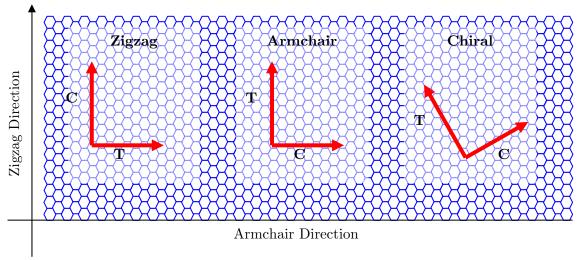

| 2.7  | Formation of nanotubes. $T$ is the translational vector $\dots$ | 12 |

| 2.8  | A zigzag nanotube with quantized $\mathbf{k}_{\mathbf{y}}$      | 13 |

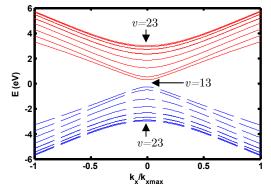

| 2.9  | Energy dispersion of (20,0) zigzag nanotube                     | 13 |

|      | with n=20, subband index $v$ from 13 to 23                      |    |

|      | and quantized $k_y$                                             |    |

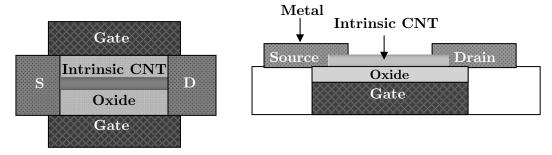

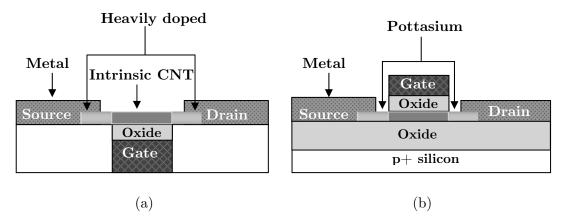

| 2.10 | Schottky barrier CNTFETs                                        | 15 |

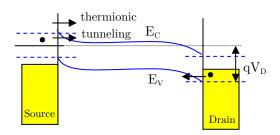

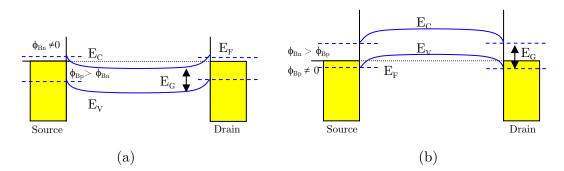

| 2.11 | Schottky barrier CNTFET with ambipolar transport                | 15 |

| 2.12 | Sketch of a full band ohmically contacted SWNT                  | 16 |

|      | FETs for (a) electron and (b) hole transport                    |    |

| 2.13 | MOSFET-like CNTFET with chemically doped                        | 16 |

|      | contacts for (a) bottom and (b) top gate design                 |    |

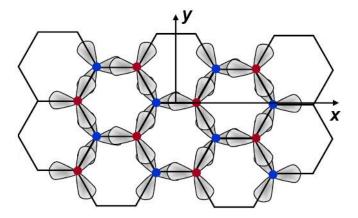

| 2.14 | ${ m sp}^2$ hybridization                                       | 18 |

| 2.15 | $2p_z$ orbitals                                                 | 19 |

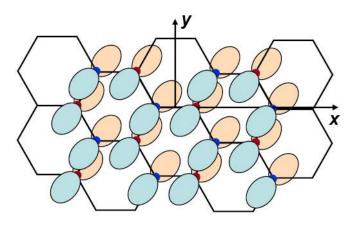

| 2.16 | (a) Energy bands near the Fermi level in                             | 20 |

|------|----------------------------------------------------------------------|----|

|      | graphene. (b) Brillouin zone of the honeycomb                        |    |

|      | lattice. A closer look at the (c) metallic and                       |    |

|      | (d) semiconducting conic structure                                   |    |

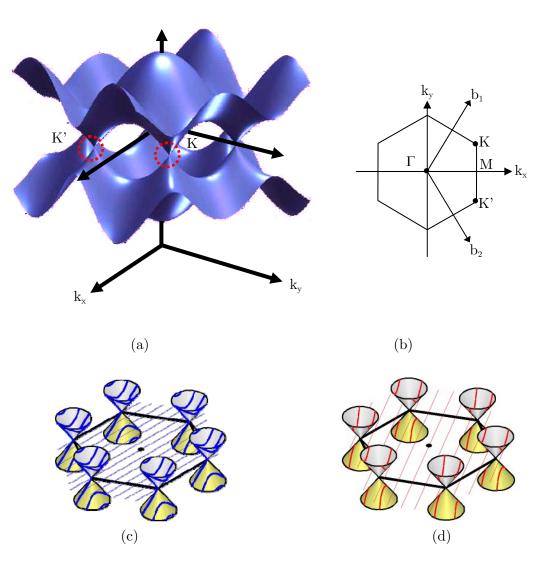

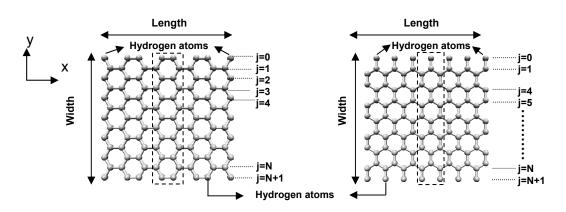

| 2.17 | Honeycomb lattice of an armchair and a                               | 21 |

|      | zigzag graphene nanoribbon                                           |    |

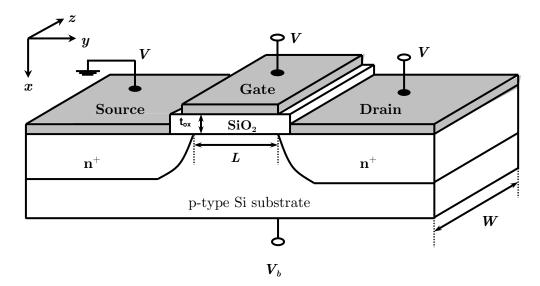

| 2.18 | Basic structure of a n-channel MOSFET                                | 25 |

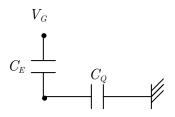

| 2.19 | Circuit representation of electrostatic and                          | 27 |

|      | quantum capacitance in series                                        |    |

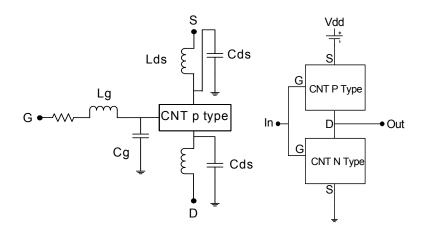

| 2.20 | Circuit model of CNT complementary circuits                          | 30 |

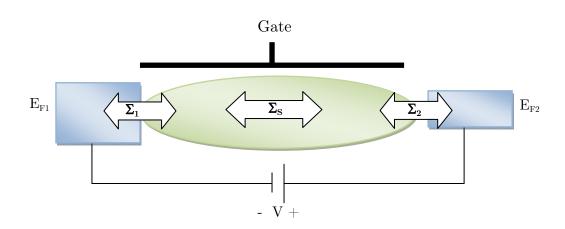

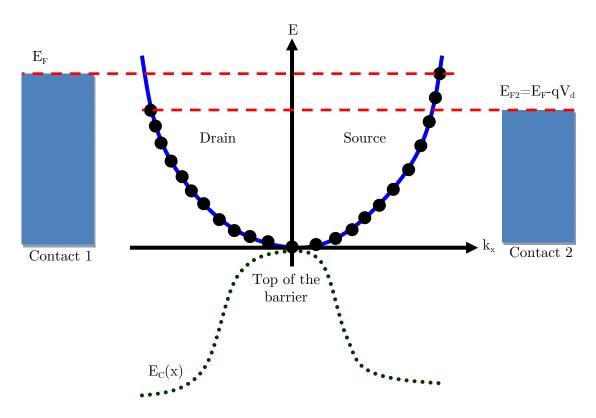

| 3.1  | General matrix model for nanoscale device                            | 46 |

|      | connected to two contacts                                            |    |

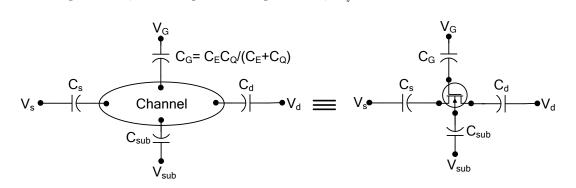

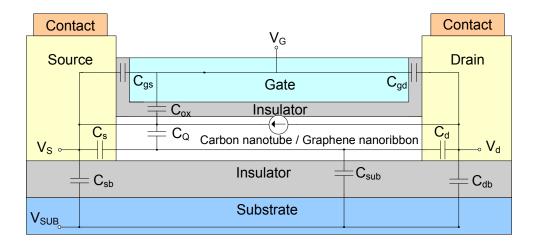

| 3.2  | Transistor circuit model with parasitic capacitance                  | 46 |

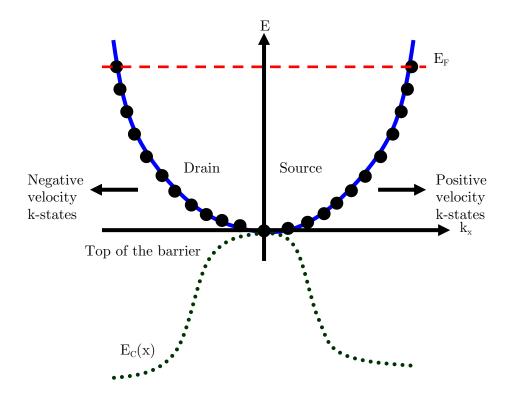

| 3.3  | Population of k-states at equilibrium at the top of                  | 47 |

|      | the barrier                                                          |    |

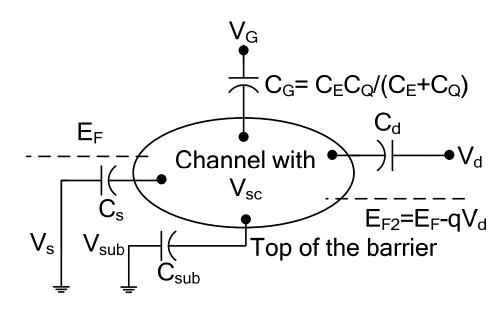

| 3.4  | A generic electrostatic capacitance model for                        | 49 |

|      | ballistic transistor                                                 |    |

| 3.5  | Population of k-states at non-equilibrium at the top                 | 50 |

|      | of the barrier                                                       |    |

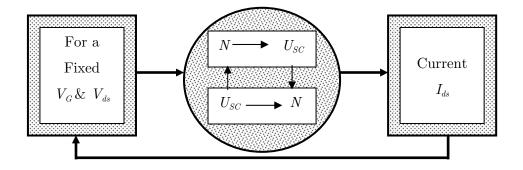

| 3.6  | Self consistent solution for $U_{SC}$ and carrier density $N$        | 53 |

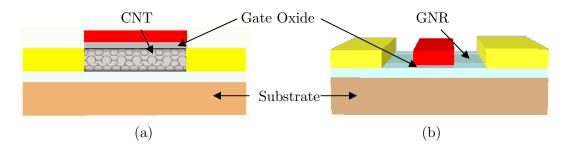

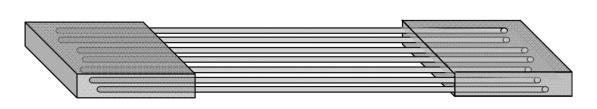

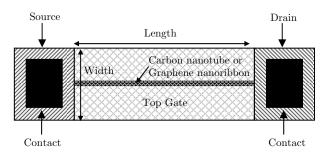

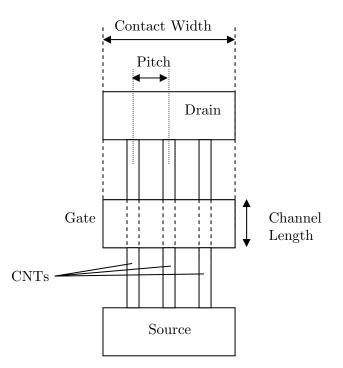

| 3.7  | Structure of a (a) carbon nanotube and (b)                           | 54 |

|      | graphene nanoribbon field effect transistor                          |    |

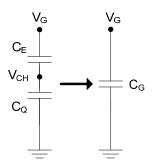

| 3.8  | $eq:Metal-Insulator-Semiconductor capacitors (electrostatic,  \dots$ | 55 |

|      | quantum, gate capacitance) with channel and gate voltage             |    |

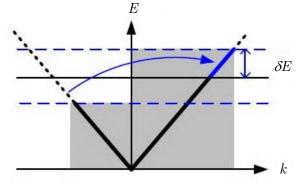

| 3.9  | Energy versus wavevector for a Q1D device                            | 56 |

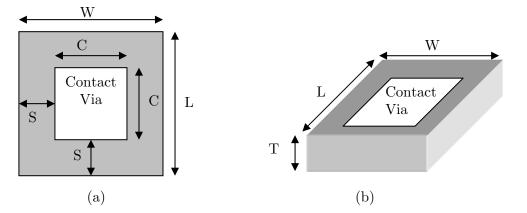

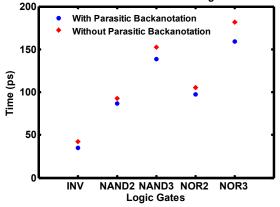

| 3.10 | Source/drain terminal geometry (a) top view and                      | 59 |

|      | (b) side view                                                        |    |

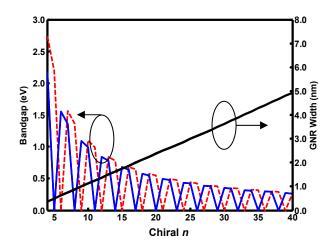

| 3.11 | Energy bandgap versus chirality $n$ for CNT and                      | 62 |

|      | GNR. GNR width versus chirality $n$                                  |    |

|      |                                                                      |    |

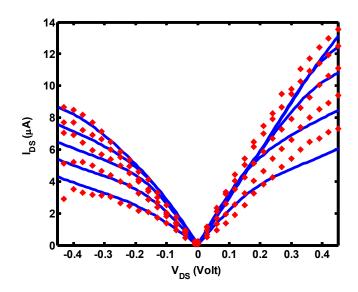

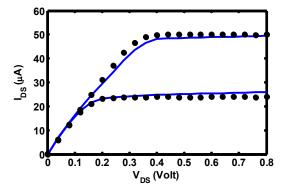

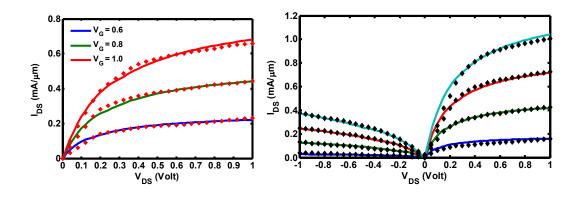

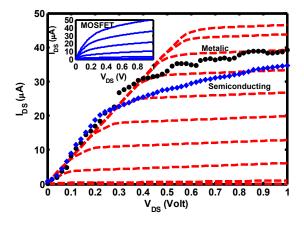

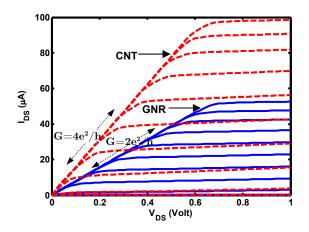

| Comparison of simulated CNT drain characteristic               | 63                                                                          |

|----------------------------------------------------------------|-----------------------------------------------------------------------------|

| versus 80nm experimental data                                  |                                                                             |

| Comparison of our CNTFET simulated results                     | 64                                                                          |

| against 10 nm Arizona CNTFET model for $V_G =$                 |                                                                             |

| 0.6 and 0.8V                                                   |                                                                             |

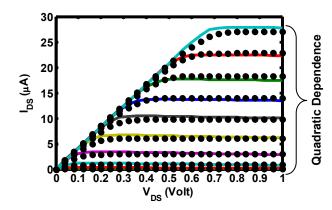

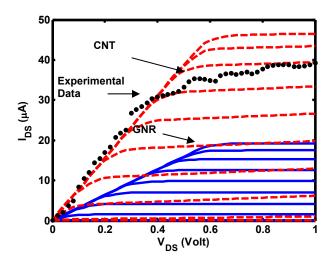

| Comparison of our CNTFET simulated results                     | 64                                                                          |

| against 50 nm single-tube Stanford CNTFET                      |                                                                             |

| model from $V_G=1V$ (top) with 0.1V spacing                    |                                                                             |

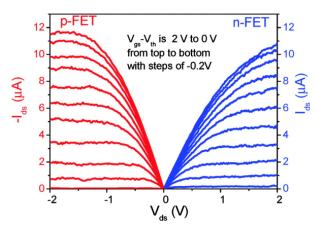

| Characteristics of the almost perfectly symmetric              | 65                                                                          |

| CNT-based CMOS inverter fabricated on the same                 |                                                                             |

| SWCNT with $d=2$ nm with gate length of                        |                                                                             |

| $L{=}4.0~\mu\mathrm{m}$                                        |                                                                             |

| Drain characteristics from $V_G=1V$ to $0V$ (top to            | 66                                                                          |

| bottom) with $0.1 \text{ V}$ spacing for n-type device and     |                                                                             |

| $V_G$ =0V to 1V (top to bottom) with 0.1 V spacing             |                                                                             |

| for p-type device                                              |                                                                             |

| Matrix row vector versus matrix column vector                  | 66                                                                          |

| plotting                                                       |                                                                             |

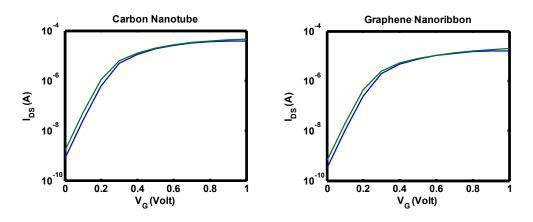

| Gate characteristic for CNTFET and GNRFET                      | 67                                                                          |

| Matrix row vector versus matrix row vector plotting            | 67                                                                          |

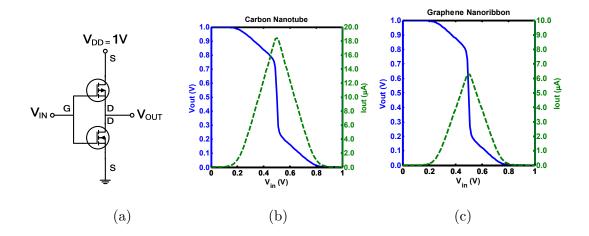

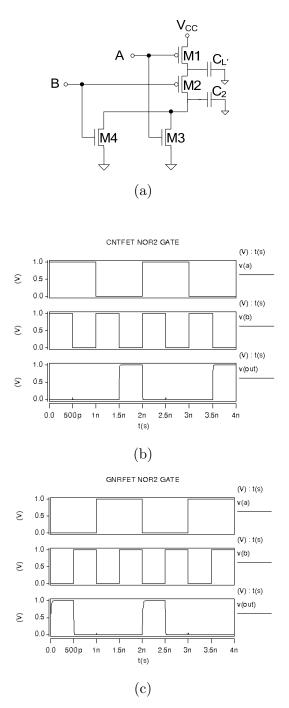

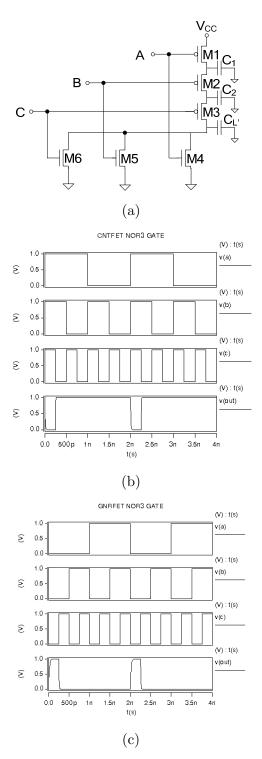

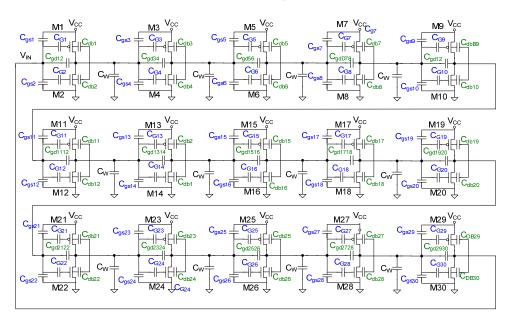

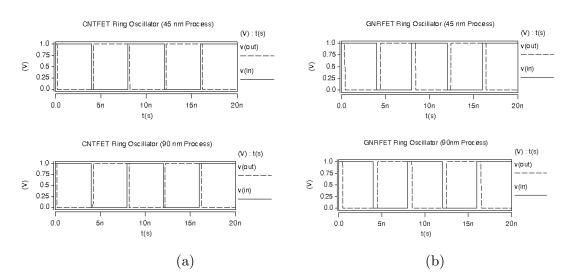

| (a) CMOS-like circuit for (b) CNTFET and (c)                   | 68                                                                          |

| GNRFET.                                                        |                                                                             |

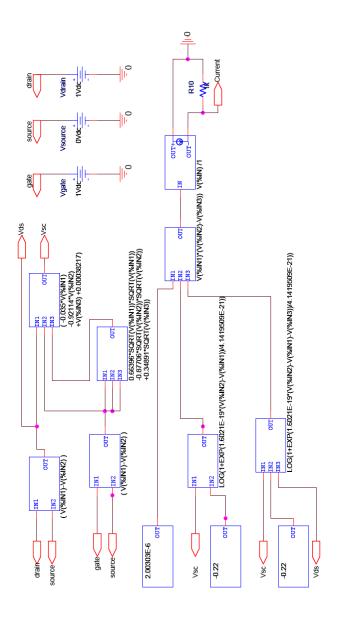

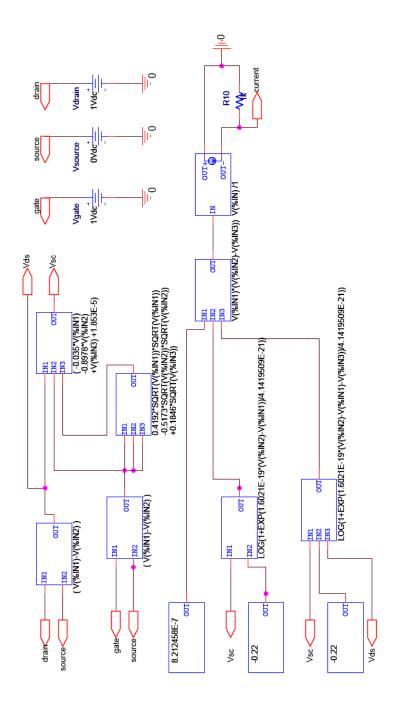

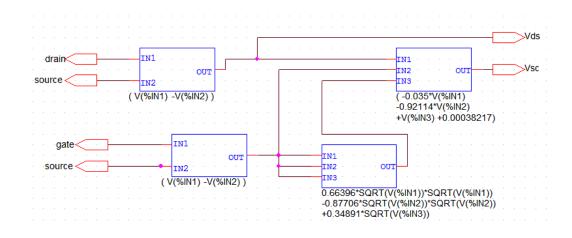

| PSPICE ABM CNTFET macro-model                                  | 70                                                                          |

| PSPICE ABM GNRFET macro-model                                  | 71                                                                          |

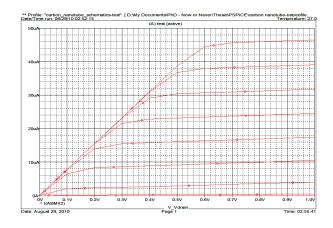

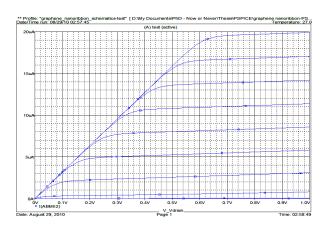

| PSPICE $I-V$ characteristic of the n-type CNTFET               | 72                                                                          |

| PSPICE $I-V$ characteristic of the n-type GNRFET               | 72                                                                          |

| $I\text{-}V$ characteristics of 80-nm MOSFET for $V_{G}$ =0.7, | 73                                                                          |

|                                                                |                                                                             |

|                                                                | versus 80nm experimental data<br>Comparison of our CNTFET simulated results |

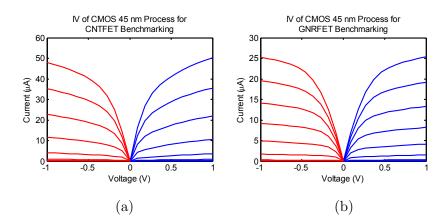

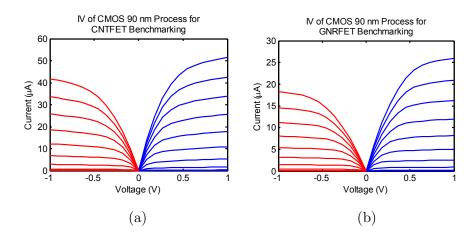

| 3.26 | (a) Simulated 45 nm MOSFET drain characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | versus 45nm TSMC experimental data at $V_G = 0.6$ V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | 0.8V and $1.0V$ (b) comparison of simulated data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | against 45nm IBM NMOS and PMOS experimental                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | data $V_{\scriptscriptstyle G} = 0.4 { m V}, 0.6 { m V}, 0.8 { m V} 	ext{ and } 1.0 { m V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

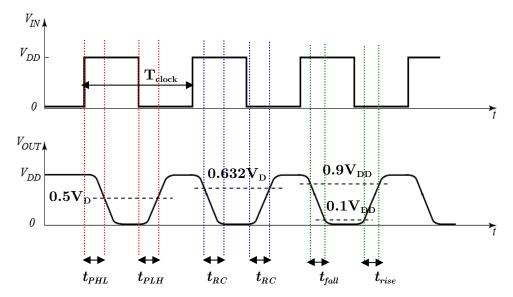

| 3.27 | Measurement $t_{PHL}$ and $t_{PLH}$ between input and output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

|      | voltage, and $t_{RC}$ , $t_{rise}$ and $t_{fall}$ in time domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

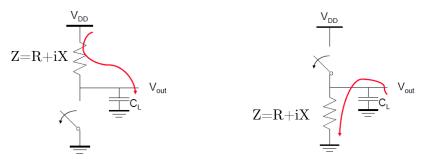

| 3.28 | Equivalent RC circuit from the p-type and n-type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75 |

|      | device charging and discharging processes. Z is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | impedance, R is resistance and X is reactance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

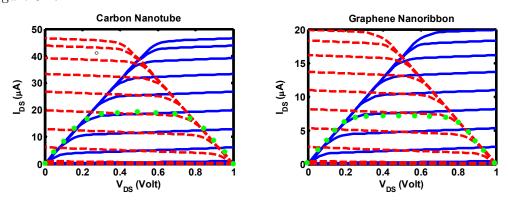

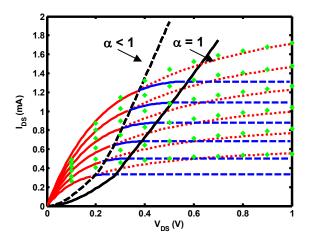

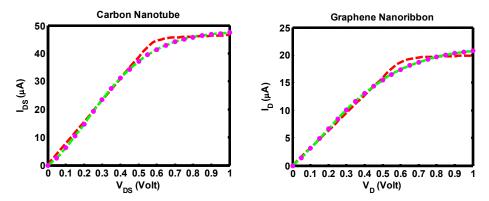

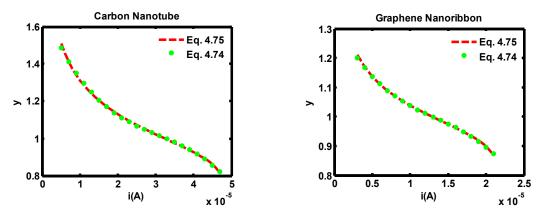

| 3.29 | Fitting curve between CNTFET and GNRFET $I-V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76 |

|      | model with empirical equation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 3.30 | Approximation for real equation and polynomial equation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78 |

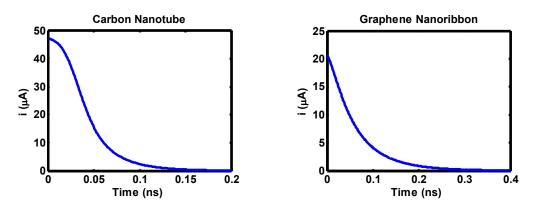

| 3.31 | The current $i(t)$ response to an RC circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79 |

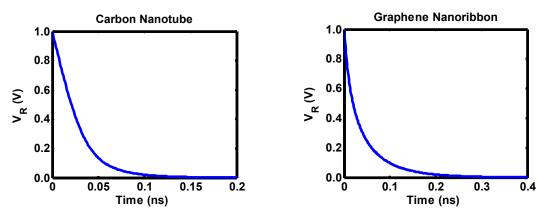

| 3.32 | The resistor voltage in the RC circuit as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79 |

|      | response to time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

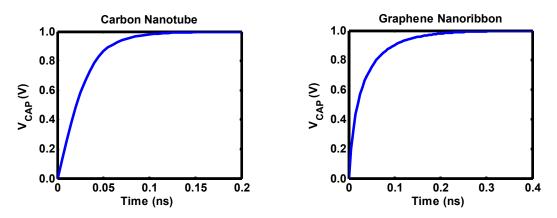

| 3.33 | The capacitor voltage in the RC circuit as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80 |

|      | a response to time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

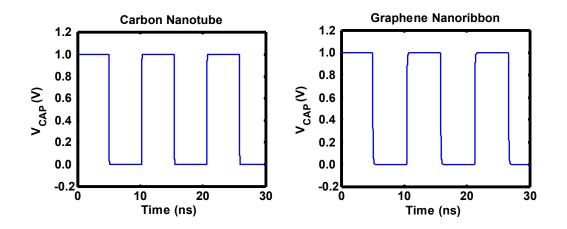

| 3.34 | RC waveforms with large time scale. 570<br>RC constant $\hfill \hfill \hfi$ | 80 |

|      | for the CNT and 211RC constant for the GNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

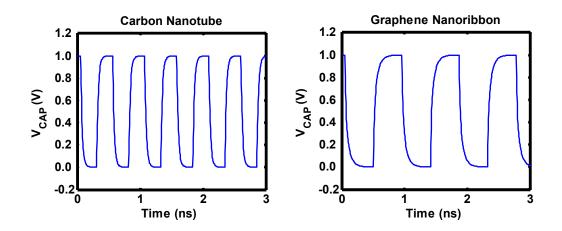

| 3.35 | $\rm RC$ waveforms with medium time scale. 27 $\rm RC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81 |

|      | constant for the CNT and $17RC$ constant for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | GNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

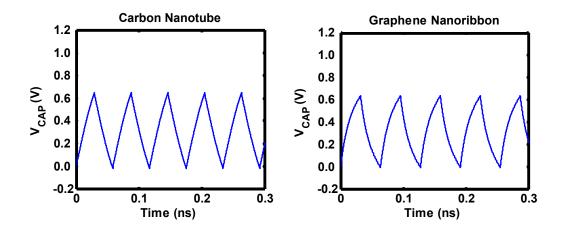

| 3.36 | $\rm RC$ waveforms with small time scale. 1 $\rm RC$ constant $~\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81 |

|      | for both the CNT and GNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

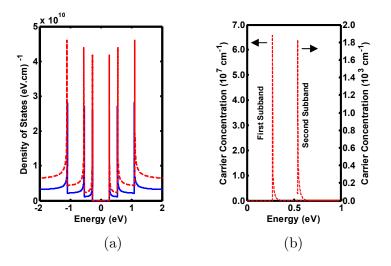

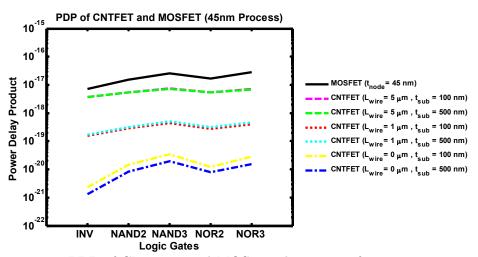

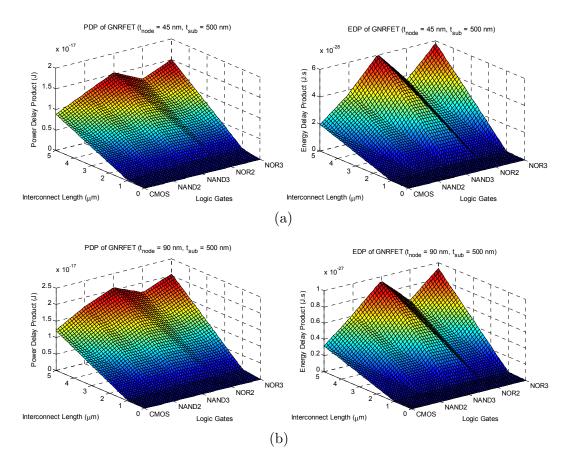

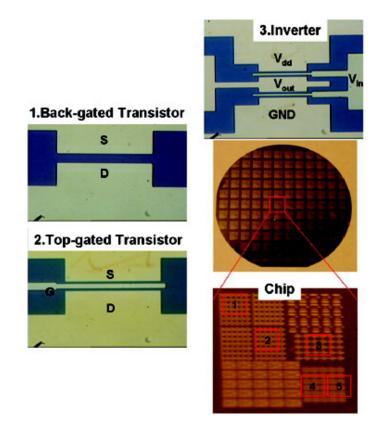

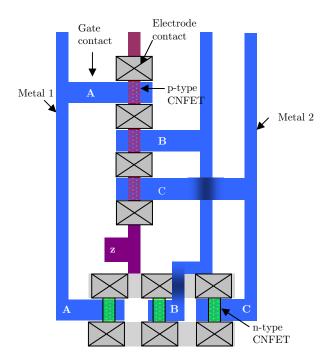

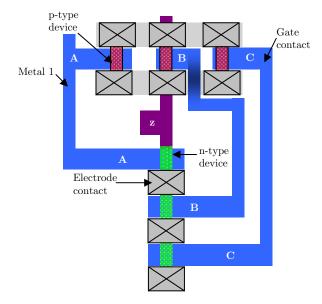

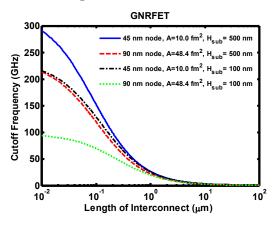

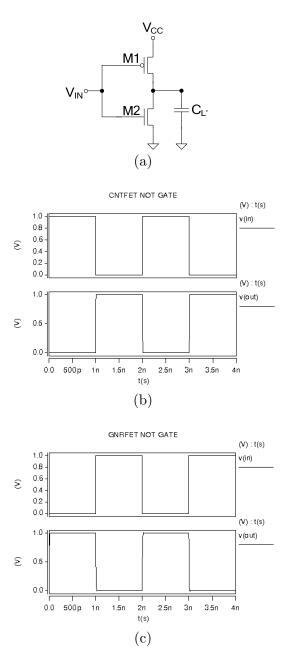

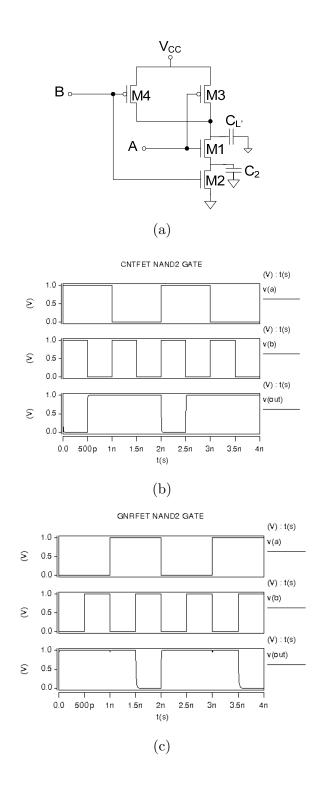

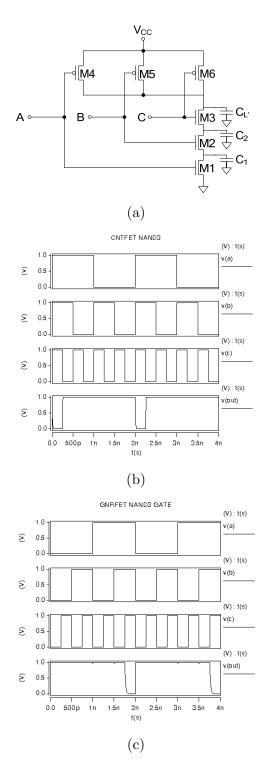

| 4.1  | (a) Electronic density of states calculated for a $[19,0]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89 |