#### Alina Vasilciuc

Bachelor in Sciences of Electrical and Computer Engineering

# Data Visualization for Benchmarking Neural Networks in Different Hardware Platforms

Dissertation submitted in partial fulfillment of the requirements for the degree of

Master of Science in **Electrical and Computer Engineering**

Adviser: Luís Gomes, Associate Professor with Habilitation,

**NOVA University Lisbon**

**Examination Committee**

Chair: Rui Neves-Silva Rapporteur: André Damas Mora Member: Luís Gomes

# Data Visualization for Benchmarking Neural Networks in Different Hardware Platforms Copyright © Alina Vasilciuc, Faculty of Sciences and Technology, NOVA University Lisbon. The Faculty of Sciences and Technology and the NOVA University Lisbon have the right, perpetual and without geographical boundaries, to file and publish this dissertation through printed copies reproduced on paper or on digital form, or by any other means known or that may be invented, and to disseminate through scientific repositories and admit its copying and distribution for non-commercial, educational or research purposes, as long as credit is given to the author and editor.

This document was created using the (pdf) LaTeX processor, based on the "novathesis" template[1], developed at the Dep. Informática of FCT-NOVA [2]. [1] https://github.com/joaomlourenco/novathesis [2] http://www.di.fct.unl.pt

| To my family, |

|---------------|

|               |

|               |

|               |

#### ACKNOWLEDGEMENTS

I would like to especially thank my supervisor Professor Luís Gomes, for all the excellent advice and for always pushing me to learn more, to work harder and for his support and guidance.

I want to thank FCT-UNL for hosting this course and making all of this possible.

I want to express my gratitude to my manager Michaela Blott who saw potential inside me and took the time to get to know me and for giving me this lifetime opportunity of doing an internship at Xilinx, Inc. I truly appreciate the confidence Michaela showed in me, for all the support, the insights and guidance. Thank you for our friendship, for lifting my spirits when hard times would come and for all advice provided.

A special thank you to Xilinx, Inc and all of my work colleagues, for their friendship, companionship and support throughout this journey.

I would like to sincerely thank my parents, their trust and confidence in me, for their support, for cheering me up through more challenging times and for making all of this possible.

And finally a big thank you to all the Professors at FCT-UNL that took the time to teach me, always pushing me harder and for the thousands of lessons they taught me throughout these five years.

#### ABSTRACT

The computational complexity of Convolutional Neural Networks has increased enormously; hence numerous algorithmic optimization techniques have been widely proposed. However, in a space design so complex, it is challenging to choose which optimization will benefit from which type of hardware platform. This is why QuTiBench - a benchmarking methodology - was recently proposed, and it provides clarity into the design space. With measurements resulting in more than nine thousand data points, it became difficult to get useful and rich information quickly and intuitively from the vast data collected.

Thereby this effort describes the creation of a web portal where all data is exposed and can be adequately visualized. All the code developed in this project resides in an online public GitHub repository, allowing contributions.

Using visualizations which grab our interest and keep our eyes on the message is the perfect way to understand the data and spot trends. Thus, several types of plots were used: rooflines, heatmaps, line plots, bar plots and Box and Whisker Plots.

Furthermore, as level-0 of QuTiBench performs a theoretical analysis of the data, with no measurements required, performance predictions were evaluated. We concluded that predictions successfully predicted performance trends. Although being somewhat optimistic because predictions become inaccurate with the increased pruning and quantization. The theoretical analysis could be improved by the increased awareness of what data is stored in the on and off-chip memory. Moreover, for the FPGAs, performance predictions can be further enhanced by taking the actual resource utilization and the achieved clock frequency of the FPGA circuit into account. With these improvements to level-0 of QuTiBench, this benchmarking methodology can become more accurate on the next measurements, becoming more reliable and useful to designers.

Moreover, more measurements were taken, in particular, power, performance and accuracy measurements were taken for Google's USB Accelerator benchmarking Efficient-Net S, EfficientNet M and EfficientNet L. In general, performance measurements were reproduced; however, it was not possible to reproduce accuracy measurements.

**Keywords:** Deep Learning, Field Programmable Gate Arrays, Graphics Processing Unit, Benchmarks, QuTiBench

#### RESUMO

A complexidade computacional de Redes Neuronais Convulsionadas aumentou muito nos últimos anos, consequentemente inúmeras técnicas de otimização têm sido propostas para endereçar este assunto. No entanto, num espaço de desenvolvimento tão complexo, é difícil escolher que otimização vai beneficiar nestas plataformas de hardware, nomeadamente nas FPGAs, GPUs e ASICs. É por isto que QuTiBench — uma metodologia de benchmarking (avaliação comparativa) — foi recentemente proposta, a qual gerou um conjunto de dados com mais de nove mil data points, os quais se tornam difíceis de analisar e tirar informação útil de forma fácil e intuitiva.

Assim, este documento tem como objetivo descrever a criação de um portal web onde todos os dados estão expostos e podem ser devidamente visualizados. Todo o código desenvolvido para este documento está no GitHub, um repositório online e público, permitindo contribuições de terceiros. Usando visualizações que captam o interesse e passam a mensagem de uma forma intuitiva é a melhor maneira de entender os dados e detetar tendências. Para o efeito, diversos tipos de gráficos foram usados tais como: rooflines, mapa de calor, gráfico de linha, gráfico de barra e diagrama de caixa.

Como o nível 0 de QuTiBench faz uma análise teórica dos dados, foi efetuada uma análise entre o previsto e o medido. Concluiu-se que as previsões teóricas conseguiram prever as tendências gerais embora ainda sendo um pouco otimistas. A análise teórica pode ser melhorada ao manter o registo de se os dados estão na memória on-chip ou off-chip. Para as FPGAs, as previsões de performance podem ser melhoradas ao ter em conta a verdadeira utilização de recursos e a frequência de clock atingida pelo circuito. Com estes melhoramentos, o nível 0 de QuTiBench consegue prever a performance com maior grau de certeza e gerar dados mais confiáveis.

Também foram feitas mais medições de consumo de energia, desempenho e precisão ao USB Accelerator da Google das redes neuronais EfficientNet S, EfficientNet M e EfficientNet L. Em geral reproduziram-se os resultados apresentados pela Google em termos de desempenho, mas não foi possível reproduzir os de precisão.

**Palavras-chave:** Deep Learning, Field Programmable Gate Arrays, Graphics Processing Unit, Benchmarks, QuTiBench

# CONTENTS

| Li | st of | Figures | 3                                              | XV   |

|----|-------|---------|------------------------------------------------|------|

| Li | st of | Tables  |                                                | xvii |

| A  | crony | ms      |                                                | xix  |

| 1  | Intr  | oductio | on                                             | 1    |

|    | 1.1   | Conte   | xt                                             | 1    |

|    | 1.2   | Motiv   | ation                                          | 2    |

|    | 1.3   | Proble  | em statement                                   | 4    |

|    | 1.4   | Object  | tives and Contributions                        | 4    |

|    |       | 1.4.1   | Objective                                      | 4    |

|    |       | 1.4.2   | Contributions                                  | 4    |

|    | 1.5   | Docur   | ment Structure                                 | 5    |

| 2  | Rela  | ated wo | ork                                            | 7    |

|    | 2.1   | Defini  | itions and Generic Background                  | 7    |

|    |       | 2.1.1   | Neural Networks                                | 7    |

|    |       | 2.1.2   | Deep Neural Networks                           | 9    |

|    |       | 2.1.3   | Convolutional Neural Networks                  | 9    |

|    |       | 2.1.4   | Popular DNN models                             | 10   |

|    |       | 2.1.5   | Popular Data Sets for Classification           | 12   |

|    | 2.2   | Algori  | ithmic Optimization techniques                 | 13   |

|    | 2.3   | Hardy   | ware for DNN Processing                        | 14   |

|    |       | 2.3.1   | Increased Efficiency in Temporal Architectures | 14   |

|    |       | 2.3.2   | Increased Efficiency in Spatial Architectures  | 15   |

|    | 2.4   | Hardy   | ware Architectures for Deep Learning           | 16   |

|    |       | 2.4.1   | FPGA: FINN and BISMO architetcures             | 18   |

|    |       | 2.4.2   | Coral USB Accelerator                          | 20   |

|    |       | 2.4.3   | Intel NCS2                                     | 22   |

|    | 2.5   | Chara   | cteristics and Challenges in Benchmarking      | 22   |

|    | 2.6   | Existin | ng Benchmarking                                | 23   |

|    |       | 2.6.1   | NN System Benchmarks                           | 23   |

# CONTENTS

|    |       | 2.6.2 ML Benchmarks                               | 24 |

|----|-------|---------------------------------------------------|----|

|    |       | 2.6.3 Performance Benchmarks                      | 25 |

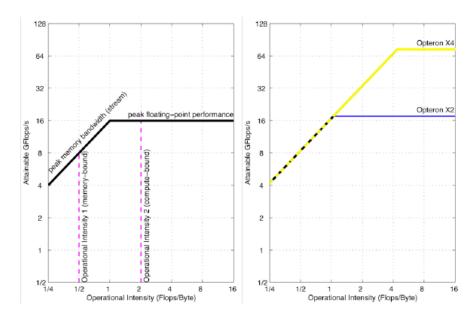

|    | 2.7   | Rooflines                                         | 25 |

|    |       | 2.7.1 Context                                     | 25 |

|    |       | 2.7.2 What is it?                                 | 26 |

|    |       | 2.7.3 The Roofline Model                          | 26 |

|    |       | 2.7.4 How to improve performance                  | 27 |

|    | 2.8   | Data Visualizations                               | 28 |

|    | 2.9   | Previous implementation: QuTiBench                | 29 |

|    |       | 2.9.1 Experimental Results and Evaluation         | 31 |

| 3  | Dev   | relopment: Benchmarking Hardware                  | 35 |

|    | 3.1   | Coral USB Accelerator                             | 35 |

|    |       | 3.1.1 Data acquisition                            | 35 |

|    |       | 3.1.2 Results                                     | 39 |

| 4  | Dev   | relopment: Website Visualizations                 | 43 |

|    | 4.1   | Theoretical Analysis - Level 0 of QuTiBench       | 44 |

|    |       | 4.1.1 Methodology                                 | 44 |

|    |       | 4.1.2 Results                                     | 48 |

|    | 4.2   | MNIST Classification - Level 3 of QuTiBench       | 55 |

|    | 4.3   | Raw Measurements                                  | 57 |

|    | 4.4   | FAIR and Open Data                                | 58 |

|    | 4.5   | How to make contributions page                    | 58 |

|    | 4.6   | Overview of the Experiments page                  | 58 |

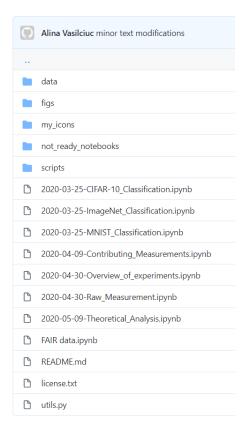

|    | 4.7   | Code and online repository                        | 58 |

| 5  | Eval  | luation                                           | 61 |

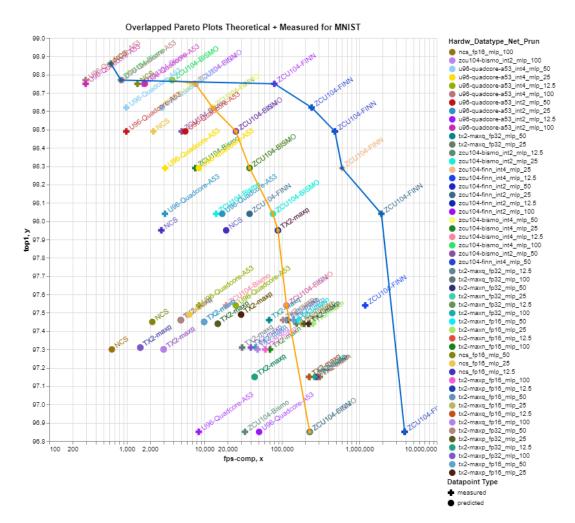

|    | 5.1   | Theoretical Pareto and Measured Pareto Overlapped | 61 |

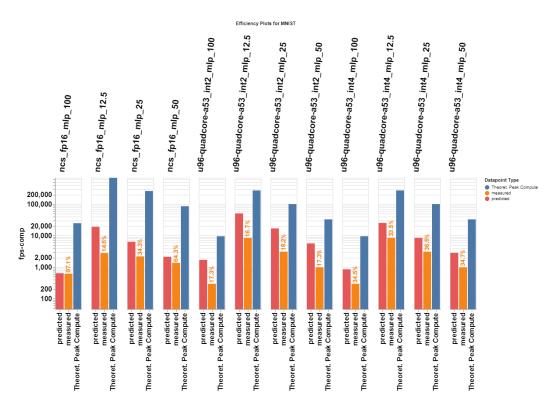

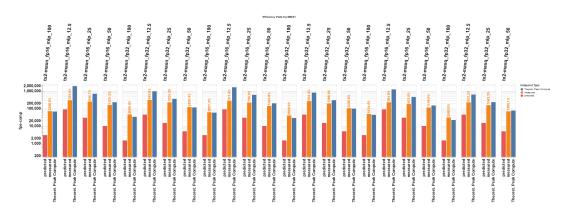

|    | 5.2   | Efficiency plots                                  | 63 |

|    | 5.3   | Evaluation between theoretical and measured       | 64 |

|    |       | 5.3.1 FPGA Platforms                              | 65 |

|    |       | 5.3.2 GPU Platforms                               | 66 |

|    |       | 5.3.3 Edge TPU and NCS2 Platforms                 | 69 |

| 6  | Con   | clusions and Future work                          | 71 |

| Bi | bliog | raphy                                             | 75 |

| Aı | ınexe | es                                                | 81 |

| I  | Ann   | nex 1 List of figures                             | 81 |

# LIST OF FIGURES

| 1.1  | lenge                                                                                                          | 3  |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2.1  | History of Neural Networks [46]                                                                                | 8  |

| 2.2  | Simple Neural Network example and terminology                                                                  | 9  |

| 2.3  | A diagram depicting all steps that a single grayscale input image endures in each layer. Figure taken from [2] | 10 |

| 2.4  |                                                                                                                | 12 |

|      | Model Scaling                                                                                                  | 14 |

| 2.5  |                                                                                                                |    |

| 2.6  | Mapping to matrix multiplication for convolutional layers                                                      | 15 |

| 2.7  | Read and write access per MAC [46]                                                                             | 16 |

| 2.8  | Memory hierarchy and data movement energy cost [46]                                                            | 16 |

| 2.9  | Floor Plan of Google's TPU [29]                                                                                | 18 |

|      | Overview of BISMO's hardware architecture [56]                                                                 | 19 |

|      | Overview of FINN flow for a BNN                                                                                | 19 |

|      | Matrix Multiplier + summation [36]                                                                             | 21 |

| 2.13 | "Roofline model for (a) AMD Opteron X2 on left and (b) Opteron X2 vs.                                          |    |

|      | Opetron X4 on the right" [58]                                                                                  | 27 |

| 2.14 | Illustration of the multi-tiered approach proposed by the benchmark method-                                    |    |

|      | ology - QuTiBench [7]                                                                                          | 29 |

| 2.15 | Rooflines provided by level 0 for GoogleNet and ResNet50 on TX2 and ZCU104                                     |    |

|      | [7]                                                                                                            | 32 |

| 2.16 | "Performance comparison layer0, layer1, layer2 and layer3 for TX2 (MaxN,                                       |    |

|      | FP16 configuration)"[7] for ResNet50                                                                           | 32 |

| 2.17 | "System Performance evaluation" [7] for TX2 and ZCU104 for INT8, FP16,                                         |    |

|      | FP32, for both GoogleNetV1 and ResNet50 and for different batch sizes [7]                                      | 32 |

| 3.1  | Block diagram between the USB accelerator and the computer                                                     | 36 |

| 3.2  | UM34C Power meter used in the power measurements                                                               | 39 |

| 3.3  | Connection between the computer, the Power Meter and the USB Accelerator.                                      | 39 |

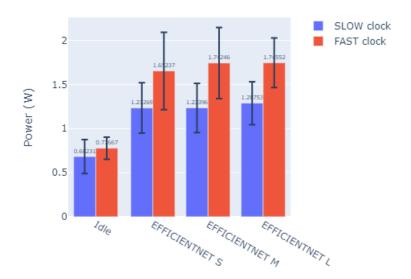

| 3.4  | Average and standard deviation for power measurements on the USB Acceler-                                      |    |

|      | ator                                                                                                           | 41 |

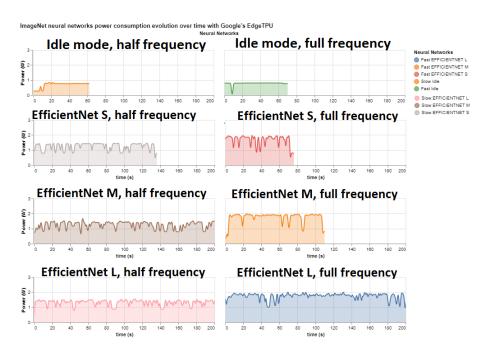

| 3.5  | Power consumption evolution over time for ImageNet task                                                        | 42 |

#### List of Figures

| 4.1  | Fastpages diagram [18]                                                                    | 43 |

|------|-------------------------------------------------------------------------------------------|----|

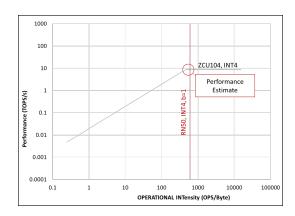

| 4.2  | Performance estimate on a Roofline model [8]                                              | 47 |

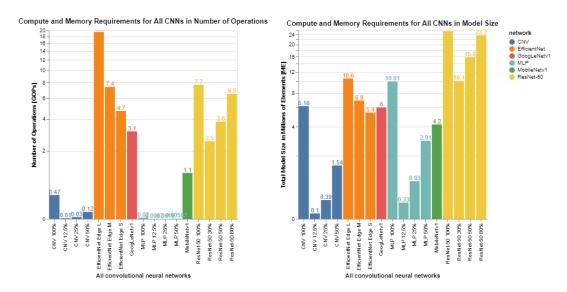

| 4.3  | CNNs compute and memory requirements. Figure available at [5]                             | 49 |

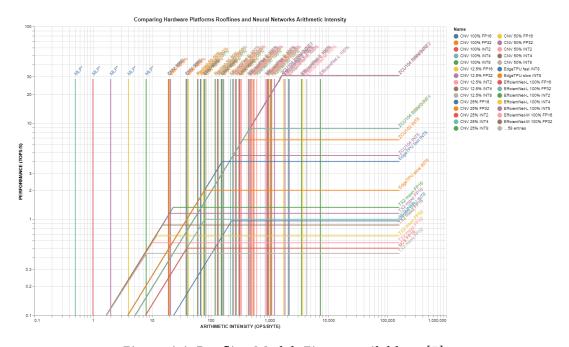

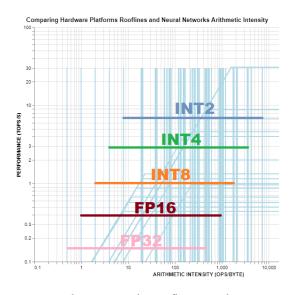

| 4.4  | Roofline Model. Figure available at [5]                                                   | 50 |

| 4.5  | Performance prediction with roofline analysis. Figure available at [5]                    | 51 |

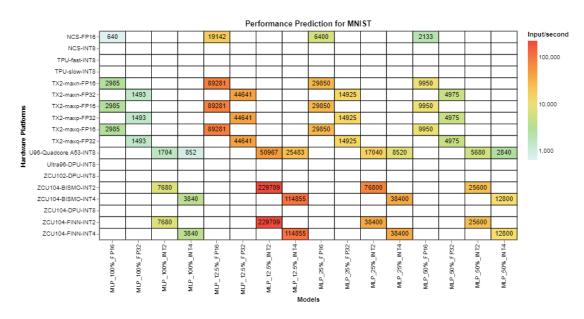

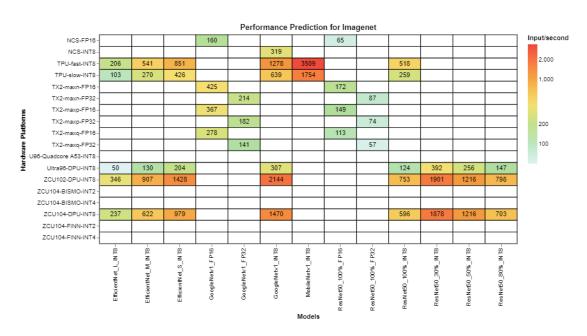

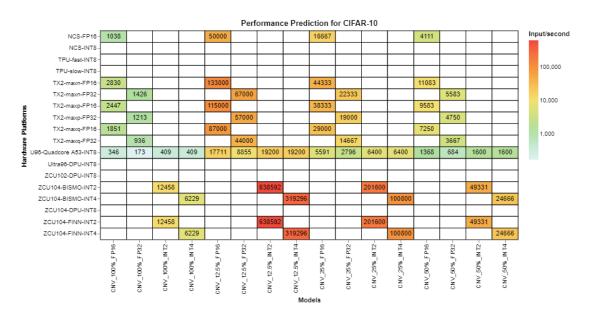

| 4.6  | Performance Predictions with Heatmaps for MNIST classification                            | 52 |

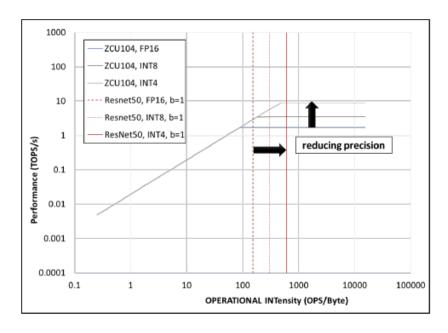

| 4.7  | Effect of quantization on OI and performance [8]                                          | 53 |

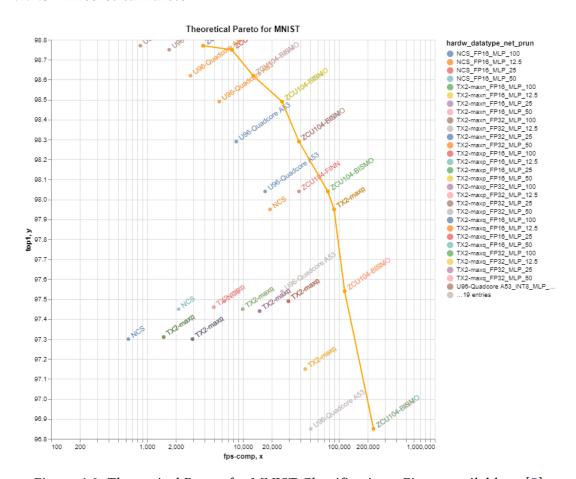

| 4.8  | Theoretical Pareto for MNIST Classifications. Figure available at [5]                     | 54 |

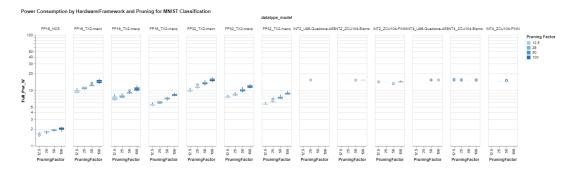

| 4.9  | Power consumption. Figure available at [5]                                                | 55 |

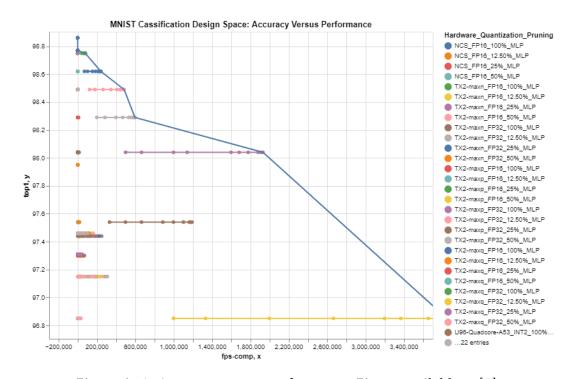

| 4.10 | Accuracy versus performance. Figure available at [5]                                      | 56 |

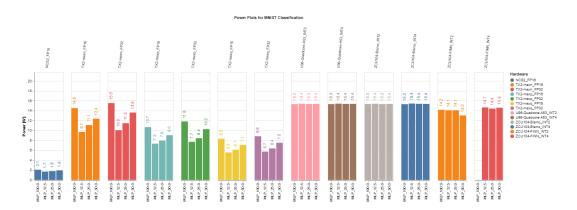

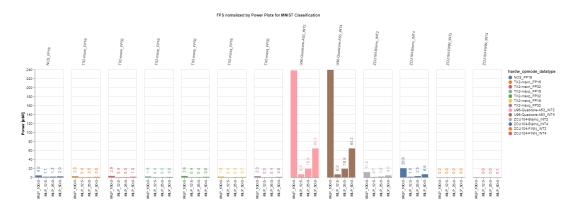

| 4.11 | Power bar charts for MNIST. Figure available at [5]                                       | 57 |

| 4.12 | Performance normalized Bar charts for MNIST. Figure available at [5]                      | 57 |

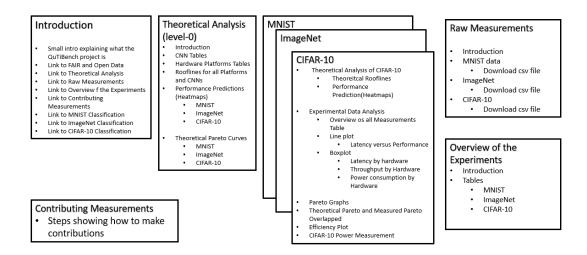

| 4.13 | Website structure                                                                         | 59 |

| 4.14 | GitHub repository overview                                                                | 59 |

| 5.1  | Overlapped pareto plot for MNIST classification                                           | 63 |

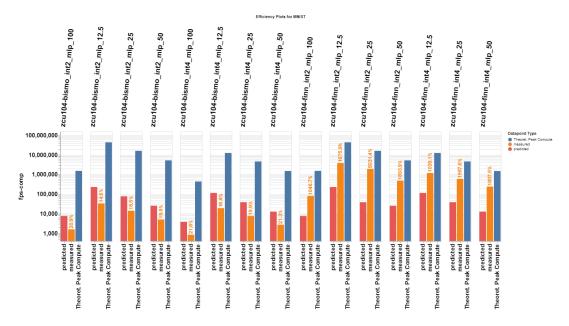

| 5.2  | Efficiency Bar charts for MNIST                                                           | 64 |

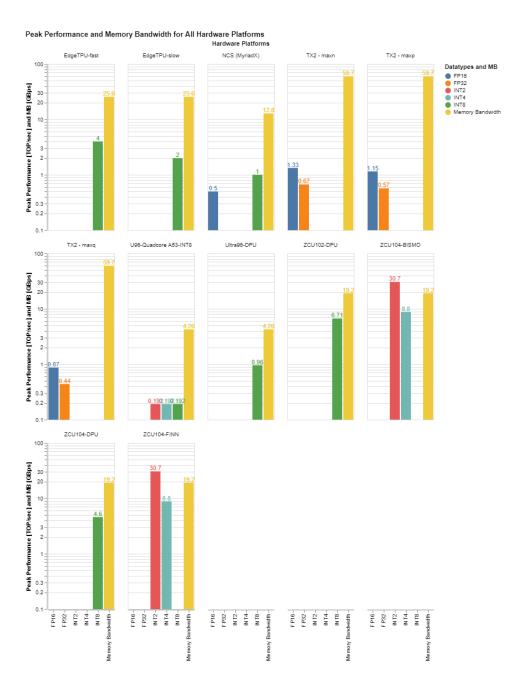

| I.1  | Hardware platforms with their Peak Performance Predictions. Figure available              | 82 |

| T 2  | at [5]                                                                                    | 02 |

| I.2  | Performance Predictions with Heatmap for ImageNet classification. Figure available at [5] | 83 |

| I.3  | Performance Predictions with Heatmap for CIFAR-10 classification. Figure available at [5] | 83 |

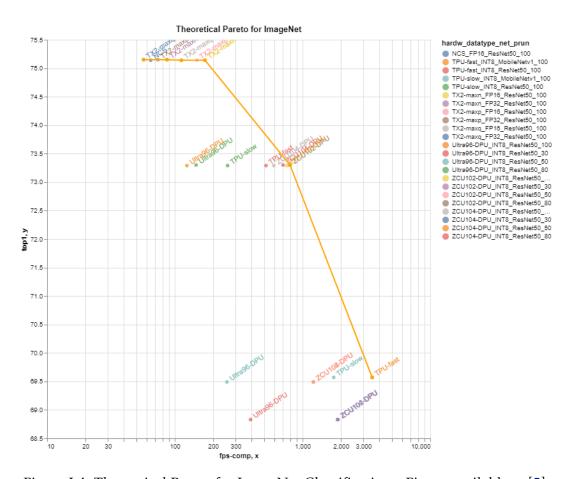

| I.4  | Theoretical Pareto for ImageNet Classifications. Figure available at [5]                  | 84 |

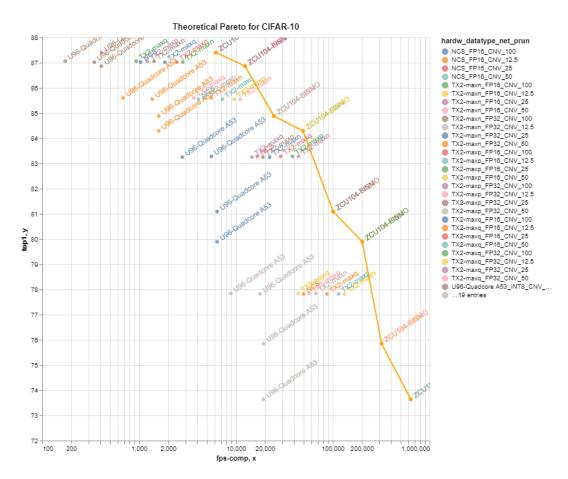

| I.5  | Theoretical Pareto for CIFAR-10 Classifications. Figure available at [5]                  | 85 |

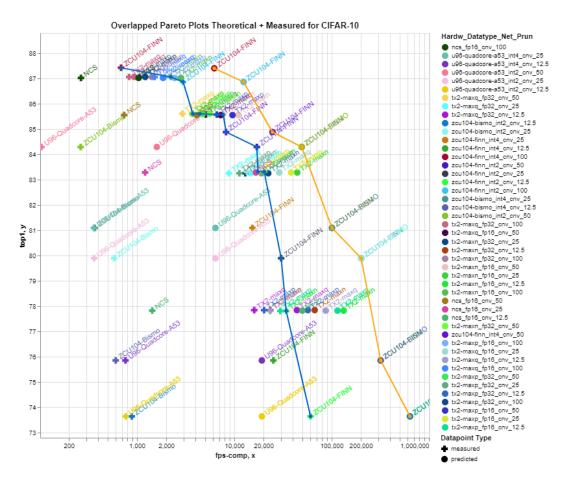

| I.6  | Overlapped Pareto Plot for CIFAR-10 Classification                                        | 86 |

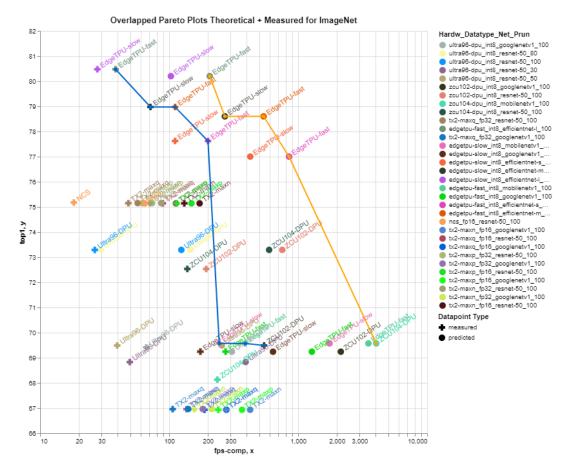

| I.7  | Overlapped Pareto Plot for ImageNet Classification                                        | 87 |

| I.8  | Bar chart showing Efficiency for MNIST classification over NCS2 and the A53.              |    |

|      | Figure available at [5].                                                                  | 88 |

| I.9  | Bar chart showing Efficiency for MNIST classification over the TX2. Figure                |    |

|      | available at [5]                                                                          | 88 |

# LIST OF TABLES

| 1.1  | ResNet models' training time benchmarked with fb.resnet.torch using four M40 GPUs. Table taken from Lecture 15 – Efficient Methods and Hardware for Deep Learning. | 3  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Tot Beep Bearining.                                                                                                                                                | J  |

| 2.1  | DNN models summarized [7]                                                                                                                                          | 13 |

| 2.2  | Hardware platforms and neural networks model [7]                                                                                                                   | 30 |

| 3.1  | Latency Results                                                                                                                                                    | 40 |

| 3.2  | Accuracy results from benchmarking EfficientNets on USB Accelerator                                                                                                | 40 |

| 3.3  | Power consumption results from benchmarking EfficientNets on USB Acceler-                                                                                          |    |

|      | ator                                                                                                                                                               | 41 |

| 4.1  | Experimental CNNs and their accuracies. Table adapted from [8]                                                                                                     | 45 |

| 4.2  | CNNs and their compute and memory requirements. Table Adapted from [8].                                                                                            | 48 |

| 4.3  | Level 0 of QuTiBench. Hardware platforms with their Peak Performance Pre-                                                                                          |    |

|      | dictions [8]                                                                                                                                                       | 50 |

| 5.1  | Terminology explained                                                                                                                                              | 62 |

| 5.2  | Efficiency results for the FPGAs for all pruned and quantized variants of CNV.                                                                                     | 66 |

| 5.3  | Efficiency results for the FPGAs for all pruned and quantized variants of MLP.                                                                                     | 66 |

| 5.4  | Efficiency results for the FPGAs for all topologies of ImageNet                                                                                                    | 66 |

| 5.5  | Efficiency results for the TX2s for all pruned and quantized variants of CNV.                                                                                      | 67 |

| 5.6  | Efficiency results for the TX2s for all pruned and quantized variants of MLP.                                                                                      | 68 |

| 5.7  | Efficiency results for the TX2s for all topologies of ImageNet                                                                                                     | 68 |

| 5.8  | Efficiency results for the NCS2 for all topologies of ImageNet                                                                                                     | 69 |

| 5.9  | Efficiency results for the NCS2 for all pruned and quantized variants of MLP.                                                                                      | 69 |

| 5.10 | Efficiency results for the NCS2 and USB Accelerator for all topologies of Ima-                                                                                     |    |

|      | geNet ML task                                                                                                                                                      | 69 |

#### ACRONYMS

AI Artificial Inteligence ALU Arithmetic Logic Unit

ASIC Application Specific Integrated Circuit

BNN Binarized Neural Network

CLB Configurable logic BLock

CNN Convolutional Neural Network

CONV Convolutional

CPU Central Processing Unit

DL Deep Learning

DNN Deep Neural Network

DPU Deep Learning Processing Unit

DRAM Dynamic random-access memory

EIE Efficient Inference Engine

FC Fully Connected

FET Field-effect TransistorsFFT Fast Fourier TransformFLOP Floating-point Operation

FPGA Field Programmable Gate Array

GOP Giga Operation

GPU Graphics Processing Unit

ILSVRC ImageNet Large Scale Visual Recognition Challenge

IoT Internet of Things

MAC Multiply AccumulateME Millions of ElementsML Machine Learning

NN Neural Network

OI Operational Intensity

PCB Printed Circuit Board

PE Processing Engine

POP Peta Operation

RF Register File

SIMD Single instruction multiple data SIMT Single instruction multiple threads

SoC System on Chip

SRAM Static Random Access Memory

TOP Tera Operation

TPU Tensor Processing Unit

C H A P T E R

#### Introduction

Isn't it a pleasure to study and practice what you have learned? -Confucious

#### 1.1 Context

Artificial Intelligence (AI), Machine Learning (ML) and Deep Learning (DL) are nowadays shaping the future of every industry and every human being. To be clear on the terms: Deep Learning forms a subset of Machine Learning, which forms a subset of Artificial Intelligence. AI is the main driver of emerging technologies like robotics, big data and IoT, and it is foreseen to continue to be a technological enabler. Some sectors are at the beginning of their AI journey, whereas others are veteran travellers. AI's impact is found on a large set of applications that goes from Transportation to Healthcare and Education.

Neural networks have been around for a while, and recently they have been on the spotlight for many machine learning applications. They can recognize patterns, clustering it and classifying it. They have been applied to all kinds of applications because they are so easy to use.

However, these algorithms strongly rely on computer power, and with it comes massive power consumption. Moreover, their heavy memory requirements make deployment rather difficult in energy-constrained environments such as embedded systems.

With addressing these issues, a new plethora of hardware architecture has emerged, specifically heterogeneous hardware architecture along with co-designed algorithms. Furthermore, to diminish computer requirements as well as more significant bandwidth requirements with the same accuracy, algorithmic and software optimizations, as well as architectural optimizations for NNs, are being searched. Although some optimizations

consist of performing the same operations faster, other optimizations change entirely the way the training is done.

Comparing all these criteria is rather difficult due to the scarcity of standard evaluation criteria that examines all these considerations. This document is based on *QuTiBench* [7], a Benchmark suite that addresses this need. Hardware systems and system topologies can differ a lot in design options. Each component and system design quite often comes with its power, programmability and design trade-offs. For a significant amount of reasons, what may be convenient for one system designer's need may not be suitable for some other system designer. However, there is no way to compare different design options. While there is some work done in this area, it only covers very little of the embedded design space. Up until today, benchmarks have trouble supporting important algorithmic optimizations such as quantization, pruning and specialized heterogeneous hardware architectures.

Due to the difficulty of comparing all these criteria, this document will present data visualizations that could provide better understanding and comparison between all the plethora of hardware architecture and techniques that have arisen.

#### 1.2 Motivation

Deep Learning relies on computer power to solve more complex problems, and with new computing technologies, companies can have AI models that can learn to solve complex problems. Deep Learning enables researchers to train "with billions of parameters" [4] "from massive datasets that improve in accuracy as the dataset grows" [10]. However, all this computer power comes with great power consumption [49], and considering that the world is experiencing an unprecedented growing electricity consumption by computers, data centres and a growing number of internet users [27], the need to turn towards greener solutions arises. To overcome the power issue makes it mandatory to shift from traditional computing paradigms to new ones.

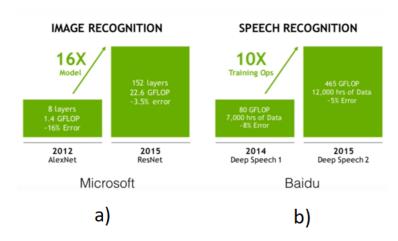

Deep Learning is changing our lives. However, there is a recent trend in which, to achieve higher accuracy, models are getting larger and larger. Figure 1.1 shows that there was an increase of 16 times in the model size of the winners in the ImageNet Challenge from 2012 to 2015. Another example is Baidu's deep speech model which increased ten times the number of operations in only one year. All these heavy models make distribution through over-the-air update very difficult. In mobile phones, for instance, if the item is larger than one hundred megabytes, it can only be downloaded through wi-fi.

Another challenge that comes with larger models is speed. Figure 1.1 illustrates the training time taken by several types of ResNets. The lowest error rate of 6.16% takes 1.5 weeks to train on four M40 GPUs. Furthermore, it is only 0.1% better than the second-best error rate. This extended training time makes the researcher's productivity greatly limited.

Figure 1.1: "Characteristics of winning Neural Networks model from the ImageNet Challenge. a)Increase of 16 times in neural networks' model size between winner AlexNet in 2012 to winner ResNet in 2015. b) Ten times increase in the number of training operations in Baidu's deep speech neural network from 2014 to 2015" [22].

Table 1.1: ResNet models' training time benchmarked with fb.resnet.torch using four M40 GPUs. Table taken from Lecture 15 – Efficient Methods and Hardware for Deep Learning.

|           | Error rate | Training time |

|-----------|------------|---------------|

| ResNet18  | 10.76%     | 2.5 days      |

| ResNet50  | 7.02%      | 5 days        |

| ResNet101 | 6.21%      | 1 week        |

| ResNet152 | 6.16%      | 1.5 weeks     |

The third most crucial challenge is energy efficiency. In the embedded environment with energy constraints, larger models can drain all the power. In data centres, power consumption is also crucial. The objective is to find the optimum balance that breaks the boundary between algorithm and hardware, thus, improving performance and power consumption.

The increasing need for more computer power has been fostering the increase in new technology targeting AI. However, existing benchmarks are not suitable enough to exhaustively analyze hardware as well as algorithms to provide knowledge on system problems and thus instigate greener solutions. Moreover, the lack of standard benchmarking methodology further aggravates the existing situation.

With more than nine thousand data points generated by QuTiBench, arises the need for adequate visualization of the data in a manner that trends can be spotted, and it can send a clear message. Moreover, there is a need for a web portal where all data can be publicly available online, and that could allow for contributions.

This is why QuTiBench [7], the benchmarking methodology, which was used to take all measurements taking into account hardware variety, numerous algorithmic optimization techniques and a plethora of neural networks now need a proper way to present results

to the public in an insightful way.

#### 1.3 Problem statement

During this work, it was verified that as AI is emerging in numerous use cases, there is a need to make it faster but especially greener. To achieve this, QuTiBench was proposed, and after it collected more than nine thousand data points now, there is a need to understand all data collected.

The following thesis is defended in this dissertation: It is possible to improve existing benchmarking work by making use of QuTiBench, a benchmark methodology, that supports a different kind of algorithmic optimizations such as quantization and provides system designers with some insight about strengths and limitations on recent compute architectures regarding Neural Networks. Having so much data from more than nine hundred measurements creates the need for a powerful tool to understand them better. In this way, different kind of visualizations need to be created to gain better comprehension into all trade-offs between algorithmic optimizations and hardware choices. Moreover, these visualizations need to be available online inside a web portal where contributions can be made to the project.

Besides a powerful way to see and understand all gathered data, there is also a need for it to be publicly accessible and to allow for contributions from third parties whom themselves have performed measurements and wish to contribute.

Moreover, more measurements need to be taken. As Google announces that Efficient-Net S, EfficientNet M and EfficientNet L achieve very high accuracy on its low power, high throughput USB Accelerator, it becomes essential to include this device in the QuTiBench measurements.

# 1.4 Objectives and Contributions

#### 1.4.1 Objective

Considering the problem statement and related considerations, the objective of the thesis is to display all data gathered by the benchmark suite to reveal the potential of different hardware platforms publicly. In the envisaged approach, the idea is to explore neural networks performance and hardware performance to maximize both for specific use cases.

#### 1.4.2 Contributions

Related publications co-authored by this dissertation author are listed below:

• Michaela Blott, Nicholas J.Fraser, Giulio Gambardella, Lisa Halder, Johannes Kath, Zachary Neveu, Yaman Umuroglu, Alina Vasilciuc, Miriam Leeser, and Linda Doyle, "Evaluation of Optimized CNNs on Heterogeneous Accelerators using a Novel Benchmarking Approach" in IEEE Transactions on Computers,

DOI: 10.1109/TC.2020.3022318.

• M. Blott, A. Vasilciuc, M. Leeser and L. Doyle, "Evaluating Theoretical Baselines for ML Benchmarking Across Different Accelerators," in IEEE Design & Test, DOI: 10.1109/MDAT.2021.3063340.

#### 1.5 Document Structure

The remaining of this report is divided into five chapters.

- Chapter 2 Related Work: presents related work. It starts with a background on neural networks, enumerates optimization techniques, an existing hardware architecture for deep learning and describes existing Benchmarking. It presents the key concepts of QuTiBench. Describes the various types of visualizations used.

- Chapter 3 Development: Benchmarking Hardware presents this work contribution; in particular, it describes how benchmarking Google's USB accelerator was done.

- Chapter 4 Development: Website Visualizations: describes the freshly build a web portal, all its contents and visualizations.

- **Chapter 5 Evaluation**: shows specific visualizations that highlight the difference between what was predicted and what was measured. Moreover, it evaluates how accurate predictions were compared to the measured data points and concludes how to improve level 0 of QuTiBench.

- Chapter 6 Conclusions and Future work: summarizes the main conclusions and presents future directions.

2

# RELATED WORK

This chapter introduces previous related work. It focuses on benchmarking deep learning algorithms and resents several state-of-the-art hardware architectures targeting neural networks.

## 2.1 Definitions and Generic Background

#### 2.1.1 Neural Networks

Neural networks are a class of machine learning algorithms based on several connected nodes called artificial neurons roughly modelled after the human brain that are designed to detect patterns.

Although they were proposed in the 1940s, their very first application did not appear until the 1980s when a network called LeNet was developed for handwritten digit recognition, which is still today used by ATMs to verify digit recognition on checks [31]. Later, in 2010 NN-based application started to grow exponentially until present days. Figure 2.1 shows a timeline of popular NNs.

Neural networks accomplish this by considering examples and by automatically finding specific characteristics from the samples they process. Over the past few years, neural networks have become a major success and have been used in a variety of tasks, including computer vision, robotics, speech recognition and machine translation. An exciting aspect of NNs is that they have the theoretical property of being a type of machine learning which requires zero domain expertise, which makes them an appealing solution both for unsolved problems and for solved ones. However, all this computational power comes at a cost, the tremendous demand for more computing power comes with enormous power consumption and memory requirements concerning capacity and access bandwidth, which becomes an obstacle, especially in the embedded space.

#### **DNN Timeline**

- 1940s Neural networks were proposed

- 1960s Deep neural networks were proposed

- 1989 Neural networks for recognizing digits (LeNet)

- 1990s Hardware for shallow neural nets (Intel ETANN)

- 2011 Breakthrough DNN-based speech recognition (Microsoft)

- 2012 DNNs for vision start supplanting hand-crafted approaches (AlexNet)

- 2014+ Rise of DNN accelerator research (Neuflow, DianNao...)

Figure 2.1: History of Neural Networks [46].

Unfortunately, evaluating ML performance for training systems is undoubtedly more challenging than performance evaluation for classic software. ML systems are not like the traditional processing systems because they operate in a very different way [39]. Traditional systems are programmed with specific logic, whereas ML systems are fed massive datasets and are expected to apply algorithms that find patterns and features in all data. "The main goal of ML is to train a model that makes high-quality predictions on unseen data, which is referred to as *generalization*" [10]. This goal is achieved through the minimization of a loss-function to find a model that can learn weights from the training dataset and more importantly, *generalizes* to new data from a similar distribution. Existing Benchmarks measure proxy metrics, for instance, time to process a minibatch of data, but do not take into account whether the system as a whole will produce a high-quality result.

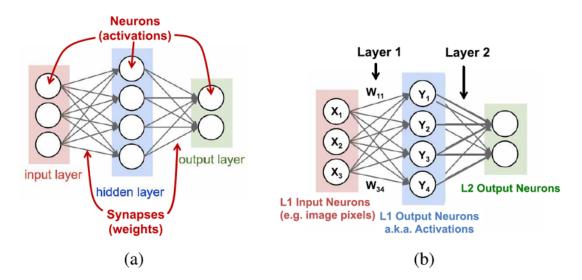

Technically described, neural networks are a connected graph of neurons. Each neuron processes a function to its input(s) to generate an output, thus being a processing component. "Edges" are the connections between two different neurons and are represented through a number. The output of each neuron is computed by a non-linear function of the sum of its inputs. Neurons, as well as edges, both have a weight, which can increase or decrease the strength of the signal, and it is continually adjusted as the learning process proceeds. Usually, neurons are assembled into many layers, in which each different layer applies a different transformation to its input. Figure 2.2 depictures a computational neural network. Values are propagated from the input layer to the hidden layer, also called the middle layer. The final value is presented to the user after all weighted sums from all hidden layers eventually propagated to the output layer. *Activations* are sometimes referred to as the outputs of neurons.

Computation at each layer is done with the following equation:  $y_i = f(\sum_{i=1}^3 W_{ij} \times x_i + b)$ , where  $W_{ij}$  are the weights,  $x_i$  are the input activations,  $y_i$  are the output activations and f(.) is a nonlinear function. The bias term is absent in Figure 2.2 for simplicity.

Figure 2.2: "Simple Neural Network example and terminology. (a) Neurons and Synapses. (b) Compute weighted sum of each layer" [46].

#### 2.1.2 Deep Neural Networks

All the different connections between all different layers define the structure of the network. Deep Neural Networks (DNNs) are classified as such due to the number of layers, in this case, more than three layers. That means that there are one or more hidden layers. Nowadays, the usual range of hidden layers goes from five to more than a thousand [46]. In a fully connected network, all neurons from a particular layer are connected to every neuron from the subsequent layer.

DNNs are broadly used for image processing, as they can distinguish high-level features. When pixels from an image are fed to the DNN, the first layer can extract low-level features like lines and edges. At the next layer, all previous features are used to extract higher-level features like shapes. In the end, the output will be a probability that all those high-level characteristics belong to a particular object or scene. The use of all those layers enables DNNs to achieve more outstanding performance in many use cases.

#### 2.1.3 Convolutional Neural Networks

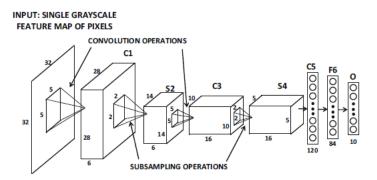

A Convolutional Neural Network' structure is similar to a DNN except for the fact that convolutional neural networks (CNNs) are specialized for image-related tasks. A CNN is a deep learning algorithm that takes an input, usually, an image and drafts the importance of all features in the token image and, after it is trained, it is ready to differentiate any given images. CNNs can understand the Spatial and Temporal dependencies in an image through the application of relevant filters. In a CNN architecture, if the input image is on grayscale, then the input layer is 1-dimensional, but if the image comes in colours, then the input layer is 3-dimensional which corresponds to the colour channels like RGB.

Each image is represented as a 3D matrix with a dimension for the height, width and depth. Depth refers to the colour channels used in an image. The architecture comprises two types of layers: convolution and subsampling, also known as pooling layers.

In a convolutional layer, the mapping of activations from each layer to the subsequent is done using a filter. Thus, a convolution is defined, as it is shown in figure 2.3. Figure 2.3 shows an input image of 32x32, which is convolved with a filter of weights of 5x5. The learned weights are *kernels* that are convolved with the image to extract features. The convolution uses a multidimensional filter of weights, which means that numerous convolutions are performed on the input, in which each operation uses a different filter. The subsequent layers are calculated by doing the dot product between the weights in the filter and the image pixels. This results in several feature maps. In figure 2.3 C1 holds all six feature maps, which means that six different filters were applied. These filters is to highlight contrast, blur, edge and many other things. Performing the convolution between the filter of weights and pixels is done at all possible positions, from left to right and from top to down.

The objective of pooling is to extract only "interesting" features, which is achieved by downsampling each one of the feature map. These convolutions, followed by pooling layers, are repeated multiple times in a CNN to produce high-quality features present in the input images.

Figure 2.3: A diagram depicting all steps that a single grayscale input image endures in each layer. Figure taken from [2].

#### 2.1.4 Popular DNN models

Apart from the neural networks described above, there are other different types, and newer ones continue to arise. In this section, an overview of some of the most popular NNs will be given, most of these models are available for download.

Some of the NNs described below competed in the ImageNet Challenge [41]. The ImageNet Large Scale Visual Recognition Challenge (ILSVRC) is an annual computer vision competition which uses the computer vision dataset called ImageNet. It accounts for more than 14 million images and around 1 million images with boxes around an

identified object in each image. Accuracy has been improved significantly from the 2010 edition to the 2014 edition. There have been many important developments and academic publications relating to ILSVRC.

LeNet [31] was one of the first Convolutional Neural Network approaches introduced in 1989, it is what made CNNs successful for the first time. Back then it was used for digit recognition on checks used by ATMs. Its designated task was to recognize digit handwritten in greyscale images of size  $28 \times 28$ . Throughput rates obtained were of more than ten digits per second. LeNet-5, the most well-known version contains three convolutional (CONV) layers and two fully connected layers (FC) [32]. Each one of the convolutional layers uses filters of size  $5 \times 5$ , being one channel per filter. After the second CONV layer, there is a subsampling layer. For the nonlinearity, a sigmoid is used. Summing up, LeNet requires 60000 weights and 341000 multiply-and-accumulate (MACS) per one input (image) [32].

AlexNet [30] won the ImageNet Challenge in 2012 being the very first convolutional neural network to achieve this. It has five CONV layers and three FC layers, it also has pooling layers. A powerful GPU implementation of the convolution operation was used to speed up training, along with saturating neuron. The overfitting in the fully connecting layers was reduced due to the application of a method called "dropout". This NN achieved a winning top-1 test error rate of 37.5% and a top-5 test error rate of 17%.

Overfeat's [42] architecture is analogous to AlexNet, it comes with "five convolutional layers and three fully connected layers" [7]. The difference between Overfeat and AlexNet is the number of filters used in each layer. For layers 3, 4 and 5 Overfeat uses a larger amount of filters. Thus, there is a significantly higher amount of weights, one hundred and forty-six million to be exact. Overfeat has two main model variations: described above is fast, and there is also another model referred to accurate model used in the ImageNet Challenge. Although the accurate model achieves better accuracy than the fast model, it performs 1.9× more MACs.

VGG-16 [43] has sixteen layers, thirteen are convolutional layers and three FC layers. Because it has so many layers,  $5 \times 5$  filters are assembled from other  $3 \times 3$  filters. It is estimated that "VGG-16 requires one hundred and thirty-eight million weights and 15.5 MACs to process a  $224 \times 224$  input image" [46]. There are two variant models of VGG: VGG-16 (described above) and VGG-19, which produces a lower top-5 error rate, however, it does  $1.27 \times$  more MACS.

GoogLeNet [47] goes deeper with twenty-two layers composed of three CONV layers followed by nine inception layers and one FC layer. It introduces an inception module that, instead of a previously single serial connection, is composed of parallel connections. It uses multiple filter sizes (e.g.,  $1 \times 1$ ,  $3 \times 3$ ,  $5 \times 5$ ). As it uses several sizes for the filter, it processes the input at multiple scales. An interesting aspect of GoogLeNet is that the weights and activation fit into a single GPU memory.  $1 \times 1$  filters are applied to diminish the number of weights by reducing channels for each filter.

ResNet [25], often referred to as Residual Net, benefits of residual connections and

has around thirty-four layers. ResNet is made of one CONV layer, sixteen shortcut layers and one FC layer. It is estimated that ResNet requires "25.5 million weights and 3.9G MACs per image" [46]. ResNet comes in different depths. The winner of the ImageNet Challenge owned one hundred and fifty-two layers.

Efficientnet S, M and L introduced in 2019 [48], were chosen to be run on the USB Accelerator for many reasons. First of all, these NNs are pre-compiled models that Google made available specifically for the USB Accelerator. The other reason is that EfficientNets were recently proposed, along with a new scaling method to achieve higher accuracy.

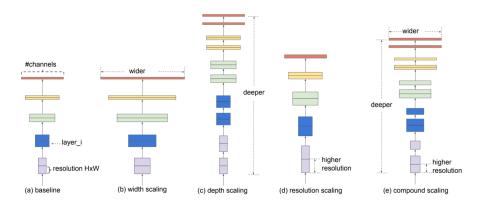

Let us start with what scaling is and why it is essential. There are three scaling dimensions: depth, width and resolution. Depth relates to the number of layers a model owns. Width relates to how vast the network is, for instance, the number of channels in a convolutional layer. Furthermore, the resolution is the input image resolution. Figure 2.4 [48], illustrates each of these concepts. Scaling is done to improve a model's accuracy on a specific task such as ImageNet classification. If done correctly, it can also improve efficiency.

Figure 2.4: Model Scaling. (a) baseline network example; (b)-(d) conventional scaling that only increases one dimension of network width, depth, or resolution. (e) is the proposed compound scaling method that uniformly scales all three dimensions with a fixed ratio. Adapted from [48].

In this paper [48] the authors proposed a straightforward but effective technique to scale the network depth uniformly, width and resolution using a compound coefficient  $\phi$ . This compound scaling method allowed to scale up a baseline ConvNet to produce an EfficientNet model that can surpass state-of-the-art accuracy while using fewer parameters and Floating-point Operations (FLOPs).

#### 2.1.5 Popular Data Sets for Classification

MNIST was introduced in 1998 and is a commonly used dataset for digit classification. It is made of sixty thousand  $28 \times 28$  pixel greyscale images of handwritten digits. When MNIST was first introduced, LeNet-5 was able to achieve a 99.05% accuracy. Since then the accuracy has increased, making MNIST a reasonably easy data set.

Table 2.1: DNN models summarized [7].

| Metrics                                | LeNet<br>5        | AlexNet   | Overfeat<br>fast | VGG<br>16 | GoogLeNet<br>v1 | ResNet<br>50 |

|----------------------------------------|-------------------|-----------|------------------|-----------|-----------------|--------------|

| Top-5 error <sup>†</sup>               | n/a               | 16.4      | 14.2             | 7.4       | 6.7             | 5.3          |

| Top-5 error (single crop) <sup>†</sup> | n/a               | 19.8      | 17.0             | 8.8       | 10.7            | 7.0          |

| Input Size                             | 28×28             | 227×227   | 231×231          | 224×224   | 224×224         | 224×22       |

| # of CONV Layers                       | 2                 | 5         | 5                | 13        | 57              | 53           |

| Depth in # of CONV Layers              | 2                 | 5         | 5                | 13        | 21              | 49           |

| Filter Sizes                           | 5                 | 3,5,11    | 3,5,11           | 3         | 1,3,5,7         | 1,3,7        |

| # of Channels                          | 1, 20             | 3-256     | 3-1024           | 3-512     | 3-832           | 3-2048       |

| # of Filters                           | 20, 50            | 96-384    | 96-1024          | 64-512    | 16-384          | 64-2048      |

| Stride                                 | 1                 | 1,4       | 1,4              | 1         | 1,2             | 1,2          |

| Weights                                | 2.6k              | 2.3M      | 16M              | 14.7M     | 6.0M            | 23.5M        |

| MACs                                   | 283k              | 666M      | 2.67G            | 15.3G     | 1.43G           | 3.86G        |

| # of FC Layers                         | 2                 | 3         | 3                | 3         | 1               | 1            |

| Filter Sizes                           | 1,4               | 1,6       | 1,6,12           | 1,7       | 1               | 1            |

| # of Channels                          | 50, 500           | 256-4096  | 1024-4096        | 512-4096  | 1024            | 2048         |

| # of Filters                           | 10, 500           | 1000-4096 | 1000-4096        | 1000-4096 | 1000            | 1000         |

| Weights                                | 58k               | 58.6M     | 130M             | 124M      | 1M              | 2M           |

| MACs                                   | 58k               | 58.6M     | 130M             | 124M      | 1M              | 2M           |

| Total Weights                          | 60k               | 61M       | 146M             | 138M      | 7M              | 25.5M        |

| Total MACs                             | 341k              | 724M      | 2.8G             | 15.5G     | 1.43G           | 3.9G         |

| Pretrained Model Website               | [56] <sup>‡</sup> | [57, 58]  | n/a              | [57-59]   | [57-59]         | [57-59]      |

<sup>†</sup>Accuracy is Measured Based on Top-5 Error on ImageNet [14]. <sup>‡</sup>This Version of LeNet-5 has 431000 Weights for the Filters and Requires 2.3 million MACs Per Image, and Uses ReLU Rather Than Sigmoid.

CIFAR [53] is a subset of Tiny Image data set consisting of colored images of different objects released around 2009. It holds sixty thousand of 32x32 images containing one of ten object classes, with six thousand images per class. There are fifty thousand training images and ten thousand test images.

ImageNet [41] was first popularized in 2010. It has  $256 \times 256$  pixel coloured images with one thousand classes. The accuracy is calculated using two metrics: Top-1 and Top-5 error. The top-5 error means that if the first five answers provided include the correct answer, then it is considered to have provided the correct answer. The top-1 error implies that the answer provided is the correct answer.

#### 2.2 Algorithmic Optimization techniques

Quantization and Numerical Representations is the idea of reducing the number of bits that represent a number. On small image classifications benchmarks show that quantized neural networks can attain results which can "achieve state of the art accuracy despite the reduction in precision" [7].

Pruning is an algorithm for efficient inference which drastically reduces memory requirements. The idea is to remove some of the unnecessary weights while still maintaining the same accuracy [13].

### 2.3 Hardware for DNN Processing

There has been a steep development in hardware platforms targeting DNNs along with new features being deployed. The goal is to minimize memory access to save power.

The Intel Knights Mill CPU will get into the DL field by introducing vector instructions into the design [28]. Nvidia Tegra, Samsung Exynos and FPGAs are an embedded system on chip (SoC) that runs inference. It is crucial to study how is the computation made to improve throughput and energy efficiency further. Multiply-and-accumulate (MAC) operations are a common component of both CONV and FC layers, which can easily be parallelized. There are two high-parallel compute paradigms that envision high performance: temporal and spatial architectures.

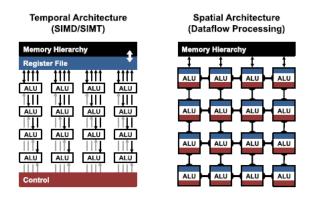

Figure 2.5: Highly parallel compute paradigms [46].

Temporal architectures are typical of both CPUs, and GPUs [46]. CPUs are latency oriented, whereas GPUs are throughput oriented. "A variety of techniques are applied to improve parallelisms, such as parallel threads (SIMT) or vectors (SIMD)"[46]. This type of architecture uses a centralized control for many ALUs. These ALUs are bound to fetch data and communicate only with Memory Hierarchy and not with each other. Spatial architectures, on the other hand, use dataflow processing which means that the ALUs can pass data one another. These ALUs that can communicate with one another and hold local memory through control logic are called as register file and are also referred to as Processing Engine (PE). Spatial architectures are most commonly used for DNN and found on ASICs and FPGAs designs.

#### 2.3.1 Increased Efficiency in Temporal Architectures

This section discusses design optimizations for efficient computing. CPUs and GPUs use some techniques called SIMT and SIMD, which are used to process things, like MACs in parallel. All ALUs have access to the same memory (register file) and control.

The first approach is to make use of the Toeplitz matrix. It is possible to map the CONV layer to matrix multiplication in a DNN using a variant form of the Toeplitz matrix. However, the downside of this approach is that it is introduced unnecessary data

into the input feature map matrix, which can lead to difficulties in accessing memory which implies inefficiency in storage.

Figure 2.6: Mapping to matrix multiplication for convolutional layers. (a) Mapping convolution to Toeplitz matrix. (b) Extend Toeplitz matrix to multiple channels and filters. Adapted from [46].

Libraries that can ultimately improve matrix multiplications for CPUs are, for instance, openBLAS, and for GPUS there is cuBLAS.

Fast Fourier Transform (FFT) comprises numerous frameworks [35]. To perform the convolution, it first takes the FFT of the feature map and the filter, it then computes the multiplication in the frequency domain. Afterwards, the inverse FFT is applied to the resulting product to recover the output feature map in the spatial domain. This way reduces the number of multiplications from  $O(N_o^2 N_f^2)$  to  $O(N_o^2 log_2 N_o)$ , in which the output size is  $N_o N_O$  and the filter size is  $N_f * N_f$ . While FFT can reduce computation, it needs higher bandwidth and storage capacity.

#### 2.3.2 Increased Efficiency in Spatial Architectures

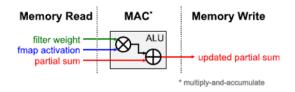

For DNNs memory access is what originates most bottlenecks. In each MAC iteration, it is necessary to perform three memory reads as shown in figure 2.7 and then it is necessary to do a memory write to update the partial sum [46]. The worst-case scenario happens when all memory access is done to the off-chip DRAM, as accessing DRAM is costly and negatively impacts throughput and power efficiency.

The energy cost of internal cache access to functional operations costs about ten pJ, whereas the cost of DRAM access is about one to two nJ, which is a lot more [26]. "DRAM power consumption is crucial in contemporary computer systems as DRAM now accounts for almost half of the total system power consumption" [19]. All this is due to the growing demand for more memory bandwidth and compute power.

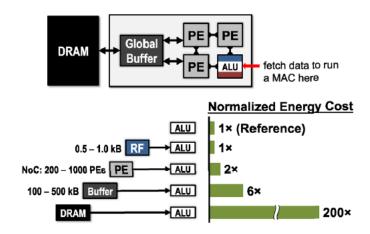

Making use of different levels of local memory hierarchy can greatly reduce the power cost of data movement, which is commonly done by numerous accelerators. This technique includes the introduction of a Global Buffer, a network of all PEs connected moving data between the ALU/s and a register file (RF) in each processing unit as shown in figure

Figure 2.7: Read and write access per MAC [46].

2.8. The introduction of multiple levels of memory hierarchy can help diminish the power cost of data moving because accessing data costs less. Specifically, getting data from the RF or the neighbour PE will cost less than fetching from DRAM.

Figure 2.8: Memory hierarchy and data movement energy cost [46].

# 2.4 Hardware Architectures for Deep Learning

This section will present several types of hardware architectures and implementation alternatives. CPUs, GPUs, FPGAs and specialized architectures are amongst the most popular ones. There has been some research on computer architecture specialized on deep learning processing units (DPUs), and this can be implemented with FPGAs or ASICs. All these different types of architectures are organized according to: "basic type of compute operation, memory bandwidth, level of parallelism, degree of specialization and inherent precision support" [7].

CPU is latency oriented processing architecture which means that it is a serial compute engine. It tries to accomplish as many operations as possible belonging to a single serial thread. Possessing different memory hierarchies, it allows floating-point operations. The memory hierarchy splits the computer storage into a *hierarchy* based on the response time. Nowadays, CPUs are mainly multicore supporting parallel processing and can incorporate vector processing units, for instance, the Intel Knights Mill CPU. A vector processing unit is a CPU that implements an instruction set containing several instructions that operate on one-dimensional arrays of data, referred to as vectors. Depending

on the workload, it can significantly improve performance.

GPUs are throughput-oriented processors. Their main aim is to maximize the total throughput of the system, rather than the latencies of all individual threads that they work on. Inherently, according to Blott, Halder, Leeser & Doyle [7] "GPUs are vector processors that support smaller floating-point formats (FP16) natively, most recently fixed point 8bit integer formats, and have a mix of implicitly and explicitly managed memory". Efficiently accessing memory is a crucial driver to fully explore the power of GPUs [37] [59]. For instance, NVIDIA's GTX980 holds a raw computational power of 4,612 GigaFLOPs/sec <sup>1</sup>, but its theoretical memory bandwidth is only 224 GB/s.

Field Programmable Gate Arrays (FPGAs) are reconfigurable hardware architecture that can adapt to every environment. Due to their massively parallel computing capacity are heavily demanded. FPGAs play an increasingly important role in data sampling and processing industry given their low power consumption and the fact that allow tailoring the amount of hardware parallelism necessary. There are many emerging new use cases for FPGA in the artificial intelligence field, for training and implement the neural networks and machine learning algorithms. Therefore, many companies have applied FPGAs into AI and Machine learning fields such as autonomous driving and Automatic Spoken Language Recognition. FPGAs are so flexible that they can even support bit-serial hardware architectures.

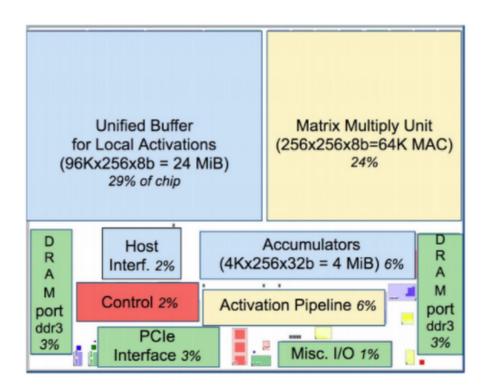

Google introduced its Tensor Processing Unit (TPU) [29] in 2016 designed to accelerate Google's Tensorflow framework. Google's TPU is a custom ASIC deployed in datacenters to specifically accelerate the inference phase of neural networks. As shown in picture 2.9, TPU's core is "a 65,536 8-bit MAC matrix multiply unit that offers a peak throughput of 92 TeraOPs/s  $^2$  and a large (28 MiB) software-managed on-chip memory" [16]. Its design for dense matrices has more than  $25\times$  as many MACs vs GPU and more than  $100\times$  as many MACs vs CPU.

In 2016, Han et al. [23] extended their work by combining Network Pruning with quantization and Huffman encoding to create Deep Compression. Based on this deep compression, the Efficient Inference Engine (EIE) is a hardware accelerator that was designed to work on a compressed model. It was able to improve energy efficiency, and it achieved substantial speedup. By compressing the network through weight sharing or pruning, it was possible to fit recent networks like AlexNet in on-chip SRAM. Processing these compressed models on CPUs and GPUs is somewhat complex and challenging due to the sparse matrices and relative indices after pruning. Han et al. [23] apply a simple rule: "multiply each non-zero activation by all non-zero elements in its corresponding column" [23].

<sup>&</sup>lt;sup>1</sup>GigaFLOPs/sec means Giga (10<sup>9</sup>) floating-point operations per second

<sup>&</sup>lt;sup>2</sup>TeraOPs/s means Tera (10<sup>12</sup>) Operations per second

Figure 2.9: Floor Plan of Google's TPU [29].

#### 2.4.1 FPGA: FINN and BISMO architetcures

The following subsections will explain some architectures presented by Xilinx Research Labs that was benchmarked as part of QuTiBench. These architectures were evaluated as part of QuTiBench project, and several results were obtained; thus, it is important to explain them beforehand.

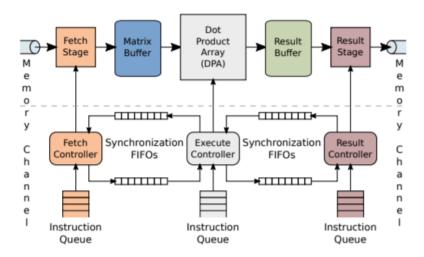

### 2.4.1.1 BISMO

BISMO [57] and [56] is a software-programmable scalable bit-serial matrix multiplication overlay that can be instantiated on an FPGA. In other words, BISMO is a programmable FPGA accelerator for few-bit integer matrix multiplication. It can achieve high performance for matrix multiplication where each matrix element is an integer of 2,3,4,.. bits. This architecture is beneficial for applications like quantized neural networks. It was developed as part of a collaboration between Xilinx Research Labs Ireland and the Norwegian University of Science and Technology Computer Architecture Lab. Its hardware is presented in figure 2.10. BISMO is composed both by a "hardware part and a software part. The hardware part is composed of a scalable bit-serial matrix multiplication datapath with the associated memory and control logic. The software part creates instructions for the hardware for the given matrix size and precision" [57].

It presents a few advantages, such as the fact that it supports several different precisions while performing matrix multiplications. The same hardware can be leveraged for

Figure 2.10: Overview of BISMO's hardware architecture [56].

many use cases, achieving higher speed with the lower precision matrix multiplication than with the higher precisions.

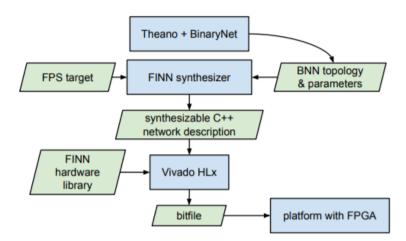

#### 2.4.1.2 FINN

FINN ([55] and [6]) is an experimental framework built at Xilinx Research Labs which explores quantized neural networks inference on FPGAs. It is essentially an open-source framework for building Binarized Neural Networks (BNN) inference accelerators on FPGA. It is very flexible as it allows to dataflow-style architectures customized for each model. It is ideal for embedded applications as it can perform millions of classifications per second.

Figure 2.11: Overview of FINN flow for a BNN

Figure 2.11 shows how an FPGA accelerator can be built from a trained BNN with FINN. Everything starts with the user supplying a Theano-trained (Theano refers to a machine learning library) BNN to the FINN synthesizer, which in turn begins with

determining the needed parameters that can meet the target fps and applies specific optimizations. After, it produces a synthesizable C++ network description which can then be loaded into Vivado HLS and deployed to an FPGA.

#### 2.4.2 Coral USB Accelerator

The Coral USB Accelerator is a small PCB that contains an Edge TPU coprocessor and a USB socket to connect to the computer. It is capable of performing 4 TeraOPs/s <sup>3</sup>, able to perform ML inference and lightweight transfer learning, but not training.

Installing the API library and the Edge TPU runtime on the host computer allows working with the USB accelerator. At this point, it is possible to select between the default clock frequency or the maximum clock frequency at which the device will operate. The maximum clock frequency is twice the default clock frequency which is translated in increased inference speed but also power consumption.

The ML runtime used to execute models is based on TensorFlow Lite. As EdgeTPU is only able to perform 8-bit math, as such, models need to be in a specific format, which means that the network needs to be trained using TensorFlow quantization technique. This technique ensures that the forward pass matches the 8-bit precision for both training and inference. The Edge TPU runtime is required to communicate with the Edge TPU and can be installed on a Linux, Mac or Windows computer host.

#### 2.4.2.1 Context

In 2019 Google released TPU hardware to the market under the Coral brand. However, these are not as powerful as google's cloud TPUs which can run a NN at more than one hundred PetaFLOPs/sec  $^4$ . These recently released TPU devices are meant to be used "at the edge".

Edge Computing means that the computation and data storage runs on local places like a computer, embedded system, IoT device or Edge Server. In contrast, Cloud Computing means that computing and data storage is done in the cloud. The access is done through the internet instead of the computer's hard drive. So data needs to be sent through an internet connection, then wait for the server to process everything and then it sends the results back. This process can be quick on a wired connection, but on bad connections can take up to a few seconds. Edge Computing avoids long-distance communication between a client and a server where bandwidth and latency are affected. This characteristic is important because we humans like to interact with fast things, more precisely, everything that runs faster than one hundred milliseconds.

Edge AI means that AI algorithms are running on a device that uses Edge Computing and all data needed is physically present on the device with no need for fetching data from the cloud. What usually runs at the edge is only inference whereas training is still

<sup>&</sup>lt;sup>3</sup>TeraOPs/s means Tera (10<sup>12</sup>) Operations per second

<sup>&</sup>lt;sup>4</sup>PetaFLOPs/sec means Peta (10<sup>15</sup>) floating-point operations per second

done on servers. However, it is possible to train the last layer of a model on this device. The inference is made with a lightweight version of TensorFlow models which have to be converted to this file type which is more power-efficient. Depending on the application type and especially on the AI workloads hardware options go from CPUs, GPUs, ASICs, FPGAs and SoC accelerators.

Some of the Advantages of Edge AI are reduced cost, security, increased speed, and easy to manage for beginners. Some examples of applications are surveillance and monitoring, autonomous vehicles, smart speakers and industrial IoT.

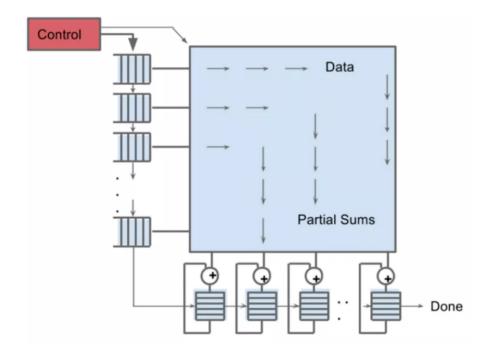

### 2.4.2.2 Edge TPU Processor

Being an ASIC, the Edge TPU is an Integrated Circuit (IC) chip customized for a very particular use rather than a general-purpose use. It combines small electronic circuits, of which field-effect transistors (FETs) and capacities, burned directly on the silicon layer. 5. The logic behind it is simple, and image 2.12 shows the basic principle upon which the Edge TPU was built.

Figure 2.12: Matrix Multiplier + summation [36].

Many neural networks consist mainly of convolutional layers. A convolution is defined by the following equation:

$$(f \times g)(t) \stackrel{\text{def}}{=} \int_{-\infty}^{\infty} f(\tau)g(t-\tau)d\tau \tag{2.1}$$

Each image pixel multiplies by each kernel pixel and then it is all summed up to create a new "image". This type of arithmetic is precisely the reason why the Edge TPU

was created. Whenever data is fed to the buffers, parallel multiplication followed by summation is done at very high speeds.

Being programmed for specific workloads, the Edge TPU can perform up to 4 TeraOPs/s <sup>5</sup> using 8-bit fixed point, and bandwidth capacity lies between 500 MB/s and 640 MB/s. Its size is about a fourth of a penny, and it only needs 500mA 5V USB port which means that its power consumption is at most 2.5 Watt. It is fast because it was greatly optimized for a specific application, unlike a CPU which can do almost everything. An ASIC is specially designed to perform multiplications so it can complete them in a very short time.

#### **2.4.3 Intel NCS2**

The Intel Neural Compute Stick 2 is Intel's deep learning inference development kit. It is packed in an USB-stick form factor and is powered by the VPU (vision processing unit) – the Intel Movidius Myriad X, which includes an on-chip neural network accelerator called the Neural Compute Engine. With 16 SHAVE cores and a dedicated hardware neural network accelerator it's set to deliver 4 trillion operations per second. Intel Distribution of OpenVINO Toolkit supports Ubuntu, CentOS, and Yocto Linux distributions along with Microsoft Windows and Raspbian 32-bit OS. OpenVINO Toolkit includes tools for generating an Intermediate Representation (IR) from TensorFlow, Caffe, and Apache MXNet models. It also supports Open Neural Network Exchange (ONNX) for importing and exporting deep learning models across multiple frameworks.

# 2.5 Characteristics and Challenges in Benchmarking

A Benchmark is a process of measuring the performance of a particular product, service or process, against those of another business. According to Blott, Halder, Leeser & Doyle [7] a more practical definition would imply that a benchmark is a "well-defined set of executable tests and measured regarding a specific set of figures of merit". Sometimes it can analyze some system aspects which can clarify system bottlenecks. The main objective is to identify opportunities for further improvement. Marketing also plays a part when it comes to benchmarking. It is important for a company's products to do well on a benchmark, otherwise it will lose popularity.

For software system designers it can identify which algorithms lead to better performance. For hardware designers, it can clarify what aspects of the architecture need improvement. As neural networks' development is progressing faster than ever, co-design of hardware and algorithms becomes crucial. Some key elements need to be taken into consideration to ensure a good benchmark.

#### 1. Benchmarks need to be **relevant** to the user;

<sup>&</sup>lt;sup>5</sup>TeraOPs/s means Tera (10<sup>12</sup>) Operations per second

- 2. They need to be **objective and repeatable** in terms of the same results and time. Nevertheless, what does repeatable mean? Does it mean that it is enough for a third-party to validate the results? This is hard mainly due to the hardware cost. Benchmarking results have to be objective in order not to favour any specific system or hardware configuration [7];

- 3. Benchmarks need to **represent** true workloads in terms of applications, algorithms and computational patterns;

- 4. Benchmarks need to support **algorithmic optimization**. Researchers making DL computing cannot rely entirely on hardware. Combining hardware optimizations with software optimizations techniques such as model compression can lead to energy-efficiency and performance improvement;

- 5. Portability needs to be taken into consideration when it comes to benchmarking.

- 6. **Complexity vs Speed vs Accuracy**: The aim is to have a benchmark which is low in complexity, very high in speed and accuracy. However, these three criteria influence one another. To lower a benchmark complexity, there is a need to consider the speed and accuracy of the output;

- 7. **Adaptive**: The benchmark suite has to be adaptive because the ML research field is evolving faster than ever, so it can keep up with the emerging algorithms.

# 2.6 Existing Benchmarking

This section will distinguish three different benchmarking types: "ML benchmarks, performance benchmarks and NN system benchmarks" [7]. ML benchmarks are driven by the improvement on accuracy, which improves the overall system performance, with no regards to power efficiency, computing workload or execution time. "Performance benchmarks record hardware performance only, specifically throughput (measured in processed inputs per time or TOPs/s), latency or response time in milliseconds (ms), and power consumption in Watts" [7]. NN system benchmarks take both things into account, hardware performance as well as accuracy.

### 2.6.1 NN System Benchmarks

**BenchIP** [50] presents a Benchmark suite for intelligence processors, and contains two types of benchmarks: micro-benchmarks and macro benchmarks. The aim is to identify performance/energy bottlenecks for potential optimization. However, it does not provide an overall score. It also does not cover the stack of layers, which is important to isolate bottleneck in data movement. It also does not provide the comparison via Pareto curves.

**Fathom** [1] assembled a collection of eight archetypal DL workloads to be studied. It determines where time is spent and studies the effects of parallelism on scaling and

focuses on understanding deep learning workloads. Nonetheless, it is rather limited at benchmarking. It contains CONV and FC layers but lacks Deconvolution, Unpooling and Batch Normalization. It does not provide a benchmarking method for customized hardware architectures. In the customized hardware field, Fathom does not process finegrained architectures' performance.

**TBD** [60] proposes a benchmark suite for DNN training, it holds a set of eight DNN models covering six ML applications. It comprises numerous frameworks, more than Fathom, and numerous applications.

MLPerf [38] aims to provide a comprehensive benchmark suite for training as well as inference over ML hardware, software and services. MLPerf began in February 2018 with several meetings between engineers and researchers from Baidu, Google and some universities from the USA. MLPerf provides insights on how to build a solution. However, it does not address hyper-parameter optimizations.

**DAWNBench** [10] is a project led by Stanford University, and it allows us to compare many DL methodologies which are done by creating competitions. It introduces a benchmark focused on training time to achieve better accuracy. Unlike prior work that focuses solely on throughput metrics, this approach focuses primarily on a combined metric called time-to-accuracy (TTA), which assesses how long it takes to train for a target. However, it only considers ImageNet for both training and inference, making it limited in the application scope, and it does not provide insights into the full design space.

Collective Knowledge Framework [11] in conjunction with the ASPLOS Request Tournament [3] give space for different hardware accelerators while providing an assessment of correlations between accuracy, performance and power trade-offs. It also supports heterogeneous hardware architectures.

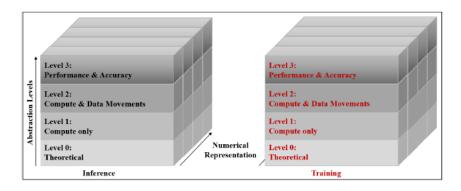

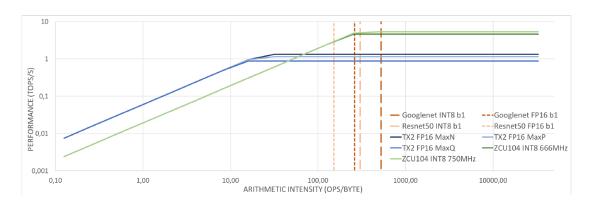

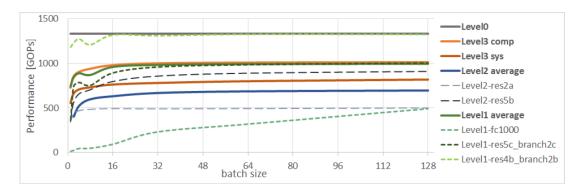

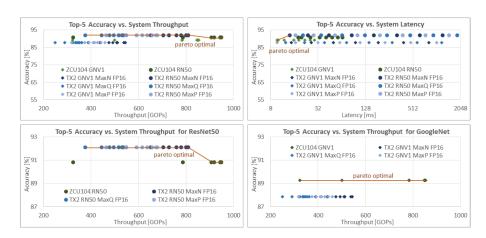

**QuTiBench** [7] is the benchmark proposal in which this work is inserted, so this was the benchmark used in this work. It will be discussed in details later in section 2.9.