## **Durham E-Theses**

## Self-healing concepts involving fine-grained redundancy for electronic systems

SCHIEFER, PHILIPP

#### How to cite:

SCHIEFER, PHILIPP (2016) Self-healing concepts involving fine-grained redundancy for electronic systems, Durham theses, Durham University. Available at Durham E-Theses Online:  $\frac{\text{http:}}{\text{etheses.dur.ac.uk}}$

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# SCHOOL OF ENGINEERING AND COMPUTING SCIENCES South Road, Durham, DH1 3LE, UK

# Self-healing concepts involving fine-grained redundancy for electronic systems

by

**Philipp Schiefer**

A thesis submitted for the

**Degree of Doctor of Philosophy**

## **Abstract**

The start of the digital revolution came through the metal-oxide-semiconductor field-effect transistor (MOSFET) in 1959 followed by massive integration onto a silicon die by means of constant down scaling of individual components. Digital systems for certain applications require fault-tolerance against faults caused by temporary or permanent influence. The most widely used technique is triple module redundancy (TMR) in conjunction with a majority voter, which is regarded as a passive fault mitigation strategy. Design by functional resilience has been applied to circuit structures for increased fault-tolerance and towards self-diagnostic triggered self-healing. The focus of this thesis is therefore to develop new design strategies for fault detection and mitigation within transistor, gate and cell design levels.

The research described in this thesis makes three contributions. The first contribution is based on adding fine-grained transistor level redundancy to logic gates in order to accomplish stuck-at fault-tolerance. The objective is to realise maximum fault-masking for a logic gate with minimal added redundant transistors. In the case of non-maskable stuck-at faults, the gate structure generates an intrinsic indication signal that is suitable for autonomous self-healing functions. As a result, logic circuitry utilising this design is now able to differentiate between gate faults and faults occurring in inter-gate connections. This distinction between fault-types can then be used for triggering selective self-healing responses.

The second contribution is a logic matrix element which applies the three core redundancy concepts of spatial- temporal- and data-redundancy. This logic structure is composed of quad-modular redundant structures and is capable of selective fault-masking and localisation depending of fault-type at the cell level, which is referred to as a spatiotemporal quadded logic cell (QLC) structure. This QLC structure has the capability of cellular self-healing. Through the combination of fault-tolerant and masking logic features the QLC is designed with a fault-behaviour that is equal to existing quadded logic designs using only 33.3% of the equivalent transistor resources. The inherent self-diagnosing feature of QLC is capable of identifying individual faulty cells and can trigger self-healing features.

The final contribution is focused on the conversion of finite state machines (FSM) into memory to achieve better state transition timing, minimal memory utilisation and fault protection compared to common FSM designs. A novel implementation based on content-addressable type memory (CAM) is used to achieve this. The FSM is further enhanced by creating the design out of logic gates of the first contribution by achieving stuck-at fault resilience. Applying cross-data parity checking, the FSM becomes equipped with single bit fault detection and correction.

## **Declaration**

No part of the work described in this thesis has been submitted in support of an application for another degree or qualification to this or any other university or institute of learning.

## **Statement of Copyright**

The copyright of this thesis rests with the author. No quotation from it should be published without the author's prior written consent and information derived from it should be acknowledged.

## **Acknowledgments**

I would like to thank those who made this thesis possible and truly believed in me for the last few years during the course of my PhD. First I would like to say thank you to my doctoral supervisor Professor Alan Purvis. He gave me a great opportunity for conducting my research with freedom and flexibility. I would like to thank my doctoral co-supervisor Doctor Richard McWilliam for his good advice, experiences and friendship. This has been invaluable on both levels academic and personally.

I would like to thank my parents Peter (who could not see the end of this, but whose memory has accompanied me and has given me inspirations) and Lieselotte Schiefer for supporting my vision and being there for me, even in times we do not see eye to eye. My sister Katrin and my uncle Fritz Großmann for their help and support they have given me for fulfilling my ambition. A special thanks towards Dr Friedrich and Ruth Schiefer for helping me in getting a great start into my professional life. Thank you to Bernhard and Else Gaul for leading by example for changing their life to fulfil a life dream despite of the risks it involved.

I would like to thank my friends for their understanding and support through the time of working on my research. The following persons I would like to specially thank: Heiko Jausel for being a friend over the years and his encouragement, even in hard times; Dr Albrecht Carver for showing me that you can conquer the hardest obstacles, personal or professional; Jürgen Böhm for being the same great person, unchanged as I have known you since school.

| Self-healing concepts involving | fine-grained redundancy for electronic systems |

|---------------------------------|------------------------------------------------|

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 | Dedicated to my wife Iris and my Son Max       |

|                                 | for their love and understanding they have     |

|                                 | given me throughout this time and beyond.      |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

| rowing old is mandatory.        | Growing up is optional." – Carroll Bryant      |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

|                                 |                                                |

## **List of Abbreviations:**

μC - micro-controller

ABS - anti-lock break systems (ABS)

ADC - analogue-to-digital converter

ALU - arithmetic logic unit

ASIC - application specific integrated circuit

BB - building block

BISR - built-in self-repair

BIST - built-in self-test

CAD - computer aided design

CAM - content-addressable memory

ccfuse - current sensing and conversion fuse

CCU - central control unit

CISC - complex instruction set computing

CLB - configurable logic blocks

CLS - control logic section

CME - coronal mass ejection

CMOS - complementary metal-oxide-semiconductor

COTS - component of the shelf

CPU - central processing unit

CSP - combined single process

DAC - digital-to-analogue converter

ECC - error correction codes

ECU - electronic control unit

FF - flip-flop

FLB - functional logic block

FPGA - field programmable gate array

FR - fault rate

FSM - finite state machine

IC - input condition

JK-FF - JK-flip-flop

LET - linear energy transfer

LET<sub>TH</sub> - LET threshold

LUT - look-up table

MBU - multibit upset

MCU - multiple-cell upset

MEMS - micro-electro-mechanical systems

MML - memory-mapped logic

PAL - programmable array logic

PCB - printed circuit board

PLA - programmable logic array

PLD - programmable logic device

PROM - programmable read-only memory

QLC - quadded logic cluster

RAM - random access memory

RISC - reduced instruction set computing

ROM - read-only memory

RTR - run-time reconfiguration

SAFR - stuck-at fault resilient

SAH - stuck-at high

SAL - stuck-at low

SBU - single bit upset

SCO - separated combinatorial outputs

SEB - Single event burnout

SEE - single event effect

SEFI - Single event interrupt

SEL - Single event latch up

SET - Single event transient

SEU - Single event upsets

SMD - surface mount devices

SoC - System-on-Chip

SOI - silicon on insulator

SRAM - static random access memory

SRO - separated registered outputs

TMR - triple module redundant

TRS - temporal-redundant systems

VHDL - Verilog hardware description language

## **Table of Contents:**

| Chapter 1: Introduction and Overview                                       |              |

|----------------------------------------------------------------------------|--------------|

| 1.1. Introduction                                                          | 1            |

| 1.2. Problem definition                                                    | 2            |

| 1.3. Objectives                                                            |              |

| 1.4. Framework of this research work                                       | <del>S</del> |

| Chapter 2: Design of electronic systems                                    |              |

| 2.1. Introduction                                                          |              |

| 2.2. Basic structure of an electronic system                               | 8            |

| 2.3. Central logic chip variation for electronic systems                   | Ç            |

| 2.3.1. Microcontroller                                                     | 10           |

| 2.3.2. Application specific integrated circuit                             | 11           |

| 2.3.3. Field programmable gate array                                       | 12           |

| 2.3.4. Mapping logic into memory                                           | 15           |

| 2.3.5. Comparison of the different logic units                             | 16           |

| 2.4. Development of FPGAs                                                  | 19           |

| 2.4.1. SRAM-based FPGAs                                                    | 20           |

| 2.4.2. Antifuse-based FPGAs                                                | 22           |

| 2.4.3. Flash-based FPGAs                                                   | 24           |

| 2.5. Summary of chapter                                                    | 26           |

| Chapter 3: Radiation effects on electronic system components               |              |

| 3.1. Introduction                                                          | 27           |

| 3.2. The sun as source of the radiation effects in electronic systems      | 27           |

| 3.3. History and impact of single event upset effects on electronic system | 29           |

| 3.4. Definition of single event effect                                     | 30           |

| 3.4.1. Types of SEEs                                                       | 31           |

| 3.4.2. Linear energy transfer function                                     | 33           |

| 3.4.3. SEU in relation to sea-level                                        | 33           |

| 3.5. SEE impacts on SRAM-based FPGAs                                       | 34           |

| 3.5.1. SEE impact on configuration data stored in SRAMs                    | 34           |

| 3.5.2. SEE impact on user data stored in SRAM                              | 35           |

| 3.5.3. SEE impact on the user logic                                        | 36           |

| 3.6. Simulation of SEE faults in an electronic system                      | 36           |

| 3.6.1. Simulation-based fault-injection                                    | 38           |

| 3.6.1.1. VHDL-based fault-injection                                        | 38 |

|----------------------------------------------------------------------------|----|

| 3.6.1.2. Fault-injection with means of run-time configuration manipulation | 38 |

| 3.6.1.3. Fault-injection into logic equation                               | 39 |

| 3.6.2. Physical-based fault-injection                                      | 41 |

| 3.6.2.1. Hardware fault-injection                                          | 41 |

| 3.6.2.2. Software fault-injection                                          | 43 |

| 3.7. Summary of the chapter                                                | 44 |

| Chapter 4: Review of type of faults and their behaviour on a system        |    |

| 4.1. Introduction                                                          | 45 |

| 4.2. Impact of chip feature-scaling development on fault-behaviour         |    |

| 4.3. Definition of fault and error in an electronic system                 | 50 |

| 4.4. Faults and errors in an electronic system                             |    |

| 4.5. Types of faults in an electronic system                               |    |

| 4.5.1. Transient faults in an electronic system                            | 52 |

| 4.5.2. Permanent faults in an electronic system                            | 54 |

| 4.5.3. Intermittent faults in an electronic system                         | 55 |

| 4.6. Detection of fault or error occurrence in an electronic system        | 55 |

| 4.6.1. Majority voter at the boundary of a functional block                | 56 |

| 4.6.2. Comparator at the boundary of a functional block                    | 62 |

| 4.7. Summary of the chapter                                                | 64 |

| Chapter 5: Concepts for increasing dependability of logic systems          |    |

| 5.1. Introduction                                                          | 65 |

| 5.2. Fault-tolerant per system design                                      | 65 |

| 5.3. Fault-tolerant approaches based on fault elimination or masking       | 65 |

| 5.3.1. Redundancy concepts in a system                                     |    |

| 5.3.1.1. Spatial redundancy system structure                               | 67 |

| 5.3.1.2. Temporal redundancy system structure                              | 69 |

| 5.3.1.3. Information redundancy data structures                            | 71 |

| 5.3.1.4. Fine-grained redundancy on logic gate level                       | 72 |

| 5.3.2. Reconfiguration concepts in a system                                | 74 |

| 5.3.2.1. Data scrubbing                                                    | 75 |

| 5.3.2.2. Reconfiguration with pre-defined data                             | 75 |

| 5.3.2.3. Tile approach with rotating reconfiguration                       | 76 |

| 5.4. Fault-tolerant approach based on fault-masking                        | 78 |

| 5.5 Fault-tolerant approach based on fault correction                      | 79 |

| 5.6. Summary of the chapter                                                           | 88  |

|---------------------------------------------------------------------------------------|-----|

| Chapter 6: Design of a fault-tolerant temporal-redundant matrix element               |     |

| 6.1. Introduction                                                                     | 90  |

| 6.2. A fault-tolerant temporal-redundant structure                                    |     |

| 6.3. Design of a fault-tolerant temporal-dependent reconfigurable round-robin element |     |

| 6.4. Fault-handling capability of QLC compared against quadded logic structures       |     |

| 6.4.1. Fault-handling evaluation of quadded logic vs. QLC, both without voter         |     |

| 6.4.2. Fault-handling evaluation of quadded logic vs. QLC, both with voter            |     |

| 6.4.3. Overview of simulation results of the different systems                        |     |

| 6.5. Summary of the chapter                                                           |     |

| Chapter 7: Design of a fault-tolerant logic gate                                      |     |

| 7.1. Introduction                                                                     | 120 |

| 7.2. A fault-tolerant logic gate                                                      |     |

| 7.2.1. Comparing of logic gates responses under the influence of fault-injection      |     |

| 7.2.2. Identifying the functionality of a fault-tolerant logic gate                   | 125 |

| 7.2.3. Design of a fault-tolerant NAND logic gate                                     | 127 |

| 7.2.4. Validation of the optimised fault-tolerant NAND logic gate                     |     |

| 7.2.5. Scalability of optimised fault-tolerant NAND logic gate                        | 135 |

| 7.3. Alteration of other fundamental logic gates according to design specification    | 138 |

| 7.4. Converting standard logic circuits into fault-tolerant logic circuits            | 139 |

| 7.4.1. Comparing a 2-bit full adder design implementation                             | 139 |

| 7.4.2. Comparing a C17 circuit design implementation                                  | 141 |

| 7.4.3. Comparing a three input majority voter circuit design implementation           | 142 |

| 7.5. Converting the logic unit of the QLC into using SAFR type logic gates only       | 144 |

| 7.6. Summary of the chapter                                                           | 146 |

| Chapter 8: Mapping FSM functionality into memory                                      |     |

| 8.1. Introduction                                                                     | 148 |

| 8.2. Principle of FSM architecture                                                    | 149 |

| 8.3. Objective of mapping FSM logic functionality into memory                         | 152 |

| 8.4. Mapping of a FSM logic functionality into memory                                 | 154 |

| 8.4.1. Mapping a JK-flip-flop into memory                                             |     |

| 8.4.2. Mapping of an FSM into memory LUT                                              |     |

| 8.4.3. Comparison between memory LUT and PLD                                          |     |

| 8.5. Comparison of different memory LUT concepts                                      | 163 |

| 8.5.1. Creating a fault-tolerant CAM circuit concept                                     | 165 |

|------------------------------------------------------------------------------------------|-----|

| 8.5.2. Protecting data memory inside CAMs against SEUs                                   | 167 |

| 8.6. Summary of the chapter                                                              | 169 |

| Chapter 9: Design of self-healing logic structure                                        |     |

| 9.1. Introduction                                                                        | 170 |

| 9.2. A self-healing fine grained logic structure                                         | 171 |

| 9.2.1. Concepts for fault self-detection with the SAFR-NAND gate                         | 173 |

| 9.2.2. Initiation of self-healing of a circuit designed out of SAFR-NAND gates           | 177 |

| 9.2.3. Initiation of self-healing at SAFR-NAND gate with reconfiguration                 | 185 |

| 9.3. Fault identification capabilities within the QLC logic structure                    | 190 |

| 9.4. Circuit interconnection fault-localisation through memory-based BIST functionality_ | 196 |

| 9.5. Summary of the chapter                                                              | 203 |

| Chapter 10: Conclusions and further work                                                 |     |

| 10.1. Conclusions                                                                        | 205 |

| 10.2. Further work                                                                       |     |

| References                                                                               | 211 |

| Appendix 1: Publications                                                               | 221            |

|----------------------------------------------------------------------------------------|----------------|

| Appendix 2: Example of FR calculation for SAH and SAL fault injection into a X         | OR logic gate  |

| structure in accordance with Figure 5.9(a)                                             | 222            |

| Appendix 3.1: MATLAB program for Chapter 4 for the FR generation data of the           | najority voter |

| under the influence of stuck-at fault injected at specified injection points           | 223            |

| Appendix 3.2: MATLAB program for Chapter 5 for the FR generation data of the           | logic circuits |

| XOR-gate and quadded logic version of the XOR function under the influence of          | stuck-at fault |

| injected at specified injection points                                                 | 224            |

| Appendix 3.3: MATLAB program for Chapter 6 for the FR generation data of the           | comparison of  |

| the fault-behaviour of the generic logic gate structure and the QLC structure under th | e influence of |

| stuck-at fault injected at specified injection points                                  | 226            |

| Appendix 3.4: MATLAB program for Chapter 7 for the purpose of analysing the fa         | ault behaviour |

| of the QLC structure                                                                   | 232            |

| Appendix 4: Spice simulation circuit of SAFR-logic gates                               | 238            |

| Appendix 5: Fault results of the fault simulation in accordance of logic gate al       | teration for a |

| certain selection of eight transistor-style variation                                  | 240            |

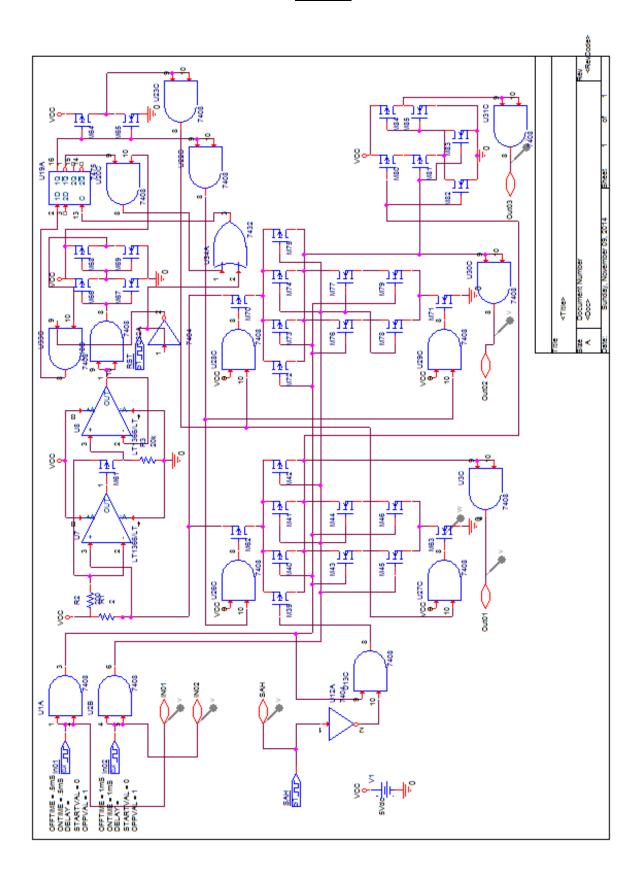

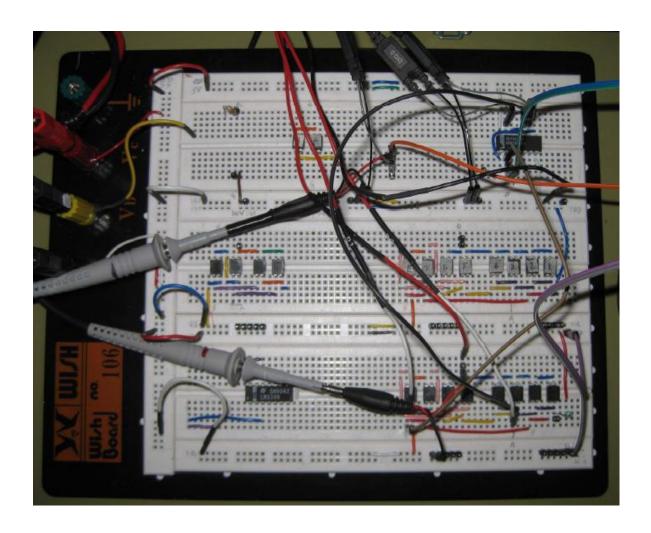

| Appendix 6: Breadboard of the SAFR-NAND gate design                                    | 243            |

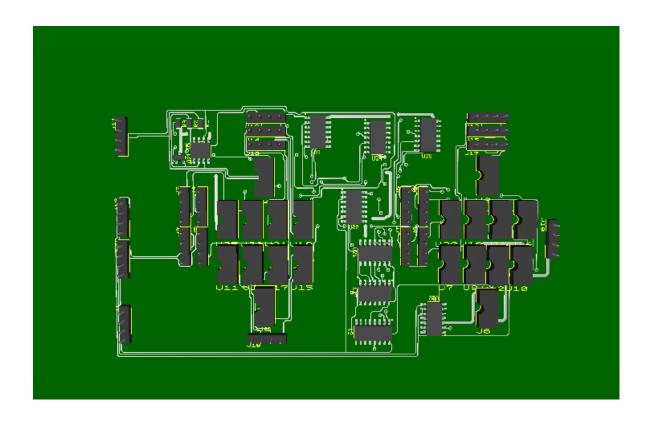

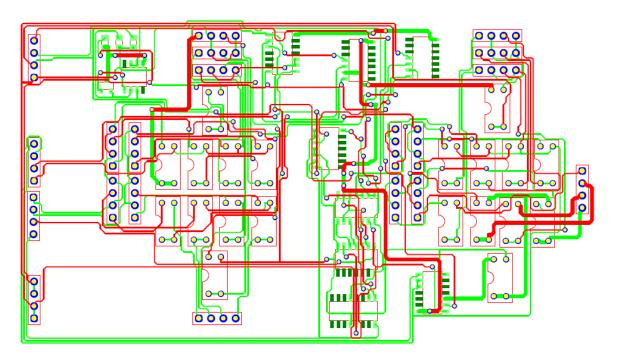

| Appendix 7: PCB design of self-healing SAFR-NAND gate                                  | 244            |

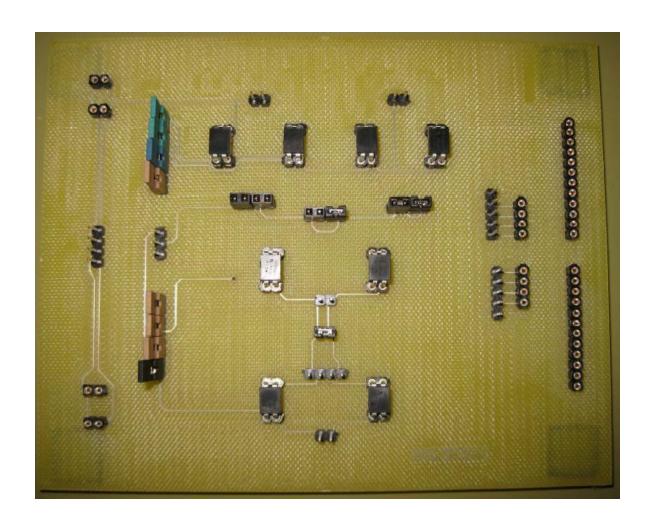

| Appendix 8: Circuit board design of the SAFR-NAND gate                                 | 245            |

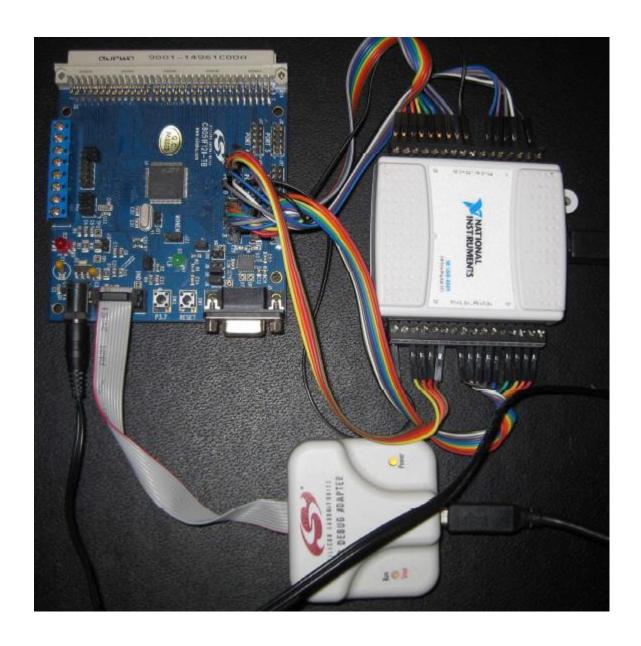

| Appendix 9: 8051 set-up for the simulation of the soda machine FSM                     | 246            |

| Appendix 10: Assembler code for the FSM soda machine                                   | 247            |

## **List of Figures and Tables:**

| Figure 1.1: (left) Coronal mass ejection and (right) multiple solar flares [1]                         | 3        |

|--------------------------------------------------------------------------------------------------------|----------|

|                                                                                                        |          |

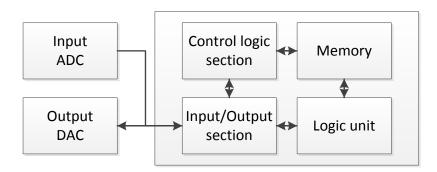

| Figure 2.1: Basic block diagram of an ECU with the central block of an ECU containing con              | ıtrol    |

| logic section, memory, input/output section and logic unit                                             | 8        |

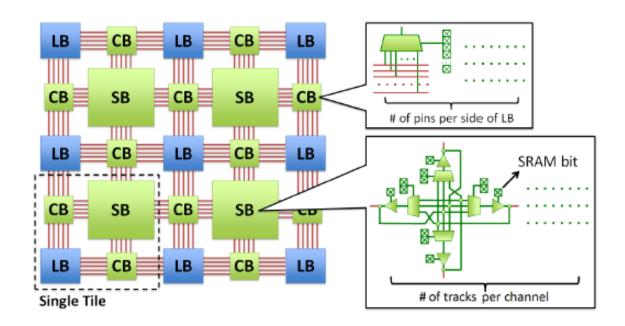

| Figure 2.2: SRAM-based FPGA with two connection blocks (CB), one switch block (SB), or                 | ne       |

| <del>-</del>                                                                                           |          |

| logic block (LB) forming a single tile [2]                                                             | 13       |

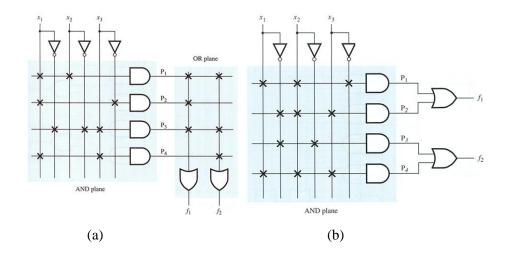

| <b>Figure 2.3:</b> (a) PLA and (b) PAL architectures of the internal section structure [3, 4]          | 13       |

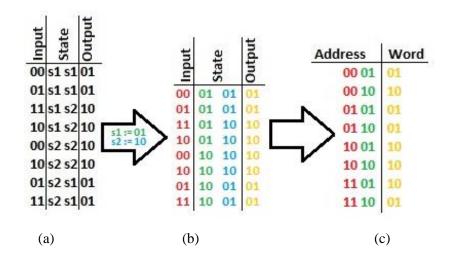

| Figure 2.4: JK-flip-flop state transition table transformation into memory; (a) state transition       | ı table; |

| (b) state transition table including coded replacement of states and can be seen as a trues table      | le; (c)  |

| memory data created out of data from (b)                                                               |          |

|                                                                                                        |          |

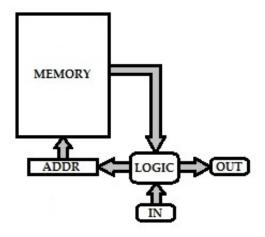

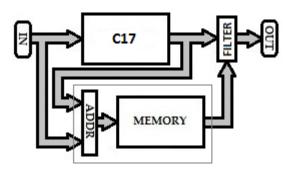

| Figure 2.5: Block diagram of a memory-mapped FSM                                                       | 16       |

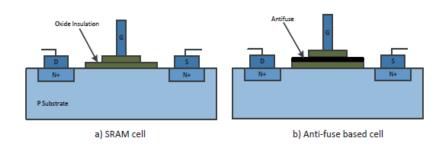

| Figure 2.6: SRAM or static RAM cell structure for programming one bit [5]                              | 20       |

|                                                                                                        |          |

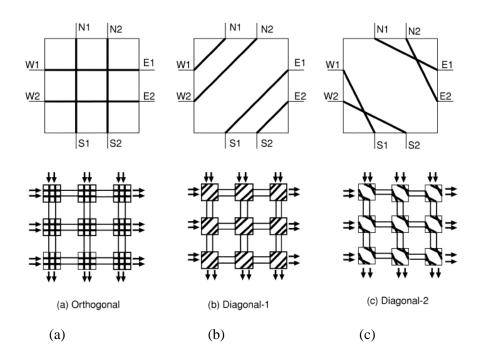

| <b>Figure 2.7:</b> Example of possible interconnection switching configuration; (a) orthogonal, (b)    | one      |

| type of diagonal, (c) another type of diagonal interconnection [6]                                     | 21       |

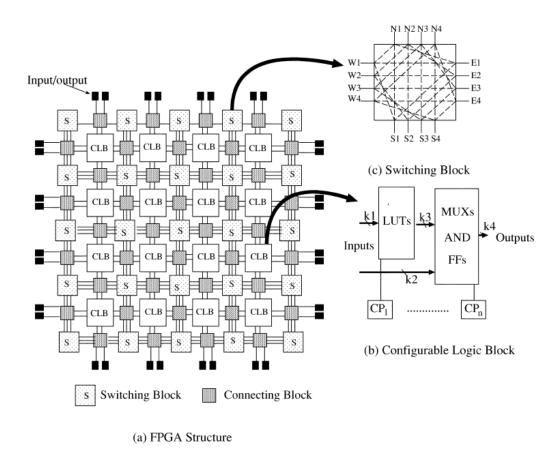

| <b>Figure 2.8:</b> (a) Block diagram of a SRAM based 4x4 CLB element structure with interconne         | ection   |

| elements building the FPGA structure; (b) block diagram of the inside of a configurable logic          | c block  |

| (CLB) [6]                                                                                              |          |

| (CED) [0]                                                                                              |          |

| Figure 2.9: (a) SRAM vs. (b)Antifuse-based programmable switch of an FPGA [5]                          | 23       |

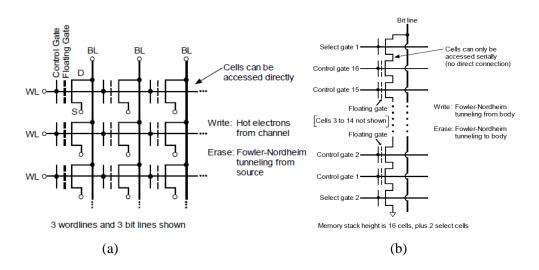

| Figure 2.10: Call prohitoeture for NOP (a) and NAND (b) gate design [7]                                | 24       |

| Figure 2.10: Cell architecture for NOR (a) and NAND (b) gate design [7]                                |          |

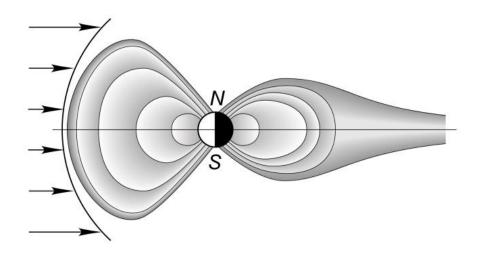

| Figure 3.1: Solar wind and Earth 's magnetic field interaction [8]                                     | 28       |

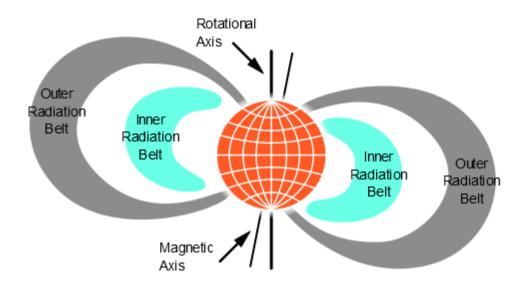

| Figure 3.2: Van Allen radiation belts of the Earth magnetic field [9]                                  | 29       |

| <b>3</b>                                                                                               |          |

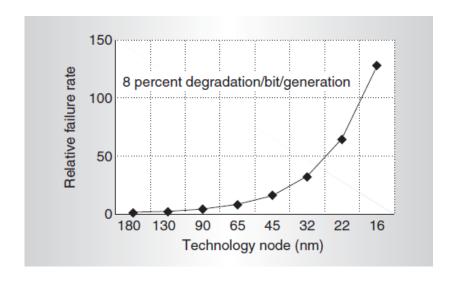

| <b>Figure 3.3:</b> Soft-error rate per chip generation (logic and memory structure included) [10]      | 30       |

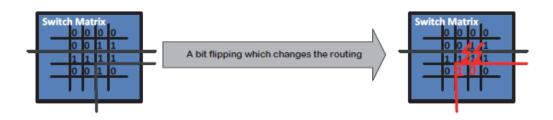

| <b>Figure 3.4:</b> SEE-induced alteration of the interconnection within a switching matrix [5]         | 35       |

| 2                                                                                                      |          |

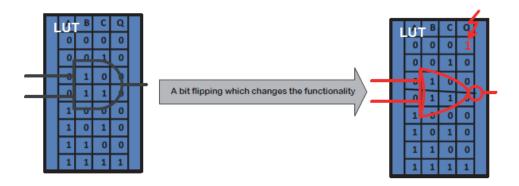

| <b>Figure 3.5:</b> SEE alteration of the stored logic function data to another logic functionality [5] | 36       |

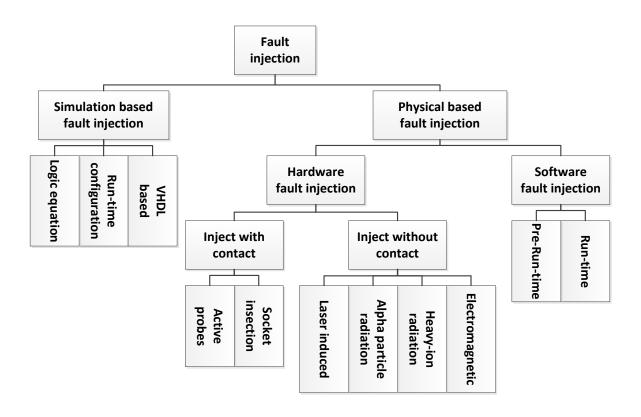

| Figure 3.6: Overview of fault-injection methods [11]                                                       |

|------------------------------------------------------------------------------------------------------------|

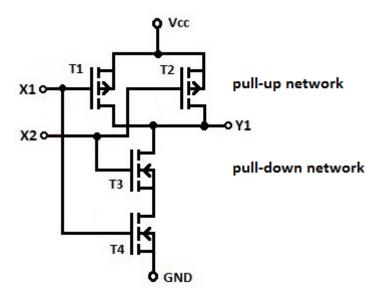

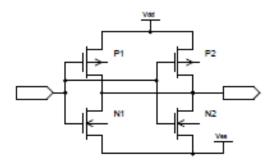

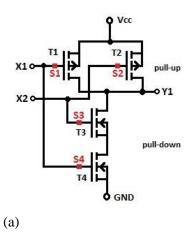

| Figure 3.7: Circuit layout of a standard NAND gate with identification of pull-up and pull-down            |

| network 39                                                                                                 |

| Figure 3.8: Some possible electronic faults in a transistor with regard to open connection or shorts       |

| between two pins [12] 41                                                                                   |

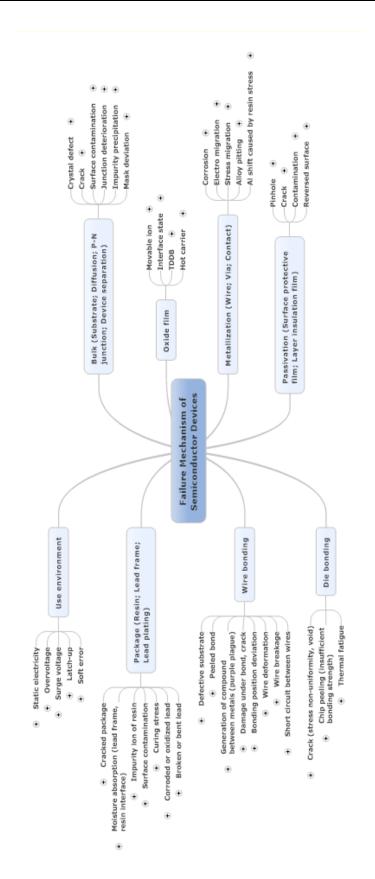

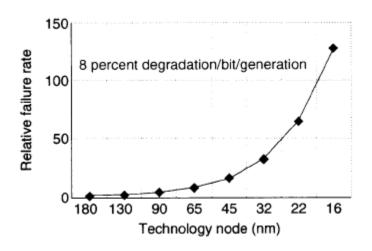

| <b>Figure 4.1:</b> Overview of possible failure mechanisms of semiconductor devices [13-15] 47             |

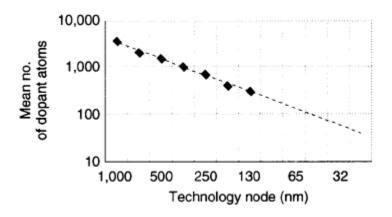

| <b>Figure 4.2:</b> Graph of the random dopant fluctuation due to feature size reduction [16] 48            |

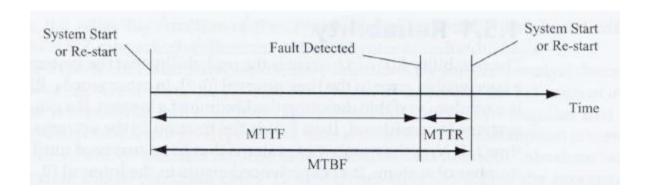

| <b>Figure 4.3:</b> Mean time of failure-type definition within a system [17]                               |

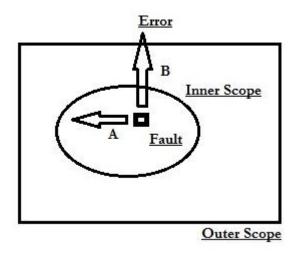

| <b>Figure 4.4:</b> Fault propagation within system [17] 52                                                 |

|                                                                                                            |

| <b>Figure 4.5:</b> Soft-error failure-in-time of a chip (logic and memory) [10]                            |

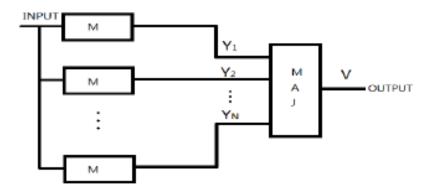

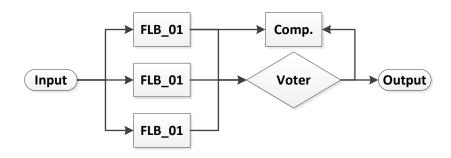

| <b>Figure 4.6:</b> Majority voter block diagram for an NMR system [18] 56                                  |

|                                                                                                            |

| <b>Figure 4.7:</b> Conventional triple module redundant (TMR) majority voter logic circuit created out     |

| of single logic gates 57                                                                                   |

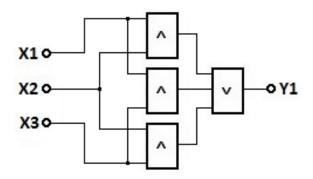

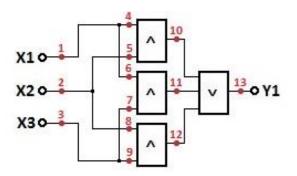

| <b>Figure 4.8:</b> Conventional TMR majority voter logic circuit with stuck-at simulation points (1 to 13) |

|                                                                                                            |

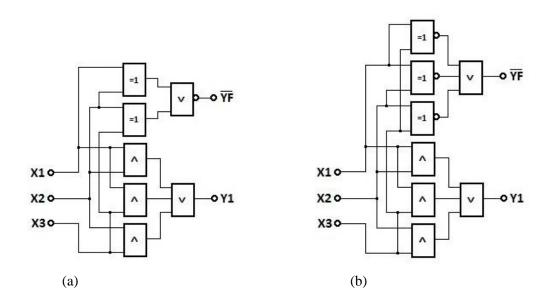

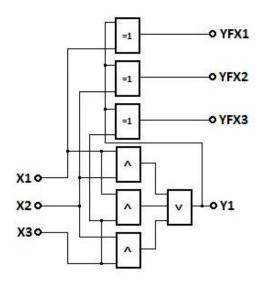

| Figure 4.9: TMR majority voter with fault indicator circuit for the case that inputs are                   |

| homogenous. (a) for homogenous of all inputs, (b) for homogenous of two out of three 60                    |

| Figure 4.10: TMR majority voter with output fed-back comparator against inputs for identifying             |

| faulty input path61                                                                                        |

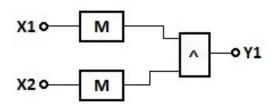

| Figure 4.11: Dual redundancy electronic system with AND-gate as a comparator at the output 62              |

|                                                                                                            |

| Figure 4.12: Dual redundancy electronic system with AND gate comparator and XOR gate as faul indicator 63  |

|                                                                                                            |

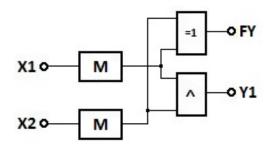

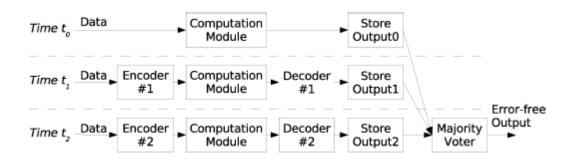

| <b>Figure 5.1:</b> Timing sequence of the encoding/decoding approach of the permanent fault-masking        |

| temporal redundancy structure [19] 70                                                                      |

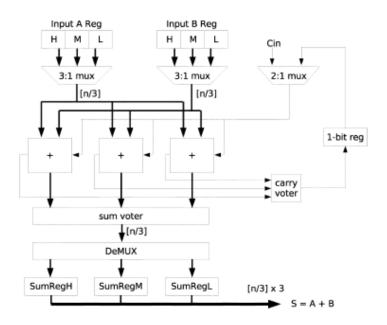

| Figure 5.2: TSTMR error correcting adder [19] 71                                                           |

|                                                                                                            |

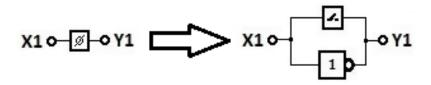

| <b>Figure 5.3:</b> Best evolved SAL resilient inverter gate [20, 21] 73                                    |

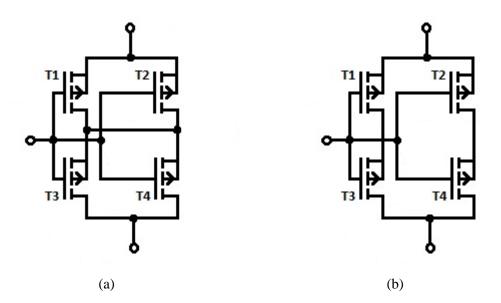

| <b>Figure 5.4:</b> The two possible replacement quadded transistor structures for a single transistor of | of a                                      |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------|

| common logic gate [22]; (a) with and (b) without cross bridge                                            | 74                                        |

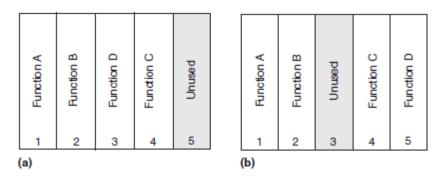

| Figure 5.5: Column-based precompiled individual functional blocks. The fault-free configurat             | tion                                      |

| is displayed in (a) and an altered configuration after a fault is shown in (b) [23, 24]                  | 76                                        |

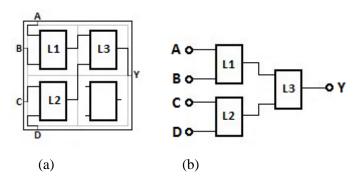

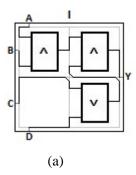

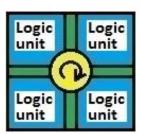

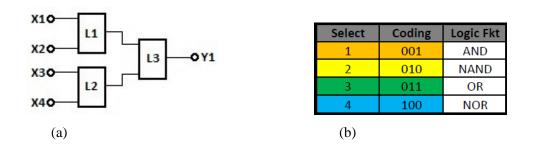

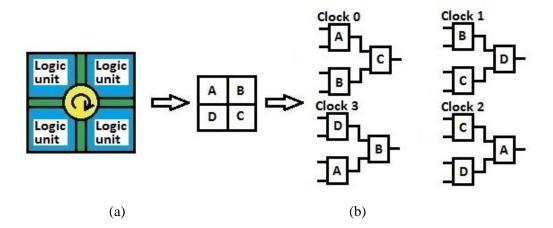

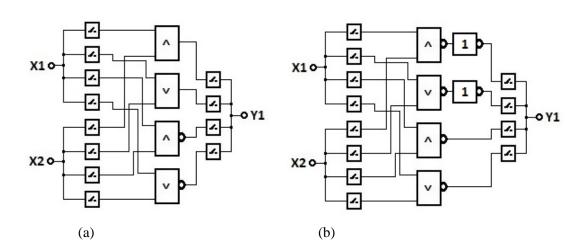

| Figure 5.6: (a) Logic cell with four logic units in accordance with [25]; (b) Internal logic structures  | cture                                     |

| created out of the three logic gates                                                                     |                                           |

| Figure 5.7: Clockwise reconfiguration of the internal circuit structure for maintaining the requ         | iired                                     |

| Boolean function [25]                                                                                    |                                           |

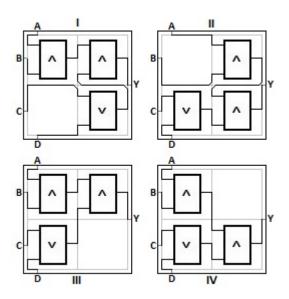

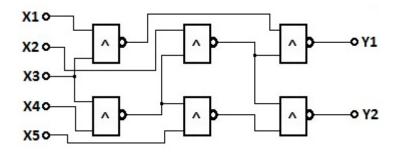

| Figure 5.8: XOR logic gate design in (a) standard logic gate structure and (b) quadded logic g           |                                           |

|                                                                                                          |                                           |

| Figure 5.9: XOR gate design in (a) standard gate structure and (b) quadded gate structure both           |                                           |

| with specific defined stuck-at fault-injection points                                                    | 83                                        |

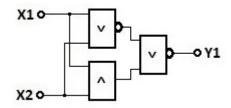

| Figure 5.10: XOR logic gate design in standard gate structure with altered output logic gate             |                                           |

| different from Figure 5.8(a)                                                                             | 86                                        |

| Figure 6.1: (a) Matrix structure divided into tiles which can be localised reconfigured in the ca        | ase                                       |

| of a fault within a single tile [25]; (b) A reconfigurable logic block between fixed interconnect        |                                           |

| points for maintaining a logic functionality in the case of a fault within a functional block [26].      |                                           |

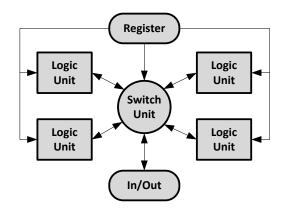

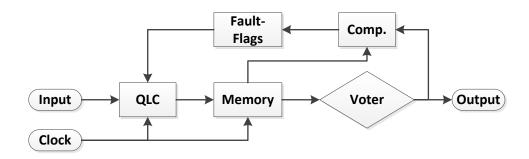

| Figure 6.2: Functional block diagram of the temporal-dependent reconfigurable round-robin                |                                           |

| matrix element                                                                                           | 96                                        |

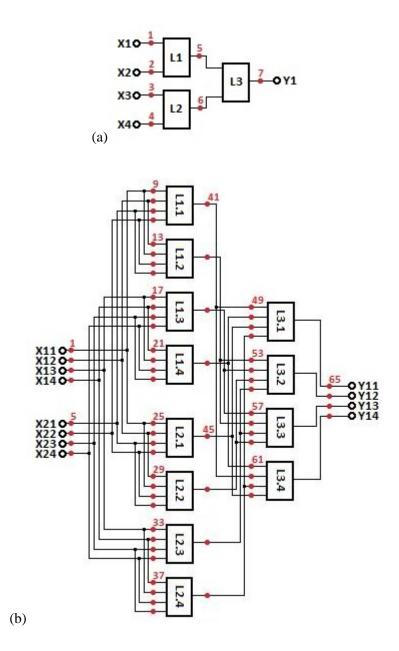

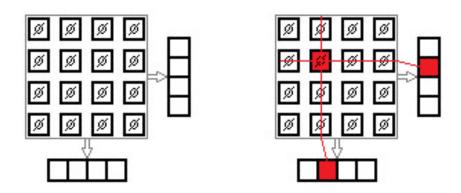

| Figure 6.3: General block diagram of the quadded logic cluster                                           | 97                                        |

| righte 6.5. General block diagram of the quadded logic cluster.                                          | <u>/                                 </u> |

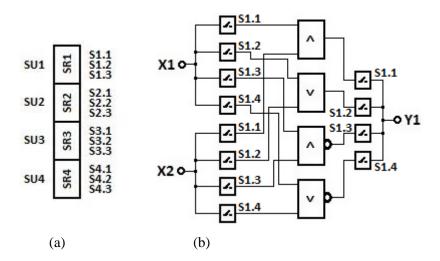

| Figure 6.4: Functional blocks of the QLC matrix element; (a) the shift-register which controls           | the                                       |

| selection of logic units and the selection of the logic gate functionality; (b) internal structure of    | f                                         |

| logic unit with switches for selecting logic gate functionality                                          | 98                                        |

| Figure 6.5: (a) Internal logic gate combination of the QLC per one clock cycle; (b) Logic fund           | ction                                     |

| corresponding to the required selection                                                                  |                                           |

| Figure 6.6: (a) Block diagram of QLC with labelled logic units, (b) configuration of logic unit          | ts in                                     |

| conjunction to round-robin clock                                                                         | .s III<br>99                              |

|                                                                                                          |                                           |

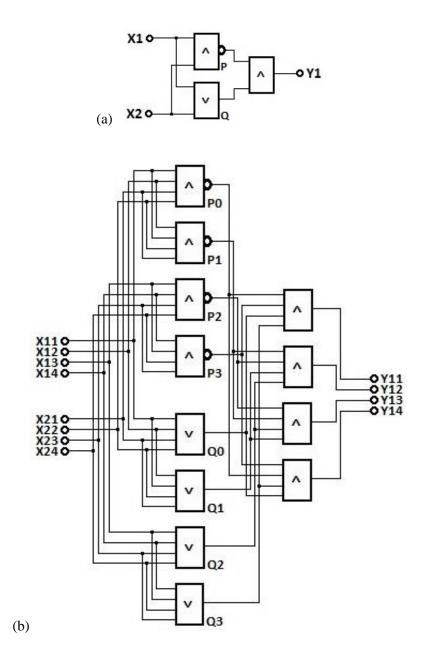

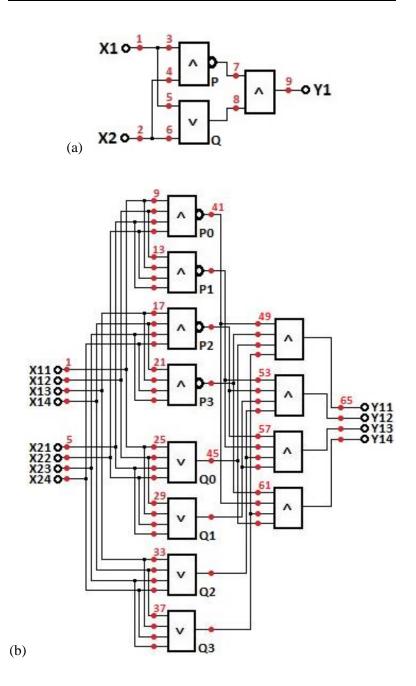

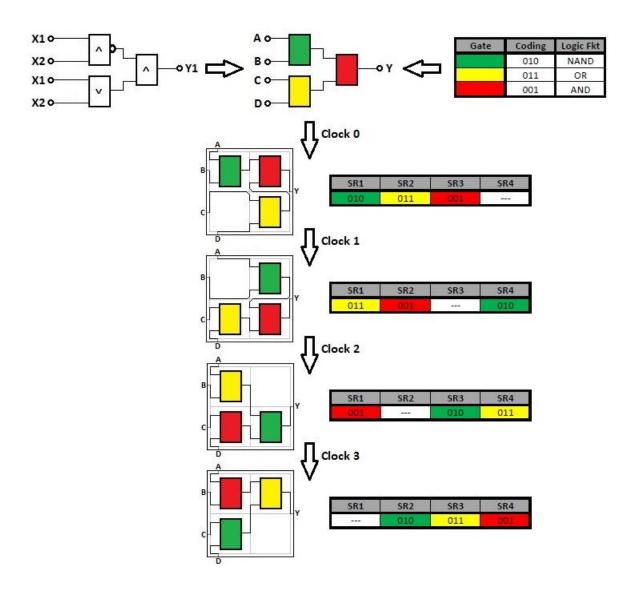

| Figure 6.7: Detailed example of the mapping of a XOR logic function onto the QLC e                                                                                                                                                                                         | elements and   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| shift-register details for the full round-robin cycle                                                                                                                                                                                                                      | 100            |

| <b>Figure 6.8:</b> (a) Shows the logic gate configuration for logic function alteration and far points at the inputs and outputs of each logic gate; (b) shows the same as (a) but for the                                                                                 | •              |

| logic structure                                                                                                                                                                                                                                                            | 103            |

| Figure 6.9: Fault-injection points at the logic structure of a logic unit excluding the swinterconnection between the logic gates                                                                                                                                          |                |

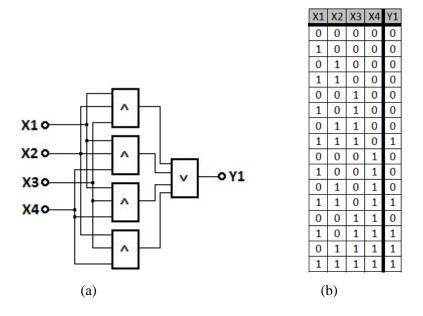

| Figure 6.10: (a) four-input voter circuit; (b) truth table of the four-input majority vote                                                                                                                                                                                 | r <u>112</u>   |

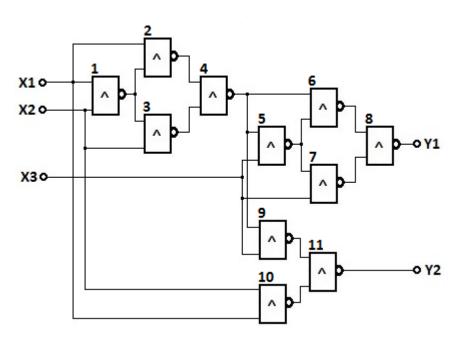

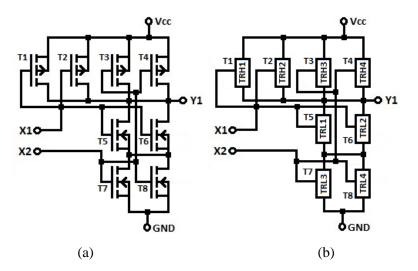

| <b>Figure 7.1:</b> Analysing the behaviour of a NAND gate under the influence of stuck-at a definition of the fault-injection points at input and output pins; (b) output results of the                                                                                   | NAND gate      |

| under the influence of stuck-at faults                                                                                                                                                                                                                                     | 122            |

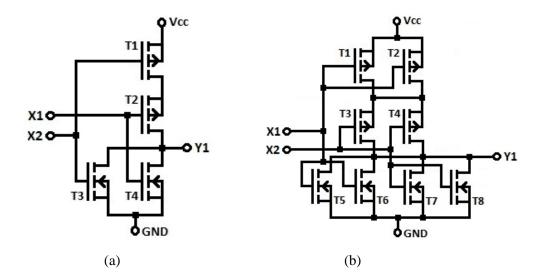

| <b>Figure 7.2:</b> Simulation results of Spice simulation of NAND gate with stuck-at fault-individual transistors; (a) definition of the fault-injection points at each transistor; (b) of the NAND gate under the influence of stuck-at faults                            | output results |

| <b>Figure 7.3:</b> SAL fault-tolerant inverter proposed in [20]; (a) circuit structure of SAL finverter with injection points; (b) output results of the INV gate under the influence of faults                                                                            | stuck-at       |

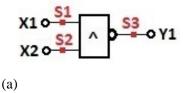

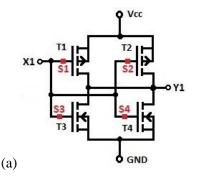

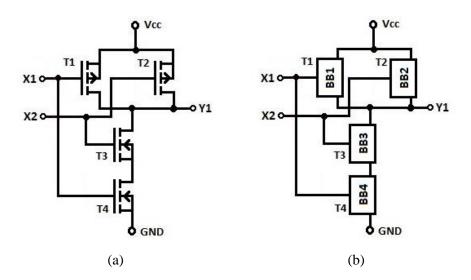

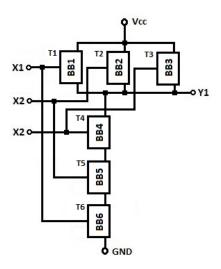

| Figure 7.4: (a) Standard NAND gate structure; (b) NAND gate with replaced to building blocks (BB)                                                                                                                                                                          |                |

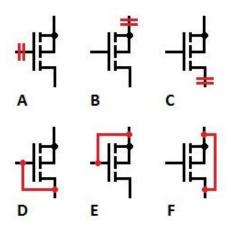

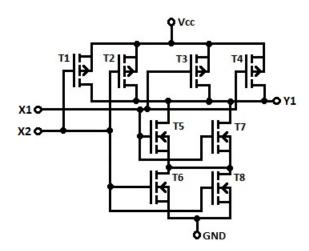

| <b>Figure 7.5:</b> All variations of transistor redundancy structures done for incremental incremental transistors performed up to quadded transistor structure                                                                                                            |                |

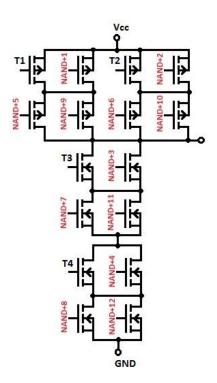

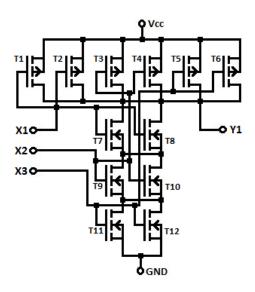

| <b>Figure 7.6:</b> Single stuck-at fault resilient (SAFR) NAND gate design as a result of the fault-injection simulation data is displayed in Table 7.3                                                                                                                    | -              |

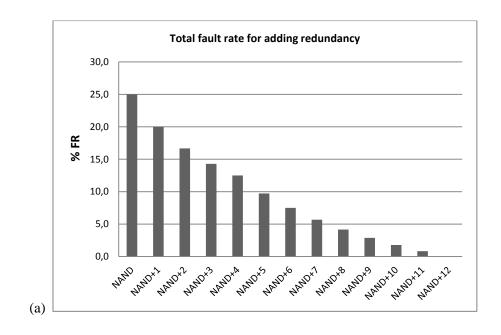

| <b>Figure 7.7:</b> NAND gate with increased redundancy by NAND+1 until NAND+12                                                                                                                                                                                             | 133            |

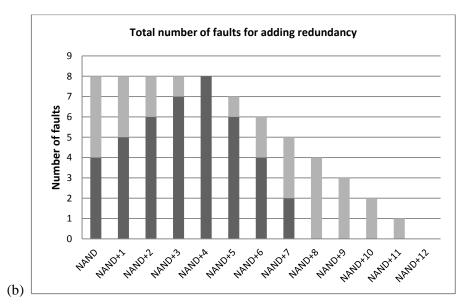

| <b>Figure 7.8:</b> (a) FR analysis for the standard NAND gate with increased addredundancy. (b) Total number of faults broken down into state three and fourth per increases transistor redundancy (The bar is split into top part logic state three and bottom per face). | creased added  |

| <b>Figure 7.9:</b> Increasing two input NAND gate with BB to a three input version                                                                                                                                                                           | 136     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 7.10: Three input optimised NAND gate resilient to SAL faults                                                                                                                                                                                         | 137     |

| Figure 7.11: (a) Standard NOR logic gate; (b) optimised NOR gate resilient to SAL faults                                                                                                                                                                     | 139     |

| <b>Figure 7.12:</b> Logic gate circuit of a full 2-bit adder constructed only out of NAND log designs                                                                                                                                                        |         |

| Figure 7.13: C17 test circuit out of the ISCAS-85 benchmark circuit library [27]                                                                                                                                                                             | 141     |

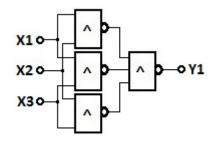

| Figure 7.14: Majority voter constructed out of NAND gate                                                                                                                                                                                                     | 143     |

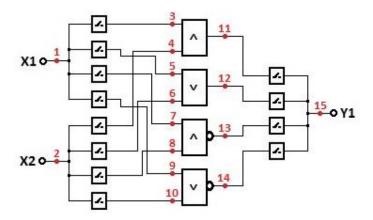

| <b>Figure 7.15:</b> (a) Logic unit design done out of standard logic gates; (b) Logic unit adapted t with SAFR-type logic gates                                                                                                                              |         |

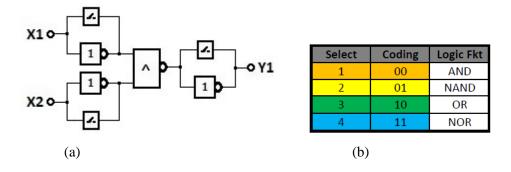

| <b>Figure 7.16:</b> (a) Optimised logic unit towards minimal logic gate use and minimal coding be Coding table for the selection of required logic function of the minimal hardware requiring unit.                                                          | g logic |

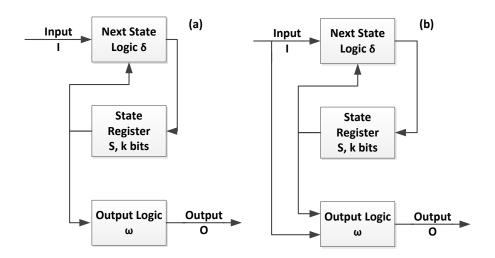

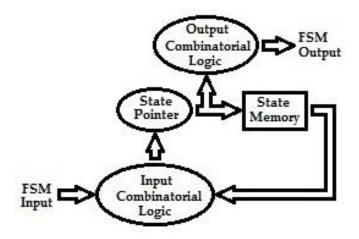

| Figure 8.1: (a) Block diagram of a Moore-based FSM; (b) Block diagram of a Mealy-base [28]                                                                                                                                                                   |         |

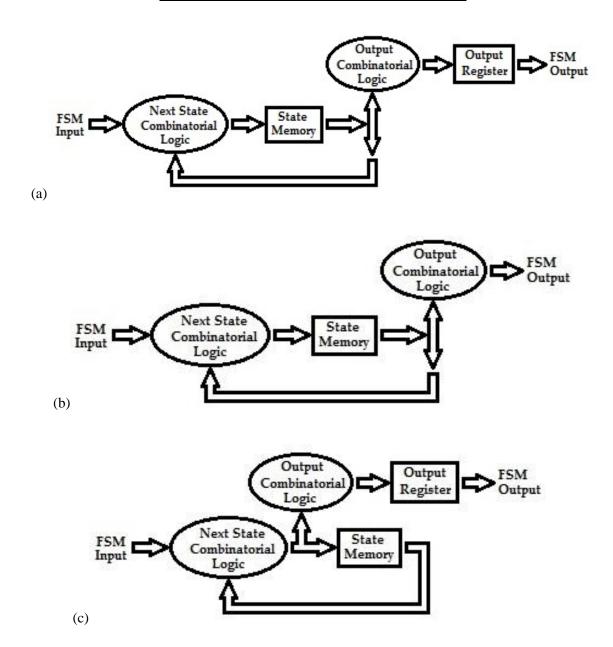

| <b>Figure 8.2:</b> (a) state diagram of a JK-FF; (b) truth table of the JK-FF                                                                                                                                                                                | 151     |

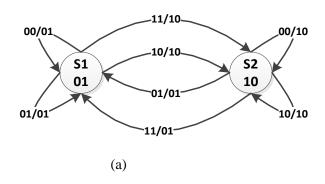

| <b>Figure 8.3:</b> Demonstration of the three different coding style within block diagrams (a) style combined single process (CSP); (b) Coding style state-separated combinatorial (SCO); (c) Coding style state-separated registered outputs (SRO) [29, 30] | output  |

| Figure 8.4: Block diagram of the memory-based FSM structure [30]                                                                                                                                                                                             | 153     |

| <b>Figure 8.5:</b> Shows the state information required for the JK-FF FSM (a) state diagram of a (b) state table of a JK-FF                                                                                                                                  |         |

| <b>Figure 8.6:</b> The state transition table of the JK-FF is transformed into a memory-usable tab memory-based FSM adaptation [31]; (a) state table; (b) state table with binary-code replacement; (c) memory LUT information                               | d state |

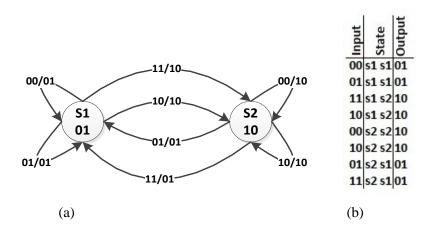

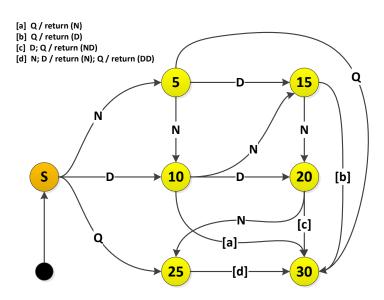

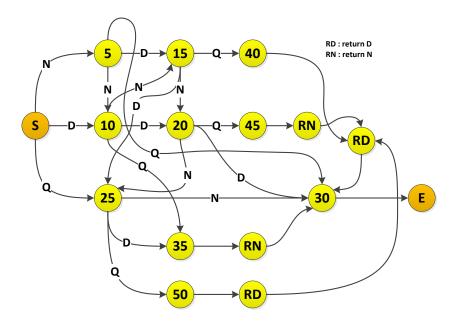

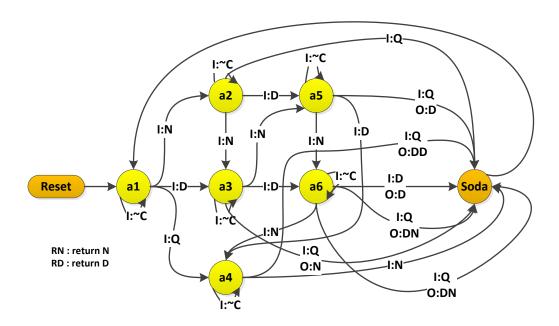

| Figure 8.7: FSM state diagram of the soda machine [32]                                                                                                                                                                                                       | 157     |

| Figure 8.8. Ontimised FSM state diagram of the soda machine [30]                                                                                                                                                                                             | 158     |

| Figure 8.9: State diagram of the soda machine with definition of all input stimuli a               | nd output   |

|----------------------------------------------------------------------------------------------------|-------------|

| functions per state transactions as required for the state diagram                                 | 159         |

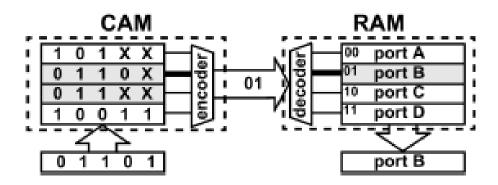

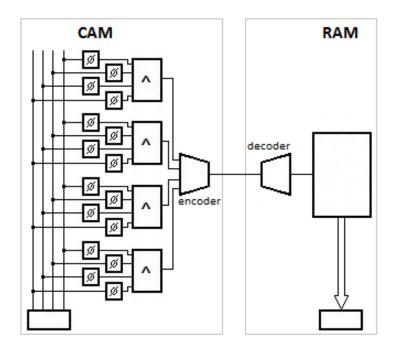

| Figure 8.10: CAM based implementation of a content-related search system out of [33]               | 164         |

| Figure 8.11: Fault-tolerant CAM block diagram                                                      | 166         |

| Figure 8.12: Block diagram of the programmable inverter                                            | 166         |

| Figure 8.13: Concept of identification of a single data-bit alteration within a stored data n      | natrix of a |

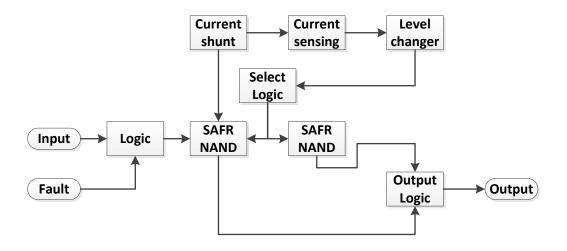

| CAM circuit                                                                                        | 168         |

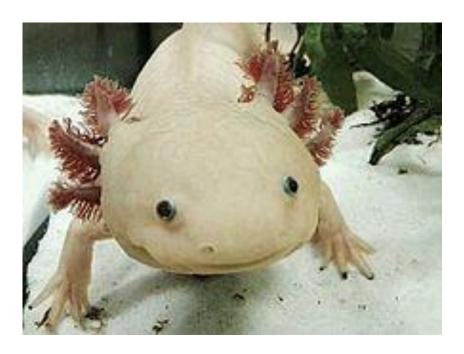

| Figure 9.1: Axolotl (ambystoma mexicanum) [34]                                                     | 173         |

| Figure 9.2: (a) Internal transistor structure of SAFR-NAND gate; (b) SAFR-NAND gate                | converted   |

| from transistor into variable resistors structure                                                  | 174         |

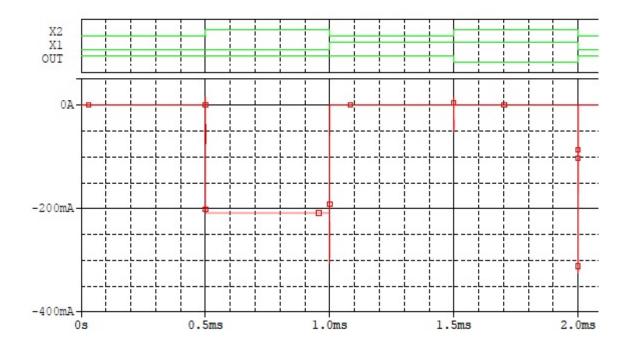

| Figure 9.3: Current response of the SAFR-NAND gate with the presence of a single SA                | H fault at  |

| T6 transistor (see Figure 9.2(a)) and required input stimulus                                      | 176         |

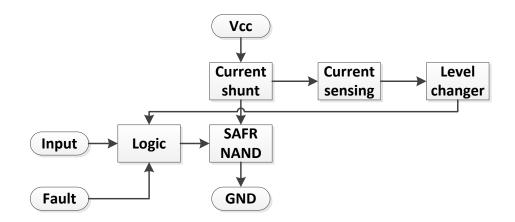

| Figure 9.4: Block diagram of the SAFR-NAND gate simulating a SAH fault-injection a                 | nd ccfuse   |

| fault-clearing capability                                                                          | 179         |

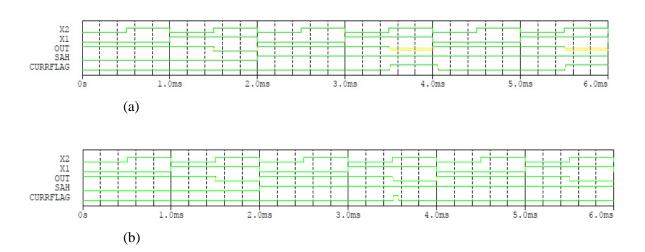

| Figure 9.5: (a) SAFR-NAND gate with SAH fault at T3 without self-healing capabilities              | es; (b) the |

| same condition as in (a) including this time self-healing capabilities for fault correction        | 180         |

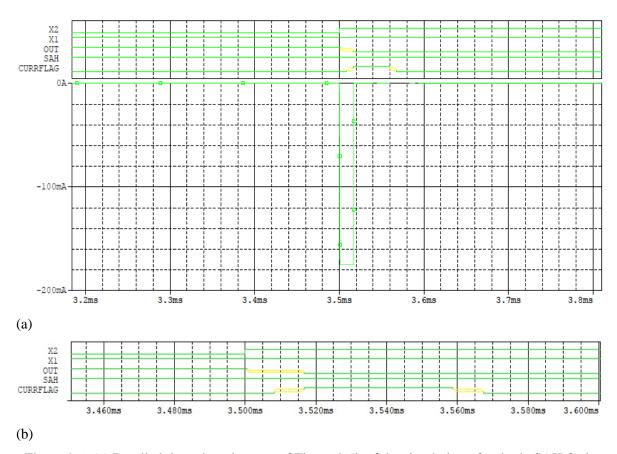

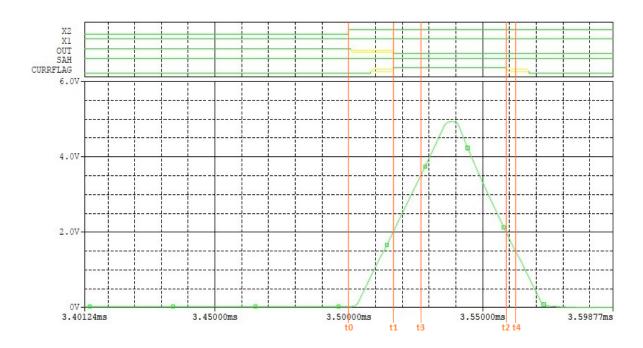

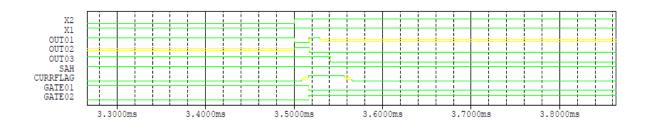

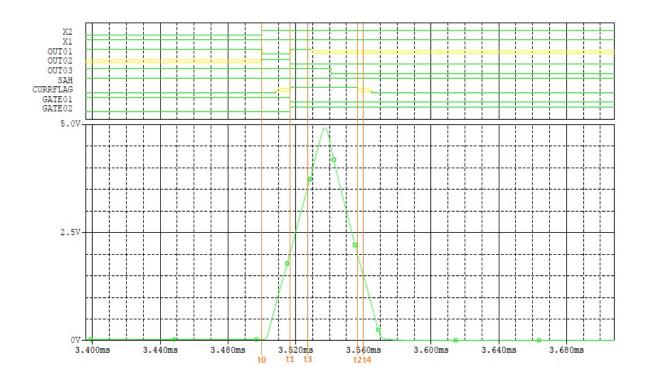

| <b>Figure 9.6:</b> (a) Detailed time slot taken out of Figure 9.5b of the simulation of a single S | SAH fault   |

| at T3 of an SAFR-NAND gate with self-healing capabilities for fault correction; (b) Hi             | gher time   |

| frame resolution of the digital signals of the self-healing phase                                  | 182         |

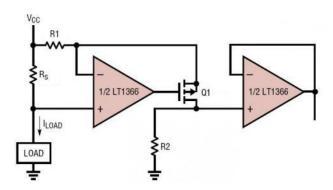

| Figure 9.7: Standard positive supply rail current-sensing circuit taken out of [35]                | 183         |

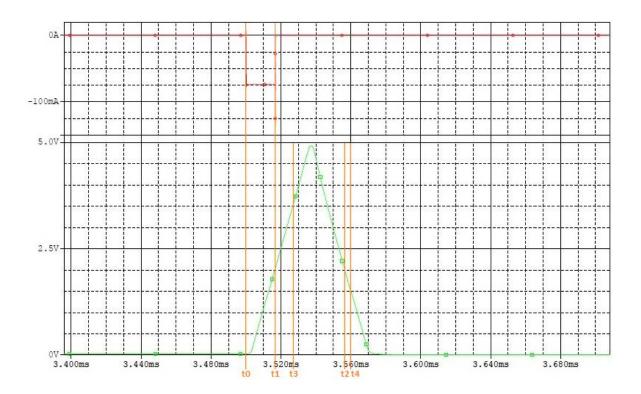

| Figure 9.8: Output voltage graph of the supply rail current sensing in relationship to t           | he digital  |

| signals of the self-healing phase                                                                  | 184         |

| Figure 9.9: Output voltage graph of the supply rail current-sensing circuit in relationship        | to the Iddq |

| current of the SAFR-NAND logic gate                                                                | 185         |

| Figure 9.10: Block diagram of Iddq current triggered self-healing of the system performa           | nce in the  |

| case of the presences of a SAH fault by means of reconfiguration                                   | 187         |

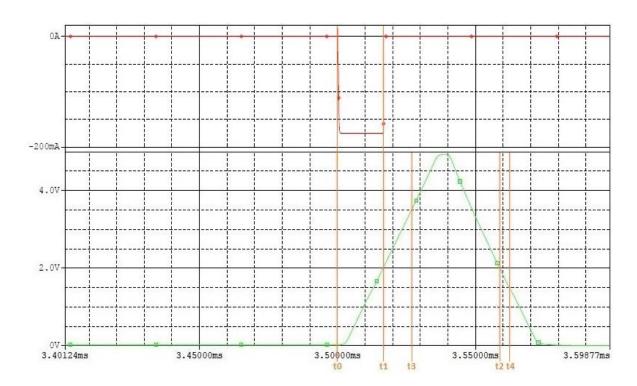

| $\textbf{Figure 9.11:} \ \ \textbf{Self-initiated switchover between two SAFR-NAND gates triggered through the } \ \ \textbf{Iddq}$                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| current for maintaining functionality after SAH fault occurred 188                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                            |

| Figure 9.12: Timing diagram of the self-initiated switchover between two SAFR-NAND gates                                                                                                                                                                                   |

| triggered through the I <sub>ddq</sub> current for maintaining functionality after SAH fault occurred 189                                                                                                                                                                  |

| Figure 0.12. Output values areals of the complement asserts in relationship to the digital                                                                                                                                                                                 |

| Figure 9.13: Output voltage graph of the supply rail current sensing in relationship to the digital                                                                                                                                                                        |

| signals of the self- initiated switchover between two SAFR-NAND gates triggered through the Iddq                                                                                                                                                                           |

| current for maintaining functionality after SAH fault occurred                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                            |

| Figure 9.14: Output voltage graph of the supply rail current sensing circuit in relationship to the                                                                                                                                                                        |

| $\label{eq:current} \textit{Iddq} \; \textit{current} \; \textit{of} \; \textit{the SAFR-NAND logic gate similar to the Figure 9.13} \qquad \qquad$ |

|                                                                                                                                                                                                                                                                            |

| $\textbf{Figure 9.15:} \ \textbf{TMR-based block diagram with majority-voted output signal fed-back into individual}$                                                                                                                                                      |

| output signal comparison 192                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                            |

| Figure 9.16: QLC with majority voter output fed-back into comparator for identification of faulty                                                                                                                                                                          |

| individual output signal stored in fault-flag associated with clock cycle 195                                                                                                                                                                                              |

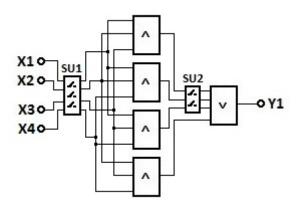

|                                                                                                                                                                                                                                                                            |

| <b>Figure 9.17:</b> Functional diagram of a decreasing input using majority voter through the use of the                                                                                                                                                                   |

| two switching units (SUx) 195                                                                                                                                                                                                                                              |

| two switching units (8 ch),                                                                                                                                                                                                                                                |

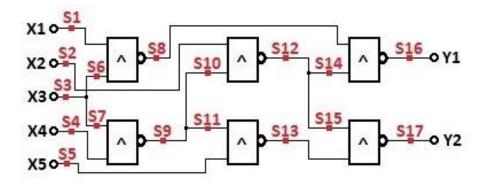

| <b>Figure 9.18:</b> Test circuit C17 of [27] with added stuck-at fault-injection points for interconnection                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            |

| fault simulation 198                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                            |

| <b>Figure 9.19:</b> Expansion of C17 circuit by memory-based fault-existing checker 202                                                                                                                                                                                    |

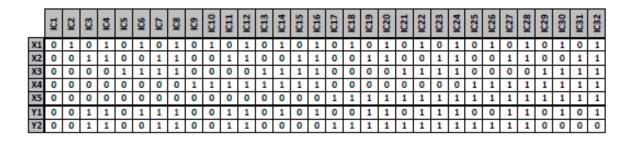

| Table 2.1: Evaluation of the different controller types against system requirements                                                                                                                                                                                                                | 19          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>Table 3.1:</b> All four possible logic state for a NAND gate in accordance with [36]                                                                                                                                                                                                            | 40          |

| <b>Table 4.1:</b> Truth table of the TMR majority voter demonstrated in Figure 4.7                                                                                                                                                                                                                 | 58          |

| <b>Table 4.2:</b> Fault rate data of the stuck-at simulation at specified injection points indicated 4.8                                                                                                                                                                                           | _           |

| <b>Table 4.3:</b> Transistor count comparison against TMR voter (see Figure 4.7) as overhead.                                                                                                                                                                                                      |             |

| <b>Table 5.1:</b> Critical and subcritical faults within different logic gate types [37]                                                                                                                                                                                                           | 80          |

| <b>Table 5.2:</b> Breakdown of the different fault results of the fault-injection at the different points of the standard XOR logic gate displayed in Figure 5.9(a)                                                                                                                                |             |

| <b>Table 5.3:</b> Breakdown of the different fault results of fault-injection at the different injec of quadded logic XOR logic gate in accordance with Figure 5.8(b)                                                                                                                              | -           |

| <b>Table 5.4:</b> Breakdown of the different fault results of fault-injection at the different injec of quadded logic XOR logic gate transformed out of Figure 5.10                                                                                                                                | -           |

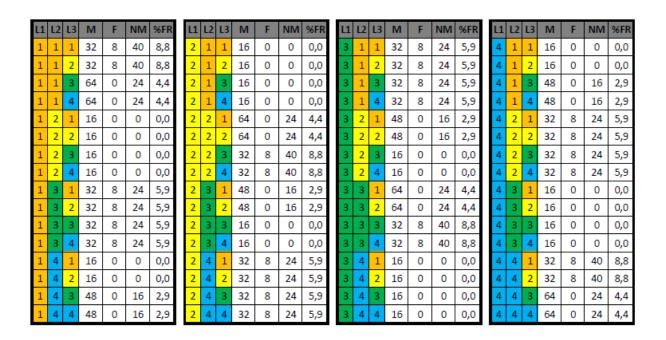

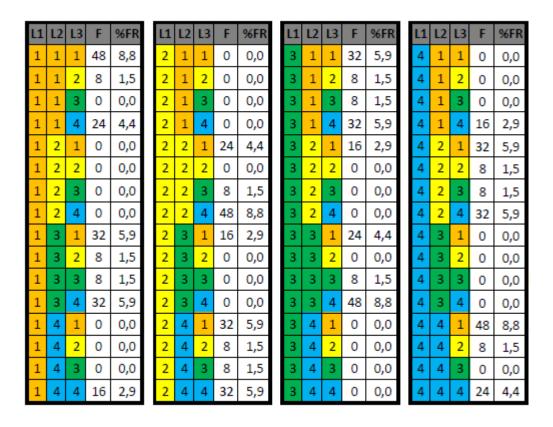

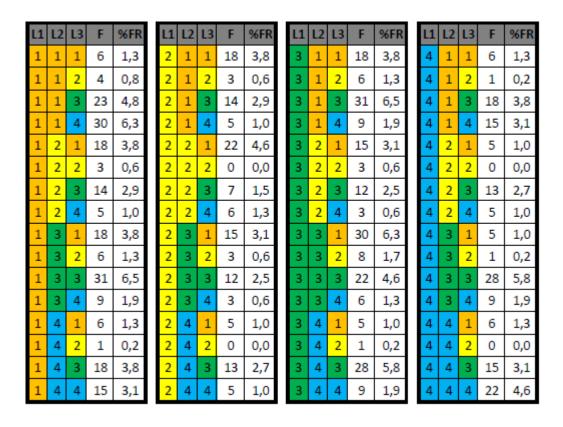

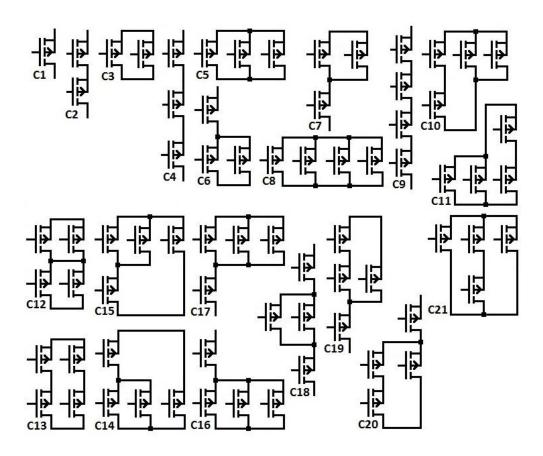

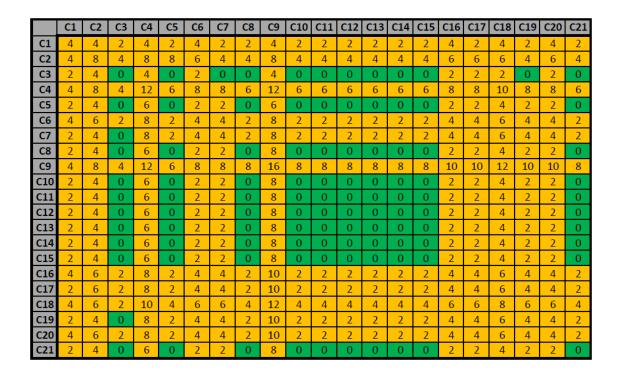

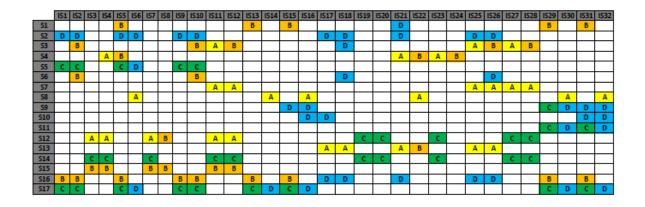

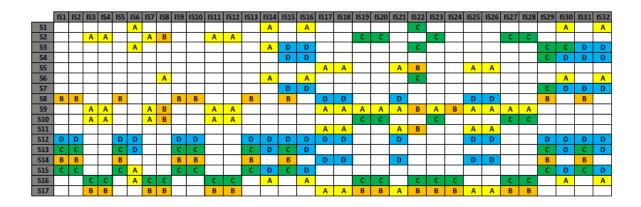

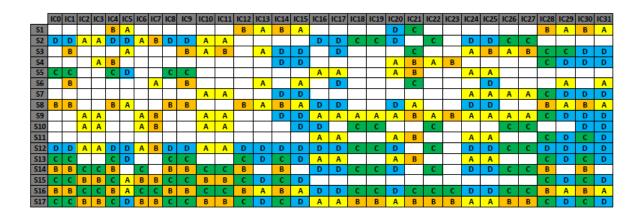

| <b>Table 6.1:</b> Results of fault simulation in accordance of logic gate alteration applied o 6.6(a) reference logic gate circuit performing the fixed logic structure of Figure 6.5(a)                                                                                                           | _           |

| <b>Table 6.2:</b> Fault breakdown per fault-injection point for the reference logic gate strushows all the logic gate variations for the minimum FR; (b) shows all the logic gate variations for the maximum FR; (c) shows the breakdown in regards to fault injection point of the firm Table 6.1 | riations fo |

| Table 6.3: Results of fault simulation in accordance with logic gate alteration applied o         5.9 quadded logic gate circuits without voter                                                                                                                                                    | _           |

| <b>Table 6.4:</b> Results of fault simulation in accordance with logic gate alteration applied of 6.6 QLC in accordance with injection points indicated in Figure 6.9 without voter                                                                                                                | _           |

| <b>Table 6.5:</b> Results of fault simulation in accordance with logic gate alteration applied o 5.9 quadded logic gate circuits with voter                                                                                                                                                        | _           |

| <b>Table 6.6:</b> Results of fault simulation in accordance with logic gate alteration applied o 6.6 OLC in accordance with injection points indicated in Figure 6.9 with voter                                                                                                                    | _           |

## $\underline{\text{Self-healing concepts involving fine-grained redundancy for electronic systems}}$

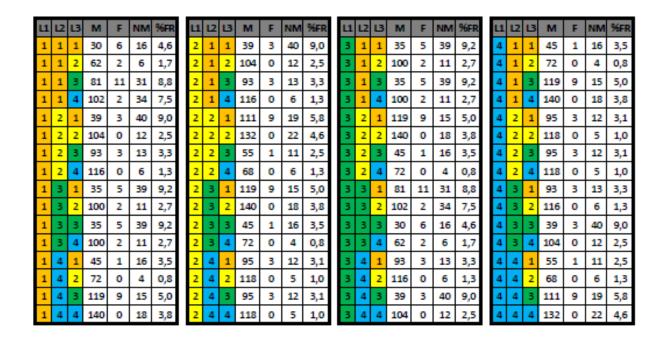

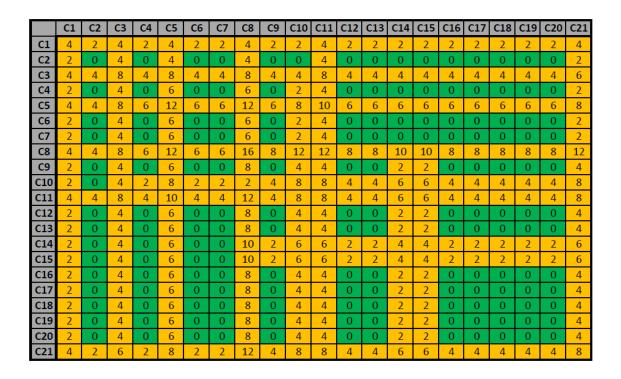

| <b>Table 6.7:</b> Overview of different results of quadded and QLC logic design including v       | with (w) or  |

|---------------------------------------------------------------------------------------------------|--------------|

| without (w/o) majority voter                                                                      | 115          |

| Table 6.8: Comparison result of FR analysis for QLC vs. quadded logic under the in                |              |

| SAH or low faults injected                                                                        | 119          |

| Table 7.1: CMOS definition of input and output voltage levels representing high and               | low digital  |

| conditions [38]                                                                                   | 124          |

| <b>Table 7.2:</b> Simulation results of the fault count $(F_{\#SAH})$ per NAND gate configuration | n under the  |

| influence of a single SAH at each individual transistor of the gate set-up                        | 130          |

| <b>Table 7.3:</b> Simulation results of the fault count $(F_{\#SAL})$ per NAND gate configuration |              |

| influence of a single SAL at each individual transistor of the gate set-up.                       | 130          |

| Table 7.4: Results of SAH fault-injection at each individual transistor of the two input N        | NAND gate    |

| and the corresponding IC where the fourth logic state occurs                                      | 132          |

| Table 7.5: Simulation results of Spice simulation of three input NAND gate with students.         | ck-at fault- |

| injection at individual transistors (mem represents memory effect)                                |              |

| <b>Table 7.6:</b> Results of SAH fault-injection at each individual transistor of the two input N | NAND gate    |

| and the corresponding IC where the fourth logic state occurs                                      | _            |

| 1 &                                                                                               |              |

| Table 7.7: (a) FR analysis of the standard 2-bit full adder.(b) shows the FR of the same          | logic gate   |

| structured using only SAFR-NAND gates for the full adder design                                   | 141          |

| <b>Table 7.8:</b> (a) FR for the standard NAND gate implementation; (b) FR for the SAFR-N         | NAND gate    |

| implementation                                                                                    | _            |

| <b>Table 7.9:</b> (a) FR for the standard NAND gate implementation; (b) FR for the SAFR-N         |              |

| implementation                                                                                    | •            |

| implementation                                                                                    |              |

| Table 7.10: Comparison between the standard and SAFR logic gate-created logic circuit             | s 147        |

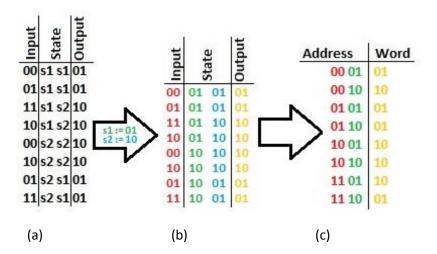

| Table 8.1: These tables are showing the transfer of state transition table information in         | to memory    |

| LUT data: (a) state transition table; (b) state transition table with coded input and outp        | ut stimulus  |

| in accordance to Table 8.2(b & c); (c) state transition table like (b) with coded states          | according    |

| Table 8.2(a): (d) memory LUT data                                                                 | 161          |

| Table 8.2: Coded information: (a) different states; (b) input coin information; (c) output                 |

|------------------------------------------------------------------------------------------------------------|

| information 161                                                                                            |

|                                                                                                            |

| Table 8.3: Comparison of cycle time for both FSM implementations within the two application                |

| platforms; (PLD programme logic device; MMLS memory-mapped logic solution) 163                             |

|                                                                                                            |

| Table 9.1: The simulation data flow of a fault within a logic unit and the approach of using round-        |

| robin logic structure reconfiguration for the identification of the single faulty logic unit. In this case |

| the logic unit B with an SAH fault (see Figure 6.6(b)) 195                                                 |

|                                                                                                            |

| Table 9.2: IC related output results of the C17 circuit without the presences of a fault within its        |

| circuit                                                                                                    |

|                                                                                                            |

| <b>Table 9.3:</b> Output result coding of the C17 circuit199                                               |

|                                                                                                            |

| Table 9.4: Corresponding fault location with IC and resulting output values in accordance with             |

| Table 9.2 for SAL fault-injection at C17 fault-injection points S1 to S17 199                              |

|                                                                                                            |

| Table 9.5: Corresponding fault location with IC and resulting output values in accordance with             |

| Table 9.2.4 for SAH fault-injection at C17 fault-injection points S1 to S17 199                            |

|                                                                                                            |

| Table 9.6: Overlaid corresponding fault location with IC and resulting output values in accordance         |

| with Table 9.2 for SAH and SAL faults injection at C17 fault-injection points S1 to S17 201                |

#### 1.1. Introduction

In the late 1950s the first bipolar junction transistor was invented at the AT&T Bell laboratories in the United States of America. This invention paved the way for the electronic revolution which subsequently followed by application of this development something which could not have been imagined at that time. In these applications the bulky electric tubes or electro mechanical relays, which were previously used for building all necessary electronic systems, were replaced by a bipolar junction transistor. This invention opened the way for smaller systems and the increased system uptime over the old systems made it a universal part of modern lifestyle. The real push into changing our lives pushed us into the digital age through the next big invention in 1959 of the metal-oxide-semiconductor field-effect transistor (MOSFET). In this thesis the MOSFET transistor is referred as the transistor. The electronic parameters of the bipolar junction transistor worked within the analogue functionality and the transistor was geared towards digital functionality. The newly developed chip industry designed integrated digital circuits on a planar silicon die surface in massive numbers and with standardised logic functionality placed in standardised packages. Since then the driving factor of the chip industry is to reduce the required silicon area per given logic function and, therefore, for that, as a result every 18 months the number of transistors per fixed area doubles. This was defined as a law in 1965 by Moore [39]. The continuous feature size reduction pushes the individual component or transistor into the nano-structure regions allowing even more integration of more individual logic functionality into a single chip. Because of the integration of even more logic functionality into one chip, this made them less likely to experience faults in the overall electronic system. These chips are not insusceptible against faults caused through a number of reasons based on their nano-structure feature size. In this thesis the main focus of faults which are going to be investigated is limited to radiation-induced effects causing temporary and permanent faults within the logic circuit.

In the case of an error affecting the behaviour of the electronic system for counteracting the effects caused by the fault, the system needs to be fault-tolerant or self-healing. Any user of this particular system will experience this circumstance, that, using this electronic system, he wishes that the system can "mysteriously" repair or fix itself. Nature has equipped specimens with the capability of self-healing. Even humans are capable of self-healing of minor cuts through the skin. Due to the requirement of electronic system users the area of fault-tolerant, self-repairing or self-healing electronic systems was originated. Novel electronic system-level concepts were introduced and designed to meet this user requirement for certain applications.

The research work of this thesis is focused on creating a matrix logic structure which is capable of self-maintaining required logic functionality through autonomous fault detection and evaluation with minimum logic hardware overheads.

#### 1.2. Problem definition

The motivation for this research work arose out of an increased requirement of equipping electronic logic systems designed for and implemented on Field Programmable Gate Arrays (FPGAs) platforms with self-maintaining capabilities to counteract the effects of radiation-induced faults in terrestrial systems. Radiation-induced faults in certain electronic components have been a known problem in space application using FPGAs-based systems as system platforms [40]. Continued efforts of the chip manufacturer to increase the amount of configurable logic circuit per square mm of their FPGA chips, are pushing the feature size into even smaller component structure dimensions. Feature sizes of individual components are created out of less than 10 atoms [41]. By reducing the feature sizes of individual components the sensitivity for radiation-induced faults increased dramatically. The increased sensitivity to radiation-induced faults was not only noticeable in space applications, but also in increased numbers of functional upset at terrestriallevel systems [42-44]. The most sensitive areas for radiation-induced faults are the memory chips due to their dense structure and way of storing data [45]. Due to the increase of radiation-induced faults on terrestrial-level electronic systems, these systems are required to be designed with the same fault-tolerance mechanics as space-based electronic systems. This counter action, arising from the type of faults the systems experienced, included fault-masking or system reconfiguration initiated by system-independent checker structures. Both approaches require a trustworthy checker structure which in all circumstances must be able to detect faults and constructed to be per design fault-tolerant. Due to the fact that these logic systems are artificial logic structures mostly created out of the same components as the one which they are checking makes it harder to be fault-tolerant. Also both structures are running on the same die likely to have the same individual transistor fault characteristic. The functionality and task of a system-checker remains a philosophical question and is not part of this research work. The research work of this thesis is focused on the realisation of logic structure with built-in autonomous self-maintenance, minimal checker logic and limited hardware overheads.

Radiation-induced faults on any integrated circuits are the result of activities on the sun, which is the centre of our cosmos and not a planet like the Earth, more like a ball of gas which is less cohesive [1]. Because of this the sun does not rotate like a solid planet, it is more like a process of rotating gas mass generating coronal mass ejection (CME) or ejecting solar flares into space (see Figure 1.1).

Figure 1.1: (left) Coronal mass ejection and (right) multiple solar flares [1]

CME consists of massive amounts of electrons and protons, which are ejected into space. Released into space they are travelling long distances having an impact on anything they meet, noticeable in integrated circuits as random information corruption is one possibility. The effect can have the nature of a temporary or permanent hardware or data fault inside a digital logic circuit. Solar flares contain a massive amount of photons of all wavelengths, but not all have an impact on everything they meet [1]. The scaling of the complementary metal-oxide-semiconductor (CMOS) into the region of feature sizes close to single numbers atoms structures is resulting out of the continuous efforts of the chip industry over recent decades. The ongoing increase of components per certain die area was predicted by Moore's law which was hypothesized in 1965 [39]. Modern integrated circuit structures are in the region of nanoscale dimensions making them even more susceptible to radiation-induced effects [5, 44]. Faults caused by radiation inside electronic logic systems made out of nanoscale components will then be relevant at ground level and no longer the only fault conditions at high altitude applications [44]. The shrinking transistor structure has been the driving force over recent decades for producing more logic functionality into a given chip. This trend of increasing the logic functionality per given die area was driven by customer demand for better calculation performance of applications. FPGAs offer more active logic components than other chips and give the system designer more possibilities for creating their required System On a Chip (SOC) design. Computer aided design (CAD) tools are available to help the designers programming their required logic functionality into the FPGA chip. By having this flexibility and the capability of constantly reconfigurable logic structure inside an FPGA this made it unnecessary to produce an Application Specific Integrated Circuit (ASIC) with fixed combinational logic. Research done on the effects of transient-induced faults caused by radiation showed that combinational logic is much less susceptible than memory elements [46]. This shows that the logic

functionality controlled within an FPGA by memory elements could be altered with potentially critical effects on the overall system behaviour. These systems require a type of checker for maintaining the integrity of the electronic system or logic structures which can mask faults inside boundaries and fix the effects of any fault.

#### 1.3. Objectives