# **Graceful Degradation of Reconfigurable Scan Networks**

Larsson, Erik; Xiang, Zehang; Murali, Prathamesh

Published in:

IEEE Transactions on Very Large Scale Integration (VLSI) Systems

DOI:

10.1109/TVLSI.2021.3076593

2021

# Link to publication

Citation for published version (APA):

Larsson, E., Xiang, Z., & Murali, P. (2021). Graceful Degradation of Reconfigurable Scan Networks. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 29(7), 1475-1479. https://doi.org/10.1109/TVLSI.2021.3076593

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Graceful Degradation of Reconfigurable Scan Networks

Erik Larsson, Zehang Xiang and Prathamesh Murali Lund University, Lund, Sweden Email: erik.larsson@eit.lth.se

Abstract—Modern integrated circuits (ICs) include thousands of on-chip instruments to ensure that specifications are met and maintained. Scalable and flexible access to these instruments is offered by reconfigurable scan networks (RSNs), e.g. IEEE Std. 1687. As RSNs themselves can become faulty, there is a need to exclude and bypass faulty parts so that remaining instruments can be used. To avoid keeping track and updating description languages for each individual IC, we propose an on-chip hardware block that makes adjustments according to fault status of a particular IC. We show how this block enables test for faulty scanchains, localization of faulty scan-chains, and repair by excluding faulty scan-chains. We made implementations and experiments to evaluate the overhead in terms of transported data and area.

Keywords—IEEE Std. P1687.1, IEEE Std. 1687, test, localization, diagnosis, repair

## I. Introduction<sup>1</sup>

The semiconductor development towards smaller, faster and more transistors gives advantages like more functionality, better performance, and lower power consumption. However, it is increasingly challenging to avoid malfunctioning. Smaller and faster transistors lead to tighter margins, which in combination with more transistors increase the risk of malfunctioning. To avoid malfunctioning, modern integrated circuits (ICs) are increasingly equipped with embedded (on-chip) instruments for testing, tuning, trimming, configuration and so on [1]. These instruments, which can be in the range of thousands, are accessed throughout the ICs' life cycle: from prototype, debug, test and validation to in-field monitoring and test [2].

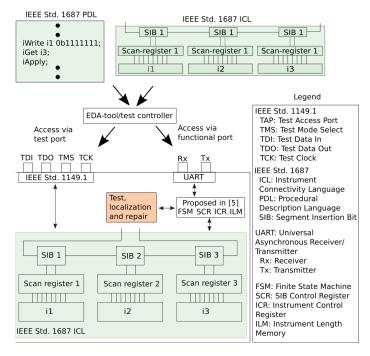

Access to instruments requires an on-chip infrastructure connecting the instruments and an interface (port) to the IC's boundary (pins). Reconfigurable scan networks (RSNs), like IEEE Std. 1687 networks, offer flexible and scalable access to instruments. The main interface for IEEE Std. 1687 is the IEEE Std. 1149.1 test access port (TAP). Figure 1 illustrates a system with three instruments connected using IEEE Std. 1687.

IEEE Std. 1687 includes two description languages, instrument connectivity language (ICL) and procedural description language (PDL) [3]. ICL describes how instruments are interconnected. Figure 1 shows the schematic equivalent of the network's ICL. PDL describes how to operate on instruments. Figure 1 shows PDL to concurrently write data to instrument *i1* and read data from instrument *i3*<sup>2</sup>. Access (test) patterns are created by an Electronic Design Automation (EDA) tool or an embedded controller with PDL and ICL as inputs. For the PDL in Figure 1, smart access patterns include instruments *i1* and *i3*,

Fig. 1. Today's and future solution to access an IEEE Std. 1687 network

while instrument i2, is excluded from the active scan-path as the PDL specifies operations on instruments i1 and i3, but not on instrument i2. Dynamic reconfiguration of the active scan-path to include or exclude instruments can be achieved by the use of segment insertion bits (SIBs).

As some ICs do not have an IEEE Std. 1149.1 TAP, the IEEE Std. P1687.1 [4] explores how to use functional ports, like serial peripheral interface (SPI), inter-integrated circuit (I2C), and universal serial bus (USB) to access IEEE Std. 1687 networks. Different from IEEE Std. 1149.1, where the TAP is described in detail, the working group of IEEE Std. P1687.1 is working towards a standard without detailing a fixed hardware. A main question becomes: what include in the hardware placed between an IEEE Std. 1687 network and a functional port?

We have previously explored the impact on transporting data when including key information from PDL and ICL in a hardware component placed between a functional port and IEEE Std. 1687 [5], see Figure 1. The basic assumption was that there are no faults in the IEEE Std. 1687 networks, which means description languages (PDL and ICL) corresponds to the physical implementation (the IEEE Std. 1687 network). In this work, we explore cases when description languages do not correspond to the physical implementation due to faults in the IEEE Std. 1687 network. The motivation of the work is as follows. PDL and ICL can be stored in a central database shared

<sup>&</sup>lt;sup>1</sup>This submission is an extension of our two-page European Test Symposium 2020 paper where we presented the basic idea but we did not include implementation and experiments

<sup>&</sup>lt;sup>2</sup>iGetReadData (iGet) reads information from an instrument

among several ICs or stored embedded (compressed) locally near each individual IC. In both cases, PDL and ICL need to be updated according to the unique status of individual ICs. For example, assume a central database with PDL and ICL serving many ICs. As long as all ICs are free from faults, the same PDL and ICL can be used for all ICs. However, as soon as one IC has faults, for example a faulty scan-register, description languages for this IC must be modified. For example, assume that scan-register 3 (Figure 1) is faulty, then the iApply group, for this particular IC, must be updated such that iGet *i3* is removed, which makes instrument *i3* to be excluded from the active scan-path. In the worst case, there is a need to keep individual versions of ICL and PDL for each individual IC, which is infeasible in practise.

The objective of the paper is to enable graceful degradation of IEEE Std. 1687 networks where faulty parts are excluded without the need of updating description languages (PDL and ICL). This means original PDL and ICL assuming no faults can be used even in the case when their physical implementation, the IEEE Std. 1687 network, do not match any longer due to faults. We believe that this important aspect have not been addressed prior to this work. The objective is met by developing an on-chip hardware block that makes automatic adjustments according to the fault status of a particular IC. This hardware block makes it possible to test if scan-chains are faulty, localize (pinpointing) faulty scan-chains, and repair networks by excluding faulty scan-chains. We implemented IEEE Std. 1687 networks with 50, 100, and 150 instruments and proposed hardware block to evaluate the overhead in terms of data to be transported and area. We compare a theoretical computation of overhead for direct operation on the IEEE Std. 1687 network against a softwarebased scheme and proposed hardware-based scheme.

The paper is organized as follows. Related work is in Section II and an introduction to the hardware component and protocol to use a functional port to interface IEEE Std. 1687 is in Section III. The schemes for test, localization, and repair are in Sections IV, V, and VI, respectively. The experimental results with implementation on a field-programmable gate array (FPGA) and evaluation of area and the amount of data transported are in Section VII. The paper is concluded in Section VIII.

## II. RELATED WORK

While there are a number of works on analysis [6], design [7], and fault management [8] [9] of IEEE Std. 1687, all these works assume that the IEEE Std. 1687 network is without any faults. Several works have addressed testing and localization (diagnostic) for regular scan-chains [10], [11], [12] and for IEEE Std. 1687 networks [13]. Kundu presented an early work on testing and diagnosing faults in scan-chains [10]. The basic principle is to shift a test sequence through the scanchain, like "001100..11", without performing capture. If there is a mismatch between the shift-out sequence and the shiftin sequence, there is one or more faults in the scan-chain. For localization, the results from the automatic test pattern generation (ATPG) test vectors are used to pin-point the faulty scan flip-flops. Cantoro et al. developed a technique to test and diagnose RSNs [13]. To the best of our knowledge, there is no work addressing the repair of RSNs.

## III. BACKGROUND

We previously explored the impact of including different amount of information in an hardware component placed be-

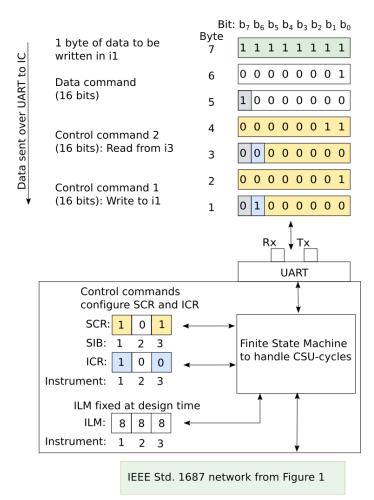

Fig. 2. Hardware and protocol to form shift-in sequence for PDL in Figure 1

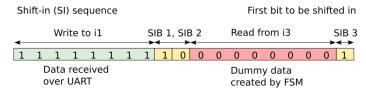

Fig. 3. Shift-in sequence from Figure 2

tween a functional port and an IEEE Std. 1687 network [5]. The most efficient solution, shown in Figure 2, is based on a Finite State Machine (FSM) complemented with three parts; SIB control register (SCR), instrument control register (ICR), and instrument length memory (ILM). The SCR keeps desired values of SIBs, the SCR keeps desired operation of an instrument, and ILM the length of each instrument. The hardware component is operated using two types of commands; control and data. Control commands are used to set SCR and ICR and data commands are used to transport data for instruments. Hence, each iApply group is translated into one or more control commands and one or more data commands.

To illustrate, the iApply group in Figure 1 is retargeted into two control commands and one data command, in total 7 bytes of information. The first control command, byte 1 and 2 in Figure 2, makes SIB 1 active and sets instrument iI in write mode. The details are as follows. Bit  $b_7=0$  in the first byte indicates that current byte and the following byte form a control command. Bit  $b_6=1$  in the first byte indicates that a *write*

operation should be performed. The following 14 bits, which holds the value 1, indicates that SIB 1 should be active so that instrument il is included in the active scan-path. The next two bytes, byte 3 and 4 in Figure 2, are also forming a control command, indicated by bit  $b_7=0$  in byte 3. This control command has  $b_6=0$ , which informs that a *read* operation should be performed. The following 14 bits, which holds the value 3 (0b11) informs that SIB 3 should be active so that instrument i3 is included in the active scan-path. The following 3 bytes, byte 5, 6, and 7 in Figure 2, form a data command as  $b_7=1$  in byte 5. The remaining 15 bits in byte 5 and 6 are used to specify the number of bytes with data that follows. In this example, the 15 bits specify the value 1, meaning that one byte of data follows. The data in byte 7 is the data that should be written to instrument i1.

Figure 3 illustrates generation of shift-in data. When a control command arrives, the hardware component automatically resets SCR and ICR and then these registers are set according to the control commands, see above. When data commands arrive, the hardware translator begins operating the IEEE Std. 1687 network. First, the active scan path is set by traversing SCR and shifting the content to the IEEE Std. 1687 network. The bits shifted out are ignored (discarded) by the hardware component as the bits do not contain any useful information. Second, the shift sequence for the active scan path is created. We describe the shift-in sequence. The FSM begins checking the SCR at the highest value, in this example 3 (SCR(3)), and includes that bit in the shift-in sequence. As SCR(3) = 1instrument i3 is included and ICR(3) is checked to learn that a read operation should be performed, which means data needs to be shifted in such that the content of instrument i3 is shiftedout. This additional (dummy) shift-in data is created by the FSM. The number of bits to shift is given by ILM(3). Then, the FSM proceeds with SCR(2). As SCR(2) = 0, indicating that instrument i2 is not in the active scan-path, the FSM adds a 0 to the shift-in sequence and focuses on next bit in SCR, which is SCR(1). SCR(1) = 1, which means instrument il should be included in the active scan-path and as ICR(1) = 1a write operation should be performed. The FSM gets the length of instrument i1 from ILM(1) and takes data from the UART buffer and adds it to the shift-in sequence. Figure 2 shows the created shift-in sequence and how its information will set the SIBs and the instruments. The hardware component can with support of SCR, ICR, and ILM, create dummy bits when needed and discard not needed data such that only useful information is transported out from the IC. Applying the PDL in Figure 1 results in that the only the information in instrument i3 is returned, as this is the only requested information.

# IV. TEST

The objective of the test procedure is to determine if there are any faults in any of the scan-chains. The section is organized in three parts: IEEE Std. 1687-based, software-based, and hardware-based test. For each part, we describe the effort needed to perform test. The basic principle of the three parts is built on traditional scan-chain test where a test sequence is shifted through the scan-chain but no capture and update is used. For test evaluation, the shifted output sequence is compared against the applied test sequence. Different from traditional scan-chains, RSN offers the possibility to configure the active scan-path. For RSNs designed as in Figure 1, our test principle is to first set the active scan-path such that all instruments are included. For

the example in Figure 1 this means that the active scan chain includes instruments i1, i2, and i3.

## A. IEEE Std. 1687-based

The scheme is straight-forward. First, the active scan-path is set to include all instruments, which means three bits are shifted in and concurrently three bits are shifted-out, in total six bits of data. In general, N bits are shifted-in and N bits are shifted-out for a flat RSN with N SIBs. Second, a test sequence, 001100..11, equal to the active scan-path, which for the example in Figure 1 is 27 (8+8+8+3) bits is shifted-in. During the shiftin of this pattern of length 27 bits, 27 bits are shifted out. To "push-through" the test sequence such that the test response is observable, another 27 bits are shifted-in, and consequently the 27 bits of actual test response are shifted out. The total number of bits becomes  $27 \times 4$ . In general, for a RSN with N SIBs, one instrument per SIB, and the length of instrument i is given by l(i), the total number of bits is given by:

$$6 \times N + 4 \times \sum_{i=1}^{N} l(i) \tag{1}$$

## B. Software-based

The software-based test scheme assumes hardware component and protocol [5], which we extended with a mechanism to not perform capture and update when applying an iApply group if desired. The idea of the test function is to include all instruments in the active scan-path, apply a test sequence, 001100..11, to all instruments and receive the output from the IEEE Std. 1687 network. For the system in Figure 1 the sequence would be as follows:

```

iWrite i1 0b00110011;

iWrite i2 0b00110011;

iWrite i3 0b00110011;

iApply (no capture and no update);

iGet i1

iGet i2

iGet i3;

iApply (no capture and no update);

```

## C. Hardware-based

In the hardware-based test scheme, the hardware component includes the proposed block and a command to perform test of scan-chains. The test command consists of 2 bytes, in a similar way as the data and control commands, Section III. When the hardware receives a test command, the block automatically sets the active scan-path to include all instruments, generates and shifts in a test sequence, and compares the output sequence with expected test sequence. The output (return value) is a single bit indicating if there was any faults or not (which becomes a byte, the smallest unit to transport in UART).

# V. LOCALIZATION

The objective of localization is to pin-point faulty scanchains. The principle is built on traditional scan-chain test and diagnosis (localization). The IEEE Std. 1687 network is configured so that only one scan-chain is active at a time. For each individual segment of the scan-chain a test sequence is shifted through the scan-chain and the output is compared against the input sequence. The section is organized in three parts: IEEE Std. 1687-based, software-based, hardware-based and for each we describe the effort needed to perform localization.

#### A. IEEE Std. 1687 based

The localization procedure assumes that the IEEE Std. 1687 network is in a reset state, which for the example in Figure 1 means that the active scan-path includes only the three SIBs. First, the active scan-path is set to include the first instrument, which means three bits are shifted in and concurrently three bits are shifted-out, in total six bits of data. Second, a test sequence, 001100..11, equal to the active scan-path, which includes instrument 1. For the example in Figure 1 11 (8+3) bits are shifted-in. During the shift-in, 11 bits are shifted out. To "push-through" the test sequence such that it becomes observable, another 11 bits are shifted-in, and consequently 11 bits are shifted out, the actual test response. In this example, the number of bits shiftedin and shifted-out is 50(3+3+11+11+11+11) for one instrument. As there are three instruments in Figure 1, the total number of bits becomes 150 ( $3 \times 50$ ). In general, the number of bits shiftedin and shifted-out during a localization procedure of a flat RSN with N SIBs, one instrument per SIB, and where l(i) is the length of instrument i is given by:

$$6 \times N^2 + 4 \times \sum_{i=1}^{N} l(i)$$

(2)

## B. Software-based Localization

The software-based localization scheme has several similarities with the test function, see Section IV-B. We assume the hardware component and protocol [5] and we have added a mechanism to not perform capture and update of iApply if desired. Different from testing (Section IV-B) localizations includes one instrument at a time in the active scan-path, apply the test sequence, 001100..11, and receive the output from the IEEE Std. 1687 network. For the system in Figure 1, the commands would be as below:

```

iWrite i1 0b00110011;

iApply (no capture and no update);

iGet i1;

iApply (no capture and no update);

iWrite i2 0b00110011;

iApply (no capture and no update);

iGet i2;

iApply (no capture and no update);

iWrite i3 0b00110011;

iApply (no capture and no update);

iGet i3;

iApply (no capture and no update);

```

## C. Hardware-based Localization

The hardware-based localization resembles the hardware-based test, with the difference that the proposed block, when initiated, automatically traverses the instruments one at a time. When the block receives a localization command, the block sets up the active scan-path to include instruments one at a time, shifts in a test sequence, and compares the output sequence with the expected test sequence. We created a dedicated command to make the block initiate localization. The command is constructed in the same way as the test command, 2 bytes of data to initiate and 1 return bit to indicate if any faults were detected (one byte as the smallest unit for UART is one byte).

#### VI. REPAIR

Repair is to make it possible to make use of a partially faulty RSN by excluding instruments with faulty scan-chains. Given is knowledge about which of the scan-chains in the IEEE Std. 1687 network that are faulty. We explore two alternative solutions to repair; software-based and hardware-based.

#### A. Software-based repair

In software-based repair, the PDL is modified according to the faults in scan-chains. For the system in Figure 1, assume it is known that the scan-chain related to instrument *i3* is faulty. This information is taken into account together with ICL and PDL in the retargeting such that the PDL is changed from this:

```

iWrite i1 0b1111111;

iGet i3;

iApply;

```

to this PDL where instrument i3 is excluded:

```

iWrite i1 0b1111111;

iApply;

```

With the above modification of the PDL, the partially faulty RSN can be used.

## B. Hardware-based repair

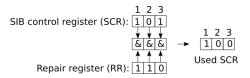

For hardware-based repair, the original PDL is applied and the hardware block automatically excludes faulty scan-registers from the active scan-path. For example, if the scan-chain related to instrument i3 in Figure 1 is faulty, the test and localization process has set the repair register to hold the value 110. This indicates that instrument i3 will not be included in the scanpath due to the 0, while the other instruments, which are not faulty, indicated by 1, see Figure 4. When the original PDL in Figure 1 is applied, the SCR will contain 101 as the PDL specifies that instruments i1 and i3 should be active, see Figure 4. Given the combination of the repair register and SCR, the FSM performs a bitwise AND between the two registers to receive the SCR to be used  $\begin{bmatrix} 1 & 0 & 0 \end{bmatrix}$ . We observe that the "used SCR" does not include instrument i3, which is faulty, hence, the FSM in our component automatically exclude instrument i3 while instrument il is included. The key advantage is that the original PDL can be used and there is no need of additional retargeting due to faults in the IEEE Std. 1687 network.

Fig. 4. Repair by excluding instrument i3

## VII. EXPERIMENTAL RESULTS

The objective of the experiments is evaluate overhead in terms of data, that is number of bits, transported to and from the IC and the area utilization of the proposed scheme for test and localization of RSNs. For repair there are no separate results as the hardware solution automatically repairs the IEEE Std. 1687 network and with the software solution, the PDL is modified according to the defects in the IEEE Std. 1687 network.

TABLE I. NUMBER OF BITS TRANSPORTED TO PERFORM TEST.

| Instruments | IEEE Std. 1687 | Hardware-based | Software-based |

|-------------|----------------|----------------|----------------|

| 50          | 1900           | 24             | 2432           |

| 100         | 3800           | 24             | 4832           |

| 150         | 5700           | 24             | 7232           |

As experimental platform we used an Nexys 4 DDR with an Artix-7 (XC7A100T-1CSG324C) FPGA. We implemented three IEEE Std. 1687 designs with 50, 100, and 150 instruments, respectively. The instruments are connected in a flat manner with one SIB per instrument, as illustrated in Figure 1. The length of each instrument is 8 bits and for communication with the outside, the IEEE Std. 1687 network is connected using UART. The overhead for the IEEE Std. 1687 network scheme is computed with Eq. 1 and Eq. 2.

Table I shows the number of bits transported to and from the IC for the test process. The hardware-based solution only need 16 bits to initiate the command and 1 bit is to report if there was any faults. As UART is used for the communication, the least amount of data to be produced is packaged in one byte. The total number of bits becomes 24. As expected, the number of bits for the IEEE Std. 1687 and the software-based alternatives increase with the number of instruments. Interesting to note is the high number of bits needed for the software-based alternative, higher than that of IEEE Std. 1687.

Table II shows the number of bits transported to and from the IC for the localization process. The hardware-based solution needs 16 bits to initiate the process and 1 bit to report if there were any faults. As discussed above, UART need at least one byte, which mean the overhead becomes 24 bits in total. In the same way as for the test process, the number of bits increases with the number of instruments for the IEEE Std. 1687 and the software-based alternatives. Note, that the number of bits for the software-based localization is significantly lower than that for the IEEE Std. 1687 alternative.

The results on data overhead for test and localization show that when the IEEE Std. 1687 solution is used, it makes sense to first do a test to check if there are faults and if faults are present, a localization action takes place. However, in the case of a software-based solution, the difference between test and localization is quite low, which means a localization function can be used without using a test procedure before. For the hardware-based solution, we have two separate functions, test and localization. While they only require 24 bits each, it would be possible to implement them as a single command performing test-localization-repair. A single command of 16-bits would initiate the process. The output could be a single bit to report if the operation was performed correctly or not. Additional output could include number and position of faults.

Table III shows the area for the hardware solution and for the IEEE Std. 1687 network at 50, 100, and 150 instruments. The area is given as configurable logic blocks (CLBs), which constitutes the basic FPGA cell. The ratio (%) is the area of the hardware solution over the area of the IEEE Std. 1687 network times 100. Interesting to note is that the ratio decreases as the number of instruments in the IEEE Std. 1687 network increases, which indicates that the relative impact of the hardware solution decreases as the number of instruments increases.

# VIII. CONCLUSIONS

We have showed that by including key information in an on-chip hardware component it is possible to get graceful

TABLE II. NUMBER OF BITS TRANSPORTED TO PERFORM LOCALIZATION.

| Instruments | IEEE Std. 1687 | Hardware-based | Software-based |

|-------------|----------------|----------------|----------------|

| 50          | 16600          | 24             | 4000           |

| 100         | 63200          | 24             | 8000           |

| 150         | 139800         | 24             | 12000          |

TABLE III. AREA FOR HARDWARE-BASED SOLUTION, IEEE STD. 1687 NETWORKS, AND RATIO BETWEEN THE TWO.

| Instruments | IEEE Std. 1687 | Hardware-based | Ratio (%) |

|-------------|----------------|----------------|-----------|

| 50          | 145            | 83             | 57        |

| 100         | 290            | 130            | 44        |

| 150         | 433            | 161            | 37        |

degradation of IEEE Std. 1687 networks. The main advantage is in respect to maintaining description languages, PDL and ICL, through the lifetime of ICs. As soon as an IEEE Std. 1687 network becomes faulty, PDL and ICL no longer match the IEEE Std. 1687 hardware. Instead of keeping copies of PDL and ICL for each individual IC, which is impractical due to large volumes, we showed that a small hardware block can perform automatic test, localization and repair, such that the original PDL assuming a fault-free IEEE Std. 1687 network is applied and the proposed block automatically, on-chip, adjust the PDL to the fault situation of each particular IC. We demonstrated that such a component gives a significant reduction in the amount of data (information) that needs to be sent to and from an IEEE Std. 1687 network via a functional port as proposed by IEEE Std. P1687.1. This is highly important as it shows that access with IEEE Std. P1687.1 can be performed without significant impact on the normal (functional) operation, which is crucial, for example during periodic test in automotive industry.

Future work may include handling of general IEEE Std. 1687 networks, advance combinations of instruments using IEEE Std. 1687 in combination with IEEE Std. 1500 and IEEE Std. 1838, and addressing other faults than scan-chain faults.

## REFERENCES

- [1] "Embedded Instrumentation: Its Importance and Adoption in the Test and Measurement Marketplace, Frost and Sullivan, Whitepaper, 2010, 20 p."

- [2] K. Posse, "Component manufacturer perspective," in 2015 International Test Conference, 2015, pp. 1–10.

- [3] "IEEE standard for access and control of instrumentation embedded within a semiconductor device," *IEEE Std* 1687-2014, 2014.

- [4] IEEE P1687.1, "Standard for the Application of Interfaces and Controllers to Access 1687 IJTAG Networks Embedded Within Semiconductor Devices," Dec. 2016.

- [5] E. Larsson, P. Murali, and G. Kumisbek, "IEEE Std. P1687.1: Translator and Protocol," in *International Test Conference*, 2019, pp. 1–10.

- [6] F. G. Zadegan et al., "Access Time Analysis for IEEE P1687," IEEE Transactions on Computers, vol. 61, no. 10, pp. 1459–1472, Oct. 2012.

- [7] —, "Design automation for IEEE P1687," in Design, Automation & Test in Europe Conference (DATE), 2011.

- [8] —, "A self-reconfiguring IEEE 1687 network for fault monitoring," in *European Test Symposium (ETS)*, 2016.

- [9] A. Jutman et al., "Invited paper: System-wide fault management based on IEEE P1687 IJTAG," in International Workshop on Reconfigurable Communication-Centric Systems-on-Chip, June 2011, pp. 1–4.

- [10] S. Kundu, "IEEE Trans. Very Large Scale Integration (VLSI) Systems," vol. 2, no. 4, pp. 512–516, Dec. 1994.

- [11] Y. Huang et al., "Survey of scan chain diagnosis," IEEE Design and Test of Computers, vol. 25, no. 3, pp. 240–248, May 2008.

- [12] D. Adolfsson et al., "On scan chain diagnosis for intermittent faults," in 2009 Asian Test Symposium, Nov 2009, pp. 47–54.

- [13] R. Cantoro et al., "Test of reconfigurable modules in scan networks," IEEE Trans. on Computers, vol. 67, no. 12, pp. 1806–1817, Dec 2018.