## Università degli Studi di Padova

Facoltà di Ingegneria Corso di Laurea Magistrale in Ingegneria Elettronica

Studio ed applicazione delle tecniche di Real Number Modeling e Assertion Based Verification al progetto di circuiti mixed-signal

Study and application of Real Number Modeling and Assertion Based Verification techniques to mixed-signal circuit design

RELATORE

Ch.mo Prof. Andrea Neviani

CORRELATORE AZIENDALE

Ing. Andrea Scenini

TESI DI LAUREA DI Pietro Vallese Matr. N. 1036150

Anno Accademico 2014/2015

# Indice

| Prefazione |                    |          |                                         | 7  |  |

|------------|--------------------|----------|-----------------------------------------|----|--|

| I.         | Re                 | al Nur   | mber Modeling                           | 9  |  |

| 1.         | Elementi di teoria |          |                                         |    |  |

|            | 1.1.               | Preme    | essa                                    | 11 |  |

|            | 1.2.               | Introd   | uzione alla                             |    |  |

|            |                    | Model    | lizzazione MS                           | 13 |  |

|            |                    | 1.2.1.   | FastSPICE                               | 13 |  |

|            |                    | 1.2.2.   | Behavioral Analog Mixed Signal Modeling | 13 |  |

|            |                    | 1.2.3.   | Real Number Modeling                    | 14 |  |

|            |                    | 1.2.4.   | Considerazioni generali                 | 15 |  |

|            | 1.3.               | Studio   | del RNM                                 | 16 |  |

|            |                    | 1.3.1.   | Panoramica sui linguaggi disponibili    | 17 |  |

|            |                    |          | 1.3.1.1. Verilog                        | 17 |  |

|            |                    |          | 1.3.1.2. VHDL                           | 18 |  |

|            |                    |          | 1.3.1.3. Specman/ $e$                   | 19 |  |

|            |                    |          | 1.3.1.4. Verilog-AMS (wreal)            | 19 |  |

|            |                    |          | 1.3.1.5. SystemVerilog                  | 20 |  |

|            |                    | 1.3.2.   | Casi particolari                        | 22 |  |

|            |                    | 1.3.3.   | Limiti della tecnica                    | 24 |  |

|            |                    | 1.3.4.   | Ricapitolazione                         | 25 |  |

| 2.         | Caso               | o di apı | plicazione                              | 27 |  |

|            |                    | • •      | zione del prodotto                      | 27 |  |

|            |                    |          | Power States                            | 30 |  |

|            |                    | 2.1.2.   | Funzioni di regolazione                 | 31 |  |

|            |                    | 2.1.3.   | Soft Start                              | 31 |  |

Indice

|     | 2.2. | Topologia Buck-Boost                                                    |    |

|-----|------|-------------------------------------------------------------------------|----|

|     |      | sincrono non invertente                                                 | 32 |

|     |      | 2.2.1. Modalità di funzionamento BOOST                                  | 33 |

|     |      | 2.2.2. Modalità di funzionamento BUCK                                   | 35 |

|     |      | 2.2.3. Modalità di funzionamento BUCK-BOOST                             | 37 |

| 3.  | VHE  | DL – ANALOG PACKAGE                                                     | 39 |

| 4.  | Netl | ister VHDL                                                              | 43 |

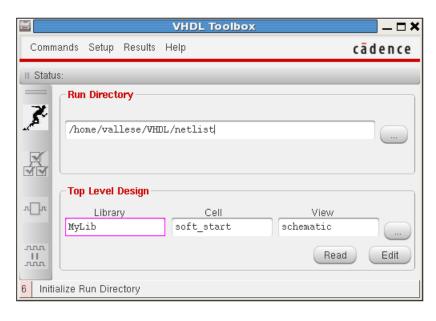

|     | 4.1. | Cadence VHDL Toolbox                                                    | 43 |

|     | 4.2. | Vantaggi e setup del Netlister                                          | 44 |

| 5.  | Eser | mpi di modelli VHDL                                                     | 49 |

|     | 5.1. | Regolatore ideale                                                       |    |

|     |      | di tensione                                                             |    |

|     |      | Comparatore                                                             |    |

|     | 5.3. | Blocco di Soft Start                                                    | 55 |

| 6.  | Mod  | dello del                                                               |    |

|     |      |                                                                         | 61 |

|     |      | Sistema di partenza                                                     |    |

|     |      | MATLAB                                                                  |    |

|     |      | MuPAD                                                                   |    |

|     | 6.4. | VHDL                                                                    | 70 |

| 7.  | Risu | Itati e conclusioni                                                     | 71 |

| 8.  | Арр  | endice                                                                  | 79 |

|     | 8.1. | Codice VHDL                                                             | 79 |

| II. |      | sertion Based Verification<br>r la simulazione di circuiti Mixed Signal | 37 |

| 9.  |      |                                                                         | 89 |

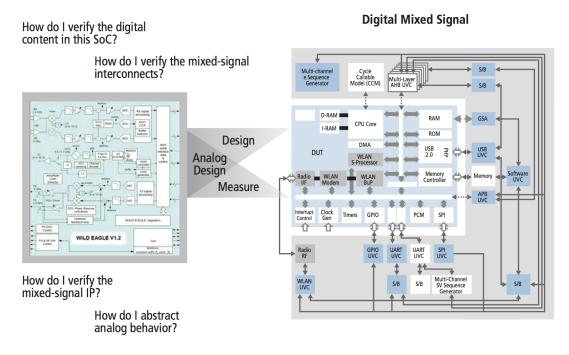

|     | 9.1. | Mixed-Signal Verification                                               | 89 |

|     | 9.2. | Universal Verification                                                  |    |

|     |      | Methodology                                                             | 92 |

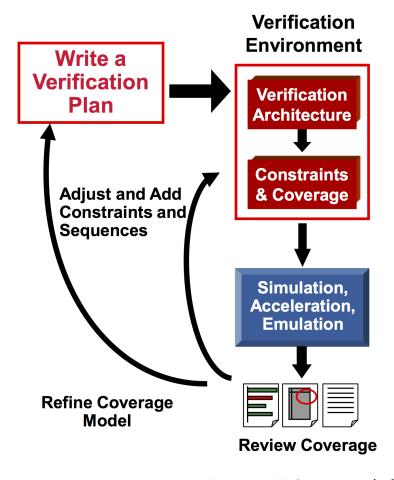

|     |      | 9.2.1. Flusso MDV                                                       | 92 |

| Indice | Indice |

|--------|--------|

|        |        |

| 9.3. Mixed Signal - MDV                                     | 0.4 |

|-------------------------------------------------------------|-----|

| 9.4. Assertion Based Verification                           |     |

| J.I. Absortion Based verification                           | 91  |

| SystemVerilog                                               |     |

| Assertions                                                  | 101 |

| 10.1. Introduzione                                          | 101 |

| 10.2. Linguaggio SVA                                        | 102 |

| 10.2.1. Asserzioni                                          | 102 |

| 10.2.1.1. Immediate Assertions                              | 102 |

| 10.2.1.2. Concurrent Assertions                             | 104 |

| 10.2.1.3. Operatore implicazione                            | 106 |

| 10.2.1.4. Properties and Sequencies                         | 106 |

| 10.2.1.5. Clock nelle asserzioni                            | 108 |

| 10.2.1.6. Reset asincrono                                   | 109 |

| 10.2.1.7. Assertion System Functions                        | 109 |

| 10.2.2. Istruzione di Bind                                  | 110 |

| SVA                                                         |     |

| asserzioni analogiche                                       | 113 |

| 11.1. analog package                                        | 113 |

| 11.2. Eventi di attivazione                                 | 115 |

| 11.2.1. Utilizzo di un segnale di clock                     | 115 |

| 11.2.2. Comparazione dei segnali con livelli di riferimento | 115 |

| 11.3. Esempi                                                |     |

| Conclusioni                                                 | 119 |

| Acronimi                                                    | 121 |

# Elenco delle figure

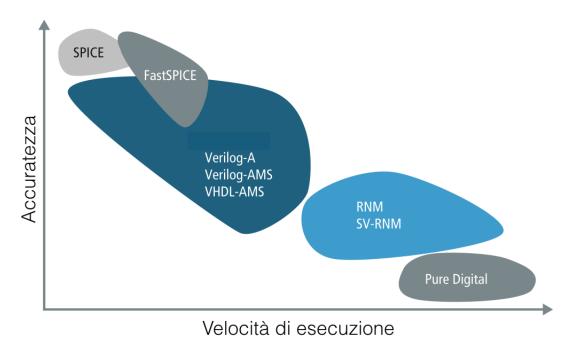

| 1.1. | Compromesso performance accuratezza [2]                                                      | 15 |

|------|----------------------------------------------------------------------------------------------|----|

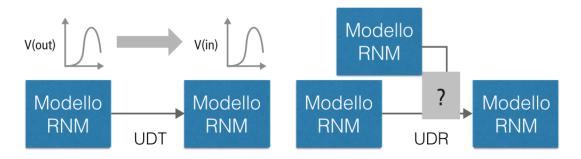

| 1.2. | UDT & UDR [2]                                                                                | 18 |

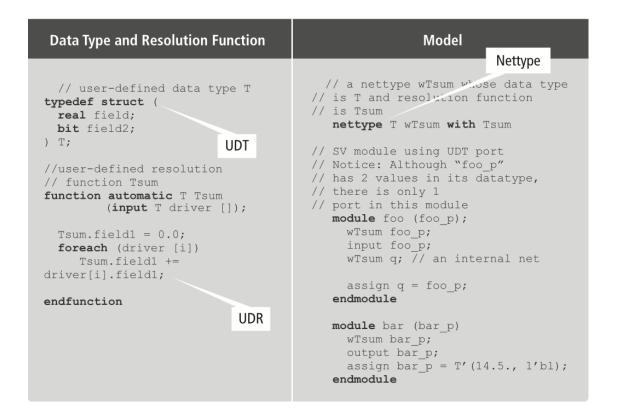

| 1.3. | Sintassi System<br>Verilog per la definizione di UDT ed UDR [2]                              | 22 |

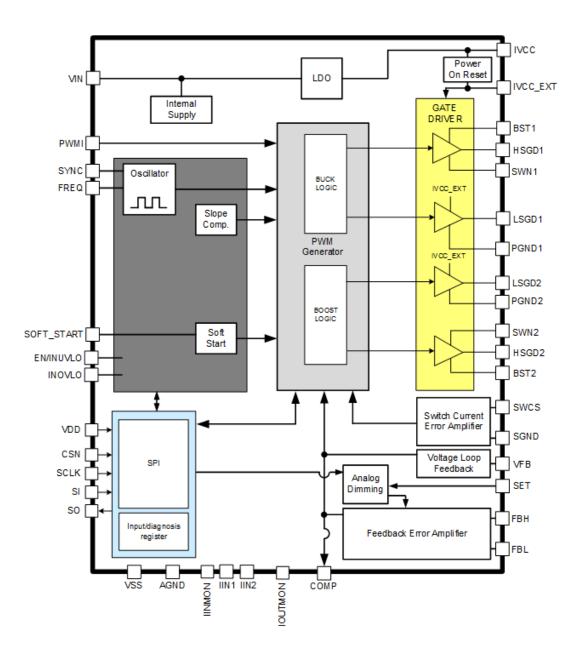

| 2.1. | Diagramma a blocchi semplificato del dispositivo [4]                                         | 29 |

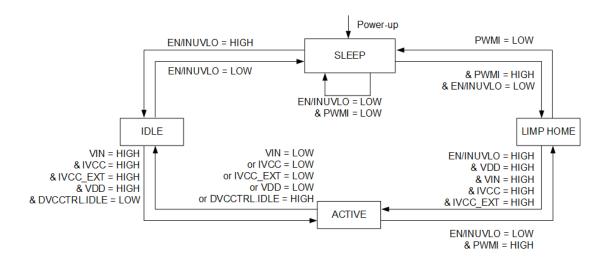

| 2.2. | Macchina a stati delle macro condizioni di funzionamento<br>[4] $\ \ldots \ \ldots \ \ldots$ | 30 |

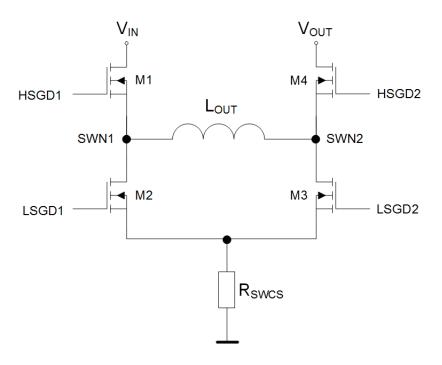

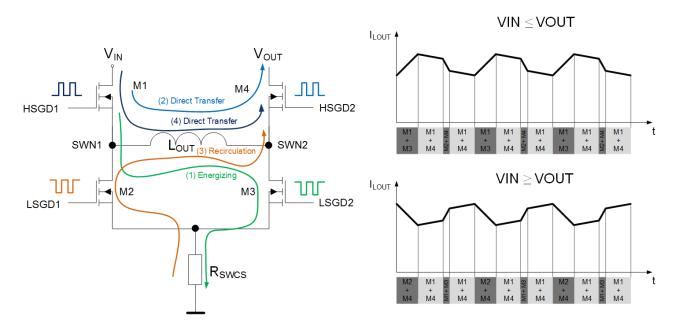

| 2.3. | Architettura a 4 interruttori Buck-Boost sincrono non invertente [4]                         | 32 |

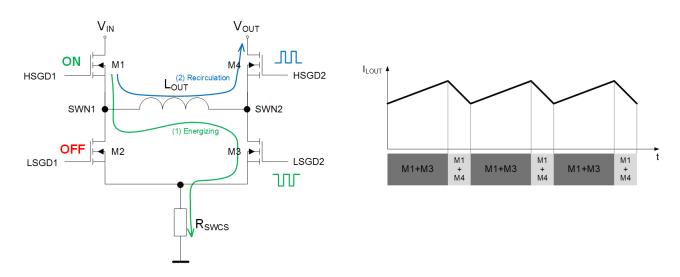

| 2.4. | Modalità di regolazione BOOST[4]                                                             | 33 |

| 2.5. | Confronto con il circuito in configurazione BOOST asincrono standard [4]                     | 34 |

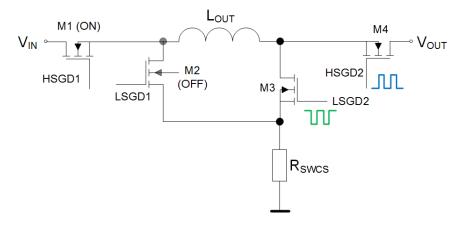

| 2.6. | Modalità di regolazione BUCK [4]                                                             | 35 |

| 2.7. | Confronto con il circuito in configurazione BUCK asincrono standard $[4]$ .                  | 36 |

| 2.8. | Modalità di regolazione BUCK-BOOST [4]                                                       | 37 |

| 2.9. | Tabella di riassunto dello stato dei transistor nelle configurazioni di lavoro               |    |

|      | [4]                                                                                          | 37 |

| 4.1. | Schermata iniziale del Cadence VHDL Toolbox                                                  | 43 |

| 4.2. | Schema di funzionamento del Netlister [7]                                                    | 46 |

| 4.3. | Setup del netlister 1 – Intestazione del file VHDL                                           | 47 |

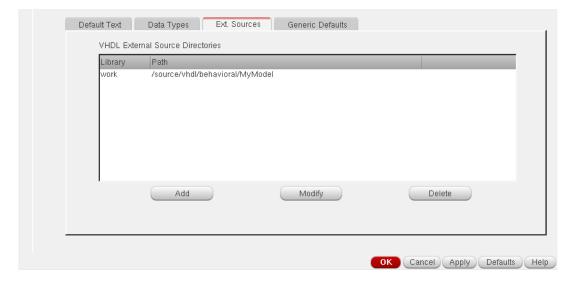

| 4.4. | Setup del netlister 2 – Percorso dei modelli                                                 | 47 |

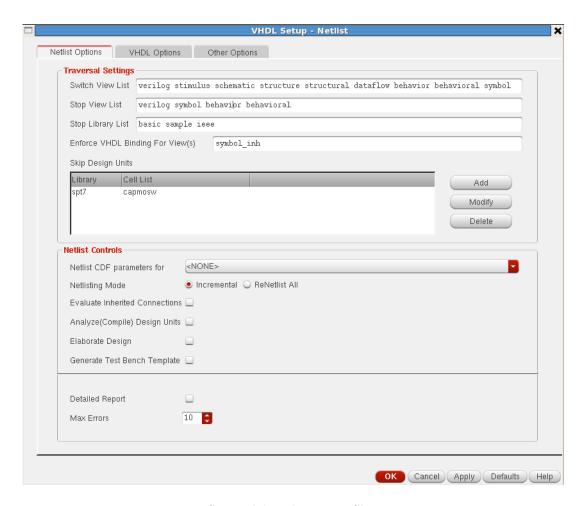

| 4.5. | Setup del netlister 3 – Skip Design Unit                                                     | 48 |

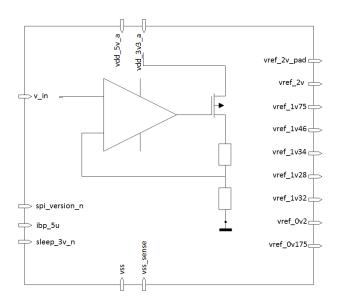

| 5.1. | Schema del Regolatore di tensione                                                            | 49 |

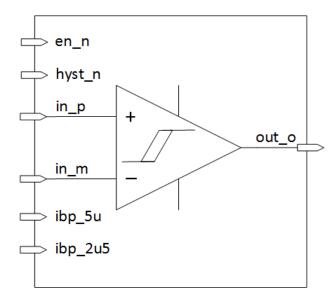

| 5.2. | Schema del comparatore                                                                       | 52 |

| 5.3. | Schema del blocco di Soft Start                                                              | 55 |

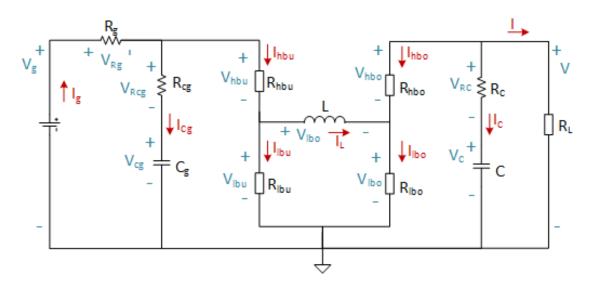

| 6.1. | Schema del PLANT                                                                             | 62 |

| 6.2. | Schema del modello del PLANT                                                                 | 63 |

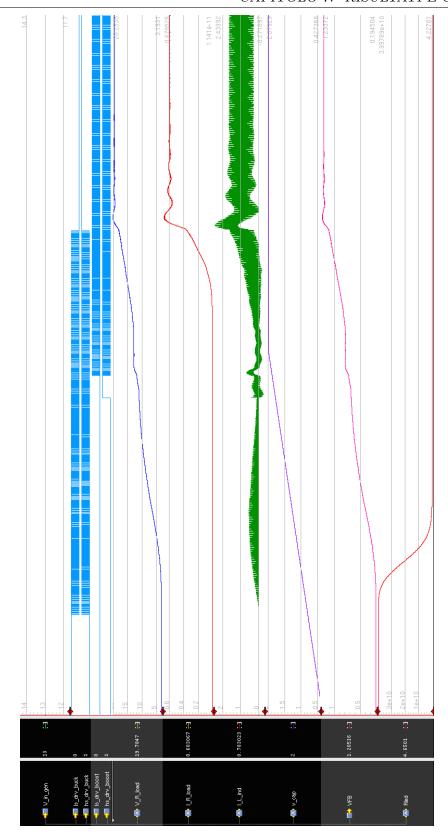

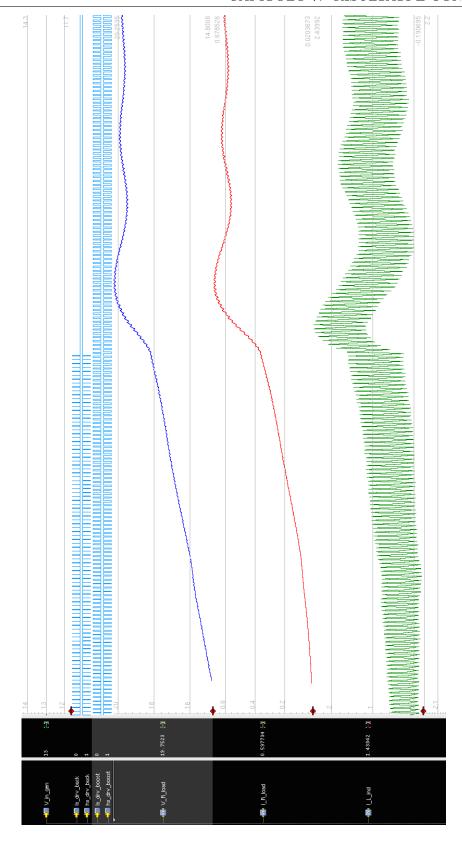

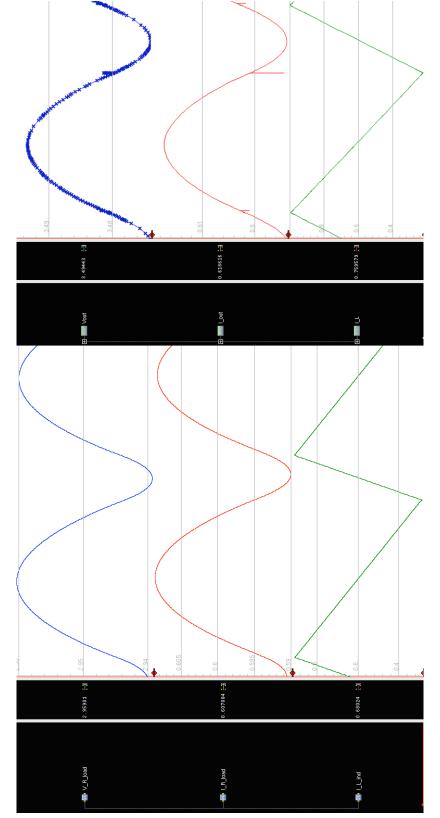

| <i>(</i> .1. | Avvio e regolazione dei dispositivo – si noti, guardando i segnali di controllo                                                                                                                                                          |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | degli interruttori, come il dispositivo passi dalle modalità BUCK, BUCK-                                                                                                                                                                 |     |

|              | BOOST a BOOST. Nell'ultima riga si può osservare l'andamento della                                                                                                                                                                       |     |

|              | resistenza del Diodo                                                                                                                                                                                                                     | 73  |

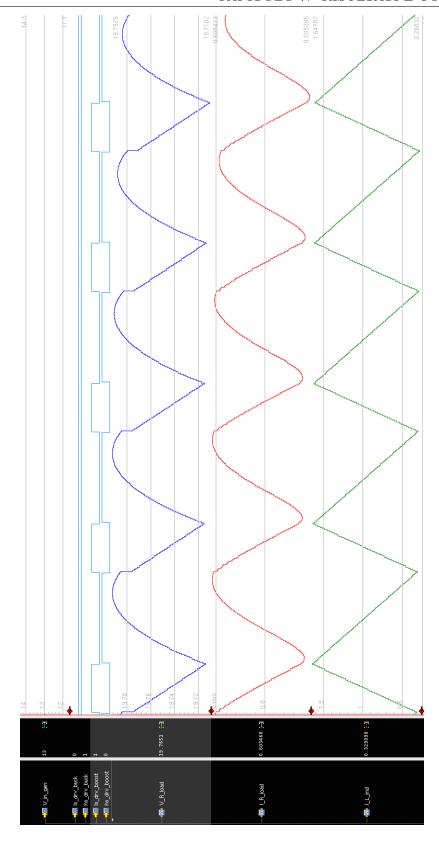

| 7.2.         | Dettaglio del passaggio dalle modalità BUCK-BOOST alla modalità BOO-                                                                                                                                                                     |     |

|              | ST                                                                                                                                                                                                                                       | 74  |

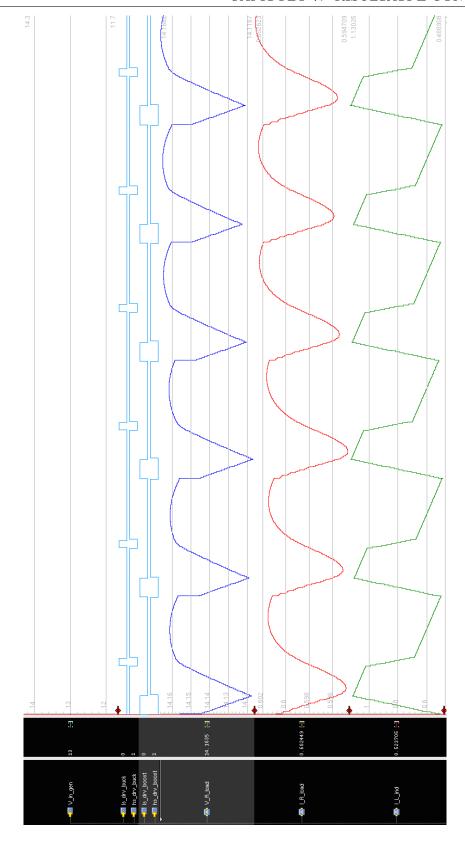

| 7.3.         | Dettaglio di alcuni cicli dei segnali nella modalità di regolazione BOOST                                                                                                                                                                | 75  |

| 7.4.         | Dettaglio di alcuni cicli dei segnali nella modalità di regolazioneBUCK-                                                                                                                                                                 |     |

|              | BOOST                                                                                                                                                                                                                                    | 76  |

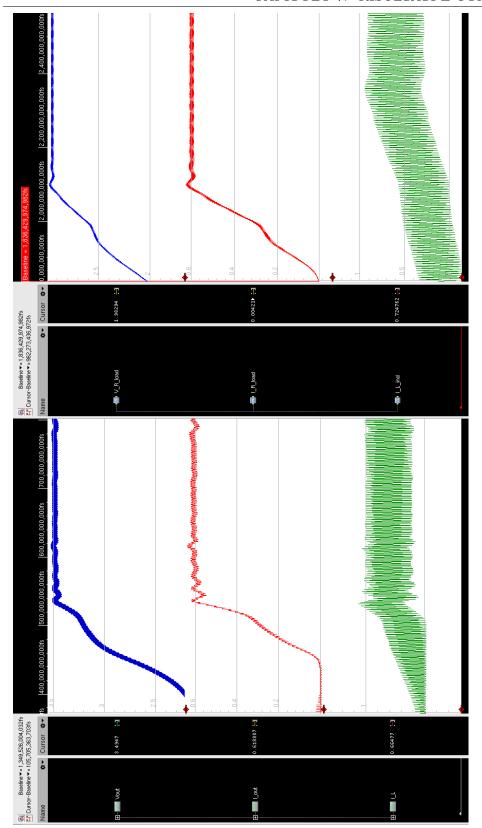

| 7.5.         | Confronto della fase di partenza tra i segnali dela tensione sul carico, della corrente di uscita da regolare e della corrente che attraversa l'induttore. A sinistra dell'immagine sono presenti i segnali risultanti dalla simulazione |     |

| 7.6.         | FastSPICE , a destra invece i segnali del modello RNM                                                                                                                                                                                    | 77  |

|              | Fast<br>SPICE , a sinistra invece i segnali del modello RNM                                                                                                                                                                              | 78  |

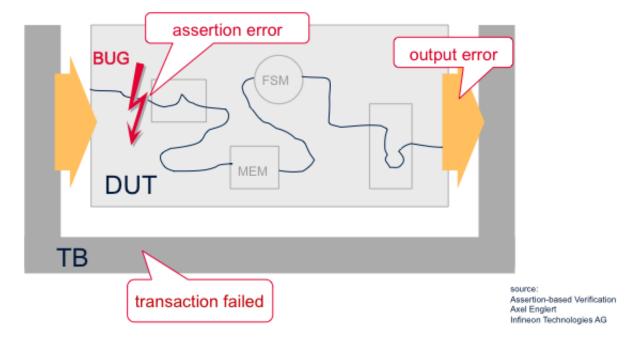

| 9.1.         | Verifica in ambito Mixed-Signal [2]                                                                                                                                                                                                      | 90  |

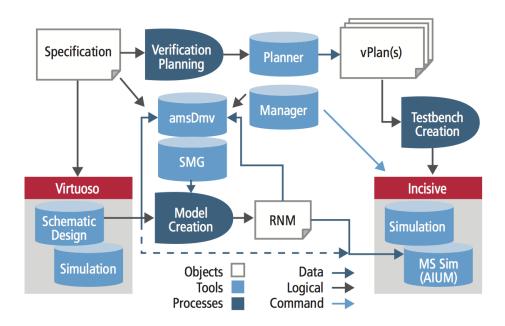

| 9.2.         | Rappresentazione schematica del flusso MDV [14]                                                                                                                                                                                          | 93  |

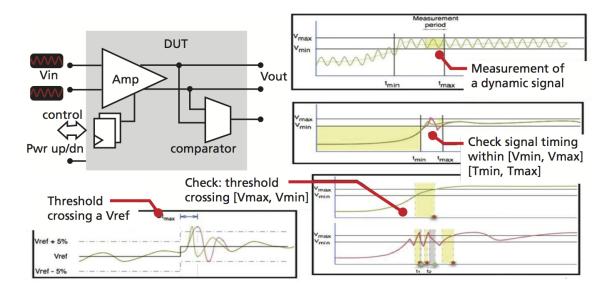

| 9.3.         | Controlli automatici sui segnali analogici [2]                                                                                                                                                                                           | 95  |

| 9.4.         | Ambiente di simulazione MS-MDV [2]                                                                                                                                                                                                       | 96  |

| 9.5.         | L'asserzione rileva l'errore nella prossimità della causa di origine $[15]$                                                                                                                                                              | 99  |

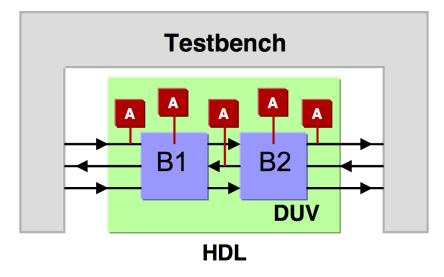

| 9.6.         | Dispositivo in fase di verifica con asserzioni integrate [1]                                                                                                                                                                             | 100 |

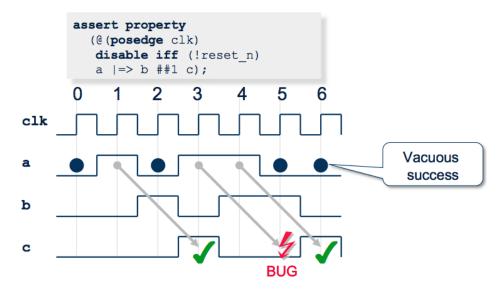

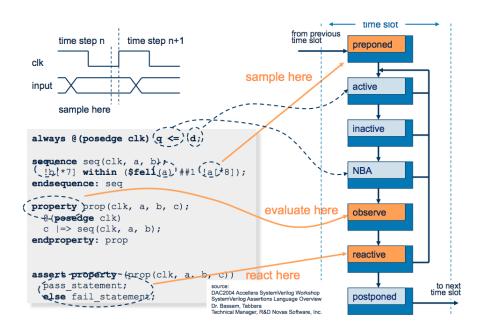

| 10.1.        | Esempio di valutazione in maniera sequenziale [15]                                                                                                                                                                                       | 105 |

| 10.2.        | Ciclo di campionamento e valutazione delle asserzioni nel SVA [15] 1                                                                                                                                                                     | 105 |

### Prefazione

L'elaborato che si va ad introdurre, tratta principalmente dello studio delle due tecniche del Real Number Modeling e dell'Assertion Based Verification, che recentemente stanno emergendo nel settore della verifica dei dispositivi Mixed-Signal.

Nel testo, inoltre, si presentano brevemente alcuni aspetti legati alla loro implementazione nell'ambito del progetto di un dispositivo in fase di sviluppo presso Infineon Technologies.

La prima parte della tesi svolge l'analisi della tecnica del Real Number Modeling. In particolare il primo capitolo contiene un approfondimento teorico, che in un primo momento introduce all'argomento dei modelli per le simulazioni in ambito Mixed-Signal e le tipologie di realizzazione attualmente disponibili.

Successivamente si sviluppa il soggetto principale presentando i presupposti di partenza, i linguaggi HDL – che costituiscono i mezzi di sviluppo –, alcuni casi particolari di applicazione ed i limiti della tecnica del Real Number Modeling.

Nel prosieguo si riportano alcuni elementi relativi all'attività di modellizzazione svolta, partendo da una presentazione sintetica, all'interno del Capitolo 2, delle caratteristiche del dispositivo di controllo per convertitori DC/DC scelto per il progetto.

I capitoli successivi illustrano due strumenti alla base dell'attività di modellizzazione svolta. Il primo è il package VHDL che definisce i tipi di dato utilizzati per rappresentare i segnali analogici. Ed il secondo è il netlister VHDL presente nel Cadence VHDL Toolbox, usato per generare in maniera efficiente la gerarchia del dispositivo, estraendo le informazioni dalle librerie già presenti in Cadence Virtuoso.

Infine, si espongono alcuni semplici esempi selezionati dai blocchi che compongono il dispositivo, e si descrive il metodo impiegato per la creazione del modello in VHDL di un convertitore DC/DC BUCK-BOOST con topologia a 4 interruttori, realizzato per ottimizzare la verifica del sistema.

Nella seconda parte l'esposizione si focalizza sull'introduzione dell'Assertion Based Verification nel campo dei circuiti Mixed-Signal.

Si avvia la trattazione descrivendo le attuali esigenze ad organizzare le tecniche di verifica anche nei progetti analogici ed effettuando una breve rassegna del'Universal Verification Methodology, che si sta imponendo nell'ambito digitale come standard per la Metric-Driven Verification (MDV).

Si prosegue la discussione andando a presentare le caratteristiche generali di una componente fondamentale del MDV, ovvero l'Assertion Based Verification

Nel Capitolo 10 si è voluto riportare una breve introduzione degli aspetti più significativi del SystemVerilog Assertion, il linguaggio scelto per la scrittura delle asserzioni.

Infine, si illustrano sinteticamente i risultati della ricerca trattata volta ad implementare lo strumento delle asserzioni per la valutazione dei segnali analogici.

# Parte I. Real Number Modeling

## 1. Elementi di teoria

#### 1.1. Premessa

Nell'ambito della progettazione di circuiti integrati, l'attività di verifica ha subito una crescita esponenziale parallelamente all'aumento della complessità dei circuiti stessi. Nella verifica dei SoC la maggior parte del tempo impiegato, e del numero di calcoli eseguiti dai computer, sono occupati dalle simulazioni.

Nel settore dei circuiti digitali la verifica funzionale impiega in media il 70% del tempo della progettazione logica, ed anche in questo caso le simulazioni non sono sufficientemente veloci. Eppure le simulazioni RTL digitali sono di molti ordini di grandezza più veloci rispetto alle simulazioni analogiche basate su SPICE.

La maggioranza dei SoC odierni comprendono però sia componenti digitali che analogiche, e per questo si parla di categoria Mixed Signal (MS). Nelle simulazioni di circuiti MS, il tempo impiegato viene influenzato prevalentemente dalle componenti analogiche del progetto.

Ciò è dovuto al fatto che simulazioni analogiche e digitali utilizzano fondamentalmente diversi paradigmi. Mentre i simulatori digitali calcolano espressioni logiche (algebra booleana) basandosi su sequenze di eventi, i simulatori analogici, in ogni istante temporale considerato, risolvono matrici di equazioni differenziali rappresentanti il circuito analogico, in cui ogni componente del sistema può istantaneamente influenzare qualsiasi altro elemento nella matrice.

I test incentrati sui circuiti analogici richiedono pochi stimoli e grande precisione: essi hanno una ridotta velocità di esecuzione a causa appunto delle complesse equazioni richieste per questo livello di accuratezza. D'altro canto, i design digitali necessitano di molte sequenze di ingresso, atte a coprire il maggior numero di possibilità per verificarne il comportamento, ma necessitano di un minor livello di precisione.

Per i motivi appena sottoposti, la verifica di un intero SoC mixed-signal risulta essere un compito impegnativo ed all'aumentare della complessità non è più sufficiente accostare la pre-verifica dei singoli blocchi analogici e l'approccio a "black-box" tipicamente digitale.

Sempre più frequentemente gli errori funzionali sono causati da errori nelle interazioni tra i domini analogico e digitale causando ritardi nei tapeouts e silicon re-spins che possono causare un'ingente perdita economica.

In risposta a tale problematica si sono sviluppate varie tipologie di soluzioni, tra cui una vasta gamma di approcci alla modellizzazione dei circuiti MS. Le simulazioni SPICE sono ancora necessarie per la verifica dei singoli blocchi analogici, mentre nel momento in cui si passa a livello di sottosistema o di chip, si possono utilizzare modelli che ne emulano il comportamento (behavioral) in grado di fornire fino ad un 100x di aumento delle prestazioni.

Per quanto riguarda la verifica top-level di SoC, invece, gli ingegneri possono convertire i modelli analogici in Real Number Model (RNM), ovvero modelli che utilizzano il simulatore ad eventi dei sistemi digitali ma con segnali a valori reali. Questi modelli consentono di rimanere completamente all'interno dell'ambiente di simulazione ad eventi, che permette una velocità quasi alla pari delle simulazioni digitali.

# 1.2. Introduzione alla Modellizzazione MS

Prima di passare ad analizzare più approfonditamente la tecnica di Real Number Modeling, si vuole presentare brevemente il contesto generale della simulazione AMS. Come già enunciato precedentemente, in questo ambito si creano dei modelli per emulare il comportamento delle componenti analogiche le cui semplificazioni permettono ai simulatori di ridurre il tempo di calcolo.

#### 1.2.1. FastSPICE

La necessità di velocizzare le simulazione analogiche era alla base dello sviluppo dei simulatori FastSPICE. Tuttavia, i risultati ottenuti raggiungevano un miglioramento massimo dell'1 o 2 ordini di grandezza rispetto ai modelli SPICE tradizionali. Questo non è risultato sufficiente per ridurre significativamente il tempo di simulazione della fase di verifica, in quanto si cerca di raggiungere almeno i 4-5 ordini di grandezza al fine di ottenere un livello sufficiente di verifica nei limiti di tempo assegnati.

#### 1.2.2. Behavioral Analog Mixed Signal Modeling

Per raggiungere velocità di simulazione considerate ragionevoli, molti team di progetto MS impiegano il "Behavioral AMS Modeling". Esso è uno stile di modellizzazione che utilizza appositi linguaggi descrittivi, con i quali i simulatori possono risolvere equazioni differenziali algebriche (DAE). Con questo metodo si utilizzano gli stessi principi dei simulatori analogici ma si possono semplificare notevolmente le descrizioni circuitali e, di conseguenza, ridurre i tempi di simulazione.

Tipicamente viene utilizzato uno dei seguenti linguaggi:

- Verilog-AMS Un linguaggio per modelli MS, basato sullo standard IEEE-1364

Verilog, che definisce comportamenti analogici e digitali, la cui semantica dispone di elementi sia per i modelli a tempo continuo che per simulatori ad eventi

- Verilog-A È il sottoinsieme del Verilog-AMS esclusivamente per il tempo continuo, teso ai progetti analogici

- VHDL-AMS Concettualmente simile al Verilog-AMS, questo linguaggio fornisce le estensioni per l'analogico e MS allo standard IEEE-1076 VHDL

Questo approccio può risultare dalle 5 alle 100 volte più veloce rispetto a SPICE. L'effettivo miglioramento dipende fortemente dall'applicazione e dal livello di dettaglio utilizzato nel modello. In quanto gli obiettivi di sviluppo dei modelli potrebbero spaziare dal delineare con precisione i comportamenti critici del circuito al descrivere il comportamento del circuito solo al livello di dettaglio necessario per verificare la corretta funzionalità del progetto.

#### 1.2.3. Real Number Modeling

Il Real Number Modeling (RNM) simula le componenti analogiche esprimendo i valori con dati di tipo reale (numeri a virgola mobile), e considera il tempo come discreto utilizzando i meccanismi tipici dei simulatori ad eventi, impiegati nelle simulazioni digitali. A fronte di quanto appena detto, l'RNM è a tutti gli effetti un modello digitale e con questo metodo si possono guadagnare diversi ordini di grandezza (è realistico parlare di un vantaggio di più di 1000x in termini di velocità).

Per la verifica dei blocchi analogici e MS, il RNM può essere utilizzato per accelerare porzioni del percorso del segnale analogico ad alta frequenza – che può occupare la maggior parte delle simulazioni di verifica – mentre DC bias e porzioni a bassa frequenza rimangono modelli SPICE. Ma il più grande vantaggio del RNM è rappresentato dalla verifica globale del SoC, dove gli ingegneri possono rappresentare tutti i segnali elettrici con equivalenti in RNM e rimanere all'interno dell'ambiente di simulazione digitale. In quest'ultimo caso l'RNM consente di realizzare test di regressione per coprire la funzionalità dell'intero chip, pur mantenendo prestazioni elevate di simulazione.

La figura 1.1 mostra il grado di compromesso che intercorre tra la precisione di simulazione e le prestazioni di SPICE, FastSPICE, Behavioral AMS Models (Verilog-A / AMS e VHDL-AMS), RNM (SV-RNM), e simulazioni puramente digitali. Questi valori sono generici e possono variare in modo significativo in base alle diverse applicazioni.

Si noti la vasta gamma di precisione e le prestazioni che è possibile raggiungere con modelli comportamentali Verilog-AMS e VHDL-AMS. La simulazione puramente digitale può rappresentare un segnale analogico solo come un valore logico, ma potrebbe essere sufficiente per effettuare controlli sulla connettività nei SoC MS.

Figura 1.1.: Compromesso performance accuratezza [2]

#### 1.2.4. Considerazioni generali

La creazione dei modelli analogici può risultare onerosa. I progettisti analogici sono avvantaggiati nella creazione di questi modelli, in quanto hanno familiarità con i propri circuiti. Ma a molti designer mancano le competenze di programmazione o le conoscenze richieste per costruire modelli comportamentali, ed un numero limitato di essi ha esperienza con il Verilog o il VHDL. I designer digitali possiedono tali competenze, ma hanno meno padronanza della progettazione dei circuiti analogici.

Un ulteriore fattore di considerevole importanza è l'impegno necessario a predisporre una simulazione e creare il modello. Mentre le simulazioni SPICE sono lente nell'esecuzione, esse sono relativamente facili da configurare. Il tempo necessario per creare un modello di alta qualità, richiede l'impiego di diverse ore di lavoro, fino a raggiungere la durata di alcune settimane nei casi più complessi e/o estesi.

Indipendentemente dal metodo scelto o dal tipo di astrazione, ogni approccio alla modellizzazione comporta una riduzione dell'accuratezza dei risultati che si ottengono dalla simulazione. Inoltre, i modelli scritti a diversi livelli di astrazione non sono equivalenti: più il livello di astrazione aumenta più ci si avvicina ad una descrizione del circuito priva della rappresentazione degli effetti non ideali. È fondamentale per chi si accinge alla formulazione dei modelli, capire e sapere quali dettagli vengono tralasciati, poiché in fase di utilizzo questi modelli non potranno mettere in evidenza situazioni e/o fallimenti, che non siano stati previsti durante la progettazione del modello.

Quanto appena enunciato implica che più di un livello di astrazione deve essere impiegato nel processo di verifica di un design, a seconda di ciò che deve essere controllato.

#### 1.3. Studio del RNM

L'utilizzo del Real Number Modeling per la verifica di design MS non è un approccio totalmente innovativo. È stato già impiegato intorno al 1988, nello stesso periodo in cui veniva standardizzato il VHDL-AMS. A quel tempo le esigenze erano diverse: non erano disponibili simulatori MS pertanto prima della fabbricazione, l'unico modo per risolvere problemi critici nelle interconnessioni tra le porzioni analogiche e quelle digitali di un design, era quello di creare dei modelli di alcune delle componenti analogiche in un simulatore ad eventi.

Oggi, invece, si possiedono linguaggi e simulatori che simulano accuratamente la parte analogica in ambiente MS. Di conseguenza, l'RNM viene principalmente impiegato per ottenere un aumento significativo di velocità durante la simulazione dei design AMS, anche se implica una perdita di precisione.

Grazie all'elevato livello di precisione ottenibile utilizzando altre tecniche di modellizzazione all'interno dell'intero flusso di verifica, tale perdita di accuratezza dei modelli RN non risulta essere così significativa come lo era un tempo.

I linguaggio attualmente disponibili per l'RNM consentono delle descrizione di tipologia signal dataflow, le quali appartengono ad un concetto della programmazione per cui l'esecuzione delle istruzioni è esclusivamente determinata dalla disponibilità degli argomenti d'ingresso delle istruzioni stesse.

In queste rappresentazioni i segnali rappresentano o un valore di tensione o un valore di corrente, ovvero si può imporre in una net una delle due informazioni ma non entrambe contemporaneamente.

Nei modelli per i simulatori analogici, le equazioni, comunque esse siano formulate, sono risolte solo implicitamente. Mentre il RNM richiede allo sviluppatore di scrivere sempre una soluzione esplicita, questo comporta che solo i sistemi con un'esplicita soluzione –

o almeno una buona approssimazione – possano essere modellati, e di conseguenza si devono formulare delle ipotesi sulle impedenze d'ingresso e/o uscita del blocco.

È possibile, con funzioni di risoluzione definite dall'utente, emulare alcuni effetti di impedenza, ma quando ciò è possibile le alternative tra cui poter scegliere sono le due seguenti: o la tensione è considerata indipendentemente dall'impedenza e la corrente è fissa; o è la corrente ad essere considerata indipendentemente dall'impedenza e la tensione è fissa. In altri termini, l'interdipendenza tra corrente e tensione non può essere modellata, ovvero il comportamento del modello non può essere influenzato dagli elementi a cui è connesso e quindi non è possibile descrivere gli effetti di accoppiamento tra i blocchi.

In compenso, in assenza di simulatori analogici, ci si deve preoccupare molto poco dei problemi legati alla convergenza.

#### 1.3.1. Panoramica sui linguaggi disponibili

Molti linguaggi di descrizione dell'hardware supportano i tipi di dati real e wire-real, o wreal. Di seguito viene proposto per ogni linguaggio considerato una sintetica presentazione ed un breve elenco delle caratteristiche interessanti in relazione al RN modeling:

#### 1.3.1.1. Verilog

Il Verilog fu inventato nel 1985 presso la Automated Integrated Design Systems (più tardi denominata Gateway Design Automation) come linguaggio proprietario. Nel 1990 l'azienda fu acquisita da Cadence Design Systems la quale rese di pubblico dominio il linguaggio, ottenendo uno standard con il nome IEEE 1364, con revisioni nel 1995, 2001 e 2005.

Gli inventori del Verilog volevano un linguaggio con una sintassi simile al C così che fosse familiare agli utilizzatori e facilmente accettato.

Allo stato attuale il Verilog assieme al più moderno ma assai più rigido VHDL possono venire considerati gli unici linguaggi utilizzati nel mondo della progettazione e simulazione digitale, con rispettivamente una quota di mercato pari a circa il 50%.

Vantaggi/svantaggi in relazione col RNM:

- Il tipo di dato real si può utilizzare solo come variabile all'interno dei moduli

- Non permette di definire porte di tipo real (richiede l'utilizzo di funzioni real2bits/bits2real)

- Non supporta gli stati X/Z (indeterminato/alta impedenza)

- Non permette più driver su net di tipo wreal

#### 1.3.1.2. VHDL

VHDL è l'acronimo di VHSIC Hardware Description Language, dove VHSIC è la sigla di Very High Speed Integrated Circuits. Viene rilasciato nel 1987 come standard IEEE 1076; subisce il maggior aggiornamento nel 1993.

Esso è stato sviluppato in un progetto del Dipartimento della Difesa Statunitense con lo scopo di documentare il comportamento delle ASIC fornite da ditte esterne, il VHDL ha preso ispirazione dal linguaggio di programmazione Ada per necessità del dipartimento. Successivamente gli sviluppatori dei simulatori logici e degli strumenti di sintesi hanno fatto in modo che i loro strumenti leggessero ed utilizzassero direttamente le informazioni presenti in questa documentazione.

Vantaggi/svantaggi in relazione col RNM:

- Possibilità di definire porte di tipo real

- L'utente può definire nuovi tipi di dato (User-defined types UDT)

- L'utente può definire nuove funzioni di risoluzioni (User-defined resolutions UDR)

- Permette le connessioni a driver multipli

- Ha delle limitazioni sulle connessioni che si interfacciano ai blocchi analogici

Figura 1.2.: UDT & UDR [2]

#### 1.3.1.3. Specman/e

Specman è stato originariamente sviluppato da Verisity, una società con sede in Israele, acquisita da Cadence nel 2005. Ora è parte della suite di verifica funzionale del Cadence, "Incisive Enterprise Simulator", anche se Specman può ancora essere concesso in licenza come prodotto autonomo.

Specman è un tool EDA (Eletronic Design Automation) che fornisce uno strumento automatico per una verifica funzionale avanzata dei progetti hardware. Esso fornisce un ambiente per lavorare, compilare e debuggare testbench scritti nel linguaggio di verifica del'hardware e.

Vantaggi/svantaggi in relazione col RNM :

- Principalmente utilizzato per i testbench

- Presenta istruzioni predisposte alla generazione casuale, alla controllo della copertura della verifica e al test automatico

- Accesso diretto ai valori analogici (receive/drive)

#### 1.3.1.4. Verilog-AMS (wreal)

Il Verilog-AMS è un derivato del Verilog, esso include estensioni per l'Analog Mixed Signal per definire il comportamento dei sistemi analogici e/o a segnale misto.

Anche se in questo particolare frangente interessa principalmente il tipo di dato wreal che può essere utilizzato nel simulatore ad eventi, nel linguaggio è disponibile la sintassi per simulatori analogici a tempo continuo.

Vantaggi/svantaggi in relazione col RNM:

- Facili interazioni con gli elementi analogici

- Connessioni dirette alla net di tipo electrical mediante i connect modules E2R and R2E (per l'utilizzo dei modelli in simulazioni con schematici analogici)

- Il compilatore partiziona le net del progetto tra i due risolutori analogico o digitale tramite il processo dell'associazione delle discipline Disciplines association che l'utente può eventualmente definire altrimenti risulta completamente automatico

- Supporto per driver multipli su net di tipo wreal

- Possibilità di specificare nuove funzioni di risoluzioni per il tipo di dati wreal

- Identifica gli stati X/Z

#### 1.3.1.5. SystemVerilog

Il SystemVerilog combina in un unico linguaggio la sintassi per la descrizione dell'hardware e per la verifica hardware.

Lo sviluppo del SystemVerilog è iniziato con la donazione del linguaggio Superlog ad Accellera nel 2002. La maggior parte delle funzionalità di verifica si basa sul linguaggio OpenVera fornito da Synopsys.

Nel 2005, SystemVerilog è stato adottato come standard IEEE 1800-2005. Nel 2009, la norma è stata unificata con lo standard Verilog (IEEE 1364-2005), creando lo standard IEEE 1800-2009. La versione attuale è lo standard IEEE 1800-2012.

L'insieme di caratteristiche del SystemVerilog può essere diviso in due ruoli distinti:

- il sottoinsieme per la progettazione RTL è un'estensione del Verilog-2005; tutte le caratteristiche di tale linguaggio sono disponibili in SystemVerilog.

- il sottoinsieme per la verifica utilizza ampiamente tecniche di programmazione object-oriented ed è più legato a Java che al Verilog.

Un serio ostacolo all'adozione dell'utilizzo del RNM per la verifica a livello di SoC, sono le lacune del linguaggio SystemVerilog standard IEEE 1800-2009. Alcune delle limitazioni di questo standard includono:

- Non dispone di generazione di numeri pseudocasuali o strumenti per analizzare la copertura della verifica su segnali del tipo di dato real

- Non consente la definizione di porte bidirezionali di tipo real

- È consentito un solo driver per ogni porta (Non supporta le funzioni di risoluzione RN per più driver)

- Non consente connessioni tra le porte definite come real con altri linguaggi (Verilog-AMS, SPICE, VHDL)

A causa di queste limitazioni, le implementazioni RNM in SystemVerilog richiedevano più codice rispetto alle stesse realizzazioni che utilizzavano il wreal.

Per superare le lacune dello standard IEEE 1800-2009, la commissione ha rilasciato un nuovo manuale di riferimento del linguaggio (Language Reference Manual – LRM) con lo standard IEEE 1800-2012.

Le più interessanti si possono riassumere in:

- User-defined types (UDTs)

- Permettono la definizione di net di tipo real

- Permettono la definizione di net con più campi

- User defined resolution (UDRs)

- Funzioni per risolvere gli UDT

- Possibilità di associare funzioni particolari alle net di UDT

- Explicit Interconnects

- nets senza il tipo di dato

- Utile per connettere solo le porte

Il SystemVerilog (IEEE 1800-2012) risulterebbe uno dei linguaggi più indicati per l'applicazione della tecnica del Real Number Modeling, ma è da notare che attualmente non tutti gli ambienti di simulazione supportano completamente le nuove caratteristiche di questo standard.

Figura 1.3.: Sintassi SystemVerilog per la definizione di UDT ed UDR [2]

#### 1.3.2. Casi particolari

Quando si utilizzano tecniche di RNM, per default i segnali non sono continui, anche se i segnali sono di tipo a virgola mobile, così vengono utilizzati dei regimi di campionamento per rappresentare un segnale continuo nel dominio discreto.

Questo richiede una conoscenza a priori della massima frequenza di interesse poiché una rappresentazione a dati campionati contiene tutte le informazioni fino ad una data frequenza.

Inoltre la scelta del periodo di campionamento è una questione di compromesso, esso deve essere sufficientemente alto per prevenire effetti di aliasing e per produrre una buona approssimazione, ma non troppo elevato per evitare di gravare sul tempo di simulazione I modelli AMS sono idonei a formulare il comportamento di un sistema in modo tale che il simulatore possa rappresentarli in termini di un insieme di equazioni algebriche differenziali (DAE) formulati sulla base delle leggi di Kirchhoff, e che presentano tempi e valori continui.

Questi paradigmi di modellizzazione non sono direttamente disponibili in RN modeling. Alcuni di essi possono essere approssimati, ma richiedono un lavoro notevole da parte di coloro ai quali è affidata la scrittura del modello.

Ad esempio per realizzare un valore continuo, è necessario approssimarlo con una funzione polinomiale. Tali approssimazioni sono definite dal numero di coefficienti costanti. Una rappresentazione chiamata Piece Wise Constant (PWC) richiede un valore a virgola mobile per ogni net o porta. Questi modelli sono semplici da scrivere e usare, al contrario di una rappresentazione Piece Wise Linear (PWL) che richiede due valori in virgola mobile per ogni net o porta: uno per il valore e uno per la sua derivata.

Questo non può essere fatto in tutti i linguaggi HDL, perché richiede che esso permetta dichiarazioni di record o strutture. Esistono delle alternative con altri coefficienti, ma sono troppo complessi da impiegare in applicazioni pratiche.

Nella simulazione analogica è possibile calcolare la risposta in frequenza di un circuito. Se la risposta in frequenza è nota, tale informazione può essere adoperata per formulare un approssimazione nel modello RN. Quando risulta possibile scrivere la funzione analogica come trasformata di Laplace (solo per alcuni sistemi lineari), si può ottenere una versione nel dominio della trasformata Z, campionando i segnali di ingresso e di uscita ad una certa frequenza. A questo scopo viene utilizzata la trasformazione bilineare:

$$s = \frac{2}{T} \frac{z - 1}{z + 1}$$

dove s è l'operatore complesso in frequenza e T il periodo di campionamento.

La limitazione intrinseca legata alla formulazione di un modello RN in termini della trasformata Z derivata da parametri misurati s, è l'assunzione di un sistema lineare: questo richiede la conoscenza a priori delle linearizzazioni che il progettista intende utilizzare. Se il sistema viola l'ipotesi di linearità, produrrà un comportamento errato, che non corrisponde affatto al circuito originale.

#### 1.3.3. Limiti della tecnica

Come è già stato riportato, il Real Number modeling è limitato a rappresentazioni signalflow, in cui deve essere presente una formulazione esplicita della funzione di trasferimento e si assumono l'impedenza di ingresso come infinita e l'impedenza di uscita pari a zero.

Il RNM non è tuttavia un sostituto per la simulazione analogica: non è adatto per le interazioni di basso livello che coinvolgono feedback in tempo continuo.

Non è previsto per i sistemi che sono molto sensibili alle interazioni non lineari delle impedenze d'ingresso/uscita.

In aggiunta, le conversioni real-to-electrical richiedono un'attenta considerazione: se una conversione è troppo conservativa, si riscontrerà un gran numero di punti temporali; se una è troppo lasca, si potrebbe verificare una perdita di precisione del segnale.

Questi casi appena enunciati costituiscono il motivo per cui risulta essere così importante capire quando l'RNM deve o non deve essere utilizzato in termini di limiti tecnici e di tipologie di informazioni (ad esempio, la precisione) che si perdono rispetto ad altre tecniche di modellizzazione.

Questo può essere fatto utilizzando un modello di riferimento che non perde alcun dettaglio, come ad esempio SPICE. Le descrizioni SPICE rappresentano il modello indipendentemente da come verrà impiegato, e forniscono un riferimento con il quale queste diverse astrazioni possono essere verificate.

È anche altamente raccomandato l'utilizzo delle asserzioni all'interno dei modelli al fine di evitare un uso improprio durante la verifica come, ad esempio, un controllo sulla massima frequenza in cui può essere utilizzato il modello.

#### 1.3.4. Ricapitolazione

L'RN modeling produce enormi miglioramenti in termini di prestazioni, nei casi in cui funzioni correttamente. Questo è un avvertimento critico, poiché l'RN modeling è limitato nella sua applicabilità ed è difficile da eseguire con precisione.

#### Andando a riassumere:

- Il primo passo è quello di definire gli effetti da modellare e garantire che vi sia un modo esplicito per descriverli, dato che gli ingressi e le uscite saranno segnali digitali.

- Quando si calcola la soluzione del sistema, si è a conoscenza solamente di ciò che sta all'interno del modello, non di quello che sarà ad esso collegato.

- Tranne utilizzando qualche formalismo VHDL o SV-2012 con rapporti tensione/corrente, gli ingressi dei modelli sono considerati come alte impedenze e le uscite basse impedenze.

- Gli ingressi e le uscite dei modelli devono essere univocamente distinguibili (niente porte bidirezionali).

- Spesso, il progettista non può scegliere il linguaggio durante la modellizzazione. Ma, come si è potuto osservare in precedenza, tutti i linguaggi disponibili non sono applicabili a tutte le caratteristiche che devono essere descritte. Quindi se il progettista ha la facoltà di scegliere il linguaggio, non dovrebbe poterlo fare fino a che non sia certo di quali effetti sono in procinto di essere modellati.

- Poiché i simulatori per l'RN Modeling eseguono solo al variare degli ingressi del modello o a seconda di passi temporali predefiniti, a volte risulta necessario inserire nelle descrizioni delle istruzioni per l'aggiornamento dei valori.

Si sono identificate tre diverse circostanze in cui le descrizioni in RN modeling possono essere utilizzate senza correre rischi:

- Modelli signal-flow che non richiedono un sistema conservativo.

- Modelli conservativi dove è sufficiente la modellizzazione solo della tensione o della corrente.

- Modelli per controllare la corretta propagazione dei dati, segnali di controllo e segnali di potenza durante la simulazione senza alcun dettaglio implementativo.

## 2. Caso di applicazione

Si è scelto di applicare la tecnica di Real Number Modeling ad un dispositivo in fase di progetto presso Infineon Technologies, realizzando la modellizzazione in linguaggio VHDL di ogni blocco analogico legato alla funzionalità del dispositivo. Di seguito si procede con una breve sintesi delle caratteristiche del prodotto

#### 2.1. Descrizione del prodotto

Il dispositivo è un circuito integrato progettato per il controllo di un convertitore DC/-DC Buck-Boost non invertente realizzato con MOSFET ed un singolo induttore. Esso incorpora varie funzioni di diagnostica e protezione ed un'interfaccia SPI. Questo sistema è particolarmente indicato per pilotare LED ad alta potenza  $(V_{LED} = 2 \div 52 [V])$  con la massima efficienza ed il minimo numero di componenti esterni.

Il circuito offre più modalità di dimming sia analogiche che digitali. Esso presenta un generatore di clock interno configurabile o sincronizzabile ad una sorgente esterna e la frequenza di switching può essere impostata in un range compreso tra i 200 [kHz] ed i 700 [kHz].

Inoltre, il sistema nella modalità di regolazione di corrente dispone di un anello stabile gestito grazie a semplici componenti esterni di compensazione. Il dispositivo possiede anche una funzione di Soft Start per limitare i picchi di corrente ed overshoot di tensione all'avvio del sistema.

#### 2.1. DESCRIZIONE DEL PRODOTTO CAPITOLO 2. CASO DI APPLICAZIONE

Riassunto delle principali funzioni:

#### • di protezione

- dai sovraccarichi dei MOSFET dei ponti

- dalla condizione di cortocircuiti del carico per scariche elettrostatiche (ESD)

- dal sovrariscaldamento con spegnimento del dispositivo e riavvio automatico

#### • di diagnostica

- informazioni di diagnostica attraverso le lettura delle "Error Flags" del SPI

- rilevamento della condizione di assenza del carico (circuito aperto) durante il funzionamento

- preavviso sulle condizioni di temperature del dispositivo e dello spegnimento per sovrariscaldamento

- monitoraggio intelligente e funzioni avanzate fornite dalle informazioni sulla corrente che attraversa i LED e la corrente dal generatore d'ingresso

Figura 2.1.: Diagramma a blocchi semplificato del dispositivo [4]

#### 2.1.1. Power States

Figura 2.2.: Macchina a stati delle macro condizioni di funzionamento[4]

La macchina a stati presente in figura 2.2 riassume i quattro macro-stati di funzionamento del circuito, dove si possono vedere anche le possibili transizioni in funzione dei segnali interessati.

Quando il dispositivo è in stato di **SLEEP**, tutte le uscite sono spente ed i registri del SPI sono in stato di reset, indipendentemente dalle tensioni VIN, VDD IVCC e IVCC\_EXT. Per la condizione di 'Power-up' è sufficiente che una delle tensioni di alimentazione VIN e VDD superino la propria soglia minima.

Nello stato di **IDLE** i regolatori delle alimentazioni interne stanno lavorando, ma non c'è attività di switching a prescindere dai valori delle tensioni di VIN, VDD IVCC e IVCC\_EXT. In questo stato le funzioni di diagnostica non sono disponibili e se in presenza di VDD con un valore sufficiente la comunicazione SPI è attiva.

Lo stato di **LIMP HOME** permette di soddisfare determinati requisiti di sicurezza del sistema e fornisce la possibilità di mantenere un livello di corrente/tensione in uscita definita tramite un circuito di controllo di riserva. Il sistema di riserva permette di pilotare il carico durante un malfunzionamento dell'eventuale microcontrollore collegato al dispositivo.

Nello stato **ACTIVE** il sistema è pronto a far partire l'attività di switching, non appena il segnale PWMI va alto.

#### 2.1.2. Funzioni di regolazione

Il controllore integra tutte le funzioni necessarie per regolare una corrente costante al carico – il caso ideale per applicazioni LED –, opzionalmente è possibile utilizzarlo per regolare una tensione costante.

Il sistema dispone di due ingressi analogici (IIN1, IIN2) per il controllo sulla corrente di ingresso per limitarne il valore ed un secondo loop con rilevamento di corrente, connesso ai pin FBL e FBH, per regolare la corrente erogata al carico.

La logica del dispositivo regola la corrente erogata fornendo un segnale PWM (Pulse Width Modulated) ai 'gate driver', figura 2.1 a pagina 29. I pin (HSGD1,2 e LSGD1,2) connessi ai gate driver vengono utilizzato per pilotare i MOSFET esterni. È anche possibile fornire il segnale PWM esternamente tramite il pin PWMI.

#### 2.1.3. Soft Start

Il comportamento della Soft Start limita le correnti che attraversano l'induttore e i MO-SFET esterni durante l'inizializzazione (alla prima accensione e dopo aver rivelato le condizioni di cortocircuito o di circuito aperto del carico). La funzione di Soft Start incrementa gradualmente la corrente nell'induttore e nei MOSFET durante  $t_{SOFT-START}$  per evitare di fornire una tensione troppo elevata al carico. La rampa di Soft Start è definita da un capacitore ( $C_{SOFT-START}$ ) connesso al pin SOFT\_START. La scelta del valore di capacità per  $C_{SOFT-START}$  dipende dalla seguente equazione:

$$t_{SOFT-START} = \frac{1.4 \, [V]}{I_{SOFT-START-PU}} C_{SOFT-START}$$

Il pin SOFT\_START è anche utilizzato per definire un filtro temporale per le condizioni di guasto. Quando viene rilevato sull'output un circuito aperto o un cortocircuito, viene attivato un generatore di corrente di pull-down  $I_{SOFT-START-PD}$ . Questa corrente abbassa il valore di  $V_{SOFT-START}$  fino a che non viene raggiunta una soglia di reset che riattiva la corrente  $I_{SOFT-START-PU}$  la quale innesca un nuovo ciclo fino all'uscita della condizione di guasto.

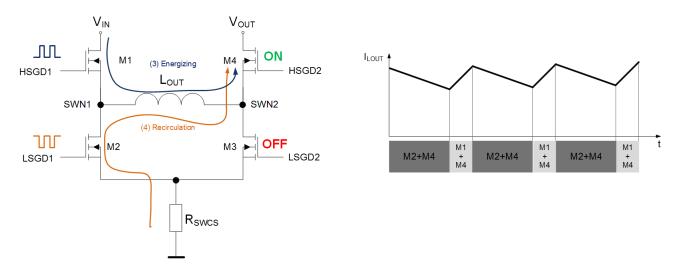

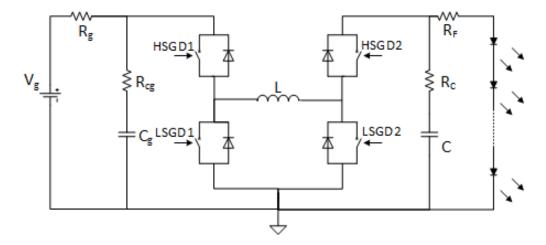

# 2.2. Topologia Buck-Boost sincrono non invertente

Il dispositivo è progettato per controllare i segnali che pilotano i terminali di gate di 4 MOSFET esterni disposti in una topologia Buck-Boost sincrono non invertente a singolo induttore. Questa topologia consente di operare in modalità BOOST, BUCK-BOOST o BUCK in applicazioni ad alta potenza con la massima efficienza.

I passaggi tra le differenti modalità di regolazione sono eseguiti automaticamente dal dispositivo, in funzione delle condizioni al contorno dell'applicazione.

Figura 2.3.: Architettura a 4 interruttori Buck-Boost sincrono non invertente [4]

La figura 2.3 presenta lo schema della configurazione con l'induttore  $L_{OUT}$  e i 4 MOSFET a canale n (M1, M2, M3 e M4).

I transistor M1 e M3 quando sono accesi formano un percorso tra  $V_{IN}$  e massa che attraversa  $L_{OUT}$  in una direzione (pilotati dai due PIN HSGD1 e LSGD2). Mentre l'accensione di M2 e M4 forma un percorso tra  $V_{OUT}$  e massa che attraversa  $L_{OUT}$  in direzione opposta (pilotati dai due PIN HSGD2 e LSGD1).

Il dispositivo monitora i nodi SWN1, SWN2, la tensione su  $R_{SWCS}$  e le correnti d'ingresso e di uscita.

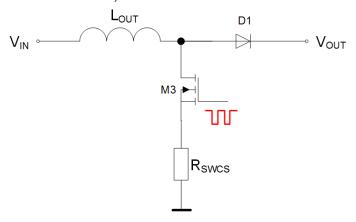

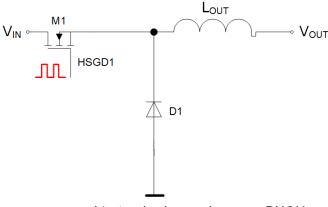

#### 2.2.1. Modalità di funzionamento BOOST

#### $V_{\rm OUT} > V_{\rm IN}$

Per lavorare in questa modalità i transistor che compongo il ponte 1, M1 e M2 vengono rispettivamente tenuti sempre acceso e spento, e l'attività di switching avviene sul ponte 2. In ogni ciclo si avvia prima M3 – in questa fase il dispositivo di controllo valuta la corrente che attraversa l'induttore (controllo dei picchi di corrente) – e rimane acceso finchè la tensione su  $R_{SWCS}$  non raggiunge la soglia massima di riferimento. Allo spegnimento di M3 si accende M4 per il tempo del ciclo residuo.

Nella figura 2.4 è rappresentato graficamente quanto appena esposto sinteticamente ed in figura 2.5 nella pagina successiva si mostra un confronto semplificato con l'approccio asincrono del Boost tradizionale.

Figura 2.4.: Modalità di regolazione BOOST[4]

#### a) 4 switch architecture BOOSTER

b) standard asynchronous BOOSTER

Figura 2.5.: Confronto con il circuito in configurazione BOOST asincrono standard [4]

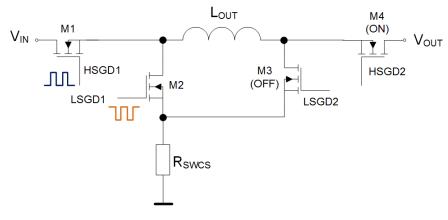

### 2.2.2. Modalità di funzionamento BUCK

### $V_{IN} > V_{OUT} \\$

Per lavorare in questa modalità i transistor che compongo il ponte 2, M4 e M3 vengono rispettivamente tenuti sempre acceso e spento, e l'attività di switching avviene sul ponte 1. In ogni ciclo si avvia prima M2 – in questa fase il dispositivo di controllo valuta la corrente che attraversa l'induttore – e rimane acceso finchè la tensione su  $R_{SWCS}$  non raggiunge la soglia minima di riferimento. Allo spegnimento di M2 si accende M1 per il tempo del ciclo residuo.

Nella figura 2.6 è rappresentato graficamente quanto appena esposto sinteticamente ed in figura 2.7 nella pagina successiva si mostra un confronto semplificato con l'approccio asincrono del Buck tradizionale

Figura 2.6.: Modalità di regolazione BUCK [4]

### a) 4 switch architecture BUCK

b) standard asynchronous BUCK

Figura 2.7.: Confronto con il circuito in configurazione BUCK asincrono standard [4]

## 2.2.3. Modalità di funzionamento BUCK-BOOST

Il controllore è in modalità Buck-Boost quando la  $V_{IN}$  è vicina alla  $V_{OUT}$  .

In questa modalità tutti e quattro i MOSFET vengono accessi alternativamente combinando le due modalità descritte precedentemente e come mostrato in figura 2.8

Figura 2.8.: Modalità di regolazione BUCK-BOOST [4]

|    | BOOST<br>MODE | BUCK-BOOST<br>MODE | BUCK<br>MODE |

|----|---------------|--------------------|--------------|

| M1 | ON            | PWM                | PWM          |

| M2 | OFF           | PWM                | PWM          |

| M3 | PWM           | PWM                | OFF          |

| M4 | PWM           | PWM                | ON           |

Figura 2.9.: Tabella di riassunto dello stato dei transistor nelle configurazioni di lavoro [4]

# 2.2. TOPOLOGIA BUCK-BOOST SINCRONO NON INVERTENTE CAPITOLO 2. CASO DI APPLICAZIONE

# 3. VHDL – ANALOG PACKAGE

Il punto di partenza per l'attività di modelizzazione è definire adeguatamente i tipi di dato da utilizzare.

Tipicamente le porte dei blocchi sono di tre tipologie differenti: pin digitali (segnali di abilitazione, clock, etc), pin analogici che rappresentano tensioni (alimentazione, tensione di riferimento) e pin analogici che rappresentano correnti (correnti di bias, sensed currents).

Ad ognuna di queste tipologie si assegna un tipo di dato diverso, andando a scegliere tra STD\_ULOGIC, ANALOG\_UT e CURRENT\_UT.

Il primo è definito nel package 'std\_logic\_1164' della 'libreria' IEEE mentre gli altri due si sono definiti nel package 'analog\_pack' della libreria 'analog\_hw'. Pertanto è importante dichiarare nell'intestazione del modello VHDL le due librerie e l'uso del package come in figura 3.1:

```

LIBRARY IEEE;

USE ieee.std_logic_1164.ALL

LIBRARY analog_hw;

USE analog_hw.analog_pack.ALL

Listing 3.1: Intestazione dei file VHDL

```

```

type std_ulogic is ( 'U', — bit non inizializzato/indefinito 'X', — valore sconosciuto (forte) '0', — valore logico basso (forte) '1', — valore logico alto (forte) 'Z', — stato di alta impedenza 'W', — valore sconosciuto (debole) 'L', — valore logico basso (debole) 'H', — valore logico alto (debole) '-'); — don't care

```

Listing 3.2: Dichiarazione del tipo di dato std ulogic

```

type analog_ut is range real 'low to real 'high;

subtype current_ut is analog_ut;

Listing 3.3: Dichiarazione del tipo di dato analog ut e current ut

```

In figura 3.2 nella pagina precedente è possibile vedere come viene dichiarato il tipo di dati STD\_ULOGIC, mentre si sono definiti ANALOG\_UT e CURRENT\_UT fondamentalmente come tipo di dato REAL – figura 3.3 – con la particolarità di aver assegnato uno specifico significato ad alcuni valori.

Questi sono:

```

'ANALOG_U'/'CURRENT_U' (valore di tensione/corrente indefinito)

'ANALOG_X'/'CURRENT_X' (valore di tensione/corrente sconosciuto)

'ANALOG_Z' (valore di alta impedenza)

constant ANALOG_U : analog_ut := analog_ut 'left;

constant ANALOG_X : analog_ut := analog_ut (real(analog_ut 'left) / 2.0);

constant ANALOG_Z : analog_ut := analog_ut (real(analog_ut 'left) / 4.0);

Listing 3.4: Dichiarazione di ANALOG_U, ANALOG_X e ANALOG_Z

constant CURRENT_U : current_ut := current_ut 'left;

constant CURRENT_X : current_ut := current_ut 'left) / 2.0);

Listing 3.5: Dichiarazione di CURRENT_U e CURRENT_X

```

Come mostrato in figura 3.4 ANALOG\_U è definito come il minimo valore che può assumere il tipo di dati REAL, si noti che nel VHDL il valore iniziale – se non specificato nella dichiarazione – dell'oggetto, variabile o signal, di tipo T è T'left, quindi ANALOG\_U/CURRENT\_U è il valore iniziale al momento della dichiarazione del segnale.

ANALOG\_X e ANALOG\_Z sono definiti rispettivamente la metà e un quarto di ANALOG\_U.

Nella tabella 3.2 sono mostrati i valori di ANALOG\_U, ANALOG\_X, ANALOG\_Z che si sono ottenuti nelle nostre applicazioni, ma per come sono stati definiti essi possono cambiare al variare del simulatore.

Per questo motivo sono state implementate due funzioni di nome 'analog\_known' e 'current\_known', le quali restituiscono il valore booleano TRUE quando il segnale passato come argomento assume uno dei valori tra ANALOG\_U, ANALOG\_X, ANALOG\_Z o CURRENT\_U e CURRENT\_X.

| ANALOG_U | -1e+308   |

|----------|-----------|

| ANALOG_X | -5e + 307 |

| ANALOG_Z | -2,5e+307 |

Tabella 3.2.: Valore di default di ANALOG\_U, ANALOG\_X e ANALOG\_Z

Tra gli altri tipi dati definiti all'interno del package sono da citare le versioni vettoriali:

```

type analog_vector_ut is array (natural range <>) of analog_ut;

type current_vector_ut is array (natural range <>) of current_ut;

Listing 3.6: Dichiarazione di anaog_vector_ut e current_ut_vector

```

e le versioni 'resolved' ANALOG T e CURRENT T.

Quando viene usato un tipo di dati 'resolved' viene richiamata un funzione di risoluzione per decidere quale tra i segnali driver ha la priorità nell'assegnazione al segnale ricevente.

La figura 3.7 illustra la funzione di risoluzione per il tipo di dato std\_logic resolved dello std\_ulogic. Per il tipo di dati ANALOG\_T, viene implementata una tabella simile.

|          | Value_2    | ANALOG_Z   | ANALOG_X   | ANALOG_U   |

|----------|------------|------------|------------|------------|

| Value_1  | 'ANALOG_X' | 'Value_1'  | 'ANALOG_X' | 'ANALOG_X' |

| ANALOG_Z | 'Value_2'  | 'ANALOG_Z' | 'ANALOG_X' | 'ANALOG_X' |

| ANALOG_X | 'ANALOG_X' | 'ANALOG_X' | 'ANALOG_X' | 'ANALOG_X' |

| ANALOG_U | 'ANALOG_X' | 'ANALOG_X' | 'ANALOG_X' | 'ANALOG_X' |

Tabella 3.4.: Tabella di risoluzione di ANALOG\_T

```

type stdlogic_table is array(std_ulogic, std_ulogic) of std_ulogic;

constant resolution_table : stdlogic_table := (

```

```

U

Ζ

Χ

0

1

W

L

Н

'U'

'U'

'U'

'U'

'U'

'U'

'U'

'U

U

'X'

'X'

'Χ'

'U'

'Χ'

'X'

'X

'X

'U'

'Χ'

' 0 '

'Χ'

'0'

0'

'0'

' 0

1'

'1'

' 1 '

'U'

'Χ'

'Χ'

'1'

1'

'X

1

'U'

' 0 '

' 1

'Z '

'W'

'H

Z

'Χ'

1'

'U'

'0

'W'

'W'

'W'

'W'

'X

W

'1'

' L '

'0'

'W'

L'

'W'

'X

L

1'

'U'

'0'

'H'

'W'

'W'

'H

'X

Н

'X'

'Χ′

'Χ'

'X'

'Χ'

'X

);

```

Listing 3.7: Funzione di resoluzione del std logic (look-up table)

Essa può essere interpretata molto semplicemente considerando ANALOG\_Z come la condizione più debole e se un altro driver sta imponendo una tensione quest'ultimo avrà priorità maggiore. Altrimenti verrà assegnato il valore ANALOG\_X in quanto non è possibile avere un nodo con più livelli di tensione.

La tabella di risoluzione del tipo di dati CURRENT\_T è molto simile a quell'ANA-LOG\_T, dove la principale differenza sta nell'implementazione della legge di Kirchhoff delle correnti, quindi un segnale connesso a più driver risulterà la somma algebrica dei valori imposti dai driver.

|           | Value_2             | CURRENT_X   | CURRENT_U   |

|-----------|---------------------|-------------|-------------|

| Value_1   | 'Value_1 + Value_2' | 'CURRENT_X' | 'CURRENT_X' |

| CURRENT_X | 'CURRENT_X'         | 'CURRENT_X' | 'CURRENT_X' |

| CURRENT_U | 'CURRENT_X'         | 'CURRENT_X' | 'CURRENT_X' |

Tabella 3.6.: Tabella di risoluzione di CURRENT T

Ad eccezione di alcuni casi in cui avere più driver è imposto dal circuito da modellizzare, si consiglia l'utilizzo di tipi di dati unresolved. Questo permette di evitare eventuali cortocircuiti indesiderati tra 2 segnali, poichè in fase di compilazione vengono segnalate le net pilotate da più di un driver.

# 4. Netlister VHDL

### 4.1. Cadence VHDL Toolbox

Come esposto precedentemente si intende creare il modello Real Number di un prodotto in fase di progetto, i cui schematici analogici sono stati in precedenza predisposti in librerie di Virtuoso<sup>®</sup> Cadence.

Questo permette l'utilizzo del Netlister disponibile nella VHDL Toolbox di Virtuoso<sup>®</sup>.

Figura 4.1.: Schermata iniziale del Cadence VHDL Toolbox

Nella schermata iniziale – figura 4.1 – nel campo 'Run Directory' è neccessario introdurre il percorso di una cartella con permesso di scrittura, mentre nel campo 'Top Level Design' si inserisce la view dell'elemento di gerarchia superiore di cui si intende creare il modello.

Dopo aver impostato alcune opzioni, di cui alcune si parlerà in seguito, il Netlister andrà a generare due file contenenti entity ed architecture per ogni blocco di ciascun livello gerarchico inferiore, ed un unico file di configurazione per il blocco superiore.

Il Netlister utilizza il metodo in tre fasi per istanziare i componenti del VHDL'87:

#### • dichiarazione:

- serve a specificare le caratteristiche dell'interfaccia del componente

- la sintassi compare nella parte dichiarativa (prima di BEGIN) delle entity dell'architecture del blocco che istanzia il componente

### • specificazione (binding)

- per ogni componente istanziato, definisce la entity e l'architecture da utilizzare

- anch'esso nella parte dichiarativa o, come in questo caso, in un file di configurazione

#### • istanza

- è l'istruzione concorrente con cui si inserisce il componente figlio, all'interno del modello VHDL del genitore

- elenca implicitamente o esplicitamente le connessioni dei terminali dell'istanza ai segnali interni del genitore

- nella parte assertiva dell'architecture (tra BEGIN ed END)

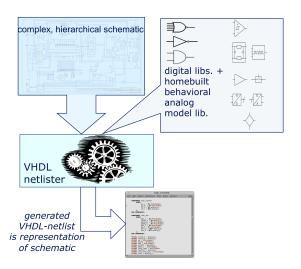

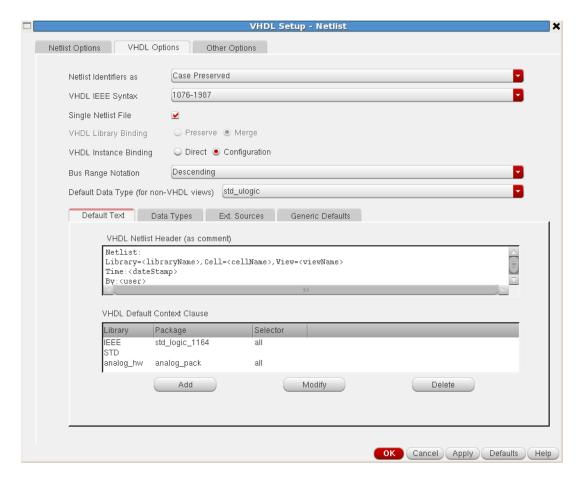

# 4.2. Vantaggi e setup del Netlister

Il primo vantaggio che il netlister offre è la capacità di recuperare automaticamente i blocchi delle porte logiche ed altri elementi puramente digitali dalle librerie presenti nel progetto. In questo passaggio si può intuire l'uso del file di configurazione infatti, nell'eventualità che le stesse celle venissero compilate in librerie con nome diverso, è sufficiente modificare le istruzione di binding presenti in un unico file. Questo fatto favorisce la portabilità e la riusabilità del lavoro.

Inoltre nel Setup – figura 4.3 – è possibile inserire il percorso delle cartelle utilizzate per salvare i modelli già realizzati, ed allo stesso modo delle porte logiche il programma li andrà automaticamente ad istanziare all'interno del blocco gerarchico superiore.

```

ARCHITECTURE <architecture father name > OF <entity father name > IS

-- [...]

component <entity son name>

[generic(<generic-list >); ]

port (A, B, CI: in std logic;

port(<port-list >);

end component;

- [...]

BEGIN

<label >: <component name>

PORT MAP (<port-association-list >);

END

CONFIGURATION < configuration name > OF < entity father name > IS

FOR <architecture son name>

FOR < label >: < component name >

USE ENTITY <library name >.<entity son name >(architecture son name);

FOR <architecture son name>

[...]

END FOR:

END FOR;

END FOR;

END <configuration name >;

```

Listing 4.1: Sintassi per l'istanza di un componente e di una configurazione in VHDL'87

In definitiva il Netlister permette di ridurre in due modi le cause di errore. Primo, creando la possibilità di atomizzare il lavoro di modellizzazione concentrandosi solo su piccoli/medi blocchi analogici che compongono i livelli gerarchici inferiori e semplificando quindi le funzioni da realizzare coi modelli. In secondo luogo, creando automaticamente le connessioni nelle gerarchie superiori.

Figura 4.2.: Schema di funzionamento del Netlister [7]

Un'altra funzionalità del programma, è la possibilità di personalizzare l'intestazione dei file VHDL, permettendo così di linkare i package delle librerie IEEE e analog\_hw come visto in figura 3.1 a pagina 39.

Questo consente di definire le porte dei modelli con i tipi di dato che si desiderano, ed esse verranno riconosciute dal blocco che li istanzia. Inoltre il netlister propaga il tipo di dato utilizzato per una porta in tutte le net e porte dei blocchi gerarchici superiori, ad eccezione del caso in cui un segnale risulti connesso a due porte di tipo diverso. In questa occasione lancia un warning sulla console, indicando il pin e le net responsabili e richiama una funzione di conversione predefinita, che nell'eventualità, si può modificare. Data la difficoltà di generalizzare quale sia la corretta procedura di conversione, si consiglia di provvedere manualmente alla risoluzione di tali problemi.

Figura 4.3.: Setup del netlister 1 – Intestazione del file VHDL

Figura 4.4.: Setup del netlister 2 – Percorso dei modelli

Come ultima nota sull'utilizzo del netlister si vuole indicare la possibilità di indicare al programma gli "Skip Design Unit". Questo elenco permette di far sostituire automaticamente gli elementi indicati – anche intere librerie – con dei circuiti aperti come potrebbe avvenire per alcuni capacitori. È anche possibile indicare in un modo diverso gli elementi che si vogliono sostituire con un cortocircuito, come può succedere per i resistori.

Figura 4.5.: Setup del netlister 3 – Skip Design Unit

# 5. Esempi di modelli VHDL

# 5.1. Regolatore ideale di tensione

Figura 5.1.: Schema del Regolatore di tensione

Lo schema in figura 5.1 si riferisce ad un regolatore di tensione presente nella Power Management Unit (PMU) del dispositivo.

Lo scopo della modellizzazione di questo elemento è quello di velocizzare la simulazione e quindi ridurre al minimo il numero di calcoli che il simulatore deve eseguire. Per questo il modello assegna semplicemente alle uscite del blocco il valore di tensione che idealmente dovrebbero avere, non appena si verificano le condizioni di abilitazione.

```

LIBRARY IEEE, STD;

USE IEEE.std logic 1164.all;

LIBRARY analog hw;

USE analog_hw.analog_pack.all;

5

ENTITY pmu vref 2v IS

PORT(

7

vdd 5v a

: IN

analog ut;

8

vdd 3v3 a

: IN

analog ut;

9

analog_ut;

VSS

IN

10

analog ut;

vss sense

: IN

11

: IN

analog ut;

vin

12

ibp 5u

current ut;

: IN

13

sleep_3v_n

: IN

std ulogic;

14

spi version n : IN

std ulogic;

15

vref_2v

: OUT analog ut;

16

vref 2v pad

: OUT analog ut;

17

vref 1v75

: OUT analog ut;

: OUT analog ut;

vref 1v46

19

vref 1v34

: OUT analog ut;

20

vref 1v28

: OUT analog ut;

21

vref_0v32

: OUT analog_ut;

22

vref 0v2

: OUT analog ut;

23

: OUT analog_ut

vref 0v175

24

);

25

END pmu vref 2v;

26

27

ARCHITECTURE schematic of pmu vref 2v IS

28

- Local SIGNALS and CONSTANTS -

29

constant vin th

: analog ut

:= 1.0;

30

constant vref 2v value

: analog ut

:= 2.0;

31

constant vref_2v_pad_value : analog_ut

:= 2.0;

32

constant vref 1v75 value

: analog ut := 1.75;

33

: analog_ut := 1.46;

constant vref_1v46_value

34

constant vref 1v34 value

: analog ut := 1.34;

35

constant vref 1v28 value

: analog ut

:= 1.28;

36

constant vref 0v32 value

: analog ut

:= 0.32;

: analog ut

constant vref 0v2 value

:= 0.2;

38

constant vref 0v175 value : analog ut

:= 0.175;

39

en internal

: std ulogic := '0';

signal

40

BEGIN

```

```

— Concurrent Signal Assignments —

en internal <= '1' when (

analog_known(vdd_5v_a)

43

and analog known (vdd 3v3 a)

44

and analog_known(vin)

45

and (vin > vin_th)

46

and current known (ibp 5u)

and (sleep 3v n = '1')

48

else '0';

49

vref 2v

<= vref 2v value

when en internal = '1' else analog ut(0.0);

50

vref_2v_pad <= vref_2v_pad_value when en_internal = '1' else analog_ut(0.0);</pre>

51

vref 1v75

<= vref_1v75_value</pre>

when en_internal = '1' else analog_ut(0.0);

52

when en internal = '1' else analog ut (0.0);

vref 1v46

<= vref 1v46 value

53

vref 1v34

<= vref_1v34_value</pre>

when en_internal = '1' else analog_ut(0.0);

54

vref 1v28

<= vref_1v28 value

when en internal = '1' else analog ut(0.0);

55

when en_internal = '1' else analog_ut(0.0);

vref_0v32

<= vref 0v32 value

56

vref_0v2

<= vref_0v2_value

when en_internal = '1' else analog_ut(0.0);

57

vref_0v175 \le vref_0v175_value

when en_internal = '1' else analog_ut(0.0);

58

```

# 5.2. Comparatore

Figura 5.2.: Schema del comparatore

Quest'esempio è un comparatore di due livelli di tensione ed uscita digitale. In esso è possibile osservare che si è riportato un'isteresi simmetrica sulla soglia di transizione ed il tempo di propagazione dagli ingressi all'uscita.

Come si può vedere il modello ignora gli effetti delle impedenze connesse ai suoi PIN. Inoltre può essere interessante notare che l'istruzione VHDL 'after' fornisce un filtro temporale sulle transizioni degli ingressi, questo evita che il comparatore riporti in uscita variazioni con durata inferiore al tempo di propagazione.

```

LIBRARY IEEE, STD;

USE IEEE.std logic 1164.all;

LIBRARY analog hw;

USE analog_hw.analog_pack.all;

5

ENTITY comparator pmos medium IS

6

PORT(

7

in m

: IN

analog ut;

8

in p

: IN

analog ut;

9

ibp_5u

: IN

current_ut;

10

ibp 2u5 : IN

current ut;

11

: IN

std ulogic;

en n

12

hyst n

std ulogic;

: IN

13

out o

: OUT std ulogic

14

);

15

END comparator_pmos_medium;

16

17

ARCHITECTURE beh of comparator pmos medium IS

19

— Local SIGNALS and CONSTANTS ——

20

constant ibp 5u treshold

: current ut := 4.5e-6;

21

constant ibp_2u5_treshold : current_ut := 2.0e-6;

22

signal

enable cond

: boolean;

23

signal

v a

: analog ut;

d int

: std logic

signal

:= '0';

signal

out o temp

: std logic;

26

— hysteresis, threshold margin

27

constant v_hys

: analog_ut := 0.04;

28

threshold

: analog_ut := v_hys;

signal

29

— propagation delay

constant t delay

: time

:= 100 \text{ ns};

31

32

BEGIN

33

— Concurrent Signal Assignments —

34

enable cond <= TRUE when ( analog known(ibp 5u)

and

35

( ibp 5u > ibp 5u treshold )

and

36

analog known(ibp 2u5)

and

37

( ibp_2u5 > ibp_2u5_treshold ) and

38

(en_n = '0')

39

else FALSE;

40

-- Differential signal input

41

```

```

<= (in_p - in_m) when enable_cond</pre>

42

v_a

else analog_ut(0.0);

43

- Treshold valutation

44

threshold

<= -v_hys when ( out_o_temp = '1' )</pre>

45

else v_hys;

46

-- Processes ----

47

comp:

48

process( v_a, enable_cond )

49

50

if enable_cond then

51

if (v_a > threshold) then

— input above reference

52

d int <= '1';

53

— input below reference

else

54

d int <= '0';

55

end if;

56

else

57

d_int <= '0';

58

end if; — enable cond

end process; -- comp

60

61

out o temp <= d int after t delay;

62

63

out\_o

<= out_o_temp;</pre>

64

65

END beh;

```

### 5.3. Blocco di Soft Start

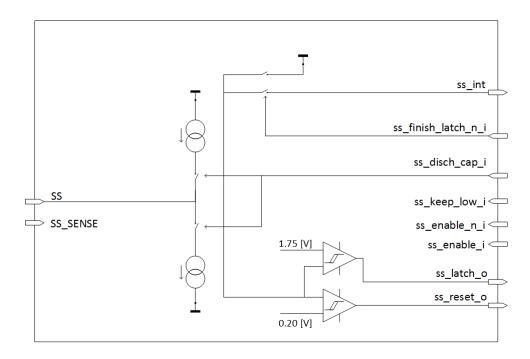

Figura 5.3.: Schema del blocco di Soft Start

In figura 5.3 viene riportato uno schema semplificato del blocco di Soft Start, il cui funzionamento è sinteticamente descritto nel paragrafo 2.1.3 a pagina 31.

Nel modello è stata riportata la generazione della rampa di tensione in funzione delle correnti che caricano o scaricano il capacitore, il cui valore di capacità è stato posto come un segnale all'interno dell'architecture.

Il blocco inoltre presenta l'istanza di due comparatori per segnalare alla logica che gestisce i segnali di controllo, l'attraversamento della tensione sul capacitore delle due soglie di riferimento.

```

LIBRARY IEEE, STD;

USE IEEE.std logic 1164.all;

LIBRARY analog hw;

USE analog_hw.analog_pack.all;

ENTITY soft_start_block IS

PORT(

analog_ut;

vdd 3v3 a

: IN

7

vss a

: IN

analog ut;

8

: IN

current ut;

9

ibp 5u rpp ss

vref

: IN

analog_ut;

10

std ulogic;

ss enable

: IN

11

ss finish latch n : IN

std ulogic;

12

ss disch cap

std ulogic;

: IN

13

vref 1v75

: IN

analog ut;

14

: IN

ss pad

std ulogic;

15

ss_pad_sense

: IN

analog_ut;

16

ss enable n

: IN

std ulogic;

17

ss keep low

: IN

std ulogic;

: IN

vref 0v2

analog ut;

19

pok

: IN

std ulogic;

20

ss latch

: OUT std ulogic;

21

ss\_reset

: OUT std_ulogic;

22

ss int

: OUT analog ut

23

24

);

END soft start block;

25

26

ARCHITECTURE beh of soft start block IS

27

COMPONENT comparator_pmos_medium

28

PORT(

29

out o

: OUT std ulogic;

30

IN

in m

analog ut;

31

hyst n

:

IN

std ulogic;

32

ibp 2u5 : IN

current ut;

33

en n

: IN

std_ulogic;

34

ibp_5u : IN

current ut;

35

in p

IN

analog ut

36

END COMPONENT;

38

Local SIGNALS and CONSTANTS

39

constant vdd_3v3_a_threshold

: analog_ut := 3.0;

40

constant ibp_5u_rpp_ss_threshold : current_ut := 4.5e-6;

41

```

```

signal

net33

: current ut;

42

signal

net35

: current ut;

43

signal

net36

: current ut;

44

signal

net37

: current ut;

45

signal

hyst n

: std_ulogic := '0';

46

signal

enable cond

: boolean;

47

-- Passo temporale fisso per la generazione della rampa

48

signal

ss time step

: time

:= 5 \text{ ns};

49

constant one psec

: time

:= 1 ps;

50

: analog_ut;

signal

charge_ampl_step

51

discharge_ampl_step

: analog ut;

signal

52

signal

vcap temp

: analog_ut := 0.0;

53

signal

v cap

: analog ut := 0.0;

54

signal