| Title            | Current increment of tunnel field-effect transistor using InGaAs nanowire/Si heterojunction by scaling of channel length                                                                                                                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)        | Tomioka, Katsuhiro; Fukui, Takashi                                                                                                                                                                                                                                                                                                                                  |

| Citation         | Applied Physics Letters, 104(7), 073507<br>https://doi.org/10.1063/1.4865921                                                                                                                                                                                                                                                                                        |

| Issue Date       | 2014-02-19                                                                                                                                                                                                                                                                                                                                                          |

| Doc URL          | http://hdl.handle.net/2115/56399                                                                                                                                                                                                                                                                                                                                    |

| Rights           | Copyright 2014 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and the American Institute of Physics. The following article appeared in Appl. Phys. Lett. 104, 073507(2014) and may be found at http://scitation.aip.org/content/aip/journal/apl/104/7/10.1063/1.4865921 |

| Туре             | article                                                                                                                                                                                                                                                                                                                                                             |

| File Information | 1.4865921.pdf                                                                                                                                                                                                                                                                                                                                                       |

## Current increment of tunnel field-effect transistor using InGaAs nanowire/Si heterojunction by scaling of channel length

Katsuhiro Tomioka and Takashi Fukui

Citation: Applied Physics Letters 104, 073507 (2014); doi: 10.1063/1.4865921

View online: http://dx.doi.org/10.1063/1.4865921

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/104/7?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Band offset determination of mixed As/Sb type-II staggered gap heterostructure for n-channel tunnel field effect transistor application

J. Appl. Phys. 113, 024319 (2013); 10.1063/1.4775606

Size, composition, and doping effects on In(Ga)As nanowire/Si tunnel diodes probed by conductive atomic force microscopy

Appl. Phys. Lett. 101, 233102 (2012); 10.1063/1.4768001

Role of InAs and GaAs terminated heterointerfaces at source/channel on the mixed As-Sb staggered gap tunnel field effect transistor structures grown by molecular beam epitaxy

J. Appl. Phys. 112, 024306 (2012); 10.1063/1.4737462

Tunnel field-effect transistor using InAs nanowire/Si heterojunction

Appl. Phys. Lett. 98, 083114 (2011); 10.1063/1.3558729

Boosting the on-current of a n -channel nanowire tunnel field-effect transistor by source material optimization

J. Appl. Phys. **104**, 064514 (2008); 10.1063/1.2981088

## Current increment of tunnel field-effect transistor using InGaAs nanowire/Si heterojunction by scaling of channel length

Katsuhiro Tomioka<sup>1,2,a)</sup> and Takashi Fukui<sup>1</sup>

<sup>1</sup>Graduate School of Information Science and Technology and Research Center for Integrated Quantum Electronics (RCIQE), Hokkaido University, Sapporo 060-8628, Japan

<sup>2</sup>Japan Science and Technology Agency (JST)-PRESTO, Honcho Karaguchi, Saitama 332-0012, Japan

(Received 17 July 2013; accepted 1 February 2014; published online 19 February 2014)

We report on a fabrication of tunnel field-effect transistors using InGaAs nanowire/Si heterojunctions and the characterization of scaling of channel lengths. The devices consisted of single InGaAs nanowires with a diameter of 30 nm grown on p-type Si(111) substrates. The switch demonstrated steep subthreshold-slope (30 mV/decade) at drain-source voltage ( $V_{DS}$ ) of 0.10 V. Also, pinch-off behavior appeared at moderately low  $V_{DS}$ , below 0.10 V. Reducing the channel length of the transistors attained a steep subthreshold slope ( $<60 \,\mathrm{mV/decade}$ ) and enhanced the drain current, which was 100 higher than that of the longer channels. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4865921]

The heterointerface of III-V nanowires (NWs) and Si raised possibilities as a specific heterojunction for several optoelectronic and electrical devices such as solar cells, <sup>1,2</sup> Esaki tunnel diodes, <sup>3,4</sup> and tunnel field-effect transistors (TFETs). <sup>5–8</sup> III-V nanowire/Si heterojunctions with less dislocations have been achieved due to recent progress in epitaxial techniques such as selective-area growth (SAG) regardless of any mismatch in lattice constant and thermal coefficients, which have enabled the integration of III-V NWs on Si with precise positioning and vertical alignment. <sup>9–11</sup> This nm-scaled heteroepitaxy has produced inherently abrupt junctions across the III-V nanowire and Si and has demonstrated the potential of steep subthreshold slope (SS) switches using InAs NW/Si heterojunctions. <sup>8,12</sup>

Conventional integrated circuits using Si complementary metal-oxide-semiconductor (CMOS) technology are now confronted with a serious problem where a huge amount of power is consumed as integration density increases due to the miniaturization of FETs. This is because miniaturizing FETs poses difficulties in suppressing off-state leakage current and shortchannel effects. However, CMOS technologies are now exploring multi-gate structures<sup>13</sup> and non-Si channel materials<sup>14,15</sup> to overcome these problems. Another issue in conventional FETs is the physical limitation of SS caused by carrier thermal diffusion (SS =  $2.3 k_B T/q = 60 \text{ mV/decade}$  at room temperature (RT)). This limitation will stop further scaling of power consumption even if multi-gate structures and high-performance III-Vs or Ge are introduced to the conventional CMOS technologies. Steeper-slope transistors based on TFETs<sup>16-18</sup> are, therefore, being explored as alternative switches because their architecture basically has excellent compatibility with that of the present FET-process and would reduce the required supply voltage below 0.5 V. The conventional TFETs fabricated from all III-V materials, however, have difficulty in forming the abrupt p-n junctions required for steep SS. Thus, the heterointerfaces of III-V NW/Si systems would be good candidates to use in tunnel diodes or TFETs.

These heterojunctions for TFET applications have not been thoroughly investigated, and reports have specified their use in InAs NW/Si systems. 5,6,8,12 Thus, we have to discuss the feasibility of using other III-V NW/Si heterojunctions for future TFET applications. In this regard, InGaAs NW/Si heterojunctions are good candidates to utilize for TFET applications because InGaAs has bandgap tuning capabilities, allowing narrow InAs- and wide GaAs-like band structures. The Schottky barrier height (SBH) at the gate-oxide/InGaAs interface can simply be controlled by changing the In-composition. 19 In addition, this ternary is a better candidate to utilize several band-engineered heterostructures such as high-electron mobility structures. 11 In this report, we studied the TFETs using InGaAs NW/Si heterojunctions with a vertical surrounding-gate structure and characterized scaling effect of channel lengths.

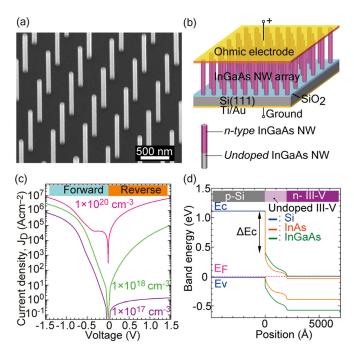

In the experiment, we used a p-type Si(111) substrate with B doping of  $1 \times 10^{17}$  cm<sup>-3</sup> –  $1 \times 10^{20}$  cm<sup>-3</sup>. The growth condition of SAG for the InGaAs NWs on Si(111) and the method of controlling the directions of NW-growth were previously reported. The opening diameters were 30 and 70 nm. Vertically aligned InGaAs NWs (numbers of 250 NW with a pitch of 600 nm) were grown on Si(111). The In composition was 70%. Representative growth results are shown in Fig. 1(a). These NWs had  $n^+$ -InGaAs/undoped-InGaAs axial junction as schematically outlined in the inset of Fig. 1(b). The carrier concentrations of the  $n^+$ -InGaAs and undoped InGaAs NWs were  $2 \times 10^{18}$  cm<sup>-3</sup> for the former and  $3 \times 10^{16}$  cm<sup>-3</sup> for the latter. These concentrations were estimated from top-gated NW FETs. The typical length of the undoped region was 200 nm and that of the Si-doped region was 1200 nm.

A two-terminal device for diode characterization was first fabricated on the p-Si substrate as shown in Fig. 1(b). The diameter of InGaAs NWs was 70 nm. The current density ( $J_D$ )-voltage (V) curve (the Si substrate was grounded) is plotted in Fig. 1(c). The measured current was divided by the number of NWs (250 NWs) and normalized by the surface contact area. Positive voltage in this diode was in the reversed bias direction against the p-i-n junction. The  $J_D$ -V curve indicates typical rectification properties under forward

a) Author to whom correspondence should be addressed. Electronic mail: tomioka@rciqe.hokudai.ac.jp

FIG. 1. (a) Representative SEM image showing InGaAs NWs grown on Si(111). (b) Illustration of InGaAs NW/Si heterojunction diode. (c) Diode characteristics. The numbers in this panel denote the carrier concentration of *p*-Si substrate. (d) Band-diagram of InGaAs NW/Si heterojunction calculated with 1D Poisson-Schrödinger equation.

bias (-1.0 < V < 0) with an ideality factor of 1.9. The  $J_D$ under reverse bias (0 < V < 1.0) increases as the carrier concentration of p-Si increases. The current in the reverse direction was found to be Zener tunneling transport across the InGaAs NW/Si heterojunction similar to that in the InAs NW/Si heterojunction. 11,12 Esaki tunneling transport was also observed in the forward bias direction (V = -0.3 V) for a heavily doped p-Si substrate  $(n = 1 \times 10^{20} \,\mathrm{cm}^{-3})$ . This is because the Fermi level lay underneath the valence band in p-Si for  $n = 1 \times 10^{20} \,\mathrm{cm}^{-3}$ . Fig. 1(d) is a band diagram calculated with a one-dimensional Poisson-Schrödinger equation, in which the band diagram has staggered type-II band discontinuity. We set the carrier concentration of p-Si to  $1 \times 10^{18} \,\mathrm{cm}^{-3}$  in this calculation. These behaviors suggest that controlling the position of the Fermi level by various electrical fields modulated the tunneling transports induced at the InGaAs NW/Si heterojunction.

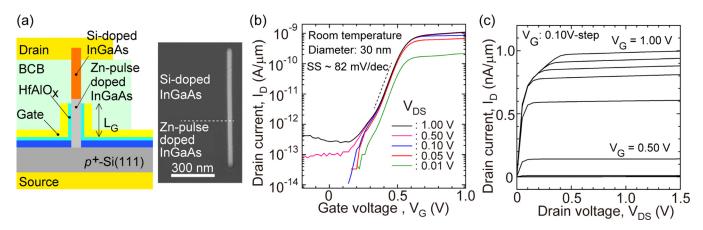

Next, we fabricated the vertical TFET in Fig. 2(a). A single vertically aligned n<sup>+</sup>-InGaAs/Zn-pulse doped InGaAs axial NW was grown on the  $p^+$ -Si substrate (carrier concentration =  $1 \times 10^{19} \,\mathrm{cm}^{-3}$ ). The NW was 30 nm in diameter as seen in the inset of Fig. 2(a). The device processes for the vertical TFET were the same as those previously reported.<sup>5,11,12</sup> Atomic layer deposition for the gate oxide was used to cover the surface of the NW with a 7-nm-thick Hf<sub>0.8</sub>Al<sub>0.2</sub>O<sub>x</sub> for a high-k gate dielectric. The gate metal was photolithography-defined tungsten (W) deposited by radio-frequency (RF) sputtering. The gate length (L<sub>G</sub>) depended on the etching time. The L<sub>G</sub> was 150 nm, which corresponded to the length of the Zn-pulse doped InGaAs NW-channel. A Ti/Pd/Au non-alloy Ohmic electrode was deposited after reactive-ion etching (RIE). Finally, the device was annealed at  $400\,^{\circ}\text{C}$  in  $N_2$  for 5 min.

We used zinc (Zn)-pulse doping 12 for the InGaAs NW-channels to reduce unintentional n-type doping of the InGaAs NWs, because important points in obtaining steeper SS are low carrier density in undoped III-V NW regions, less modulation of surface accumulation in the III-V NWs, and reduced diameter of III-V NW/Si heterointerfaces. These points arise from increments in NW-channel resistance and heterojunction resistance that induce large internal electric fields under lower bias. Pure intrinsic III-V NW channels are ideally required to induce large internal electric fields at III-V NW/Si heterojunctions under small bias. However, undoped InGaAs NWs had slightly high carrier density in this TFET due to unintentional n-type doping with  $10^{16}$ – $10^{17}$  cm<sup>-3</sup> using metalorganic vapor phase epitaxy (MOVPE),<sup>21</sup> which probably originated from contamination from MO precursors. This unintentional doping in InGaAs NW channels lowered the resistance in channel region among the series resistances of device. In this case, it is difficult to induce an internal voltage to heterojunction or channel region at low  $V_{\rm G}$  and  $V_{\rm DS}$ . This meant large bias was required to induce tunnel transport, which resulted in large SS above 60 mV/decade. A compensation doping effect using a p-type dopant was therefore introduced during the growth of the undoped InGaAs NW-channel. In this case, Zn atoms from diethylzinc (DEZn) were utilized to compensate for the unintentional doping in the InGaAs NWs. The carrier concentration of the Zn dopant was approximately estimated

FIG. 2. (a) Illustration of device structure and SEM image of single InGaAs NW with diameter of 30 nm. (b) Transfer characteristic of TFET using InGaAs NW (Si-doped InGaAs/Zn-compensated InGaAs axial NW)/Si heterojunction. (c) Output characteristics.

to be  $\sim 1 \times 10^{17} \, \text{cm}^{-3}$ , measured from the secondary ion mass spectroscopy (SIMS) profile on Zn-doped InGaAs planar layer grown under the same doping conditions. The Zn-pulsed doping is composed of DEZn with a pulse of 1 s alternately supplied with an interval of 9 s. This sequence was repeated 18 times to make a Zn-compensated InGaAs NW-channel. The benefit of the Zn-pulsed doping is to achieve very small amount of impurities in the tiny NWs. It is usually difficult to doze such very few dopants for conventional doping since single Zn atom in InGaAs NW with 30 nm in diameter and 1 nm in height corresponds to  $\sim$ 4 × 10<sup>17</sup> cm<sup>-3</sup>. We formed Si-doped InGaAs/Zn-pulse doped InGaAs axial NWs under the same conditions as those of the sample in Fig. 2(a). If the Zn dopant compensates for almost all the unintentional dopants, the InGaAs NW-channel become near intrinsic layer. We estimated the carrier concentration (N<sub>D</sub>) of the Zn-pulse doped InGaAs NW from the threshold voltage of the vertical FET. The N<sub>D</sub> of the InGaAs NWs was estimated to be  $7.8 \times 10^{15} \, \text{cm}^$ which was lower than that of non-doped InGaAs NWs  $(N_D = 5.2 \times 10^{16} \, \text{cm}^{-3})$ , see supplementary material for Fig. S1).12

Figures 2(b) and 2(c) show switching properties of a single InGaAs NW/Si TFET at a drain-source voltage (V<sub>DS</sub>) of 0.01-1.00 V. The L<sub>ch</sub> is 200 nm and L<sub>G</sub> is 150 nm. The curve was measured using a parameter analyzer (Agilent 4156C) at RT in the dark. The current values were normalized using a gate perimeter (0.22  $\mu$ m). Switching properties with an average SS of 82 mV/decade were observed in the reverse bias direction ( $V_G$  was positive for the n-i-p junction). The ratio of ON/OFF current was approximately 10<sup>4</sup> at a V<sub>DS</sub> of 0.50 V. More importantly, this switching behavior appeared at a V<sub>DS</sub> of 10 mV. The turn-on (threshold) voltage, V<sub>T</sub>, of the  $I_D$  was 0.40 V. The  $I_D$  has a slight dependence on  $V_{DS}$  in Fig. 2(b), which is different from conventional FETs. The tunneling probability from the p-Si to InGaAs is thought to become constant under high V<sub>G</sub>. The tunnel junction in this device did not have a well gated structure. It seemed to induce very high electrical field that led to impact ionization, but the switching behavior at a V<sub>DS</sub> of 10 mV suggested the transport and switching mechanisms were not an ionization mechanism. The I<sub>D</sub> in Fig. 2(b) has a slight dependence on the V<sub>DS</sub> with drain induced barrier lowering (DIBL) of 5 mV/V because the DIBL in itself is inherently low in the device under reverse bias conditions. Figure 2(c) plots the  $I_D-V_{DS}$  curves for  $V_G$  ranging from 0 to 1.00 V. The curves indicate pinch-off behavior under low V<sub>DS</sub>, where I<sub>D</sub> started to be saturated,  $V_{DS} > 0.1 \text{ V}$ . This pinch-off behavior totally differed in both the conventional FETs and InAs NW/Si heterojunction TFETs demonstrating sub-linear dependence due to poor gate controllability. The superior pinch-off behavior for the InGaAs NW/Si was thought to have resulted from the better controllability of electrostatic gate bias controllability because of the fixed SBH and Fermi level close to the conduction band due to the In-composition of InGaAs. 19

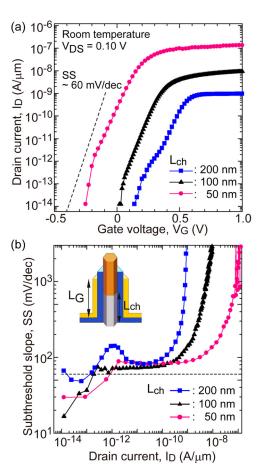

Next, we investigated the scaling effect of channel length ( $L_{\rm ch}$ ). Fig. 3(a) shows the  $L_{\rm ch}$  dependence on the transfer curve at a  $V_{\rm DS}$  of 0.10 V. The  $L_{\rm G}$  was fixed to 150 nm, and the growth condition and sequence of the Zn-pulse doping was same for the different  $L_{\rm ch}$ . We chose a

FIG. 3. (a) Transfer characteristics with variation of  $L_{\rm ch}$ .  $V_{\rm DS}$  is 0.10 V at RT in the dark. Dashed line plots theoretical limitation of carrier thermal diffusion (SS  $\sim$  60 mV/decade). (b) Subthreshold slope as a function of  $I_{\rm D}$ . Dashed line is SS = 60 mV/dec. Inset illustrates NW-channel.

low V<sub>DS</sub> to characterize steep turn-on behavior. Fig. 3(b) exhibits SS with variations in drain current. There are two regions in these curves, i.e., steep SS and large SS regions, which have already been observed in InAs/Si steep-SS transistors<sup>11,12</sup> and calculations.<sup>22</sup> The minimum SS in the steep-SS region below 60 mV/decade achieved 48 mV/dec for  $L_{ch} = 200 \,\text{nm}$  and  $30 \,\text{mV/decade}$  for  $L_{ch} = 50 \,\text{nm}$ . The coexistence of a steep SS and a large SS region is similar to those of calculated behaviors in TFETs.<sup>22</sup> The steep SS region depends on degeneration, controlled by carrier concentration, in the source region. The carrier concentration in Fig. 3 corresponds to non-degenerate or weak degenerate conditions. The reason for the appearance of the steep-SS window has another origin, that is, III-V/Si heterojunction inherently poses specific band discontinuity to suppress the off-state leakage current. The effect of an electron pocket layer using heterojunctions in different InGaAs alloys was recently investigated to suppress parasitic leakage current.<sup>23</sup> The very low parasitic leakage current at low V<sub>DS</sub> in the InGaAs NW/Si TFET also demonstrated a similar effect, which indicated the InGaAs NW/Si heterojunction inherently formed similar heterojunction as an electron pocket layer. The steep SS characteristics are also similar to those of calculated behaviors in TFETs.<sup>22</sup>

The steep SS region ( $<60 \,\mathrm{mV/decade}$ ) in Fig. 3(b) tends to widen with decreasing  $L_{\rm ch}$ . The current at the boundary from sub- to super- $60 \,\mathrm{mV/decade}$  ( $I_{60}$ )<sup>24</sup> also increases for

shorter  $L_{ch}$ . The  $I_{60}$  was  $10^{-12}$  A/ $\mu m$  for  $L_{ch} = 50$  nm. Thus, an internal electrical field with short Lch was effectively induced as compared to the longer L<sub>ch</sub>. The volume of the NW-channel for  $L_{ch} = 50 \, \text{nm}$  simply resulted in four-fold resistivity compared with  $L_{ch} = 200 \, \text{nm}$  that induced higher internal electrical fields. The region of super-60 mV/decade was resulted from that the tunneling transport in this region was dominated by the trap-assisted tunneling through the defect level, which was formed at InGaAs NW/Si heterojunction. The defect level was originated from misfit dislocation due to lattice mismatch. Recently, the numbers of misfit dislocation could be decreased as the diameter of heterojunction decreased. 12 Thus the coherent growth regardless of misfit dislocation should be achieved by reducing the opening diameter in order to suppress the trap-assisted tunneling process. Further investigations by using the very small opening diameter (<10 nm) are required as next issue.

Another effect of scaling in  $L_{ch}$  is enhanced  $I_D$ . The  $I_D$  in Fig. 3(a) achieved with short  $L_{ch}$  reached  $10^{-7}\,A/\mu m$  which is 100 times that of longer  $L_{ch}$ . This indicates that a source edge would be better close to the tunnel junction to enhance  $I_D$  since tunneling carriers are subject to influence from scattering processes in longer channels. In addition, the device structure in this case had no ideal well-gated structure at the heterointerface. The  $L_{ch}$  underneath the gate electrode should therefore be shorter than the gate length to effectively apply an electrical field from the gate. The scaling on  $L_{ch}$  to increasing  $I_D$  would be predictably effective for Lch < 10 nm because the tunnel distance is usually on the scale of several nanometers. Thus, scaling  $L_{ch}$  has a synergetic effect on increasing both  $I_{60}$  and  $I_D$ .

In summary, we have demonstrated the fabrication of tunnel FETs using an InGaAs NW/Si heterojunction. The switch offered by the InGaAs NW/Si heterojunction demonstrated steep turn-on behavior, very small DIBL and better pinch-off behaviors. The scaling of channel lengths that indicated a steep SS window widened while increasing  $I_{60}$  in channel lengths of 50 nm. The drain current was also enhanced to 100 times due to the source edge being close to the tunnel junction. Additional techniques are required to further increase  $I_{60}$  and  $I_{\rm D}$  in practical devices while expanding the steep SS window.

This work was financially supported by a Grant-in-Aid for Scientific Research from the Ministry of Education, Culture, Sports, Science and Technology (MEXT) and Japan Science and Technology Agency (JST)-PRESTO program.

- <sup>1</sup>W. Wei, X.-Y. Bao, C. Soci, Y. Ding, Z.-L. Wang, and D. Wang, Nano Lett. **9**, 2926 (2009).

- <sup>2</sup>J. C. Shin, K. H. Kim, K. J. Yu, H. Hu, L. Yin, C.-Z. Ning, J. A. Rogers, J.-M. Zuo, and X. Li, Nano Lett. 11, 4831 (2011).

- <sup>3</sup>M. T. Björk, H. Schmid, C. D. Bessire, K. E. Moselund, H. Ghoneim, S. Karg, E. Lörtscher, and H. Riel, Appl. Phys. Lett. 97, 163501 (2010).

- <sup>4</sup>T. Yang, S. Hertenberger, S. Morkötter, G. Abstreiter, and G. Koblmüller, Appl. Phys. Lett. **101**, 233102 (2012).

- <sup>5</sup>K. Tomioka and T. Fukui, Appl. Phys. Lett. **98**, 083114 (2011).

- <sup>6</sup>K. E. Moselund, H. Schmid, C. Bessire, M. T. Björk, H. Ghoneim, and H. Riel, IEEE Electron Devices Lett. 33, 1453 (2012).

- <sup>7</sup>C. D. Bessire, M. T. Björk, H. Schmid, A. Schenk, K. B. Reuter, and H. Riel, Nano Lett. 11, 4195 (2011).

- <sup>8</sup>K. Tomioka, M. Yoshimura, and T. Fukui, IEEE VLSI Symp. Tech. Dig. 2012, 47.

- <sup>9</sup>K. Tomioka, J. Motohisa, S. Hara, and T. Fukui, Nano Lett. **8**, 3475 (2008).

- <sup>10</sup>K. Tomioka, Y. Kobayashi, J. Motohisa, S. Hara, and T. Fukui, Nanotechnology 20, 145302 (2009).

- <sup>11</sup>K. Tomioka, M. Yoshimura, and T. Fukui, Nature **488**, 189 (2012).

- <sup>12</sup>K. Tomioka, M. Yoshimura, and T. Fukui, Nano Lett. **13**, 5822 (2013).

- <sup>13</sup>I. Ferain, A. A. Colinge, and J.-P. Colinge, Nature **479**, 310 (2011).

- <sup>14</sup>J. A. del Alamo, Nature **479**, 317 (2011).

- <sup>15</sup>R. Pillarisetty, Nature **479**, 324 (2011).

- <sup>16</sup>A. C. Seabaugh and Q. Zhang, Proc. IEEE **98**, 2095 (2010).

- <sup>17</sup>W.-Y. Choi, B.-G. Park, J. F. Lee, and T.-J. K. Liu, IEEE Electron Devices Lett. 28, 743 (2007).

- <sup>18</sup>R. Gandhi, Z. Chen, N. Singh, K. Benerjee, and S. Lee, IEEE Electron Devices Lett. 32, 437 (2011).

- <sup>19</sup>H. H. Wieder, J. Vac. Sci. Technol. B **21**, 1915 (2003).

- <sup>20</sup>J. Noborisaka, T. Sato, J. Motohisa, S. Hara, K. Tomioka, and T. Fukui, Jpn. J. Appl. Phys. 46, 7562 (2007).

- <sup>21</sup>Z. M. Fang, K. Y. Ma, R. M. Cohen, and G. B. Stringfellow, Appl. Phys. Lett. **59**, 1446 (1991).

- <sup>22</sup>L. D. Michielis, L. Lattanzio, K. E. moselund, H. Riel, and A. M. Ionescu, IEEE Electron Devices Lett. 34, 726 (2013).

- <sup>23</sup>G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, IEEE IEDM Tech. Dig. 2011, 785.

- <sup>24</sup>W. G. Vandenberghe, A. S. Verhulst, B. Sorée, W. Magnus, G. Groeseneken, Q. Smets, M. Heyns, and M. V. Fischetti, Appl. Phys. Lett. 102, 013510 (2013).

- <sup>25</sup>See supplementary material at http://dx.doi.org/10.1063/1.4865921 for the effect of Zn pulse doping of InGaAs nanowire.